## WICAT

# System 150

Hardware Reference Manual

187-055-201B

# 27 September 1983

WICAT SYSTEMS INCORPORATED

· · · · · ·

Orem, Utah

,

## Copyright Statement

Copyright C 1983 by WICAT Systems Incorporated All Rights Reserved Printed in the United States of America

Receipt of this manual must not be construed as any kind of commitment, on the part of WICAT Systems Incorporated, regarding delivery or ownership of items manufactured by WICAT.

This manual is subject to change without notice.

WARNING: The equipment described in this manual generates, uses, and can radiate radio frequency energy, and if not installed in accordance with instructions provided in the hardware documentation for the equipment, may interfere with radio communications. Furthermore, the equipment has been tested and found to comply with the limits for a Class A computing device pursuant to subpart J, Part 15 of FCC rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of the equipment (described in this manua!) in a residential area is likely to cause interference. Where the equipment will be used in a residential area, it is the user's responsibility to ensure that any interference is corrected.

## Revision History

First Printing July 1982 Second Printing September 1983

## The Purpose of This Manual

This document provides the technical information users will need should they want to modify or program the System 150 PC boards to interface with peripheral devices not supplied by WICAT Systems, Inc.

## Intended Audience

Field service technicians, OEM representatives, and WICAT maintenance personnel. Readers must be knowledgable in electronics and familiar with the hardware terminology of computer science.

# Table Of Contents

## CHAPTER 1 SYSTEM OVERVIEW

.

| 1.1     | INTRODUCTION                      |

|---------|-----------------------------------|

| 1.2     | FEATURES OF THE SYSTEM 150        |

| 1.3     | SYSTEM CONFIGURATION              |

| 1.4     | SYSTEM COMPONENTS                 |

| 1.4.1   | Central Processing Unit (CPU) 1-3 |

| 1.4.2   | Memory                            |

| 1.4.3   | Storage                           |

| 1.4.4   | Other Elements                    |

| 1.4.4.1 |                                   |

| 1.4.4.2 | ÷                                 |

| 1.5     | PLACEMENT OF BOARDS               |

| 1.6     | PC BOARD INTERACTION              |

| 1.6.1   | Explanation Of Bus Structure 1-5  |

| 1.6.2   | Bus Control                       |

| 1.6.3   | Serial Priority Bus Control 1-6   |

| 1.7     | SYSTEM DATA FLOW                  |

| 1.8     | CONTROLLER INTERFACE              |

| 1.8.1   | Serial Interfaces                 |

| 1.8.2   | Parallel Interface                |

| 1.8.3   |                                   |

CHAPTER 2 CPU BOARD

| 2.1     | INTRODUCTION                                       |

|---------|----------------------------------------------------|

| 2.2     | CPU BOARD CONFIGURATION                            |

| 2.3     | MICROPROCESSOR CIRCUITRY                           |

| 2.3.1   | System Memory Map                                  |

| 2.3.2   | MC68000 Peripheral Control                         |

| 2.4     | THE MULTIBUS INTERFACE                             |

| 2.4.1   | Bus Arbitration Circuitry                          |

| 2.4.2   | Interrupt Circuitry                                |

| 2.4.3   | Interrupt Control                                  |

| 2.4.4   | The Multibus Interface                             |

| 2.4.5   | Address Bus                                        |

| 2.4.6   | Data Bus                                           |

| 2.4.7   | Asynchronous Bus Control                           |

| 2.4.7.1 | Command Lines (MRDC/, MWTC/, IOWC/, And IORC/) 2-8 |

| 2.4.7.2 | Transfer Acknowledge Line (XACK/) 2-9              |

| 2.4.8   | System Control                                     |

| 2.5     | ON-BOARD FUNCTIONS                                 |

| 2.5.1   | Memory Mapping Registers                           |

| 2.5.2   | Memory Mapping                                     |

| 2.5.3   | Error Control                                      |

| 2.5.4 | Address Errors                               | 2-11 |

|-------|----------------------------------------------|------|

| 2.5.5 | Memory Mapping Flag And Bus Arbitration Lock |      |

|       | Flag                                         | 2-12 |

| 2.5.6 | On Board Memory                              | 2-12 |

| 2.6   | APPENDIX A                                   | 2-13 |

| 2.7   | APPENDIX B                                   | 2-14 |

| 2.8   | APPENDIX C                                   | 2-16 |

# CHAPTER 3 INPUT/OUTPUT (I/O) BOARD

| 3.1   | INTRODUCTION                                 |

|-------|----------------------------------------------|

| 3.2   | INSTALLATION AND OPERATION                   |

| 3.3   | I/O BOARD CONFIGURATION                      |

| 3.3.1 | The Board Address Select Jumpers             |

| 3.3.2 | The Serial Interface - Signetics 2661 3-2    |

| 3.3.3 | The Real-Time Calendar ClockNational         |

|       | Semiconductor 58174                          |

| 3.3.4 | The Interval Timers - Synertek 6522A 3-4     |

| 3.3.5 | The Parallel Port - Synertek 6522 3-4        |

| 3.3.6 | The Parallel Port Direction And LED Register |

|       | -74LS259                                     |

| 3.3.7 | The Select/Configuration Switches            |

## CHAPTER 4 MEMORY BOARD

| 4.1     | INTRODUCTION                              |

|---------|-------------------------------------------|

| 4.2     | DEFINITION AND FEATURES                   |

| 4.3     | MEMORY MODULE SIGNALS                     |

| 4.4     | ELECTRICAL CHARACTERISTICS                |

| 4.4.1   | Error Detection And Correction (EDAC) 4-2 |

| 4.4.2   | Status Registers (CSR And ESR) 4-2        |

| 4.4.2.1 | Error Status Register (ESR) 4-5           |

| 4.4.2.2 | ESR Signal Definitions 4-6                |

| 4.4.2.3 | Error Status LEDs 4-7                     |

| 4.4.2.4 | Error Detection And Correction (EDAC) 4-8 |

| 4.4.2.5 | Interrupt Options 4-8                     |

| 4.5     | CONFIGURING THE MEMORY BOARD              |

| 4.5.1   | Starting Address                          |

| 4.5.2   | Ending Address                            |

| 4.5.3   | Enabling Extended Address Lines 4-10      |

| 4.5.4   | Setting Address For Extended Lines 4-11   |

| 4.5.5   | I/O Port Address                          |

| 4.5.6   | Switch Settings 4-12                      |

|         |                                           |

# CHAPTER 5 THE WINCHESTER FLOPPY CONTROLLER BOARD (WFC)

| 5.1 | INTRODUCTION        | • | ٠ | • | • | • | • | • | • | • | • | • | • | • | • | 5-1 |

|-----|---------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| 5.2 | GENERAL DESCRIPTION | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 5-1 |

| 5.3 | FEATURES            | ٠ | • | • | ٠ | ٠ | • | • | ٠ | • | • | • | • | • | • | 5-1 |

| 5.4      | SPECIFICATIONS                                | . 5-2 |

|----------|-----------------------------------------------|-------|

| 5.5      | THEORY OF OPERATION                           | . 5-4 |

| 5.5.1    | Host Interface                                | . 5-4 |

| 5.5.2    | Task Files                                    | • 5-4 |

| 5.5.3    | Command Register (Write Only)                 | . 5-5 |

| 5.5.4    | Size/Drive/Head Register                      |       |

| 5.5.5    | Cylinder Number                               | . 5-7 |

| 5.5.6    | Sector Number                                 | . 5-7 |

| 5.5.7    | Sector Count                                  | . 5-7 |

| 5.5.8    | Write Precompensation Register                | . 5-7 |

| 5.5.9    | Switches Register                             | . 5-8 |

| 5.5.10   | Status And Error Registers                    | . 5-8 |

| 5.5.11   | Macro Commands                                | 5-11  |

| 5.5.11.1 | Floppy Winchester                             | 5-12  |

| 5.5.11.2 | Type I Commands                               | 5-13  |

| 5.5.11.3 | Type II Command                               | 5-16  |

| 5.5.11.4 | Type III Commands                             | 5-18  |

| 5.6      | PROGRAMMING THE WFC BOARD                     | 5-22  |

| 5.6.1    | Setting Up Task Files                         | 5-22  |

| 5.6.2    | Type I Command Programming (Restore And Seek) | 5-23  |

| 5.6.3    | Type II Command Programming (Read Sector)     | 5-24  |

| 5.6.4    | Type III Command Programming (Write Sector) . | 5-25  |

| 5.6.5    | Mapping Bad Blocks                            | 5-27  |

| 5.7      | SOFTWARE INTERFACE DATA                       | 5-29  |

| 5.7.1    | 34-Pin Winchester Drive Control Connector     | 5-30  |

| 5.7.2    | Winchester Drive Data Connector               | 5-31  |

| 5.7.3    | Drive Control Timing                          | 5-32  |

| 5.7.4    | Drive Data Timing                             | 5-33  |

| 5.7.5    | Adjustment Procedures                         | 5-33  |

# CHAPTER 6 DEI CARTRIDGE TAPE CONTROL BOARD

| 6.1    | INTRODUCTION                          |

|--------|---------------------------------------|

| 6.2    | DRIVE INTERFACE REQUIREMENTS 6-2      |

| 6.3    | PERFORMANCE SPECIFICATIONS            |

| 6.3.1  | Tape Motion - Steady State 6-2        |

| 6.3.2  | Reliability And Failures 6-4          |

| 6.4    | DATA INPUT FORMAT                     |

| 6.5    | THEORY OF OPERATION                   |

| 6.5.1  | DEI Processor 6-6                     |

| 6.5.2  | DEI Buffer RAM 6-6                    |

| 6.5.3  | DEI Bus Interface 6-7                 |

| 6.5.4  | DEI Tape Interface 6-8                |

| 6.6    | OPERATIONAL FUNDAMENTALS              |

| 6.7    | STORAGE DETAILS                       |

| 6.8    | I/O CODES                             |

| 6.9    | HOST-TO-INTERFACE TRANSFER WORDS 6-13 |

| 6.10   | INTERFACE-TO-HOST TRANSFER WORDS 6-16 |

| 6.11   | COMMAND EXPLANATIONS                  |

| 6.12   | I/O SIGNALS                           |

| 6.12.1 | Input Data Signals                    |

| 6.12.2 | Output Signals                   | 6-27 |

|--------|----------------------------------|------|

| 6.13   | POWER AND SIGNAL PIN ASSIGNMENTS | 6-29 |

| 6.13.1 | Power Connections                | 6-29 |

| 6.13.2 | Signal Pin Assignments           | 6-32 |

CHAPTER 7 IEEE 488 - 1975/78 INTERFACE BUS

| 7 1    |                                      |

|--------|--------------------------------------|

| 7.1    |                                      |

| 7.2    | IEEE-488 STANDARDS                   |

| 7.3    | IEEE 488 BUS CONFIGURATION           |

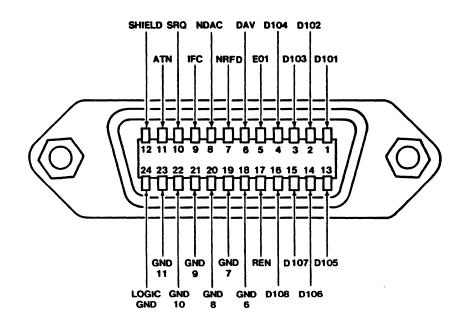

| 7.4    | GPIB CONNECTOR                       |

| 7.5    | THEORY OF OPERATION                  |

| 7.5.1  | Peripherals (Device Application) 7-2 |

| 7.5.2  | Data Flow                            |

| 7.5.3  | I/O Mapped Registers                 |

| 7.5.4  | Addresses                            |

| 7.5.5  | Asynchronous Communication           |

| 7.6    | TMS 9914 ARCHITECTURE                |

| 7.7    | REGISTERS                            |

| 7.8    | TERMINAL ASSIGNMENTS AND FUNCTIONS   |

| 7.9    | HARDWARE RESET                       |

| 7.10   | CONTROLLER FUNCTION                  |

| 7.11   | TALKER FUNCTION                      |

| 7.12   | LISTENER FUNCTION                    |

| 7.13   | ADDRESSING                           |

| 7.14   | HANDLING INTERRUPTS                  |

| 7.15   | SERVICE REQUESTS                     |

| 7.16   | GPIB SIGNAL DEFINITIONS              |

| 7.17   | MEMORY MAP                           |

| 7.18   | DIRECT MEMORY ACCESS (DMA)           |

| 7.18.1 | DMA Limitations                      |

| 7.18.2 | DMA Enhancements                     |

| 7.18.3 | DMA Operation                        |

|        | •                                    |

| 7.18.4 | DMA Idle Cycle                       |

| 7.18.5 | DMA Active Cycle                     |

| 7.18.6 | DMA Transfer Types                   |

| 7.18.7 | DMA Register Description             |

| 7.19   | APPENDIX A                           |

| 7.20   | APPENDIX B                           |

|        |                                      |

.

## CHAPTER 1

## SYSTEM OVERVIEW

#### 1.1 INTRODUCTION

This manual is organized into chapters or self-contained modules, one for each printed circuit board that can possibly constitute a System 150. Each module or chapter covers the operation of a specific PC board. You need read only those modules that pertain to the boards found with your particular system configuration. If, for example, your system has no cartridge tape subsystems, you need not read chapter six.

The system overview (this chapter) is common to all System 150 configurations.

## 1.2 FEATURES OF THE SYSTEM 150

The WICAT System 150 is a 68000-based microcomputer system with mainframe capabilities.

- o Central Processing Unit (CPU) (1.4.1)

- o Memory (1.4.2)

- o Storage and storage backup (1.4.3)

- o Several standard and optional peripherals (1.4.4)

## 1.3 SYSTEM CONFIGURATION

The System 150 is self-contained in a video terminal and has a detachable keyboard as shown in figure 1.1. The left front of the unit contains a 5-1/4 inch Winchester disk drive as the primary boot and storage device, and either a 5-1/4 inch floppy

,

## SYSTEM CONFIGURATION

disk drive as a secondary boot and memory device. The cabinet contains a card cage with six slots for printed circuit boards. Those boards are the subject of this manual. Additional Winchester disk drives and/or a DEI cartridge tape drive may be housed in an accompanying Disk Expansion Unit (DEU).

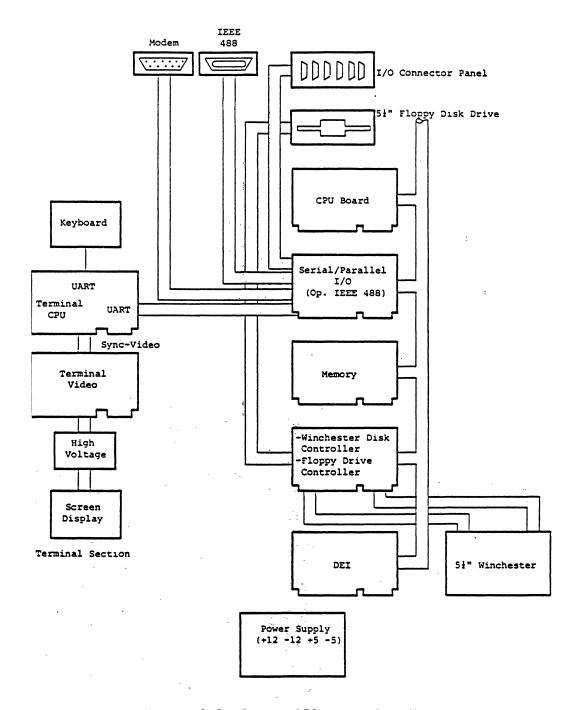

Figure 1.1 System 150 (common configuration)

#### 1.4 SYSTEM COMPONENTS

1.4.1 Central Processing Unit (CPU)

The processor for the System 150 is the Motorola 68000 microprocessor, which runs at 8 MHz and executes up to one million instructions per second. Thirty-two bit internal registers support 32-bit data operations.

See Chapter 2 for more information on the CPU.

1.4.2 Memory

The System 150 is equipped with a single memory board containing 256 Kbytes of Dynamic Random Access Memory (DRAM) that is expandable to 512 Kbytes by fully populating the board. Additional memory boards may be added to increase the available memory space to 1.5 Mbytes dynamic ECC RAM.

See Chapter 4 for more information.

## 1.4.3 Storage

Mass storage, with the optional DEU, can include up to three 5-1/4 inch Winchester disk drives, a DEI cartridge tape drive, and/or one or more 5-1/4 inch floppy disk drive(s) for backing up and porting files.

See Chapters 5 and 6 for more information.

1.4.4 Other Elements

Other components of the System 150 are:

- o 5 RS-232 C serial interfaces (1.8.2)

- o 16-bit parallel interface (1.8.2)

- o Battery-backed calendar clock (1.4.41)

- o Intelligent disk controller (1.4.4.2)

- o IEEE 488 general purpose interface bus (GPIB) (optional) (1.8.3 and Chapter 7)

- 1.4.4.1 Battery-backed Calendar Clock -

This clock, located on the I/O board, is a real time calendar clock for the system. An on-board battery powers this clock in the event of a system failure or unexpected loss of power.

1.4.4.2 Intelligent Disk Controller -

The Winchester controller board controls the Winchester disk and performs local interpreting functions such as editing, checking input validity and decoding complex commands.

1.5 PLACEMENT OF BOARDS

The motherboard in the standard CPU chassis contains the PC boards shown on table 1-A. (See the appropriate module for a detailed explanation.)

- o CPU board

- o I/O board

- o Memory board

- o Controller boards (only WFC is standard)

- 1. Winchester and Floppy Disk (WFC)

- 2. DEI cartridge magnetic tape drive

Placement is significant for designating or assigning bus priority, as noted in 1.6.2.

|          |   | وي المحمد الله الله عن الله الله الله الله الله الله الله الل                                                        |

|----------|---|----------------------------------------------------------------------------------------------------------------------|

| Slot No. | 1 | PC Board Identity                                                                                                    |

| 6        | 1 | Primary disk (SMD or WFC)                                                                                            |

| 5        | 1 | WFC or I/O (1st)                                                                                                     |

| 4        |   | 2nd I/O or memory (optional)                                                                                         |

| 3        | 1 | memory (optional)*                                                                                                   |

| 2        | 1 | memory                                                                                                               |

| 1        | 1 | CPU I                                                                                                                |

|          |   | هده باید هاه چین انتاز این ۱۸۸۰ برید که جرد شد این انت باید که انترا بری ۲۸۰ میک باید ها این این اندا این ها ای<br>ا |

Table 1-A S150 Placement of Boards

\*Memory options: 256 or 512 Kbytes

If you must replace a board, observe the stuffing order noted in table 1-A.

## 1.6 PC BOARD INTERACTION

The **bus structure** is a common group of circuit paths over which input and output signals are routed. This structure enables communication between the CPU board and the other PC boards.

1.6.1 Explanation Of Bus Structure

The PC boards and the CPU board are interconnected via the motherboard, located in the base of the chassis. The CPU board controls the bus.

There are three kinds of buses:

- The address bus carries the signals needed to define any of the possible memory or I/O locations in the system.

- 2. The data bus carries all instructions and data.

3. The control bus carries signals generated by the CPU used to direct the action of the other elements in the system.

## 1.6.2 Bus Control

The MC68000 microprocessor allocates CPU time for requesting processes and devices. The basic theory of allocation is as follows: First, the CPU receives a request signal for bus use. Second, based on internally defined priorities, the request is either granted immediately or delayed until previous or higher priority requests are processed. Finally, when the request is granted, the requesting device acknowledges to the CPU that it is using the bus, and the cycle continues.

The device or process using the bus is called the bus master. (WICAT computers allow only one bus master at a time.) A device called the slave then receives data from or transmits data to the bus master.

### 1.6.3 Serial Priority Bus Control

Priority functions allow bus masters to break deadlocks that occur when more than one master concurrently requests the bus. The System 150 supports bus mastery for the CPU board, the I/O board, and the various controller boards. The CPU board (slot 1) is the default master and is on the lowest priority end of the motherboard. The SMD board (slot 12) is the highest priority.

BPRN is the signal for bus priority in; BPRO is the signal for bus priority out. BPRN indicates to a particular master that no higher priority master is requesting the use of the bus.

The motherboard contains slots for twelve PC boards (table 1-A). Pin 15 on each slot is BPRN; pin 16 is BPRO. In front of each slot on the motherboard is an extractable multibus jumper pin. If left in place, the jumper pin completes the circuit for the daisy-chain relay of the bus priority signal. A PC board with the jumper pin left in place cannot drive BPRO high and therefore cannot be bus master.

For example, to qualify the primary disk PC board as a

possible bus master, extract JP12. Do the same thing with JP11, JP10, and JP1 to qualify the other bus masters. The relay of the bus priority signal for these boards thereafter takes place on the circuitry of the respective board.

#### 1.7 SYSTEM DATA FLOW

Primary data communication to the System 150 is via an external terminal connected to port zero of the connector port panel (CPP) (see figure 1.2).

FLOW

Figure 1.2 System 150 Data Flow Chart

## **1.8 CONTROLLER INTERFACE**

#### 1.8.1 Serial Interfaces

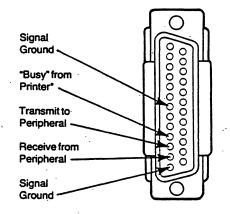

Serial interfaces are used as input/output ports for various peripheral devices such as printers, terminals, etc. The interfaces are located on the I/O board (see module 3) and conform to the standard RS-232 C to ensure asynchronous data transfers. Figure 1.3 is a diagram of the RS-232 C port.

Figure 1.3 The RS-232 C Port

#### NOTE

Pins 1 and 7 are signal grounds. Do not connect them as a chassis ground for peripherals and terminals.

The System 150 receives on pin 2 and transmits on pin 3.

The TTY device driver automatically handles XONXOFF data handshaking, i.e., control of data flow. Use pins 2, 3, and 7 in this configuration. Pin 4 is used for "busy" handshaking. It may be necessary to remove a jumper on the I/O board to use hardware handshaking on each serial port. Use pins 3, 4, and 7 in this configuration.

## 1.8.2 Parallel Interface

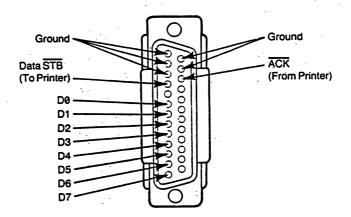

The parallel interface is a 16-bit parallel port organized as two 8-bit bidirectional ports and set up to act as a standard Centronics interface. The port is used as shown in figure 1.4.

Figure 1.4 The Parallel Port

#### NOTE

WICAT does not use a busy line in the parallel interface. Each time ACK is received, the next character in the buffer is strobed on the data bits.

## 1.8.3 IEEE 488 Interface (Optional)

Additional ICs to make up this option can be inserted on the I/O board (see chapter 3). The IEEE 488 interface is a standard General Purpose Interface Bus (GPIB), allowing the use of other external peripherals. The IEEE 488 interface connector and the WICAT memory map using this option are covered in chapter 7.

#### CHAPTER 2

## CPU BOARD

## 2.1 INTRODUCTION

This module explains the functions of the CPU board (part number 810-077-001).

## 2.2 CPU BOARD CONFIGURATION

The CPU board comprises four main areas of circuitry.

- o CPU chip and supporting circuits

- o Memory mapping registers

- o On board ROM

- o Multibus interface

#### 2.3 MICROPROCESSOR CIRCUITRY

The circuitry of the CPU board is divided according to two principal functions: the board fetches and sends data (bus-related functions), and the board decodes signals and executes commands (on-board functions).

The CPU board contains the Motorola MC68000 Microprocessor, which directs control, logic, and arithmetic operations. The processor circuitry comprises the microprocessor and its associated buffers; system clocks; and bus error, interrupt, and arbitration logic.

For additional information, refer to Motorola's publication entitled: MC68000 16-bit Microprocessor User's Manual.

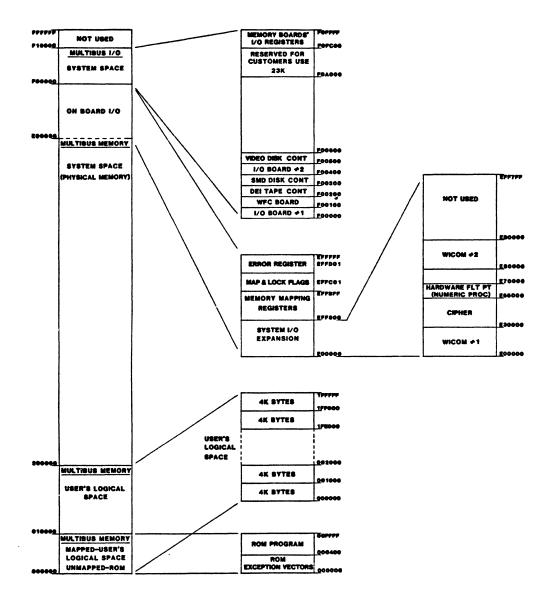

## 2.3.1 System Memory Map

Table 2-A Memory Address Map

2.3.2 MC68000 Peripheral Control

The I/O board contains the only 6800-family device used on the System 150. The MC68000 provides three lines for interfacing 6800-family synchronous bus peripheral devices:

- Enable (E) is a clock signal that synchronizes transactions between the processor and MC6800 peripherals. The clock period is ten times the system clock (10 x 125nS = 1.25uS) and has a 60/40 duty cycle (6 clocks low, 4 clocks high).

- 2. Valid Peripheral Address (VPA) is asserted by the peripheral device when it recognizes its address on the address bus. VPA L, used to distinguish between auto and nonautovectored interrupts, is unavailable on the Multibus.

- 3. Valid Memory Address (VMA) is asserted by the processor in response to the assertion of VPA during an MC6800 peripheral data transfer.

E, VMA, and VPA are normally on an undefined pin of the Multibus (P2 connector).

#### 2.4 THE MULTIBUS INTERFACE

#### 2.4.1 Bus Arbitration Circuitry

The CPU bus arbitration scheme conforms to the Multibus specification for serial priority. Serial priority involves the CPU as the default bus master. The I/O board and the various controller boards can gain control of the bus according to bus priority signals governed by the software. Priority functions allow bus masters to break deadlocks that occur when more than one master concurrently requests the bus. The CPU board (slot 1) is on the lowest priority end of the motherboard. The SMD board (slot 12) is the highest priority.

BPRN is the signal for bus priority in; BPRO is the signal for bus priority out. The BPRO of each master is daisy chained to the BPRN signal of the next lower priority master. The BPRN signal tells a particular master that no higher priority master is requesting the use of the bus.

Below is the scheme used in the System 150 for resolving

serial priority.

SERIAL PRIORITY BUS CONTROL

- 1. A master requests the bus by driving BPRO high

- This request disables the BPRN of all lower priority masters.

- 3. The CPU reads this BPRO high signal and drives its BPRN high

- 4. The CPU releases the busy line by driving the busy line high.

- 5. The requesting master sees the CPU busy line go high and asserts busy by qualifying BPRN.

- 6. When finished with the bus, the master drives BPRO low and gives up the bus.

The motherboard contains slots for six PC boards (see table 1-A). Pin 15 on each slot is BPRN; pin 16 is BPRO. In front of each slot on the motherboard is an extractable multibus jumper pin. If left in place, the jumper pin completes the circuit for the daisy-chain relay of the bus priority signals. A PC board with the jumper pin left in place cannot assert BPRN as high and therefore cannot be bus master.

With the appropriate jumper pin extracted, the software needed to designate bus master priority can be effective in designating priorities for bus masters. For example, to enable the primary disk PC board as a master, extract JP6. Do the same thing with JP5, JP4, and JP1. The relay of the bus priority signal for bus master PC boards thereafter takes place on the circuitry of the pertinent board.

## 2.4.2 Interrupt Circuitry

The CPU board supports seven levels of interrupts, INTO/ through INT6/. INTO/ has the highest priority and is the only nonmaskable interrupt. Multibus INTO/ corresponds to 68000 interrupt level 7. Multibus INT6/ corresponds to 68000 level 1. Multibus INT7/ has no correspondence to a 68000 interrupt. All interrupts are autovectored to addresses designated by the MC68000. (For additional information see section 2.4.5 and the appropriate section of Motorola's MC68000 16-Bit Microprocessor User's Manual.)

## 2.4.3 Interrupt Control

Interrupts are a subset of a more general class of operations called exceptions. Interrupts are always autovectored, meaning the processor generates the interrupt vector number internally, as a function of the interrupt level.

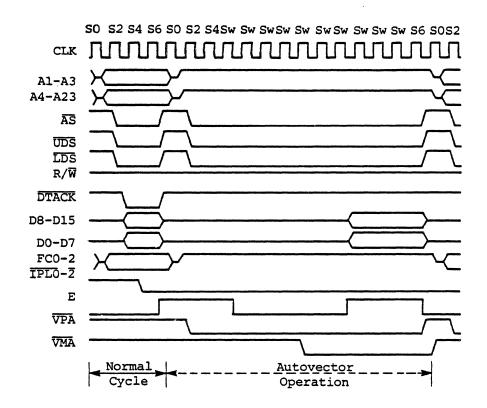

## Figure 2.1 Signal Activity During an Autovectored Interrupt Sequence

After the interrupt vector number is obtained, the processor saves the status and return address on the system stack and then uses the vector number to access the interrupt vector (interrupt handler routine address) from memory. The processor then continues execution of the interrupt handler routine.

VPA will always be asserted automatically during an interrupt acknowledge bus cycle.

CPU BOARD THE MULTIBUS INTERFACE

## 2.4.4 The Multibus Interface

The CPU conforms to the IEEE 796 proposed Multibus standard, with some minor differences. Data bit 0 of the Multibus is data bit 0 of the 68000, but the 68000 defines the lower byte of the data bus as odd and the upper byte of the data bus as even. The Multibus reverses this organization. A byte swap buffer is implemented between the microprocessor and the Multibus. The byte swap buffer interface ensures that odd and even single-byte transfers take place on the low order data lines. Word transfers use the full set of sixteen data lines, under the control of the BHEN signal, i.e., A0.

#### NOTE

When writing a byte to a peripheral device, the least significant address bit must be complemented or inverted by the software because of the MC68000 to Multibus incompatibility.

#### 2.4.5 Address Bus

The microprocessor uses a 24-bit address bus to provide 16 megabytes of addressing. Address bit zero (0) is required on the Multibus and is generated by the CPU board as a function of the upper and lower data strobes of the Motorola 68000 (see 68000 manual for additional information). The lower 11 address lines are directly buffered onto the bus connector. Normally, the upper 12 lines are routed directly from the 68000 to the bus The upper 12 lines may also be connector. translated by memory mapping registers into a physical location when the 68000 is in user state or when the the processor is in the supervisory state with the memory mapping flag set and the address less than \$200000 (HEX address).

The address bus is asserted LOW at the bus connector and is the logical inversion of the address bus at the microprocessor. The address lines from the CPU board are put into a high impedance state when another master controls the bus.

## 2.4.6 Data Bus

The MC68000 uses a 16-bit data bus to transfer processor instructions and data. The data bus is buffered at the bus connector. Both byte and word transfer operations are supported.

The data lines are active low on the Multibus. When another master has control of the bus, the CPU board bus buffers are placed in a high impedance state.

## 2.4.7 Asynchronous Bus Control

The control signals comprise four command lines and one response line.

- 1. Memory Read Control (MRDC/)

- 2. Memory Write Control (MWTC/)

- 3. I/O Read Control (IORC/)

- 4. I/O Write Control (IOWC/)

- 5. Transfer Acknowledge (XACK/)

Together, these lines coordinate data transfer on an asynchronous bus.

2.4.7.1 Command Lines (MRDC/, MWTC/, IOWC/, And IORC/) -

The four command lines are communication links between the bus masters and bus slaves. An active command line tells the slave that the address lines are carrying a valid address, and that the slave should perform the specified operation.

The CPU board defines a portion of the 68000's address space as I/O space. When accesses are made in the address range

F00000 to F0FFFF, the CPU board generates an I/O read or write command on the bus (depending on the state of the R/W line from the 68000) to initiate a data transfer. During an I/O transfer, only the lower 16 address bits are defined for a total of 64 K bytes of I/O space.

2.4.7.2 Transfer Acknowledge Line (XACK/) -

This line is the slave's acknowledgement of the master's command. XACK/ tells the master that the slave has placed data on or accepted data from the data bus.

2.4.8 System Control

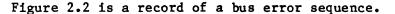

A timeout of the bus error clock tells the processor that a specified time has elapsed without a slave process responding to the assertion of a data transfer command. The clock provides a nonadjustable bus error timeout value of 20.0 uS.

Figure 2.2 Bus Error Sequence

### 2.5 ON-BOARD FUNCTIONS

### 2.5.1 Memory Mapping Registers

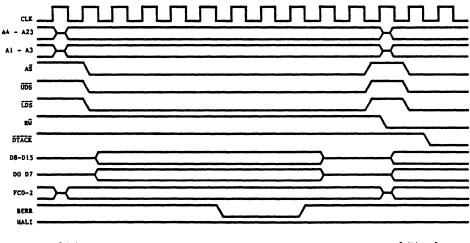

The memory mapping registers use 1,024 bytes of high speed static RAM. When mapping is enabled, address lines Al2-A20 are the register select inputs to the mapping register RAM, and the data lines out of the RAM become the new address lines Al2-A23. Mapping is automatically enabled when the processor is in the user mode and the processor address is below 200000, or in supervisor mode and the map flag register is set (shown in figure 2.2).

#### 2.5.2 Memory Mapping

If mapping is enabled, the original upper three address bits from the processor (A21-23) must be zeroes. (Users are confined to the lowest two megabytes of address space.) The next nine address bits (A12-20) are used to access one of 512 locations of the memory mapping registers. These registers are 16 bits wide, containing 12 bits of new address and three bits of access control information. One bit is not used. Each register location within the memory map represents a four-Kbyte segment of logical space, for a total of two megabytes of user logical memory space.

When a memory mapping register is accessed, the 12 bits of new address information replace the original upper 12 address bits from the processor. This scheme allows the system to map any of the user's 512 four-Kbyte segments into any of the system's physical address spaces, including I/O space.

The three bits of access control information interact with the function codes (representing the state of the processor) and the memory mapping flag to check for access errors described in 2.5.4. Figure 2.3 shows the memory mapping register format.

Figure 2.3 Memory Mapping Register Format

The memory mapping registers are accessible as read/write memory, beginning at location \$EFF800.

## 2.5.3 Error Control

The CPU board error control circuitry monitors the operation of the board. When an error occurs, the error type is latched, and a level seven interrupt is generated that allows a routine to handle the error.

## 2.5.4 Address Errors

An illegal condition on the address bus causes an address error. All addresses are inherently legal to the 68000 (except for a word access on a byte boundary). Therefore, an access error can occur only when mapping is active. Four address errors are associated with use of the memory mapping:

access violation occurs when accessing outside of user logical space, defined as 000000 - 1FFFFF (2 megabytes).

- 2. write violation occurs when writing to a logical segment that is write protected.

- 3. invalid segment occurs when accessing a nonallocated logical segment.

- 4. nonresident segment occurs when accessing a nonresident segment.

Conditions 2, 3, and 4 result directly from the access control information stored in the upper bits in each location of the memory mapping register.

## 2.5.5 Memory Mapping Flag And Bus Arbitration Lock Flag

If the processor is in supervisor state and the processor address bus is carrying an address below 2 megabytes, the value of the memory y mapping flag determines whether the address is mapped. (The address is mapped if the value of the flag is a one.) To set the memory mapping flag write 80 to location \$EFFCO1, which is an even byte address. Reset the flag by writing 00 to the same location. The value of the flag may not be read and is automatically reset to zero when the system is reset.

Also at address EFFCO1 is the flag to lock bus arbitration. By writing a \$81 to EFFCO1, all external bus requests are masked. The flag is cleared by writing a \$01 to \$EFFCO1.

#### 2.5.6 On Board Memory

Sockets for 8 UV-EPROMs (2K x 8) allow for 16 Kbytes of ROM. The CPU board supports the 2716. The select jumpers are located between C7 and C8 on the CPU board. The jumper area consists of six pads arranged in three rows of two columns. See appendix A for the various jumper configurations.

.

## 2.6 APPENDIX A

.

## JUMPER CONFIGURATION

## JP1 JP2

For

|        |      | o | ο |   | То | Bus Conn | ectors |

|--------|------|---|---|---|----|----------|--------|

| or TMS | 2716 | 1 | Ι | Α |    | 1        |        |

|        |      | 0 | ο |   |    | 1        |        |

|        |      |   |   | В |    | 1        |        |

|        |      | 0 | 0 |   |    | V        |        |

.

CPU BOARD APPENDIX B

2.7 APPENDIX B

## PAL EQUATIONS

Uncommitted logic space in the chips is configured as per the following equations:

PAL10L8 PAL DESIGN SPECIFICATION P/N 318-021-001 CONTROL SIGNAL GENERATOR - POSTITON G2, S150 MMU CPU BOARD

SYSIO PA8 PA9 PA10 /PA0 /MWTC /MRDC /BHEN /CBUSY GND SEL UHALF ERRSEL FLGSEL IOXACK LBYTE SWBYTE HBYTE LHALF VCC

- LHALF = /PAO +BHEN

- UHALF = PAO +BHEN

- IOXACK = SYSIO\*MRDC\*CBUSY +SYSIO\*MWTC\*CBUSY

- ERRSEL = SYSIO\*MRDC\*PA10\*/PA9\*PA8\*/PA0

FLGSEL = SYSIO\*MWTC\*CBUSY\*PA10\*/PA9\*/PA8\*/PA0

#### DESCRIPTION:

This chip generates the byte control lines for the on-board I/0, which includes the ROM, the flag register, the error register, and the map registers.

PAL12H6 PAL DESIGN SPECIFICATION P/N 318-022-001 ERROR AND VAS GENERATOR - POSITION B4, S150 MMU CPU BOARD

NRS NVS SWP /AS RW FC2 /MAPPED MAPFLG PIN9 GND PIN11 PIN12 PIN13 AV WV SNV SNR VADD USP VCC

- VADD = MAPPED\*/NRS\*/NVS\*RW\*AS +MAPPED\*/NRS\*/NVS\*/SWP\*AS +FC2\*/MAPFLG\*AS +FC2\*AS\*/USP

- AV = /FC2\*/USP

- SNV = NVS\*MAPPED

- WV = SWP\*/RW\*MAPPED

- SNR = NRS\*MAPPED

### DESCRIPTION:

This PAL generates the valid address strobe and the error flags.

CPU BOARD APPENDIX C

2.8 APPENDIX C

## EPROM CONFIGURATION FIRMWARE

A 32 x 8 PROM on the CPU board is used for ROM address decoding. Its contents depend on the size of ROM for which the CPU has been configured. The following tables show the contents of the PROM for three typical EPROM configurations.

|    |   |   | Table  | 2-в        |

|----|---|---|--------|------------|

| 2K | X | 8 | EPROMS | (standard) |

| Address | Data    | 1 | Address | Data    |

|---------|---------|---|---------|---------|

| 0       | •••• OE | 1 | 10      | •••• OF |

| 1       | •••• OD | 1 | 11      | •••• OF |

| 2       | •••• OB | 1 | 12      | OF      |

| 3       | •••• 07 | 1 | 13      | OF      |

| 4       | •••• OF | 1 | 14      | •••• OF |

| 5       | •••• OF | 1 | 15      | •••• OF |

| 6       | •••• OF | i | 16      | OF      |

| 7       | •••• OF | i | 17      | OF      |

| 8       | OF      | i | 18      | OF      |

| 9       | •••• OF | i | 19      | OF      |

| Α       | OF      | 1 | 1A      | OF      |

| в       | •••• OF | 1 | 1B      | •••• OF |

| С       | •••• OF | İ | 1C      | OF      |

| D       | •••• OF | i | 1D      | •••• OF |

| Ε       | OF      | í | 1E      | OF      |

| F       | •••• OF | i | 1F      | OF      |

|         |         | i |         |         |

## CHAPTER 3

## INPUT/OUTPUT (1/0) BOARD

## 3.1 INTRODUCTION

The System 150 I/O board, part number 810-104-001, handles all system input and output, and fully supports the IEEE-488 data bus option.

This module deals with the physical and logical aspects of the I/O board and discusses in particular the I/O board configuration, the serial interface, the interval timer, and the parallel port.

## 3.2 INSTALLATION AND OPERATION

The I/O board malfunctions if used with the incorrect connector panel module. The correct correspondence is shown here by part numbers:

| I/O Board                                                        | Connector Panel Module                                                                                 |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| الله منه الله جب الله جاه منه باله منه باله المه منه عليه الله ج | وي خد من الله عن الله عن الله عن الله عن إلا الله عن علام عن عن عن عن الله عن خد عن الله عن عن عن عن ا |

| 810-104-00X                                                      | 810-086-001                                                                                            |

If you ever need to install the 810-104-001 board, remove the bus arbitration jumper that corresponds to the I/O board slot on the motherboard. Otherwise, the system will fail.

Configure and correctly wire your system to printers, terminals, and modems according to the I/O board in use. The 810-104 board requires the pin-out of the RS-232 port to be configured as DTE.

## 3.3 I/O BOARD CONFIGURATION

The I/O board comprises eight main areas of circuitry:

- o the board address select jumpers (3.3.1)

- o the serial interface (3.3.2)

- o the real-time calendar clock (3.3.3)

- o the interval timers (3.3.4)

- o the general purpose parallel port (3.3.5)

- o the parallel port direction and LED register (3.3.6)

- o the select/configuration switches (3.3.7)

## 3.3.1 The Board Address Select Jumpers

The I/O board registers are located in Multibus I/O space. The board compares address bits 8/ through F/ on the bus with the board select jumpers. Changing the select jumpers allows multiple boards to be placed in the same system. The addresses described in this manual are shown in the following format:

#### \$XX YY

where:

XX = base board address in the range 00 YY to FF YY,

and

#### 3.3.2 The Serial Interface - Signetics 2661

The Signetics 2661 EPCI (Enhanced Programmable Communications Interface) is used to allow seven RS-232 C serial interfaces with full handshaking to be implemented on the I/O board. The PCIs generate the baud rate, which is software selectable from 110 baud to 19.2K baud.

YY = specific device register on the board.

All seven PCIs (0-6) are selected at the even address locations (see figure 3.1, I/O Memory Map) between XX00 and XX36, with the first PCIs using the first four locations, the second using the next four, and so on.

All PCIs use INT5/ on the Multibus, which is interrupt level 2 on the 68000 chip. The PCIs are tied to the lower byte of the data bus. Select internal registers on address lines BADR1-BADR2. PCIs 1-5 communicate externally through the I/O connector panel. PCI O connects to the internal terminal.

PCI six is configured to be used with a modem and for this reason is brought off the board on its own connector, which is labelled P4 on the circuit board. All handshaking lines, including data carrier detect (DCD) input signals, are available.

A register at I/O location (XX)D4 controls the port 6 PCI transmitter interrupt to be enabled or disabled. It is enabled by writing a  $\pm$  to I/O location XXD4 and disabled by writing a  $\pm$  to I/O XXD4.

XX = base board I/0 address

| XX00-06 | Serial Port O                   |

|---------|---------------------------------|

| XX08-0E | Serial Port l                   |

| XX10-16 | Serial Port 2                   |

| XX18-1E | Serial Port 3                   |

| XX20-26 | Serial Port 4                   |

| XX28-2E | Serial Port 5                   |

| XX30-36 | Serial Port 6                   |

| XX40-5E | Parallel Port & Interval Timers |

| XX60-7E | Calendar Clock                  |

| XXD0    | LEDs/Parallel Port Direction    |

| XXD2    | Select/Configuration Switches   |

Figure 3.1 System 150 I/O Memory Map

#### NOTE

The addresses specified in this document are hexadecimal Multibus I/O addresses.

3.3.3 The Real-Time Calendar Clock--National Semiconductor 58174

The CPU can set and read the real-time clock (RTC), a calendar clock with registers all in binary coded decimal format. The RTC is equipped with an array of registers, so the CPU can increment the RTC by one interval every fixed period. Twelve fixed periods are possible:

| 1/10 of a second | 10 minutes | 10 days     |

|------------------|------------|-------------|

| seconds          | hours      | day of week |

| 10 seconds       | 10 hours   | months      |

| minutes          | days       | 10 months   |

A battery backup circuit provides power to the RTC for one to two years. Select the RTC at even byte addresses from F00060-F0007E, and select internal registers on address lines BADR1 - BADR4 (see figure 3.1, I/O Memory Map). The RTC data bus is four bits wide and is tied to the four least significant bits of the low byte of the system data bus.

### 3.3.4 The Interval Timers - Synertek 6522A

Two interval timers are included on the I/O board. The MCS uses these timers for precise timing of external events, i.e., for real-time references. Each timer is programmable to operate in several modes and can interrupt the microprocessor when software-specified conditions occur. The timers are contained in the SY6522 timer/PIA IC and are tied to the lower byte of the data bus. Select the internal register on address lines BADR1-BADR4.

The Synertek 6522A IC is selected at even byte I/O addresses XX40-XX5E and uses INT6/ on the Multibus, which is interrupt level 1 on the 68000 processor.

## 3.3.5 The Parallel Port - Synertek 6522

The I/O board has a 16-bit, general purpose, bidirectional parallel port, with four handshaking lines. The parallel port is made up of two bidirectional, eight-bit ports, port A and port B, supplied by the SY6522 Timer/PIA IC. An input and an output handshaking line are associated with each eight-bit data port. Both eight-bit ports are externally buffered with bidirectional buffers. On power up both eight-bit ports are configured as inputs. To configure the ports as either inputs or outputs, the correct data must be written to the SY6522 IC and also to a bit-addressable latch that controls the external buffers. The addressable latch is described in detail in the parallel port direction and LED register description in 3.3.6.

# 3.3.6 The Parallel Port Direction And LED Register -74LS259

The parallel port buffers and the six LEDs are controlled by an addressable latch. Select the latch at location XXDO. The function of each output is described below.

- BDIR Direction control for port B. A one at this output causes the buffer on port B to become an output, while a zero causes the buffer to become an input.

- 2. ADIR Direction control for port A. A one at this output causes the buffer on port A to become an output, while a zero causes the buffer to become an input.

- 3. LEDI-LED6 On/off control for the SIX LEDs. A low at one of these outputs causes the corresponding LED to be turned on, while a one causes the corresponding LED to be turned off.

- 4. All outputs are cleared to zeros on power up and on reset.

\*Decoded address from bit address latch

| 0 | Port A  | Buffer | Input  |

|---|---------|--------|--------|

| 1 | Port B  | Buffer | Input  |

| 2 | CR1 ON  |        | -      |

| 3 | CR2 ON  |        |        |

| 4 | CR3 ON  |        |        |

| 5 | CR4 ON  |        |        |

| 6 | CR5 ON  |        |        |

| 7 | CR6 ON  |        |        |

| 8 | Port A  | Buffer | Output |

| 9 | Port B  | Buffer | Output |

| Α | CR1 OFF |        |        |

| В | CR2 OFF |        |        |

| С | CR3 OFF |        |        |

| D | CR4 OFF |        |        |

| Ε | CR5 OFF |        |        |

| F | CR6 OFF |        |        |

# Figure 3.2 Explanation of Addressable Latch Operation

An addressable latch is a write-only latch on which one bit is written at a time. This is accomplished by using three bits of the input data as an address to select which of the latch outputs is to be written to. Another bit of the input data is used as the data to be written to the addressed output. The input data byte is organized as shown below:

|     | 6   5   4 | 4   3   2                                  | 1  |  |

|-----|-----------|--------------------------------------------|----|--|

| x ( | x   x   : | x  data  A2                                | A1 |  |

|     |           | i i i<br>i i i<br>i i <u>i</u><br>i i<br>i |    |  |

Figure 3.3 Input Data Byte Organization

3.3.7 The Select/Configuration Switches

The eight read-only DIP switches can be read by the system and are selected at address XXD2.

.

.

# CHAPTER 4

#### MEMORY BOARD

## 4.1 INTRODUCTION

.

This module describes the memory board signals, the electrical characteristics of the board, and the board configuration, including the location and the use of address switches.

# 4.2 DEFINITION AND FEATURES

The memory board is a dynamic RAM memory module organized as 256K words by 16 bits and uses the 64K DRAM chip. The board's circuitry incorporates the following:

- o ECC: Error checking and correction (ECC)

- o Status registers: A control status register to select options, and an error status register to make error conditions available to software

- o Decoding:

- 24 lines of address capability

- Four extended address lines to select any of 16 1-megabyte pages

- . Data access in either word or byte mode

MEMORY BOARD MEMORY MODULE SIGNALS

#### 4.3 MEMORY MODULE SIGNALS

Signals common to the Multibus are defined in the Intel Multibus Specification Manual 9800683 or in the system bus standard for the IEEE 796 bus.

## 4.4 ELECTRICAL CHARACTERISTICS

4.4.1 Error Detection And Correction (EDAC)

EDAC employs an additional six bits of check bit data to detect and correct single bit errors and to detect double bit/gross errors. When enabled, EDAC completes all operations having a single bit READ error by attempting to write corrected data back to memory.

#### 4.4.2 Status Registers (CSR And ESR)

The memory module has a control status register (CSR) and an error status register (ESR).

<u>Address Selection</u>: Both registers are accessed at an I/Oaddress. CSR is selected with ADRO = 1 (an electrical high); ESR is selected with ADRO = 0. The I/O port base address is designated with eleven on board switches. Eight switches are compared with ADRB/ and ADR4/, and the three start address switches are compared with ADR1/ through ADR3/. Selecting addresses this way permits the eight more significant bits of the I/O port address to be identical to other memory boards in the system and to mirror the I/O port address selection made based on the position of the memory board within the address space.

See table 4-G for the switch settings.

<u>CSR</u> <u>Operation</u>: The CSR is used on a programmable I/O chip for read and write operations. It controls operation and stores information about errors. To use this I/O chip, the microprocessor must configure the chip by executing two operations for every port:

- 1. Load the CSR

- 2. Designate lines as inputs or outputs

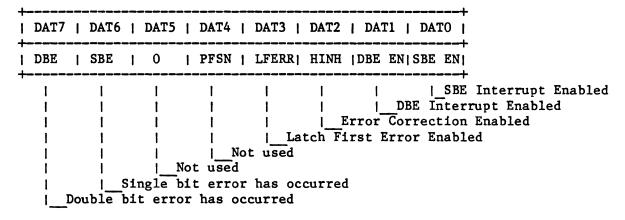

CSR Formats: Figure 4.1 shows the format for reading data from the CSR:

Figure 4.1 CSR Read Format

Figure 4.2 shows the format for writing data into the CSR:

|      |    | ، حد حد حد حد | -  | ، هه هه که می ه | -   | و حدو حدو حدو حدو |    |       | -  |        |    |      | _   | _   |     |      |                     |

|------|----|---------------|----|-----------------|-----|-------------------|----|-------|----|--------|----|------|-----|-----|-----|------|---------------------|

| DAT7 | I  | DAT6          | I  | DAT5            | I   | DAT4              | 1  | DAT3  | 1  | DAT2   | 1  | DAT  | [1  | 1   | DA' | ro I |                     |

| 0    | 1  | 0             | I  | 0               | 1   | RPFS              | 1] | LFERR | 1  | HINH   | 1  | OBE  | EN  | I S | BE  | EN   |                     |

|      |    |               |    |                 |     |                   |    | 1     |    | 1      |    |      |     |     |     |      | r<br>Enable, O=Rese |

| 1    |    | 1             |    | I               |     | I                 |    | 1     |    | I      |    | 1    |     |     |     |      | SBE Interrupt       |

| I    |    | 1             |    | 1               |     | 1                 |    | 1     |    | 1      |    | _۱_  | _1= | En  | ab: | le,  | 0=Reset             |

| 1    |    | 1             |    | 1               |     | 1                 |    | I     |    | I      |    |      |     | DB  | E   | Inte | errupt              |

| 1    |    | 1             |    | 1               |     | 1                 |    | I     |    | I      | Er | ror  | Со  | rr  | ect | tion | n Disabled          |

| 1    |    | 1             |    | 1               |     | I                 |    | 1     | La | tch Fi | Lr | st H | Err | or  | Eı  | nabl | Led                 |

| 1    |    | 1             |    | 1               |     | _1                | Ňo | effe  | ct |        |    |      |     |     |     |      |                     |

| 1    |    | 1             |    | 1_1             | Not | t used            | 1  |       |    |        |    |      |     |     |     |      |                     |

| 1    |    |               | No | t used          | 1   |                   |    |       |    |        |    |      |     |     |     |      |                     |

| اا   | No | t use         | đ  |                 |     |                   |    |       |    |        |    |      |     |     |     |      |                     |

Figure 4.2 CSR Write Format

<u>CSR Flag Control Bits</u>: The system supports six CSR Flag Control Bits, described below.

## Double Bit Error Flag (DBE)

. . . . . . . . . .

DBE indicates that two bits in the same word failed or that a gross error has been detected. DBE is set when a double bit error occurs, then reset when the DBE EN control bit is taken to zero. Setting DBE EN back to a logic one enables detection of the next double bit error.

Single Bit Error Flag (SBE)

SBE, a read only signal, indicates that a single bit error has been detected. SBE is set when the error is detected, then reset when the SBE EN control bit is taken to logic zero. Setting the SBE EN control bit back to a logic one enables the detection of the next single bit error.

## Power Fail Sense F/F Flag (PFSN L)

This function is not used on WICAT equipment.

Latch First Error (LFERR)

LFERR allows you to select whether ERR data are updated each time a SBE/DBE is detected, or only once on the first error detected. Writing a logic one to the LFERR control bit enables LFERR so that the next error can be stored. When you set LFERR to zero, the last error always updates the ESR. LFERR can be read or written.

Error Correction Disabled (HINH)

When equal to logic one, HINH disables error detection, error correction, and the write function to the checkbits. Use HINH only for testing. HINH can be read or written, and the board cannot be initialized when this bit is set.

Enable DBE Interrupt (DBE EN)

When DBE EN equals logic one, interrupts on DBEs are possible. Taking this DBE EN control bit to a zero resets any current DBE flag bit. Leaving DBE EN at a zero disables DBE interrupts. DBE EN can be read or written.

Enable SBE Interrupt (SBE EN)

When SBE EN equals logic one, interrupts on SBEs are

possible. Taking the SBE EN control bit to a zero resets any current SBE. Leaving SBE EN at zero disables SBE interrupts. SBE EN can be read or written.

4.4.2.1 Error Status Register (ESR) -

.

When a single bit error occurs and the conditions for FE/LE have been satisfied, the ESR stores the error information. The ESR is a read-only register. Clear the ESR either by writing to it or by resetting the system.

Figure 4.3 shows the format for reading data from the ESR.

| +                           | DAT6                            | DAT5                   | DAT4                     | DAT3   | DAT2   | DAT1   | DATO                     | +<br>!               |       |

|-----------------------------|---------------------------------|------------------------|--------------------------|--------|--------|--------|--------------------------|----------------------|-------|

| BANK1  ]                    | BANKO I                         | SYN5                   | SYN4 1                   | SYN3   | SYN2   | SYN1   | I SYNO                   | +<br>!               |       |

| <br> <br> <br> <br> <br> Ba | <br> <br> <br> <br> Ban<br>nk_0 | <br> <br> <br> <br> Sy | I<br>I<br>ISyn<br>ndrome | ndrome | ndrome | ndrome | _Syn<br>yndrome<br>bit 2 | +<br>ndrome<br>bit l | bit O |

Figure 4.3 ESR Read Format

.

4.4.2.2 ESR Signal Definitions -

Bank:

Bank 1 and Bank 0 define the physical row of DRAMS (BANK) in which an SBE occurs. Table 4-A shows the relationship between the bank address s and the reference designator for memory devices within that row.

Table 4-A Bank Signals Reference Table

| Bank 1 | Bank O | Memory                                    | Reference                                                | Chip Numbers |

|--------|--------|-------------------------------------------|----------------------------------------------------------|--------------|

| 0      | 0      | 0000                                      | through                                                  | u021         |

| 0      | 1      | U1 00                                     | through                                                  | ul21         |

| 1      | 0      | U200                                      | through                                                  | u221         |

| 1      | 1      | U300                                      | through                                                  | u321         |

|        |        | . حين فيه جره خرة بالله وي قيل وي الله وي | وي وي وي وي وي وي اين اين اين اين اين اين اين اين اين اي |              |

Syndrome bit 5 through bit 0 (SYN5 - SYN0)

Bits 5 through 0 define the modified Hamming code generated by the SN74LS630 EDAC device when a SBE occurs. Table 4-B shows the relationship between the syndrome code and bit location within a given bank.

# MEMORY BOARD ELECTRICAL CHARACTERISTICS

| Syndrome Code<br>(Bit 5 4 3 2 1 0) | Data<br>Bit | Check<br>Bit X  | Bit Location<br>=0,1,2,3 (Bank) |

|------------------------------------|-------------|-----------------|---------------------------------|

| 1 1 0 1 0 0                        | 0           |                 | x00                             |

| 1 1 0 0 1 0                        | 1           |                 | X01                             |

| 1 1 0 0 0 1                        | 2           |                 | X02                             |

| 101100                             | 3           |                 | X03                             |

| 101010                             | 4           |                 | X04                             |

| 101001                             | 5           |                 | X05                             |

| 100101                             | 6           |                 | X06                             |

| 100011                             | 7           |                 | X07                             |

| 0 1 1 1 0 0                        | 8           |                 | X08                             |

| 011010                             | 9           |                 | X09                             |

| 0 1 0 1 1 0                        | 10          |                 | X10                             |

| 010101                             | 11          |                 | X11                             |

| 010011                             | 12          |                 | X12                             |

| 0 0 1 1 1 0                        | 13          |                 | X13                             |

| 001101                             | 14          |                 | X14                             |

| 001011                             | 15          |                 | X15                             |

| 1 1 1 1 1 0                        |             | 0               | X16                             |

| - 111101                           |             | 1               | X17                             |

| 1 1 1 0 1 1                        |             | 2               | X18                             |

| 1 1 0 1 1 1                        |             | 3               | X19                             |

| 101111                             |             | 4               | X20                             |

| 0 1 1 1 1 1                        |             | 5               | X21                             |

| 0 0 0 0 1 1                        | Gross       | s Error Conditi | on                              |

| 1 1 1 1 0 0                        | Gross       | s Error Conditi | on                              |

# Table 4-B Syndrome Code

Note: 1 = lamp on

The syndrome codes for DBEs are mutually exclusive of any SBE codes. If you clear the ESR by writing to it, then by reading the ESR and comparing it to zero you can check (poll) the board for errors.

# 4.4.2.3 Error Status LEDs -

The ten light emitting diodes (LEDs) near the address switches display the error status: the left-most light indicates a DBE; the next light indicates a SBE. Interpretation of the next eight lights is the same as the ESR. Writing to the ESR clears the ten LEDs. An active input on the INIT/line clears the LEDs and the ESR.

### 4.4.2.4 Error Detection And Correction (EDAC) -

#### EDAC Enabled

EDAC is enabled by an active INIT/ during power up. When the CSR bit HINH is low, the EDAC device, SN74LS630, is enabled. EDAC generates checkwords, syndrome bits, and error flags (DBE and SBE), and corrects data words. Corrected data from the EDAC are stored in a data latch so that during a read operation the corrected data are available on the bus, can replace error data (write back on error), and are made available for byte write operations.

# EDAC Disabled

When the CSR bit HINH is high, the EDAC device is held in an input mode, and the error flags (DBE and SBE) are held reset. Read data are not corrected, and the write operation to the checkbits is inhibited. Thus, write data generate no checkbits, and writing a word to a location with HINH active modifies the 16 data bits but leaves the six check bits unchanged from the last write operation to where HINH was inactive.

## 4.4.2.5 Interrupt Options -

#### Hardware Programming

The interrupt request lines generate nonbus vectored interrupts to the bus master (68000 interrupt level 7).

Interrupts are always wired so that a SBE or a DBE causes INTO/ to be asserted.

# Software Programming

With SBE EN and DBE EN bits in the CSR, you can

enable or disable SBE interrupt and DBE interrupt respectively. To clear the current interrupt, disable the interrupt, then reenable so that the interrupt will operate on future errors.

## 4.5 CONFIGURING THE MEMORY BOARD

On powerup, the CSR is initialized so that error detection and correction are enabled, the ESR captures the last error, and DBE and SBE interrupts are disabled. For initial checkout, you need set only the four address switches.

Turn the board so that the switches are facing you. From left to right the switches facing you are the starting address, ending address, and I/O port base address switches. The megabyte page address switch is in the upper right-hand corner.

#### NOTE

The MSB is on the left of each switch. ON equals logical zero. OFF equals logical one.

4.5.1 Starting Address

The starting address is WX000 hexadecimal. WX represents two hex digits (eight bits) that correspond directly to the eight bits of the starting address switch, S2. Consider the example in table 4-C.

# Table 4-C Starting Address Settings

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | Desired Starting<br>Address (hex) | : | WX       | : | -1     |        |        | 1 S2<br>-4 | -      | -6     | -7     | -8               |  |

|------------------------------------------------------|-----------------------------------|---|----------|---|--------|--------|--------|------------|--------|--------|--------|------------------|--|

| C0000 : C0 : 1 1 0 0 0 0 0 0                         | 40000<br>80000                    | : | 40<br>80 | : | 0<br>1 | 1<br>0 | 0<br>0 | 0          | 0<br>0 | 0<br>0 | 1<br>0 | 0<br>0<br>0<br>0 |  |

Physical memory begins at location \$200000 in a system using the 810-077-001 CPU board (multi-user mapped) and

must be contiguous. The physical address of fully populated (512K) board 0 starts at \$200000, of board 1 at \$280000, and of board 2 at \$300000.

Starting switch settings for a fully populated board are given in table 4-G.

#### 4.5.2 Ending Address

The ending address is YZFFF hexadecimal. YZ represents two hex digits (eight bits) that correspond directly to the eight bits of the ending address switch, S3. Consider the example in table 4-D.

| Desired Ending<br>Address (hex) | : | YZ | 8 |   | Swit<br>-2 |   |   | -5 | -6 | -7 | -8 |   |

|---------------------------------|---|----|---|---|------------|---|---|----|----|----|----|---|

| 3FFFF                           | : | 3F | ; | 0 | 0          | 1 | 1 | 1  | 1  | 1  | 1  | - |

| 7ffff                           | : | 7F | : | 0 | 1          | 1 | 1 | 1  | 1  | 1  | 1  |   |

| BFFFF                           | : | BF | : | 1 | 0          | 1 | 1 | 1  | 1  | 1  | 1  |   |

| FFFFF                           | : | FF | : | 1 | 1          | 1 | 1 | 1  | 1  | 1  | 1  |   |

# Table 4-D Ending Address Settings

The physical address on fully populated 512K boards ends at 27FFFF on board 0, at 2FFFFF on board 1, and at 37FFFF on board 2.

Ending address switch settings for fully populated boards are given in table 4-G.

## 4.5.3 Enabling Extended Address Lines

To enable the four extended address lines, locate the 5 position DIP switch, S5, in the upper right-hand corner when the board is component side up and the gold fingers are away from you. The leftmost switch, S5-1, enables or disables the four additional address lines as shown here:

| Switch       | : | Position | : | Function                                                        |

|--------------|---|----------|---|-----------------------------------------------------------------|

| S5-1<br>S5-1 | • |          |   | enables ADR14/ through ADR17/<br>disables ADR14/ through ADR17/ |

When used in a mapped system (S150, S155, or S160), S5-1 is always set to logical zero.

## 4.5.4 Setting Address For Extended Lines

The board's location is one of 16 possible one-megabyte pages. From the remaining four positions of the five-position DIP switch S5, select one page as shown in table 4-E.

| One-megabyte<br>page | S5 <b>-</b> 2 | Swite<br>S5-3 |   | S5 <b>-</b> 5 |

|----------------------|---------------|---------------|---|---------------|

| 0                    | 0             | 0             | 0 | 0             |

| 1                    | 0             | 0             | 0 | 1             |

| 2                    | 0             | 0             | 1 | 0             |

| 3                    | 0             | 0             | 1 | 1             |

| 4                    | 0             | 1             | 0 | 0             |

| 5                    | 0             | 1             | 0 | 1             |

| 6                    | 0             | 1             | 1 | 0             |

| 7                    | 0             | 1             | 1 | 1             |

| 8                    | 1             | 0             | 0 | 0             |

| 9                    | 1             | 0             | 0 | 1             |

| Α                    | 1             | 0             | 1 | 0             |

| В                    | 1             | 0             | 1 | 1             |

| С                    | 1             | 1             | 0 | 0             |

| D                    | 1             | 1             | 0 | 1             |

| E                    | 1             | 1             | 1 | 0             |

| F                    | 1             | 1             | 1 | 1             |

Table 4-E Switch Setting for Each Page

# 4.5.5 I/O Port Address

The I/O port base address is OPQR hexadecimal. PQ represents two hex digits (eight bits) in direct correspondence to the eight bits of the I/O port base address switch, S4, and R is a hex digit comprising the three more significant bits of W (from the module starting address) plus the state of ADRO/ from the bus.

Table 4-F shows an example of how to set the I/O port base address.

# Table 4-F Address Settings for I/O Port

|   | :/0 | Swit<br>Por | t S | Sett             |   |   | -8 | : | _ | irt | R<br>tch S2<br>Address<br>-3   | Logical<br>ADRO                               | (PQR)<br>I/O<br>Port<br>Addr | REG |

|---|-----|-------------|-----|------------------|---|---|----|---|---|-----|--------------------------------|-----------------------------------------------|------------------------------|-----|

| 1 | 1   | 1           | 1   | 0                | 0 | 1 | 0  | : | 0 | 0   | 0                              | L                                             | 0F20                         | CSR |

| 1 | 1   | 1           | 1   | 0                | 0 | 1 | 0  | : | 0 | 0   | 0                              | н                                             | OF21                         | ESR |

| 1 | 1   | 1           | 1   | 0                | 0 | 1 | 1  | : | 0 | 0   | 0                              | L                                             | 0F30                         | CSR |

| 1 | 1   | 1           | 1   | 0                | 0 | 1 | 1  | : | 0 | 0   | 0                              | H                                             | 0F31                         | ESR |

| 1 | 1   | 1           | 1   | 1                | 1 | 1 | 1  | : | 0 | 0   | 0                              | L                                             | OFFO                         | CSR |

| 1 | 1   | 1           | 1   | 1                | 1 | 1 | 1  | : | 0 | 0   | 0                              | H                                             | OFF1                         | ESR |

|   |     |             |     | ومو وعده جلالة و |   |   | -  |   |   |     | به خله هو خله جله خل کار خله خ | 0 400 800 400 500 600 400 400 800 800 800 800 |                              |     |

4.5.6 Switch Settings

Memory board DIP switch settings for a fully populated board (512K) are shown in table 4-G.

MEMORY BOARD CONFIGURING THE MEMORY BOARD

Table 4-GMemory Board Switch Settings (512 K boards)

| Board Address |                    | Switch Settings |   |   |   |   |   |   |   |  |

|---------------|--------------------|-----------------|---|---|---|---|---|---|---|--|

|               |                    | 1               | 2 | 3 | 4 | 5 | 6 | 7 | 8 |  |

| 0             | Starting Address   | 0               | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

|               | Ending Address     |                 | 1 |   | 1 | 1 | 1 | 1 | 1 |  |

|               | I/O Port base      | 1               | 1 | 1 | 1 | 0 | 0 | 1 | 0 |  |

|               | S-5 (Page Address) | 0               | Ō | 0 | 1 | 0 |   |   |   |  |

| 1             | Starting Address   | 1               | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

|               | Ending Address     | 1               | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |

|               | I/O Port base      | 1               | 1 | 1 | 1 | 0 | 0 | 1 | 0 |  |

|               | S-5 (Page Address) | 0               | 0 | 0 | 1 | 0 |   |   |   |  |

| 2             | Starting Address   | 0               | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

|               | Ending Address     |                 | 1 |   | 1 | 1 | 1 | 1 | 1 |  |

|               | I/O Port base      | 1               | 1 | 1 | 1 | 0 | 0 | 1 | 1 |  |

|               | S-5 (Page Address) | 0               | 0 | 0 | 1 | 1 |   |   |   |  |

Table 4-HSwitch Settings for 256K boards

| Board | Address          | Switch Settings<br>1 2 3 4 |   |   |   | • |   | 1=OFF) |   |

|-------|------------------|----------------------------|---|---|---|---|---|--------|---|

|       |                  | 1                          | 2 | 3 | 4 | 5 | 6 | 7      | 8 |

|       |                  |                            |   |   |   |   |   |        |   |

| 0     | Starting Address | 0                          | 0 | 0 | 0 | 0 | 0 | 0      | 0 |

|       | End              | 0                          | 0 | 1 | 1 | 1 | 1 | 1      | 1 |

|       | I/O Port         | 1                          | 1 | 1 |   | 0 | 0 | 1      | 0 |

|       | S-5C Page        | 0                          | 0 | 0 | 1 | 0 |   |        |   |

| 1     | Starting         | 0                          | 1 | 0 | 0 | 0 | 0 | 0      | 0 |

|       | Ending           | 0                          | 1 | 1 | 1 | 1 | 1 | 1      | 1 |

|       | I/O Port         | 1                          | 1 | 1 | 1 | 0 | 0 | 1      | 0 |

|       | <b>S-</b> 5      | 0                          | 0 | 0 | 1 | 0 |   |        |   |

| 2     | Start            | 1                          | 0 | 0 | 0 | 0 | 0 | 0      | 0 |

|       | End              | 1                          | 0 | 1 | 1 | 1 | 1 | 1      | 1 |

|       | I/O Port         | 1                          | 1 | 1 | 1 | 0 | 0 | 1      | 0 |

|       | S-5              | 0                          | 0 | 0 | 1 | 0 |   |        |   |

#### CHAPTER 5

## THE WINCHESTER FLOPPY CONTROLLER BOARD (WFC)

# 5.1 INTRODUCTION

This module describes the Winchester Floppy Controller Board (WFC), including specifications, configuration, theory of operation, programming, diagnostics, and adjustments.

#### 5.2 GENERAL DESCRIPTION

The WFC can accommodate up to four 5 1/4-inch Winchester disk drives and four 5 1/4-inch floppy disk drives on the S150 host computer. The WFC board includes all necessary buffers and receivers/drivers for direct connection.

The WFC is compatible with the IEEE 796 Bus. All parameters and commands are given through the registers mapped into the I/O space of the system bus. Data transfers use direct memory access (DMA).

#### 5.3 FEATURES

The major features of the WFC board include:

- o Built-in data separator

- o Built-in write precompensation logic

- o Data rates up to 5 Mbits/sec

- o Control for up to 8 R/W heads per drive

- o 1024 cylinder addressing range

THE WINCHESTER FLOPPY CONTROLLER BOARD (WFC) FEATURES

- o 256 sector addressing range

- o CRC generation/verification

- o Automatic formatting

- o 128, 256, 512, or 1024 bytes per sector (ROM selectable)

- o Unlimited sector interleave capability

- o Implied seek on all commands

- o Automatic retries on all errors

- o Automatic restore and seek on seek errors

- o IEEE 796 bus compatible interface

## 5.4 SPECIFICATIONS

Table 5-A is an item by item display of the System 150 specifications.

| ITEM                       | SPECIFICATION                                                                    |

|----------------------------|----------------------------------------------------------------------------------|

| Winchester Interface:      | ST-506 compatible                                                                |

| Floppy Interface:          | Shugart compatible                                                               |

| Encoding Method:           | Modified Frequency Modulation (MFM)                                              |

| Cylinders (max):           |                                                                                  |

| per Winchester:            | 1024                                                                             |

| per Floppy:                | 256                                                                              |

| Sectors per Track (max):   | 256                                                                              |

| Heads per Drive (max):     | 8                                                                                |

| Winchester:                | 8                                                                                |

| Floppy:                    | 2                                                                                |

| Drive Selects:             | 8 (4 Winchester, 4 Floppy)                                                       |

| Step Rate:                 |                                                                                  |

| Winchester:                | 10 uS to 7.5 mS (0.5 mS increments)                                              |

| Floppy:                    | 6, 12, 20, or 30 mS                                                              |

| Disk Data Rate:            |                                                                                  |