# ANALOG-TO-DIGITAL CONVERTER MODULES

#### INTRODUCTION

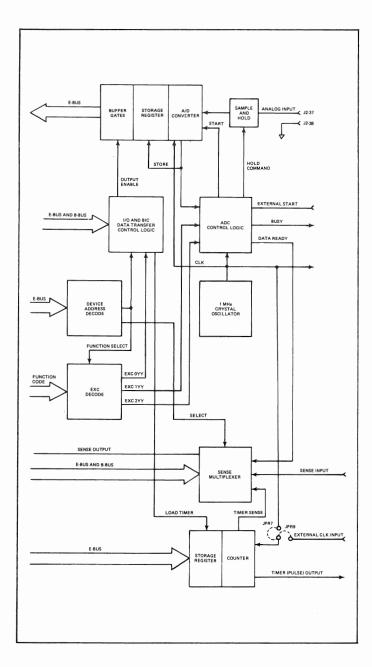

The Model 620-85A Analog-to-Digital Converter Module (ADCM) is an option for use with the Varian Data 620 series computers. The ADCM provides an analog-to-digital converter (ADC), sample and hold amplifier, and programmable timer.

The ADCM accepts a high-level analog signal which it samples and holds for conversion by the ADC. The ADC outputs a 13-bit word in binary two's complement format to a 620 computer. The timer can be used to establish time intervals for system control.

## GENERAL DESCRIPTION

The ADC employs the successive approximation technique for conversion. It's conversion rate is 13 microseconds for 13 bits, with a sample and hold amplifier settling time of 6 microseconds. The ADC can be initiated by the computer, the programmable timer, or an external pulse. The programmable timer provides an internal and external control capability. Under internal control, the timer sets a timing interval through a data word which it receives from the computer. The timer decrements the data word at 1 microsecond per count until the zero state is reached. The timer then emits a pulse, restores the original data word, and again initiates the cycle. Under external control, the timer can be inhibited at any time by an external signal which holds the timer at its load point, Timing intervals start at the instant the external signal level is removed or set to a high logic state. New timing intervals can be sent by the computer while the timer is externally inhibited.

ADCM data transfers can occur by programmed output command execution or under the optional Buffer Interlace Controller (BIC) control. When operating under program control, data transfers are initiated by the computer and are executed under input/output instruction control. The BIC permits automatic, high-speed, block data transfers between ADCM and the 620 computer memory without disturbing the sequence of the main program.

The Model 620-85A ADCM provides for a single analog input. This configuration can be readily expanded to multiple input channels by the addition of a Multiplexer Module, Model 620-860 or 861.

#### PREREQUISITES

- 620 System Computer

- 620 Expansion Chassis (requirements determined on indi-. vidual system basis)

- 620-88 Analog Power Supply (requirements determined on individual system basis)

- 620 Peripheral Backplane Wiring Panel (requirements determined on individual system basis)

| PRODUCT | Analog-to-Digital<br>Converter |  |

|---------|--------------------------------|--|

| MODEL   | 620-85A                        |  |

| DATE    | September 1, 1971              |  |

|         |                                |  |

# varian data machines

## SOFTWARE

A comprehensive software package is provided comprising a test program and an I/O Driver Program. The test program is an effective tool for determining the operational status of the ADCM.

The I/O Driver Program provides convenient access to the ADCM without detailed knowledge of the hardware. The program can be used by itself or embedded in an operating system. The I/O Driver Program consists of two routines: Programmed Data Transfers and Direct Memory Access Data Transfers. These routines permit the user to specify the following parameters:

- Destination array and quantity of incoming data.

- Time between acquisition frames (a frame is defined to be the period of time required to input data)

- An error address to which control will pass when any one of several error conditions are detected.

## SPECIFICATION

| Programmable Timer                           |  |

|----------------------------------------------|--|

| Clock frequency                              |  |

| Clock drift ±1PPM/°C                         |  |

| Clock stability                              |  |

| Resolution                                   |  |

| (Computer E-Bus $2^0 - 2^{15}$ )             |  |

| Programmed PRF 1 MHz to 15.26 Hz             |  |

| 1 microsecond to 65.535 milliseconds         |  |

| Timer Output 100 nanosecond pulse to ground. |  |

| 1K ohms to $+5$ V sinks 100 mA.              |  |

| Maximum capacity load 1000 pF.               |  |

| CLK Output 100 nanoseconds pulse from        |  |

| low to high. TTL output.                     |  |

| Available fanout: 6 logic loads.             |  |

| PRF = 1.0 MHz ±.01%.                         |  |

| Timer Clock Input                            |  |

| PRF = 10 MHz. Increments                     |  |

| counter on low to high transition.           |  |

| Sample & Hold                                |  |

| Gain and Accuracy                            |  |

| Voltage Gain +1                              |  |

| Accuracy ±.01%                               |  |

| Gain Temp Coefficient ±10 PPM/°C             |  |

| Track Mode                                   |  |

| Full Power Response 75 kHz                   |  |

| (20V peak-to-peak                            |  |

| sine wave)                                   |  |

| Slew rate                                    |  |

| Settling Time to                             |  |

| 6 microseconds                               |  |

| Input Characterisitics, Single Ended |

|--------------------------------------|

| Signal Range±10V                     |

| Maximum Rating,                      |

| without damage±15V                   |

| Input Impedance                      |

| with 5000 pF                         |

| Offset Voltage ±2 mV maximum         |

| VS Temperature                       |

| Input Characterisitics, Differential |

| Signal Range±10V                     |

| Maximum Rating,                      |

| without damage±30V                   |

|                                      |

| Input Impedance                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------|

| Signal Range                                                                                                                           |

| (Hold Mode) 1 mV peak-to-peak<br>Decay Rate in, Hold Mode ±10 mV/Second<br>Feedthrough 20V Step,                                       |

| (Hold Mode)                                                                                                                            |

| Aperture Time, Maximum 100 nanoseconds<br>Offset Pedestal, Maximum ±2 mV                                                               |

| Acquisition Time, Maximum 6 microseconds<br>Analog to Digital Converter                                                                |

| Resolution                                                                                                                             |

| Output Format                                                                                                                          |

| Conversion Accuracy±.012% of 20V Full Scale,<br>±½ LSB                                                                                 |

| Conversion Time                                                                                                                        |

| Temperature Coefficient $\pm 50 \mu\text{V/}^{\circ}\text{C}$ maximum                                                                  |

| Warm up Time Essentially Zero                                                                                                          |

| Full Scale Range±10V                                                                                                                   |

| Digital Outputs                                                                                                                        |

| BUSY High (true) during Analog-to-Digital                                                                                              |

| Conversion. Available fanout: 8 logic loads.                                                                                           |

| Maximum capacitive load: 100 pF.                                                                                                       |

| STORE Low (true) during the last                                                                                                       |

| 1 microsecond of the BUSY signal.<br>Available fanout: 10 logic loads.                                                                 |

| Maximum capacitive load: 1000 pF.                                                                                                      |

| Output Enable High (true) during the time ADC                                                                                          |

| data is on the E-Bus (1.90 microseconds).                                                                                              |

| Available fanout: 20 logic loads.                                                                                                      |

| Maximum capacitive load: 100 pF.                                                                                                       |

| Digital Inputs                                                                                                                         |

| EXT START 1 K ohms to +5V, Lower to                                                                                                    |

| start ADC must raise and relower                                                                                                       |

| to restart ADC.                                                                                                                        |

| EXT SENSE 5.6 ohms to +5V, Low true                                                                                                    |

| sense input. Computer may test the status                                                                                              |

| of this input with a SEN 2YY instruction.                                                                                              |

| Power                                                                                                                                  |

| -22 Vdc ±2%; 2 mA                                                                                                                      |

| +5 Vdc ±5%; 1275 mA                                                                                                                    |

| Temperature Range                                                                                                                      |

| Specification                                                                                                                          |

| Operating                                                                                                                              |

| Storage                                                                                                                                |

| Physical Characteristics Dimensions: One printed circuit board 7 <sup>3</sup> / <sub>4</sub> x 12 x <sup>1</sup> / <sub>2</sub> inches |

| Connectors: One 122-terminal                                                                                                           |

| Connectors. One 122 terminal                                                                                                           |

| Two 44-terminal Card Edge connectors                                                                                                   |

|                                                                                                                                        |