## **Sun-3 Architecture Manual**

Version 1.0

**Company Confidential**

Sun Microsystems Inc.

14 January 1985

This document contains unpublished, proprietary information and describes subject matter proprietary to SUN MICROSYSTEMS INC. This document may not be disclosed to third parties or copied or duplicated in any form without the prior written consent of SUN MICROSYSTEMS INC.

# **Table of Contents**

| 1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 1                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------------------------------------------------------------|

| <ul><li>1.1. Definitions</li><li>1.2. Architecture Overview</li><li>1.3. Implementation Configurations</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 1<br>2<br>3                                                                           |

| 2. Address Spaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 4                                                                                     |

| <ul><li>2.1. CPU Space</li><li>2.2. Control Space</li><li>2.3. Device Space</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 4<br>4<br>4                                                                           |

| 3. CPU Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 5                                                                                     |

| 3.1. CPU Space Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | • | 5                                                                                     |

| 4. Control Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 6                                                                                     |

| <ul> <li>4.1. Access to Control Space Devices</li> <li>4.2. Sun-3 Memory Management Unit Summary</li> <li>4.3. Summary <ul> <li>4.3.1. Address Translation</li> </ul> </li> <li>4.4. MMU Overview</li> <li>4.5. Contexts</li> <li>4.6. Segment Map</li> <li>4.7. Page Map <ul> <li>4.7.1. Valid Bit</li> <li>4.7.2. Write Bit</li> <li>4.7.3. Supervisor Bit</li> <li>4.7.4. Don't Cache Bit</li> <li>4.7.5. PageType</li> <li>4.7.6. Statistics Bits: Accessed and Modified</li> <li>4.7.7. Reserved Field</li> <li>4.7.8. Physical Page Number</li> </ul> </li> <li>4.8. ID PROM</li> <li>4.9. System Enable Register</li> <li>4.10. User DVMA Enable Register</li> <li>4.11. Bus Error Register</li> <li>4.12. Diagnostic Register</li> </ul> |   | 6<br>7<br>7<br>8<br>8<br>8<br>8<br>8<br>8<br>9<br>9<br>9<br>9<br>10<br>11<br>12<br>13 |

| 5. Device Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 15                                                                                    |

| <ul> <li>5.1. Main Memory</li> <li>5.2. Frame Buffer</li> <li>5.2.1. No Frame Buffer</li> <li>5.2.2. Main-Memory Frame Buffer</li> <li>5.2.3. Dual-Ported Frame Buffer</li> <li>5.3. Memory Error Register</li> <li>5.3.1. Parity Error Register</li> <li>5.3.2. ECC Error Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 15<br>16<br>16<br>16<br>17<br>18<br>18                                                |

| 5.4. Clock                                                                               | 20       |

|------------------------------------------------------------------------------------------|----------|

| 5.5. Interrupt Register                                                                  | 21       |

| 5.6. EPROM                                                                               | 22       |

| 5.7. EEPROM                                                                              | 22       |

| 5.8. Serial Port                                                                         | 22       |

| 5.9. Keyboard/Mouse UART                                                                 | 23       |

| 5.10. Encryption Processor                                                               | 23       |

| 5.11. AMD Ethernet Interface                                                             | · 23     |

| 5.12. Intel Ethernet Interface                                                           | 25       |

| 5.13. VMEbus Master Interface                                                            | 26       |

| 5.13.1. VMEbus Master Interface                                                          | 26       |

| 5.14. VMEbus Slave Interface                                                             | 27       |

| 5.14.1. System DVMA                                                                      | 27       |

| 5.14.2. User DVMA                                                                        | 27       |

| 6. CPU Reset                                                                             | 29       |

| 7. CPU Interrupts                                                                        | 30       |

|                                                                                          |          |

| 8. The Sun-3 Cache Architecture                                                          | 31       |

| 8.1. The Sun-3 Cache: Its Structure and Operation                                        | 31       |

| 8.1.1. The Sun-3 Cache: Overview                                                         | 31       |

| 8.1.2. Cache Tags                                                                        | 32       |

| 8.1.3. The Cache Hit and Protection                                                      | 32       |

| 8.1.4. Definition of a Cache Hit                                                         | 33       |

| 8.1.5. Definition of Cache Protection                                                    | 33       |

| 8.1.6. Enabling the Cache                                                                | 33       |

| 8.1.7. Cache Access and Block Replacement                                                | 33       |

| 8.1.8. The MMU Accessed Bit                                                              | 35       |

| 8.1.9. Modified Bits for the Cache and MMU                                               | 35       |

| 8.1.10. Control Space Operations for the Cache                                           | . 35     |

| 8.1.11. Write Back Cycles, Control Space Operations, and the MMU                         | 36       |

| 8.1.12. Application of Control Space Operations on Sun-3 Caches                          | 37<br>37 |

| 8.1.13. Cache Error Conditions                                                           | 37<br>38 |

| 8.2. Sun-3 Cache Data Consistency                                                        | 38       |

| 8.2.1. Data Consistency: Overview 8.2.2. Data Consistency through Modulo 128K Addressing | 38       |

| 8.2.3. Modulo 128K Addressing: Sun-3 Cache Hardware Controls                             | 39       |

| 8.2.4. Data Consistency through Don't Cache Pages                                        | 39       |

| 8.3. Sun-3 Cache System Controls                                                         | 39       |

| 8.3.1. Sun-3 Cache System Controls: Overview                                             | 39       |

| 8.3.2. Read/Write Cache Tags                                                             | 41       |

| 8.3.3. Read/Write Cache Data                                                             | 42       |

| 8.3.4. Flush Cache Set [Context Match]                                                   | 43       |

| 8.3.5. Flush Cache Set [Page Match]                                                      | 44       |

| 8.3.6. Flush Cache Set [Segment Match]                                                   | 45       |

| 8.3.7. Block Copy [Read]                                                                 | 46       |

| 8 3 8 Rlock Copy [Write]                                                                 | Δ7       |

| Sun-3 Architecture Rev 1.0                 | Table of Contents              | ii    |

|--------------------------------------------|--------------------------------|-------|

| 9. The Sun-3 ECC Memory Arc                | hitecture                      | 48    |

| 9.1. The Sun-3 ECC Memory: (               | Overview                       | 48    |

| 9.1.1. ECC Memory Opera                    | ations                         | 48    |

| 9.1.2. Memory Error Cond                   | litions                        | 48    |

| 9.2. Error Reporting for ECC M             | lemory Systems                 | 48    |

| 9.2.1. Enabling Error Che                  | cking and Reporting            | 49    |

| 9.2.2. Reporting ECC Erro                  | ors                            | 49    |

| 9.3. Device Space Registers for ECC Memory |                                | 50    |

| 9.3.1. The Memory Error                    | and Address Registers          | 50    |

| 9.4. Addressing Registers on E             | ECC Memory Boards              | 51    |

| 9.4.1. The ECC Memory E                    | nable Register                 | 51    |

| 9.4.2. The ECC Memory E                    | nable Register: Initialization | 52    |

| 9.4.3. The Correctable Er                  | ror Register                   | 53    |

| 9.4.4. The ECC Chip Diag                   | nostic Register                | 53    |

| 10. Appendix: Physical Addres              | ss Map Example                 | 54    |

| 10.1. Physical Address Assign              | ments                          | 54    |

| 44 Deferences                              | · ·                            | p. p. |

## 1. Introduction

This document describes the Sun-3 architecture. It is intended as a reference for Sun-3 software, hardware, and systems implementors.

Features. The Sun-3 architecture is an extension of the Sun-2 architecture. Its main features are support of the 68020 CPU, the 68881 FPP, 8 KB pages, eight 256 MB contexts, and a 32-bit VMEbus. The Sun-3 architecture does not necessarily apply to any future CPUs.

Scope. This Sun-3 architecture manual describes all devices on the CPU Board. It does not describe devices that are on the system bus.

Implementation. The main part of this document is independent of a particular implementations of the architecture. Implementation specific data, such as timing information, need to be defined for each implementation.

Correctness. An important goal of this document is correctness. Please report any errors, omissions, or oversights immediately so they can be corrected in future revisions.

### 1.1. Definitions

In the subsequent description of the Sun-3 architecture the following abbreviations are used:

**CPU:** Central Processing Unit

**DVMA:** Direct Virtual Memory Access

MMU: Memory Management Unit

PMEG: Page Map Entry Group

POR: Power-On-Reset

### 1.2. Architecture Overview

The Sun-3 architecture is divided into three spaces: the CPU space, Control space, and Device space.

Introduction

The CPU space comprises all references of the 68020 CPU in function code 7.

The Control space is the core of the Sun-3 architecture. It includes the Sun-3 memory management unit (the "MMU") as well as all other Sun-3 architecture extensions to the CPU, such as the bus error register, the system enable register, the diagnostic register, and the ID-PROM. The ID-PROM contains a unique serial number and indicates the implementation type of the architecture.

The Device space of the Sun-3 architecture defines what devices exist in the architecture and how they are accessed. These devices include main memory, the system bus, and I/O devices.

All CPU accesses to device space pass through the MMU and thus are translated and protected in an identical fashion. In addition, direct memory accesses by DVMA masters such as the Ethernet or the VMEbus slave interface also pass through the memory memory management and thus operate in a fully protected environment.

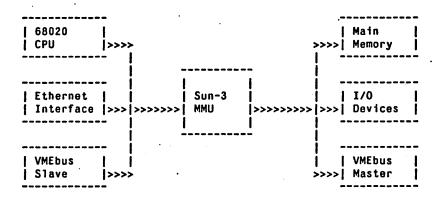

The figure below illustrates how the CPU, MMU, and devices are interconnected in the Sun-3 architecture. The CPU sends out a virtual address that is translated by the MMU into a physical address. The VME Master Interface, Main Memory, Video Memory, and I/O Devices are addressed with physical addresses on the right side of the MMU.

The CPU, Ethernet Interface, and VME Slave Interface arbitrate for and share the virtual address bus on the left side of the MMU. Of these three devices, the Ethernet has the highest priority, the VMEbus slave interface is the second highest, and the CPU is lowest.

## 1.3. Implementation Configurations

The Sun-3 architecture allows each implementations of the Sun-3 architecture to have its own configuration of devices. In addition, configurations may provide certain options in terms of main memory size and I/O devices. With this configuration flexibility comes a number of optional bits in registers. These Sun-3 implementation configurations are treated uniformly as follows:

- Machine Configuration. The machine type in the IDPROM indicates which devices the

machine has, or has options for, and the address assignment of such devices. The result

of an accesses to a physical address that is not defined for a given machine type is not

specified.

- Optional Main Memory. Each Sun-3 machine type has a minimum and maximum main memory. The minimum main memory size on a Sun-3 is 2 megabytes, the maximum depends on the machine type. An access to memory that is addressable, but not physically present, responds with timeout/bus error.

- Optional I/O Devices. Optional I/O devices are devices that are defined for a given machine type, but not necessary installed on a given machine, such as an optional data encryption processor. An access to an optional I/O defined that is not physically present respond with timeout/bus error.

- Optional Bits in Registers. These bits are defined in the architecture, but are only used in certain implementations, such as many of the bits in the system enable register. These bits exist for all implementations but have only an affect when used in a particular implementation.

- Unused bits in Page Map. Unimplemented bits in the page map physical address field read back as 0s.

## 2. Address Spaces

The Sun-3 architecture uses three address spaces: CPU Space, Control Space, and Device Space. These address spaces are decoded with different processor function codes.

The following table describes how different CPU function codes are mapped to the CPU, Control, and Device space.

| Address Space                     |

|-----------------------------------|

| Reserved                          |

| Device Space (User Data)          |

| Device Space (User Program)       |

| Control Space                     |

| Reserved                          |

| Device Space (Supervisor Data)    |

| Device Space (Supervisor Program) |

| CPU Space                         |

|                                   |

## 2.1. CPU Space

CPU space consists of all cycles that use function code 7. These include coprocessor cycles, interrupt, breakpoint and ring-protection cycles.

## 2.2. Control Space

Control space consists of all cycles that use function code 3. This includes accesses to the memory management unit (the "MMU"), to the bus error register, the system enable register, the user enable register, the diagnostic register, the ID-PROM, and the cache if one is present.

## 2.3. Device Space

Device space includes all devices that are accessed by the CPU with data or program space instructions. These devices include main memory, the VMEbus, I/O devices, and so on. All devices are accessed via the MMU. This allows all devices to be protected, shared, and managed in a uniform manner in a multiprocess environment.

# 3. CPU Space

CPU space consists of all cycles that use function code 7. This includes coprocessor cycles, interrupt, breakpoint and ring-protection cycles.

## 3.1. CPU Space Cycles

In the Sun-3 architecture, address bits A16 and A17 are decoded to determine the type of CPU space cycle as follows:

| TYPE              | A17 | A16 | RESPONSE        |

|-------------------|-----|-----|-----------------|

| BREAKPOINT CYCLE  | 0   | 0   | BERR            |

| RINGPROTECTION    | 0   | 1   | BERR            |

| COPROCESSOR CYCLE | 1   | 0   | DSACK/BERR      |

| INTERRUPT CYCLE   | 1   | 1   | AVEC/DSACK/BERR |

Breakpoint and ringprotection cycles are terminated with Bus Error.

For Coprocessor cycles, address bits A13 through A15 are also decoded. If A13 = 1 and A14 = 0 and A15 = 0 then the reference is directed to the floating point coprocessor and terminated normally. If no floating point coprocessor is physically present, i.e. if the FPP chip is not plugged in, a timeout/bus error is generated to allow software emulation of the instruction. Other coprocessor cycles are terminated with timeout/bus error as well.

Interrupt cycles are normally terminated with AVEC (autovector) for most onboard interrupts, and with DSACK for VME and vectored interrupts, unless the interrupt vector acquisition is aborted with BERR.

## 4. Control Space

Control Space includes the Sun-3 memory management unit and all Sun-3 architectural extensions to the CPU. These extensions include the bus error register, the system enable register, the user enable register, the diagnostic register, the ID-PROM, and the cache if one is present.

## 4.1. Access to Control Space Devices

Control space devices are decoded via the high-order address bits. For IDPROM and map accesses, additional virtual address bits determine which map entry is being modified. For accesses to the page map and segment map, the value of the context register determines which context's map will be modified. Thus, for user virtual address V, the map entries are accessed as follows:

| REGISTER/MAP                                                                                                | ADDRESS BASE                                                                                                                               | SIZE                                                            | TYPE                                              | RELEVANT BITS                                      |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------|

| ID PROM PAGE MAP SEGMENT MAP CONTEXT REG. SYSTEM ENABLE USER ENABLE BUS ERROR REG. DIAGNOSTIC REG. RESERVED | 0x00000000 + V<br>0x10000000 + V<br>0x20000000 + V<br>0x30000000<br>0x40000000<br>0x50000000<br>0x60000000<br>0x70000000<br>0x8000000000xF | BYTE<br>LONG<br>BYTE<br>BYTE<br>BYTE<br>BYTE<br>BYTE<br>OOOOOOO | READ<br>R/W<br>R/W<br>R/W<br>R/W<br>READ<br>WRITE | V & 0x0000001F<br>V & 0x0FFFE000<br>V & 0x0FFE0000 |

The reserved addresses are reserved for controlling cache operation in machines that have a cache. Accessing these locations has no effect if no cache is implemented.

## 4.2. Sun-3 Memory Management Unit Summary

### 4.3. Summary

8 KBytes page size: segment size: 128 KBytes process size: 256 MBytes # of contexts: 8 # of segments/context: 2048 # of pages/segment: 16 # of pmegs: 256 4096 . # of pages total: # of segments total: 16384

### 4.3.1. Address Translation

#### 4.4. MMU Overview

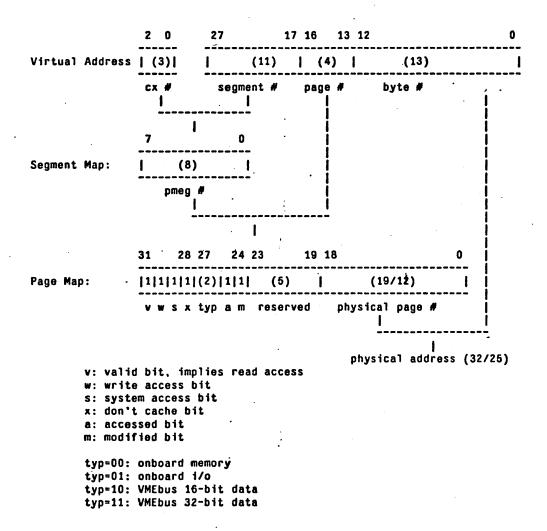

The memory management consists of a context register, a segment map, and a page map. Virtual addresses from the processor are translated into intermediate addresses by the segment map and then into physical addresses by the page map. The MMU uses a page size of 8K bytes and a segment size of 128K bytes. Eight contexts with an address space of 256M bytes each are provided.

### 4.5. Contexts

The Sun-3 MMU is divided into 8 distinct address spaces or "contexts". The current context is selected by means of a 3-bit *context* register. The same context applies to both user and supervisor state.

## 4.6. Segment Map

The segment map has 16384 entries. It is indexed by the 3 bits of the current context register and the 11 most significant bits of the virtual address, bits 17 through 27. Thus, the segment map is divided into 8 contexts of 2048 entries each. Segment map entries are 8 bits wide, pointing to a page map entry group (pmeg).

## 4.7. Page Map

The page map contains 4096 page entries each mapping an 8K byte page. Page map entries are composed of a valid bit, protection field, don't cache bit, type field, accessed and modified bits, and a page number.

The page map is divided into 256 sections of 16 entries each. Each section is pointed to by a segment map entry and is called a page map entry group, or *pmeg*.

### 4.7.1. Valid Bit

The valid bit means that the page entry is valid. It also allows read and execute access to the page.

### 4.7.2. Write Bit

The write bit allows write access to the page.

## 4.7.3. Supervisor Bit

If the supervisor bit is set, the read and write access protection applies only to the supervisor and no access is permitted to the user. If the supervisor bit is clear, the access protection applies both to the supervisor and user.

### 4.7.4. Don't Cache Bit

If this bit is set then the page referenced will not be cached. The don't cache bit is meaningful only for implementations of the Sun-3 architecture that include a cache. In machines without a cache the bit can be read and written but has no effect.

## 4.7.5. PageType

The 2-bit page type field provides for four physical address spaces, each starting at a physical address of 0. The four types are:

PMAP<27..26>: TYPE

0 - Main Memory

1 - I/O Devices

2 - VMEbus 16-bit data

3 - VMEbus 32-bit data

### 4.7.6. Statistics Bits: Accessed and Modified

The accessed and modified bits are set, as the name implies, whenever a page is accessed or modified (written into). The statistics bits are automatically updated for all cycles except if the page is invalid or protected. The statistic bits may not be correct if a cache is present.

PMAP<25>: ACCESSED

0 - Not Accessed

1 - Accessed

PMAP<24>: MODIFIED

0 - Not Modified

1 - Modified

In Sun-3 implementations with a cache, the accessed and modified bits are only updated on memory accesses that "miss" the cache. The section "MMU Access Bit" and "Modified Bits for the Cache and MMU" in the Cache chapter further discuss statistic bit updates in systems with a cache.

## 4.7.7. Reserved Field

The reserved field in the page map has no function. It can be written into, but it always reads back as 0.

PMAP<24..19>: RESERVED

## 4.7.8. Physical Page Number

The page number field in conjunction with the byte address generates the physical address. The page number field is either 12 bits or 19 bits wide. In conjunction with the 13-bit physical byte number, the 12-bit page number field generates a 25-bit physical address, whereas the 19-bit page number field generates a 32-bit physical address. In case of the 12-bit page number field, the unused bits <18..13> have no function; they can be written into, but they always reads back as 0.

PMAP<18..0>: PAGE NUMBER

### **4.8. ID PROM**

The purpose of the ID PROM is to provide information about the machine. This includes basic information on the machine type, a unique serial number for software licensing and distribution, a unique Ethernet address, the date of manufacturing, and a checksum. In addition, the ID PROM stores configuration data for the machine.

The ID PROM is a 32 byte bipolar PROM that is not modifiable.

| REG   | ISTER | ₹    | ADDRESS | SIZE  | TYPE      |

|-------|-------|------|---------|-------|-----------|

| ID    | PROM  | 0    | 0x0000  | BYTE  | READ-ONLY |

| ID    | PROM  | 1    | 0x0001  | BYTE  | READ-ONLY |

| ID    | PROM  | 2    | 0x0002  | BYTE  | READ-ONLY |

| • • • |       |      | • • •   | • • • | • • •     |

| ID    | PROM  | 0x1F | 0x001F  | BYTE  | READ-ONLY |

The content of the ID PROM is as follows:

| Entry Field                                                                        |                                          | $0 \times = 500 \times 3$                               |

|------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------------------|

| <ul><li>(1) Format</li><li>(2) Machine Type</li><li>(3) Ethernet Address</li></ul> | 1 Byte<br>1 Byte<br>6 Bytes              | X1 = MULTIBUS<br>X2 = Ume                               |

| (4) Date<br>(5) Serial Number<br>(6) Checksum<br>(7) Reserved                      | 4 Bytes<br>3 Bytes<br>1 Byte<br>16 Bytes | 1 = Carrera (160)<br>12 = M25 (50)<br>13 = SICIUS (260) |

| dotoil                                                                             |                                          | 14 = prism (110)<br>17 = SUNSF (60)                     |

#### In detail:

- (1) Format. The format of the ID PROM.

- (2) Machine Type. A number specifying an implementation of the architecture.

- (3) Ethernet Address. This is the unique 48-bit Ethernet address assigned by Sun to this machine.

- (4) Date. The date the ID PROM was generated. It is in the form of a 32-bit long word which contains the number of seconds since January 1, 1970.

- (5) Serial Number. This is a 3-byte serial number.

- (6) Checksum. The checksum is defined such that the longitudinal XOR of the first 16 bytes of the PROM including the checksum yields 0.

- (7) Reserved. This field will be specified in a future revision of this document.

## 4.9. System Enable Register

The System Enable Register enables system facilities and allows booting. This register can be read and written under software control and is cleared on power up (hardware reset) and watchdog reset, but not upon CPU reset. Bits are assigned as follows:

Initialization: cleared on power-up-reset

REGISTER ADDRESS DATA TYPE

SYSTEM ENABLE 0x40000000 BYTE READ/WRITE

The fields of the system enable register are as follows:

#### SYSTEM ENABLE REGISTER FIELDS

| DO EN.DIAG Read back diagnostic switch       |               |

|----------------------------------------------|---------------|

| D1 (res) reserved                            |               |

| D2 EN.COPY Enable copy mode to video memory  | , if present  |

| D3 EN.VIDEO Enable video display and copy mo | de if present |

| D4 EN.CACHE Enable external cache if present | •             |

| D5 EN.SDVMA Enable system DVMA if present    |               |

| D6 EN.FPP Enable floating point processor    | if present    |

| D7 EN.BOOT- Enable Boot State (0 => boot, 1  |               |

When cleared after power-up or watchdog reset, all bits are initialized to 0. In this state, boot state is active whereas all other enables are disabled.

EN.DIAG. This bit reads back the external diagnostic switch. A "0" bit read means that the switch is in its normal state (not-diagnostic), whereas a "1" means that the switch is activated (diagnostic).

EN.COPY. This bit enables the copy update mode to the video memory, if present.

EN. VIDEO. This bit enables the video signal to the video monitor, if present,

EN.CACHE. This bit enables the external cache, if present.

EN.SDVMA. This bit enables the system DVMA from the system bus, if present.

EN.FPP. This bit enables the floating point coprocessor (FPP), if present. If this bit is deasserted, then accesses to the FPP cause a bus error. If the bit is asserted, accesses are directed to the FPP. In the later case, if no FPP is present, then the access still will result in bus error.

EN.BOOT. Boot state forces all supervisor program fetches to the EPROM device independent of the setting of the memory management. All other types of references are unaffected and will be mapped as during normal operation of the processor.

## 4.10. User DVMA Enable Register

On implementations of the architecture that allow user DVMA, this register controls which contexts have DVMA access. For each context, a separate enable bit is provided.

|               |            | ed on power-up-reset |            |  |

|---------------|------------|----------------------|------------|--|

| REGISTER      | ADDRESS    | DATA                 | TYPE       |  |

| USER DVMA EN. | 0x50000000 | BYTE                 | READ/WRITE |  |

The fields of the user DVMA enable register are as follows:

| SYSTEM | ENABLE REGISTER FIELDS |

|--------|------------------------|

|        |                        |

| D0     | EN.CXO                 |

| D1     | EN.CX1                 |

| D2     | EN.CX2                 |

| D3     | EN.CX3                 |

| D4     | EN.CX4                 |

| D5     | EN.CX5                 |

| D6     | EN.CX6                 |

| D7     | EN.CX7                 |

|        |                        |

When cleared after power-up or watchdog reset, all bits are initialized to 0. In this state, all user DVMA is disabled.

## 4.11. Bus Error Register

When a bus error occurs, the bus error register latches its cause to allow software to identify the source of the bus error. The bus error register always latches the cause of the most recent bus error. Thus, in the case of stacked bus errors, the information relating to the earlier bus errors is lost.

The bus error register is a read-only register.

| REGISTER  | ADDRESS    | DATA | TYPE      |

|-----------|------------|------|-----------|

|           |            |      |           |

| BUS ERROR | 0x60000000 | BYTE | READ-ONLY |

The fields of the bus error registers are defined as follows:

| BIT                  | NAME        | MEANING          |

|----------------------|-------------|------------------|

| D0<br>D1<br>D2<br>D3 | 0<br>0<br>0 | Watchdog Késet   |

| D4                   | VMEBERR     | VMEbus Bus Error |

| <b>D</b> 5           | TIMEOUT     | Timeout Error    |

| D6                   | PROTERR     | Protection Error |

| <b>D7</b>            | INVALID     | Invalid Page     |

|                      |             |                  |

In more detail, the bus error conditions are as follows:

- INVALID means that the valid bit in the page map was not set.

- PROTERR means that the page protection bits did not allow the kind of operation attempted.

- TIMEOUT results from accessing non-existing devices, both on-board and off-board.

- VMEBERR indicates a VMEbus cycle acknowledged with a bus error.

## 4.12. Diagnostic Register

The diagnostic register drives an 8-bit LED display for displaying error messages. A "0" bit written will cause the corresponding LED to light up, a "1" bit to be dark. Upon power-on-reset, the diagnostic register is initialized to 0 causing all LEDs to light up.

| Initialization: |         |      |            |

|-----------------|---------|------|------------|

| REGISTER        | ADDRESS | DATA | TYPE       |

| DIAGNOSTIC REG. |         | BYTE | WRITE-ONLY |

## 5. Device Space

Device space includes all the devices of the system that are accessed through the memory management. This includes main memory, video memory, and input/output devices.

In the following, each device is described in terms of its initialization, interrupts, exceptions, reference, and register mapping.

Not all devices are present in all implementations of the architecture. Which devices are present and their physical addresses are described in the implementation section for each machine type. However, the following devices are required for all implementations:

- Main Memory

- Memory Error Register

- Interrupt Register

- EPROM

- EEPROM

- Clock

## 5.1. Main Memory

Main memory is the primary system memory. It has a minimum size of 2 Megabytes and it is contiguous in physical addresses. The addressing hardware decodes all bits present in the page number field of the MMU. An access to addressable but not-existing memory causes a timeout.

| LOCATION   | ADDRESS    | DATA | ТҮРЕ       |

|------------|------------|------|------------|

| 0x00000000 | 0x00000000 | LONG | READ-WRITE |

|            |            |      |            |

In most implementations, main memory is built from dynamic RAM chips. The dynamic RAMs are refreshed in hardware.

For main memory equipped with parity checking, parity must be initialized by writing all of memory. A Parity exception is caused if parity read is different from parity written and parity checking is enabled in the parity error register.

### 5.2. Frame Buffer

A Sun-3 implentation has one of three frame buffer options: no frame buffer, main-memory frame buffer, and dual-ported frame buffer. These options are further described below.

Additional, external display devices and frame buffers can be added to those implementations of the architecture that include a system bus. Those external frame buffers are not within the scope of this document.

The main-memory and the dual-ported frame buffer have the same architecture. In both cases, the frame buffer is mapped to the display screen as follows:

Data bit 15 of Word 0 of frame buffer is the first visible pixel in the upper left corner of the display. Consecutive words are displayed along the horizontal scanline left to right. After \display-width\number of pixels have been displayed, the next word is displayed at the beginning of the next horizontal line, up to \display-height\number of lines. \display-width\number and \display-height\number are implementation constants. The display data polarity is such that "1" bits are black on the screen and "0" bits are white.

### 5.2.1. No Frame Buffer

| WORD (M-1)\*N | ...

N = <display-width> / 16

If there is no frame buffer, then the Video Enable Bit and the Copy Enable Bit of the System Enable Register are not used.

## 5.2.2. Main-Memory Frame Buffer

In this alternative the frame buffer is resident in main memory and the video display is refreshed out of main memory.

The visible display area starts at memory address 1 megabyte and extends to the size of the display. The maximum size of the visible display area is 128 kilobytes.

| REGISTER | ADDRESS  | DATA | ТҮРЕ       |

|----------|----------|------|------------|

| 0x000000 | 0x100000 | LONG | READ-WRITE |

| 0x01FFFC | 0x11FFFC | LONG | READ-WRITE |

Relevant bits in the system enable register are the Video Enable Bit and the Copy Enable Bit. The Video Enable Bit turns the display on and off. The Copy Enable Bit is not used. 4 14065 1000 to 1000 1000

**Device Space**

### 5.2.3. Dual-Ported Frame Buffer

In this configuration, the frame buffer is located in a dedicated 128K byte video memory. This video memory is dual-ported; one port performs video refresh, the second port provides processor access.

| REGISTER | ADDRESS  | DATA | TYPE .     |

|----------|----------|------|------------|

| 0x000000 | 0x000000 | LONG | READ-WRITE |

| 0x01FFFC | 0x01FFFC | LONG | READ-WRITE |

Relevant bits in the system enable register are the Video Enable Bit and the Copy Enable Bit. The Video Enable Bit turns the display on and off. The Copy Enable Bit enables the copy mode (see below).

The video memory can be updated in two ways. First, it can be read and written directly like memory. As such, it is visible as a 128 KByte block of memory locations. Second, the video memory can be written in copy mode as a side-effect of writing into special region of main memory.

Main memory shadowes video memory in the range of physical addresses starting at 1 megabytes and extending for 128 kilobytes. This area of main memory is called the copy region. If the copy enable bit in the system enable register is set, then data written into this copy region is also written into the video memory at the same location within the 128K region. A read from the copy region returns the data in main memory and does not affect the video memory.

## 5.3. Memory Error Register

All Sun-3 implementations have either memory parity error detection or memory equipped with error correction. The error reporting from these memory error mechanism is performed by the memory error register described in this section.

The memory error register consists of a control and an address register. If an error occurs, the control register stores information relevant to the error. The memory error address register stores the virtual address, the context number, and the CPU/DVMA bit of the memory cycle at which the error was detected.

Errors are reported via the non-maskable level 7 interrupt. In case of multiple (stacked) memory errors, the information relating to the first error is latched in the memory error register. The interrupt is held pending and the error information in the memory error register is latched (frozen) until it is cleared (unfrozen) by a write to bits <31...24> of the memory error address register.

| Interru<br>Initial | •                                  | vel 7 Autove<br>eared on po |              | set                                    |            |

|--------------------|------------------------------------|-----------------------------|--------------|----------------------------------------|------------|

| ADDRESS            | REGISTER                           |                             | DATA         | TYPE                                   |            |

| 0                  | MEMORY ERR<br>MEMORY ERR           |                             | BYTE<br>Long | READ-WRITE<br>READ-WRITE               |            |

| MEMORY             | ERROR ADDRE                        | SS REGISTER                 |              |                                        |            |

| BIT                | NAME                               | MEANI                       | NG           |                                        |            |

| D<302              | DVMA-BIT<br>8> CX<20><br>0> VA<270 | Conte                       | xt Number    | cle caused pa<br>(3 bit)<br>s (28 bit) | arity erro |

The definition of the memory error control register depends on the error reporting mechanism and is detailled below for parity and ECC error detection.

## 5.3.1. Parity Error Register

For systems equipped with parity main memory, the memory error control register provides the necessary control and information to deal with parity error.

It stores the information on the byte causing the parity error, it indicates parity error interrupts pending, and it provides functions to test parity error checking.

| PARITY | ERROR CO | NTROL REGIS  | rer              |          |

|--------|----------|--------------|------------------|----------|

| BIT    | NAME     |              | ТҮРЕ             |          |

| D<0>   | PARITY   | ERROR OO     | 'read-only       |          |

| D<1>   | PARITY   | ERROR 08     | read-only        | <b>k</b> |

| D<2>   | PARITY   | ERROR 16     | read-only        |          |

| D<3>   | PARITY   | ERROR 24     | read-only        |          |

| D<4>   | PARITY   | CHECK        | read-write       |          |

| D<5>   | PARITY   | TEST         | read-write       |          |

| D<6>   | PARITY   | INTERRUPT EI | NABLE read-write |          |

| D<7>   | PARITY   | INTERRUPT    | read-only        |          |

The four parity error bits are set when a parity error was detected in the corresponding byte. Parity

Sun Microsystems Inc CONFIDENTIAL 14 January 1985

check is set to enable parity checking on memory read cycles. Parity test is set to write parity with the inverse polarity to test the operation of the parity error circuitry. With parity test off, correct parity is generated on all memory write cycles. Parity interrupt enable enables level 7 interrupts if a parity error is detected. Parity interrupt is true if a parity interrupt is pending.

## 5.3.2. ECC Error Register

For systems equipped with ECC main memory, the memory error control register provides the necessary control and information to deal with ECC error. The format of the ECC error register is spelled out in the section on ECC memory.

## 5.4. Clock

The timer is an Intersil 7170 time-of-day clock with battery backup. The timer crystal has a frequency of 32.768 kHz. It is expected that the clock interrupt output is driven in the 100 Hz periodic mode. This clock interrupt output signal causes an interrupt request on level 5 or 7 via the interrupt register, if the respective levels are enabled.

| Interrupt:<br>Initialization:<br>Reference: | None    |      | tovector<br>ata Sheet |

|---------------------------------------------|---------|------|-----------------------|

| REGISTER                                    | ADDRESS |      | TYPE                  |

| CLOCK REG 0x0                               | 0       | ВҮТЕ | READ/WRITE            |

| CLOCK REG 0x11                              | 0x11    | ВҮТЕ | READ/WRITE            |

## 5.5. Interrupt Register

The interrupt register provides for the generation of software interrupts and controls the video and clock hardware interrupts on the board. It has the following fields:

Initialization: cleared on reset Interrupt: Level 1,2,3,4,5,7, autovectored ADDRESS DATA VIDEO CONTROL REGISTER O BYTE READ-WRITE \_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_ NAME MEANING BIT EN.INT Enable all Interrupts EN.INT2 Software Interrupt Level 2 read-write

EN.INT3 Software Interrupt Level 3 read-write

FN.INT4 Fortage Property Control of the Property Control o D1 D2 D3 EN.INT4 Enable Video Interrupt Level 4 read-write **D4** D5 EN.INT5 Enable Clock Interrupt Level 5 read-write EN.INT6 (reserved) read-write **D7** EN.INT7 Enable Clock Interrupt Level 7 read-write

EN.INT. This bit enables all interrupts. If this bit is off, no interrupts will occur.

*EN.INT[1..3]*. These bits cause software interrupts on the corresponding level. The interrupt request caused by an EN.INT[1..3] bit stays active until software clears the corresponding bit.

EN.INT4 enables video interrupt requests on level 4. When enabled, a level 4 interrupt request is set at the rising edge of vertical retrace. The level 4 interrupt request is cleared by momentarily turning off the EN.INT4 bit.

EN.INT5 enables clock interrupt requests on level 5. When enabled, a level 5 interrupt request is set on the rising edge of the clock interrupt output. The level 5 interrupt request is cleared by momentarily turning off the EN.INT5 bit.

EN.INT6 is a reserved bit. It can be read and written but has no effect.

EN.INT7 enables clock interrupt requests on level 7. When enabled, a level 7 interrupt request is set on the rising edge of the clock interrupt output. The level 7 interrupt request is cleared by momentarily turning off the EN.INT7 bit.

### **5.6. EPROM**

Device EPROM consists of one 27128, 27256, or 27512 type EPROM providing 16K, 32K, or 64K bytes of PROM storage, respectively.

| none    |                         |                               |

|---------|-------------------------|-------------------------------|

| none    |                         |                               |

| none    |                         |                               |

| ADDRESS | DATA                    | TYPE                          |

| 0       | BYTE                    | READ-ONLY                     |

| 1       | BYTE                    | READ-ONLY                     |

|         |                         | •                             |

|         | none<br>none<br>ADDRESS | none none ADDRESS DATA 0 BYTE |

Unlike other devices, the EPROM is addressed directly with virtual address bits from the CPU. Thus, even though each 8K page must be enabled with its own entry in the page map, the physical page number in the page map is ignored and the low-order bits of the virtual address are used instead.

The EPROM device is also accessed in boot state. In boot state, all supervisor program fetches are forced to fetch from the EPROM device, independent of the setting of the memory management.

### 5.7. EEPROM

Device EEPROM consists of one 2816 type EEPROM providing 2K Bytes of electrically erasable storage.

| Reference:<br>Interrupt:<br>Initialization: | none<br>none |      |            |

|---------------------------------------------|--------------|------|------------|

| REGISTER                                    | ADDRESS      | DATA | ТУРЕ       |

| BYTE 0                                      | 0            | BYTE | READ-WRITE |

| BYTE 1                                      | 1            | BYTE | READ-WRITE |

| • • • •                                     |              |      |            |

To modify the EEPROM, each byte must be written separately. After writing each byte a 10 millisecond pause must be observed before the EEPROM can be read or written again.

### 5.8. Serial Port

Serial ports are implemented with the Zilog 8530 SCC (serial communication controller). The SCC features two high-speed, fully symmetrical and highly programmable serial channels with built-in baud-rate generators. Channel A is connected to the UART A, channel B to UART B. The clock input to the SCC is a 4.9152 MHz clock, independent of the CPU clock.

The SCC is mapped as follows:

Interrupt: Level 6 Vectored (preferred) or Autovectored Initialization: Needs to be initialized in software Reference: Zilog 8530 SCC data sheet Recovery Time: 1.6 microseconds

REGISTER ADDRESS DATA TYPE

CH B CONTROL 0 BYTE READ/WRITE CH B DATA 2 BYTE READ/WRITE CH A CONTROL 4 BYTE READ/WRITE CH A DATA 6 BYTE READ/WRITE

## 5.9. Keyboard/Mouse UART

These serial ports are implemented with the Zilog 8530 SCC (serial communication controller). The SCC features two high-speed, fully symmetrical and highly programmable serial channels with built-in baud-rate generators. Channel A is connected to the Keyboard, channel B to the mouse. The clock input to the SCCs is a 4.9152 MHz clock, independent of the CPU clock. Control lines are not used.

#### The SCC is mapped as follows:

Interrupt: Level 6 Vectored (preferred) or Autovectored Initialization: Needs to be initialized in software Reference: Zilog 8530 SCC data sheet Recovery Time: 1.6 microseconds

REGISTER ADDRESS DATA TYPE

CH B CONTROL 0 BYTE READ/WRITE CH B DATA 2 BYTE READ/WRITE CH A CONTROL 4 BYTE READ/WRITE CH A DATA 6 BYTE READ/WRITE

## 5.10. Encryption Processor

The Encryption processor is an AMD 8068 data ciphering processor providing high-speed NBS DES encryption. To access an internal register in the 8068, the address register must be written first. Once the address register is setup, the selected register can be accessed repeatedly.

Initialization: none

Interrupts: none

Reference: AMD 8068 data sheet.

Recovery Time: 1.6 microseconds

REGISTER ADDRESS DATA TYPE

DATA REGISTER 0 BYTE READ/WRITE

ADDRESS REG. 2 BYTE WRITE-ONLY

### 5.11. AMD Ethernet Interface

The AMD Ethernet Interface uses the AMD 7990 chip. The 7990 accesses the top 16 Megabytes of the current virtual address space with a supervisor data function code. The 7990 must be configured

in BCON = 0 mode in its CSR register.

Bus cycles The 7990 must access TYPE0 space only, otherwise they will not complete and the 7990 will post a timeout error. The 7990 can also post a timeout error because of a protection error, or a parity error on read operations.

Initialization: reset on all resets

Interrupts: Level 3, Autovector

Reference: AMD 7990 data sheet.

REGISTER ADDRESS DATA TYPE

DATA PORT 0 WORD READ/WRITE

CONTROL PORT 2 WORD READ/WRITE

### 5.12. Intel Ethernet Interface

The Intel Ethernet Interface uses the Intel 82586 chip. Configured in maximum mode, the 82586 accesses the top 16 Megabytes of the current virtual address space with a supervisor data function code.

The 82586 must access TYPE0 space only, otherwise it gets a bus error. The 82586 also can get a bus error because of a protection error, or a parity error on read operations. If a bus error occurs during an 82586 operation, the error bit in the Ethernet control register is set and further activity is inhibited until the 82586 is reset.

The 82586 is connected to the system in a permanent byte-reversed mode, i.e. 82586 bits 0 through 7 are connected to 68000 bits 8 through 15 and vice versa. This causes Ethernet data to be stored in memory in CPU byte order, whereas 82586 control blocks in memory are byte swapped.

Overall operation of the Ethernet Interface is controlled by the Ethernet control register that has the following definition.

| Initialization:<br>Interrupts:<br>Reference: | Level 3 | on all<br>, Autove<br>2586 dat | ctor       |

|----------------------------------------------|---------|--------------------------------|------------|

| REGISTER                                     | ADDRESS | DATA                           | TYPE       |

| CONTROL REG.                                 | 0 .     | BYTE                           | READ/WRITE |

The fields of the Ethernet control register are assigned as follows:

| BIT       | NAME   |                   | ТҮРЕ       |

|-----------|--------|-------------------|------------|

| DO        | INT    | Interrupt Pending | Read-Only  |

| D1        | ERR    | Error Pending     | Read-Only  |

| D2        | 0      | 0                 | Read-Only  |

| D3        | 0.     | 0                 | Read-Only  |

| D4        | INTEN  | Interrupt Enable. | Read-Write |

| D5        | CA     | Channel Attention | Read-Write |

| D.6       | LOOPB* | Loopback          | Read-Write |

| <b>D7</b> | RESET* | Reset             | Read-Write |

|           |        |                   |            |

INT signals Interrupt from the 82586 or an error pending condition (ERR = 1).

ERR indicates that a Bus Error occured during an 82586 channel operation, inhibiting further channel activity. To reset the ERR condition, the

CRESET bit in the Ethernet control register must be activated.

INTEN enables 82586 interrupts to the CPU.

CA signals channel attention to the 82586.

LOOPB\* controls whether the front-end encoder/decoder is configured in loopback mode (LOOPB\* = 0) or connected to the transceiver cable (LOOPB\* = 1).

RESET initializes the 82586 when active (RESET\* = 0) and allows normal operation when inactive (RESET\* = 1). It also clears the ERR condition when active.

### 5.13. VMEbus Master Interface

The VMEbus interface is dual-ported. The VMEbus Master Interface provides access from the CPU to the VMEbus, whereas the VMEbus Slave Interface provides access from the VMEbus to the CPU. Neither the slave or the master interface supports sequential access modes or read-modify-write cycles.

The VMEbus interface does not support multiple Sun-3 boards in one backplane, except for testing purposes. It does not implement an interrupter function to the VMEbus. Other specifications of the VMEbus interface are:

Address Bus Option: A32 MASTER, A32 SLAVE

• Data Bus Option: D32 MASTER, D32 SLAVE

• Timeout Period: 100 microseconds minimum excluding bus acquisition

Arbiter Option: ONE (single level), can be disabled

Requestor Option: ROR (release on request)

Interrupt Handler Options: IH(1-7)

### 5.13.1. VMEbus Master Interface

The Master VMEbus Interface uses two page map types: one for 16-bit data, and one for 32-bit data. For each type, three VMEbus address spaces are supported: 4 Gbytes minus the top 16 MBytes for 32-bit addressing, the top 16 MBytes minus the top 64 KBytes for 24-bit addressing, and the top 64 KBytes for 16-bit addressing.

| Interr<br>Except<br>Refere | ions: Timeou                                 | Level 1 through 7, Vectored<br>Timeout after 200 microseconds<br>Motorola VMEbus Specification |  |  |

|----------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------|--|--|

| TYPE                       | ADDRESS                                      | ADDRESS SPACE                                                                                  |  |  |

| 2                          | 32-bit                                       | VMEbus 16-bit data                                                                             |  |  |

|                            | [0x00000000]<br>[0xff000000]<br>[0xffff0000] | VMEbus 32-bit address space<br>VMEbus 24-bit address space<br>VMEbus 16-bit address space      |  |  |

| 3                          | 32-bit                                       | VMEbus 32-bit data                                                                             |  |  |

|                            | [0x00000000]<br>[0xFF000000]<br>[0xFFFF0000] | VMEbus 32-bit address space<br>VMEbus 24-bit address space<br>VMEbus 16-bit address space      |  |  |

|                            |                                              |                                                                                                |  |  |

Initialization: Processor Reset causes VMEbus INIT

### 5.14. VMEbus Slave Interface

The VMEbus Slave Interface provides access from the VMEbus to the CPU. The VMEbus Slave Interface causes a range of VMEbus memory addresses to be treated as though they were a range of virtual addresses generated by the processor.

There are two kinds of VMEbus DVMA in the Sun-3: System DVMA and User DVMA. Both modes have the following attributes:

- Byte, Word, and Longword transfers are supported.

- Only physically existing on-board memory (TYPE = 0) may be accessed. Access to nonexisting memory or other devices is not defined.

- VMEbus Bus Error is signalled if the DVMA cycle encounters a protection error, attempt

to access a page type that is not equal to 0, or on read cycles that cause a memory parity

or uncorrected double-bit ECC error. The memory parity error is synchronous unlike

processor parity errors. Memory parity errors are also reported to the CPU via interrupts.

- Implementations of DVMA can offer high-bandwidth burst modes that allow fast DVMA devices to increase throughput.

## 5.14.1. System DVMA

System DVMA responds to the lowest megabyte of the VMEbus address range in both the 24-bit and 32-bit address spaces and shifts the reference to the highest megabyte in virtual address space. System DVMA is enabled via a bit in the system enable register. System DVMA cycles use supervisor function code in accessing memory; a bus error is signalled if the page being accessed is not valid or if a write is attempted to a read-only page.

| VME-Address A24, A32   | Virtual Address        |

|------------------------|------------------------|

| [0x000000000x000FFFFF] | [0xfff000000xffffffff] |

### 5.14.2. User DVMA

User DVMA responds to the most significant 2 GBytes of the VMEbus 32-bit address space. A user DVMA reference is mapped to the virtual address contained in bits 0 through 27 of the VMEbus address and to the context contained in bits 28 through 30 of the VMEbus address. User DVMA is enabled via the user DVMA enable register which has one bit per context. If a context is not enabled for user DVMA, then the CPU does not respond to the addresses on the VME cycle at all; this allows sharing of the upper 2 gigabytes of the VME address space with other VME devices.

User DVMA cycles use user function code in accessing memory; a bus error is signalled if the page being accessed is not valid for user access. This bus error is not visible to the CPU. VMEbus masters that expect bus error support from the CPU must then post an interrupt to the CPU and must make the appropriate information about the bus error available to the CPU.

| VME-Address                                                                                                                                                                              | Virtual Address                                                                                                                                                                                                                    |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [0x800000000x8FFFFFFF] [0x900000000x9FFFFFFF] [0xA00000000xAFFFFFFF] [0xB00000000xBFFFFFFF] [0xC00000000xCFFFFFFF] [0xD00000000xCFFFFFFF] [0xE00000000xEFFFFFFF] [0xF000000000xFFFFFFFF] | CX=0 [0x000000000x0fffffff] CX=1 [0x000000000x0fffffff] CX=2 [0x000000000x0fffffff] CX=3 [0x000000000x0fffffff] CX=4 [0x000000000x0fffffff] CX=6 [0x000000000x0ffffffff] CX=6 [0x000000000x0ffffffff] CX=7 [0x000000000x0ffffffff] |  |

## 6. CPU Reset

Three types of reset need to be distinguished: Power-On Reset, Watchdog Reset, and CPU Reset.

Power-On Reset. Power-On Reset (POR) is active for 100 milliseconds minimum after the power supply voltage reaches 4.5V. POR resets the CPU and clears the System Enable register forcing boot state, and it resets the diagnostic register, lighting all the LEDs.

Watchdog Reset. The Sun-3 architecture provides a watchdog circuit which generates a signal equivalent to power-on reset (POR) whenever the CPU halts with a double bus fault. The result of a watchdog reset is identical to a POR, as far as the CPU and the system is concerned.

CPU Reset. When the CPU executes a reset instruction, it resets all on-board and off-board I/O devices that offer an external reset function. No other devices are affected. Specifically, Control Space devices such as the system enable register and the diagnostic register are not affected by CPU Reset.

Sun Microsystems Inc CONFIDENTIAL 14 January 1985

# 7. CPU Interrupts

The devices defined in the Sun-3 architecture use autovectored interrupts, except for the SCC UARTs that use either vectored or autovectored interrupts, with vectored being the preferred implementation. Devices on the VMEbus use vectored interrupts. A list of the interrupt assignments is in the table below:

| Level | Device(s)                            |  |

|-------|--------------------------------------|--|

| 7     | Parity Error or Clock                |  |

| 6     | SCCs                                 |  |

| 5     | Clock .                              |  |

| 4     | Video .                              |  |

| 3     | Ethernet or System Enable Register 3 |  |

| 2     | System Enable Register 2             |  |

| 1     | System Enable Register 1             |  |

## 8. The Sun-3 Cache Architecture

## 8.1. The Sun-3 Cache: Its Structure and Operation

The Sun-3 cache architecture describes the cache structure for a whole class of systems, extending beyond systems with 68020 processors. All of the caches encompassed by this architecture have a common structure and common operation. In particular, they all are direct mapped caches (i.e., one way set associative). They vary only in the number of cache blocks and, of course the cache access timing (not an architectural parameter).

This cache architecture finds application in the Sirius system, the first Sun-3 workstation to incorporate a high speed local cache as a part of its memory hierarchy. Important architectural considerations result from the use of this cache. Its structure and operation are described in this appendix from this viewpoint.

The description below will generally apply to the entire class of Sun-3 caches. Examples unique to the Sirius system will be so identified.

### 8.1.1. The Sun-3 Cache: Overview

The Sun-3 cache is organized as a direct mapped virtual addressed cache containing 16 byte blocks (or lines). Its size is variable, from 1K blocks (16K bytes) for the Sirius system up to 8K blocks (128K bytes) for the largest allowable Sun-3 cache.

Data are organized as 8KB pages within 128KB contexts for all cache sizes. Sun-3 caches, like the MMU, support 8 virtual contexts with 28 bit virtual address spaces.

In the Sirius system, cache tags are addressed by A13:A4; in the largest allowable Sun-3 cache, tags are addressed by A16:A4. The cache tags include sufficient virtual address to define the 28 bit virtual address space, a 3 bit Context ID (CID) field, protection bits, and controls. (See below for a description of all tag bits.)

The Sun-3 cache is a Write Back cache: at any instant the cache may contain valid modified data that are not in the main memory. Modified data are only transferred to main memory upon block replacement or block flush.

All Sun-3 cache based systems are linked to memory over the 64 bit Sirius bus. ECC memory is used in all Sun-3 cache systems. Data are transfered between the cache and memory in block transfers of 128 bits, with two data transfers per memory cycle. The data path between the memory and the cache for the Sirius system is 64 bits wide. Data are stored in eight 2Kx8 static RAM's accessed by address bits A13:A3.

The Sun-3 cache may only contain data that can be obtained in units of 16 bytes over the Sirius bus. It does NOT have provision for data obtained through Programmed I/O accesses by the processor to I/O devices. (This data can only be accessed in units of 4 bytes or less.)

Since both System and User DVMA map through the MMU into main memory, the cache can contain DVMA data. In particular, it supports virtual I/O transfers (User DVMA) over the 32 bit VME bus. Note that for User DVMA transfers, the Context Identifier is obtained from VME address bits A30:A28. (See the Sun-3 User DVMA section for a complete description.)

## 8.1.2. Cache Tags

Sun-3 cache tags are listed below. The use of these tags in cache control is explained in the next section.

- Valid (1 bit): Self explanatory.

- Modified (1 bit): Indicates that the cache block has been modified by one (or more) Write cycles.

- Virtual Address field (up to 14 bits): Sufficient virtual address bits to define a 28 bit virtual address space. These bits are compared against the access virtual address for all read or write operations to the cache, and for some cache Control Space operations. For the 16K byte Sirius cache, the Virtual Address field is A27:A14; for the 128K byte Sun-3 cache, the VA field is A27:A17.

- Protection (2 bits): Write allowed and Supervisor access protection bits, identical to those

in the MMU. The use of the Protection bits is explained below under Definition of Cache

Protection.

- Context ID (CID) field (3 bits): compared against the CID register (or VME address bits A30:A28) for cache read/write operations and for some cache Control Space operations.

```

| D31 D30 D29 D28 D27 D26 D25 D24 D23 D22 D21 D20 D19 D18 D17 D16 | D31 Mod|Unused | Control Space operations | Val|Mod|Unused | Control Space operations

```

### 8.1.3. The Cache Hit and Protection

Contexts may contain both Supervisor and User data, as indicated by the Supervisor protection bit. Within the MMU, access to common Supervisor code from two separate contexts is through two separate Page Map Entry Groups (PMEG's). Within the cache, however, common Supervisor code must be recognized regardless of the context.

The Sun-3 cache architecture therefore REQUIRES that all Supervisor code and data must have identical address mapping across all contexts. For protection consistency, the Sun-3 cache architecture further REQUIRES that if a page is marked as having Supervisor access within one context, then that page must be marked as having Supervisor access for all contexts.

Having stated this requirement, the cache hit and protection may be defined. Note that the cache protection checking must be a simple extension of MMU protection checking. No differences in results (except performance) should be discernable whether a Sun-3 system is run with its cache enabled or disabled.

#### 8.1.4. Definition of a Cache Hit

The cache hit is defined as follows. The source for a cache request may be either a processor or DVMA device; in both cases, a full 28 bit virtual address (extended for DVMA, if necessary) is assumed. The source context is either the Context ID register or address bits A30:A28 for VME User DVMA. There are two requirements for a cache hit. First, the source address A27:A4 must match the cache virtual address tags plus the cache block address. For Sirius, the tags match A27:A14, and the cache block is addressed by A13:A4.

Second, either the source context must match the cache Context ID tags, or the cache Supervisor protection tag must be set. In the first case, the cache hit is within the same context, regardless of whether the cache request is a User or Supervisor request. In the second case, the cache hit definition allows a source request to access common Supervisor code within the cache, regardless of the source's context.

The concept of a cache hit has meaning for all read or write bus cycles to memory (Type 0 access). In addition, it also applies for the Block Copy (Read) and Block Copy (Write) Control Space operations.

#### 8.1.5. Definition of Cache Protection

The cache protection is defined as follows. First, no cache protection violation can result unless there is a cache hit. Second, if the source access is a User request, a protection violation results on a hit if either the cache block has a Supervisor protection tag, or if the source attempts to write into a cache block whose Write protection tag is reset. Notice, as a result, that a User request from one context which matches a Supervisor cache block in another context will terminate with a protection violation. Third, if the source access is a Supervisor request, a protection violation results on a hit only if the source attempts to write into a cache block whose Write protection tag is reset.

A protection violation terminates the bus cycle with a bus error, while setting the Protection Error bit in the Bus Error register (on CPU bus cycles). Protection checking in inhibited on all Control Space operations.

### 8.1.6. Enabling the Cache

The "Enable External Cache" bit, D4 of the System Enable register, determines whether the cache is enabled for Read and Write accesses. In Boot state, the cache is disabled. If disabled, all cache accesses "miss" the cache, no cache blocks are written back to memory, and memory data are directly read from or written to main memory. The Control Space operations for the cache, however, remain unaffected by the Enable bit.

## 8.1.7. Cache Access and Block Replacement

Whenever a normal Device space data access is initiated by either the processor or through DVMA, the cache is accessed if it is enabled. If a cache "hit" occurs, data are directly read from (or written to) the cache, assuming a valid protection check. If a cache "miss" occurs, then an I/O transfer, control register access, or main memory access is initiated, depending on the Page Map. If a main

14 January 1985

memory access is required, then the sequence of memory accesses that follow depend on the state of the cache block that is being replaced and whether the access is to a "Don't Cache" page.

If the access is to a "Don't Cache" page (see Cache Consistency, below) then data are directly read from or written to main memory without disturbing the cache. All Sun-3 cache systems operate with ECC memory, and the check bits for ECC are defined over 64 bits. So a "Don't Cache" write to memory (four bytes or less) requires a memory read before check bits can be generated on the write data. On Sirius, the 64 bits of read data are merged with the new write data on the memory board.

The remainder of this cache access description assumes that the data may be cached. The description is for a cache access on the Sirius system; some details may change for other Sun-3 cache implementations.

Upon detecting the cache miss, a memory Read for the new cache block is begun, regardless if the cache access were a Read or Write access. (This memory Read is aborted if the MMU translates the address to some non-memory device, if a protection check occurs, or if the access is a write to a "Don't Cache" page.) If the cache block being replaced has been modified, the virtual address of this block is translated through the MMU and compared with the real address for the memory Read request, which is held in the Sirius bus address register. For the Sirius system, only translated address bits A27:A13 are compared.

If these real addresses match, then the data from memory are stale; the cache contains updated data for this block. So when the block from memory returns, it must be discarded, while the cache tags are still updated to show the new virtual address and new protection. (See also the discussion on cache data consistency, below.)

Whether the real addresses match or not, the old modified block data from the cache, the translated address for this block, and controls are loaded into Sirius Write Data buffers before the memory access for the Read data completes. Eventually a block Write to memory returns this data to memory.

If the cache block being replaced has not been modified, the cache controls simply await the return of the Read data from memory. The Read data from memory are always returned with the missing data included in the first 64 bit transfer. The type of cache access being made determines how the data are handled when the memory data are returned.

On a Read access, if the first 64 bit transfer is successful (i.e., no uncorrectable errors), the memory data are simultaneously passed to the processor and to the cache data RAM's to be written as new data. If the second 64 bit data transfer from memory is successful, then these data are written into the cache and the cache tags are validated. If either transfer is unsuccessful, the cache block is left invalid and the uncorrectable error is reported to the processor as an interrupt. (See also the appendix on ECC Memory.)

On a Write access, if the first 64 bit transfer is successful, the processor's write data are merged with the data from memory and written into the cache. Following a successful second 64 bit transfer from memory, the cache data update is completed and the cache tags are validated. Both the cache Modified tag and the MMU Modified bit are set active. If either transfer from memory contains an uncorrectable error, then the cache block remains invalid and the processor's Write data are lost. This error is reported to the processor as an interrupt.