# 8-Channel Programmable Interface

# Manual

Copyright © June, 1983 Sigma Information Systems Anaheim, CA

## Contents

#### SECTION 1 - GENERAL INFORMATION

| 1.1   | INTRODUCTION<br>GENERAL DESCRIPTION<br>FEATURES | 1<br>2<br>2 |

|-------|-------------------------------------------------|-------------|

| -     | SPECIFICATIONS                                  | 3           |

| SECTI | ON 2 - INSTALLATION                             |             |

| 2.1   | UNPACKING AND INSPECTION                        | 5           |

| 2.2   | ADDRESS SELECTION                               | 7           |

| 2.3   | VECTOR SWITCH SELECTION                         | 8           |

|       | BAUD RATE SELECTION                             | 9           |

| 2.5   | LINE PARAMETERS SWITCH SELECTION                | 10          |

| -     | CONSOLE SELECTION                               | 10          |

| 2.7   | BREAK RESPONSE                                  | 11          |

| 2.8   | CABLING                                         | 11          |

| 2.9   | MODULE INSTALLATION                             | 12          |

|       | RACKMOUNT PANEL (OPTION)                        | 12          |

#### SECTION 3 - PROGRAMMING CONSIDERATIONS

| 3.1   | INTRODU | JCTION                          | 13   |

|-------|---------|---------------------------------|------|

| 3.2   | DEVICE  | ADDRESS FORMAT                  | 15   |

| 3.3   | VECTOR  | INTERRUPT FORMAT                | 16   |

| 3.4   | WORD FO | DRMATS                          | 17   |

|       | 3.3.1   | Receive Control/Status          |      |

|       |         | Register (RCSR)                 | 17   |

|       | 3.4.2   | Receive Buffer (RBUF)           | 18   |

|       | 3.4.3   | Transmit Control/Status         |      |

|       |         | Register (XCSR)                 | 19   |

|       | 3.4.4   | Transmit Buffer (XBUF)          | 19   |

|       |         |                                 |      |

|       |         |                                 |      |

| APPEI | NDIX A  | BUS SIGNALS AND PIN ASSIGNMENTS | A-11 |

## Figures

| 2-1 | COMPONENT LOCATIONS | SHOWING | FACTORY |    |

|-----|---------------------|---------|---------|----|

|     | CONFIGURATIONS      |         |         | 6  |

| 2-2 | RACKMOUNT CONNECTOR | PANEL   |         | 12 |

|     |                     |         |         |    |

## Tables

| 2-1 | EXAMPLE ADDRESS SELECTION               | 7  |

|-----|-----------------------------------------|----|

| 2-2 | VECTOR SELECTION EXAMPLES               | 8  |

| 2-3 | BAUD RATE SELECTION                     | 9  |

| 2-4 | LINE PARAMETERS SWITCH SELECTION        | 10 |

| 2-5 | CONSOLE ENABLE                          | 10 |

| 2-6 | BREAK RESPONSE                          | 11 |

| 2-7 | CABLE PIN ASSIGNMENTS                   | 11 |

| 3-1 | STANDARD ADDRESS AND VECTOR ASSIGNMENTS | 14 |

## Section 1 - General Description

#### 1.1 INTRODUCTION

This manual supplies the information needed to install and operate the SCD-DLV11J/8 8-channel serial line interface module manufactured by Sigma Information Systems, Anaheim, California. The material is arranged into the following sections:

SECTION 1 - GENERAL INFORMATION. This section contains a general description of the interface module, along with features. Specifications are included.

SECTION 2 - INSTALLATION. This section contains the switch selection and associated register formats for device and vector address assignments, baud rates and line parameters. Cabling and backplane installation is included.

SECTION 3 - PROGRAMMING CONSIDERATIONS. This section contains the address/vector formats and register formats for transmit and receive control/status and buffer registers.

APPENDIX A - The appendix lists the bus signals and their associated pin assignments.

#### 1.2 GENERAL DESCRIPTION

The SCD-DLV11J/8 is a dual-wide asynchronous interface between the LSI-11 bus and up to eight standard serial I/O devices. It is software compatible with DEC\* operating systems and diagnostics designed for the DLV11J. It plugs directly into any dual Q bus\* slot.

Sigms's SCD-DLV11J/8 has switch selectable address (160000 to 177776) and vector (000 to 776) assignments. Once the initial address and vector are assigned, all eight channels are contiguous except the console channel which, if selected, resides at 177560 with vector at 60.

All channels share a programmable baud rate with a switch selectable default value. Baud rates range from 50 to 19.2K buad. The SCD-DLV11J/8 supports only RS-232C devices with all channels sharing switch selectable line parameters.

The interface module includes two 12-foot, 4-channel cables, each with four DB25P connectors. An optional rackmount panel provides convenient mounting for the eight DB25P connectors.

#### 1.3 FEATURES

The following are some of the features of the SCD-DLV11J/8P.

- Eight asynchronous serial lines can be supported on one dual-wide module.

- The module is plug compatible with LSI-11 backplanes and plugs directly into any Q bus slot without backplane modification.

- The interface is software compatible with operating systems and diagnostics designed for the DLV11J.

- Baud rate is programmable with a switch selectable default value.

- Device address and vector assignments are switch selectable.

- Line parameters are switch selectable.

\*DEC and Q bus are registered trademarks of Digital Equipment Corporation.

#### 1.4 SPECIFICATIONS

| Power Requirements:                                   | +5VDC AT 2.0A<br>12VDC at 0.2A                                                                                                                                                                    |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Address:                                       | Switch selectable 160000-177776<br>(Console = 177560)                                                                                                                                             |

| Vector<br>Baud Rate:                                  | Switch selectable 000-776<br>(console = 60)<br>Programmable per channel<br>50, 75, 110, 134.5, 150, 200, 300,<br>600, 1200, 1800, 3400, 3600, 4800<br>7200, 9600 and 19.2K                        |

| Line Parameters:<br>Data Bit:<br>Parity:<br>Stop Bit: | Switch selectable. Shared by<br>all channels<br>7 or 8<br>Odd, even or none<br>1 or 2                                                                                                             |

| Operation:                                            | Full duplex                                                                                                                                                                                       |

| Interface Type:                                       | RS-232C                                                                                                                                                                                           |

| Bus Load:                                             | One DC load                                                                                                                                                                                       |

| Cables:                                               | Includes two 12-ft, 4-channel cables,<br>each with four DB25P connectors.<br>Terminals require null modem cables<br>with DB25S connectors to SCD-DLV11J/8P<br>and associated terminal connectors. |

| Optional Panel:                                       | Mounts the eight DB25P connectors for<br>convenient rear rackmount cabling to<br>RS-232C devices.                                                                                                 |

| Installation:                                         | Plugs directly into any standard Q bus<br>slot that provides continuous BIAK1 and<br>BIAKO lines.                                                                                                 |

| Dimensions:                                           | Single dual-wide module: 5.2"W x 8.9"H<br>(13.2cmW x 22.8cmH)                                                                                                                                     |

| Temperature<br>Operating:<br>Storage:                 | 0°C to 50°C<br>-40°C to 85°C                                                                                                                                                                      |

| Humidity:                                             | 10% to 90% noncondensing                                                                                                                                                                          |

June 10, 1983 Page 4

## Section 2 – Installation

#### 2.1 UNPACKING AND INSPECTION

The SCD-DLV11J/8P is shipped in a special packing carton designed to keep the module from vibrating and to give it maximum protection during shipment. The packing carton should be retained in case the unit requires reshipment.

Unpack the SCD-DLV11J/8P and visually inspect it for any damage that may have occurred during shipment. If any damage has occurred notify Sigma Information Systems immediately.

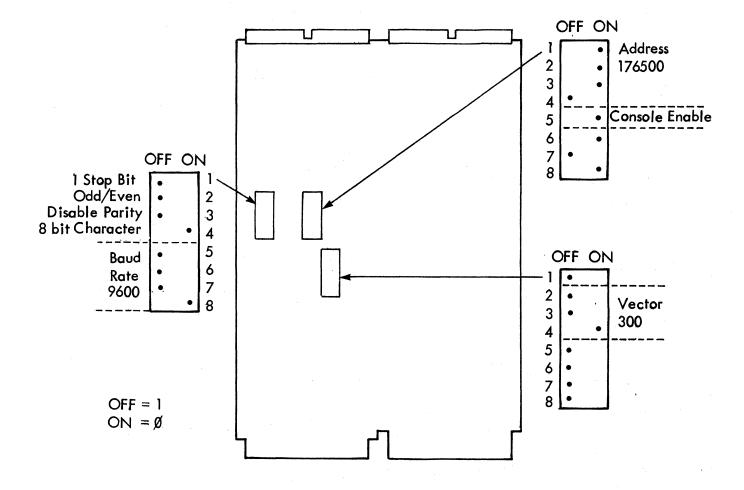

Verify that the factory set switches are set correctly according to Figure 2-1.

June 10, 1983 Page 6

FIGURE 2-1: COMPONENT LOCATIONS SHOWING FACTORY CONFIGURATIONS

June 9, 1983 Page 7

#### 2.2 ADDRESS SELECTION

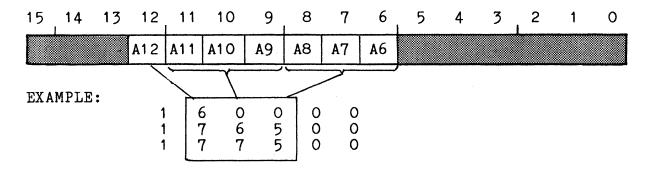

The SCD-DLV11J/8P has switch selectable device addressing in the range of 160000 to 177776 (octal). Once an initial address is assigned, the remaining seven channels are contiguous except the console which, if selected, resides at 177560 as channel 7. Refer to Section 3.1 for a description of the device address and vector interrupt assignments. The initial address format is shown below.

#### Significant address bits set by SW3

The initial address is determined with significant address bits A6-A12 set by switch SW3. Some examples follow in Table 2-1.

| ADDRESS       |                   |                | A12         | — AI<br>A1 1 | DRES         |             |             | A7          | A6.         |

|---------------|-------------------|----------------|-------------|--------------|--------------|-------------|-------------|-------------|-------------|

| SET BY<br>SW3 |                   |                | 1           | SV<br>2      | 13-P(<br>  3 | DSIT:<br>4  | IONS<br>8   | 7           | 6           |

| 1<br>*1<br>1  | 764<br>765<br>766 | 00<br>00<br>00 | 1<br>1<br>1 | 1<br>1<br>1  | 1<br>1<br>1  | 0<br>0<br>0 | 1<br>1<br>1 | 0<br>0<br>1 | 0<br>1<br>0 |

\*Factory preset

O = ON1 = OFF

#### TABLE 2-1: EXAMPLE ADDRESS SELECTION

#### 2.3 VECTOR SWITCH SELECTION

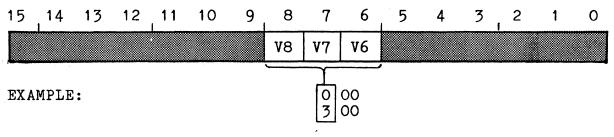

The SCD-DLV11J/8P has switch selectable vector assignments in the range of 000-776 (octal). Once the initial vector is assigned the remaining seven vectors are contiguous except the console which, if assigned, resides at 60 as channel 7. The initial vector format is shown below.

Significant vector bits set by SW1

The initial vector is determined by significant vector bits V6-V8 set by switch SW1. Some examples follow in Table 2-2.

| VECTOR        | VECT | OR BI      | TS        |

|---------------|------|------------|-----------|

|               | V8   | V7         | V6        |

| SET BY        |      | OSITI      | ons —     |

| SW1           |      | 3          | 2         |

| 2 00          | 0    | 1          | 0         |

| *3 00         | 0    | 1          | 1         |

| 6 00          | 1    | 1          | 0         |

| *Factory pres | ent  | 0 =<br>1 = | ON<br>OFF |

TABLE 2-2: VECTOR SELECTION EXAMPLES

#### 2.4 BAUD RATE SELECTION

All channels share the same programmable baud rate. The baud rate format is shown below.

| 15  | 14  | 13  | . 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|-----|-----|------|----|----|---|---|---|---|---|---|---|---|---|---|

| BR3 | BR2 | BR1 | BRO  |    |    |   |   |   |   |   |   |   |   |   |   |

where BRO-BR3 define programmable baud rates and SW2 defines default switch selectable baud rates as shown in Table 2-3.

| BAUD<br>RATE                                                                                                           | 15<br>5                                                       | -XCSR<br> 14<br> W2 P0<br> 6                                            | BITS<br><u>  13</u><br>SITIO<br>  7                                          | 12                                                                 |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 50<br>75<br>110<br>134.5<br>150<br>200<br>300<br>600<br>1200<br>1800<br>2400<br>3600<br>4800<br>7200<br>9600*<br>19.2K | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 |

\*Factory present O = ON

1 = OFF

TABLE 2-3: BAUD RATE SELECTION

#### 2.5 LINE PARAMETERS SWITCH SELECTION

All eight channels share the same line parameters. The start bit is 1, but data bit, parity and stop bits can be assigned via switch SW2 as shown in Table 2-4.

| LINE<br>PARAMETER   | SW2<br>POSITION | DEFINITION                                                                |

|---------------------|-----------------|---------------------------------------------------------------------------|

| CHARACTER<br>LENGTH | 4               | 0 = 7 BITS, *1 = 8 BITS                                                   |

| PARITY              | 3<br>2          | *O = DISABLE PARITY, 1 = ENABLE PARITY<br>O = ODD PARITY, 1 = EVEN PARITY |

| STOP BITS           | 1               | *O = 1 STOP BIT, 1 = 2 STOP BITS                                          |

\*Factory preset

$\begin{array}{rcl}

O &=& ON \\

1 &=& OFF

\end{array}$

#### TABLE 2-4: LINE PARAMETERS SWITCH SELECTION

#### 2.6 CONSOLE SELECTION

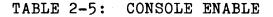

The console, if selected, is assigned channel 7. The SCD-DLV11J/8P is shipped with the console enabled. To disable the console set switch SW3-5 as shown in Table 2-5.

| SW3-5   | CONSOLE        | STATUS |

|---------|----------------|--------|

| 0<br>*1 | DISAI<br>ENABI |        |

\*Factory preset O = ON1 = OFF

#### 2.7 BREAK RESPONSE

Channel 7 can be configured to either bootstrap, halt (console emulation mode), or have no response to a receive break condition. A bootstrap operation upon a receive break condition causes the CPU to execute the bootstrap program strating at the memory location defined by the power-up mode jumpers of the CPU. A halt operation unpon a receive break condition causes the processor to halt and the console octal debugging technique (ODT) microcode to be invoked. Configurations are shown in Table 2-6.

| BREAK RESPONSE | E1-E2     | E1-E3      |

|----------------|-----------|------------|

| None<br>Boot   | OUT<br>IN | OUT<br>OUT |

| Halt           | OUT       | IN         |

TABLE 2-6: BREAK CONFIGURATIONS

#### 2.8 CABLING

The SCD-DLV11J/8P has two 40-pin connectors and is supplied with two cables, each terminating in four DB25P connectors. The 40-pin connectors and associated 25-pin terminating connector pin assignments are defined in Table 2-6.

| SIGNAL           | DESCRIPTION                                                                               | 25-PIN<br>DB25P |           |    | ONNE<br>NUMB<br>2<br>6 |   |

|------------------|-------------------------------------------------------------------------------------------|-----------------|-----------|----|------------------------|---|

| Transmit<br>Data | Data transmitted from<br>SCD-DLV11J/8 to terminal                                         | 3               | 33        | 23 | 13                     | 3 |

| Receive<br>Data  | Data received by SCD-DLV11J/8P<br>from terminal                                           | 2               | 38        | 28 | 18                     | 8 |

| Clear<br>to Send | Signal sent by device to SCD-<br>DLV11J/8 to indicate readi-<br>ness for transmitted data | 5               | 34        | 24 | 14                     | 4 |

| Ground           | Signal Ground                                                                             | 1,7             | <u>39</u> | 25 | 12                     | 5 |

| Ground           | Protective Ground                                                                         | 1,7             | 32        | 22 | 15                     | 2 |

TABLE 2-7: CABLE PIN ASSIGNMENTS

June 9, 1983 Page 12

The SCD-DLV11J/8P provides a Clear to Send input which can be driven by the attached serial line device to cause the SCD-DLV11J/8P channel to stop transmitting. The common use for this feature is with a printer that does not support XON-XOFF, but does provide a buffer full signal. This buffer status signal can be used to assert the CTS signal and effectively control transmission of data to the printer from the SCD-DLV11J/8P.

Cabling to terminals requires null modem cables with DB25S sockets between the SCD-DLV11J/8P connectors and associated terminal connectors.

#### 2.9 MODULE INSTALLATION

The SCD-DLV11J/8P plugs directly into any Q bus slot, providing BIAK1 and BIAKO lines from the interface to the CPU are continuous. Bus signals and associated pin assignments are listed in Appendix A.

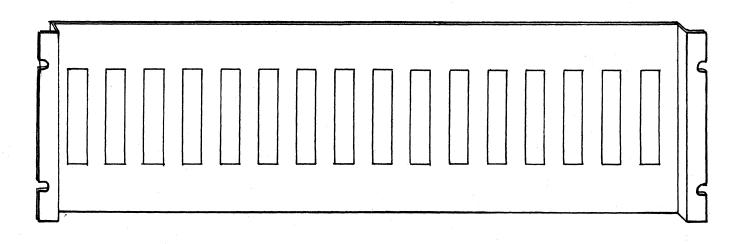

#### 2.10 RACKMOUNT PANEL (OPTION)

An optional rackmount panel provides convenient mounting for the eight DB25P connectors. The panel is illustrated in Figure 2-2.

#### FIGURE 2-2: RACKMOUNT CONNECTOR PANEL

## Section 3 - Programming Considerations

#### 3.1 INTRODUCTION

The SCD-DLV11J/8P is controlled by four device registers per channel for a total of 32 device registers. The four device registers provided for each of the eight channels are:

| RCSR | Receive Control/Status Registers |

|------|----------------------------------|

| RBUF | Receive Buffer                   |

| XCSR | Transmit Control/Status Register |

| XBUF | Transmit Buffer                  |

With the exception of the console channel, the device registers are assigned in a contiguous block by setting the address of channel O. If the SCD-DLV11J/8P is used as the console device, channel 7 is assigned the console address and vector. If the SCD-DLV11J/8P is not used as the console, channel 7 is assigned as the last contiguous address set. Table 3-1 illustrates an initial address and vector assignment with contiguous locations.

## June 10, 1983 Page 14

| [         | ADDRESS           | REGISTER     | VECTOR   | CHANNEL   |  |

|-----------|-------------------|--------------|----------|-----------|--|

|           | 176500<br>176502  | RCSR<br>RBUF | 300      | 0         |  |

|           | 176504            | XCSR         | 304      | 0         |  |

|           | 176506            | XBUF         |          |           |  |

|           | 176510<br>176512  | RCSR<br>RBUF | 310      | 1         |  |

|           | 176514<br>176516  | XCSR<br>XBUF | 314      | 1         |  |

|           | 176520            | RCSR         | 320      | 2         |  |

|           | 176522<br>176524  | RBUF<br>XCSR | 324      | 2         |  |

|           | 176526            | XBUF         | 5-1      | -         |  |

|           | 176530<br>176532  | RCSR<br>RBUF | 330      | 3         |  |

|           | 176534            | XCSR         | 334      | 3         |  |

|           | 176536            | XBUF         |          |           |  |

|           | 176540<br>176542  | RCSR<br>RBUF | 340      | 4         |  |

|           | 176544<br>176546  | XCSR<br>XBUF | 344      | 4         |  |

|           | 176550            | RCSR         | 350      | 5         |  |

|           | 176552<br>176554  | RBUF<br>XCSR | 354      | 5         |  |

|           | 176556            | XBUF         | <u> </u> |           |  |

|           | 176560            | RCSR         | 360      | 6         |  |

| -         | 176562<br>176564  | RBUF<br>XCSR | 364      | 6         |  |

|           | 176566            | XBUF         |          |           |  |

|           | 176570*<br>176572 | RCSR<br>RBUF | 370      | 7         |  |

|           | 176574<br>176576  | XCSR<br>XBUF | 374      | 7         |  |

| *<br>T-P- | the console i     |              | + nogido | L ot ohou |  |

|           | the last fou      |              |          |           |  |

| -         | 177560            | RCSR         | 60       | 7         |  |

|           | 177562            | RBUF<br>XCSR | 64       | 7         |  |

|           | 177566            | XBUF         |          |           |  |

TABLE 3-1: STANDARD ADDRESS AND VECTOR ASSIGNMENTS

## 3.2 DEVICE ADDRESS FORMAT

|    | _    |                                               |                                                                       |                                               |     |     |     |    |    |    |    |        |       |   |   |   |

|----|------|-----------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------|-----|-----|-----|----|----|----|----|--------|-------|---|---|---|

| 17 | 16   | 15                                            | 14                                                                    | 13                                            | 12  | 11  | 10  | 9  | 8  | 7  | 6  | 5      | <br>3 | 2 | 1 | 0 |

| 1  | 1    | 1                                             | 1                                                                     | 1                                             | A12 | A11 | A10 | A9 | Å8 | A7 | A6 |        |       |   |   |   |

|    |      | cted<br>ial                                   | Addr                                                                  |                                               |     |     |     |    |    |    |    |        |       | · |   |   |

|    | (See | Sec                                           | tion                                                                  | 2.2                                           | ?)  |     |     |    |    |    |    |        |       |   |   |   |

|    | Chan | 000<br>001<br>010<br>011<br>100<br>101<br>110 | (Dev:<br>= CI<br>= CI<br>= CI<br>= CI<br>= CI<br>= CI<br>= CI<br>= CI | H 0<br>H 1<br>H 2<br>H 3<br>H 4<br>H 5<br>H 6 | Sel | ect |     |    |    |    |    |        |       |   |   |   |

|    | Regi | 00<br>01<br>10                                | Sele<br>= RCS<br>= RBN<br>= XCS<br>= XBN                              | SR<br>JF<br>SR                                |     |     |     |    |    |    |    |        | <br>  |   |   |   |

|    | Byte | Poi                                           | nter                                                                  |                                               |     |     |     |    |    |    |    | ****** | <br>  |   |   |   |

The address configurations are listed in Table 3-2.

## 3.3 VECTOR INTERRUPT FORMAT

The interrupt vector format is shown below.

| 17 | 16           | 15                                     | 14                                            | 13                                     | 12           | 11          | 10           | 9  | 8                                     | 7  | 6          | 5      | 4 | 3 | 2                               | 1 | 0 |

|----|--------------|----------------------------------------|-----------------------------------------------|----------------------------------------|--------------|-------------|--------------|----|---------------------------------------|----|------------|--------|---|---|---------------------------------|---|---|

|    |              |                                        |                                               |                                        |              |             |              |    | <b>V</b> 8                            | ٧7 | <b>V</b> 6 |        |   |   |                                 |   |   |

|    | Init<br>(See |                                        |                                               |                                        | )            | -           |              |    | · · · · · · · · · · · · · · · · · · · |    |            | •••••• |   |   | <u></u>                         |   |   |

|    | Chan         | nel                                    | Requ                                          | esti                                   | ng I         | nter        | rupt         |    |                                       |    |            | ·      |   |   |                                 |   |   |

|    |              | 001<br>010<br>011<br>100<br>101<br>110 | = C<br>= C<br>= C<br>= C<br>= C<br>= C<br>= C | H 1<br>H 2<br>H 3<br>H 4<br>H 5<br>H 6 |              |             |              |    |                                       |    |            |        |   |   |                                 |   |   |

|    | Inte         | 0 =                                    | Rec                                           | eive:<br>nsmi                          | r In<br>tter | terr<br>Int | upt<br>errup | ot | -                                     |    | 919        |        |   |   | ni ku ya anka na ku ku ku ku ku |   |   |

All bits not used are read as O.

#### 3.4 WORD FORMATS

The four word formats, one for each device register within a channel, are described in the following sections.

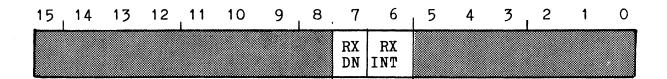

3.4.1 Receive Control/Status Register (RCSR)

- RX DN RECEIVER DONE. Set when an entire character has been received and is ready for input to the CPU. Cleared when RBUF is read or BINIT L signal goes true. If RX INT (bit 6) is set, setting RX DN starts an interrupt sequence. Read only.

- RX INT RECEIVER INTERRUPT ENABLE. Set under program control to generate a receiver interrupt request (when a character is ready for input to the processor signified by bit 7 being set). Cleared under program control or by BINIT signal. Read/write.

All bits not used are read as O.

June 10, 1983 Page 18

#### 3.4.2 Receiver Buffer (RBUF)

| 15 14             | 13         | 12         | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4     | 3    | 2 | 1 | 0 |

|-------------------|------------|------------|----|----|---|---|---|---|---|-------|------|---|---|---|

| CH OVR<br>ERR RUN | FRM<br>ERR | PAR<br>ERR |    |    |   |   |   |   | D | ATA 1 | BITS |   |   |   |

- CH ERR CHANNEL ERROR STATUS. Logical OR of bits 14, 13, and 12. Read only.

- OVR OVERRUN ERROR. When set, indicates that the reading RUN of the previously received character was not completed (receiver done not cleared) prior to receiving a new character. Cleared by BINIT signal. Read only.

NOTE: When "back-to-back" characters are received, one full character time is allowed from the time instant receiver done (bit 7) is set to the occurrence of an overrun error.

- FRM FRAMING ERROR. When set, indicates that the character ERR read had no valid stop bit. Cleared by BINIT signal. Read only.

- PAR PARITY ERROR. When set, indicates that the parity ERR received does not agree with the expected parity. This bit is always O if no-parity operation is configured for the channel. Read only.

NOTE: Error bits remain valid until the next character is received, at which time the error bits are updated.

DATA DATA BITS. Contains seven or eight data bits in a BITS right-justified format. Bit 7 = 0 when 7 data bits are enabled. Read only.

All bits not used are read as O.

-• 5

3.4.3 Transmit Control/Status Register (XCSR)

| 15         | 14  | 13                      |                                  | 11                               | 10                      | 91                              | 8 7                                                  | 6                          | <u>  5</u>                | 4                      | 3 .                   | 2                    | 1              | 0           |

|------------|-----|-------------------------|----------------------------------|----------------------------------|-------------------------|---------------------------------|------------------------------------------------------|----------------------------|---------------------------|------------------------|-----------------------|----------------------|----------------|-------------|

| BR3        | BR2 | BR1                     | BRO                              | BR<br>ENB                        |                         |                                 | 9665555555                                           | XMT<br>INT                 |                           |                        |                       |                      |                | X MT<br>BRK |

|            | _   |                         |                                  |                                  |                         |                                 |                                                      | -                          |                           |                        |                       |                      |                |             |

| BR3<br>BR0 |     | cho                     | oose                             | a ba                             |                         | te f                            | re sei<br>rom 50                                     |                            |                           |                        |                       |                      |                |             |

| BR<br>ENI  |     | se                      |                                  |                                  |                         |                                 | re ENA<br>te ind                                     |                            |                           |                        |                       |                      |                |             |

| XM1<br>RD3 |     | ano<br>INI              | other                            | r cha<br>lu <mark>r</mark> in    | racte                   | r fo                            | when<br>r trar<br>p or d                             | smiss                      | sion.                     | Īť                     | is a                  | lso                  | $\mathtt{set}$ | Ъy          |

| XM1<br>IN1 |     | who<br>red<br>fo:       | en it<br>quest<br>r tra          | t is<br>t whe<br>ansmi           | desir<br>n tra<br>ssion | red to<br>insmit                | NABLE.<br>o gene<br>tter i<br>leared<br>struct       | erate<br>.s rea<br>l unde  | a tra<br>idy to<br>er pro | ansmi<br>acc<br>ogran  | tter<br>ept<br>con    | 'int<br>a ch         | erri<br>arad   | upt<br>cter |

| XM1<br>BRF |     | Who<br>Hov<br>ope<br>se | en se<br>weven<br>erate<br>t, no | et, a<br>r, tr<br>e, al<br>ormal | cont<br>ansmi<br>lowin  | inuo<br>t don<br>g so:<br>acte: | or res<br>us spa<br>ne and<br>ftware<br>r trar<br>e. | ice le<br>l tran<br>e timi | evel i<br>smit<br>ng of   | ls tr<br>inte<br>f bre | ansm<br>errup<br>eak. | itte<br>ot ca<br>Whe | d.<br>.n s     | ot          |

| A1)        | bi  | ts no                   | ot us                            | sed a                            | re re                   | ad a                            | s 0.                                                 |                            |                           |                        |                       |                      |                |             |

| 3.4        | 1.4 | Tra                     | ansmi                            | it Bu                            | ffer                    | (XBU                            | <u>F)</u>                                            |                            |                           |                        |                       |                      |                |             |

| 1 5        | 1 4 | 17                      | 10                               | 4 4                              | 10                      | 0                               | 0 5                                                  | c c                        | c                         | 4                      | 7                     | 2                    | 4              | 0           |

| 15 | 14 | 13 | 12 | , 11 | 10 | 9 | , 8 | 7 | 6 | 5 | 4    | 3    | 2 | 1 | 0 |

|----|----|----|----|------|----|---|-----|---|---|---|------|------|---|---|---|

|    |    |    |    |      |    |   |     |   |   | ] | DATA | BITS | 3 |   |   |

Bits 0-7 contain the seven or eight right-justified data bits. Loaded under program control for serial transmission. Bits not used are read as 0.

|     | CONNECTOR A | CON | INECTOR B   |

|-----|-------------|-----|-------------|

| PIN | SIGNAL NAME | PIN | SIGNAL NAME |

| AAl | Not Used    | BAl | врсок н     |

| AB1 | Not Used    | BB1 | Not Used    |

| AC1 | Not Used    | BC1 | Not Used    |

| AD1 | Not Used    | BD1 | Not Used    |

| AE1 | Not Used    | BEl | Not Used    |

| AF1 | Not Used    | BF1 | Not Used    |

| AH1 | Not Used    | BH1 | Not Used    |

| AJ1 | GND         | BJ1 | GND         |

| AK1 | Not Used    | BK1 | Not Used    |

| AL1 | Not Used    | BL1 | Not Used    |

| AM1 | GND         | BM1 | GND         |

| AN1 | Not Used    | BN1 | Not Used    |

| AP1 | BHALH       | BP1 | Not Used    |

| AR1 | Not Used    | BR1 | Not Used    |

| AS1 | Not Used    | BS1 | Not Used    |

| AT1 | GND         | BT1 | GND         |

| AU1 | Not Used    | BUl | Not Used    |

| AV1 | Not Used    | BV1 | +5VDC       |

| AA2 | +5VDC       | BA2 | +5VDC       |

| AB2 | Not Used    | BB2 | Not Used    |

| AC2 | GND         | BC2 | GND         |

| AD2 | +12VDC      | BD2 | Not Used    |

| AE2 | BDOUT L     | BE2 | BDAL2 L     |

| AF2 | BRPLY L     | BF2 | BDAL3 L     |

| AH2 | BDIN L      | BH2 | BDAL4 L     |

| AJ2 | BSYNC L     | BJ2 | BDAL5 L     |

| AK2 | Not Used    | BK2 | BDAL6 L     |

| AL2 | BIRQL       | BL2 | BDAL7 L     |

| AM2 | BIAKI L     | BM2 | BDAL8 L     |

| AN2 | BIAKO L     | BN2 | BDAL9 L     |

| AP2 | BBS7 L      | BP2 | BDAL10 L    |

| AR2 | BDMGI L     | BR2 | BDAL11 L    |

| AS2 | BDMGO L     | BS2 | BDAL12 L    |

| AT2 | BINIT L     | BT2 | BDAL13 L    |

| AU2 | BDALO L     | BU2 | BDAL14 L    |

| AV2 | BDALI L     | BV2 | BDAL15 L    |

#### BUS SIGNALS AND PINS ASSIGNMENTS