# DATA SET CONTROLLER MODELS 7601,7602,7603

XEROX

701 So. Aviation Blvd., El Segundo, Calif. 90245, 213 679-4511

# Effective Pages

| LIST OF EFFECTIVE PAGES |

|-------------------------|

|-------------------------|

# Total number of pages is 84, as follows:

| Page | No. |

|------|-----|

|------|-----|

#### Issue

Page No.

Issue

| Title         | Original |

|---------------|----------|

| A             | Original |

| i thru iv     | Original |

| 1–1 thru 1–6  |          |

| 2-1 thru 2-12 | Original |

| 3–1 thru 3–44 | Original |

| 4-1 thru 4-16 | Original |

### TABLE OF CONTENTS

| Section | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I       | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | 1-1 Introduction   1-2 List of Related Publications                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 - 1<br>1 - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 1-3 Physical Description   1-4 Functional Description   1-5 Specifications and Leading Particulars                                                                                                                                                                                                                                                                                                                                                                                 | 1-1<br>1-1<br>1-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| II      | OPERATION AND PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | 2-1Introduction2-2Function Indicators2-3SIO, HIO, and TIO Indicators2-4TDV Indicator.2-5AIO Indicator.2-6ASC Indicator.2-7Output Orders2-8Write Order2-9Dial Order2-10Read Order2-11Enable Ring Detect Order.2-12Disconnect Call Order2-13Disconnect Call Order2-14Generate Long Space Order.2-15Input Orders2-16Terminal Order2-17Format Units2-18Asynchronous Units2-19Synchronous Units                                                                                         | 2-1<br>2-1<br>2-1<br>2-4<br>2-4<br>2-4<br>2-4<br>2-4<br>2-6<br>2-6<br>2-6<br>2-6<br>2-6<br>2-6<br>2-6<br>2-6<br>2-6<br>2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| III     | PRINCIPLES OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | 3-1 Introduction .   3-2 General Principles .   3-3 Detailed Principles .   3-4 Function Indicator Acknowledgment .   3-5 SIO .   3-6 TIO or TDV .   3-7 HIO .   3-8 AIO .   3-9 States and State Flow .   3-10 Even Channel States .   3-11 Not Busy State .   3-12 Order Output State .   3-13 Input Wait State .   3-14 Read Cycle State .   3-15 Data Input State .   3-16 Order Input State .   3-17 Odd Channel States .   3-18 Not Busy State .   3-19 Order Output State . | 3-1<br>3-2<br>3-3<br>3-3<br>3-10<br>3-14<br>3-14<br>3-14<br>3-14<br>3-14<br>3-14<br>3-14<br>3-14<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-16<br>3-19<br>3-19 |

i

### Contents

### 901179

# TABLE OF CONTENTS (Cont.)

Section

IV

# Title

Page

| 3-21  | Data Output State                                      | 3-19 |

|-------|--------------------------------------------------------|------|

| 3-22  | Dial Cycle State · · · · · · · · · · · · · · · · · · · | 3-19 |

| 3-23  | Write Cycle State                                      | 3-19 |

| 3-24  | Order Input State                                      | 3-19 |

| 3-25  | Service Cycle                                          | 3-20 |

| 3-26  | Service Cycle States                                   | 3–20 |

| 3-27  | Service Cycle Timing                                   | 3–20 |

| 3-28  | Read Order Timing Sequence                             | 3-23 |

| 3-29  | Full-Duplex Versus Half-Duplex Read Order Timing       | 3-23 |

| 3-30  | Asynchronous Read Order Timing                         | 3-23 |

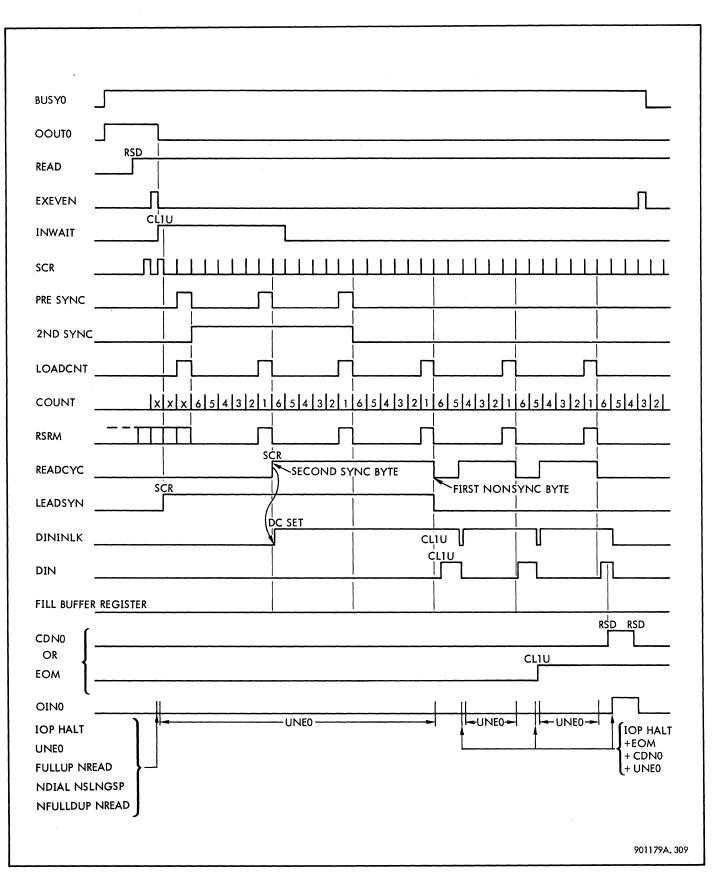

| 3-31  | Synchronous Read Order Timing                          | 3-27 |

| 3-32  | Write Order Timing Sequence                            | 3-30 |

| 3-33  | Full-Duplex Versus Half-Duplex Write Order Timing      | 3–30 |

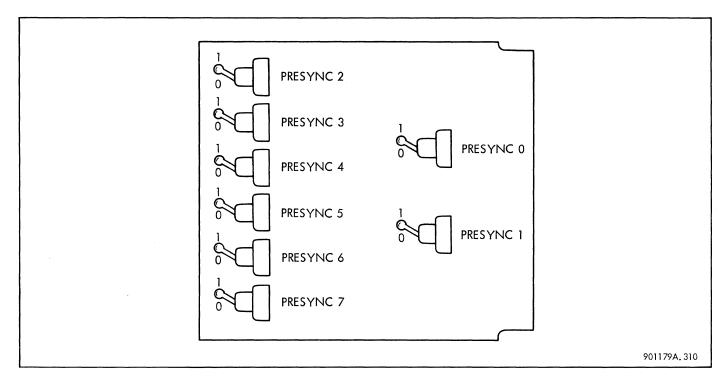

| 3-34  | Asynchronous Write Order Timing                        | 3-31 |

| 3-35  | Synchronous Timing                                     | 3-34 |

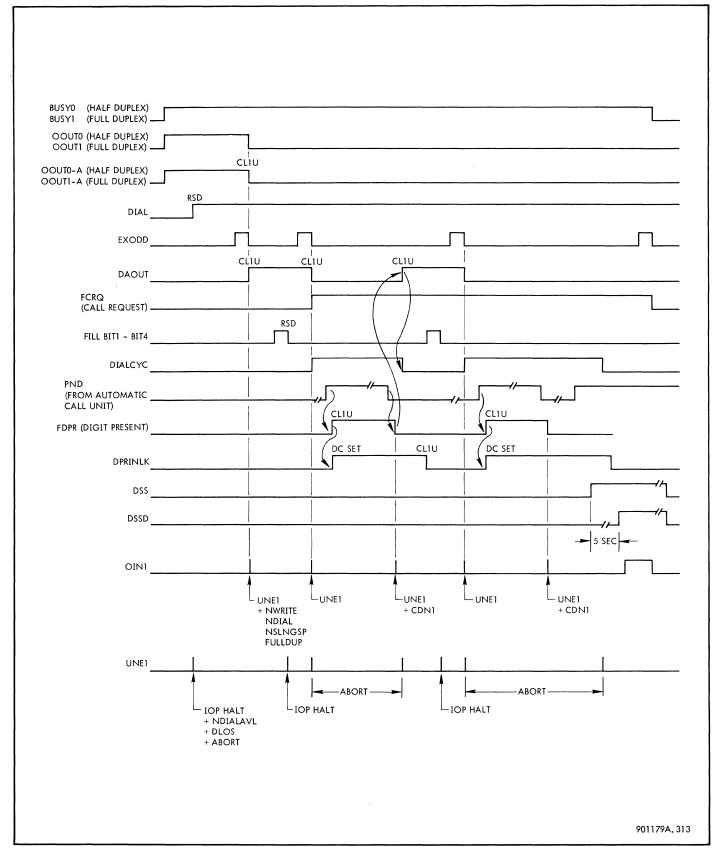

| 3-36  | Dial Order Timing Sequence                             | 3-38 |

| 3-37  | Disconnect Order Timing Sequence                       | 3-41 |

| 3-38  | Disable or Enable Ring Order Timing Sequence           | 3-41 |

| 3-39  | Automatic Hangup                                       | 3-42 |

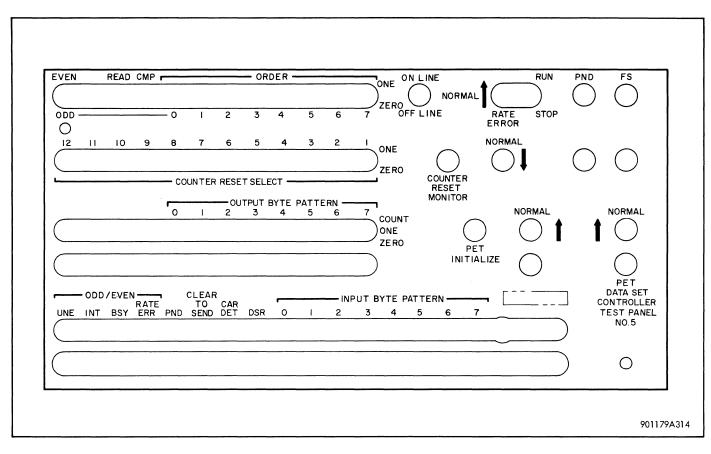

| 3-40  | PET Operation                                          | 3-42 |

| MAINT | ENANCE AND PARTS LIST                                  | 4-1  |

| 4-1   | Introduction                                           | 4-1  |

| 4-2   | Maintenance                                            | 4-1  |

| 4-3   | Special Tools and Test Equipment                       | 4-1  |

| 4-4   | Cleaning Agents                                        | 4-1  |

| 4-5   | Preventive Maintenance Schedule                        | 4-1  |

| 4-6   | Performance Testing (Using the PET)                    | 4-3  |

| 4-7   | Preliminary Procedur <b>es</b>                         | 4-3  |

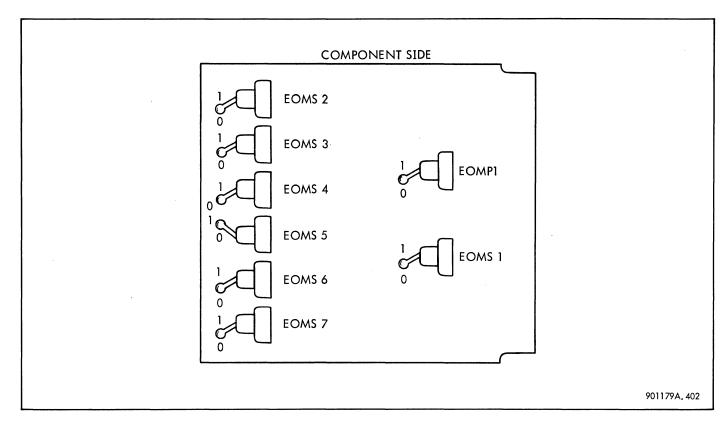

| 4-8   | Installation Checks                                    | 4-3  |

| 4-9   | Selecting the End-of-Message Character                 | 4-3  |

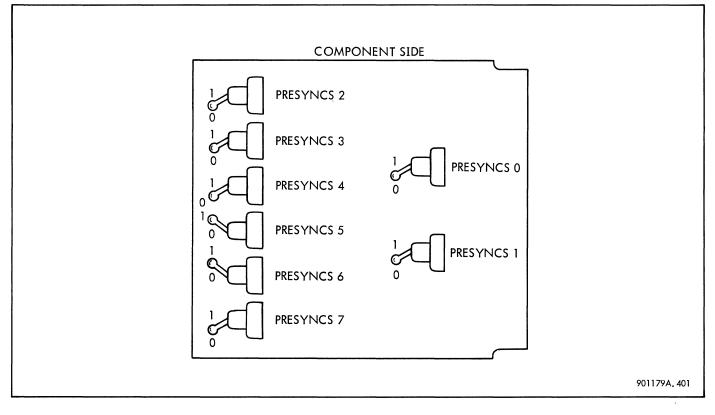

| 4-10  | Selecting the Synchronizing Character                  | 4-4  |

| 4-11  | Interpretation of ODD/EVEN Switch on PET Panel Overlay | 4-4  |

| 4-12  | Read/Write Asynchronous Test                           | 4-4  |

| 4-13  | Read/Write Synchronous Test                            | 4-7  |

| 4-14  | Enable Ring Detect Test                                | 4-9  |

| 4-15  | Disconnect Test                                        | 4-9  |

| 4-16  | Generate Long Space Test                               | 4-10 |

| 4-17  | Dial Option Test                                       | 4-10 |

| 4-18  | Automatic Disconnect Timing Adjustment                 | 4-12 |

| 4-19  | Voltage Margins                                        | 4-12 |

| 4-20  | Parts List                                             | 4-12 |

| 4-21  | Parts List Table and Module Location Chart             | 4-12 |

| 4-22  | Arrangement of Parts List Table                        | 4-12 |

| 4-23  | Manufacturers Code Index                               | 4-12 |

### Illustrations-Tables

### 901179

### LIST OF ILLUSTRATIONS

| Figure | Title                                                                 | Page |

|--------|-----------------------------------------------------------------------|------|

| 1-1    | Data Set Controller Models 7601, 7602, and 7603                       | 1-2  |

| 1-2    | Communication Link Diagram                                            | 1-3  |

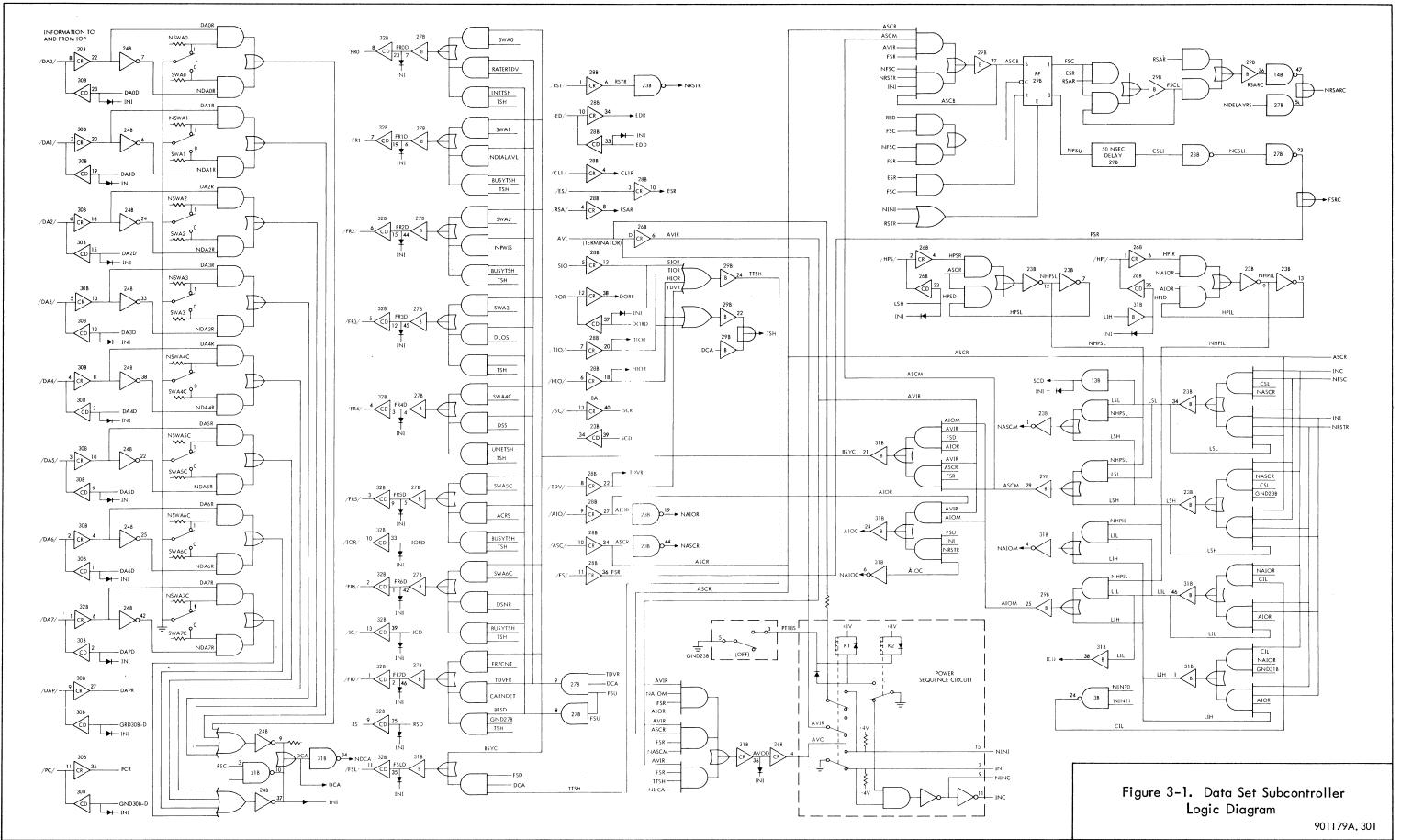

| 3-1    | Data Set Subcontroller Logic Diagram                                  | 3-11 |

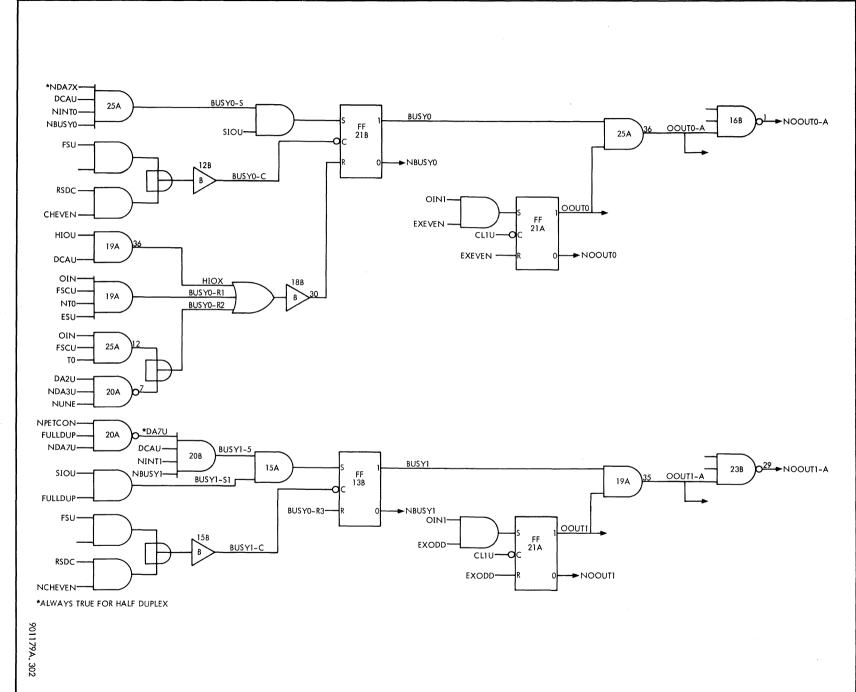

| 3-2    | Flip-flops BUSYO and BUSY1, Functional Diagram                        | 3-13 |

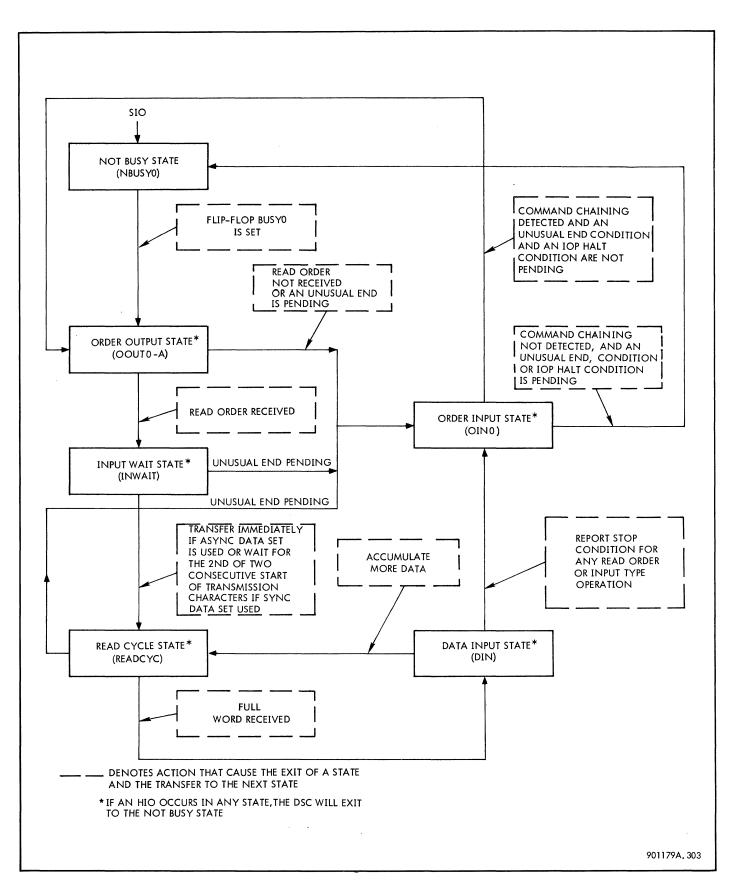

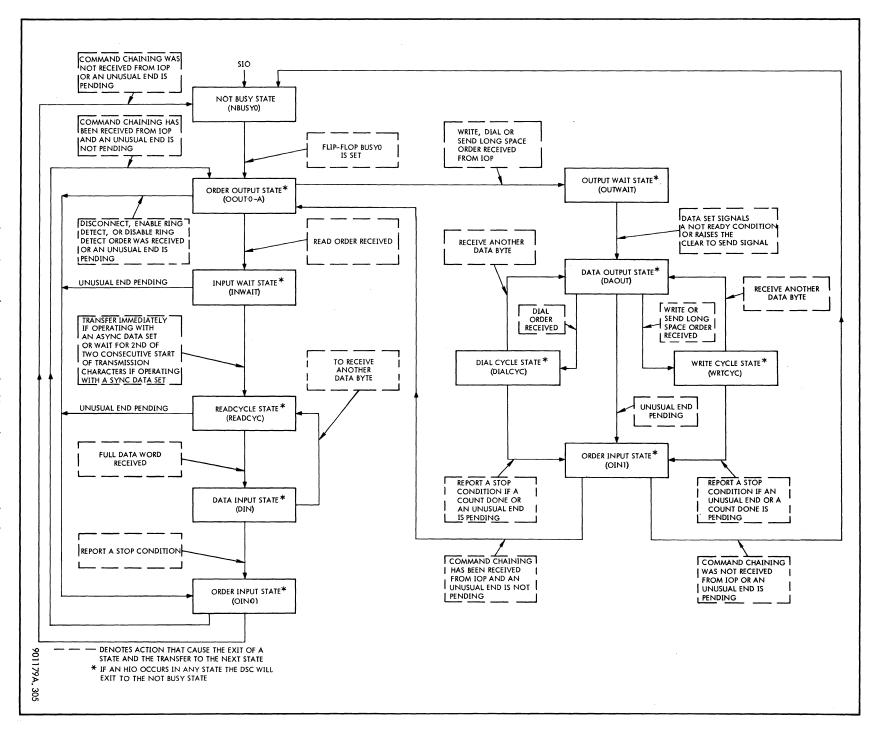

| 3-3    | Even Channel Input/Output State (Full-Duplex Operation), Flow Diagram | 3-15 |

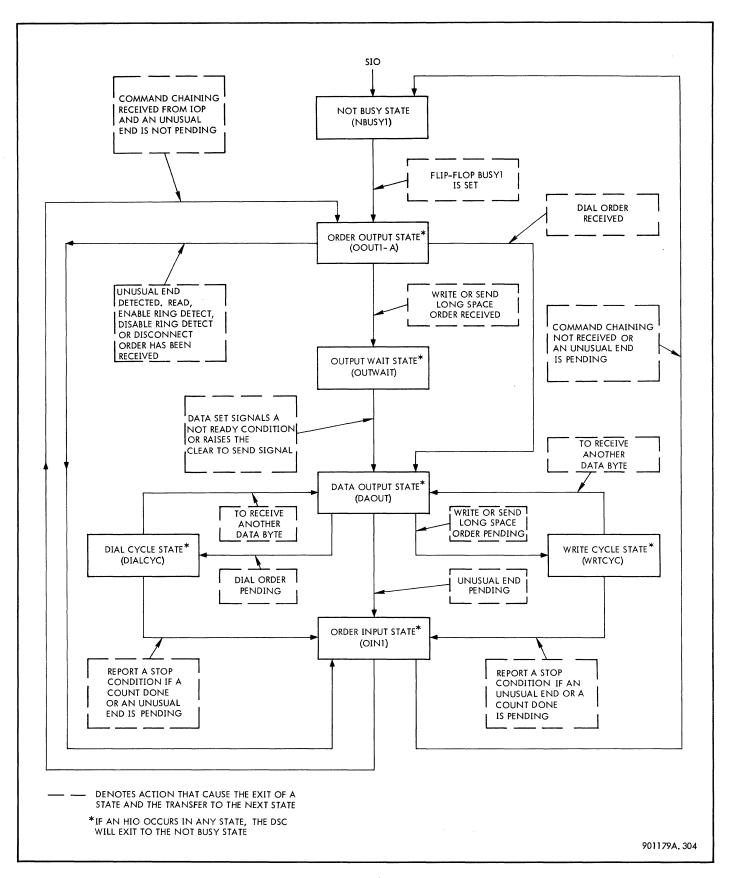

| 3-4    | Odd Channel Input/Output State Flow Diagram                           | 3-17 |

| 3-5    | Odd Channel Input/Output State (Half-Duplex Operation), Flow Diagram  | 3-18 |

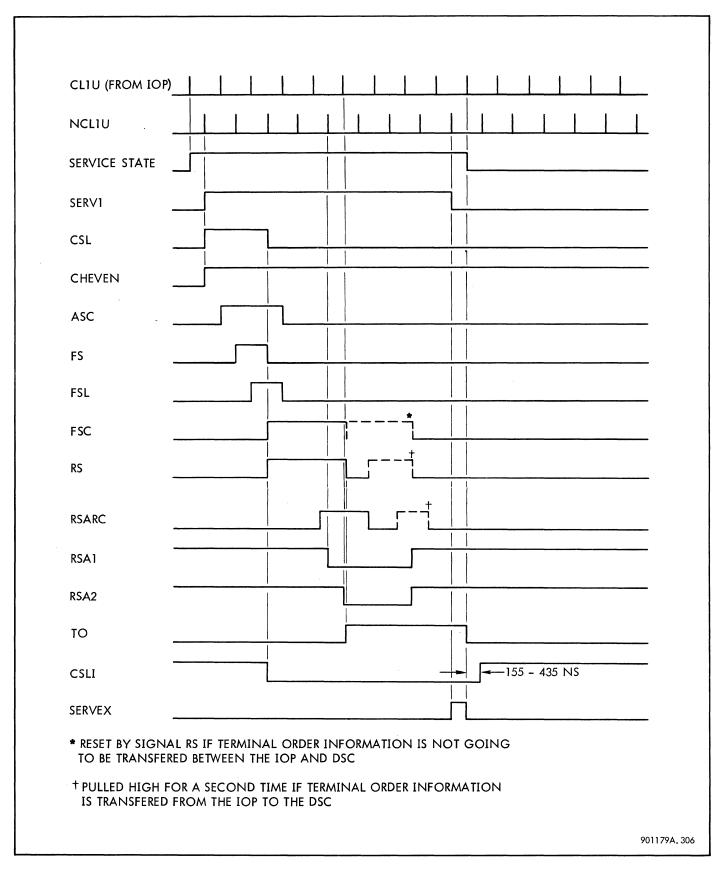

| 3-6    | Even Channel Service Cycle, Timing Diagram                            | 3-21 |

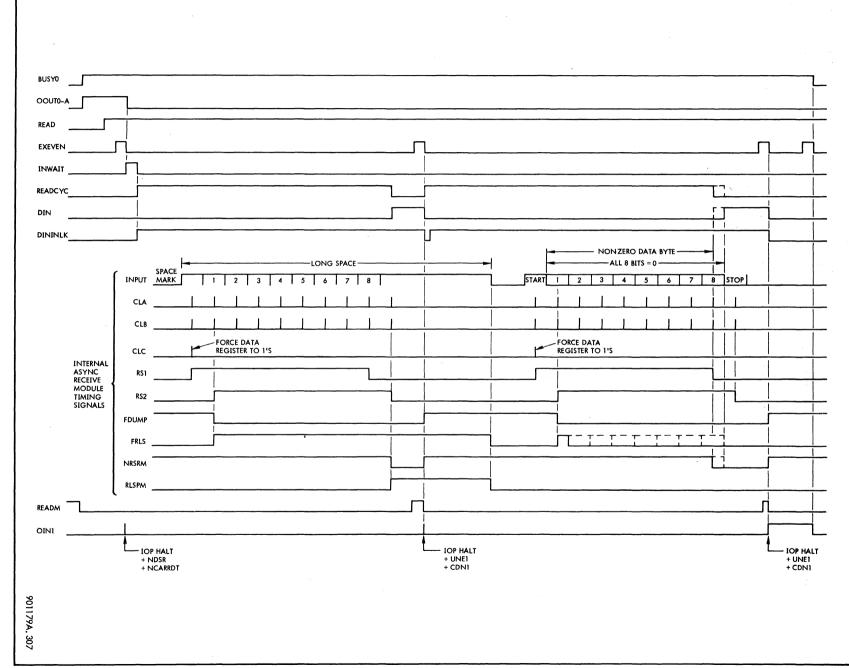

| 3-7    | Asynchronous Read (Format 3 8L/10U), Timing Diagram                   | 3-24 |

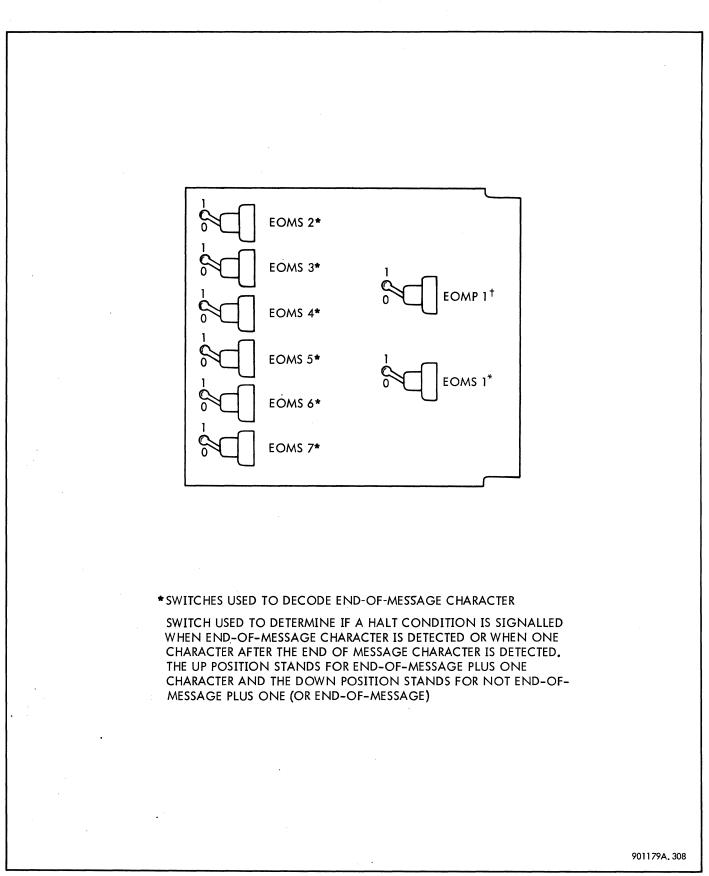

| 3-8    | End-of-Message Decoding Switches                                      | 3-26 |

| 3-9    | Synchronous Read (Six Bits/Byte), Timing Diagram                      | 3-28 |

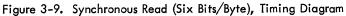

| 3-10   | Synchronous Character Decoding Switches                               | 3-29 |

| 3-11   | Ásynchronous Write, Timing Diagram                                    | 3-32 |

| 3-12   | Synchronous Write (Five Bits/Byte), Timing Diagram                    | 3-36 |

| 3-13   | Dial Order, Timing Diagram                                            | 3-39 |

| 3-14   | PET Panel Overlay Diagram                                             | 3-43 |

| 4-1    | Switch Settings, End-of–Message Character                             | 4-5  |

| 4-2    | Switch Settings, Synchronous Character                                | 4-5  |

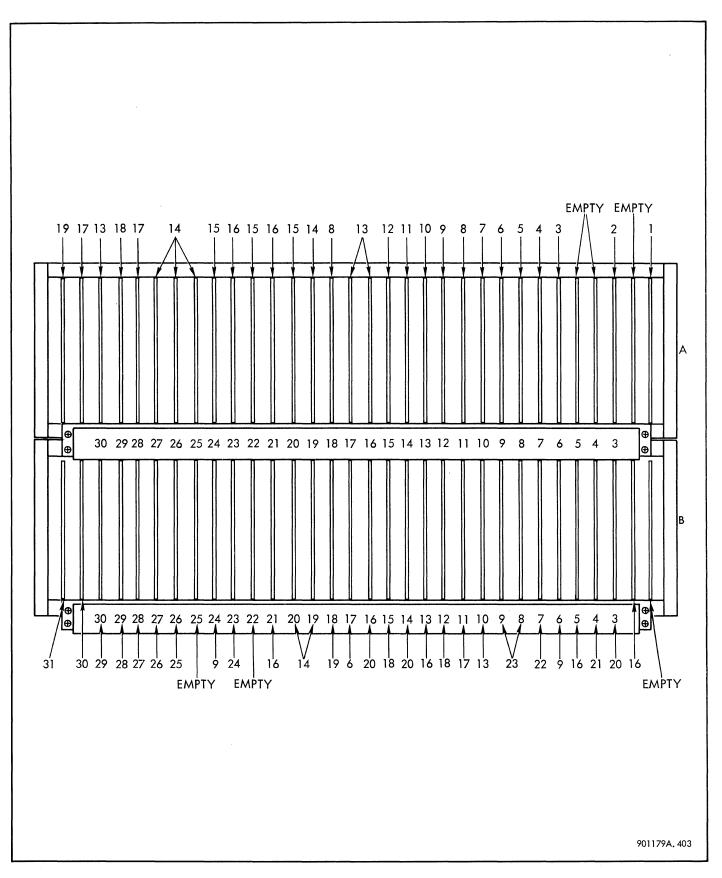

| 4-3    | Data Set Controller Module Location Chart                             | 4-15 |

### LIST OF TABLES

### Table

# Title

### Page

| 1-1 | Data Set Controller Options                                        | 1-4  |

|-----|--------------------------------------------------------------------|------|

| 1-2 | Data Set Controller Specifications and Leading Particulars         | 1-5  |

| 2-1 | Data Set Controller Response to SIO, HIO or TIO                    | 2-1  |

| 2-2 | Data Set Controller Response to TDV                                | 2-3  |

| 2-3 | Data Set Controller Response to AIO                                | 2-5  |

| 2-4 | DSC Response to Output Orders                                      | 2-5  |

| 2-5 | Information Supplied by Data Set Controller During Order Input     | 2-7  |

| 2-6 | Data Set Controller Response to Terminal Orders                    | 2-7  |

| 2-7 | Data Set Controller Format Units                                   | 2-9  |

| 2-8 | Data Set Description                                               | 2-10 |

| 3-1 | Interconnecting Cable Assemblies                                   | 3-1  |

| 3–2 | Glossary of Terms                                                  | 3-3  |

| 3-3 | Exiting Conditions, Even Channel Order Output State                | 3-16 |

| 3-4 | Exiting Conditions, Odd Channel Order Output State                 | 3-19 |

| 3-5 | Exiting Conditions, Odd Channel Data Output State                  | 3-19 |

| 3-6 | Exiting Conditions, Odd Channel Order Input State                  | 3-20 |

| 4-1 | Special Tools and Test Equipment                                   | 4-1  |

| 4-2 | Preventive Maintenance Schedule                                    | 4-2  |

| 4-3 | Modification Kit Installation Checks                               | 4-2  |

| 4-4 | Storage Bit Register                                               | 4-11 |

| 4-5 | Data Set Controller Models 7601, 7602, and 7603, Replaceable Parts | 4-13 |

| 4-6 | Manufacturers Code Index                                           | 4-14 |

|     | *                                                                  |      |

#### LIST OF RELATED PUBLICATIONS

The following publications contain information which is not included in this manual, but which contributes to a complete understanding of Data Set Controller Model 7601 when used with related SDS equipment.

| Publication Title                                                                            | Publication No. |

|----------------------------------------------------------------------------------------------|-----------------|

| Diagnostic Control Program for Sigma<br>2 Computer Peripheral Devices,<br>Reference Manual   | 900839          |

| Diagnostic Control Program for Sigma<br>5/7 Computer Peripheral Devices,<br>Reference Manual | 900712          |

| Sigma 2 Data Set Controller, Diagnostic<br>Program Manual                                    | 901510          |

| Sigma 5 and 7 Data Set Controller,<br>Diagnostic Program Manual                              | 901509          |

| Sigma Computer Systems/Interface<br>Design Manual                                            | 900973          |

| Power Supply Model PT16, Technical Manual                                                    | 901080          |

| Sigma 7 Computer, Reference Manual                                                           | 900950          |

| Sigma 5 Computer, Reference Manual                                                           | 900959          |

| Sigma 5 and 7 Relocatable Diagnostic<br>Program Loader, Diagnostic Program Manual            | 900972          |

| Sigma Symbol and Meta <b>-Symbol</b><br>Reference Manual                                     | 900952          |

### SECTION I GENERAL DESCRIPTION

#### 1-1 INTRODUCTION

This manual describes Data Set Controller (DSC) Models 7601, 7602, and 7603, manufactured by Xerox Corporation. The information in this manual is arranged in the following format:

- a. Section I General Description

- b. Section II Operation and Programming

- c. Section III Principles of Operation

- d. Section IV Maintenance and Parts List

The DSC enables Sigma computers to connect to a synchronous or asynchronous data set and to transmit and receive data over common carrier private lines or public switched network facilities, in a half-duplex or full-duplex mode of operation.

#### 1-2 LIST OF RELATED PUBLICATIONS

The related publications listed in the front matter of this manual contain the following information:

a. The diagnostic control program manuals for Sigma 2, 5, and 7 computers describe the diagnostic control programs that serve as interface between the user and the specific peripheral program.

b. The data set controller diagnostic program manuals for Sigma 2, 5, and 7 computers describe the self-loading and object programs used to test and exercise the data set controller.

c. The Sigma computer interface design manual describes how external devices are connected to Sigma computers.

d. The Power Supply Model PT16 technical manual describes the principles of operation, adjustments, operational checks, and methods of installing Power Supply Model PT16.

e. The Sigma 2, 5, and 7 computer reference manuals describe Sigma computer program format and application and computer operation.

f. The Sigma relocatable diagnostic program loader manual describes the program used to load peripheral diagnostic programs into main memory.

g. The symbol and metasymbol reference manual describes the symbolic source language programs and how these programs are converted to machine language.

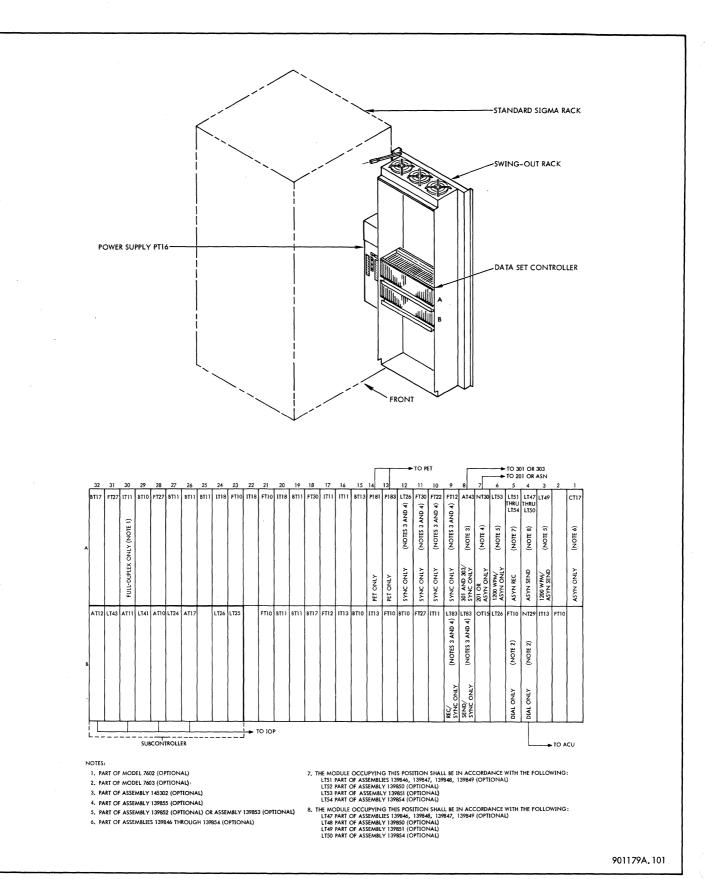

#### 1-3 PHYSICAL DESCRIPTION (Figure 1-1)

The basic DSC consists of two chassis mounted in a standard Sigma swing frame. The two chassis contain 64 module positions (32 in each chassis). During the asynchronous mode of operation, 46 module positions are used. During the highspeed synchronous mode of operation, 49 module positions are used. Four standard eight-bit input/output channel interface cables and one data set cable are used to connect the DSC to the IOP and the data set. When an option such as automatic dialing is added, an additional cable assembly and two modules are required to connect the dialing unit to the DSC.

Power Supply Model PT16 supplies power to the DSC. The supply is external to the DSC and is mounted on the standard Sigma swing frame. Refer to publication 901080 for a complete physical description of this power supply.

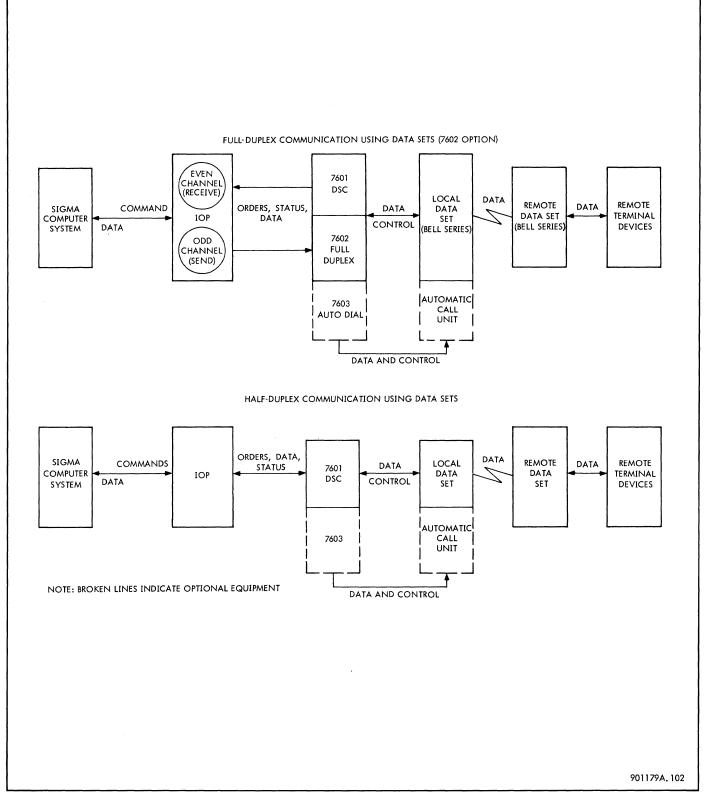

#### 1-4 FUNCTIONAL DESCRIPTION (Figure 1-2)

Figure 1-2 illustrates a communication link diagram of the DSC. Most of the blocks in the figure are not integral parts of the DSC; they are shown merely to illustrate how data is transmitted and received between the Sigma computer system and the remote device, as well as how the DSC controls the application of this two-way exchange.

The Sigma computer system communicates with the IOP. Communication begins with an SIO directive from the CPU. The IOP communicates with the DSC subcontroller (which is an integral part of the DSC), and the DSC communicates with a local data set. The local data set in turn communicates with a remote data set, which communicates with the devices connected to it for service.

The DSC is capable of communicating with asynchronous or synchronous data sets in a half-duplex or full-duplex mode of operation. (See table 1-1 for a description of these modes and other options.) The basic DSC provides the half-duplex send and receive capability plus a ring detection circuit with interrupt features. Adding modules to the basic DSC provides the DSC with full-duplex capabilities. The fullduplex feature provides the capabilities of sumultaneously sending and receiving data over a private line or over standard telephone lines.

If standard telephone lines are used, communication with a remote data set must be established manually or programmatically before data exchange can take place. To programmatically establish communication with the remote data set, an automatic dialing system, consisting of two modules is added to the basic DSC configuration. The dialing system is then

Figure 1-1. Data Set Controller Models 7601, 7602, and 7603

Figure 1–2. Communication Link Diagram

| Option         | Model | Configuration                                      | Additional Modules | Format                       | Description                                                                                                                                                                                                                               |

|----------------|-------|----------------------------------------------------|--------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Half duplex    | 7601  |                                                    | None               |                              | Capable of sending and<br>receiving data plus provid-<br>ing a ring detection circuit<br>with interrupt features.<br>Communicates with one<br>IOP channel                                                                                 |

| Full duplex    | 7602  |                                                    | 1                  |                              | Permits DSC to simultan-<br>eously send and receive<br>data. Communicates with<br>two consecutive IOP chan-<br>nels – odd and even. Odd<br>channel is associated with<br>send; even, with receive.<br>Read channel is highest<br>priority |

| Automatic dial | 7603  |                                                    | 2                  |                              | Allows outgoing calls over<br>standard telephone lines to<br>initiate remote data set ring<br>circuit. When full-duplex<br>option is installed, dialing<br>feature is extension of write<br>operation                                     |

| Asynchronous   |       | 103A, 103F, 301B,<br>303, 202C, 202D               |                    | 5-7.5<br>7-9<br>8-10<br>8-11 | Transmits and receives data<br>at a rate determined by the<br>DSC. Supplies no clock or<br>timing pulses to distinguish<br>data pulses from non-data<br>pulses. Transmits all data<br>in a selected format                                |

| Synchronous    |       | 201A, 201B, 301B,<br>303B6, 303C6,<br>303D6, 303E6 | None               |                              | Transmits and receives data<br>in a back-to-back fashion                                                                                                                                                                                  |

| Table 1- | -1. | Data | Set | Control | ller | Options |

|----------|-----|------|-----|---------|------|---------|

|----------|-----|------|-----|---------|------|---------|

programmed to ring the remote data set before data transfer takes place. When the local and remote data sets are connected together by a private line, the automatic dialing system is not required.

The rate at which data is transmitted and received over a private line or standard telephone lines is determined by the DSC and the type of data set used. If an asynchronous set is used, no timing or clock pulse is supplied by the data set to distinguish data pulses from non-data pulses. Consequently, all data is transmitted in a preselected data format containing a group of data bits preceded by a start pulse and followed by one or more stop pulses. If the data set used is synchronous, clock timing pulses are supplied by the data set while data is transmitted and received. Thus, synchronization is controlled by the data set and the responsibility for generating start and stop pulses is removed from the DSC. With this arrangement, the DSC is able to transmit and receive data in a back-to-back fashion.

1-4

In full-duplex operation, the DSC responds to two IOP address channels that have identical coding on the first seven most significant digits of the eight-digit address. The IOP address channels are referred to by the DSC as the odd channel address and the even channel address. The odd channel address is associated with writing, disconnecting, generating long space, or dialing. The even channel is associated with reading data or disabling or enabling the DSC ring detection circuit. If the DSC is in the halfduplex mode of operation, the DSC will respond to only one IOP channel address. This channel address is determined by all eight digits of the eight digit address and is decoded by the eight toggle switches on the subcontroller.

#### 1-5 SPECIFICATIONS AND LEADING PARTICULARS

Table 1-2 lists the power requirements, environmental requirements, physical characteristics, and performance characteristics of the data set controller.

| 11                       |          | JIREMENTS   |                                             |          |                        |                      |  |

|--------------------------|----------|-------------|---------------------------------------------|----------|------------------------|----------------------|--|

| Unit                     |          | Requirement |                                             |          |                        |                      |  |

| Data set controller      |          |             | +4∨ <b>,</b> 5.0                            | A        |                        |                      |  |

|                          |          | +8V, 3.5A   |                                             |          |                        |                      |  |

|                          |          |             |                                             | -87, 1.0 | A                      |                      |  |

| Power Supply Model PT1   | 6        |             |                                             | 120V (±5 | %), 2000 Hz, 15.0A     |                      |  |

| Fan                      |          |             |                                             | 120∨, 60 | ) Hz, 0.2A             |                      |  |

|                          | ENVIRO   | NMENTAL     | REQU                                        | IREMENTS |                        |                      |  |

| Unit                     |          |             |                                             |          | Requirement            |                      |  |

| Data set controller      |          |             |                                             | Temperat | ure                    |                      |  |

|                          |          |             |                                             | Opera    | ating: +5°C - +50°C    |                      |  |

|                          |          |             |                                             | Nono     | perating: -40°C - +60° | °C                   |  |

|                          |          |             |                                             | Humidity |                        |                      |  |

|                          |          |             | Operating: 10% - 95%                        |          |                        |                      |  |

|                          | •        |             | Nonoperating: No limits                     |          |                        |                      |  |

|                          |          |             | Temperature change                          |          |                        |                      |  |

|                          |          |             | rate: -12°C/hr max                          |          |                        |                      |  |

|                          |          |             | Wet bulb temperature: 30 <sup>0</sup> C max |          |                        |                      |  |

|                          | PHYSIC   | CAL CHARA   | ACTER                                       | ISTICS   |                        | are a                |  |

| Unit                     | Height   | Widt        | h                                           | Depth    | Weight                 | Service<br>Clearance |  |

| Data set controller      | 10.5 in. | 19 in       | n. 6 in. 18 lb. approx. 15 in.              |          |                        |                      |  |

|                          | PERFORM  | ANCE CHA    | ARACTI                                      | ERISTICS |                        |                      |  |

| Featu                    | re       |             | Characteristic                              |          |                        |                      |  |

| Bit transmission rate    |          |             | 45-230.4 kilobit/s                          |          |                        |                      |  |

| Rate classification      |          |             | Low to high speed, message oriented         |          |                        |                      |  |

| Maximum possible byte r  | ate      |             | 100 kilobit/s                               |          |                        |                      |  |

| Disconnect time          |          |             | 50 ms                                       |          |                        |                      |  |

| Successful dialing opera | tion     |             | 5–50 plus digit dialing time                |          |                        |                      |  |

|                          |          |             |                                             |          |                        |                      |  |

# Table 1–2. Data Set Controller Specifications and Leading Particulars

### SECTION II OPERATION AND PROGRAMMING

#### 2-1 INTRODUCTION

This section describes the programmed function indicators issued by the IOP to the DSC, and the response of the DSC to these programmed function indicators. The different format units used by the DSC to accommodate a wide variety of remote terminals are also described.

#### 2-2 FUNCTION INDICATORS

The function indicators issued by the CPU via the IOP to the DSC are as follows:

- a. Start input/output (SIO)

- b. Halt input/output (HIO)

- c. Test input/output (TIO)

- d. Test device (TDV)

- e. Acknowledge interrupt (AIO)

- f. Acknowledge service call (ASC)

#### 2-3 SIO, HIO, AND TIO INDICATORS

The SIO, HIO, or TIO function indicator is issued by the IOP along with an address to initiate a start, halt, or test operation within the addressed DSC. In response to the function indicator, the DSC supplies status information to the IOP according to table 2-1. In full- or half-duplex operation, the status reported applies to the channel being addressed. If an HIO is issued on either channel during full-duplex operation, the HIO causes both channels (odd and even) to go to the ready state.

#### 2-4 TDV INDICATOR

The TDV function indicator permits the IOP to test specific conditions within the DSC. In response to a TDV, the DSC provides the IOP with status information according to table 2-2.

#### Note

Although the HIO function indicator and the IOR signal reset the usual DSC flipflops (unusual end, busy, interrupt), they have no effect on the data set in autodial device condition.

| STATUS            | ۶U۲ | VCT. | ION | RES | PON | <b>VSE</b> | LINE | S | DORD | IORD | CONDITION                                                                                                                                                                                                                                                                                                        |  |

|-------------------|-----|------|-----|-----|-----|------------|------|---|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                   | 0   | 1    | 2   | 3   | 4   | 5          | 6    | 7 | CC1  | CC2  |                                                                                                                                                                                                                                                                                                                  |  |

| Interrupt pending | 1   |      |     |     |     |            |      |   |      |      | DSC has issued an interrupt which<br>has not been acknowledged. An<br>interrupt is issued when any of<br>the following conditions exists:<br>a. DAOR is true during a<br>terminal order (TO)<br>b. Ring detect is enabled<br>and carrier is received<br>c. Long space has been de-<br>tected (asynchronous mode) |  |

Table 2-1. Data Set Controller Response to SIO, HIO or TIO

|                        | FUNCTION RESPONSE LINES DORD IORD |   |   |   |   |   |   |   |     |     |                                                                                                                |

|------------------------|-----------------------------------|---|---|---|---|---|---|---|-----|-----|----------------------------------------------------------------------------------------------------------------|

| STATUS                 | 0                                 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | CC1 | CC2 | CONDITION                                                                                                      |

| Device ready           |                                   | 0 | 0 |   |   |   |   |   |     |     | DSC is in ready state and will<br>accept an SIO unless an inter-<br>rupt is pending                            |

| Device not operational |                                   | 0 | 0 |   |   |   |   |   |     |     | Cannot occur                                                                                                   |

| Device unavailable     |                                   | 0 | 1 |   |   |   |   |   |     |     | Cannot occur                                                                                                   |

| Device busy            |                                   | 1 | 1 |   |   |   |   |   |     |     | DSC is busy performing a task<br>initiated by a previous SIO                                                   |

| Automatic mode         |                                   |   |   | 1 |   |   |   |   |     |     | Always true (1)                                                                                                |

| Unusual end            |                                   |   |   |   | 1 |   |   |   |     |     | Unusual end occurred while<br>terminating last operation.<br>Unusual end is caused by any<br>of the following: |

|                        |                                   |   |   |   |   |   |   |   |     |     | a. Loss of data set ready<br>during a read or write oper-<br>ation                                             |

|                        |                                   |   |   |   |   |   |   |   |     |     | b. Loss of clear-to-send signal during write operation                                                         |

|                        |                                   |   |   |   |   |   |   |   |     |     | c. Failure to complete<br>dialing operation                                                                    |

|                        |                                   |   |   |   |   |   |   |   |     |     | d. Line occupied and dialing operation attempted                                                               |

|                        |                                   |   |   |   |   |   |   |   |     |     | e. Data set ready is off<br>and a read or write order is<br>received                                           |

|                        |                                   |   |   |   |   |   |   |   |     |     | f. Rate error occurred<br>during a read or write oper–<br>ation (cannot occur on asyn–<br>chronous write)      |

|                        |                                   |   |   |   |   |   |   |   |     |     | g. DSC received IOP hal<br>during a TO                                                                         |

| DSC ready              |                                   |   |   |   |   | 0 | 0 |   |     |     | DSC is in ready state and will<br>accept an SIO unless an inter-<br>rupt is pending                            |

| DSC not operational    |                                   |   |   |   |   | 0 | 1 |   |     |     | Cannot occur                                                                                                   |

| DSC unavailable        |                                   |   |   |   |   | 1 | 0 |   |     |     | Cannot occur                                                                                                   |

| DSC busy               |                                   |   |   |   |   | 1 | 1 |   |     |     | DSC busy performing a task<br>initiated by previous SIO                                                        |

# Table 2-1. Data Set Controller Response to SIO, HIO or TIO (Cont.)

|                                         | FU | NC | 10I | N RE | SPO | NSE | LIN | ES | DORD | IORD |                     |

|-----------------------------------------|----|----|-----|------|-----|-----|-----|----|------|------|---------------------|

| STATUS                                  | 0  | 1  | 2   | 3    | 4   | 5   | 6   | 7  | CC1  | CC2  | CONDITION           |

| Not used                                |    |    |     |      |     |     |     | 0  |      |      | Always false (zero) |

| SIO successful (SIO)                    |    |    |     |      |     |     |     |    |      | 1    |                     |

| DSC not busy when<br>HIO occurred (HIO) |    |    |     |      |     |     |     |    |      | 1    |                     |

| SIO can be accepted<br>(TIO)            |    |    |     |      |     |     |     |    |      | 1    |                     |

| Address recognition                     |    |    |     |      |     |     |     |    | 1    |      |                     |

|                                         |    |    |     |      |     |     |     |    |      |      |                     |

Table 2-1. Data Set Controller Response to SIO, HIO or TIO (Cont.)

|                                | FL | INC. | 101 | N RE | SPO | NSE | LIN | ES | DORD | IORD |                                                                                                                                                                         |  |

|--------------------------------|----|------|-----|------|-----|-----|-----|----|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| STATUS                         | 0  | 1    | 2   | 3    | 4   | 5   | 6   | 7  | NCC1 | NCC2 |                                                                                                                                                                         |  |

| Rate error                     | 1  |      |     |      |     |     |     |    |      |      | Rate error occurred during read<br>or write operation. (Rate error<br>cannot occur during asynchro–<br>nous write)                                                      |  |

| Local phone in use             |    |      |     | 1    |     |     |     |    |      |      | Local phone in use (used with<br>auto dialing)                                                                                                                          |  |

| Carrier detect off             |    |      |     |      |     |     |     | 1  |      |      | Local data set not receiving<br>carrier from remote data set.<br>During connect sequence, this<br>indicates handshaking not<br>complete                                 |  |

| Local data set in data<br>mode |    |      |     |      | 1   |     |     |    |      |      | Local data set in data mode<br>(used with auto dialing)                                                                                                                 |  |

| Data set not ready             |    |      |     |      |     |     | ]*  |    |      |      | Data set not ready caused by<br>any of the following conditions<br>a. No power                                                                                          |  |

|                                |    |      |     |      |     |     |     |    |      |      | b. Data set in talk, test, c<br>local mode (controlled by data<br>set switches)                                                                                         |  |

|                                |    |      |     |      |     |     |     |    |      |      | c. "Originate" data set<br>has not received carrier from<br>"answer" data set during con-<br>nect sequence or "answer" data<br>set has not received ring indi-<br>cator |  |

| Table 2-2. | Data Set | Controller | Response | to TDV  |

|------------|----------|------------|----------|---------|

|            | Dura Sci | Connorior  | Response | 10 10 1 |

|                                                                                                      | FL | JNC | TIO | n re | SPC | NSE |   |   |      |      |                                                                                                                           |

|------------------------------------------------------------------------------------------------------|----|-----|-----|------|-----|-----|---|---|------|------|---------------------------------------------------------------------------------------------------------------------------|

| STATUS                                                                                               | 0  | 1   | 2   | 3    | 4   | 5   | 6 | 7 | NCC1 | NCC2 | CONDITION                                                                                                                 |

| Automatic dial not avail–<br>able<br>Automatic dial does not<br>have power<br>Abandon call and retry |    | 1   | 1   |      |     | 1   |   |   |      |      | Automatic dial feature not<br>installed<br>Auto-dial unit does not have<br>power<br>Dialing operation not suc-<br>cessful |

| Undefined                                                                                            |    |     |     |      |     |     |   |   |      | 0    | Always zero                                                                                                               |

| Address recognition                                                                                  |    |     |     |      |     |     |   |   | 1    |      |                                                                                                                           |

Table 2-2. Data Set Controller Response to TDV (Cont.)

#### 2-5 AIO INDICATOR

When the DSC has an interrupt pending, the low priority interrupt call line to the IOP via the subcontroller is pulled high. The IOP acknowledges the interrupt call by pulling the AIO function indicator and the function strobe lines high. During the time the function strobe line is high, status is supplied to the IOP according to table 2-3.

#### 2-6 ASC INDICATOR

The ASC function indicator is generated by the IOP in response to a service call from the DSC. If the DSC is the highest priority with a service call pending, the DSC connects itself for a service request cycle. This service request cycle is part of the input/output operation routine.

#### 2-7 OUTPUT ORDERS

The response of the DSC to orders such as write, dial, read, enable ring detect, disable ring detect, disconnect call, or generate long space is described in the following paragraphs. Table 2-4 should be referred to for the program code and the bits sampled by the DSC to define the correct order.

#### 2-8 WRITE ORDER

The DSC has four different timing sequences that can occur during the processing of a write order. Each timing sequence is unique to the option installed in the DSC and the type of data set that is communicating with the DSC. One timing sequence occurs when the DSC is operated in the full-duplex mode of operation. A second timing sequence occurs when the DSC is operated in the halfduplex mode of operation. A third timing sequence occurs when the DSC is operating with an asynchronous data set. A fourth and final timing sequence occurs when the DSC is operating with a synchronous data set.

A write order is initiated when the DSC accepts an SIO on the odd channel input/output address during full-duplex operation or on the odd or even channel input/output address during half-duplex operation. Accepting the SIO sets the appropriate busy flip-flop and transfers the DSC to the order output state. In the order output state, the DSC decodes the write order. The decoded write order initiates the transmission of a number of characters from computer memory to the data set after the clear-to-send signal is received from the data set.

The three-bit C field of the write order shown in table 2-4 is ignored if an asynchronous format unit is installed in the DSC. However, if a synchronous format unit is installed in the DSC, the three-bit C field specifies the number of bits to be transmitted out of each eight-bit byte from memory. A value of 000 in the C field signifies that eight bits per byte are to be transmitted.

Values of 010 through 111 (count of 001 is not allowed) correspond to two through seven bits per byte. That is, a value of 010 in the C field will cause only the information contained in data lines 6 and 7 to be transmitted, whereas another value in the C field will cause different data line bits to be transmitted. Also during the synchronous mode of operation the programmer must send at least four synchronizing characters at the beginning of each message.

#### 2-9 DIAL ORDER

Table 2-4 illustrates the dial order that initiates dialing if the automatic dialing feature is installed. If the automatic dialing feature is not installed, an unusual end will be reported to the IOP. With the automatic dialing feature

|                                                                                                  | FL | INC | TIO | n re | SPO | NSE | LIN | IES | DORD | NORD |                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------|----|-----|-----|------|-----|-----|-----|-----|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATUS                                                                                           | 0  | 1   | 2   | 3    | 4   | 5   | 6   | 7   | NCCI | NCC2 | CONDITION                                                                                                                                                                                                                                                                                                               |

| Rate error<br>Ring (even channel only<br>for full–duplex operation)                              | 1  | 1   |     |      |     |     |     |     |      |      | Rate error occurred during read<br>or write operation (cannot oc-<br>cur during asynchronous write)<br>DSC sensed carrier detection<br>after receiving an enable ring<br>detect order. This bit signifies<br>that connection has been estab-<br>lished between the two data<br>sets and that data exchange<br>may start |

| Long space detected (even<br>channel only for full du–<br>plex operation)<br>Address recognition |    |     | ]   |      |     |     |     |     | 1    |      | Long space has been received                                                                                                                                                                                                                                                                                            |

| No faults exist<br>Not used                                                                      |    |     |     | 0    | 0   | 0   | 0   | 0   |      | 1    | Rate error not being reported                                                                                                                                                                                                                                                                                           |

## Table 2-3. Data Set Controller Response to AIO

### Table 2-4. DSC Response to Output Orders

|                                        | -          |     |    |    |     |    |   |   |  |  |  |  |

|----------------------------------------|------------|-----|----|----|-----|----|---|---|--|--|--|--|

|                                        | WRIT       | ΓE  |    |    |     |    |   |   |  |  |  |  |

|                                        | DATA LINES |     |    |    |     |    |   |   |  |  |  |  |

|                                        | 0          | 1   | 2  | 3  | 4   | 5  | 6 | 7 |  |  |  |  |

| Programmed code                        | C          | C   | С  | 0  | 0   | 0  | 0 | 1 |  |  |  |  |

| Bits sampled by DSC<br>to define write | С          | fie | Íd |    | Х   | Х  | Х | Х |  |  |  |  |

|                                        | DIA        | L   |    |    |     |    |   |   |  |  |  |  |

|                                        |            |     | DA | TA | LIN | ES |   |   |  |  |  |  |

|                                        | 0          | 1   | 2  | 3  | 4   | 5  | 6 | 7 |  |  |  |  |

| Programmed code                        | 0          | 0   | 0  | 0  | 0   | 1  | 0 | 1 |  |  |  |  |

| Bits sampled by DSC<br>to define dial  |            |     |    |    |     | Х  | Х | Х |  |  |  |  |

|                                        | REA        | D   |    |    |     |    |   |   |  |  |  |  |

|                                        |            |     | DA | TA | LIN | ES |   |   |  |  |  |  |

|                                        | 0          | 1   | 2  | 3  | 4   | 5  | 6 | 7 |  |  |  |  |

| Programmed code                        | c          | С   | c  | 0  | 0   | 0  | 1 | 0 |  |  |  |  |

| Bits sampled by DSC to<br>define read  | С          | fie | ld |    |     |    |   | Х |  |  |  |  |

# Table 2-4. DSC Response to Output Orders (Cont.)

| ENIADIE                                                 |   | <u> </u> | ETE  | <u>ст</u> |     |     |   |   |

|---------------------------------------------------------|---|----------|------|-----------|-----|-----|---|---|

| ENABLE                                                  |   | 5 0      |      |           |     |     |   |   |

|                                                         |   |          | DA   | TA        | LIN | ES  |   |   |

|                                                         | 0 | 1        | 2    | 3         | 4   | 5   | 6 | 7 |

|                                                         |   |          |      |           |     |     |   |   |

| Programmed code                                         | 0 | 0        | 0    | 0         | 0   | 1   | 1 | 1 |

| Bits sampled to define<br>enable ring detect            |   |          |      |           | Х   | Х   | Х | х |

| DISABLE                                                 |   | IG I     | DETI | ECT       |     |     |   |   |

|                                                         |   |          | DA   | ٨TA       | LIN | IES |   |   |

|                                                         | 0 | 1        | 2    | 3         | 4   | 5   | 6 | 7 |

| Programmed code                                         | 0 | 0        | 0    | 0         | 0   | 0   | ] | ] |

| Bits sampled by DSC<br>to define disable<br>ring detect |   |          |      |           | х   | Х   | х | Х |

| DISCONNECT CALL                                         |            |     |       |     |     |    |   |   |  |  |  |

|---------------------------------------------------------|------------|-----|-------|-----|-----|----|---|---|--|--|--|

| DISCO                                                   | <b>NNE</b> | CTC |       | -   |     |    |   |   |  |  |  |

|                                                         | DATA LINES |     |       |     |     |    |   |   |  |  |  |

|                                                         | 0          | 1   | 2     | 3   | 4   | 5  | 6 | 7 |  |  |  |

| Programmed code                                         |            |     |       |     | 1   | 0  | 1 | 1 |  |  |  |

| Bits sampled by DSC<br>to define disconnect<br>call     |            |     |       |     | x   |    | x | х |  |  |  |

| GENERAT                                                 | E LC       | NO  | \$ SP | ACI | 2   |    |   |   |  |  |  |

|                                                         |            |     | DA    | TA  | LIN | ES |   |   |  |  |  |

|                                                         | 0          | 1   | 2     | 3   | 4   | 5  | 6 | 7 |  |  |  |

| Programmed code                                         | 0          | 0   | 0     | 0   | 1   | 0  | 0 | 1 |  |  |  |

| Bits sampled by DSC<br>to define generate<br>long space |            |     |       |     | x   | x  | x | × |  |  |  |

Table 2-4. DSC Response to Output Orders (Cont.)

installed and data lines 5, 6, and 7 of the dial order as shown, the DSC forwards the four least significant digits of each data byte to the automatic call unit (ACU) in a binary coded decimal (BCD) configuration.

The BCD string to the ACU can be of any length because the BCD string is controlled completely by the program. That is, the DSC will continue to request digits until count done is received from the programmer. When the DSC is operating in the full-duplex mode, the dial order from the IOP must be presented on the odd-numbered input/output address channel. If the dial order is presented on the evennumbered input/output address channel with the full-duplex feature installed, a channel end will occur. If the local data set is busy or the connection to the remote terminal is not completed when the dial order is initiated, an unusual end will also occur.

#### 2-10 READ ORDER

Table 2-4 illustrates the read order that causes the DSC to assemble bits received from the data set into bytes which are then forwarded to computer memory. In the synchronous mode of operation the C field of the read order specifies the number of bits to be assembled per computer memory byte. A value of 000 in the C field signifies that eight bits per byte are to be read. Values of 010 through 111 (count 001 is not allowed) in the C field correspond to two through seven bits per byte respectively. That is, count 010 will cause data line 6 (DA6) and data line 7 (DA7) to contain data. All unused bits will contain zeros.

In the asynchronous mode of operation, the C field of the write order is ignored. The number of bits assembled into a byte is determined by the format unit installed in the DSC. All unused data bits will contain binary ones. Channel end is reported if count done occurs, end-of-text character is received, or end-of-text character plus one is received.

### 2-11 ENABLE RING DETECT ORDER

The enable ring detect order (table 2-4) enables the DSC to generate a device interrupt when the carrier detect signal from the data set is on. Thus, before transmission actually commences, the computer can be interrupted when dialed via the switched network. If the full-duplex feature is installed, the enable ring detect order is only accepted by the DSC on the even-numbered input/output address channel.

#### 2-12 DISABLE RING DETECT ORDER

The disable ring detect order (table 2-4) prevents a device interrupt from occurring when the carrier detect signal from the data set is on by disabling the ring detect circuit. The ring detect circuit is also disabled by the HIO and input/ output reset signals. If the full-duplex feature is installed, the disable ring detect order is only accepted by the DSC on the even-numbered input/output address channel.

#### 2-13 DISCONNECT CALL ORDER

The disconnect call order described in table 2-4 disconnects the local data set from the switched telephone network and terminates all dialed calls. If the full-duplex feature is installed, the disconnect call order is accepted by the DSC on either the odd or the even-numbered input/output address channel.

#### 2-14 GENERATE LONG SPACE ORDER

The generate long space order detailed in table 2-4 applies to asynchronous format units only. When this order is issued, it causes the DSC to generate long spaces. The byte count determines how many continuous long space characters are transmitted. (Long-space characters are defined as continuously transmitted zero characters without intervening stop bits.) If the generate long space order is received during synchronous mode of operation, channel end is reported and the DSC will not generate long space.

### 2-15 INPUT ORDERS

Table 2-5 presents the information supplied by the DSC to the IOP in response to input orders.

#### 2-16 TERMINAL ORDER

Table 2-6 gives the response of the DSC to a terminal order (TO).

### 2-17 FORMAT UNITS

The basic DSC does not include a format unit. However, each basic DSC is prewired to accept different format units. This arrangement allows the basic DSC to accommodate a

| STATUS             |   |   | ۵ | ATA | LINES | 5 |   |   | CONDITION                                                                                                         |

|--------------------|---|---|---|-----|-------|---|---|---|-------------------------------------------------------------------------------------------------------------------|

|                    | 0 | 1 | 2 | 3   | 4     | 5 | 6 | 7 |                                                                                                                   |

| Transmission error | 1 |   |   |     |       |   |   |   | Transmission error has occurred during a read<br>or write operation (cannot occur during asyn-<br>chronous write) |

| Incorrect length   |   | 0 |   |     |       |   |   |   | Not applicable                                                                                                    |

| Chaining modifier  |   |   | 0 |     |       |   |   |   | Not applicable                                                                                                    |

| Channel end        |   |   |   | 1   |       |   |   |   | Input/output operations are terminated                                                                            |

| Unusual end        |   |   |   |     | 1     |   |   |   | Unusual end is reported if any of the follow-<br>ing conditions exists:                                           |

| · · · · ·          |   |   |   |     |       |   |   |   | a. The data set ready signal goes off during a read or write operation                                            |

|                    |   |   |   |     |       |   |   |   | b. An IOP halt signal is received during a terminal order                                                         |

|                    |   |   |   |     |       |   |   |   | c. A transmission rate error occurs during a read or write operation                                              |

|                    |   |   |   |     |       |   |   |   | d. A dial order is attempted and dialing option is not available                                                  |

|                    |   |   |   |     |       |   |   |   | e. Line is occupied and dialing operation is attempted                                                            |

|                    |   |   |   |     |       |   |   |   | f. Dialing operation is not completed                                                                             |

|                    |   |   |   |     |       |   |   |   | g. The clear to send signal goes off dur-<br>ing a write operation                                                |

| Unused bits        |   |   |   |     |       | 0 | 0 | 0 |                                                                                                                   |

|                    |   |   |   |     |       |   |   |   |                                                                                                                   |

# Table 2-5. Information Supplied by Data Set Controller During Order Input

| STATUS INDICATOR        |   |   |   | ATA | LINES |   |   | _ | RESPONSE                                                                                                                |

|-------------------------|---|---|---|-----|-------|---|---|---|-------------------------------------------------------------------------------------------------------------------------|

|                         | 0 | 1 | 2 | 3   | 4     | 5 | 6 | 7 |                                                                                                                         |

| Interrupt<br>Count done | 1 | 1 |   |     |       |   |   |   | DSC causes an interrupt call<br>DSC completes input/output operation, reports<br>channel end, and enters not busy state |

|                  | DATA LINES |   |   |   |   |   |   |   | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                      |  |  |

|------------------|------------|---|---|---|---|---|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| STATUS INDICATOR | 0          | 1 | 2 | 3 | 4 | 5 | 6 | 7 | RESPONSE                                                                                                                                                                                                                                                                   |  |  |

| Command chain    |            |   | 1 |   |   |   |   |   | Senses command chain following reporting of<br>channel end. Causes DSC to request a new<br>order. Command chaining during synchronous<br>receive causes DSC to search for a minimum of<br>two more synchronizing characters before<br>transferring data to computer memory |  |  |

| IOP halt         |            |   |   | 1 |   |   |   |   | DSC immediately reports unusual end and enters not busy state                                                                                                                                                                                                              |  |  |

| Unused bits      |            |   |   |   | 0 | 0 | 0 | 0 |                                                                                                                                                                                                                                                                            |  |  |

Table 2-6. Data Set Controller Response to Terminal Orders (Cont.)

wide variety of remote terminal devices. Selection of a format unit is determined by the remote input/output terminal device that is to communicate with the DSC. If the DSC is to communicate with an asynchronous data set, an asynchronous format unit is installed in the DSC; if with a synchronous data set, a synchronous unit is installed. Table 2-7 lists the standard format units along with the speeds, format unit modules, data sets, crystals, and typical terminal devices required for each format unit. Table 2-8 gives the various data sets and dialing units along with a brief description of each.

#### 2-18 ASYNCHRONOUS UNITS

When the asynchronous data format unit is installed in the DSC, the DSC communicates with an asynchronous data set. In this configuration, the rate at which data is transmitted and received is determined by the DSC, because the data set does not supply timing pulses for data transmission or reception. For this reason, all data is transmitted and received in a preselected format having a group of data bits preceded by a start pulse (space) and followed by one or more stop pulses (mark). Four data formats are available as options on the DSC:

Format 1: 5-7.5. This format consists of five data bits preceded by one start pulse and followed by 1.5 stop pulses.

Format 2: 7–9. This format consists of seven data bits preceded by one start pulse and followed by one stop pulse.

Format 3: 8–10. This format consists of eight data bits preceded by one start pulse and followed by one stop pulse.

Format 4: 8-11. This format consists of eight data bits preceded by one start pulse and followed by two stop pulses.

#### 2-19 SYNCHRONOUS UNITS

In the synchronous mode of operation, the DSC communicates with a synchronous data set. The synchronous data set supplies the clock timing pulses that determine the data transmission and reception rate. With the data set supplying the clock timing pulses, the DSC transmits and receives data in a backto-back fashion. Thus, all data bits transferred from the DSC are in synchronization with the data set clock. For a more detailed description of the synchronous format unit see paragraph 3-2.

When communicating in synchronous mode, from two to eight bits can be accumulated in each data word. When transferring data via a synchronous data set, at least four start-of-transmission characters must be transferred at the beginning of each message sent, along with an endof-transmission character at the end of the message. The start-of-transmission characters allow the remote device to synchronize with the incoming data. The end-of-transmission character notifies the remote device that the last of the data has been transmitted.

| SPEED CRYSTAL DATA SET TYPICAL REMOTE DEVICE CONTRO<br>Send Receive Timing                    | OLLED |

|-----------------------------------------------------------------------------------------------|-------|

| 60 wpm LT47 LT51 CT17 128131-010 103A, 103F Teletype Models 28 and 32                         |       |

| 66 wpm LT47 LT51 CT17 128131-011 103A, 103F Teletype Models 28 and 32                         |       |

| 75 wpm LT47 LT51 CT17 128131-012 103A, 103F Teletype Models 28 and 32                         |       |

| 100 wpm LT47 LT51 CT17 128131-018 103A, 103F Teletype Models 28 and 32                        |       |

| 148 wpm LT48 LT52 CT17 128131-013 103A, 103F IBM 1050                                         |       |

| 150 wpm LT49 LT53 CT17 128131-015 103A, 103F Multipurpose keyboard display, Telet<br>Model 37 | уре   |

| 1200 wpm LT49 LT53 CT17 128131-015 202C, 202D Multipurpose keyboard display                   |       |

| 1800 wpm LT49 LT53 CT17 128131-012 202C, 202D Multipurpose keyboard display                   |       |

| 100 wpm LT50 LT54 CT17 128131-014 103A, 103F Teletype Models 33, 35                           |       |

| 2000 bit/s LT83 LT83 None None 201A General purpose, medium speed devi                        | ces   |

| 2400 bit/s LT83 LT83 None None 201B General purpose, medium speed devi                        | ces   |

| 40800 bit/s LT83 LT83 None None 301B General purpose, high speed devices                      |       |

| 19.2 kilobit/s LT83 LT83 None None 303 General purpose, high speed devices                    |       |

| 50.0 kilobit/s LT83 LT83 None None 303 General purpose, high speed devices                    |       |

| 230.0 kilobit/s LT83 LT83 None None 302 General purpose, high speed devices                   |       |

|                                                                                               |       |

|                                                                                               |       |

2-9

DATA FORMAT

5 level/7.5 unit

5 level/7.5 unit

5 level/7.5 unit

5 level/7.5 unit

7 level/9 unit

8 level/10 unit

8 level/10 unit

8 level/10 unit

8 level/11 unit

2 to 8 level,

synchronous

synchronous

synchronous

synchronous

synchronous

synchronous

| Data Set/Dialing<br>Unit Designation | Maximum Data<br>Rate Bit/s | Used With<br>Auto-Dial       | Clocking       | Full–Duplex<br>Capability | Typical Service                                      | Remarks                                                                                     |