## **SDS SIGMA 5/7** HIGH-SPEED RAD STORAGE SYSTEM MODELS 7211/7212

**Reference Manual**

# **HIGH-SPEED RAD ORDER CODES**

| Code<br>(Hexadecimal) | Function                                                                                                          |

|-----------------------|-------------------------------------------------------------------------------------------------------------------|

| 01                    | Write                                                                                                             |

| 02                    | Read (Report any transmission error at "count done")                                                              |

| 03                    | Seek                                                                                                              |

| 04                    | Sense                                                                                                             |

| 05                    | Check-write                                                                                                       |

| 12                    | Read (Terminate data transfer and report any transmission error at end of current sector if error is encountered) |

# **HIGH-SPEED RAD STORAGE SYSTEM**

# MODELS 7211/7212

# **REFERENCE MANUAL**

for

# SDS SIGMA 5/7 COMPUTERS

PRELIMINARY EDITION

90 09 80A

June 1968

SCIENTIFIC DATA SYSTEMS/1649 Seventeenth Street/Santa Monica, California

# **RELATED PUBLICATIONS**

| Title                                                 | Publication No. |

|-------------------------------------------------------|-----------------|

| SDS Sigma 5 Computer Reference Manual                 | 90 09 59        |

| SDS Sigma 7 Computer Reference Manual                 | 90 09 50        |

| SDS Sigma 5/7 Symbol and Meta-Symbol Reference Manual | 90 09 52        |

ALL SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE

# CONTENTS

| 1. | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                  |

| 2. | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                                                                  |

|    | Data Presentation<br>RAD States<br>Operational States<br>Transitions Between States                                                                                                                                                                                                                                                                                                                                                                             | 2<br>2                                                             |

|    | Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                                                                  |

| 3. | PROGRAM INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                                                                  |

|    | RAD Orders    Addressing Format      Addressing Format    Start Input/Output      Start Input/Output    Output      Unusual End Conditions    Channel End Conditions      Fault Conditions    Fault Conditions      Transmission Error Conditions    Incorrect Length Conditions      Incorrect Length Conditions    Incorrect Length Conditions      I/O Instruction Status Bits    Device Status Byte      Operational Status Bute    Operational Status Bute | 4    4    4    4    4    4    4    4    4    4    4    4    4    5 |

|    | Operational Status Byte                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6                                                                  |

| Programming Considerations | 6 |

|----------------------------|---|

| Information Protection     | 6 |

| Sequence of Activity       | 6 |

## **APPENDIX**

Sigma 5/7 Programming Example

12

# ILLUSTRATIONS

|    | Model 7212 Storage Unit                   | _ iv |

|----|-------------------------------------------|------|

|    | High-Speed RAD Interior View              | _ iv |

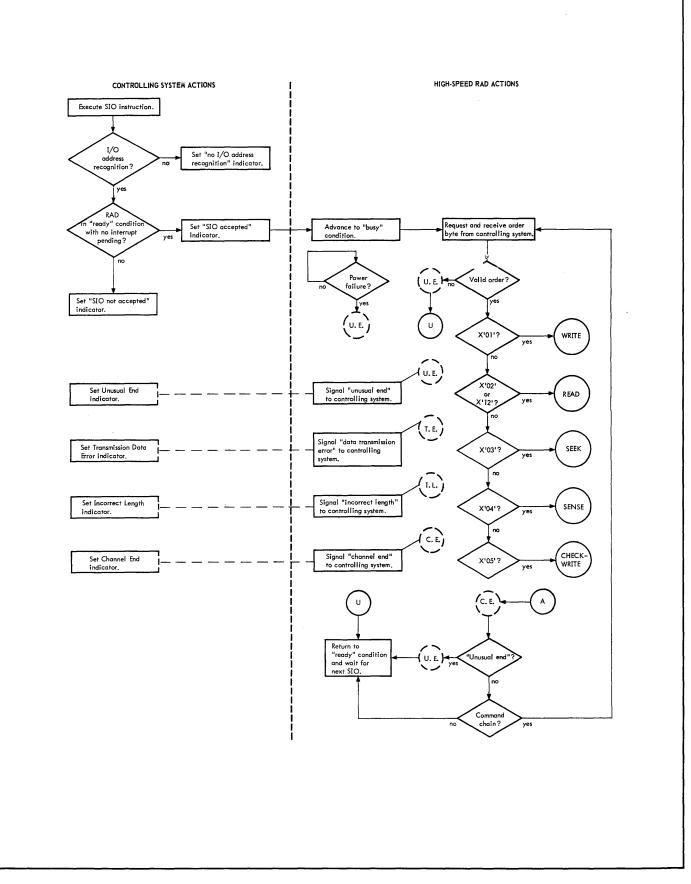

| 1. | Controlling System/High-Speed RAD Actions | _ 7  |

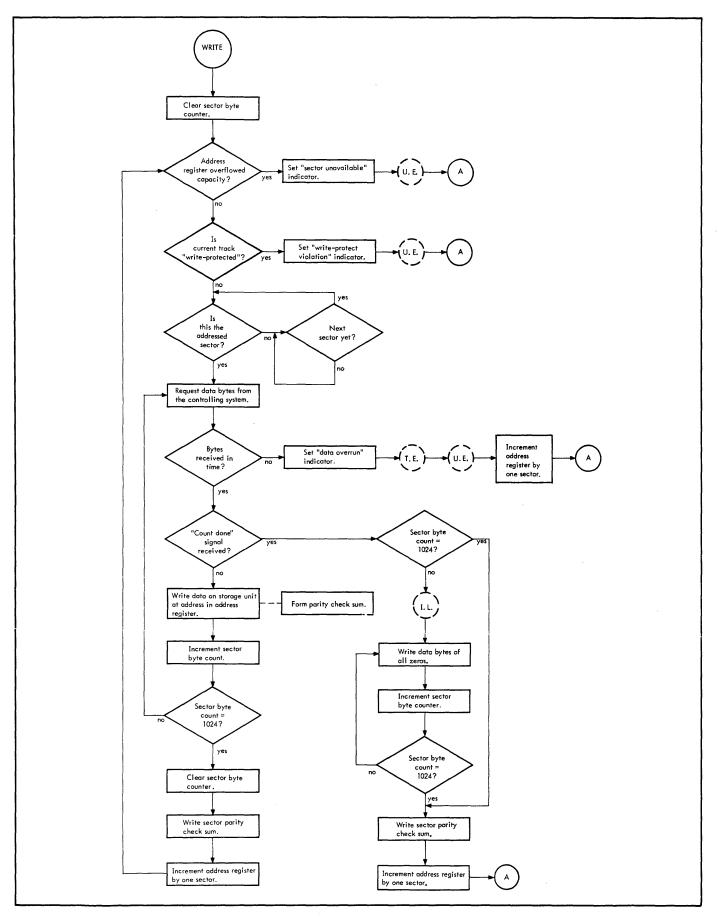

| 2. | Write Order RAD Actions                   | _ 8  |

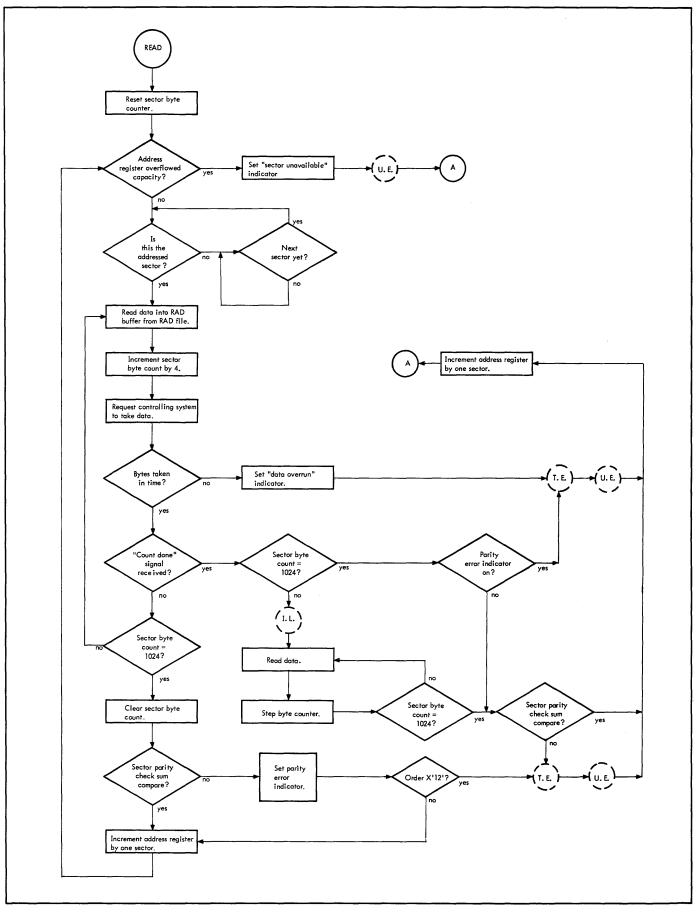

|    | Read Order RAD Actions                    |      |

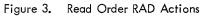

| 4. | Seek/Sense Order RAD Actions              | _ 10 |

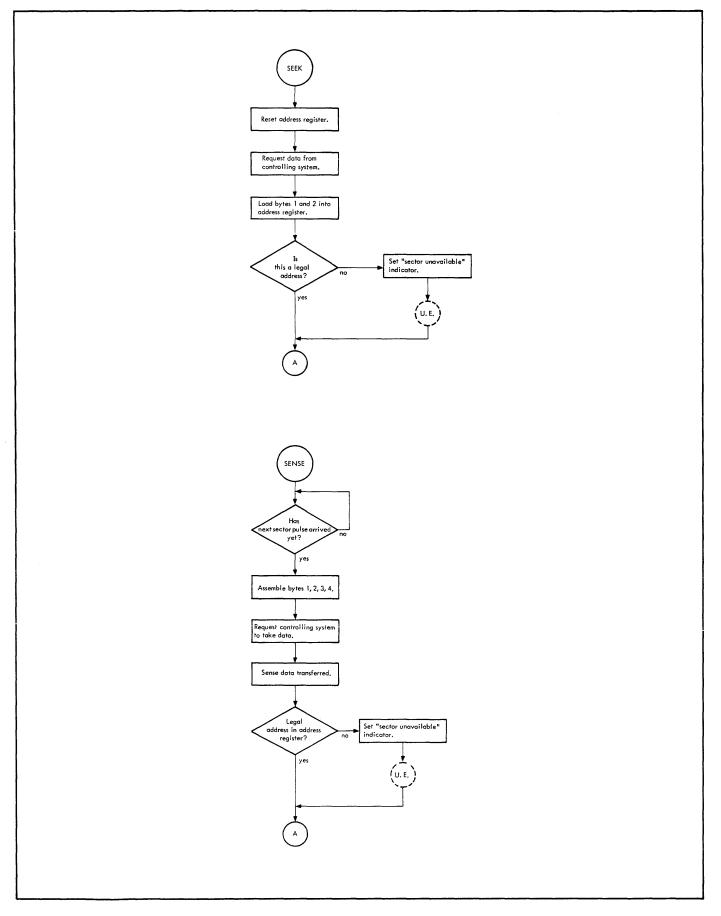

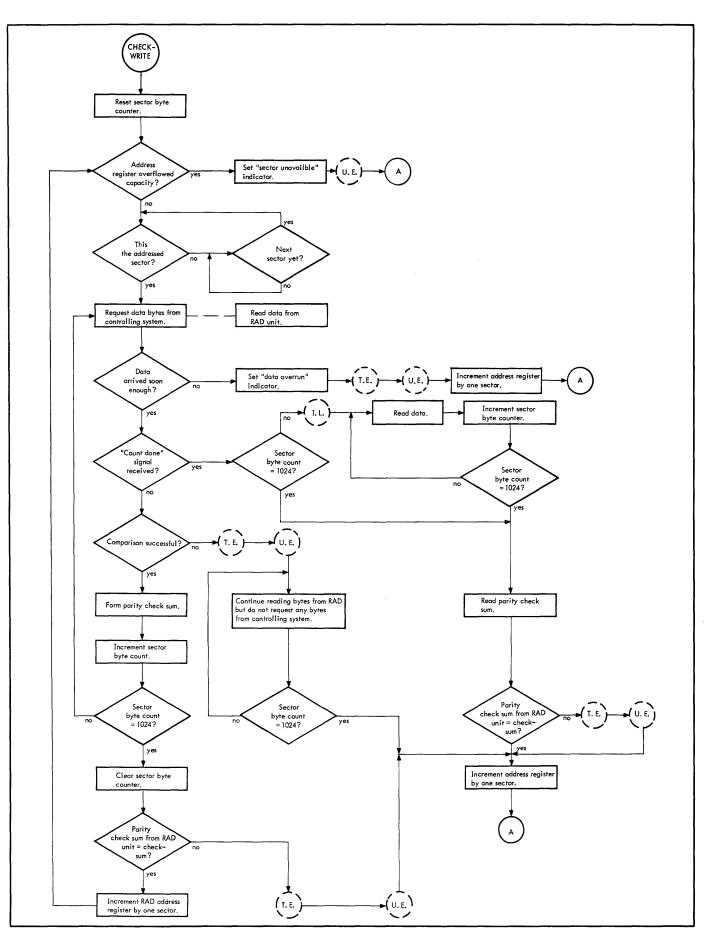

| 5. | Check-write Order RAD Actions             | _11  |

|    |                                           |      |

# TABLES

| 1. | Specifications                         | 1 |

|----|----------------------------------------|---|

| 2. | RAD Controller State Transitions       | 2 |

| 3. | RAD I/O Instruction Execution Response | 5 |

Model 7212 Storage Unit

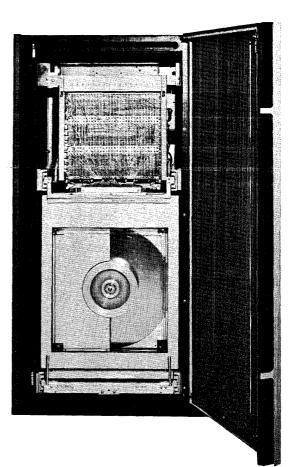

High-Speed RAD Interior View

# **1. GENERAL DESCRIPTION**

#### INTRODUCTION

Model 7211/7212 Rapid Access Data (RAD) Storage System provides fast, auxiliary, random-access memory for SDS Sigma 5/7 computers. RAD units may be used for system, scratch pad, or working storage for processing programs. In a time-sharing system, they may serve as permanent file storage, "swap" storage, and as a medium for storing realtime programs.

A high-speed RAD system consists of one Model 7211 Controller and one to four storage units, Model 7212. Model 7211 Controller connects to a Sigma Selector Input/Output Processor (SIOP). Multiple 7211s can be installed in a Sigma system. Each storage unit is housed in a separate cabinet. The controller is housed separately from the storage units.

The basic addressable unit of information is a sector of 1024 data bytes. There are 82 sectors to each band. A RAD unit has 64 bands (8 tracks/band). Data is presented in four 8-bit bytes to the RAD by the controlling system, and each byte is written in parallel on the selected sector. Access time is minimal because each band has separate read/write heads (average access time is 17 milliseconds).

Rotational delay may be reduced by sensing the unit's current position before initiating an input or output operation and then transferring data beginning immediately at the next sector to be accessed. If desired, a data record can overlap from sector to sector or from band to band; the RAD controller automatically performs sector and band incrementing.

The contents of RAD storage units are permanently protected against primary power failure. Also, "write-protect" switches prevent inadvertent destruction of recorded information due to programming error. Each switch inhibits writing on 4 adjacent bands.

The term "RAD" in this manual indicates a device controller and storage unit. Any separate reference is specified by "controller" or "storage unit".

To use this manual effectively, the reader should be familiar with the Sigma Computer Reference Manual (see Related Publications, page ii) applicable to his installation (particularly the input/output instructions and input/output operations sections).

#### Table 1. Specifications

| Operating Characteristics |                                                                                     |  |  |

|---------------------------|-------------------------------------------------------------------------------------|--|--|

| RAD file rotational speed | 1774 rpm                                                                            |  |  |

| Total time per revolution | 33.8 milliseconds                                                                   |  |  |

| Inter-sector gap time     | 42 microseconds                                                                     |  |  |

| Sector-to-sector time     | 413 microseconds                                                                    |  |  |

| Read/write format         | Byte (8–bit) parallel                                                               |  |  |

| Byte transfer rate        |                                                                                     |  |  |

| Single sector             | 3,000,000 bytes/second                                                              |  |  |

| Multiple sectors          | 2,470,000 bytes/second                                                              |  |  |

| Byte capacity             | 5,373,952 bytes (64 bands,<br>82 sectors/band, 1024<br>bytes/sector)                |  |  |

| Write protection          | 16 independent switches.<br>Each switch protects a group<br>of 4 consecutive bands. |  |  |

| Physical                  | Dimensions                                                                          |  |  |

| Height                    | 63 in.                                                                              |  |  |

| Width                     | 30 in.                                                                              |  |  |

| Depth                     | 29 in.                                                                              |  |  |

| Weight (7211/7212)        | 1600 lb (approx.)                                                                   |  |  |

| Environmento              | al Characteristics                                                                  |  |  |

| Power requirements        |                                                                                     |  |  |

| Service                   | 208 vac ± 10%,<br>60 ± 0.5 Hz, 3-phase                                              |  |  |

| Start                     | 7 kva                                                                               |  |  |

| Run                       | Controller — 300 watts<br>Storage unit — 2000 watts                                 |  |  |

| Ambient temperature       | 50° to 105° F.                                                                      |  |  |

| Operating humidity        | 10% to 90%                                                                          |  |  |

# 2. FUNCTIONAL DESCRIPTION

#### DATA PRESENTATION

Data is presented to the RAD system four bytes at a time, and is written byte-serially on the designated band and sector. Similarly, bytes read from the disc are assembled into four 8-bit groups for presentation to the controlling system. (See "RAD Orders" and "Addressing Format".)

#### **RAD STATES**

The RAD's initial operational state depends on its power status. If all power is off, it is removed from the line ("not operational" state). Any attempt to access it results in a response of "No I/O address recognition" to the I/O instruction. The status response, if requested, is unpredictable under these conditions.

#### OPERATIONAL STATES

When required power is on, the RAD enters the "automatic" mode and the "ready" condition. The exact RAD condition may be determined by examining the status response to one of the instructions, START INPUT/OUTPUT (SIO), HALT INPUT/OUTPUT (HIO), or TEST INPUT/OUTPUT (TIO). Other I/O instructions, TEST DEVICE (TDV) and ACKNOWL-EDGE INPUT/OUTPUT INTERRUPT (AIO), provide addi-tional specific status indications (see "RAD Status Response"). A brief explanation of RAD conditions and modes follows.

#### CONDITIONS

<u>Ready</u>. The "ready" condition is entered when required power is initially turned on. In this condition, an SIO instruction can be accepted by the RAD controller and executed, provided that no interrupt is pending.

Busy. In this condition, the RAD controller has already accepted an SIO instruction. A new SIO will not be accepted until the current operation is completed and no device interrupt is pending.

#### MODES

Automatic. The RAD is in the "automatic" mode as long as required power is on ("ready-automatic" or "busyautomatic").

#### TRANSITIONS BETWEEN STATES

Table 2 summarizes the allowable state transitions and the conditions required to cause them.

| Next<br>State<br>Present<br>State | Not<br>Operational     | Ready<br>Automatic                                                       | Busý<br>Automatic             |

|-----------------------------------|------------------------|--------------------------------------------------------------------------|-------------------------------|

| Not<br>Operational                |                        | Power is<br>turned on                                                    | Not<br>possible               |

| Ready<br>Automatic                | Power is<br>turned off |                                                                          | SIO has<br>been ac-<br>cepted |

| Busy<br>Automatic                 | Power is<br>turned off | Operation<br>completed,<br>or HIO, or<br>I/O reset<br>signal<br>received |                               |

#### Table 2. RAD Controller State Transitions

#### **DATA TRANSFER**

A RAD operation is initiated by the controlling system with a START INPUT/OUTPUT OPERATION (SIO) instruction if all the following conditions are satisfied:

- 1. Input/output address recognition (i.e., addressed device exists).

- 2. The RAD is in the "ready" condition.

- 3. No RAD interrupt is pending.

If these are satisfied, the RAD enters the "busy" condition. The RAD controller now initiates the transfer of data to or from the RAD storage unit as specified by the order (Write or Read) until the required number of bytes have been transferred. The operation then terminates, and the RAD returns to the "ready-automatic" state. The operation may also be terminated:

- 1. By an Input/Output Processor (IOP) Halt, generated by the IOP on certain error conditions (in which case all data may not have been transferred).

- 2. By a HALT I/O (HIO) instruction (in which case all data may not have been transferred).

Following an HIO or IOP Halt, the RAD is in a "readyautomatic" state.

# 3. PROGRAM INTERFACE

write

#### **RAD ORDERS**

The RAD contains an address register that selects the band and sector to be accessed. This register is initially loaded by executing a Seek order. During a data transfer, if more bytes are transferred than can be contained in one sector (1024 bytes), the address register is automatically incremented so that the next sector is addressed. The address register is cleared by means of the I/O RESET switch. An error results, however, if the address register is incremented when addressing the last available sector. This error condition also occurs if a programmer tries to use a Seek order to load the address register with a nonexistent band or sector address.

Upon completion of a data transfer, the address register is incremented so that it addresses the sector following the last one involved in the data transfer.

During a write operation, each byte received is summed to form a parity check sum. This sum is always written in the last 4 byte positions of the sector, even if less than 1024 bytes are transmitted. During a read operation, the data is summed as it is read, and the result is compared with the parity check sum. Failure to compare results in an error condition.

The six valid orders are:

| Order | Action |

|-------|--------|

|       |        |

X'01' Write

The Write order causes the RAD unit to record the number of bytes specified in the command doubleword, starting at the band and sector address currently selected by the RAD controller address register (this address is specified by the previous Seek order or the last sector involved in the data transfer incremented by one). Transmission continues until the computer indicates to the storage unit that the entire record has been transferred. If the transmitted information does not completely fill the last sector, zeros are written into the remainder of the sector. If a write operation is attempted in a protected area, the operation is not performed and the condition is immediately reported to the controlling system (see "Addressing Format" and "RAD Status Response" in this section).

X'02' Read This Read order causes the RAD to read the bytes specified in the command doubleword, starting at the band and sector address currently selected by the RAD controller address register (this address is specified by the previous Seek order or the last sector involved in the data transfer incremented by one). The data is stored in core memory

| Order      | Action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | beginning at the location specified by the<br>command doubleword. Any transmission<br>errors are signalled at the end of the logi–<br>cal record.                                                                                                                                                                                                                                                                                                                                                        |

| X'12' Read | This Read order reads the number of bytes<br>specified in the command doubleword from<br>the band and sector currently selected by<br>the RAD controller address register (this ad-<br>dress is specified by the previous Seek or-<br>der or the last sector involved in the data<br>transfer incremented by one). The data is<br>stored in core memory starting at the loca-<br>tion specified by the command doubleword.<br>Any transmission errors are signalled at the<br>end of the failing sector. |

| X'03' Seek | The Seek order causes two bytes to be sent<br>to the RAD where they are loaded into the<br>RAD controller address register. The con-<br>troller then directs any subsequent read/                                                                                                                                                                                                                                                                                                                        |

byte count of 2 should be specified in the I/O doubleword associated with the Seek order. X'04' Sense The Sense order causes the storage unit to transmit four bytes of position and status information into core memory. The first two bytes are the contents of the RAD address register currently stored in the controller. The first bit of the first byte indicates whether the band associated with the current band address is "write-protected". The third byte indicates the current rotational position of the last unit addressed. The fourth byte indicates which of the 8 tracks has detected a parity or check-write error. A byte count of 4 should be specified in the I/O doubleword associated with the Sense order.

write operation to begin at this address. A

The Sense order also causes a sector unavailable error if the address register has incremented beyond the last available sector.

X'05' Check-The Check-write order is used to verify recorded data. It causes data to be sent to the RAD controller by the controlling system where it is compared with that being read from the RAD. In the event that a byte does not compare, a "transmission error" signal is transmitted to the controlling system at the end of the current sector, and the data transfer is terminated. Data on the RAD and in core storage are not recorded or modified, but only compared.

#### ADDRESSING FORMAT

The format of the two bytes sent to the RAD by a Seek order is:

| Byte 1 |      | Byte 2 |   |

|--------|------|--------|---|

|        | Band | Sector |   |

| 0      | 7    | 01     | 7 |

The format of the four bytes received on a Sense order is:

| Byte | e 1  | Byte 2 | Byte | 3 E   | Byte 4    |

|------|------|--------|------|-------|-----------|

| s    | Band | Sector | Curr | i Fau | ing track |

| 0123 | 7'0  | 1      | 701  | 7'0   | 7         |

where

- S is the setting of the write-protect switch for the indicated band (0=not write-protected; 1=write-protected).

- Band is the band number currently contained in the RAD controller address register.

- Sector is the sector number currently contained in the RAD controller address register.

- Current sector is the current sector position (rotational) of the RAD.

- Failing track bits 0-7 indicate that tracks 0-7, respectively, have failed (1=error).

#### **KEY EVENTS**

The key events that occur during a RAD operation are described in the following paragraphs. No chronological order of occurrence should be assumed from the order of presentation.

#### START INPUT/OUTPUT

A RAD operation is initiated with the execution of an SIO instruction by the controlling system. If I/O address recognition exists and the RAD is in the "ready" condition with no interrupt pending, the controlling system sets its "I/O address recognition" and "SIO accepted" indicators. The RAD then advances from the "ready" to the "busy" condition. It then requests an order byte from the controlling system and proceeds with the operation defined by the order byte.

#### UNUSUAL END CONDITIONS

Detecting any of the following conditions after receiving an order causes the RAD to return an "unusual end" indication to the controlling system when the condition occurs:

- 1. Invalid order code

- 2. Power failure in the addressed unit

- 3. Incrementing the RAD controller address register beyond the last available sector in the current RAD unit

- 4. Nonexistent "Seek" address

- 5. Attempting to write on a write-protected band

- 6. Transmission data error

#### CHANNEL END CONDITIONS

After receiving an order from the controlling system, the RAD signals "channel end" to the controlling system when all data has been transferred or when an "unusual end" condition occurs while a data transfer is in process.

#### FAULT CONDITIONS

A fault condition is any condition that causes a peripheral device to become "not operational". Absence or failure of ac or dc power causes the RAD to become "not operational".

#### TRANSMISSION ERROR CONDITIONS

The RAD can detect and report transmission errors to the controlling system. Conditions causing this error are:

- 1. Failure of end of sector parity check during a "read".

- Failure of a data comparison on a "check-write" (the parity byte is also automatically compared).

- A data overrun: the controlling system has failed to maintain the data transfer rate required by the RAD during the execution of the previous Read, Write, or Check-write order.

#### INCORRECT LENGTH CONDITIONS

The RAD can detect and report incorrect length errors to the controlling system. Conditions causing this error are:

- 1. A byte count greater than 4 has been specified in the I/O doubleword associated with a Seek order.

- 2. A byte count greater than 4 has been specified in the I/O doubleword associated with a Sense order.

- 3. The last Read, Write, or Check-write order did not specify a count that was an integral multiple of 1024 bytes.

#### **RAD STATUS RESPONSE**

The RAD system returns various status flags in response to computer-executed I/O instructions. A detailed explanation of the I/O instructions and their status information is contained in the reference manuals for Sigma computers. The following paragraphs explain the significance of each status flag returned to the controlling system.

#### I/O INSTRUCTION STATUS BITS<sup>†</sup>

The execution of an I/O instruction by the controlling system provides two bits of immediate information pertaining

<sup>&</sup>lt;sup>t</sup>When the RAD (or Selector IOP) is "busy", SIO, TIO, or TDV instructions addressed to the RAD will be "partially executed" (i.e., only condition codes are stored – status information is not updated) with the condition codes CC 1 and CC 2 returned as "10".

to the general status of the addressed I/O device and its controller. This information is retained by the controlling system in a form that allows for conditional branching based on the response of the device (and its controller) to the I/O instruction. Table 3 lists the possible status bit settings provided by the execution of each I/O instruction and the significance of each setting.

#### DEVICE STATUS BYTE

The following eight bits of information are made available to the controlling system in response to the execution of an I/O instruction.

#### STATUS RESPONSE FOR SIO, TIO, AND HIO

Bit 0: Device Interrupt Pending. If this bit is a 1, an interrupt call is pending (issued but not yet acknowledged by an AIO instruction). The RAD continues to transmit data (if specified) until the current operation is completed (all data transferred or operation terminated due to an error condition), but does not accept a new SIO instruction until this interrupt has been acknowledged. However, a new order can be accepted, if command chaining is specified, even though an interrupt may be pending. The interrupt may be cleared by executing an AIO or HIO instruction.

<u>Bits 1-2: RAD Storage Unit Condition</u>. The RAD storage unit condition is indicated by these bits:

| Flags | Condition |

|-------|-----------|

|       |           |

- 00 RAD Ready The RAD storage unit is inactive, i.e., it is not engaged in a data transfer operation.

- 01 RAD Not Operational Power is not applied to the RAD storage unit or it is off-line for testing purposes.

|             | Cond<br>Code | ition | Address/<br>Interrupt | Operation       | Status<br>Returned to |                                                                             |

|-------------|--------------|-------|-----------------------|-----------------|-----------------------|-----------------------------------------------------------------------------|

| Instruction | CC 1         | CC 2  | Recognition           | Accepted        | CPU Registers         | Significance                                                                |

| SIO         | 0            | 0     | Yes                   | Yes             | Yes                   | Device was "ready", now "busy".                                             |

|             | 0            | 1     | Yes                   | No              | Yes                   | Device was "not ready".                                                     |

|             | 1            | 0     | Yes                   | No <sup>t</sup> | No                    | Selector IOP was "busy".                                                    |

|             | 1            | 1     | No                    | No              | No                    | I/O address not recognized.                                                 |

| HIO         | 0            | 0     | Yes                   | Yes             | Yes                   | Device (and selector IOP) was "not busy"                                    |

|             | 0            | 1     | Yes                   | Yes             | Yes                   | Device (and/or selector IOP) was "busy".                                    |

|             | 1            | 0     | No                    | No              | No                    | Invalid code.                                                               |

|             | 1            | 1     | No                    | No              | No                    | I/O address not recognized.                                                 |

| TIO         | 0            | 0     | Yes                   | Yes             | Yes                   | Device is "ready".                                                          |

|             | 0            | 1     | Yes                   | Yes             | Yes                   | Device is "not ready".                                                      |

|             | 1            | 0     | Yes                   | No <sup>t</sup> | No                    | Selector IOP is "busy".                                                     |

|             | 1            | 1     | No                    | No              | No                    | I/O address not recognized.                                                 |

| TDV         | 0            | 0     | Yes                   | Yes             | Yes                   | Previous operation was not terminated because of a "fault" condition.       |

|             | 0            | 1     | Yes                   | Yes             | Yes                   | Previous operation was terminated because of a "fault" condition.           |

|             | 1            | 0     | Yes                   | No <sup>t</sup> | No                    | Selector IOP is "busy".                                                     |

|             | 1            | 1     | No                    | No              | No                    | I/O address not recognized.                                                 |

| AIO         | 0            | 0     | Yes                   | Yes             | Yes                   | Normal interrupt (i.e., "channel end"<br>or "zero byte count") recognition. |

|             | 0            | 1     | Yes                   | Yes             | Yes                   | Abnormal interrupt (i.e., "fault")<br>recognition.                          |

|             | 1            | 0     | No                    | No              | No                    | Invalid code.                                                               |

|             | 1            | 1     | No                    | No              | No                    | No interrupt recognition.                                                   |

Table 3. RAD I/O Instruction Execution Response

#### Flags Condition

### **PROGRAMMING CONSIDERATIONS**

- 10 Device Unavailable This condition is not applicable to the RAD.

- RAD Busy The RAD storage unit is currently active,

i.e., it is engaged in a data transfer operation through the controller.

Bit 3: Mode-Automatic or Manual. This bit is always a 1, indicating "automatic" mode.

<u>Bit 4: Device Unusual End.</u> This bit is a 1 if the previous operation terminated due to an abnormal condition, as listed under "Unusual End Conditions".

Bits 5-6: RAD Controller Condition. The RAD controller condition is indicated by these bits:

#### Flags Condition

- 00 RAD Controller Ready The RAD Controller is capable of accepting an SIO instruction, if no interrupt is pending (and no storage unit is busy).

- 01 Device Controller Not Operational This condition is not applicable to the RAD.

- 10 Device Controller Unavailable This condition is not applicable to the RAD.

- 11 RAD Controller Busy The RAD controller is currently executing a previous order (one storage unit is also busy).

<u>Bit 7: Unassigned.</u> This bit is currently unassigned and is always reset to 0.

#### STATUS RESPONSE FOR TDV AND AIO

<u>Bit 0: Data Overrun</u>. If this bit is a 1, a data overrun has occurred during execution of the previous order (see "Transmission Error Conditions").

<u>Bit 1: Unassigned.</u> This bit is currently unassigned and is always reset to 0.

<u>Bit 2: Sector Unavailable.</u> If this bit is a 1, the RAD controller address register was incremented beyond the last available sector during the previous order, or a Seek order loaded the RAD controller address register with a value greater than the last available sector or a Sense order was issued and the previous data transfer accessed the last available sector of the file.

<u>Bit 3: Write-protect Violation.</u> If this bit is a 1, the previous Write order attempted to write on a band that was write-protected.

Bits 4-7: Unassigned. These bits are currently unassigned and are always reset to zeros.

#### OPERATIONAL STATUS BYTE

In addition to the information contained in the Device Status Byte, there are other indicators, bits 8–15 in the Operational Status Byte, made available to the controlling system at the conclusion of each operation. See the table "Status Bits for I/O Instructions" in the applicable Sigma Computer Reference Manual. This RAD system is designed to permit band switching and/or order modification (read to write and vice-versa) during the gap between sectors. The command chaining feature of the I/O system must be used instead of separate SIO instructions to perform this order modification or band switching.

Since this system operates at data rates approaching the maximum that can be handled by the Selector IOP and the central processor memory, special programming precautions should be taken to minimize the chance of data overruns. Frequent use of data or command chaining, or of test instruction loops and certain other I/O instructions, causes a reduction of the effective RAD data transfer rate due to the additional communication between the I/O system and the central processor or memory.

To ensure a minimum probability of overruns, the following programming restrictions should be observed:

- Data chaining without zero count interrupts will be no more frequent than once every 512 bytes (approximately 175 microseconds).

- Data chaining with zero count interrupts will be no more frequent than once every 5/2 + 3(T-40) bytes, where T is the central processor response time to that interrupt in microseconds.

- 3. Data chaining with zero count interrupts earlier than 200 bytes (approximately 70 microseconds) after the beginning of a transfer is not allowed.

- 4. HIO instructions should not be issued to, nor interrupt requests generated by, other device controllers attached to the RAD's Selector IOP.

When "immediate" mode transfer techniques are used (data transmission at the next available sector) the programmer must add 1 to the sector number received as a result of the Sense order. This procedure ensures one sector time (413 microseconds) for preparing the command list for the subsequent data transfer. Command chaining should be used between the ensuing Seek order and the related data operation, i.e., Read, Write or Check-write. If command chaining is not used, 2 must be added to the sector number received from the Sense order, or the time of one revolution of the RAD will be lost before data transfer is initiated.

#### INFORMATION PROTECTION

The contents of RAD storage units are protected in case of primary power failure; recorded information is not lost or altered.

"Write-protect" switches prevent inadvertent destruction of recorded data due to programming error. These toggle switches are located on a panel inside the cabinet. Writing is inhibited with the switch in the "up" position. Each switch protects 4 bands. The first switch inhibits writing on bands 0 through 3; the second inhibits writing on bands 4 through 7, etc.

#### SEQUENCE OF ACTIVITY

The following figures illustrate the sequential relationship of the key events that occur during RAD operations.

Figure 1. Controlling System/High-Speed RAD Actions

Figure 2. Write Order RAD Actions

Figure 4. Seek/Sense Order RAD Actions

Figure 5. Check-write Order RAD Actions

----

# APPENDIX SIGMA 5/7 PROGRAMMING EXAMPLE

The following example is a subroutine for reading or writing data on the RAD in a Sigma 5 or 7 computer system. The subroutine assumes that the RAD is the only I/O device currently being used and that the main program sets up locations indicating the storage unit address, band and sector address, address of the I/O area in the main core memory, and the number of bytes to be transferred.

The subroutine is called with the instruction BAL, 15 RADREAD or BAL, 15 RADWRITE. There are three possible returns that the subroutine can make to the main program:

- 1. If the operation is completed normally, return to calling location + 1.

- 2. If the operation cannot be started ("no I/O address recognition" or "SIO not accepted"), return to calling location + 2.

- 3. If an error occurs during or upon completion of the operation, return to calling location + 3.

| Label    | Command           | Argument          | Comments                                                                                             |

|----------|-------------------|-------------------|------------------------------------------------------------------------------------------------------|

| RADREAD  | LD,R8             | RDSORDER          | Load R8 and R9 with read command pair.                                                               |

|          | LI, R10           | -1                | Set read-write indicator for read.                                                                   |

|          | В                 | \$ + 3            |                                                                                                      |

| RADWRITE | LD,R8             | WRTORDER          | Load R8 and R9 with write command pair.                                                              |

|          | LI, R10           | 0                 | Set read–write indicator for write.                                                                  |

|          | OR,R8             | BFRADDRS          | Set up memory byte address (the main program stores an address in "BFRADDRS" before branching here). |

|          | OR, R9            | BYTCOUNT          | Set up byte count (the main program sets this location before branching here).                       |

|          | STD, R8           | COMMLIST + 2      | Save assembled command pair in command list.                                                         |

|          | MTW, 0            | R10               |                                                                                                      |

|          | BCS, 1            | IOINTSUP          | Is this a write operation?                                                                           |

|          | LD,R8             | COMMLIST + 6      | Yes — set up check-write command pair.                                                               |

|          | AND, R8           | FLAGMASK          | Save order field.                                                                                    |

|          | AND, R9           | FLAGMASK          | Save flag field.                                                                                     |

|          | OR, R8            | BFRADDRS          | Set up memory byte address.                                                                          |

|          | OR, R9            | BYTCOUNT          | Set up byte count.                                                                                   |

|          | STD,R8            | COMMLIST + 6      | Store check-write command pair in command list.                                                      |

| IOINTSUP | LW, R8<br>STW, R8 | DSCIOINT<br>X'5C' | Get and store an "XPSD DSCINTPT" instruction into<br>location 5C.                                    |

|          | LI,R8             | X'20'             | Set I/O interrupt arming bit.                                                                        |

|          | WD,R8             | X'1200'           | Arm and enable the I/O interrupt.                                                                    |

|          | LI,RO             | DA(COMMLIST)      | Load register 0 with the doubleword address of the first command pair in the command list.           |

|          | SIO, R10          | *DISCADDR         | Start disc operation ("DISCADDR" is set up by the main program and is the disc "unit address").      |

|          | STCF              | DSCCSAVE          | Save the condition code for the SIO.                                                                 |

|          | BCR, 12           | \$ + 3            | Was SIO accepted?                                                                                    |

|          | MTW, 1<br>B       | R15<br>*R15       | No – step return address and return to the main program.                                             |

| Label          | Command                      | Argument                     | Comments                                                                                                                                                                                                                                                     |

|----------------|------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | WAIT                         |                              | Yes – wait for the I/O interrupt.                                                                                                                                                                                                                            |

| DISCDONE       | AIO,R10                      | 0                            | Acknowledge the interrupt.                                                                                                                                                                                                                                   |

|                | STCF                         | DSCCSAVE                     | Save the AIO condition code.                                                                                                                                                                                                                                 |

|                | LCF                          | DSCCSAVE                     | Get saved condition code.                                                                                                                                                                                                                                    |

|                | BCR,4                        | \$ + 2                       | Did operation finish successfully?                                                                                                                                                                                                                           |

|                | MTW, 2                       | R15                          | No – add 2 to return address.                                                                                                                                                                                                                                |

| DISCEXIT       | LI,R8<br>WD,R8               | X'20'<br>X'1100'             | Yes – disable and disarm the I/O interrupt.                                                                                                                                                                                                                  |

|                | B<br>:                       | *R15                         | Return to the main program.                                                                                                                                                                                                                                  |

|                | BOUND                        | 8                            | This is an assembler directive ensuring that the following constants are on a doubleword boundary.                                                                                                                                                           |

| RDSORDER       | DATA<br>DATA                 | X'02000000'<br>X'1E000000'   | Read command pair-flags = interrupt on channel end or<br>unusual end, halt on transmission error, and suppress<br>incorrect length.                                                                                                                          |

| WRTORDER       | DATA<br>DATA                 | X'01000000'<br>X'2E000000'   | Write command pair-flags = command chain, interrupt on unusual end, halt on error, and suppress incorrect length.                                                                                                                                            |

| COMMLIST<br>+1 | DATA<br>DATA                 | X '03000800'<br>X '2E000002' | Seek command pair – the address 800 is the byte address<br>of a location (200) where the main program stores the<br>band and sector address for the read or write operation,<br>the byte count is 2, and the flags are the same as the<br>write flags above. |

| +2<br>+3       | DATA<br>DATA                 | 0<br>0                       | The read or write command pair are stored here.                                                                                                                                                                                                              |

| +4<br>+5       | DATA<br>DATA                 | X'03000800'<br>X'2E000002'   | Seek command pair – this command is used on a write operation and is identical to the one above.                                                                                                                                                             |

| +6<br>+7       | DATA<br>DATA                 | X'05000000'<br>X'1E000000'   | Check–write command pair – this command pair is exe-<br>cuted on a write operation to verify data on the disc<br>from the write just executed.                                                                                                               |

| FLAGMASK       | DATA                         | X'FF000000'                  | "Order" and "flag" field mask.                                                                                                                                                                                                                               |

| DSCIOINT       | XPSD                         | DSCINPT                      | This instruction is stored in X'5C'.                                                                                                                                                                                                                         |

| DSCINTPT       | DATA<br>DATA<br>DATA<br>DATA | 0<br>0<br>DISCDONE<br>0      | When the I/O interrupt occurs, the program status double-<br>word is saved in "DSCINTPT" and "DSCINTPT + 1" and<br>the program branches to "DISCDONE".                                                                                                       |

| DSCCSAVE       | DATA<br>:<br>MAIN PROGRAM    | 0                            | Temporary storage for condition code.                                                                                                                                                                                                                        |

| BFRADDRS       | DATA                         |                              | This location contains the address of the I/O buffer area.                                                                                                                                                                                                   |

| BYTCOUNT       | DATA                         |                              | This location contains the byte count.                                                                                                                                                                                                                       |

| DISCADDR       | DATA<br>:                    |                              | This location will contain the unit address.                                                                                                                                                                                                                 |

| Label | Command | Argument        | Comments                                                                       |

|-------|---------|-----------------|--------------------------------------------------------------------------------|

|       | BAL,15  | RADREAD         | Call (branch to) RAD read routine; save return address in general register 15. |

|       | В       | RDONE or \$ + 3 | Normal return.                                                                 |

|       | В       | RABNORM         | Abnormal return (no I/O address recognition or RAD not operational).           |

|       | B<br>:  | RERROR          | Erro <b>r-re</b> turn.                                                         |

|       | BAL,15  | RADWRITE        | Call RAD write routine; save return address in general register 15.            |

|       | В       | WDONE           | Normal return.                                                                 |

|       | В       | WABNORM         | Abnormal return.                                                               |

|       | В       | WERROR          | Error return.                                                                  |