# SDS 925/930/9300 INPUT/OUTPUT INTERFACE DESIGN MANUAL

.

SDS 900561A

December 1965

SCIENTIFIC DATA SYSTEMS • 1649 Seventeenth Street • Santa Monica, Calif. • (213) 871–0960

© 1965, Scientific Data Systems, Inc.

### PREFACE

This manual describes the Input/Output System available with the SDS 925/930/9300 Computers with special emphasis placed on the available interface signals and connections. The interface described represents the junction between the Input/Output communication channels and the external equipment. In the case of System Priority Interrupts it describes the junction requirements between external interrupt input signals and the Priority Interrupt Chassis. Detailed descriptions of each available interface connection is stressed to facilitate the efficient design or implementation of the coupling electronics required to connect external units to the computer; therefore, the reader should be familiar with the following publications pertinent to his specific application.

| SDS 925 Reference Manual                 | 900099A |

|------------------------------------------|---------|

| SDS 925 Theory of Operation Manual       | 900633  |

| SDS 930 Reference Manual                 | 900064B |

| SDS 930 Theory of Operation Manual       | 900066  |

| SDS 9300 Reference Manual                | 900050C |

| SDS 9300 Theory of Operation Manual      | 900570  |

| Models 93200/93202 TMCC                  | 900685  |

| Model 91602 Data Multiplex Channel – DMC | 900828  |

| Model 91500 Memory Interface Connection  | 900808  |

# CONTENTS

| Section |                                                       | Page       |

|---------|-------------------------------------------------------|------------|

| I       | INPUT/OUTPUT SYSTEMS                                  | 1-1        |

|         | General Description<br>Time-Multiplexed Communication | 1-1        |

|         | Channel (TMCC)                                        | 1-1        |

|         | POT, PIN Instructions                                 | 1-3        |

|         |                                                       | 1-3        |

|         | Multiple Access to Memory                             | 1-3        |

|         | Direct Access Communication                           |            |

|         | Channel (DACC)                                        | 1-3        |

|         | Data Multiplexing System (DMS)                        | 1-3        |

|         | Data Multiplex Channel (DMC)                          | 1-3        |

|         | Data Subchannels (DSC)                                | 1-3        |

|         | External Interlace (EIN)                              | 1-4        |

|         | Memory Interface Connection (MIC)                     | 1-4<br>1-4 |

|         | Priority Interrupt                                    | 1-4        |

| II      | INPUT/OUTPUT INSTRUCTIONS                             | 2-1        |

|         | General                                               | 2-1        |

|         | Energize Output M (EOM)                               | 2-1        |

|         | Buffer Control EOM                                    | 2-1        |

|         | Internal Control EOM                                  | 2-1        |

|         | Input/Output Control EOM                              | 2-1        |

|         | System Control EOM                                    | 2-1        |

|         | EOM Interface Signals                                 | 2-2        |

|         | Energize Output to Direct Access                      |            |

|         | Channels (EOD)                                        | 2-2<br>2-2 |

|         | EOD Interface Signals<br>Parallel Output (POT)        | 2-2<br>2-3 |

|         | POT Interface Signals                                 | 2-3        |

|         | Parallel Input (PIN)                                  | 2-4        |

|         | PIN Interface Signals                                 | 2-4        |

|         | SDS 925 Special I/O Operations                        | 2-5        |

|         | Input (BPI)                                           | 2-5        |

|         | Output (BPO)                                          | 2–5        |

|         | Skip If Signal Not Set (SKS)                          | 2-6        |

|         | SKS Interface Signals                                 | 2-6        |

| III     | INPUT/OUTPUT CHANNEL                                  |            |

|         | DESCRIPTION                                           | 3-1        |

|         | General                                               | 3-1        |

|         | Time Multiplexed Communication                        |            |

|         | Channel (TMCC)                                        | 3–1        |

|         | Interlace                                             | 3–1        |

|         | Input                                                 | 3-1        |

|         | Input Clock Characteristics                           | 3-5        |

|         | Input Termination                                     | 3-5        |

|         | Output Timing                                         | 3-5        |

| Section |                                                                                                                                                                                                                                                            | Page                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|         | Output Termination<br>Interlace Operation                                                                                                                                                                                                                  | 3–8<br>3–8                                           |

|         | Direct Access Communication<br>Channel (DACC)<br>Memory Interface Connection (MIC)<br>Data Multiplexing System (DMS)<br>Data Subchannel (DSC)<br>DSC-I Operation<br>DSC-II Operation                                                                       | 3-9<br>3-12<br>3-12<br>3-14<br>3-14<br>3-14          |

|         | Input/Output Using External<br>Interlace<br>Word Increment Function<br>Priority Interrupt Operation<br>Interrupt States<br>Interface Signals                                                                                                               | 3-19<br>3-19<br>3-20<br>3-20<br>3-21                 |

| I٧      | INTERFACE CIRCUIT AND CABLE<br>REQUIREMENTS                                                                                                                                                                                                                | 4-1                                                  |

|         | General<br>Cable Requirements<br>Connector Requirements<br>Circuit Requirements<br>Output Circuits<br>Low-Speed Outputs, Type O1<br>Low-Speed Outputs, Circuit Type O2                                                                                     | 4-1<br>4-1<br>4-1<br>4-1<br>4-1<br>4-1<br>4-3        |

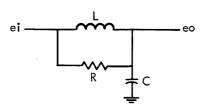

|         | High-Speed Outputs, Circuit<br>Type O3<br>Input Circuits<br>Input Circuit Type I1<br>Input Circuit Type I2<br>Input Circuit Type I3<br>Input Circuit Type I4<br>Driving Input Signals<br>High-Speed Inputs<br>Formulae for LRC Circuits<br>Standard Cables | 4-3<br>4-4<br>4-5<br>4-5<br>4-5<br>4-5<br>4-6<br>4-6 |

| V       | INTERFACE CONNECTOR PIN<br>DESCRIPTIONS                                                                                                                                                                                                                    | 5-1                                                  |

|         | General<br>TMCC Interface Connectors<br>DACC Interface Connectors<br>MIC Interface Connector<br>DSC-I Interface Connectors<br>DSC-II Interface Connectors<br>System Priority Interrupt Interface<br>Connectors                                             | 5-1<br>5-21<br>5-36<br>5-41<br>5-41<br>5-50          |

# Figures

Page

# Tables

|               |                                                                             | 0          |

|---------------|-----------------------------------------------------------------------------|------------|

| 1-1           | 925/930/9300 General Computer                                               |            |

|               | Configuration                                                               | 1-2        |

| 2-1           | Signals Generated by EOM Instructions                                       | 2-2        |

| 2-2           | Signals Generated by EOD Instruction                                        | 2-2        |

| 2-3           | Signals Generated by POT Instruction                                        | 2-4        |

| 2-4           | Signals Generated by PIN Instruction                                        | 2-5        |

| 2-5           | Signals Generated by 925 BPI Instruction                                    | 2-6        |

| 2-6           | Signals Generated by 925 BPO Instruction                                    | 2-7        |

| 2-7           | Signals Generated by SKS Instruction                                        | 2-7        |

| 3-1           | TMCC Simplified Block Diagram                                               | 3-2        |

| 3–2           | Input Timing Characteristics                                                | <b>0</b> 4 |

| ~ ~           | Asynchronous Mode                                                           | 3-4        |

| 3-3           | Input Clock Timing Diagram                                                  | 3-6        |

| 3-4           | TMCC Input Timing, Synchronous Clock                                        | 3-7        |

| 3–5<br>3–6    | TMCC Output Timing, Synchronous Clock                                       | 3-7<br>3-9 |

| 3-7           | DACC Timing, Asynchronous Input Mode<br>DACC Timing, Synchronous Input Mode | 3-9<br>3-9 |

| 3-8           | DACC Timing, High-Speed Synchronous                                         | 5-7        |

| 0-0           | Input Mode                                                                  | 3-10       |

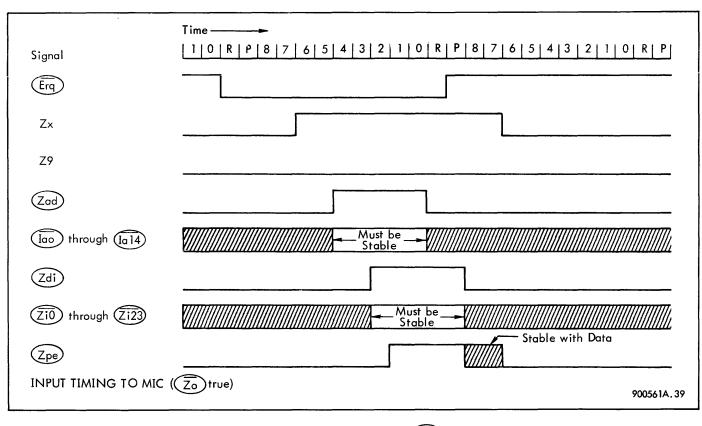

| 3-9           | MIC Input Timing (Zo True)                                                  | 3-13       |

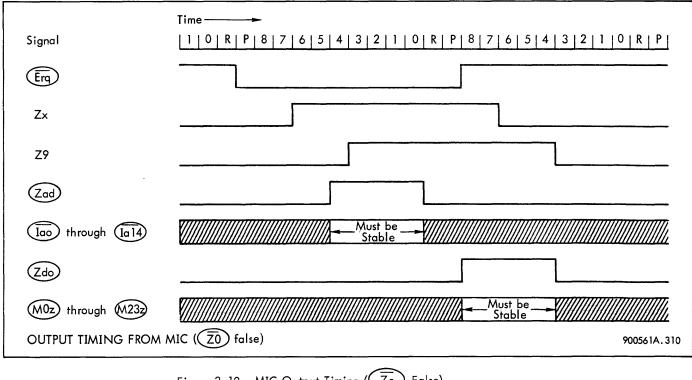

| 3-10          | MIC Output Timing ( Zo False)                                               | 3-13       |

| 3-11          | Timing Diagram DSC-II Terminating                                           | • • •      |

|               | Input/Output with External Address                                          | 3-16       |

| 3-12          | Timing Diagram DSC-II Terminating                                           |            |

|               | Input/Output with External Address                                          | 3-18       |

| 3-13          | Timing Diagram DSC-II Input/Output                                          |            |

|               | Using Internal Interlace                                                    | 3-19       |

| 3-14          | Timing Diagram DSC–II Word                                                  |            |

|               | Increment Function                                                          | 3-20       |

| 3-15          | System Priority Interrupt Configuration                                     | 3-21       |

| 4-1           | Typical AND Gate                                                            | 4-1        |

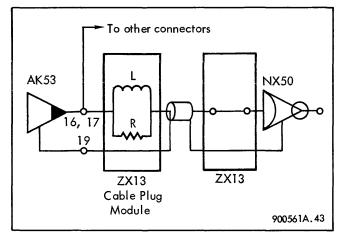

| 4-2           | Cable Driver AK53                                                           | 4-1        |

| 4-3           | Typical Interface Connection, Low-Speed                                     |            |

|               | Outputs, Type Ol                                                            | 4-2        |

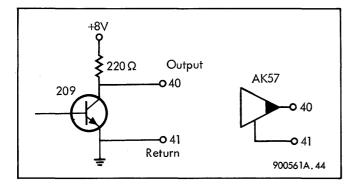

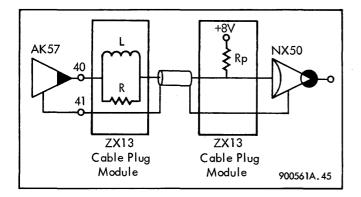

| 4-4           | Cable Driver AK57 Output                                                    | 4-3        |

| 4-5           | Low-Speed Output, Circuit Type O2                                           | 4-3        |

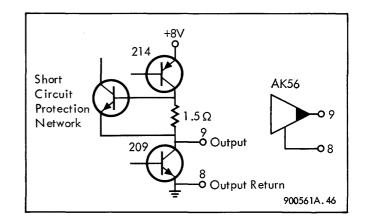

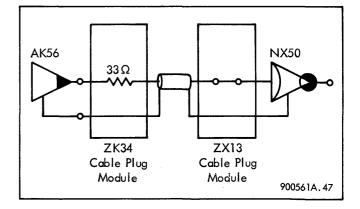

| 4-6           | Cable Driver AK56                                                           | 4-3<br>4-3 |

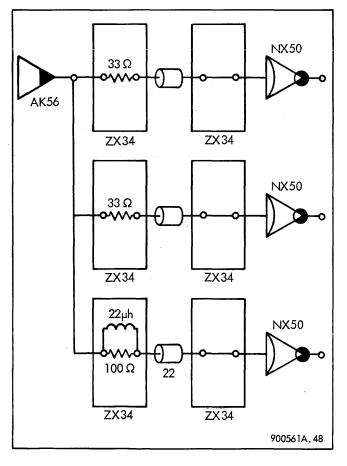

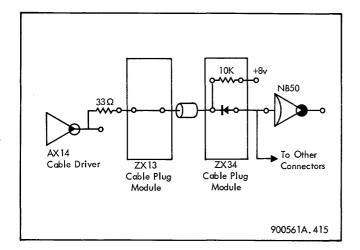

| 4-7<br>4-8    | High-Speed Output, Circuit Type O3                                          | 4-3<br>4-4 |

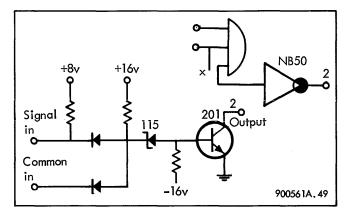

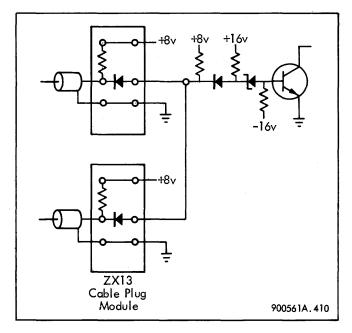

| 4-0<br>4-9    | Cable Driver AK56 Loading<br>Interface Inverter, NB50                       | 4-4<br>4-4 |

| 4-10          | Input Signal Gating                                                         | 4-4<br>4-4 |

| 4-11          | Input Circuit Type 13                                                       | 4-4<br>4-5 |

| 4 <b>-</b> 12 | Interrupt Inputs Type I4                                                    | 4-5        |

| 4-13          | Low-Speed Input Cable Driver AX14                                           | 4-5        |

| 4-14          | AX14 Driving Low-Speed Input                                                | 4-5        |

| 4-15          | High-Speed Input Connection                                                 | 4-6        |

|               | <b>V</b> (1) (1) (1) (1) (1) (1) (1) (1) (1) (1)                            | -          |

|               |                                                 | Page |

|---------------|-------------------------------------------------|------|

| 1-1           | TMCC Models                                     | 1-1  |

| 3–1           | Unit Address Codes                              | 3-3  |

| 3-2           | Interlace Extended Mode Terminal                | 3-8  |

| 3-3           | DACC Terminal Functions Extended Mode           | 3-11 |

| 3-4           | Unit Address Codes                              | 3-11 |

| 3-5           | EOM/POT/SKS Function Combinations               | 3-15 |

| 3-6           | Relationship of DMC Functions and               |      |

|               | Interface Signals                               | 3-17 |

| 4-1           | R/L Network Values                              | 4-2  |

| 4-2           | Standard Cables Assemblies                      | 4-6  |

| 5-1           | TMCC W Buffer Interface Connectors              |      |

|               | (AUXW-A)                                        | 5-1  |

| 5-2           | TMCC W Buffer Interface Connector               |      |

|               | (DISCW)                                         | 5-3  |

| 5-3           | TMCC W Buffer Interface Connectors (PIN)        | 5-5  |

| 5-4           | TMCC W Buffer Interface Connectors (POT)        | 5-7  |

| 5-5           | TMCC W Buffer Interface Connector               |      |

|               | (MA GW)                                         | 5-9  |

| 5-6           | TMCC W Buffer Interface Connectors (WRDW)       | 5-11 |

| 5-7           | TMCC Y Buffer Interface Connectors<br>(AUXY-B)  | 5-13 |

| 5-8           | TMCC Y Buffer Interface Connector (DISCY)       | 5-15 |

| 5-9           | TMCC Y Buffer Interface Connector (MAGY)        | 5-17 |

| 5-10          | TMCC Y Buffer Interface Connectors (WRDY)       | 5-19 |

| 5-11          | DACC Interface Connectors (AUX)                 | 5-21 |

| 5-12          | DACC Interface Connector (DISC)                 | 5-23 |

| 5-13          | DACC Interface Connector (MAG)                  | 5-25 |

| 5-14          | DACC Interface Connectors (PIN)                 | 5-27 |

| 5-15          | DACC Interface Connectors (POT)                 | 5-29 |

| 5-16          | DACC Interface Connectors (WRD)                 | 5-31 |

| 5-17          | DACC Interface Connectors (ZIN)                 | 5-33 |

| 5-18          | DACC Interface Connectors (ZOUT)                | 5-35 |

| 5-19          | MIC Interface Connectors (MCTL)                 | 5-36 |

| 5-20          | MIC Interface Connectors (MIN)                  | 5-38 |

| 5-21          | MIC Interface Connectors (MOUT)                 | 5-39 |

| 5-22          | DSC-II (W) Interface Connector<br>(DSC Control) | 5-41 |

| 5 <b>-2</b> 3 | DSC-II (X) Interface Connector<br>(DSC Control) | 5-44 |

| 5-24          | DSC-II (W) Interface Connector (DSC In)         | 5-46 |

| 5-25          | DSC-II (X) Interface Connector (DSC In)         | 5-48 |

| 5-26          | DSC-II (W and X) Interface Connectors           | 2 .0 |

|               | (DSC Out)                                       | 5-49 |

| 5-27          | Channel Priority Interrupt, Arming              | ,    |

|               | Interrupt                                       | 5-51 |

| 5-28          | Directory Priority Interrupt                    | 5-52 |

|               | , , ,                                           |      |

# SECTION I INPUT/OUTPUT SYSTEMS

#### **GENERAL DESCRIPTION**

The standard I/O system provided with all SDS 925/930/ 9300 Computers allows operations with all standard SDS peripheral equipment as well as with special purpose devices. Alternate I/O system options are available which are of particular use for systems handling multiple sources of data and for systems requiring very high data acquisition rates.

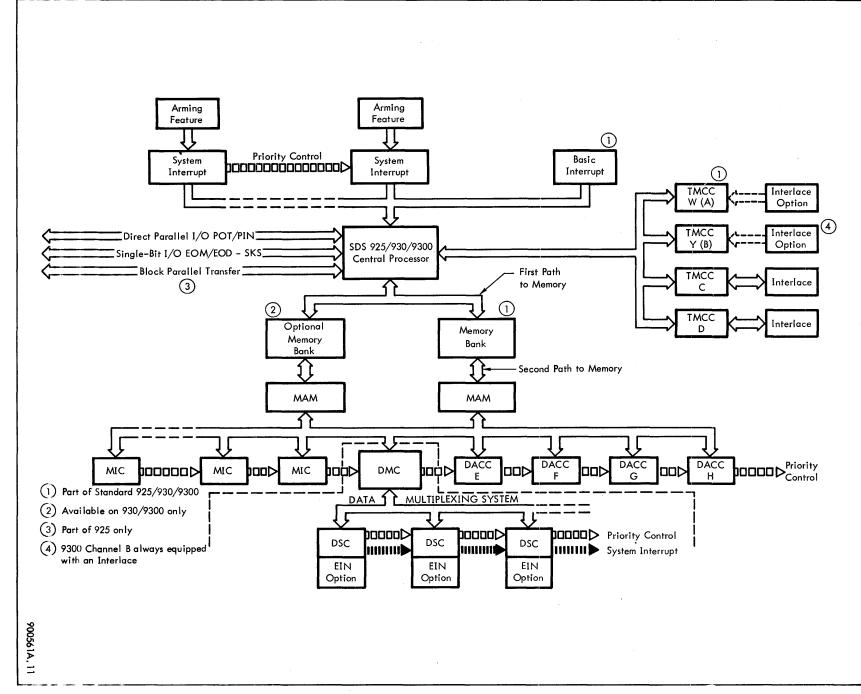

Two separate paths along which I/O data can flow to and from memory are provided for the SDS 925/930/9300 Computers. Figure 1-1 shows input/output memory paths and systems configuration. The first path is the normal path that exists between memory and the central processor; the second path exists between memory and the I/O control units via a Multiple Access to Memory unit (MAM). Advantages of the multiple access to memory feature are: I/O memory accessing without loss of computation time; higher data transfer rates; and program simplification. Although all I/O channels available with the multiple access to memory option are available to the SDS 925, this computer treats all input and output operations on a priority time multiplexed basis only since the SDS 925 can have no more than one memory bank.

The first path of data flow between memory and central processor uses the following methods of I/O information transfer:

- a. Time Multiplexed Communication Channels (TMCC)

- b. Parallel Input (PIN)

- c. Parallel Output (POT)

- d. Single-Bit Input/Output

The second path of data flow between memory and I/O control units and devices uses the following methods of transfer:

- a. Data Multiplexing System (DMS)

- b. Direct Access Communication Manuals (DACC)

- c. Memory Interface Connection (MIC)

All second path to memory systems communicate with memory through a Multiple Access to Memory unit (MAM). Two or more separate memory banks are a prerequisite for taking full advantage of the multiple access to memory option.

#### TIME-MULTIPLEXED COMMUNICATION CHANNEL (TMCC)

The basic 925/930/9300 configuration includes one TMCC for 6-bit character input/output. This TMCC is referred to as the W channel in the 925/930 and as the A channel in the 9300. The TMCC is capable of controlling I/O devices such as typewriter, paper tape, card, magnetic tape, and line printers on a time multiplexed basis. A computer may have from one to four TMCC's connected to it. Additional channels are designated Y (B on 9300), C, and D. The basic model number is 93200. Model numbers for additional channels and optional features are listed in table 1-1. Any 6-bit TMCC can be expanded to 12 bits by adding the Model 93201 option or to 24 bits by addition of the Model 93202 option. With the 12- and/or 24-bit options character size is controlled by the external device. The 24-bit buffer can handle either 6, 12, or 24 bit characters according to device requirements.

Table 1-1. TMCC Models

| Model | Description                                                      | Used on<br>Channel   |

|-------|------------------------------------------------------------------|----------------------|

| 93200 | 6-bit characters, without interlace,<br>single channel           | W(A), C              |

| 91210 | Interlace option for 93200                                       |                      |

| 93201 | 12–bit character extension option<br>for 93200                   |                      |

| 93202 | 24–bit character extension option<br>for 93200                   |                      |

| 93221 | 6–bit characters, without interlace,<br>two channels             | W(A) plus<br>Y(B) or |

| 91210 | Interlace option for either channel of 93221                     | C plus D             |

| 93201 | 12–bit character extension option<br>for either channel of 93221 |                      |

| 93202 | 24-bit character extension option<br>for either channel of 93221 |                      |

The memory interlace feature may be added to any TMCC by adding the Model 91210 Memory Interlace Control unit. This optional feature is useful for input/output of large blocks of data at high transfer rates. The memory interlace automatically controls the transfer of data words for its associated channel buffer by maintaining a current memory address and word count during input/output operations. Figure 1–1. 925/930/9300 General Computer Configuration

1-2

The interlace also controls terminal functions and provides end-of-record and zero word count interrupts.

Channels C and D (and B on the 9300) must always have interlace installed since no computer instructions exist in the 9300 to allow use of these channels without interlace. Any TMCC operating with interlace has priority over the central processor for memory access with channel priority in the order: Channels D, C, Y(B), W(A).

The maximum data transfer rate of a TMCC is one word every two memory cycles or 280,000 words per second.

# POT, PIN INSTRUCTIONS

The 925/930/9300 Computers include two instructions, parallel output and parallel input, which permit the transfer of words between core memory and external equipment without interfering with the operation of other I/Q channels. The execution of either the POT or PIN instruction causes a signal to be sent to the external device requesting it to acknowledge when it is ready to receive or transmit the data word. After the request signal is sent, the computer suspends operations until the acknowledge signal is received. The maximum data transfer rate for PIN operations is 114,000 words per second (five cycles for each word transfer). The maximum data transfer rate for POT operations is 143,000 words per second (four cycles for each word transfer).

The Block POT and Block PIN (BPO/BPI) operations which are unique to the SDS 925 transfer words at a maximum rate of 570,000 words per second (one cycle for each word transfer).

# SINGLE-BIT INPUT/OUTPUT

The two instructions, Energize Output M (EOM) and Skip If Signal Not Set (SKS) when operating in the system mode are used to provide single-bit input/output transmission. Execution of an EOM operating in the system mode causes a signal to be transmitted to one of a possible 8, 192 signal destinations. The maximum signal transfer rate is 570,000 pulses per second. Execution of an SKS in the special system test mode permits the computer to test the condition of any one of a possible 8, 192 input lines. The maximum test rate depends on the condition of the line: 286,000 per second if program does not skip next instruction, or 190,000 per second if program does skip the next instruction.

# **MULTIPLE ACCESS TO MEMORY**

The Multiple Access to Memory feature (MAM) provides the necessary modules on both main frame and memory to permit memories to be accessed via the second memory path. Transfer of one word over this path in either direction requires one memory cycle. If the computer has two or more memory banks, the main frame can communicate with one memory via the first path to one memory while some peripheral device is communicating with the other memory via the second path without interference or loss of computation time. The Multiple Access to Memory feature (MAM) is required for the attachment of Direct Access Communication Channels (DACC), Data Multiplex Channels (DMC), or Memory Interface Connections (MIC).

## DIRECT ACCESS COMMUNICATION CHANNEL (DACC)

The Direct Access Communication Channel, Model 92220, is available for systems requiring high-speed input/output simultaneous with computation. Up to four DACC's may be connected to the core memory through the Multiple Access to Memory (MAM), Model 92990 (Model 92992 for the 925) for each memory module. The four channels are designated E, F, G, and H. Simultaneous access to memory will occur if the channel and computer are addressing separate memory modules. If simultaneous access to the same memory module is required, priority is in the order: MAM, TMCC, Central Processor.

The maximum data transfer rate in the high-speed mode is one word every memory cycle, or approximately 570,000 words per second.

The DACC communicates with external equipment by means of a bidirectional 24-bit register using 6-, 8-, 12-, or 24-bit characters plus a parity bit. Character size is controlled by the external device.

# DATA MULTIPLEXING SYSTEM (DMS)

The data multiplex system consists of two basic elements:

- a. The Data Multiplex Channel (DMC) for communicating with several data sources/destinations, and for synchronizing I/O operations with memory.

- b. One or more Data Subchannels (DSC) for interfacing between peripheral devices or systems and the DMC.

# Data Multiplex Channel (DMC)

The data multiplex channel is equipped with an internal interlace feature that allows specified input/output tables in memory to be processed by the addressed peripheral device via the associated subchannel.

# Data Subchannels (DSC)

Two standard subchannels are available. Model 91711 DSC-I provides character oriented operations, and Model 91712 DSC-II is full-word (24-bit) oriented. Up to 128 DSCs can be attached to the DMC. Two or more DSCs can be active simultaneously using an internal priority arrangement to determine which subchannel can transmit to the DMC at any given time.

# External Interlace (EIN)

An External Interlace Model 91800 can be attached to any DSC. The EIN controls the transmissions of the DSC at a maximum rate of one word per memory cycle. Maximum data transfer rate using internal interlace is 190,000 words per second. With external interlace the maximum transfer rate is increased to 570,000 words per second.

# **MEMORY INTERFACE CONNECTION (MIC)**

The Memory Interface Connection, Model 91500, is available for direct access to core memory under control of external equipment. A prerequisite for MIC is a Multiple Access to Memory (MAM) Model 92990 for each memory module. The 925 Computer requires the Multiple Access to Memory (Model 92992). The external device must provide signals to the MIC indicating when an I/O operation is to take place, it must specify the memory address, and must indicate whether the function is an input or an output. The MIC checks parity on inputs and generates parity on outputs. Data transfer is in the form of 24-bit words plus odd parity.

The maximum data transfer rate is 570,000 words per second.

# **PRIORITY INTERRUPT**

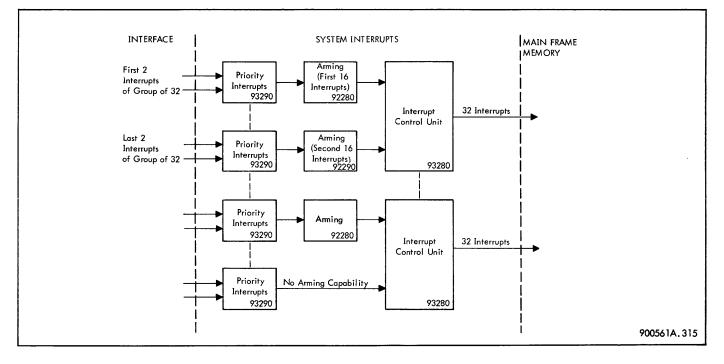

The 925/930/9300 Computers are capable of program sequence interruption by signals generated by communication channels, special features, and external equipment, on a priority basis. Each 925/930/9300 includes a basic interrupt unit that provides two interrupts (four for 9300) with 22 more available (20 more for 9300) for use with optional I/O channels and special features. Up to 896 system priority interrupts for general purpose use are available for external systems by adding Model 93280 interrupt control units. Each Model 93280 can control up to 32 priority interrupts. The Model 93280 does not include the interrupts. However, interrupts may be added to the Model 93280 by connecting a Model 93290 priority interrupt. Each Model 93290 contains two levels of priority interrupt; thus 16 Model 93290's (32 levels of interrupt) can be added to each interrupt control unit.

An arming feature may be added to the interrupt control unit by adding a Model 92280 arming option to provide arming for the first 16 levels of interrupt on a Model 93280. Arming for the second 16 levels of interrupts can be added by adding a Model 92290 arming option to the Model 92280.

# SECTION II INPUT/OUTPUT INSTRUCTIONS

#### GENERAL

Five instructions control input/output operations of the 925/930/9300 Computers. These are:

- a. Energize Output M (EOM)

- b. Energize Output to Direct Access Channels (EOD)

- c. Parallel Input (POT)

- d. Parallel Input (PIN)

- e. Skip If Signal Not Set (SKS)

In addition to the five instructions above the SDS 925 provides for a block transfer variation of the POT and PIN operations, BPO and BPI. In this manual emphasis is placed on interface information and the reader should refer to the 925, 930, or 9300 reference manual for a detailed description of each instruction.

#### ENERGIZE OUTPUT M (EOM)

The EOM instruction is used primarily to control input/ output through all channels except the DACC. This instruction operates in four basic modes that are program selectable by the setting of two bits (C10, C11) within the EOM instruction format:

| <u>C10</u> | <u>C11</u> | Function             |

|------------|------------|----------------------|

| 0          | 0          | Buffer Control       |

| 0          | 1          | Input/Output Control |

| 1          | 0          | Internal Control     |

| 1          | 1          | System Control       |

One computer cycle (1.75 µsec) is required to execute an EOM instruction in any mode. During the execution of the EOM instruction the control register (C register) of the computer is held stable. At that time this 24-bit register (C0-C23) contains the EOM instruction word. The output of this register is available to the TMCC and to the external units. If an interrupt occurs during the execution of any EOM in any mode, it will not be acknowledged until the execution of the instruction following the EOM is complete.

#### **Buffer Control EOM**

The EOM instruction operating in the buffer control mode prepares the channel and device for data transmissions or other peripheral activities. The channel to be used, the peripheral unit on that channel, the operation to be performed, and the type of character format to be used, are all detailed within the EOM in this mode. The use of BCD or binary data transmission, the allowance or not of a leader (as in paper tape functions), and the direction of operation (in magnetic tape functions) are all detailed to the channel and its connected peripheral unit. Execution of such an EOM connects the specified peripheral unit to the channel. Interlace can also be alerted with EOM in this mode.

#### Internal Control EOM

The EOM in the internal control mode is used to enable and disable the interrupt system, to prepare the system for the selective arming and disarming of the system interrupt levels, to reset the overflow, and to record exponent overflow. The EOM, internal control mode, does not apply directly to I/O control, and therefore, it does not generate interface signals.

#### Input/Output Control EOM

The EOM in the input/output mode is used to direct peripheral devices to perform nontransmitting operations such as rewind magnetic tape and upspace the printer. Selection of certain channel operations such as interrupt response and the input/output terminal function desired is made with this EOM. It is also used to alert peripheral devices that a Parallel Input (PIN) or Parallel Output (POT) instruction is to follow. The C register outputs, C18 through C23, must be decoded by the external unit during this instruction to avoid interference with standard device control.

#### System Control EOM

The EOM in the system control mode can control internal equipment by providing a single-bit output of approximately 1.4 µsec to any addressable connector. The system control mode can be divided into two distinct submodes by gating bit 9 with bits 10 and 11 of the system mode EOM.

| <u>C1</u> | <u>C9</u> | <u>C10</u> | <u>C11</u> |                               |

|-----------|-----------|------------|------------|-------------------------------|

| Х         | 0         | 1          | 1          | EOM System Control (External) |

| Х         | 1         | 1          | 1          | EOM System Control (Internal) |

The internal system control submode provides control for standard I/O systems such as the DMS, data communications, and display. The external system control submode provides a means of controlling special non-standard I/O equipment or systems. C1 must always be included in the decoding circuitry since the term C1 separates the Data Multiplex System (C1) from other I/O buffer units (C1).

#### **EOM Interface Signals**

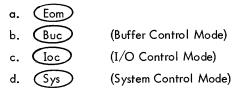

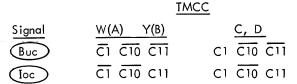

Four signals generated by the EOM instruction are available at the TMCC I/O connectors. See figure 2-1. These signals, when true, indicate that the contents of the C register (C0-C23) are to be transferred to external equipment. The four signals are:

The signals, (Buc), (Ioc), and (Sys), indicate to the external system which EOM mode is currently being executed.

The Eom signal is generated by all EOM instructions, and is true during periods  $T7 - Tr (1.4 \mu sec)$ . The Eom pulse is also generated during the FILL operation. The Eom signal is inhibited during the second EOM instruction of the interlace loading sequence and during time-share operations.

The signals, Buc and loc are derived from the EOM instruction according to configuration of bits C1, C10, and C11.

Figure 2-1. Signals Generated by EOM Instructions

The terms C17 and  $\overline{C17}$  must be used by the external system to distinguish between TMCC-W(A) and TMC-Y(B), and, similarly, between TMCC-C and TMCC-D.

$$C17 = TMCC-W(A)$$

or TMCC-C

C17 = TMCC-Y(B) or TMCC-D

The Sys signal is derived from the EOM instruction (external system submode) according to bits C9, C10 and C11.

$$\overline{\text{Sys}} = \overline{\text{C9}} \text{ C10} \text{ C11}$$

If the contents of the C register (C0, C1, C2, C12-C23) are decoded during the Sys signal, up to 32,768 singlebit outputs can be obtained.

# ENERGIZE OUTPUT TO DIRECT ACCESS CHANNELS (EOD)

The EOD instruction is used to control input/output through the DACC. This instruction is similar to the EOM instruction and performs analogous functions for the direct access channels E, F, G, and H.

#### **EOD Interface Signals**

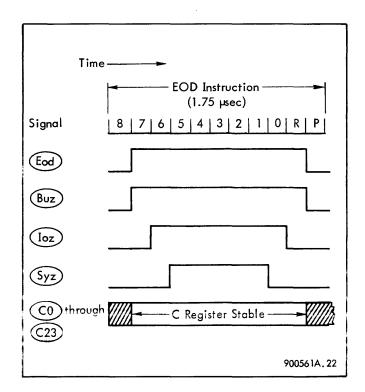

Four signals generated by the EOD instruction are available at the DACC I/O connectors. See figure 2-2. These signals, when true, indicate that the contents of the C register

Figure 2-2. Signals Generated by EOD Instruction

(CO-C23) are to be transferred to external equipment. These signals are:

The signals, Buz, loz, and Syz, indicate to the external system which EOD mode is currently being executed.

Eod is generated by all EOD instructions and is true during periods T7 – Tr (1.4  $\mu$ sec). This Eod pulse is inhibited during time-share operations and during the interlace loading sequence.

The Buz and Ioz signals are derived from the EOD instruction according to the configuration of bits C1, C10, C11, and C17.

|        |    |          |            | D,         | ACC |      |          |            |

|--------|----|----------|------------|------------|-----|------|----------|------------|

| Signal |    | E        | <u>.</u>   |            |     | 1    | <u>F</u> |            |

| Buz    | CI | C17      | <u>C10</u> | <u>C11</u> | CI  | C17  | C10      | <u>C11</u> |

| loz    | CI | C17      | C10        | C11        | CI  | C17  | C10      | C11        |

|        |    | <u>(</u> | 3          |            |     | ļ    | <u>H</u> |            |

| Buz    | CI | C17      | <u>C10</u> | <u>C11</u> | C1  | C17  | C10      | CII        |

| loz    | CI | C17      | C10        | C11        | CI  | C 17 | C10      | C11        |

Because C17 and C17 are included in the Buz and Ioz terms, external recognition of C17 and C17 is not required.

(Ioz) is inhibited during the interlace loading sequence.

Syz signal is derived from the EOD instruction according to bits C9, C10, and C11.

$$\overline{\text{Syz}}$$

=  $\overline{\text{C9}}$  C10 C11

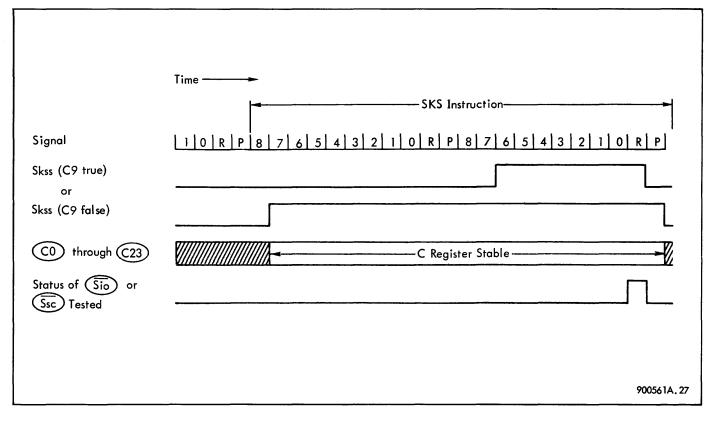

#### PARALLEL OUTPUT (POT)

The POT instruction provides a means of direct parallel transfer of up to 24 bits from memory to an I/O channel or external device via the C register of the processor. Each word transfer is under direct program control. The POT instruction must be preceded by an EOM instruction to select the desired device. During a POT instruction, the computer accesses the word to be transferred from a location of memory determined by the effective address of the instruction. The computer then proceeds to a wait phase and holds the word to be transferred in the C register.

The wait phase consists of an integral number of computer cycles (1.75 µsec each). During the wait phase, the C register output lines CO-C23 are stable and contain the 24-bit word to be transferred to the external device. Upon

receipt of a ready signal from the external device which is to receive the data, the computer exits from the wait phase and continues computation. (The computer will remain in the wait phase, thereby suspending computation, until it is released by the ready signal from the external device). If the device was ready before the computer entered the wait phase, the computer would spend only one cycle in the wait phase and then resume computation. Thus all POT instructions spend at least one computer cycle in a wait phase. The POT instruction requires 2 + n cycles,  $[(3.5 \ \mu sec) + n (1.75 \ \mu sec)]$  where n = n number of wait phases for execution.

#### **POT Interface Signals**

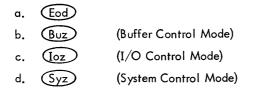

The following signals are available on POT connectors provided with each DACC and TMCC. See figure 2-3. The ready signal supplied by the external device is designated  $\mathbb{R}^{+}$ . This signal, when low (0v) indicates that the unit is ready, and when high (+8v) that the unit is not ready. The status of this ready signal is tested once every machine cycle during the wait phase. (The actual sampling time is T7-T3). The ready signal must be at ground level for at least one computer cycle (1.75 µsec) after the start of the POT wait phase to ensure acknowledgment by the central processor. The wait phase terminates at the completion of that machine cycle during which the unit ready signal was acknowledged.

The following signals are generated by a POT instruction:

- a. (Pot ) This signal is true during the entire wait phase of the POT instruction, and is false at all other times. (Pot ) being true indicates to the external device that the C register output lines are stable and contain the 24-bit word to be transferred. (Pot ) going false indicates to the external device that the computer has acknowledged the ready signal and has exited from the wait phase.

- b. (Pot 2) This signal is true from T5-T1 of every machine cycle during the POT wait phase, and is false at all other times. (Pot 2) may thus be used as a strobe by the external device to strobe the C register output lines (CO C23). If a time-share operation occurs during the wait phase, the (Pot 1) signal will remain true, but (Pot 2) will be inhibited. At the completion of the time-share operation, depending upon the condition of (Rt), at least one more cycle of wait phase will occur.

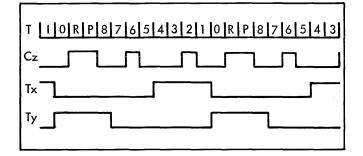

The following three signals are also generated by both the TMCC's and the DACC's, and are derived from the pulse counters in the communication channel. These timing signals may be used to clock Eom, Sys, Pot, etc., in an external device.

a. Qq1 - This signal is true from T5 through T0 of every computer cycle, and is false at all other times.

Figure 2–3. Signals Generated by POT Instruction

- b. Qq2 This signal is true from T6 through T3 of every computer cycle, and is false at all other times. This signal may be used during the POT wait phase to indicate to the external device the time period during which the ready line Rt will be tested.

- c. Qq3 This signal is true from T7 through T4 of every computer cycle, and is false at all other times.

# PARALLEL INPUT (PIN)

The PIN instruction provides a means of direct parallel transfer of up to 24 bits of data from an external device into memory via the C register of the computer. Each word transferred is under direct program control. The PIN instruction must be preceded by an EOM instruction to select the desired device. During the execution of a PIN instruction the computer proceeds to a wait phase almost identical to that of a POT instruction. The wait phase consists of an integral number of computer cycles. The C register is first reset, then the input lines (Cd0 - Cd23) are strobed into the C register. This process of resetting the C register and of then strobing the data repeats once every machine cycle during the wait phase of a PIN instruction.

When the ready signal is received (Rt going to ground level) from the external device, the computer exits from the wait phase and continues computation. The wait phase terminates at the completion of that machine cycle during which the external ready signal was acknowledged by the computer; therefore, a PIN instruction must go through at least one wait phase. The requirements for the ready signal are identical to those for a POT instruction. Thus, a PIN instruction requires 3 + n cycles [(5, 25 μsec)+n (1, 75 μsec)] where n = number of wait phases for execution.

#### NOTE

The C register input lines (Cd0 -Cd23) are inverted before they are strobed into the C register; thus, the C register will receive the ones complement of the data impressed on Cd0 - Cd23.

# **PIN Interface Signals**

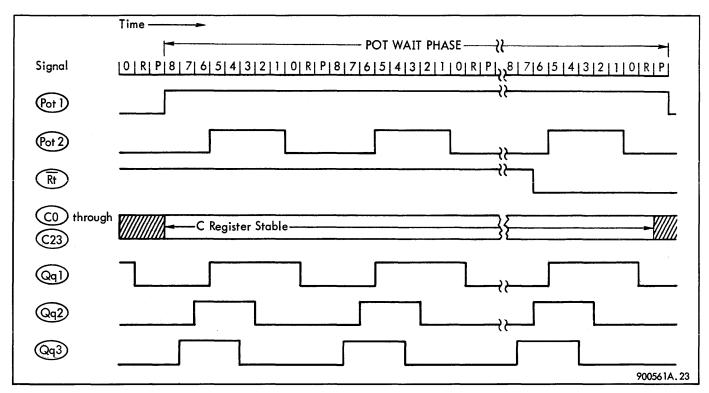

Two signals are generated by a PIN instruction. See figure 2-4. These signals generated in the computer are available at the PIN connectors provided with each DACC and TMCC.

- a. (Pin) This signal is true from T7 through T0 of every computer cycle during a PIN wait phase and is false at all other times. (Pin) indicates to the external device that the C register input lines are being strobed into the C register and therefore must be stable at this time.

- b. Rti This signal is a 1.4 µsec ground level signal generated when the PIN instruction exits from the wait phase. Rti going to ground indicates to the external system that the CPU has acknowledged the ready signal by exiting from the wait phase and has accepted 24 bits of data. (Rti is positive in its quiescent condition).

Figure 2-4. Signals Generated by PIN Instruction

If a time-share operation occurs during the wait phase, the Pin signal will be inhibited. At the completion of the time-share operation, depending on the condition of Rt, at least one more cycle of wait phase will occur.

If a time-share operation occurs during the cycle after the last wait phase cycle, Rti will be inhibited until the completion of the time-share operation.

### SDS 925 SPECIAL I/O OPERATIONS

The 925 Computer includes two additional I/O instructions, Block Parallel Output (BPO) and Block Parallel Input (BPI). These instructions are block transfer versions of POT and PIN instructions. The transmission of data is initiated by performing the following programming steps:

- a. Load the number of words to be transferred, minus one, into the A register.

- b. Alert the external unit by means of an EOM instruction.

- c. Start the transfer with a BPO or BPI instruction.

The computer now enters a wait and transfer phase. If the external unit is ready, information will be transferred at a rate of one word each computer cycle (1.75  $\mu$ sec) until the word count placed into the A register (which is counted down by one each I/O cycle) or until the external unit supplied the terminate signal Bt.

#### Input (BPI)

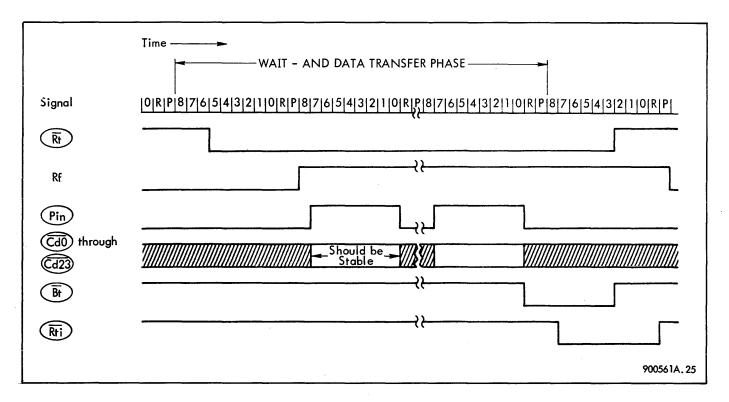

The computer remains in the wait and data transfer phase until ready detector flip-flop, Rf, is set by the externally supplied ready signal (Rt). See figure 2-5.

$$sRf = (\emptyset 2 \ \overline{O5} \ O6 \ T_p) Rt$$

$$rRf = (\emptyset 2 \ \overline{O5} \ O6 \ T_p) \overline{Rt}$$

The computer supplies a Pin signal each time a word is being transferred into the C register.

Pin =

$$(\emptyset 2 \ O6) (T7-T0) \ \overline{Ts} \ O2 \ Rf$$

This process continues until the word count reaches zero or until the external unit supplies a ground to the terminate signal line Bt. Either condition causes the computer to exit from the wait and data transfer phase at pulse time Tp. The computer now generates the transfer complete signal Rti.

Rti =

$$(\emptyset 4 \ \overline{O1} \ \overline{O4} \ O6) \ \overline{Ts} \ (T7-Tr)$$

If the external unit cannot supply information each 1.75  $\mu$ sec, the ready signal line Rt, can be used as a clock to synchronize the operations.

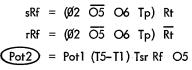

#### Output (BPO)

The computer enters the wait and data transfer phase and supplies the Pot1 signal. The external unit must supply the ready signal, Rt, before the computer can generate the Pot2 signal. The Rt signal sets the ready detector

Figure 2-5. Signals Generated by 925 BPI Instruction

flip-flop Rf in the same manner as for block parallel inputs. See figure 2-6.

The Pot2 signal can be used by the external unit to strobe the C register outputs. This process continues until the word count reaches zero or the external unit supplies a ground on the terminate signal line Bt. Bt is recognized at pulse time Tp, and therefore must be low for at least one cycle to ensure acknowledgement. Either condition causes the computer to exit from the wait and data transfer phase at pulse time Tp.

As in block input operations the ready signal line,  $\overline{Rt}$ , can be used as a clock to synchronize the block parallel output operation.

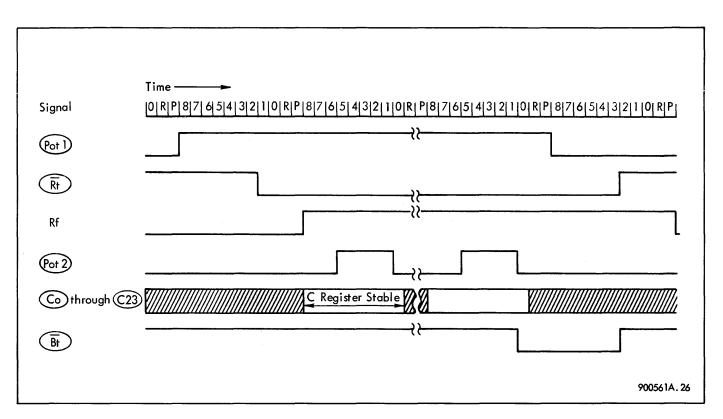

# SKIP IF SIGNAL NOT SET (SKS)

The SKS instruction provides a means of program sensing both internal and external conditions. This instruction operates in four basic modes that are program selectable by the setting of two bits (C10 and C11) within the SKS instruction format.

| <u>C10</u> | <u>C11</u> | <u>Mode</u>           |

|------------|------------|-----------------------|

| 0          | 0          | Special Internal Test |

| 0          | 1          | Channel/Device Test   |

| 1          | 0          | Internal Test         |

| 1          | 1          | System Test           |

Only channel/device test and system test are available to the external equipment, and will be described.

The SKS system test mode is divided into two submodes (system test external, and system test internal) by gating bit 9 with bits 10 and 11. This is necessary if the two submodes of the EOM system control are utilized. Refer to paragraph on system control EOM.

| <u>C1</u> | <u>C9</u> | <u>C10</u> | <u>C11</u> |                            |

|-----------|-----------|------------|------------|----------------------------|

| х         | 0         | 1          | 1          | SKS System Test (External) |

| х         | 1         | 1          | 1          | SKS System Test (Internal) |

The SKS instruction tests the status of signals supplied to the computer by peripheral devices or system equipment. If the signal is low, the next instruction in sequence is skipped. If this signal is positive, the program does not skip but continues in its normal sequence. Cl must always be included in the decoding circuitry since the term Cl separates the Data Multiplex System  $\overline{(C1)}$  from other I/O units (C1).

The SKS instruction requires two computer cycles (3.5  $\mu sec)$  if no skip occurs, and three cycles (5.25  $\mu sec)$  if a skip does occur.

# **SKS Interface Signals**

The following signals necessary to implement the SKS tests are available at the I/O connectors on each TMCC and DACC. See figure 2-7.

Figure 2–6. Signals Generated by 925 BPO Instruction

Figure 2-7. Signals Generated by SKS Instruction

a. (Skss) - This signal is generated by each SKS instruction and indicates that the C register outputs (C1), C9 through C23) are stable and may be decoded by external equipment prior to supplying the computer with the test signal. The external equipment should decode all available bits (C1), C9 through (C23)) since some configurations have been pre-assigned for use with standard equipment such as data multiplexing systems, message switching, etc.

The (Skss) signal is true from T6 - Tr of the second cycle of the SKS instruction if bit C9 is true. If bit C9 is false, (Skss) is true from T7 of the first cycle through Tr of the second cycle. (Skss) is inhibited during a time-share operation. If a time-share operation occurs during either of the first two cycles of an SKS instruction, both cycles will be repeated at the completion of the time-share operation.

- b. Sio This signal is generated by peripheral devices when Skss is true during the SKS instruction, channel/device mode. The C register bits C1, C9, C10, and C11 are decoded internally and need not be decoded externally to determine channel/device mode. Bits C12 through C23 must be decoded to select the desired device. A zero volt condition on this line causes the computer to skip the next instruction in sequence.

- c. (Ssc) This signal is generated by external system equipment when (Skss) is true during the SKS instruction, system mode. The C register bits C1 and C9 must be decoded externally to determine system test external mode with bits C12 through C23 providing the desired single-bit input address.

# SECTION III INPUT/OUTPUT CHANNEL DESCRIPTION

#### GENERAL

This section describes the optional features, timing considerations, and interfacing requirements of the several input/ output channels available to the SDS 925/930/9300 Computers – the TMCC, DACC, DMS, MIC, and Priority Interrupts.

#### TIME MULTIPLEXED COMMUNICATION CHANNEL (TMCC)

The TMCC is a time multiplexed input/output channel for communication between a peripheral device and the SDS 925/930/9300 Computers. Its operation is designated "time multiplexed" because it gains access to the computer memory through the same path utilized by the computer and must therefore momentarily interrupt computation to store or obtain a word of information. Up to four TMCC's may be connected to one computer and all may be active simultaneously. Since their operation is time multiplexed, however, only one channel at a time can communicate with the computer memory.

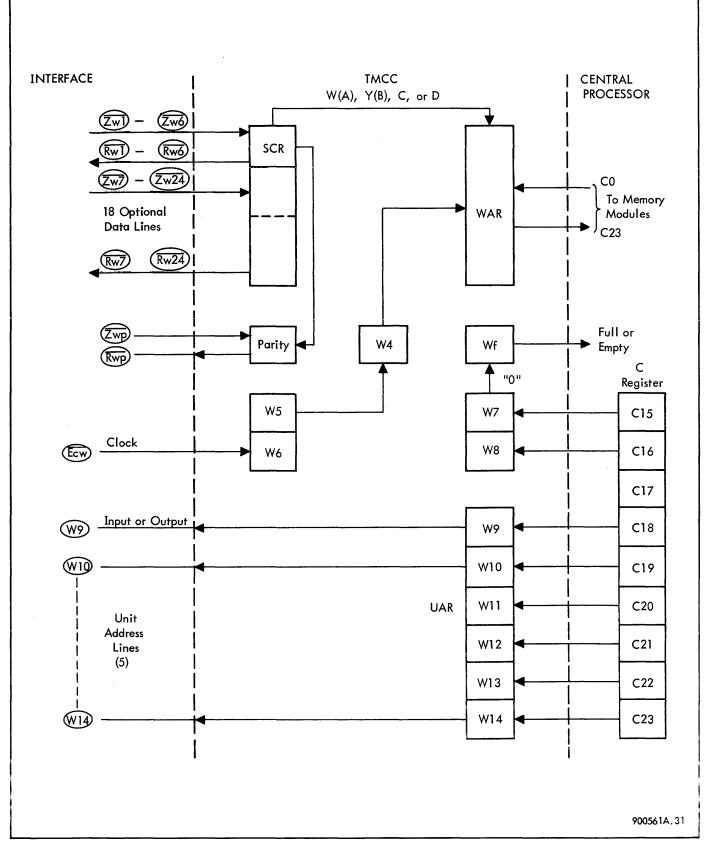

TMCC has two registers for data storage which provide the means to assemble input characters into words or to disassemble words into output characters. The TMCC communicates with the computer by means of a 24-bit Word Assembly Register (WAR) which transfers words between the TMCC and the computer's C register. The TMCC communicates with external systems by means of the bidirectional Single Character Register (SCR) using either a 6-, 12-, or 24-bit character format plus a parity bit. See figure 3-1. The character size depends on the optional registers that may be installed. The number of characters per word is under program control but is limited to a maximum of four 6-bit characters, two 12-bit characters, or one 24-bit character. Mode of transfer is serial by character, parallel by bit. A TMCC having the larger character-length options may be switched from one size to another under control of the external system. The length is selected by activating one of the control lines,  $(W \times 12)$  or  $(W \times 24)$ . A particular device can activate only one of these lines; if none is activated, the TMCC assumes the 6-bit character format. The rate of information transfer is determined by the clock signal (Ecw) from the external device. For both input and output, the TMCC will slave itself to the frequency of the device's clock.

Information may be input or output by executing an instruction for each word. The instruction may be given in advance of the time it is needed, in which case the computer remains idle until the channel is ready. Or the computer interrupt system may be used so that the channel can call for an instruction when it is ready. This allows the computer to continue with other computations when not actually engaged in the I/O process.

#### Unit Address Codes

Sixty-four unit address codes are available to the TMCC. Refer to table 3-1. Two of these codes (00 and 40) are reserved for channel disconnect. While the code 40 will disconnect the channel it is not generally used for this purpose since it does not reset W9 flip-flop as it disconnects.

The remaining 62 addresses are divided into 31 input device codes (W9), and 31 output device codes (W9). When choosing a device code for equipment other than those listed in table 3-1, care must be taken that no code reserved for any magnetic tape operation or for paper tape input be used. If W11 is true (magnetic tape) the buffer will modify the normal terminate condition. If a paper tape input code is used, an all zero character (Rw1 - Rwp = 0) will cause a gap indication to the buffer.

#### Interlace

An optional interlace feature may be installed in the TMCC for either the W or Y channels to facilitate input/output operations with fewer instructions. The interlace logic allows a program to tell the TMCC how many words are to be transferred and the memory location of the first word. Then, with no further instructions, the TMCC will assemble or disassemble the number of words specified and call on the computer each time it is ready to transfer a word to or from memory. Thus, the I/O process may be interlaced with computation or with similar I/O operations on other channels.

Two additional registers are provided with the interlace feature:

- a. Word Counter a 15-bit counter used to store the number of words to be transferred during the interlace I/O operation. With each word transfer, one is subtracted from the number in the counter.

- b. Address Counter a 15-bit register used to store the address of the memory location currently being accessed. Each time a word is taken from or sent to memory, a one is added to the number in this register.

#### Input

A brief description of a non-interlaced process follows. The TMCC is initialized by an EOM instruction, buffer control

| Code | Unit                                    | Code | Unit                                     |  |  |  |

|------|-----------------------------------------|------|------------------------------------------|--|--|--|

| 00   | Disconnect                              | 40   |                                          |  |  |  |

| 01   | Type Input No. 1                        | 41   | Type Output No. 1                        |  |  |  |

| 02   | Type Input No. 2                        | 42   | Type Output No. 2                        |  |  |  |

| 03   | Type Input No. 3                        | 43   | Type Output No. 3                        |  |  |  |

| 04   | Paper Tape Input No. 1                  | 44   | Paper Tape Punch Output No. 1            |  |  |  |

| 05   | Paper Tape Input No. 2                  | 45   | Paper Tape Punch Output No. 2            |  |  |  |

| 06   | Card Reader Input No. 1                 | 46   | Card Punch Output No. 1                  |  |  |  |

| 07   | Card Reader Input No. 2                 | 47   | Card Punch Output No. 2                  |  |  |  |

| 10   | Magnetic Tape Input No. 0               | 50   | Magnetic Tape Output No. 0               |  |  |  |

| 11   | Magnetic Tape Input No. 1               | 51   | Magnetic Tape Output No. 1               |  |  |  |

| 12   | Magnetic Tape Input No. 2               | 52   | Magnetic Tape Output No. 2               |  |  |  |

| 13   | Magnetic Tape Input No. 3               | 53   | Magnetic Tape Output No. 3               |  |  |  |

| 14   | Magnetic Tape Input No. 4               | 54   | Magnetic Tape Output No. 4               |  |  |  |

| 15   | Magnetic Tape Input No. 5               | 55   | Magnetic Tape Output No. 5               |  |  |  |

| 16   | Magnetic Tape Input No. 6               | 56   | Magnetic Tape Output No. 6               |  |  |  |

| 17   | Magnetic Tape Input No. 7               | 57   | Magnetic Tape Output No. 7               |  |  |  |

| 20   |                                         | 60   | High-Speed Printer Output No. 1          |  |  |  |

| 21   |                                         | 61   | High-Speed Printer Output No. 2          |  |  |  |

| 22   |                                         | 62   |                                          |  |  |  |

| 23   |                                         | 63   |                                          |  |  |  |

| 24   |                                         | 64   | Incremental Plotter Output No. 1         |  |  |  |

| 25   |                                         | 65   | Incremental Plotter Output No. 2         |  |  |  |

| 26   | Disc File or Auxiliary Drum Input No. 1 | 66   | Disc File or Auxiliary Drum Output No. 1 |  |  |  |

| 27   | Disc File or Auxiliary Drum Input No. 2 | 67   | Disc File or Auxiliary Drum Output No. 2 |  |  |  |

| 30   | Scan Magnetic Tape No. 0                | 70   | Magnetic Tape Erase No. 0                |  |  |  |

| 31   | Scan Magnetic Tape No. 1                | 71   | Magnetic Tape Erase No. 1                |  |  |  |

| 32   | Scan Magnetic Tape No. 2                | 72   | Magnetic Tape Erase No. 2                |  |  |  |

| 33   | Scan Magnetic Tape No. 3                | 73   | Magnetic Tape Erase No. 3                |  |  |  |

| 34   | Scan Magnetic Tape No. 4                | 74   | Magnetic Tape Erase No. 4                |  |  |  |

| 35   | Scan Magnetic Tape No. 5                | 75   | Magnetic Tape Erase No. 5                |  |  |  |

| 36   | Scan Magnetic Tape No. 6                | 76   | Magnetic Tape Erase No. 6                |  |  |  |

| 37   | Scan Magnetic Tape No. 7                | 77   | Magnetic Tape Erase No. 7                |  |  |  |

Table 3-1. Unit Address Codes

mode. This operation also places the address code for the external device into the Unit Address Register (UAR) and fills the character counter (W7, W8) with the number of characters per word count. Each external device decodes the UAR outputs W9 through W14 and prepares to send information to the TMCC when addressed. The unit address lines W9 through W14 are false when the TMCC is inactive. Once addressed, the external device generates a clock signal Ecw each time a character is ready to be transferred into the TMCC via the data input lines  $\overline{Zw1}$  through  $\overline{Zw24}$  and  $\overline{Zp}$ . See figure 3-2. These data lines are inverted before they are strobed into the data placed on  $\overline{Zw1}$  through  $\overline{Zw24}$  will be received.

$$sRw1 = \overline{W9} \quad W6 \quad \overline{W5} \quad Zw1 + - - -$$

The input data is strobed into the single character register until flip-flop W5 is set. It will be shown later that W5 will set after the input clock signal (Ecw) has been removed.

The TMCC monitors the Zwp input line, checking for parity errors after information is strobed into the single character register. If an error is detected, the error indicator flip-flop, We, is set. The status of this flip-flop can be tested by the program. If the external device does not generate the parity bit (odd parity is used), the parity checking feature can be inhibited by making the interface line (Npw) low during data transfer.

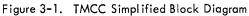

The quiescent state of the signal clock (Ecw) is positive. To initiate a data transfer, (Ecw) must first go low to set clock detector flip-flop W6.

$$sW6 = W5$$

Ecw T8

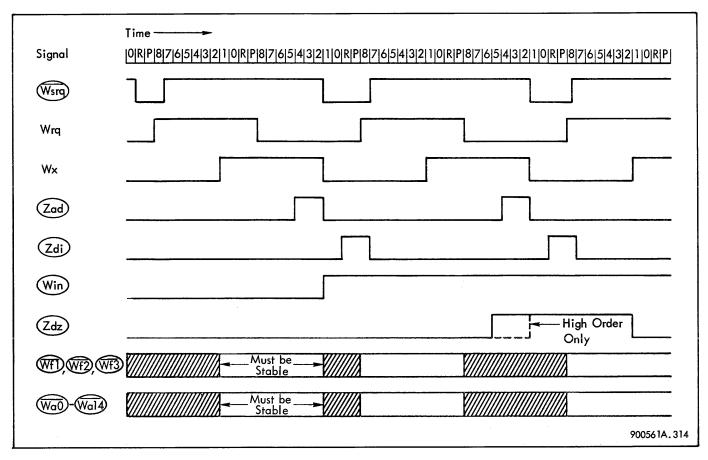

Figure 3-2. Input Timing Characteristics Asynchronous Mode

After W6 is set, the character register is filled

$$sRw1 = Zw1 \overline{W9} \overline{W5} W6 + - - -$$

$$sRw24 = Zw24 \overline{W9} \overline{W5} W6 + - - -$$

and the precess detector flip-flop W5 is set after Ecw goes high.

$$sW5 = \overline{W5} W6 \overline{Ecw} T0$$

The contents of the SCR are now ready to be shifted into the word assembly register under control of flip-flop W4 providing Wf is true.

sW4 = W5 Wf T8 Wg

The Wf signal will be false if the WAR is not able to accept data (the computer has not yet serviced the previous word in WAR because of a higher priority channel requiring access, or because the WIM command has not yet been given). After the shift, W4, W5, W6 and the SCR are reset in preparation for reception of the next character from the external device.

$$rW4 = W4 T0$$

$$rW5 = W4 T0$$

$$rW6 = W5 T0$$

$$rRw1 = \overline{W9} \overline{W6} \overline{W5} \overline{W4}$$

$$\frac{1}{1}$$

$$rRw6 = \overline{W9} \overline{W6} \overline{W5} \overline{W4}$$

This process repeats until the proper number of characters (indicated by the character count register) have been shifted to the Word Assembly Register (WAR). The "buffer full" flipflop, Wf, is then reset to indicate to the computer that a word has been assembled and is ready for transfer to memory. The WIM instruction will perform the actual transfer when the interlace feature is not available. If the WIM instruction occurs before Wf is reset, the computer program will be delayed until the TMCC is full and Wf is reset. If the WIM instruction occurs too late (i.e., after the SCR is ready to shift another character into the WAR) the error detector flipflop, We, is set.

#### Input Clock Characteristics

The Ecw signal from the device indicates to the channel that the character in the SCR has been accepted by the device. Each time a character is accepted by the device (Ecw), the next character is shifted into the SCR unless the character accepted by Ecw was the last character to be output from the channel. If the accepted character was the last character, W6 and W5 will set, W6 will reset, but W5 will remain set resulting in the halt interlock condition  $\overline{W0W5W6}$ .

If the channel is activated to output with no leader (the usual case for output), W5 is set by the Buc-type EOM instruction. W5 will remain set until the word has been transferred from the computer to the channel buffer and the first character is in the character register. When the transfer is complete W5 will reset. When W5 is false the device recognizes that the first output character is ready.

If the channel is activated to output with leader, W5 is reset, indicating to the output device that the character is ready. The character register and the parity output are in the reset condition.

Figure 3-2 shows the characteristics of a typical input clock signal and its relationship to the input data and clock counter flip-flops. An examination of this figure and the equations for W4, W5 and W6 will show that if the data is sampled by W6  $\overline{\text{W5}}$  it should be stable during this time.

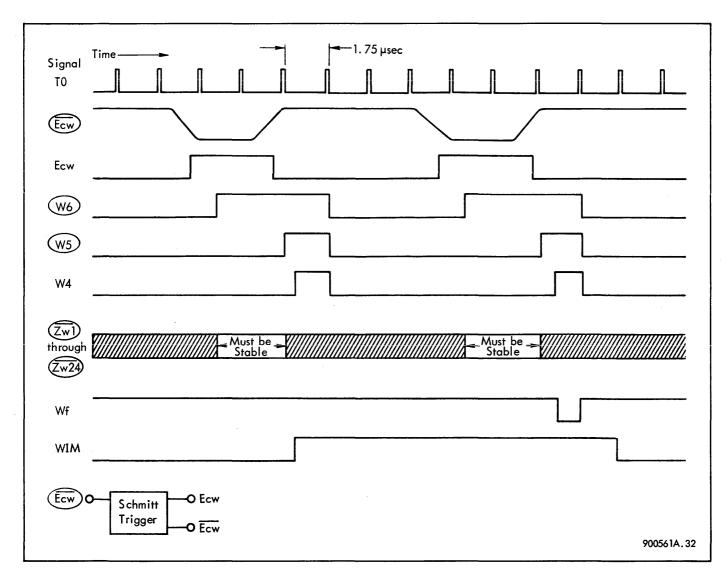

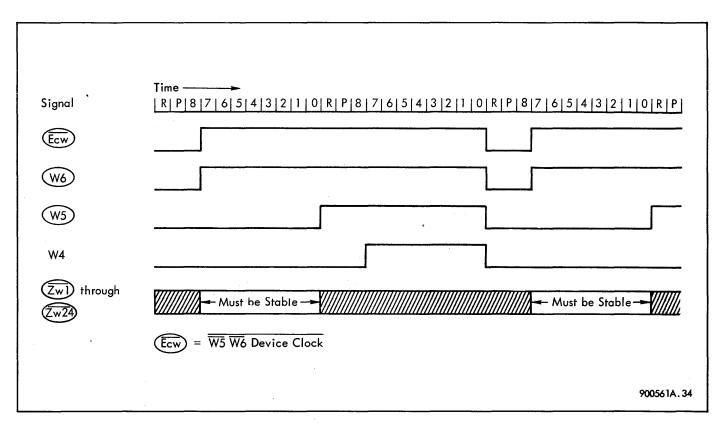

Figure 3-3 illustrates two detailed examples of the clock signal, Ecw. In examining these figures, bear in mind that to be assured of a timing pulse occurring during the off (to set W6) and on (to set W5) periods of Ecw., each of these periods must be at least one machine cycle in length. This prescribes an input clock cycle of no less than two machine cycles. Actually, the clock rate must be somewhat slower than this for proper operation of W6, W5, and W4. Figure 3-3a shows two input clocks with timing such that the second clock is missed. Ideally, any clock rate slower than that of figure 3-3a would be satisfactory; however, a safety margin must be provided to compensate for noise and variations in waveshape and frequency. The input frequency may be increased as shown in figure 3-3b if the clocks are interlocked with W5 and W6 such that

$$\overline{\text{Ecw}}$$

=  $\overline{\text{W5}}$   $\overline{\text{W6}}$  Device Clock

In this case, only two machine cycles per input clock are needed. Some of the peripheral device couplers already include this feature. Gating the device clock with W5 W6 does not necessarily mean that the Ecw signal will appear to by synchronous in respect to itself; that is, that it will always be low for the same time duration. Ecw can be low for as much as seven pulse times or for as little as a single pulse time, depending upon when the device clock falls in relationship to pulse time T8.

If the clock rate is too fast, the error detector flip-flop will be set.

sWe = W0

$$\overline{W6}$$

W5 Ecw T8 + - - -

This equation, in effect, says that an error indication will occur if the clock signal Ecw is received before the previous character has been shifted out of the character register. When the interlock feature of figure 3-3b is employed, the condition W6 W5 Ecw cannot occur to set We. Under such circumstances, the external device must be capable of detecting its own rate errors and reporting them via the Wes line available to the interface connector.

$$sWe = Wes + - - -$$

The Wes line can be used for indicating an error condition by an external device during either input or output operations. Input timing characteristics with synchronous clock is shown in figure 3-4.

#### **Input** Termination

Terminating an input operation can take place in one of several ways. The simplest procedure is to program an EOM instruction to disconnect the external device after a predetermined number of WIM instructions have been processed. Special logic within the TMCC will cause automatic disconnect of paper tape input when "Leader" (all zeros) is read.

A more common method of terminating inputs is by external control of the end-of-record line, Whs. The Whs line when held low (0 volts) by the external device will cause the TMCC disconnect sequence.

# **Output Timing**

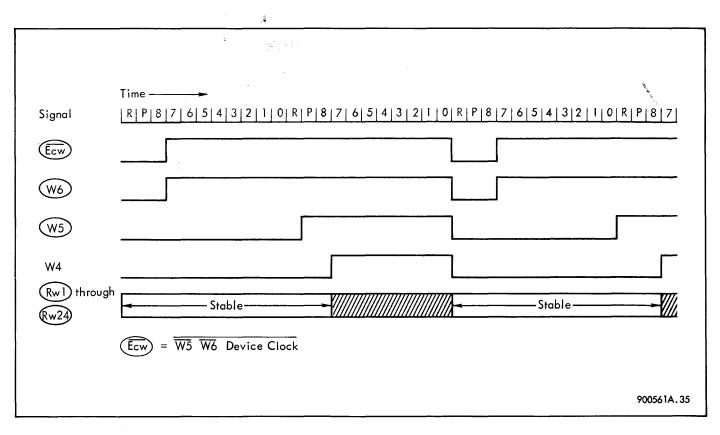

An EOM instruction, buffer control mode, enables the TMCC for outputs in a manner similar to that described for inputs. The EOM instruction must be followed closely by a MIW instruction to fill the Word Assembly Register (WAR). The external device must again decode the unit address register outputs, W9 through W14, before supplying output clock signals. The clock signal, Ecw characteristics are the same as for inputs and should be interlocked with TMCC terms, W5 and W6, to prevent clock signals at excessive rates and to prevent clocks before the word assembly register is filled. See figure 3-5.

The single character register outputs, Rw1 through Rw24, and parity output Rwp, are initially set false. For outputs requiring "leader" (such as for paper tape punch) these outputs will remain false until the external device supplies a clock signal.

Figure 3-3. Input Clock Timing Diagram

Figure 3-4. TMCC Input Timing, Synchronous Clock

Figure 3-5. TMCC Output Timing, Synchronous Clock

Where "leader" is not requested, the first character is precessed into the SCR immediately after the MIW instruction. In this case W5 will be true until the SCR is filled.

An odd parity bit is generated by the TMCC for each output character.

# **Output Termination**

Terminating an output can be accomplished in several ways. The simplest method is to follow the MIW instruction which loads the last output word into the WAR with a "terminate output" EOM instruction. The TMCC will automatically disconnect after the last character has been accepted by the external device. The end-of-record line Whs will also cause automatic disconnect if held low by the external device.

Three signals generated by the TMCC can be combined by the external device to recognize when the last character has been transmitted.

Halt Interlock Signal =  $W5 \overline{W6} \overline{W0}$

The halt interlock signal can be used to alert the external unit to send the end-of-record response signals such as  $\overrightarrow{Whs}$  and  $\overrightarrow{Wes}$  to the TMCC.

# **Interlace** Operation

The interlace feature provides the TMCC with a means for transferring blocks of words without requiring a separate instruction for each word to be transferred. The interlace operation falls into two categories - compatible and extended. The two modes differ basically in the methods used for terminating an input/output process. The compatible mode is directly compatible with the SDS 920 Computer. The types of interrupts that can be requested in the compatible mode are the End-of-Word and End-of-Transmission interrupts. The extended mode expands the I/O capability to include additional termination methods utilizing countequal-zero and end-of-record interrupts. The I/O mode is selected by the binary state of bit 12 of the EOM instruction, where bit 12 = 0 causes the system to operate in the compatible mode, and where bit 12 = 1 causes the system to operate in the extended mode.

As far as the interface signals are concerned, the compatible mode allows the TMCC to operate in the manner described previously. However, the extended mode provides additional terminating options as outlined in table 3-2. The method of terminating is determined after the interlace has been alerted by bits 15 and 16 of the EOM instruction.

|                                                          | EOM | Instru | ction |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------|-----|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Terminal Function                                        | C12 | C15    | C16   | Summary of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IORD<br>Input/output of<br>record then<br>disconnect.    | 1   | 0      | 0     | The I/O operation proceeds until the word count equals zero then terminates.<br>On input, the channel disconnects when the End-of-Record is encountered.<br>On output, the channel signals the device that the last character has been<br>transmitted then disconnects after the device provides an End-of-Record<br>response.                                                                                                                                                    |

| IOSD<br>Input/output until<br>signal then<br>disconnect. | 1   | 0      | 1     | The channel disconnects when the word count equals zero or at the end of a record.                                                                                                                                                                                                                                                                                                                                                                                                |

| IORP<br>Input/output of<br>a record then<br>proceed.     | 1   | 1      | 0     | The I/O operation proceeds until the word count equals zero but does not<br>terminate. On input, the channel sets the inter-record indicator when the<br>end of a record is encountered. On output, the channel signals the device<br>that the last character has been transmitted then sets the inter-record<br>indicator after the device provides an End-of-Record response. The channel<br>does not disconnect (except for magnetic tape when not programmed to<br>continue). |

| IOSP<br>Input/output<br>until signal<br>then proceed.    | 1   | 1      | 1     | When the word count equals zero, the program should either reload the interlace to continue, or terminate the operation before the next clock is received; otherwise a rate error will occur.                                                                                                                                                                                                                                                                                     |

Table 3-2. Interlace Extended Mode Terminal Functions

#### DIRECT ACCESS COMMUNICATION CHANNEL (DACC)

The DACC provides a means of direct memory access by a communication channel, under interlace control, either simultaneous or time multiplexed with computation. The memory access will be simultaneous with computation if the memory bank to be accessed by the channel is not being accessed in computation. If the memory bank to be accessed by the control processor, the transfer will be time multiplexed with computation. The SDS 925 is limited to one memory bank, and therefore

all input/output operations in this computer are time multiplexed with computation.

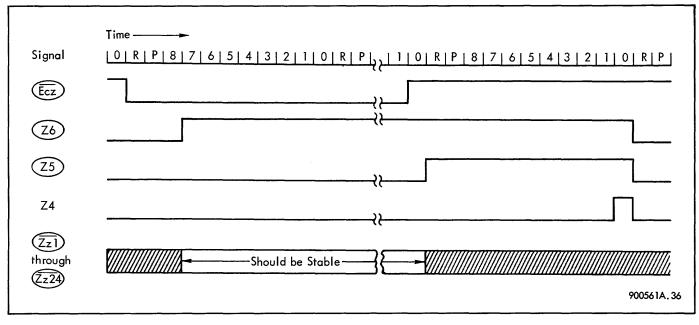

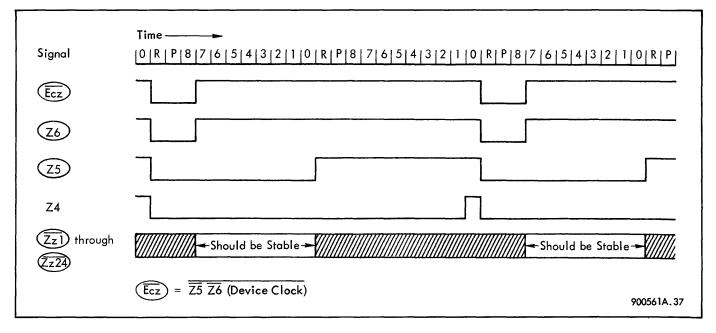

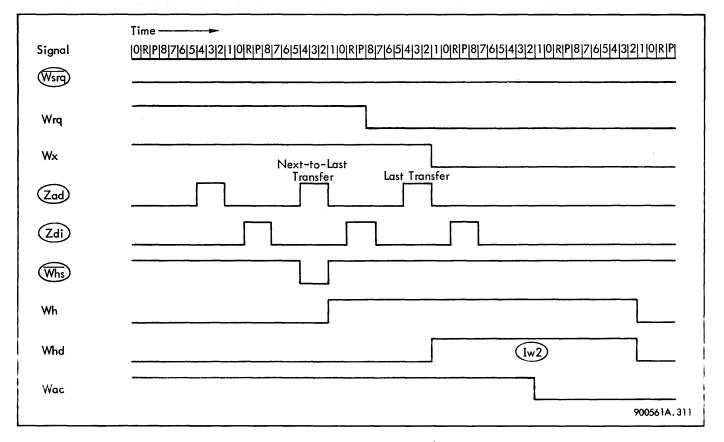

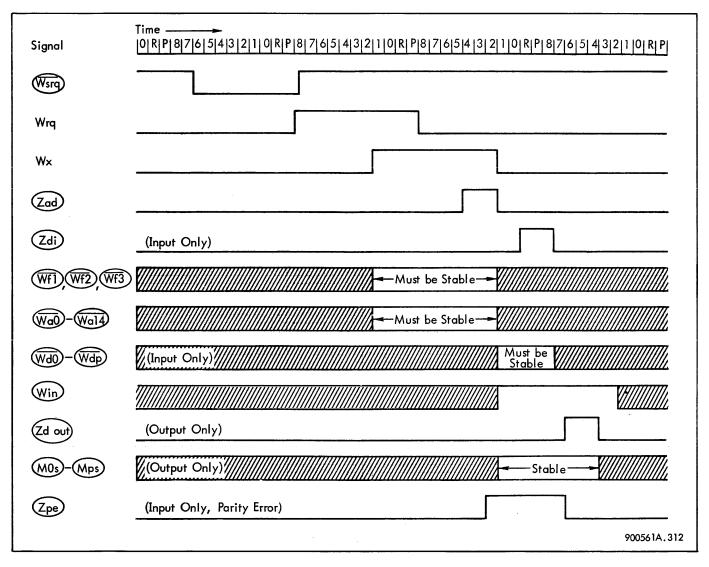

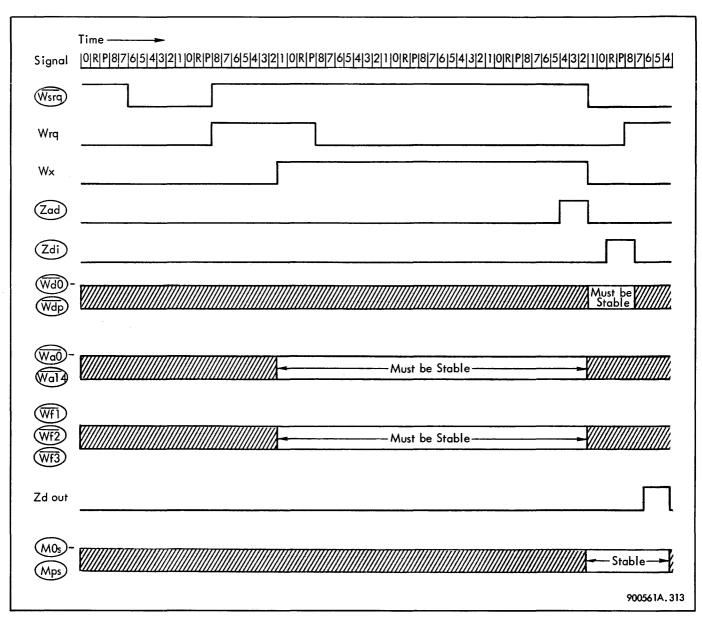

The operation and interface signals for the DACC are similar to the TMCC with interlace. In fact, external units designed to operate with the TMCC are completely compatible and will operate with the DACC (normal mode). Refer to figures 3-6 and 3-7 for timing consideration of the DACC normal mode operation both asychronous and synchronous.

The DACC, however, does have some additional features described in the following paragraphs.

Figure 3-6. DACC Timing, Asynchronous Input Mode

Figure 3-7. DACC Timing, Synchronous Input Mode

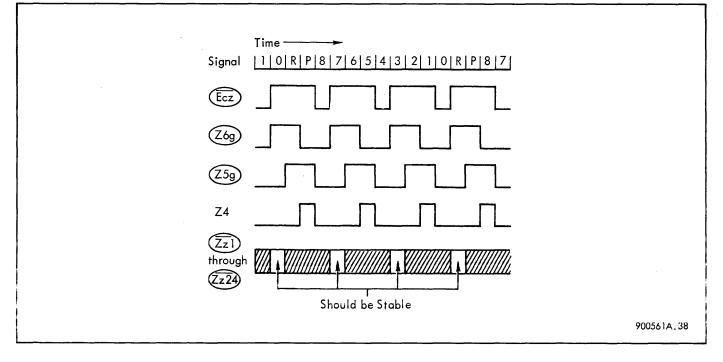

The DACC communicates with an external system by means of a bidirectional 24-bit shift register using 6-, 8-, 12-, or 24-bit characters plus a parity bit. The character size is selected by the external device through activation of one of the control lines,  $\overline{Zx8}$ ,  $\overline{Zx12}$ , or  $\overline{Zx24}$ . A particular device is allowed to activate only one of the lines at any time and does so by causing the line to become false (low) while the device is addressed. If none of the lines is activated when an I/O unit is addressed, the DACC assumes a 6-bit character format. The characters thus transferred are assembled on input, or disassembled on output, in accordance with a word length which is under program control. The computer word contains 24 bits and the programmer may assign any number of characters per word which is within this limit (e.g. a maximum of three 8-bit characters per word). When an input word contains less than the maximum number of characters, the unused bits (in the most significant positions) are undefined. The rate of information transfer is controlled by the input clock signal, (Ecz), supplied by the external device. For both input and output, the DACC will slave itself to the frequency of (Ecz).

Information transfers can occur in either a normal mode or a high-speed mode. The rate is selected by the external device through activation of the high-speed select line,  $\overline{Zft}$ . When operating in the normal mode, the clock signal  $\overline{Ecz}$ , is treated by the DACC in the same manner as it is in the TMCC. However, if the high-speed select line  $\overline{Zft}$  is held false by the external equipment, the clock detector flip-flops, Z5 and Z6, are able to set and reset immediately as the clock goes true and false without waiting for specific pulse times.

$$sZ6 = \overline{Z5} Ecz (---+Zft)$$

$rZ6 = Z5 (---+Zft)$

$sZ5 = \overline{Z5} Z6 \overline{Ecz} (---+Zft)$

$rZ5 = Z4 (\overline{Zx12} + Z15)$

Under these conditions, the input/output rate can be increased from one character every 2 computer cycles to one character every 4 clock periods. Refer to figure 3-8. The input rate of fully assembled words into memory from the DACC cannot exceed the memory cycle time (1.75 µsec). Therefore, in the high-speed mode, care must be taken that the transfer rate of fully assembled words is not greater than one every 1.75 µsec. The DACC memory transfer must be synchronous with the computer cycle, and although five characters can be clocked every two cycles, the maximum transfer rate for 4-character words cannot exceed one transfer every two cycles.

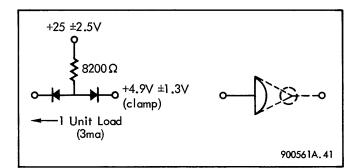

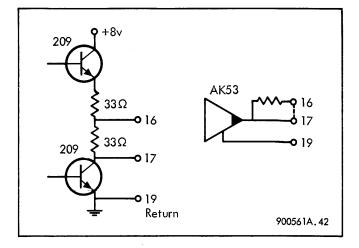

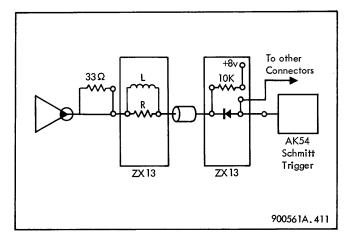

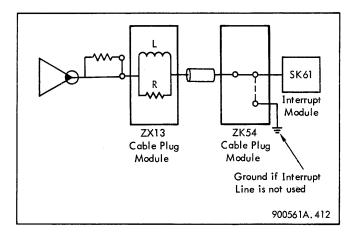

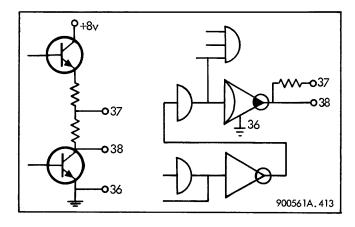

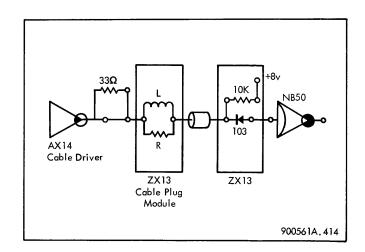

The interface signal lines must be treated differently when operating in the high-speed mode. Typical signal transmission considerations are discussed in Section IV.