IM88-0428-00 HARDWARE INSTRUCTION MANUAL ND 4410 DATA ACQUISITION AND DISPLAY SYSTEM

ND NUCLEAR DATA INC

"THIS DOCUMENT IS THE EXCLUSIVE PROPERTY OF NUCLEAR DATA, INC. AND MAY NOT BE REPRODUCED, NOR MAY THE INFORMATION CONTAINED THEREIN OR DERIVABLE THEREFROM BE USED IN ANY MANNER, EXCEPT BY WRITTEN PERMISSION OF NUCLEAR DATA, INC. THE PROPRIETARY RIGHTS TO THE AFORESAID INFORMATION, BOTH OF A PATENTABLE AND UNPATENTABLE NATURE, ARE EXPRESSLY RESERVED TO NUCLEAR DATA, INC."

## NUCLEAR DATA, INC. Post Office Box 451 Palatine, Illinois 60067

March, 1972

Preliminary Edition

IM88-0428-00 HARDWARE INSTRUCTION MANUAL ND 4410 DATA ACQUISITION AND DISPLAY SYSTEM

> Copyright 1972 by Nuclear Data, Inc. Printed in U.S.A.

"THIS DOCUMENT IS THE EXCLUSIVE PROPERTY OF NUCLEAR DATA, INC. AND MAY NOT BE REPRODUCED, NOR MAY THE INFORMATION CONTAINED THEREIN OR DERIVABLE THEREFROM BE USED IN ANY MANNER, EXCEPT BY WRITTEN PERMISSION OF NUCLEAR DATA, INC. THE PROPRIETARY RIGHTS TO THE AFORESAID INFORMATION, BOTH OF A PATENTABLE AND UNPATENTABLE NATURE, ARE EXPRESSLY RESERVED TO NUCLEAR DATA, INC."

## TABLE OF CONTENTS

## SECTION

1

## TITLE

# PAGE

| INTRC | $DUCTION \dots \dots \square $ |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1-1.  | General Description                                                                                                                                            |  |

| 16.   | Options                                                                                                                                                        |  |

| 18.   | Functional Description • • • • • • • • • • • • • • • • • • •                                                                                                   |  |

| 110.  |                                                                                                                                                                |  |

| 1-14. | ND812 Central Processor 1–5                                                                                                                                    |  |

| 116.  | Control Module                                                                                                                                                 |  |

| 1-18. | Display Oscilloscope                                                                                                                                           |  |

| 120.  | Power Supply                                                                                                                                                   |  |

| 1-22. |                                                                                                                                                                |  |

| EQUIP | MENT PREPARATION                                                                                                                                               |  |

| 2-1.  | General                                                                                                                                                        |  |

| 2-3.  | Preparation for Use                                                                                                                                            |  |

| 2-4.  | Unpacking and Inspection                                                                                                                                       |  |

| 2-6.  | System Installation and Interconnections                                                                                                                       |  |

| 2-10. | Preliminary Check-Out                                                                                                                                          |  |

| 2-12. | Initial Start-Up Procedure                                                                                                                                     |  |

| OPERA | TING INSTRUCTIONS                                                                                                                                              |  |

| 3-1.  | General                                                                                                                                                        |  |

| 3-3.  | Control and Indicator Functions                                                                                                                                |  |

| 3-5.  | Operational Considerations                                                                                                                                     |  |

| 3-6.  | Specific Hardware Considerations                                                                                                                               |  |

| 3-7.  | Analog to Digital Converter Module                                                                                                                             |  |

| 3-16. | Control Module                                                                                                                                                 |  |

| 3-18. | Oscilloscope Calibration                                                                                                                                       |  |

| 3-19. | Pulse Height Analysis Experiment                                                                                                                               |  |

| 3-20. | Specific Software Considerations                                                                                                                               |  |

| 3-21. | ND4410 Instruction Repertoire                                                                                                                                  |  |

Ш

| SECTION |      |                                        |

|---------|------|----------------------------------------|

| IV      | FUNC | TIONAL                                 |

|         | 4-5. | Genera<br>Genera<br>Functia<br>Detaile |

# TITLE

| IV  | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 4-1.General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| V   | MAINTENANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

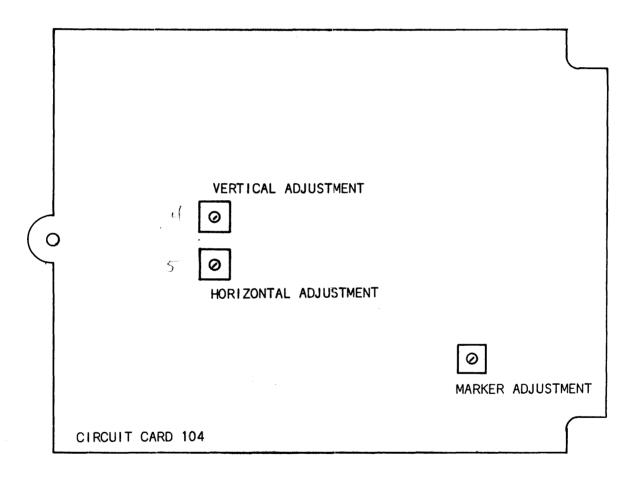

|     | 5-1.General5-15-3.Maintenance Philosophy5-15-6.Equipment Required For Maintenance5-15-8.Maintenance Controls, Indicators, and Test Points5-25-10.Preventive Maintenance5-25-11.Periodic Inspection5-25-12.Performance Standards Tests5-25-15.DC Voltages and Power Distribution Tests5-25-16.ND812 Computer Tests5-35-17.ND4410 Control Module Tests5-35-23.Corrective Maintenance5-65-24.Alignment and Adjustment5-65-27.Horizontal Display Position Adjustment5-65-28.Vertical Display Position Adjustment5-65-29.Display Marker Position Adjustment5-7 |

| VI  | REPLACEABLE PARTS LIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 6-1. General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

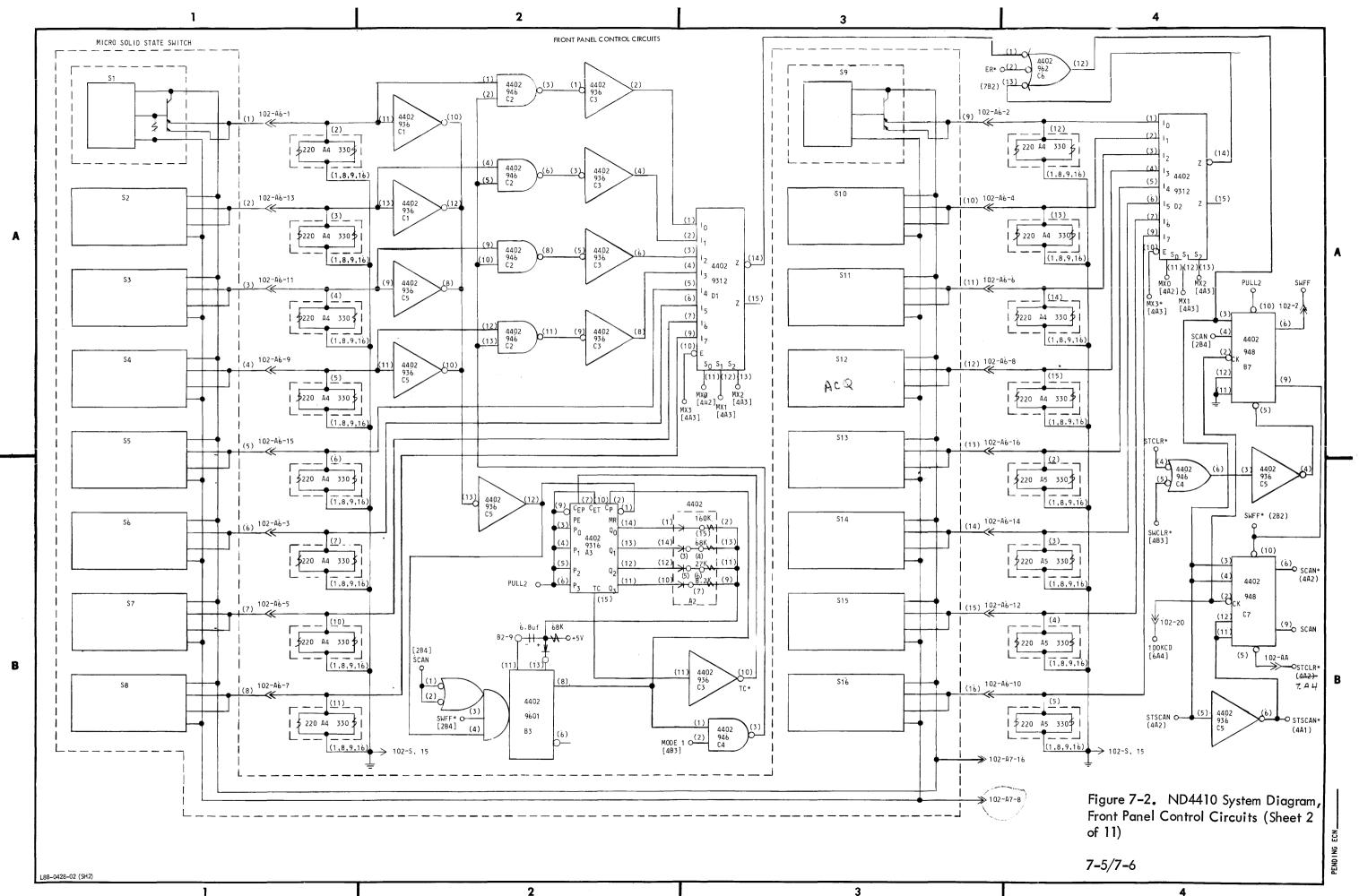

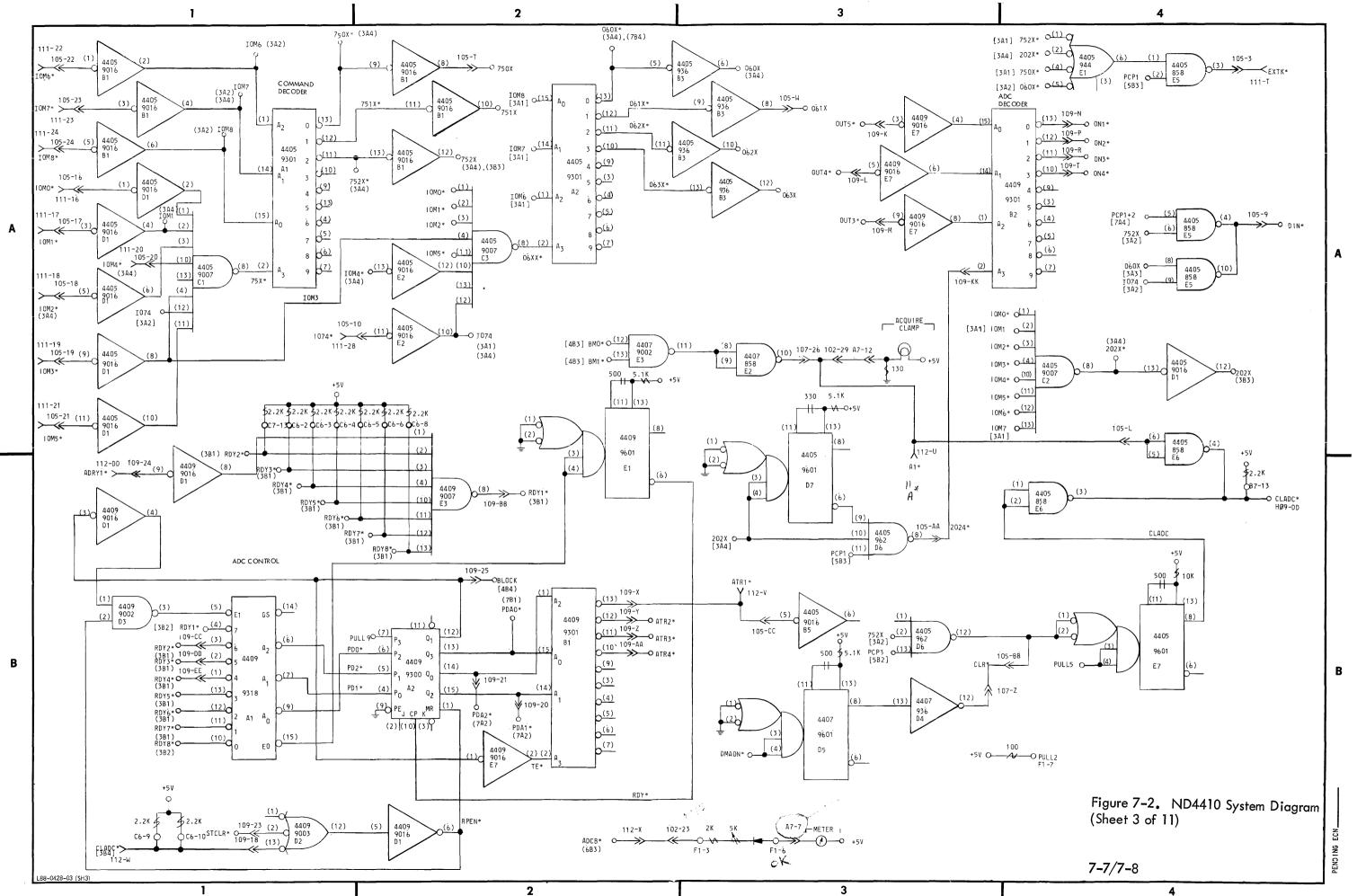

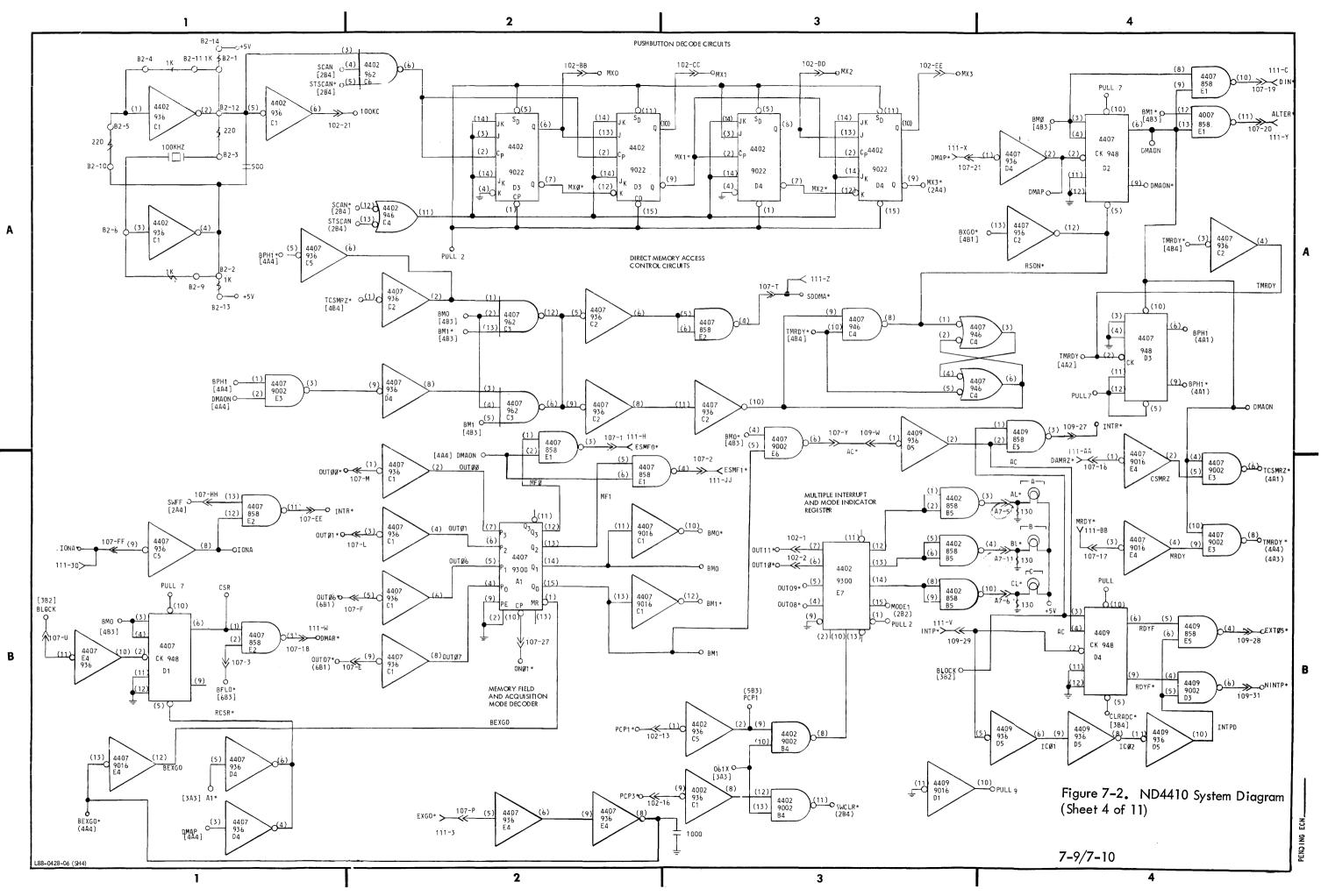

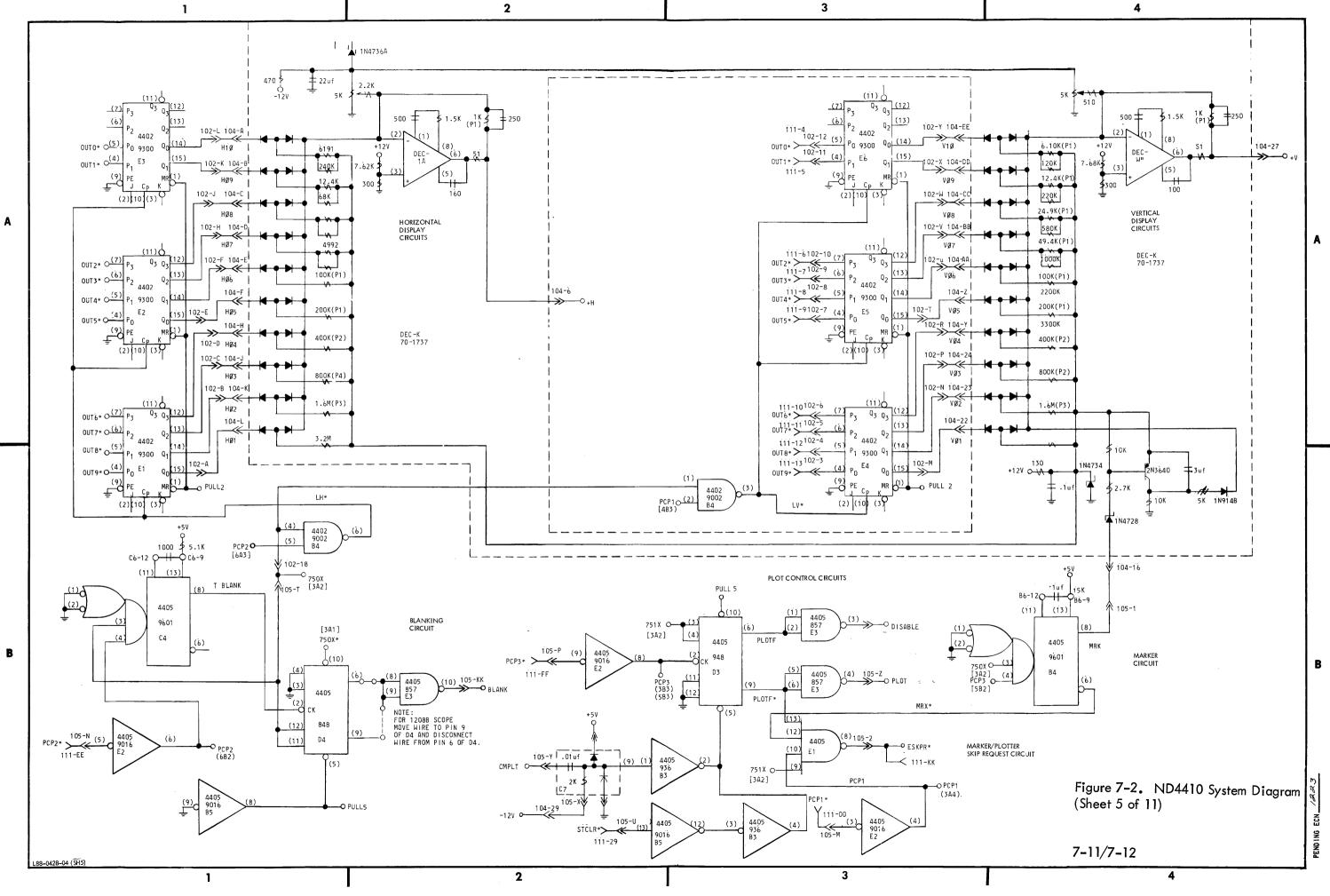

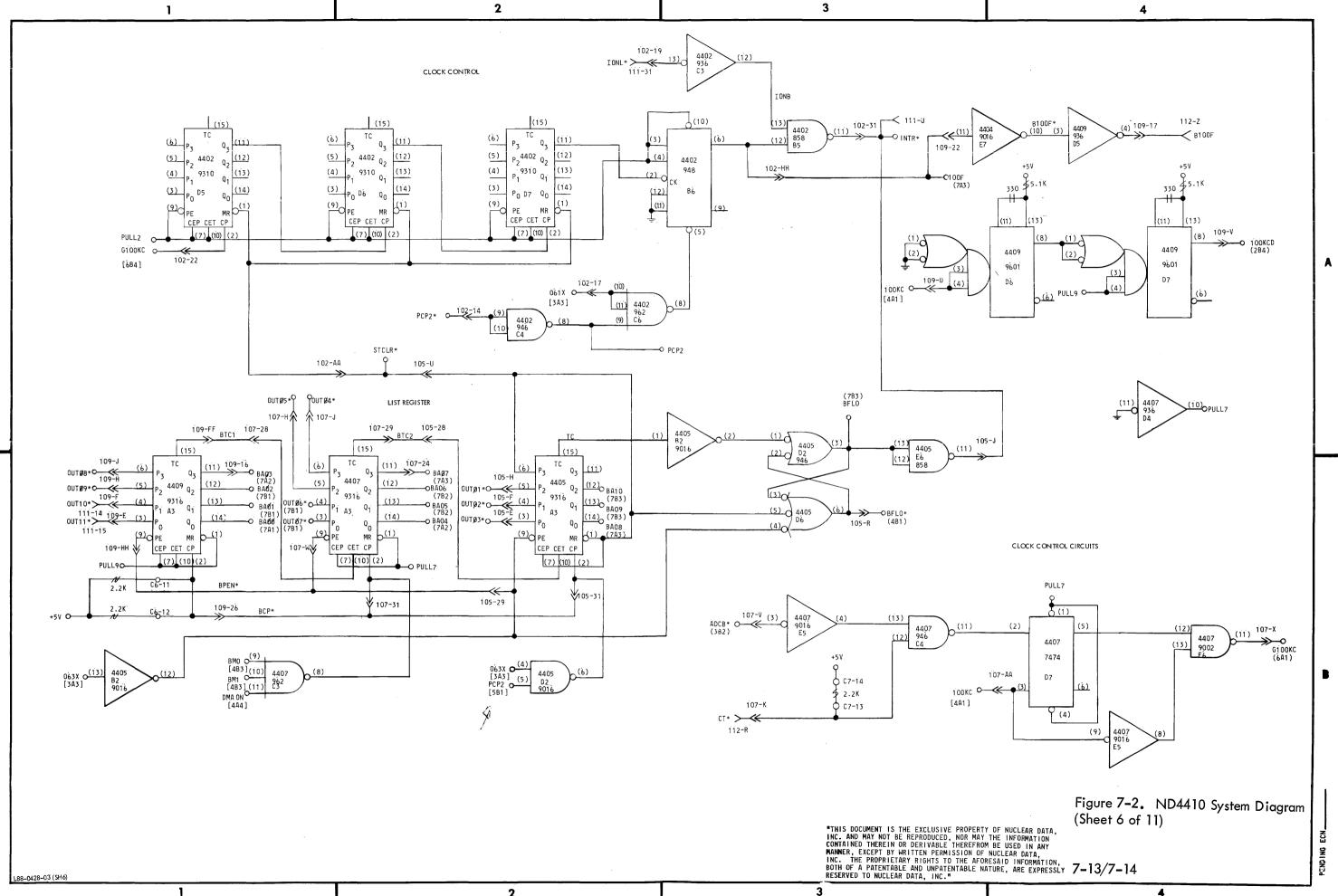

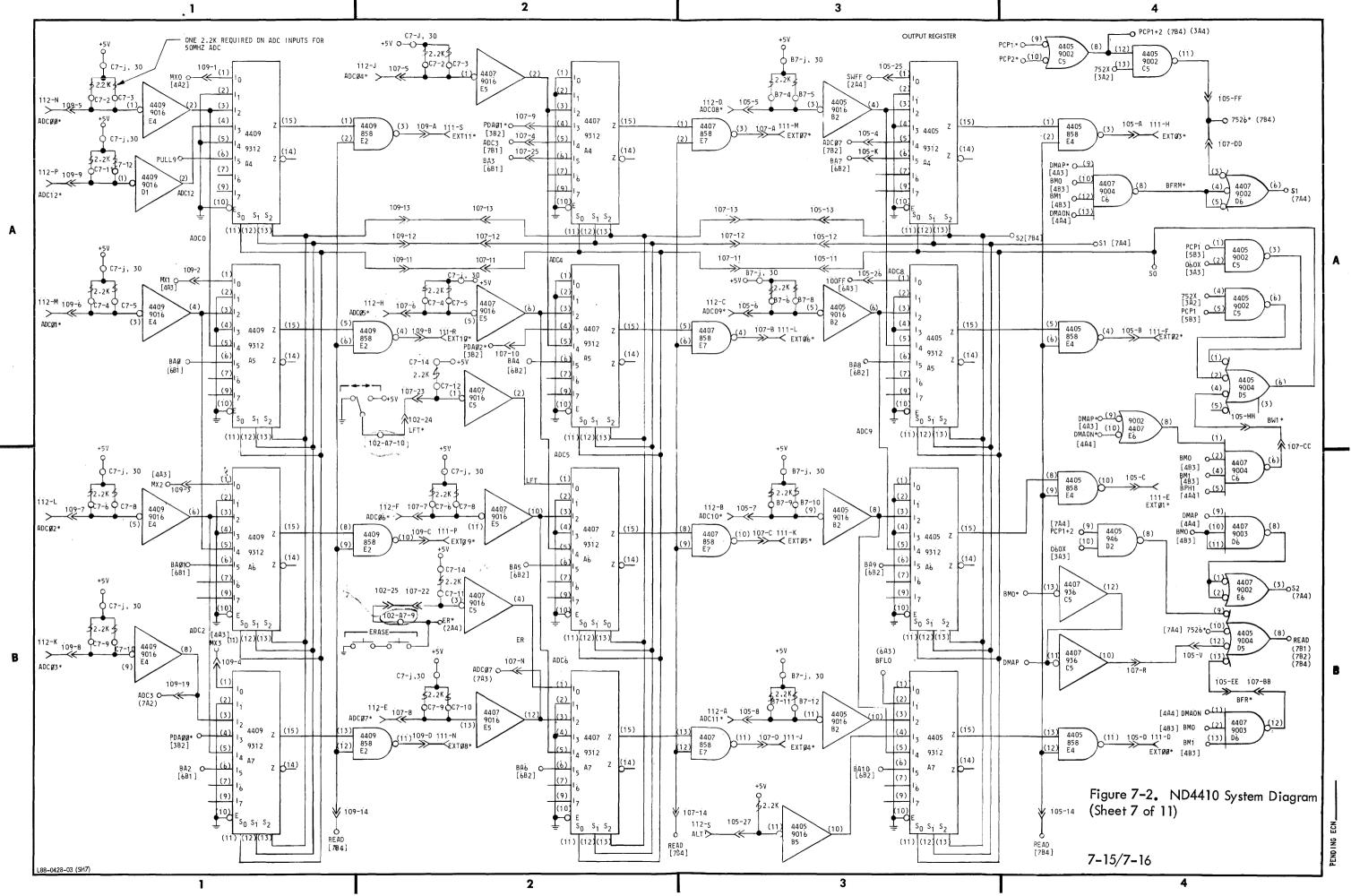

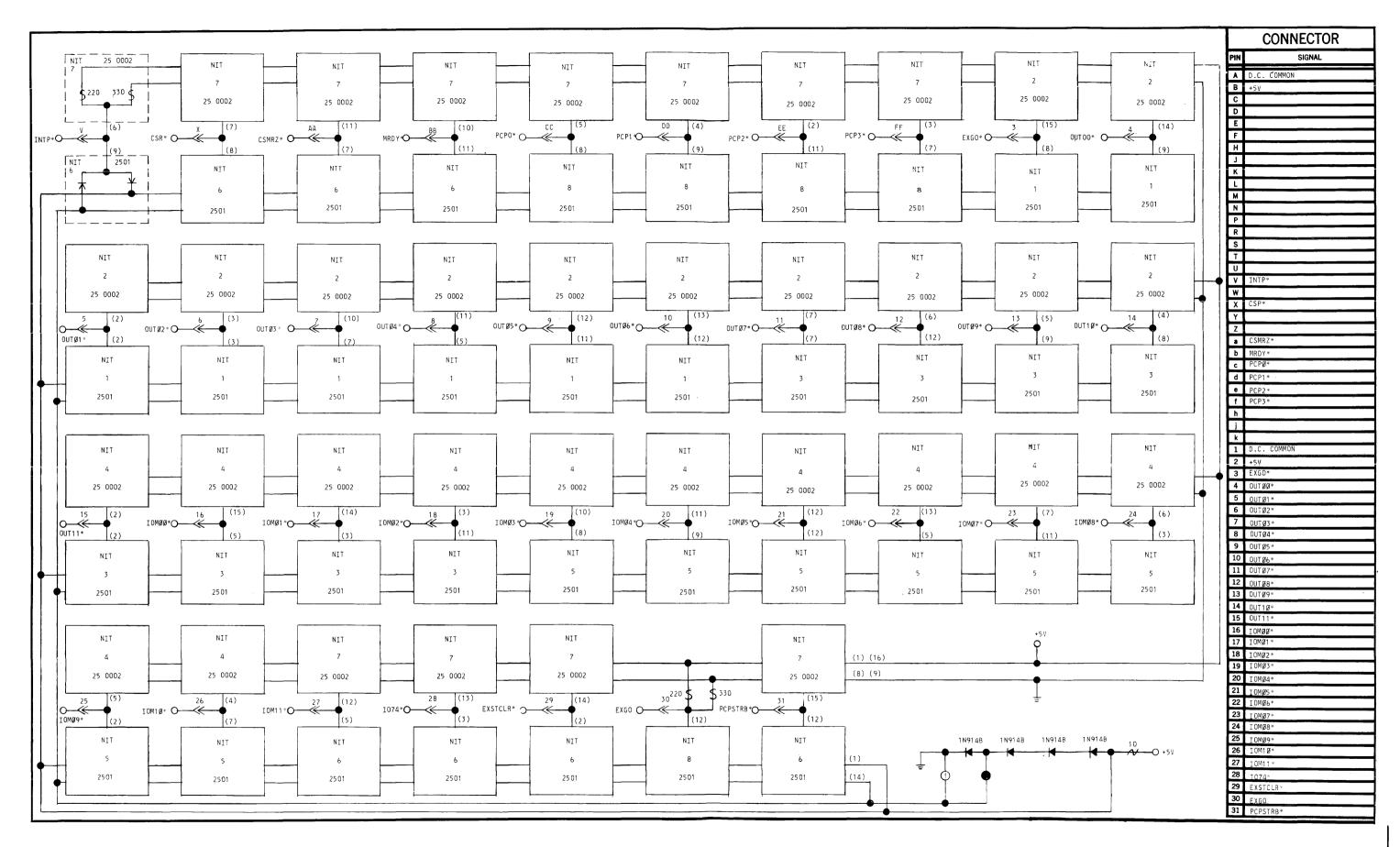

| VII | DIAGRAMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

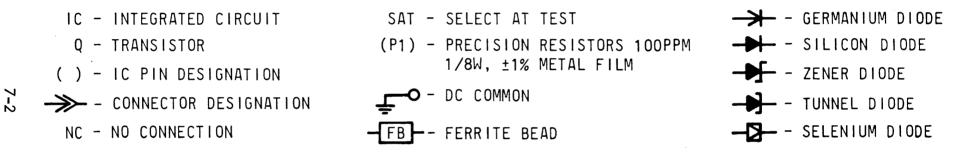

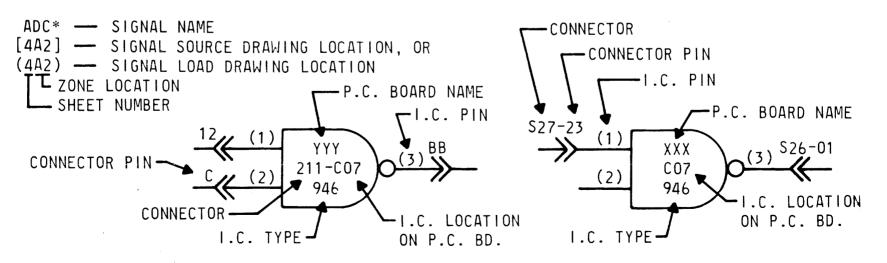

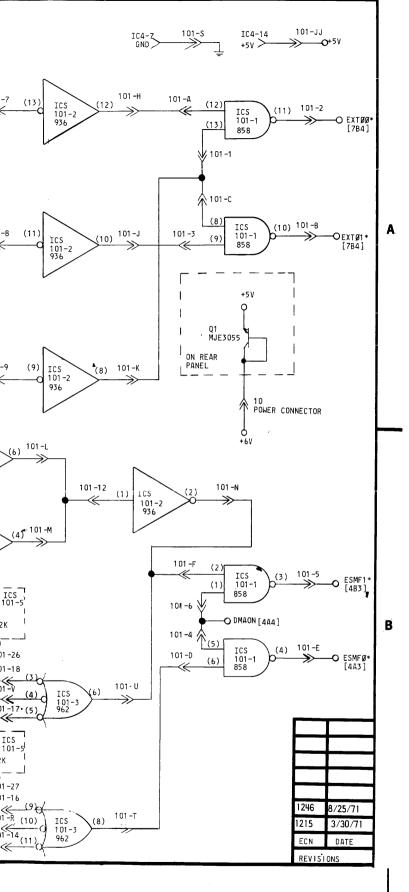

|     | 7-1. General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# LIST OF ILLUSTRATIONS

| FIGURE     | TITLE                                              | PAGE             |

|------------|----------------------------------------------------|------------------|

| 1-1        | ND4410 System with Various Options                 | 1–2              |

| 2-1        | Series 4410 System Interconnection Diagram         | 2 <b>-</b> 5/2-6 |

| 3-1<br>3-2 | Control Module Front Panel Controls and Indicators | 3-2              |

| 0-2        | Experiment                                         | 3-14             |

| 4-1        | Signal Inversion                                   |                  |

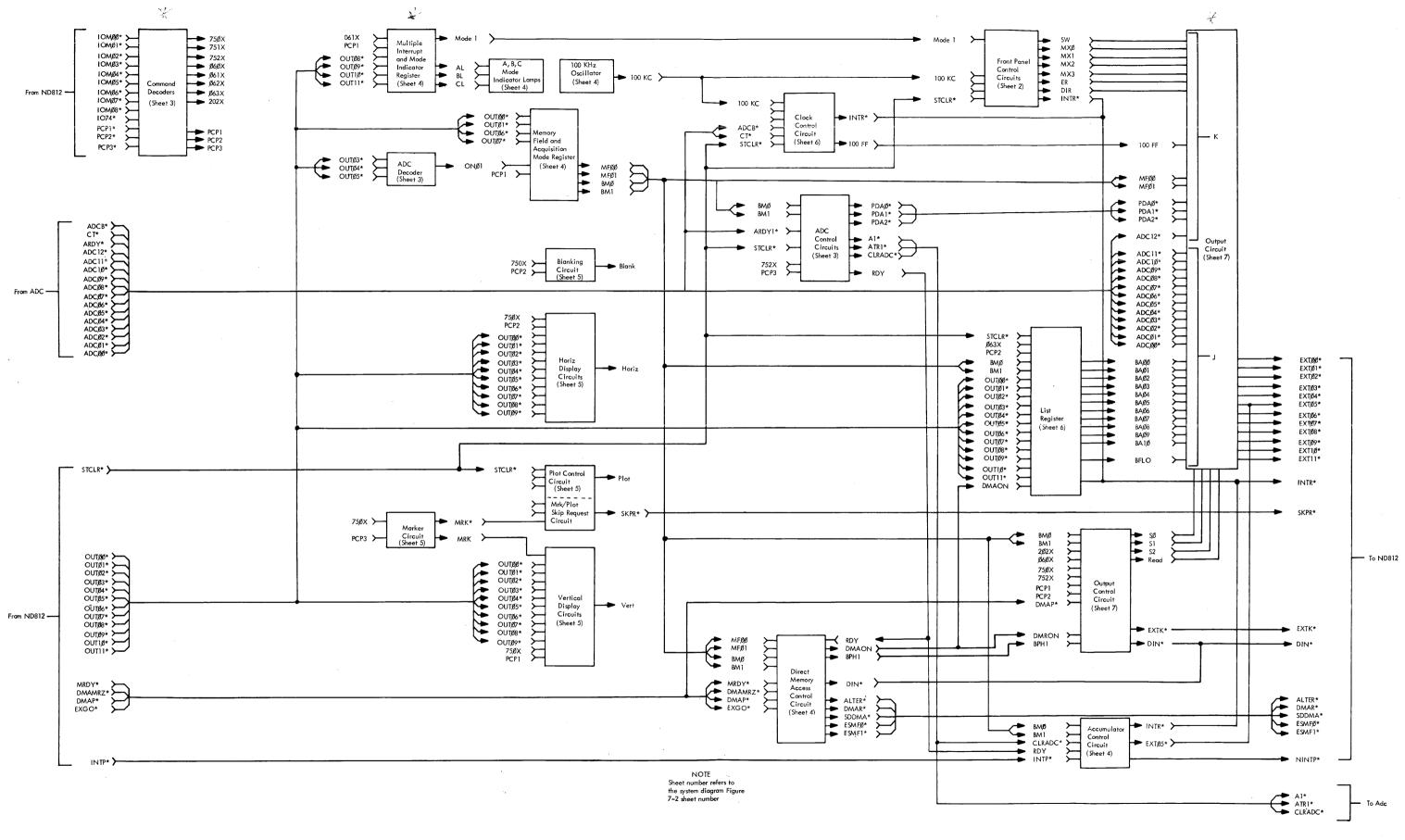

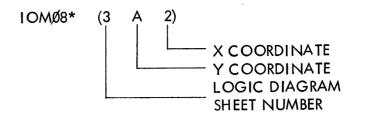

| 4-2        | ND4410 Control Module Functional Block Diagram     | 4-3/4-4          |

| 4-3        | Signal Reference                                   | 4-6              |

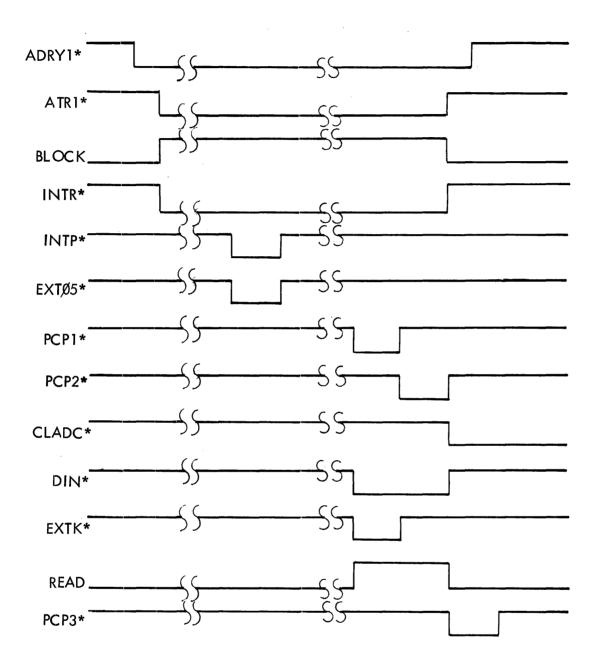

| 4-4        | Program Control Mode Timing Diagram                |                  |

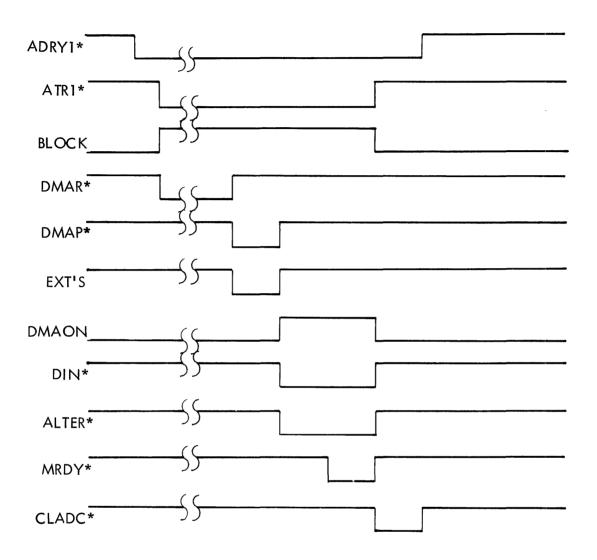

| 4-5        | DMA Increment Mode Timing Diagram                  |                  |

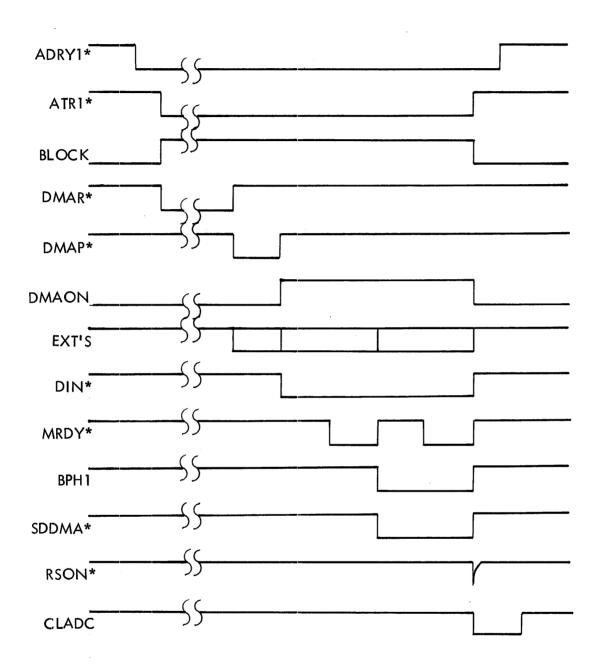

| 4-6        | DMA List Mode Timing Diagram                       |                  |

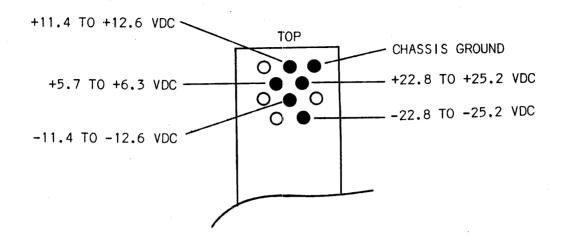

| 5-1.       | NIM Bin Connector, Dc Voltage Requirements         | 5-3              |

| 5-2        | ND4410 Control Module, Adjustment Locations        | 5 <b>-7</b>      |

## LIST OF TABLES

| TABLE | TITLE                                                   | PAGE |

|-------|---------------------------------------------------------|------|

| 1-1   | Basic ND4410 System Components                          | 1-3  |

| 1–2   | ND4410 Options                                          |      |

| 1–3   | ND4410 Control Module, Physical and Functional          |      |

|       | Characteristics                                         | 1-6  |

| 1-4   | ND812 Computer, Physical and Functional Characteristics | 1-8  |

| TABLE             | TITLE                                                                                                    | PAGE                 |

|-------------------|----------------------------------------------------------------------------------------------------------|----------------------|

| 1-5<br>1-6        | 50 MHz ADC, Physical and Functional Characteristics<br>NIM Bin and Power Supply, Physical and Functional | 1-9                  |

|                   | Characteristics                                                                                          | 1-12                 |

| 3-1               | Control Module, Function of Controls and Indicators                                                      | 3-3                  |

| 4-1<br>4-2<br>4-3 | Input/Output Signals, Printed Circuit Board                                                              | 4-16<br>4-20<br>4-22 |

| 5-1<br>5-2<br>5-3 | Required Test Equipment                                                                                  | 5-1<br>5-4<br>5-5    |

| 6–1               | Replaceable Parts List                                                                                   | 6-1                  |

| 7-1               | Diagram Index                                                                                            | 7-1                  |

-

.

## SECTION I. INTRODUCTION

#### 1-1. GENERAL DESCRIPTION

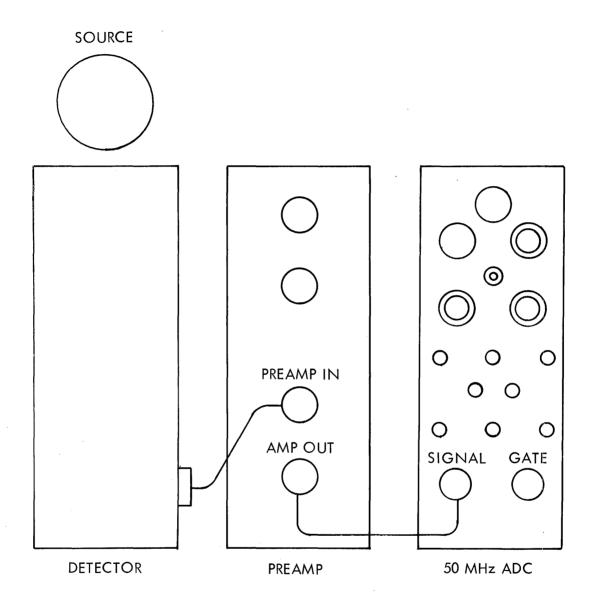

1-2. This manual contains instructions necessary to operate and maintain the ND4410 system, part number 88-0428, manufactured by Nuclear Data, Incorporated. The ND4410 system (figure 1-1) is a single parameter data acquisition and display system used for measurement, storage, display, and processing of data obtained in physical science research.

1-3. The ND4410 basic system consists of a Function Control Module, a 50 MHz Analog to Digital Converter (ADC), a Dead Time Monitor, an ND812 Central Processor with 4K memory (expandable to 16K), a Teletype Interface with Auto Loading, NIM Bin with three connectors, Bin power supply, Tektronix 602 display Oscilloscope (option), and Teletype (option). The basic system can be expanded to include up to eight ADC's (with a digitizing rate of 50 or 100 MHz), and the selection of an 8K, 12K, or 16K ND812 Central Processor (Refer to table 1-1 for description, part number and quantity of basic ND4410 system components). Also, various basic system options and peripheral options are available.

1-4. Several software packages for the ND4410 system are available. Current packages include a Basic Physics Analyzer, a Basic X-Ray Analyzer, and a Floating Point Physics Analyzer. The Basic Physics Analyzer package requires only 2K, 12 bits of core storage, leaving 1K of 24 bits for data storage. The Basic X-Ray Analyzer requires 3K of 12 bits, and the Floating Point Physics Analyzer requires 4K of 12 bits. Information on these packages and packages presently in work are available on request.

1-5. The operation and maintenance instructions contained in this manual cover the basic ND4410 system and are primarily centered around the ND4410 Control Module. Refer to the appropriate instruction manual for specific instructions on the Analog to Digital Converter, Dead Time Monitor, ND812 Central Processor, Teletype Interface with Auto Loading, Bin Power Supply, Display Oscilloscope, Teletype, and all system and peripheral options. Also, refer to the ND4410 Single Parameter Data Acquisition and Display System Software Instruction Manual for specific information on system software.

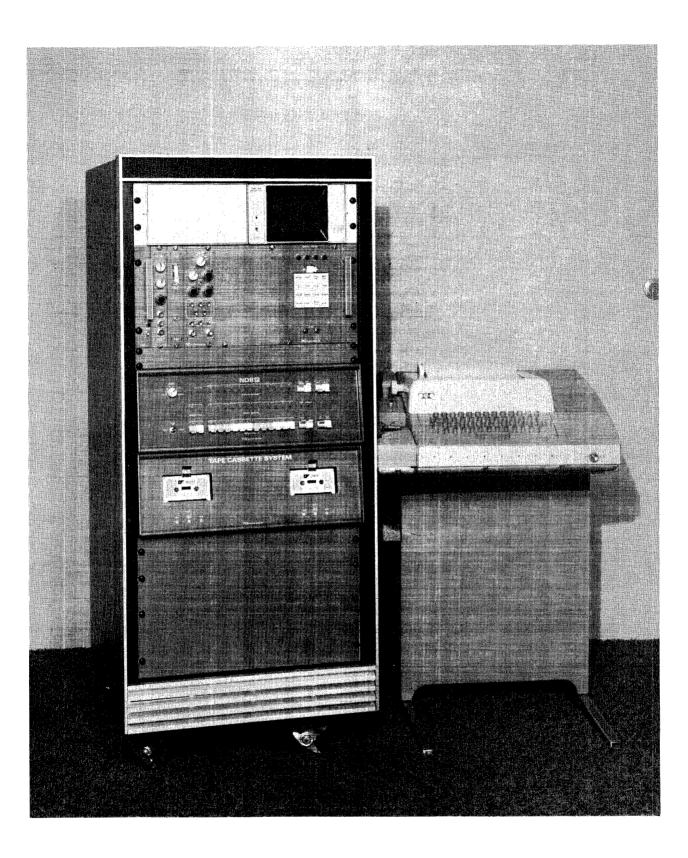

Figure 1–1. Typical ND4410 System with Various Options

| Description                                                | Part Number | Quantity |

|------------------------------------------------------------|-------------|----------|

| ND4410 Function Control Module                             | 88-0428     | 1        |

| ND560 ADC, 4096, 50 MHz                                    | 88-0415     | 1        |

| *ND565TM Dead Time Monitor                                 | 88-0435     | 1        |

| ND812 Central Processor/4K x 12 Bit memory                 | 88-0097/    | 1        |

|                                                            | 88-0096     |          |

| Teletype Interface with Auto Loading                       | 88-0481     | 1        |

| NIM Bin with three connectors                              | 88-0344     | 1        |

| Bin Power Supply, +6 Vdc, 5A; +12 Vdc, 2.5A<br>+24 Vdc, 1A | 88-0297     | 1        |

### Table 1-1. Basic ND4410 System Components

\*Not required when optional 8192, 100 MHz ADC (part number 88-0426) is used.

### 1-6. OPTIONS

1-7. Basic ND4410 system options, peripheral options, and memory expansion options are given in table 1-2. Various bulk storage devices, magnetic tape I/O devices, paper tape I/O devices, hard copy devices, and miscellaneous ND812 options are also available. Information and price list on these devices and options are available on request.

## 1-8. FUNCTIONAL DESCRIPTION

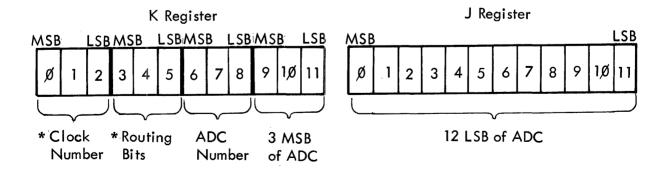

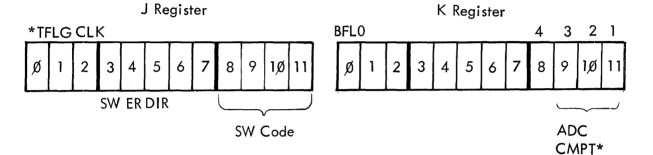

1-9. There are three modes of software-controlled data acquisition. These are Program Control Mode, Buffer or List Mode, and Direct Memory Increment Mode. The Program Control Mode places restrictions on the digitized data following the selection of areas of interest. The 24-bit word transferred contains up to 15 bits of ADC data (32K channels), 3 bits to identify one ADC out of the possible eight, 1 bit for the clock, and 5 unassigned bits. The Buffer or List Mode transfers up to 24 bits directly into the computer memory. The number of ADC's used are initialized by software. The Direct Memory Increment Mode treats the ADC word as an address with the contents of the address being incremented creating a spectrum of counts versus channels.

### 1-10. ANALOG TO DIGITAL CONVERTER MODULE

1-11. The ND560 ADC is a highly versatile analog to digital converter designed for processing amplitude modulated signals, such as are encountered when measuring fast random phenomenon. It may also be used to sample dc or slowly varying voltages.

1-12. Data acquisition efficiency is enhanced by a 50 megahertz digitizing rate. The digitizing oscillator is crystal-controlled to ensure high, long term stability. In addition, all critical circuitry is temperature compensated to ensure drift free operation.

## Table 1-2. ND4410 Options

| Description                                       | Part Number |

|---------------------------------------------------|-------------|

| Basic System Options                              |             |

| ND4410 Digiplex – Two Function Control Module     | 88-0461     |

| ND4410 Digiplex - Two Function Control/Digiplex - | 88-0461/    |

| Four Option                                       | 84-0152     |

| Analog to Digital Converter, 8192, 100 MHz        | 88-0426     |

| Digital Spectrum Stabilizer                       | 88-0058     |

| Two Input Zero Dead Time Multichannel Scaler      | 88-0477     |

| Time of Flight                                    | 88-0145     |

| Eight Input Router                                | 88-0502     |

| NIM Bin – 6 Connectors                            | 88-0300     |

| NIM Bin – 12 Connectors                           | 88-0346     |

| Basic System Peripherals                          |             |

| Teletype Model TC33ASR Combination Punch          | 86-0085     |

| Paper Tape and Page Printer                       |             |

| Tektronix 602 Oscilloscope                        | 86-0140     |

| Rack Mount                                        | 86-0141     |

| Filler Panel                                      | 86-0142     |

| Hewlett Packard Model 1208B Oscilloscope          | 86-0199     |

| Rear Terminal and Blanking Option                 | 86-0200     |

| Hewlett Packard Model 7004B XY Plotter            | 86-0149     |

| Memory Expansion Options                          |             |

| 8K x 12 Bit Memory (4K to 8K Expansion)           | 84-0097     |

| ND812 Memory Extension Unit with                  | 88-0431     |

| 4K x 12 Bit Memory (8K to 12K Expansion)          | 84-0094     |

| ND812 Memory Extension Unit with                  | 88-0431     |

| 8K x 12 Bit Memory (8K to 16K Expansion)          | 84-0095     |

| 8K x 12 Bit Memory (12K to 16K Expansion)         | 84-0095     |

1-13. Conversion gain is selectable in binary increments from 128 to 4096 channels full scale. Front panel selection of group size in binary increments from 64 to 4096 allows resolution up to 4096 channels in a memory group of only 64 channel capacity. A digital zero shift selector is included which utilizes five toggle switches representing 256, 512, 1024, and 2048 channels. By placing these switches in the appropriate positions, the selected channel may be digitally moved to zero, automatically suppressing all previous channels. Any combination of switches may be used providing a maximum zero shift of 3968 channels.

## 1-14. ND812 CENTRAL PROCESSOR

1-15. The ND812 is a general purpose computer designed for the scientific researcher. The basic ND812 contains a 12-bit, 4K memory, with optional 8K, 12K or 16K memories available. This computer is extremely versatile, in that the entire core locations (up to 16K) are directly addressable by using two-word instructions. A total of 256 single-word or 4096 two-word I/O commands are possible. Other outstanding features are the 12 or 24-bit programmed I/O transfer, a four level priority interrupt, four micro-programmable pulses per I/O instruction, direct memory access, four arithmetic registers, hardware multiply and divide, and 100% integrated control logic circuitry.

1-16. CONTROL MODULE

1-17. The Control Module interfaces the ADC's and display scope with the ND812 Central Processor. Sixteen front panel pushbutton switches control the system, establish the number of channels displayed, increasing or decreasing the number of counts full scale, and the position of two data markers. Data contained between the markers can be totalized; read out by channel (with channel ID every eight channels); read out to an X-Y plotter; or altered by addition, subtraction, division and multiplication. A front panel pushbutton switch also initiates display of system parameters on the display oscilloscope.

## 1-18. DISPLAY OSCILLOSCOPE

1-19. The 602 display oscilloscope is a compact, solid state monitor with excellent resolution providing accurate displays of information from X, Y, and Z signal inputs. Display is provided on a 5-inch, flat-faced, rectangular cathode ray tube with an internal graticule. Signal inputs are via BNC connectors on the rear panel.

## 1-20. POWER SUPPLY

1-21. The bin mounted power supply is furnished with a 23-pin female bin interface connector for distributing power to the bin power connectors. The rear panel contains two line fuses, an ac line cord, and a switch for selection of 115 or 230 volt operation. This unit is also equipped with thermal cutouts which disconnect the ac line when the heat sink exceeds the preset temperature.

## **1-22.** SPECIFICATIONS

1–23. Physical and functional characteristics for the ND4410 Control Module, ND812 Computer, 50 MHz ADC, and NIM Bin Power Supply are given in tables 1–3, 1–4, 1–5, and 1-6 respectively. Refer to the appropriate instruction manual for specifications on all other modules and peripheral equipments.

Table 1-3. ND4410 Control Module, Physical and Functional Characteristics

| Characteristic                                                         | Specification                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physical Characteristics<br>Height<br>Width<br>Depth<br>NIM Compatible | 8.71 in<br>5.36 in<br>9.7 in<br>four-wide module                                                                                                                                                                                                                           |

| Functional Characteristics<br>Input/Output<br>Accumulator Mode         | Directly compatible with ND812 I/O Buss.<br>Each event (24 bits) is transferred to the<br>ND812 accumulators. The information<br>contained in the 24 bits is then available<br>for software processing. Communication<br>via the interrupt, "trap" address is<br>provided. |

| List Mode                                                              | Each event (24 bits) is transferred directly<br>to the ND812 memory. The number of<br>events contained in the list and the<br>processing of the list is software selectable.<br>Communication is via direct memory access,<br>transmit.                                    |

| Direct Memory Increment Mode                                           | The ADC address for each event directly<br>identifies a location in the ND812 memory<br>and causes a read, add-1, write at that<br>location. Communication is via direct<br>memory access, increment.                                                                      |

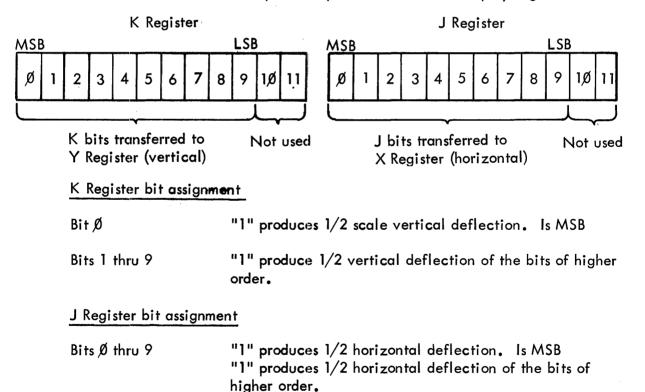

| Display Decoding                                                       | X-Axis: 10 bits<br>Y-Axis: 10 bits                                                                                                                                                                                                                                         |

| Display Output                                                         | Horizontal: 0 to 1V<br>Vertical: 0 to 1V<br>Blanking: +5V on, 0V blank                                                                                                                                                                                                     |

| Characteristic      | Specification                                                                                                                                         |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Display Markers     | Internal circuitry and software selection<br>permit generation on the display scope of<br>a marker (a full–scale vertical line) at<br>any address.    |  |

| Plotter Control     | External connectors and software selection permit analog readout to a plotter, X-Y, incremental, or strip chart.                                      |  |

| Function Control    | 16 software-selection pushbuttons provide control of analyzer functions.                                                                              |  |

| Direction Control   | Two-position switch selects direction of parameter movement.                                                                                          |  |

| Acquisition Control | An internal 100 MHz crystal-controlled<br>time base permits software selection of<br>acquisition time at 10 ms clock or live time<br>gated intervals. |  |

| Data Erasure        | Dual pushbuttons, which must be depressed simultaneously, prevent accidental erasure of stored data.                                                  |  |

| Mode Indication     | Four front panel lamps provide indication of acquisition and display modes.                                                                           |  |

| Power Requirements  | +6 Vdc, 2A<br>+12 Vdc, 50mA                                                                                                                           |  |

Table 1-3. ND4410 Control Module, Physical and Functional Characteristics (Cont'd)

| Characteristic                                       | Specification                                                                                                                                                            |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physical Characteristics<br>Height<br>Width<br>Depth | 7.00 in<br>19.00 in<br>22.00 in                                                                                                                                          |

| <u>Functional Characteristics</u><br>Memory          | Magnetic core, 4096 words, 12 bits, 2 µS<br>cycle time. Memory options: Minimum<br>4K, field expandable to 16K in 4K<br>increments.                                      |

| Addressing                                           | Relative, indirect, and direct。<br>Hardware multiple field control.                                                                                                      |

| Arithmetic                                           | Parallel, binary, fixed point, 2's complement.<br>Hardware multiply and divide。                                                                                          |

| Instructions                                         | Single and two-word instructions which<br>include 25 memory reference instructions,<br>three literals, and more than 50 arithmetic<br>and register control instructions. |

| Input/Output                                         | Interrupt: Programmable 4–level priority interrupt. Trap to any core location in first 4K of memory.                                                                     |

| Programmed I/O Transfer                              | Transmit 12 or 24 bits.<br>Receive 12 or 24 bits.<br>Transmit 12 and receive 12 bits.<br>Receive 12 and transmit 12 bits.                                                |

| I/O Instruction                                      | Includes four microprogrammable pulses<br>for multi–function operation with single<br>instruction.                                                                       |

| Single-Word Instructions                             | 256 possible I/O commands at 3 μS per<br>instruction.                                                                                                                    |

| Two-Word Instructions                                | 4096 possible I/O commands at 5 $\mu$ S per instruction.                                                                                                                 |

## Table 1-4. ND812 Computer, Physical and Functional Characteristics

Table 1-4. ND812 Computer, Physical and Functional Characteristics (Cont'd)

| Characteristic                 | Specification                                                              |

|--------------------------------|----------------------------------------------------------------------------|

| Control, data, and sense lines | Total of 75 available on single connector.                                 |

| Direct Memory Access (DMA)     | 6 megabits/s; read, load, increment or decrement on DMA with single cycle. |

| Accumulator                    | Dual accumulators with individual sub-<br>accumulators.                    |

| Timing                         | 16 MHz crystal-controlled clock assures absolute and drift-free timing.    |

| Voltage Requirements           | 115/230 Vac <u>+</u> 10%, 50/60 Hz, single<br>phase.                       |

| Power Consumption              | 400W maximum                                                               |

Table 1-5. 50 MHz ADC, Physical and Functional Characteristics

| Characteristic                                      | Specification                               |                                                                                              |

|-----------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------|

| Physical Characteristic<br>Height<br>Width<br>Depth | 8.71 in<br>2.68 in<br>9.70 in               | •                                                                                            |

| Functional Characteristics<br>Conversion Gain       | 128, 256, 512,<br>full-scale.               | 1024, 2048 or 4096 channels                                                                  |

| Digitizing Rate                                     | 50 MHz on all c                             | onversion ranges.                                                                            |

| ADC Conversion Time                                 | Gain Setting<br>4096<br>2048<br>1024<br>512 | Conversion Time (µS)<br>6.0 µS + 0.02N<br>6.0 µS + 0.02N<br>6.0 µS + 0.02N<br>6.0 µS + 0.02N |

| Characteristic                          | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | Gain SettingConversion Time (µS)256 $6.0  \mu S + 0.02 N$ 128 $6.0  \mu S + 0.02 N$ N is equal to the number of addressadvances for a given input event. Thefixed dead time includes initialization,pedestal rundown, delay line propagation,bad data flag (ALT) check, etc.                                                                                                                                                                                                                            |

| Signal Inputs                           | Coupling: ac or dc, switch-selectable.<br>Amplitude: 0 to +8V, nominal.<br>Polarity: Positive monopolar or initially<br>positive bipolar.<br>Rise Time: 0.2 to 70 µS<br>Duration: 1 µS, minimum.<br>Internal Delay: 1 µS.<br>Input Impedance: 1000 ohms.                                                                                                                                                                                                                                                |

| Baseline Restoration                    | Type: Robin <b>so</b> n。<br>Input: Positive monopolar, operative in<br>ac mode only。                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Coincidence or Anticoincidence<br>Input | Selection: Coincidence, anticoincidence<br>or normal operation.<br>Amplitude: 3 to 10V, ac or dc-coupled.<br>Polarity: Positive from 0V reference.<br>Duration: $1 \mu$ S minimum.<br>Timing: Determined by internal modifi-<br>cation which allows the coincidence or<br>anticoincidence pulse to occur before or<br>after the input event. Nominally set at<br>$2 \mu$ S. Overlap of the input event is not<br>necessary in either coincidence or anti-<br>coincidence<br>Input Impedance: 1000 ohms. |

| Strobe                                  | Front-panel-switch-selectable for use in<br>measuring slowly varying dc signals or<br>rapidly determining the zero energy inter-<br>cept.                                                                                                                                                                                                                                                                                                                                                               |

## Table 1–5. 50 MHz ADC, Physical and Functional Characteristics (Cont'd)

| Characteristic     | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | Auto Position: Opens the linear gate for<br>a pre-determined time, as selected by<br>the LGT control. Rate is nominally 8,000<br>samples per second. An external 3 to 10V<br>positive strobe pulse, 1 to 10 µS in duration,<br>may be entered via rear panel BNC to open<br>the linear gate for the pre-determined<br>time. Pulse rate not to exceed 8,000<br>samples per second.<br>Normal Position: Disables internal<br>and external auto strobe. |

| Linearity          | Integral: Better than 0.075% of full scale.<br>Differential: Conservatively estimated<br>at less than 1.0% deviation from mean<br>channel width over 99% of full scale.                                                                                                                                                                                                                                                                              |

| Stability          | Time: Less than 0.5 channel per day<br>at stable ambient temperature.<br>Temperature: Less than +0.01% zero drift<br>and less than +0.01% gain shift per 1°C<br>from 15 to 40°C.                                                                                                                                                                                                                                                                     |

| Power Requirements | +24 Vdc, 115mA<br>-24 Vdc, 115mA<br>+12 Vdc, 840mA<br>-12 Vdc, 15mA<br>When +6 Vdc supply is available, 800mA<br>is automatically switched from the +12<br>Vdc to +6 Vdc.                                                                                                                                                                                                                                                                            |

| LGT Control        | Continuously variable from 7 to 70 nSec<br>(must be set such that the linear gate line<br>(LGT) exceeds the rise time of the input<br>event).                                                                                                                                                                                                                                                                                                        |

Table 1–5. 50 MHz ADC, Physical and Functional Characteristics (Cont'd)

| Characteristic                                           | Specification                                                                                                                                                                                                                              |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physical Characteristics<br>Height<br>Width<br>Depth     | 9.71 in<br>19.00 in<br>16.00 in                                                                                                                                                                                                            |

| <u>Functional Characteristics</u><br>Voltage Requirement | 115/230 Vac, 50/60 Hz, single phase                                                                                                                                                                                                        |

| Power Requirement                                        | 500W maximum                                                                                                                                                                                                                               |

| Power Output                                             | +6 Vdc, 5A<br>+12 Vdc, 2.5A<br>+24 Vdc, 1A                                                                                                                                                                                                 |

| Regulation                                               | +0.1% (+12 and +24 Vdc) and +0.5%<br>(+6 Vdc) for 100% load change or +10%<br>line variation.                                                                                                                                              |

| Temperature Drift                                        | Less than 0.02%/ <sup>o</sup> C, 0 to 50 <sup>o</sup> .                                                                                                                                                                                    |

| Ripple and Noise                                         | Less than 10 mV peak to peak                                                                                                                                                                                                               |

| Voltage Adjustment                                       | +5% nominal                                                                                                                                                                                                                                |

| Recovery Time                                            | Less than 100 µS (+12 and +24 Vdc) and less<br>than 250 µS (+6 Vdc) is required to return<br>within +0.1% of nominal output voltage<br>after any change in input voltage or a<br>10 to 100% step change (1 µS rise time)<br>in rated load. |

Table 1-6. NIM Bin and Power Supply, Physical and Functional Characteristics

## SECTION II. EQUIPMENT PREPARATION

### 2-1. GENERAL

2-2. This section contains instructions for preparation for use, system installation and interconnections, and preliminary check-out.

### 2-3. PREPARATION FOR USE

### 2-4. UNPACKING AND INSPECTION

2-5. Carefully unpack the units which make up the ND4410 System, saving the shipping cartons for possible reshipment. Thoroughly inspect the units for damage. If damage is apparent, notify the delivering carrier about damage incurred during transit and then notify the nearest Nuclear Data sales office or the Nuclear Data home office.

#### NOTE

The delivering carrier must be notified within 24 hours after receipt of the units to insure reimbursement for any damages incurred during transit.

2-6. SYSTEM INSTALLATION AND INTERCONNECTIONS

2-7. Normal heat generated by the ND4410 System will not hamper its operation. However, the system should not be located over radiators or systems using vacuum tubes, since the high ambient heat may adversely affect system operation.

2-8. The ND4410 System requires a 115 or 230-volt, 50/60 Hz, ac source which is free of excessive noise or fluctuations. A voltage stabilizing transformer can be inserted between the ac source and the system where available power is subject to large fluctuations. Noise produced by various types of electrical equipment can be eliminated or greatly reduced by connecting a suitable filter between the ac source and the interfering equipment.

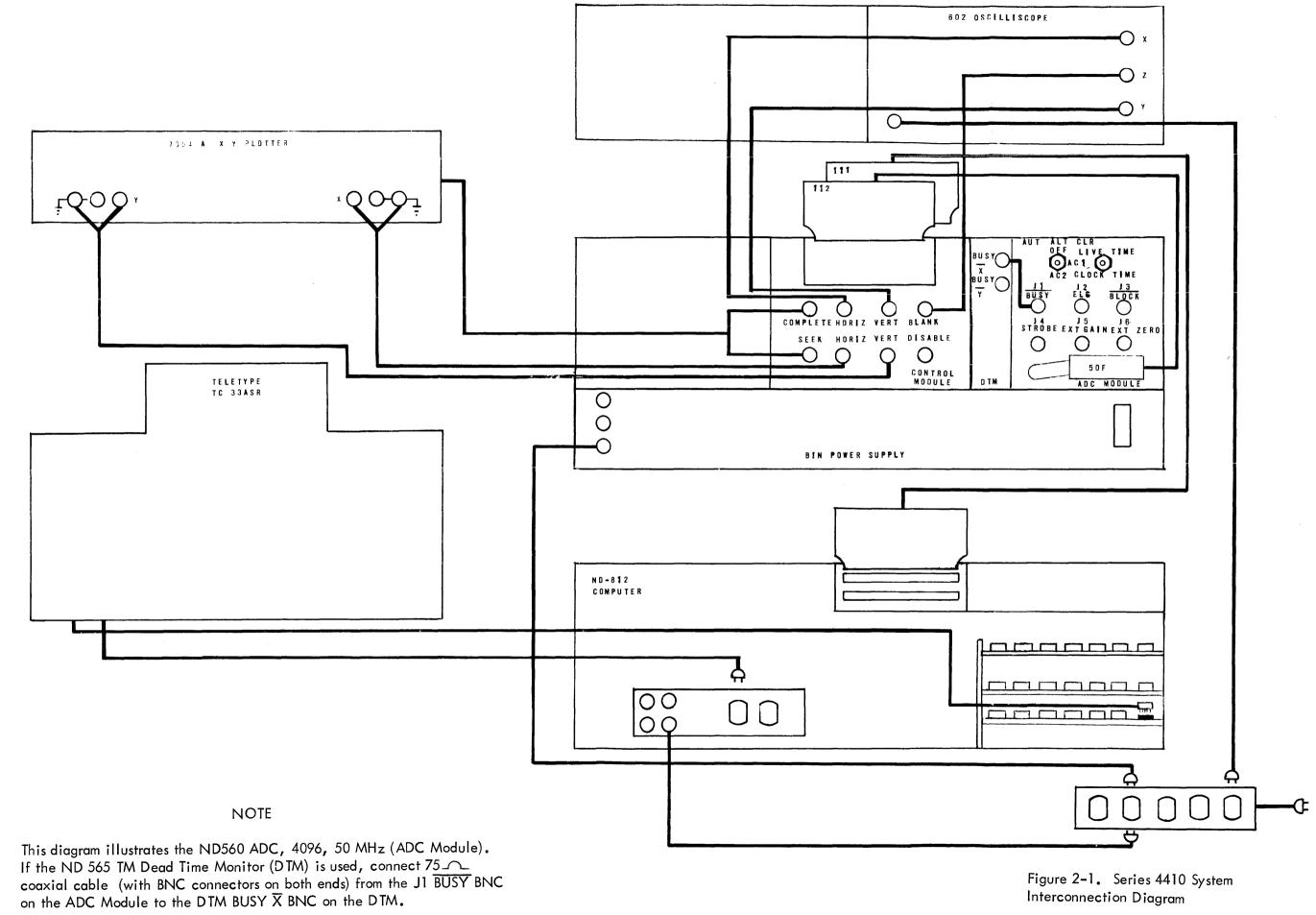

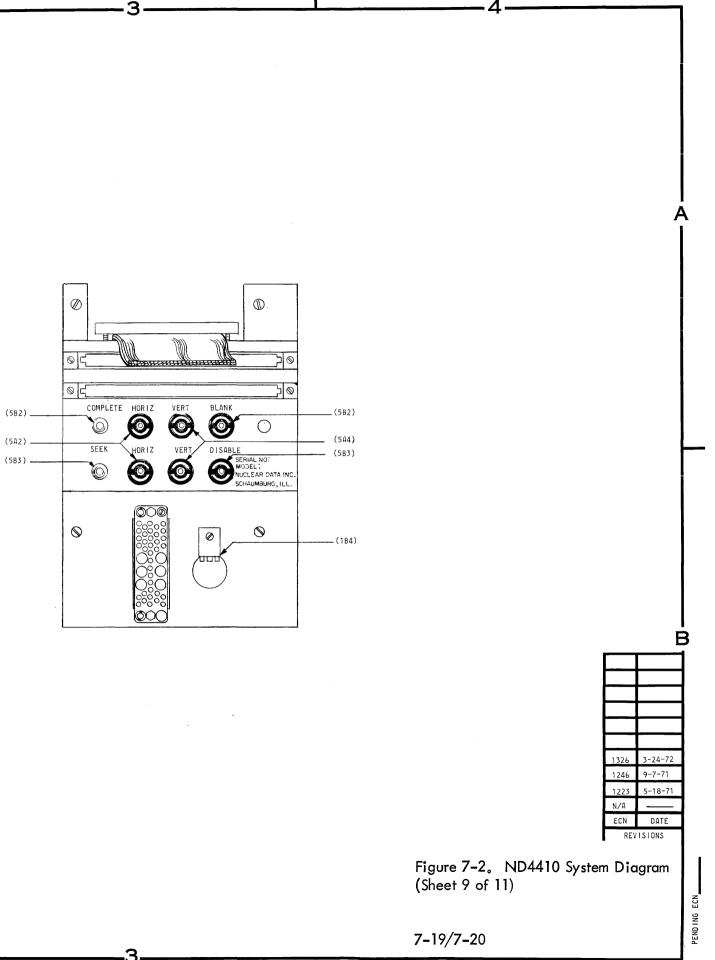

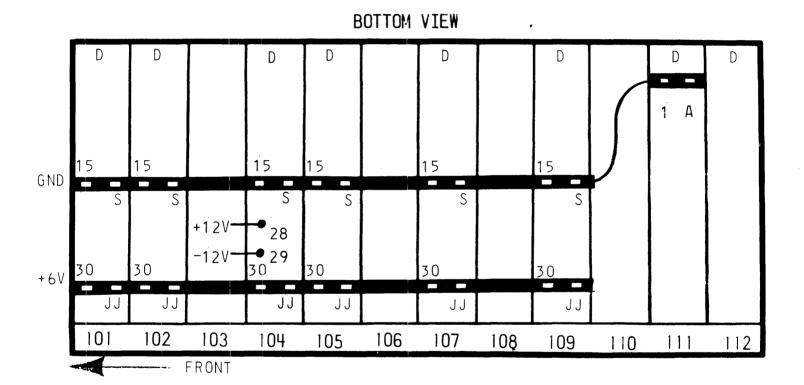

2-9. Using the ND4410 System Interconnection Diagram (Figure 2-1) and the following step-by-step procedure, interconnect the units that make up the ND4410 system.

a. Interconnect the Control Module to the ND812 Computer using ribbon cable equipped with card connectors on both ends as follows:

- (1) Insert card connector into location 111 on Control Module.

- (2) Insert card connector on other end of ribbon cable into either of the two input/output printed circuit board connectors located on the rear of the ND812 Computer.

b. Interconnect the Control Module to the ADC Module using ribbon cable equipped with a card connector on one end and a 50-pin male connector on the other end as follows:

- (1) Insert card connector into location 112 on Control Module.

- (2) Insert 50-pin male connector on other end of ribbon cable into 50-pin female connector designated 50F on the ADC module.

#### NOTE

The card connectors referred to in steps (a) and (b) above are slotted to prevent inserting them the wrong way.

c. Interconnect the Control Module to the 602 Oscilloscope as follows using three 75\_\_\_\_\_ coaxial cables with BNC connectors on both ends:

- (1) From the HORIZ BNC Connector (upper) on control module rear panel to the X input on the 602 oscilloscope.

- (2) From the VERT BNC Connector (upper) on the Control Module rear panel to the Y input on the 602 oscilloscope.

- (3) From the BLANK BNC Connector (upper) on the Control Module rear panel to the Z input on the 602 oscilloscope.

d. Connect ac line cords from the 602 Oscilloscope, Bin Power Supply, and ND812 Central Processor, to the Power Junction Box.

e. Connect ac line cord from the Power Junction Box to a nearby 115 volt ac source.

### NOTE

Step f applies to ND4410 systems equipped with an optional X-Y plotter.

- f. Connect the X-Y HP-7004B Plotter to the Control Module as follows:

- (1) Plug BNC/dual banana adapters into X and Y inputs on the HP-7004B front panel. Ground negative side of each input with ground strap.

- (2) Connect 75-ohm coaxial cable (with BNC connectors on both ends) from X input on HP-7004B front panel to the HORIZ BNC connector (lower) on rear of Control Module.

- (3) Connect 75-ohm coaxial cable (with BNC connectors on both ends) from Y input on HP-7004B front panel to VERT BNC connector (lower) on rear of Control Module.

- (4) Connect cable with 9-pin female connector on one end and blue and yellow banana jacks on other end as follows:

- a. Plug blue and yellow banana jacks into blue (COMPLETE) and yellow (SEEK) receptacles respectively, on the Control Module rear panel.

- b. Connect 9-pin female connector into 9-pin male receptacle of HP-17173 Null Detector Plug-in on bottom of the HP-7004B.

#### NOTE

Step g applies to ND4410 systems equipped with optional TC33ASR Teletype.

- g. Connect the TC33ASR Teletype into the ND812 Computer as follows:

- Plug male integrated circuit connector (on grey ribbon cable) into female integrated receptacle (rear row, second from left) on ALT printed circuit board of the ND812 Computer.

- (2) Connect ac line cord from TC33ASR to one of two ac receptacles on the ND812 Computer.

#### 2-10. PRELIMINARY CHECK-OUT

2-11. The following procedures provide step-by-step instructions to ensure the ND4410 System is ready for normal operation. These procedures should be performed as a matter of routine before operating the ND4410 System. Set front panel switches and controls as follows:

- a. Analog to Digital Converter Module

- (1) Front Panel

Interconnection Diagram

2-5/2-6

#### Switch/Control

CONVERSION GAIN Switch

GROUP Switch

ULD Control LLD Control ZERO Trim Potentiometer FINE ZERO Control ZERO SUPPRESSION Switches STROBE ON/STROBE OFF Switch DC/AC Switch COIN/NORM/ANTI Switch

(2) Rear panel

Switch/Control

AUT ALT CLR Switch LGT Control

LIVE TIME/CLOCK TIME

b. ND812 Computer

Switch/Control

POWER OFF/POWER ON/ CONTROL OFF Switch SINGLE STEP Switch SINGLE INSTR Switch SWITCH REGISTER Switches (0-11) MEMORY FIELD Switches (0, 1) SELECT REGISTER Switch

c. Control Module

Switch/Control

Direction  $( \leftrightarrow )$  Switch

d. 602 Oscilloscope

Initial Position

Equivalent to memory group size selected at external analyzer. Equivalent to memory group size selected at external analyzer. Fully clockwise (10.0) Fully counter clockwise (0.0) Fully counter clockwise Fully counter clockwise (0.0) All zero (0) STROBE ON AC NORM

Initial Position

As desired Set at a time greater than the rise time of the input event. As desired

### Initial Position

POWER ON Down All Down Both Down EXTERNAL

Initial Position

Left (←)

| ounterclockwise                |

|--------------------------------|

| ounter <mark>cloc</mark> kwise |

|                                |

| on                             |

|                                |

|                                |

| on                             |

|                                |

|                                |

2-12. INITIAL START-UP PROCEDURE

2-13. After all controls have been initially set, load the programs into the ND812 Computer in accordance with the procedures given in the ND4410 Single Parameter Data Acquisition and Display System Software Instruction Manual. After the programs have been loaded, start the ND4410 system as follows:

a. Place the POWER Switch on the Bin Power Supply in the "up" position. Power indicator lamp shall light.

b. Place the ON switch on the 602 Oscilloscope in the "up" position. Adjust INTENSITY control until a dot is visible on oscilloscope screen.

### NOTE

If HP-1208B oscilloscope is used, refer to note on Figure 7-2, sheet 5 of 11 for proper blanking circuit hookup.

c. Turn the LINE/OFF/LOCAL Switch on the Teletype to the LINE position.

d. Set the SWITCH REGISTER Switches on the ND812 Computer to 0200g.

e. Depress the STOP Key on the ND812 Computer.

f. Depress the LOAD AR Key on the ND812 Computer.

g. Depress the START Key on the ND812 Computer. The teletype should now perform a carriage return and line feed and type an asterisk (\*). The system is now in operation.

h. Depress ACQUIRE pushbutton switch on Control Module. ACQ lamp shall light.

i. Adjust FINE ZERO control until storage is observed in channel zero.

j. Set STROBE ON/STROBE OFF switch to STROBE OFF.

k. Apply an appropriate signal to the front panel SIGNAL INPUT BNC.

I. Adjust the LLD control clockwise until storage of a spectrum is observed. The ADC is now operational and properly zeroed.

## SECTION III. OPERATING INSTRUCTIONS

### 3-1. GENERAL

3-2. Most of the actual operating instructions are governed by the specific program applications as defined by the various ND4410 System Software Manuals. However, in the following pages, certain manual operations which will facilitate experiment set-up will be discussed along with an example experiment. In addition, the 4410 Instruction Repertoire will be explained. This instruction repertoire, in conjunction with the "Principles of Programming the ND812 Computer", should provide an excellent guide for understanding the ND4410 Software.

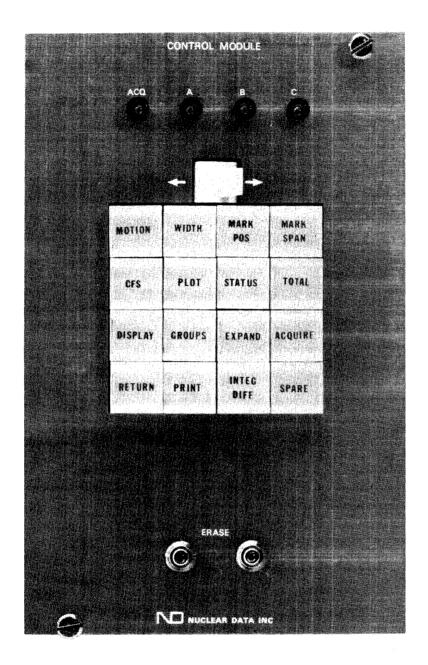

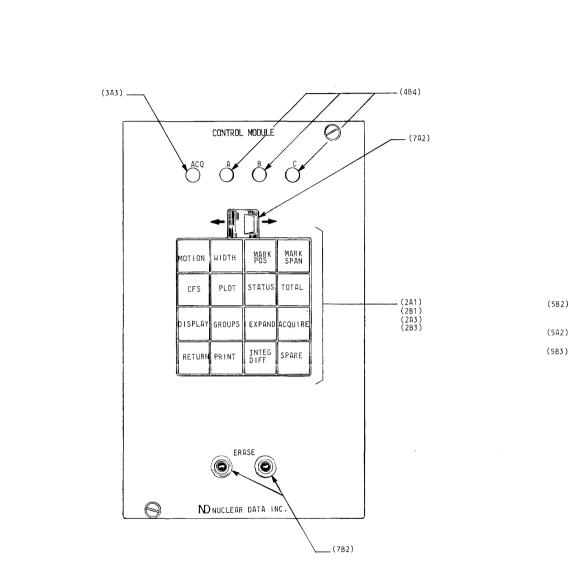

## 3-3. CONTROL AND INDICATOR FUNCTION

3-4. The ND4410 control module provides the primary controls necessary for operation of the ND4410 system. The controls and indicators for the control module are illustrated in Figure 3-1. Table 3-1 lists the controls and indicators, and describes their functions. Refer to the appropriate instruction manual for controls and indicators information on all other system units and peripheral options.

Figure 3-1. Control Module Front Panel Controls and Indicators

| Control/Indicator    | Description             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACQ                  | Indicator lamp          | Illuminates when the ND4410<br>System is in an Acquisition<br>Mode。                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| А,В,С                | Indicator lamps         | illuminate when the ND4410<br>System is in the program selec<br>A, B or C mode of operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Direction Switch     | Toggle switch           | Determines the direction in<br>which the display limit, marke<br>or group will move when the<br>selected pushbutton is depresse                                                                                                                                                                                                                                                                                                                                                                                                              |

| MOTION<br>Pushbutton | Pushbutton<br>Switch S1 | Holding the MOTION Push-<br>button depressed causes the<br>display to move horizontally<br>in the direction selected by<br>the setting of the Direction (<br>Switch. The rate of movemen<br>is a function of the length of<br>time the MOTION pushbutton<br>is held depressed. A momen-<br>tary switch depression will<br>move the display one channel.<br>Depressing the GROUPS<br>pushbutton returns the display<br>to the initial position.                                                                                               |

| WIDTH<br>Pushbutton  | Pushbutton<br>Switch S2 | Holding the WIDTH pushbuttor<br>depressed horizontally contract<br>the display when the Direction<br>Switch is in the Left ()<br>position, or horizontally<br>expands when the Direction<br>Switch in the Right ()<br>position. Horizontal expansion<br>increases the spacing between<br>channels, causing the<br>number of channels displayed<br>to decrease, while horizontal<br>contraction decreases the<br>spacing between channels,<br>causing the number of channel<br>displayed to increase. The<br>rate of expansion or contraction |

| Table 3–1. | Control Module, | Function | of Controls and | Indicators |

|------------|-----------------|----------|-----------------|------------|

| Control/Indicator       | Description             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                         | is a function of the length<br>of time the WIDTH pushbuttor<br>is depressed. A momentary<br>depression will only expand a<br>contract the display by one<br>channel.                                                                                                                                                                                                                                                                                                                                 |

| MARK POS<br>Pushbutton  | Pushbutton<br>Switch S3 | Holding the MARK POS<br>Pushbutton depressed, causes<br>the left and right markers<br>(full scale vertical lines<br>imposed upon the spectrum)<br>to move in the direction<br>specified by the Direction<br>( $\leftarrow$ ) Switch. The rate of<br>movement is a function of<br>the length of time the<br>MARK POS Pushbutton is<br>held depressed. A momen-<br>tary depression will move the<br>markers one channel.                                                                               |

| MARK SPAN<br>Pushbutton | Pushbutton<br>Switch S4 | Holding the MARK SPAN<br>pushbutton depressed, causes<br>the right marker (a full<br>scale vertical line imposed<br>upon the spectrum) to move<br>in the direction specified<br>by the Direction ( $\leftarrow$ )<br>Switch increasing or decreasi<br>the number of channels<br>between the markers. The<br>rate of movement is a function<br>of the length of time the<br>MARK SPAN pushbutton is<br>held depressed. A momen-<br>tary depression will only<br>move the right marker one<br>channel. |

| Control/Indicator | Description             | Function                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFS<br>Pushbutton | Pushbutton<br>Switch S5 | Depressing the CFS pushbuttor<br>increases the counts full<br>scale value by a factor of<br>two when the Direction<br>Switch is in the Left ( $\leftarrow$ -)<br>position or decreases the<br>counts full scale value by<br>a factor of two when the<br>Direction Switch is in the<br>Right ( $\rightarrow$ ) position. Each<br>time the CFS pushbutton is          |

| ·                 |                         | depressed, the counts full<br>scale value will be increased<br>or decreased by a factor of<br>two until it becomes zero.<br>The range of counts full scale<br>values is from 1 to 2 <sup>24</sup> –1 in<br>binary increments. Logarithe<br>display is selected by depress<br>the CFS pushbutton after the<br>minimum counts full scale<br>value (1) is reached with |

|                   |                         | the Direction Switch in the<br>Right (→) position or after<br>the maximum counts full<br>scale value (2 <sup>24</sup> –1) is reache<br>with the Direction Switch in<br>the Left (←) position.                                                                                                                                                                       |

|                   |                         | Display of the counts full<br>scale value when selected<br>by the STATUS pushbutton<br>will appear as follows:<br>Ø, 1, 2, 8388607, -1, Ø.<br>The counts full scale value<br>displayed for 2 <sup>24</sup> -1 is -1.<br>The counts full scale value                                                                                                                 |

|                   |                         | displayed for logarithmic<br>display is zero (Ø).                                                                                                                                                                                                                                                                                                                   |

| Control/Indicator    | Description             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLOT<br>Pushbutton   | Pushbutton<br>Switch S6 | Depressing the PLOT push-<br>button plots the current<br>display (including the<br>current STATUS selected<br>display parameters and the<br>content of the channels in<br>the current group) at the<br>X-Y Plotter. The X-Y plot<br>operation can be terminated<br>at any time by depressing<br>the RETURN pushbutton.<br>An asterisk (*) is typed at<br>the teletype to indicate<br>initiation and termination of<br>the X-Y plot operation. |

|                      |                         | NOTE<br>Calibration of the<br>X-Y plotter is described<br>in Section IV of the<br>ND4410 system<br>software manual<br>under OPERATIONAL<br>PROCEDURE. When<br>an X-Y plotter is<br>not used, depressing<br>the PLOT push-<br>button causes an<br>asterisk (*) to be<br>typed.                                                                                                                                                                 |

| STATUS<br>Pushbutton | Pushbutton<br>Switch S7 | Depressing the STATUS push<br>button sequentially displays<br>the following parameters:<br>(1) Center pointer channel/<br>content, and left marker<br>channel-right marker channel<br>with the channels relative<br>to the currently displayed<br>group; (2) current group<br>number/total groups, curren<br>group width, and counts full                                                                                                     |

| Control/Indicator     | Description               | Function                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |                           | scale; (3) Elapsed time, and<br>preset analysis time; or (4) Of<br>(no parameters displayed).<br>After the last parameter,<br>display reverts back to<br>the first parameter.                                                                                                                                                                                                            |

| TOTAL<br>Pushbutton   | Pushbutton<br>Switch S8   | Depressing the TOTAL push-<br>button prints the current<br>group number, the channel<br>locations of the left and<br>right markers, the elapsed<br>analysis time, totalizes the<br>counts stored in the channels<br>between the left and right<br>markers, subtracts the back-<br>ground from the total and<br>then prints the total and the<br>net total (total minus back-<br>ground). |

| DISPLAY<br>Pushbutton | Pushbutton<br>Switch S9   | Depressing the DISPLAY<br>pushbutton alternately selects<br>live or static display. Static<br>display presents the data to<br>the display oscilloscope<br>continually while live<br>display presents the data to<br>the display oscilloscope only<br>when the corresponding<br>channel has been addressed<br>by the ADC.                                                                 |

| GROUPS<br>Pushbutton  | Pushbutton<br>Switch \$10 | Depressing the GROUPS<br>pushbutton sequentially<br>selects the groups for data<br>storage and display. The<br>direction of selection is<br>determined by the Direction<br>( ) Switch. In the Left<br>( ) position, the next<br>lower group is selected.                                                                                                                                 |

| Control/Indicator     | Description              | Function                                                                                                                                                                                                                                                                                                                                 |

|-----------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |                          | After the first group, selection<br>reverts to the last group.<br>In the Right (->) position,<br>the next higher group is<br>selected. After the last<br>group, selection reverts<br>back to the first group.<br>Display of the current group,<br>total groups and current<br>group width can be selected<br>using the STATUS pushbutton |

| EXPAND<br>Pushbutton  | Pushbutton<br>Switch S11 | Depressing the EXPAND<br>pushbutton expands the<br>display between the left<br>and right markers to full<br>scale. The display can be<br>returned to normal by<br>depressing the GROUPS<br>Pushbutton.                                                                                                                                   |

| ACQUIRE<br>Pushbutton | Pushbutton<br>Switch S12 | Depressing the ACQUIRE<br>pushbutton alternately starts<br>or stops data acquisition.<br>Data acquisition stops<br>automatically after the<br>preset analysis time. The<br>preset analysis time is entere<br>using the Clock Set Command                                                                                                 |

|                       |                          | NOTE                                                                                                                                                                                                                                                                                                                                     |

|                       |                          | Since data storage<br>occurs in the group<br>currently displayed<br>at the start of<br>analysis, the<br>GROUPS Pushbutton<br>should be used to<br>select the desired<br>storage group prior<br>to starting analysis.                                                                                                                     |

# Table 3-1. Control Module, Function of Controls and Indicators (Cont<sup>®</sup>d)

| Control/Indicator           | Description                       | Function                                                                                                                                                                                                                                                                                                             |

|-----------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             |                                   | The preset and<br>elapsed acquisi-<br>tion time can be<br>displayed using<br>the STATUS<br>pushbutton.                                                                                                                                                                                                               |

| RETURN<br>Pushbutton        | Pushbutton<br>Swit <b>c</b> h S13 | Depressing the RETURN<br>pushbutton terminates the<br>routine in progress and<br>returns the program to<br>display.                                                                                                                                                                                                  |

| PRINT<br>Pushbutton         | Pushbutton<br>Switch S14          | Depressing the PRINT<br>pushbutton prints the<br>current group number, the<br>channel locations of the<br>left and right markers,<br>the elapsed analysis time<br>in centiseconds (0.01 second)<br>and the content of the<br>channels between the<br>markers with channel<br>identification every eighth<br>channel. |

| INTEG<br>DIFF<br>Pushbutton | Pushbutton<br>Switch S15          | Depressing the INTEG/DIFF<br>pushbutton with the Direction<br>Switch in the Right (                                                                                                                                                                                                                                  |

# Table 3-1. Control Module, Function of Controls and Indicators (Cont'd)

| Control/Indicator   | Description              | Function                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |                          | currently displayed group<br>with storage of the integral<br>in the marker defined area.<br>Depressing the INTEG/DIFF<br>pushbutton with the Direction<br>Switch in the Left (<)<br>position selects differentiation<br>of the area defined by the<br>left and right markers in the<br>currently displayed group<br>with storage of the differentic<br>in the defined area. |

| SPARE<br>Pushbutton | Pushbutton<br>Switch S16 | Available for future software operation.                                                                                                                                                                                                                                                                                                                                    |

# Table 3-1. Control Module, Function of Controls and Indicators (Cont'd)

# 3-5. OPERATIONAL CONSIDERATIONS

### 3-6. SPECIFIC HARDWARE CONSIDERATIONS

3-7. ANALOG TO DIGITAL CONVERTER MODULE. The storage capacity of the analyzer memory being used is an important consideration in the selection of the conversion gain. The number of address advance pulses for a full scale (8 volt) input signal corresponds to the conversion gain switch positions of 128, 256, 512, 1024, 2048, and 4096. Therefore, it would seem feasible to select the switch position corresponding to the memory size, i.e., for a 1024 channel memory, select switch setting of 1024; for a 2048 channel memory, select a switch setting of 2048; etc. In many experiments the above holds true, but in others, different factors require different settings. For example, if the energy of interest does not exceed 5 volts, it may be better to select a conversion gain of 1024 with a 2048 channel memory size. This allows the spectrum peaks to spread out over the full memory rather than half the memory.

3-8. Another factor to consider is resolution. With the conversion gain switch set at 1024, each channel represents 8 millivolts (horizontally on the display oscilloscope) for a full scale 8 volt input. This means the voltage levels can be resolved to within 8 millivolts of each other. The conversion gain is directly proportional to the resolution. Therefore, if the experiment requires high resolution, a higher conversion gain might be more advantageous.

3-9. Speed is another factor. The analysis time required for a full scale input with the conversion gain switch set at 1024 is twice as long as it would be with the switch set at 512. Therefore, a lower conversion gain may be desirable where speed is more important

than resolution. However, since the average analysis time rather than the maximum is usually used in evaluating the selection of proper conversion gain, the percentage of increase in speed is considerably less, and the loss in resolution may be enough to offset the advantages of increased speed. Therefore, the tradeoffs among these factors must be determined in evaluating the experiment to be performed, and then the selection of the proper conversion gain may be made.