COMPUTING SYSTEMS

D9

<sup>49</sup> Sheets-Sheet 1

COMPUTING SYSTEMS

Original Filed Dec. 15, 1959

Ĺ

<sup>40</sup> Sheets-Sheet C

<sup>4.3</sup> Sheets-Sheet .

Original Filed Dec. 15, 1959

40 Sheets-Sheet 4

3,302,178

COMPUTING SYSTEMS

<sup>49</sup> Sheets-Sheet 3

Original Filed Dec. 15, 1959

49 Sheets-Sheet ∂

COMPUTING SYSTEMS

<sup>49</sup> Sheets-Sheet "

Original Filed Dec. 15, 1959

4) Sheets-Sheet -

Original Filed Dec. 15, 1959

40 Sheets-Sheet 🔅

COMPUTING SYSTEMS

Original Filed Dec. 15, 1959

$4\theta$  Sheets-Sheet 10

Original Filed Dec. 15, 1959

40 Sheets-Sheet 11

P. HOLLORAN ETAL

H

T. P. HOLLORAN ET AL

COMPUTING

SYSTEMS

FIG. 15

Original Filed Dec.

15,

1959

40 Sheets-Sheet 14

COMPUTING SYSTEMS

Original Filed Dec. 15, 1959

49 Sheets-Sheet 13

Original Filed Dec. 15, 1959

to Sheets-Sheet it

Jan.

ω

-

196

<u>.</u>

5

P. HOLLORAN ETAL

COMPUTING

SYSTEMS

ч

3,302,178

ω

Original Filed Dec. 15, 1959

The Sheets-Sheet 1

Original Filed Dec. 15, 1959

40 Sheets-Sheet 12

Original Filed Dec. 15, 1959

4.) Sheets-Sheet 20

<sup>40</sup> Sheets-Sheet 24

#### COMPUTING SYSTEMS

Original Filed Dec. 15, 1959

J1281 \_(3228) o WR XGØ DØM (1282) J3229 (12) (12) (12) (3269)(WR) 1283 **3230** <u>.₩R</u> RI) (12) (12) XGI (284 (323) (3270) ODI **\_**3231 (XG)  $\begin{array}{c} \text{RI} & (12) \\ 1285 \\ 1285 \\ 3232 \\ \end{array}$ 0. WR R) (12) (12) XG2 1286 (3233 (XC2)' <u>. D2</u> \_(WR) 1287 . WR XG3 112 12 XG3 1288 3235 12 3274 RI 0**D3** 1289 3236 (XG3) 3236 3275 RI \_(WR) 0.WR (112) (12) (12) (12) (3237) (3237) (3237)~ ----RI } ₀<u>D4</u> (1**290**` (112) (12) (XG4) (3238) (XG4) (3277) (WR) RI 1291 0. WR (1292 3239 (XG5) (1292 3239 (XG5) RI <u>0</u>5 (WR) R) wR 0 D6 RI - 112 12 12 13281 1295 3242 <u>wr</u> RI (12) 12 13282 0**D7** {1296<u></u>\_3243\_ RI)--(12)-(12)(XG7) (WR) <sup>1</sup>3283 1297 3244 0<u>.WR</u> XG8 1298 3245 12001 0<u>.08</u> (II2)--(I2)(XG8) <u>(WR</u>) RI } -3285 J299 3246 WR (12)-(12)-12)-3286 300 (3247-3286) (12)-3286 XG9 RI D9M (1300) (12)(XG9) <u>(WR)</u> 843 (112) RI 3287 CRX FIG. 26 TCCR -7001

: Sheets-Sheet 25

P. HOLLORAN ETAL

H

Original Filed Dec. 15, 1959

: Sheets-Sheet 27

Original Filed Dec. 15, 1950

4. Sheets-Sheet f

COMPUTING SYSTEMS

Original Filed Dec. 15, 1959

de Sheets-Sheet 29

P. HOLLORAN ET

P

-

COMPUTING SYSTEMS

Original Filed Dec. 15, 1959

40 Sheets-Sheet 31

<sup>40</sup> Sheets-Sheet 30

<sup>40</sup> Sheets-Sheet 31

Original Filed Dec. 15, 1959

40 Sheets-Sheet Co-

Original Filed Dec. 15, 1959

40 Sheets-Sheet 36

Original Filed Dec. 15, 1959

Original Filed Dec. 15, 1959

Original Filed Dec. 15, 1959

Original Filed Dec. 15, 1959

Jan. 31, 1967

P. HOLLORAN ET AL

-1

3,302,178

3,302,178

Jan. 31, 1967

Jan. 31, 1967

T. P. HOLLORAN ET AL

3,302,178

Jan. 31, 1967

P. HOLLORAN ET COMFUTING SYSTEMS

$\mathbf{\Sigma}$

ŕ

Η

3,302,178

Original Filed Dec. 15, 1959

<sup>4.)</sup> Sheets-Sheet 4.)

Jan. 31, 1967

P. HOLLORAN ETAL COMPUTING SYSTEMS

-1

3,302,178

Original Filed Dec. 15, 1959

40 Sheets-Sheet 4"

Jan. 31, 1967

Original Filed Dec. 15, 1959

P. HOLLORAN ETAL

COMPUTING SYSTEMS

1: Sheets-Sheet 4

-1

3,302,178

Original Filed Dec. 15, 1959

65

1

# 3,302,178

COMPUTING SYSTEMS Thomas P. Holloran, Brookville, and Patrick B. Close, Dayton, Ohio, assignors to The National Cash Register Company, Dayton, Ohio, a corporation of Maryland Original application Dec. 15, 1959, Ser. No. 859,598, now Patent No. 3,112,394, dated Nov. 26, 1963. Divided and this application Oct. 7, 1963, Ser. No. 314,094 3 Claims. (Cl. 340-172.5)

The present application is a division of copending application Serial No. 859,598, filed December 15, 1959, by P. B. Close et al., (now United States Patent No. 3,112,-394) and assigned to the same assignee as the present 15divisional application and related generally to a unique general purpose type of electronic digital computing system.

With the ever increasing enormity and complexity of record keeping and accounting systems in the business 20world of today, there is accordingly an ever increasing demand, by necessity, for the adaptation and utilization of high-speed mechanization techniques compatible with such systems. Even though the installation of large scale data processors and electronic computing equipment has partially satisfied the needs of the larger business establishments, unfortunately they are not economically within the realm of practical usage by the smaller business establishments. Consequently, the long-felt need by smaller businesses is yet to be satisfied. 30

It is a primary object of the present invention to devise an ambiguous-word type computer which is capable of utilizing in an extremely simple manner, an address incrementing and decrementing format for an internally stored program whereby a single instruction of the pro-35 gram is capable of initiating a sequence of like operations on a multitude of word significations.

The features of the present invention which are believed to be novel are set forth with particularity in appended claims. The organization and manner of operation of 40the invention, together with further objects and advantages thereof, may best be understood by reference to the following description taken in connection with the accompanying drawings, in the several figures of which like reference characters identify like elements, and in 45 which:

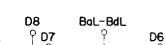

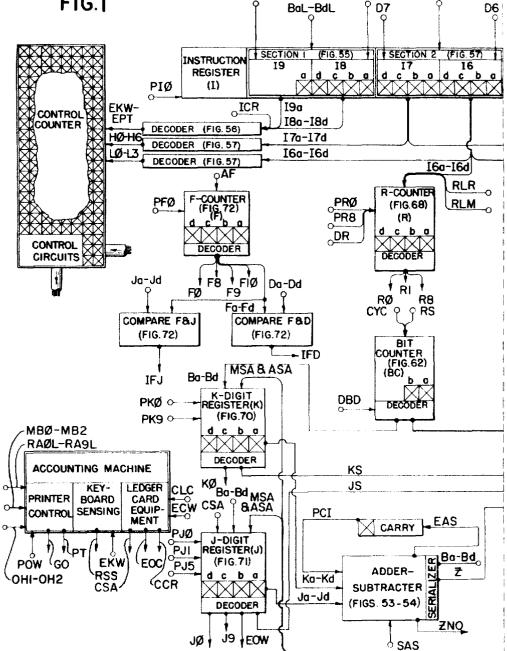

FIGS. 1 and 2, when joined together at the dashed lines, form a simplified block diagram of the computer circuitry;

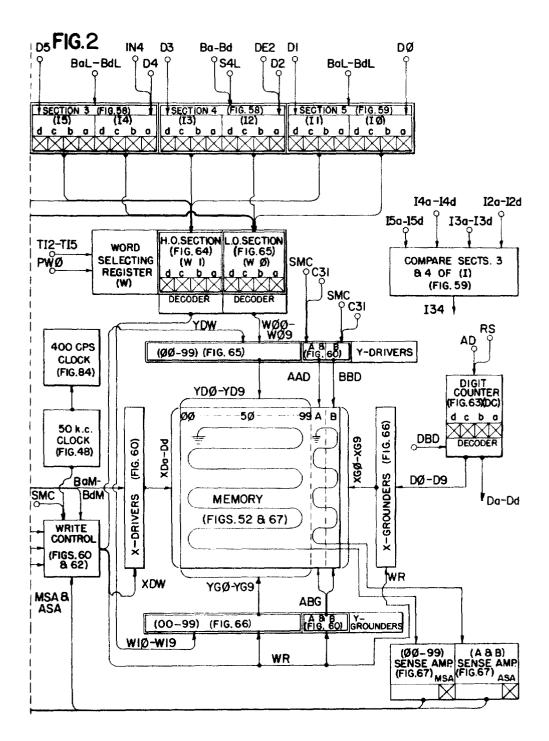

FIG. 3 is a simplified block diagram of the adder-sub- 50 tracter portion of the computer circuitry;

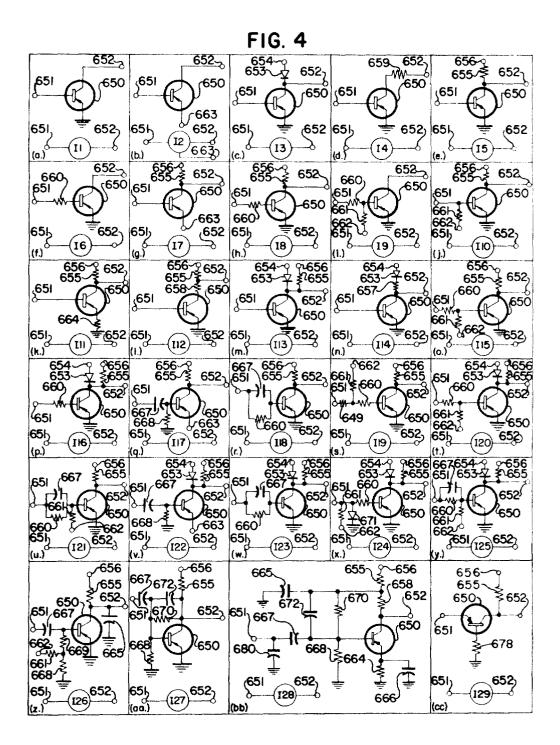

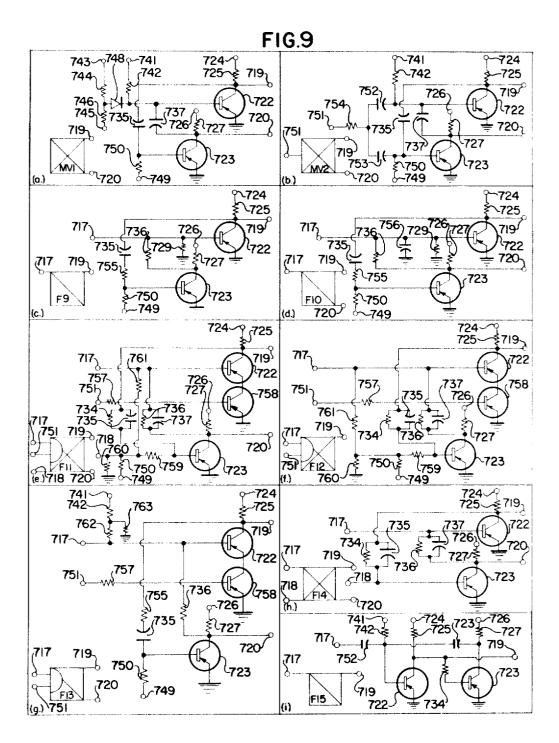

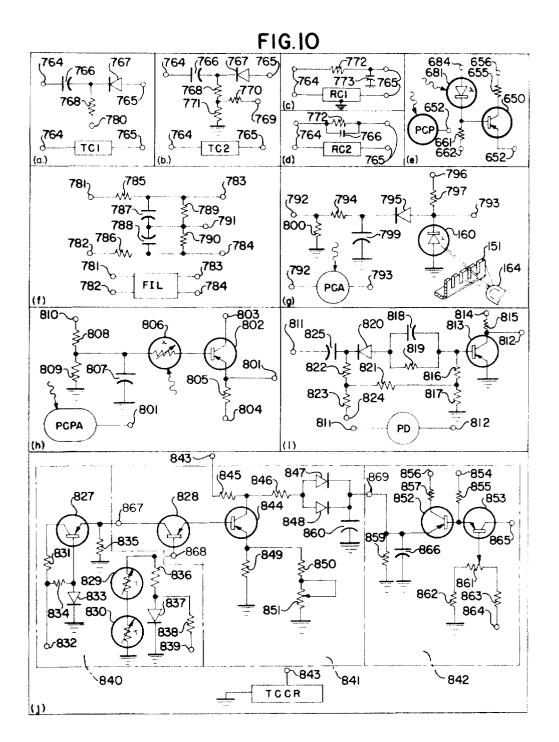

FIGS. 4 thru 10 disclose the schematic circuit diagrams of all of the various building blocks utilized in constructing the circuitry portion of the computer;

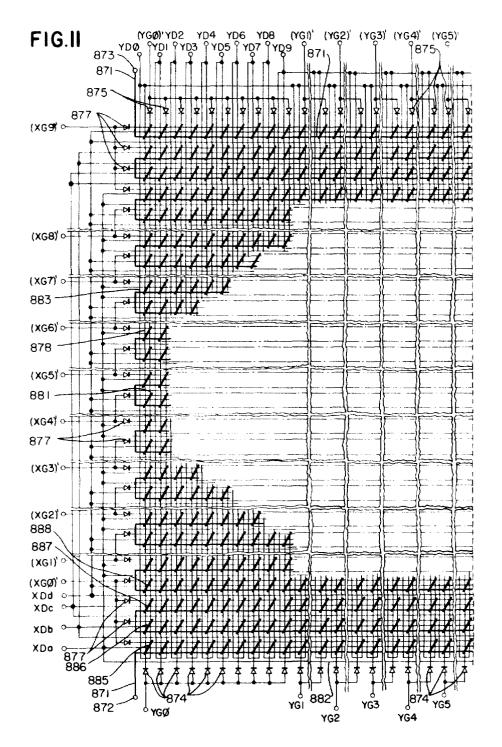

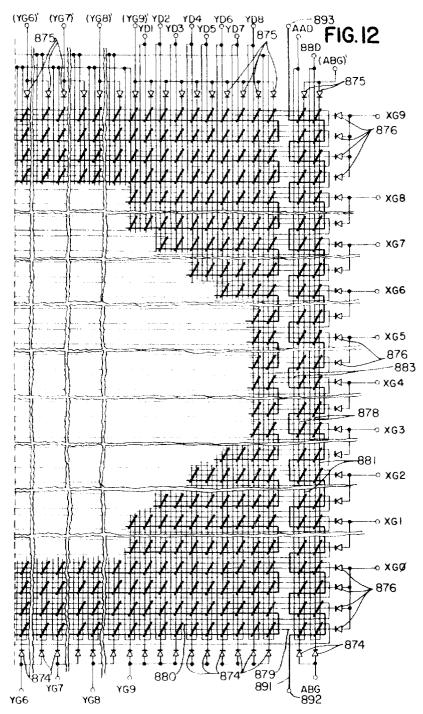

FIGS. 11 and 12, when joined at the dashed lines, form 55 a schematic circuit diagram of the coincident-current magnetic core memory;

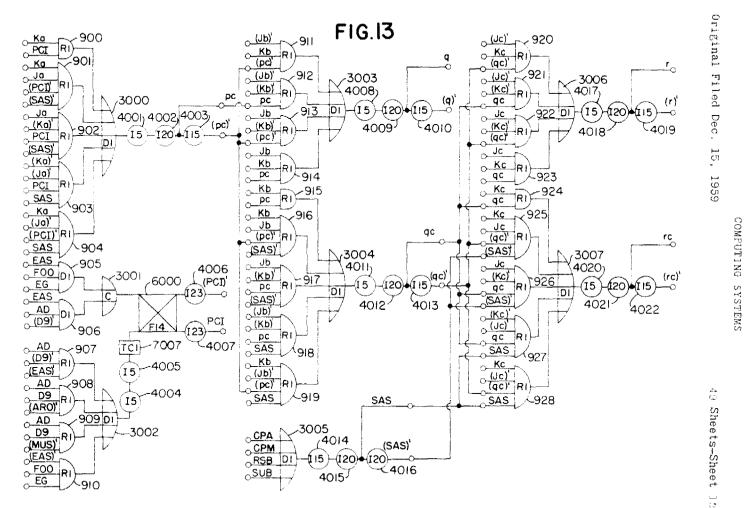

FIG. 13 is a portion of the logical diagram of the adder-subtracter circuitry;

FIG. 14 is the remaining portion of the logical diagram 60 of the adder-subtracter circuitry;

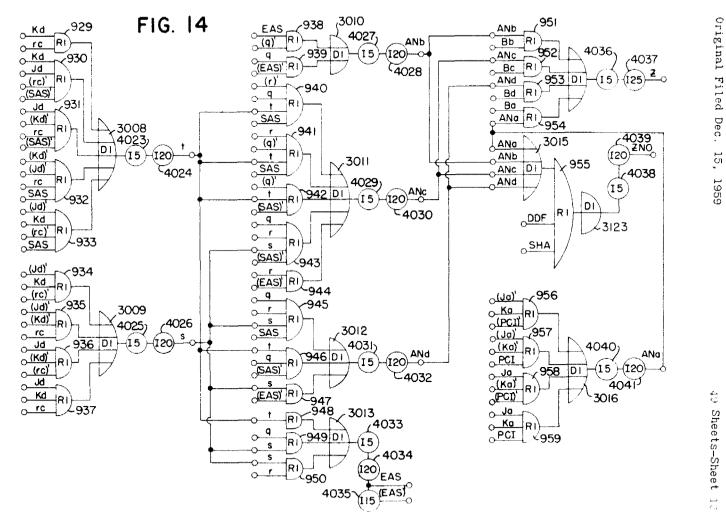

FIG. 15 is a logical diagram of section-1 of the instruction register;

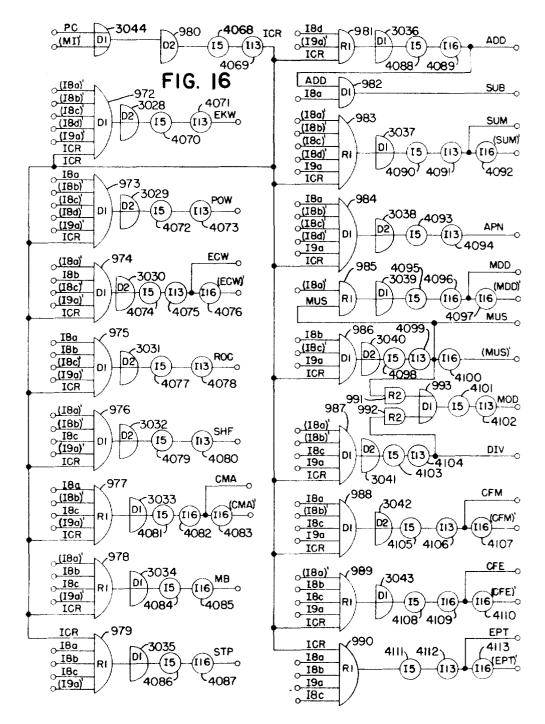

FIG. 16 is a logical diagram of the decoder portion of section-1 of the instruction register;

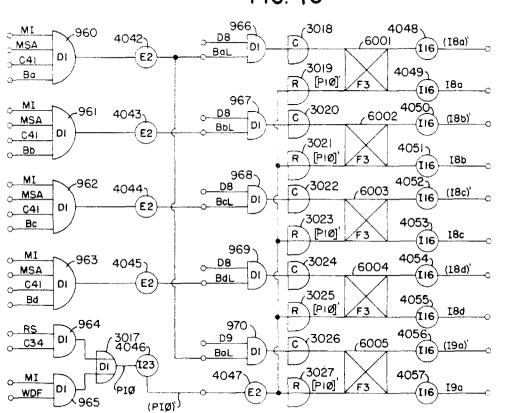

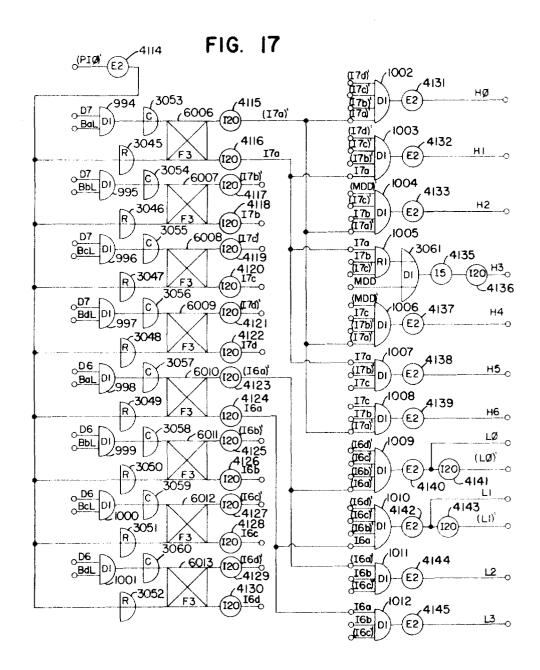

FIG. 17 is a logical diagram of the section-2 of the instruction register;

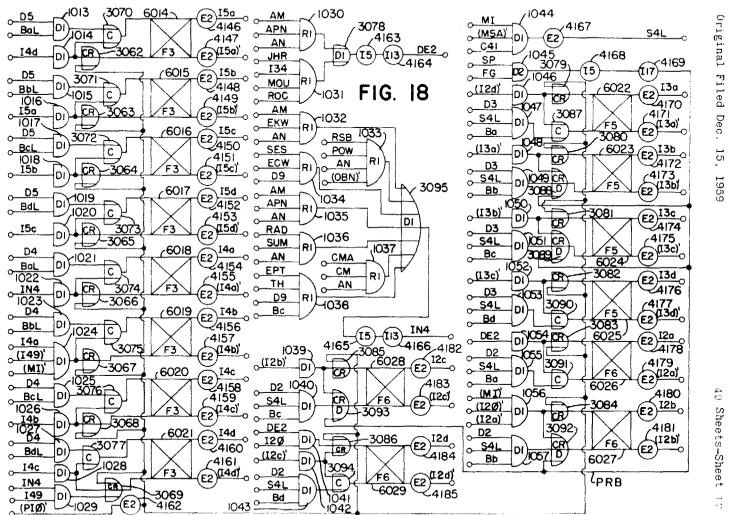

FIG. 18 is a logical diagram of sections 3 and 4 of the instruction register;

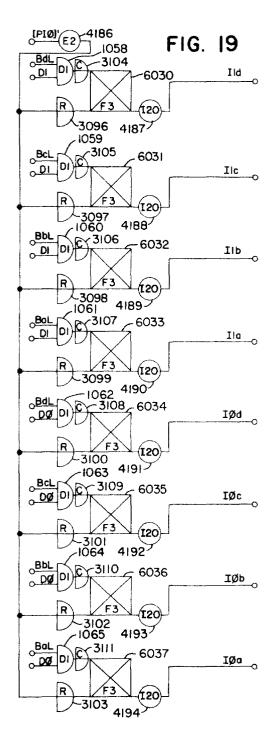

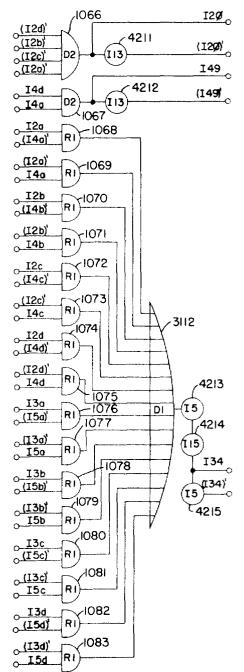

FIG. 19 is a logical diagram of section-5 of the in- 70 struction register and the compare circuitry relating to sections 3 and 4 of the instruction register;

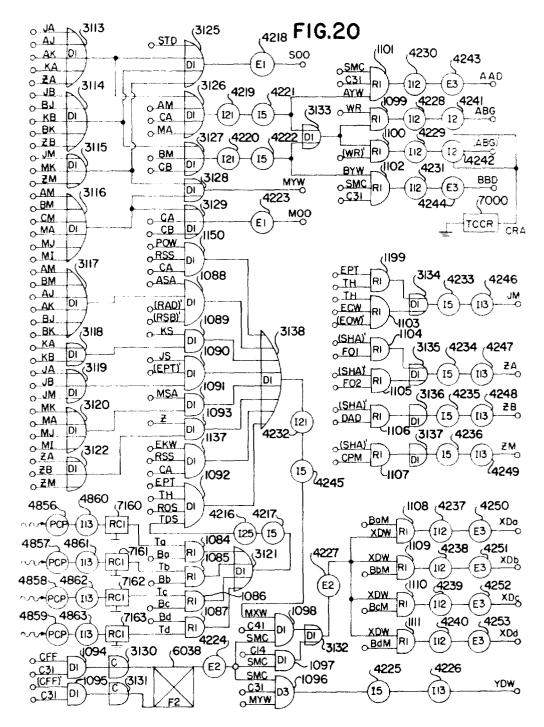

FIG. 20 is a portion of the logical diagram of the read-write, digit-cycle, word-cycle and subcommand initiating circuitry;

FIG. 21 is an additional portion of the logical diagram of the read-write, digit-cycle, word-cycle and subcommand initiating circuitry;

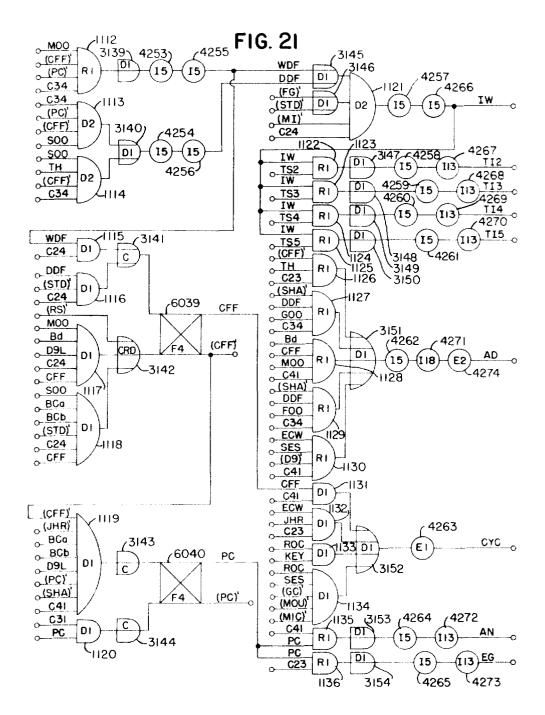

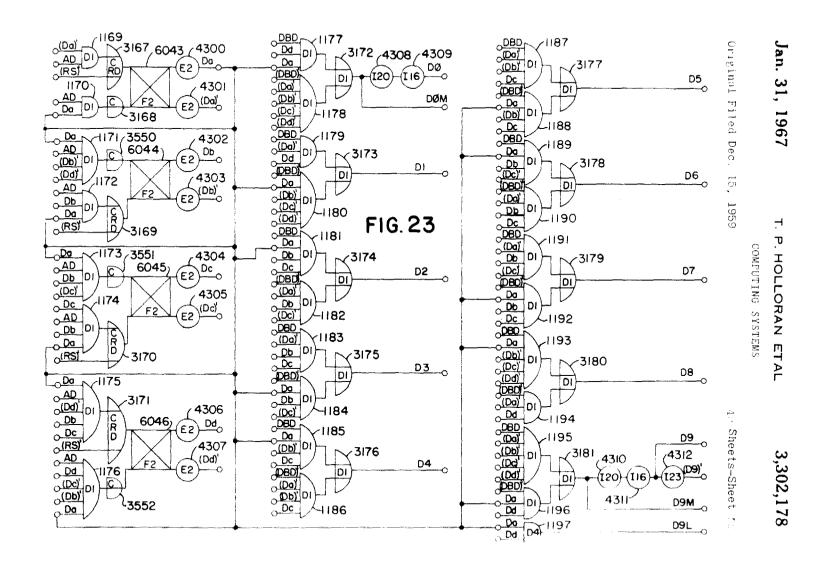

FIG. 22 is a logical diagram of the bit-counter; FIG. 23 is a logical diagram of the digit-counter;

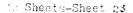

FIG. 24 is a logical diagram of the high-order section 10 of the word-selecting register;

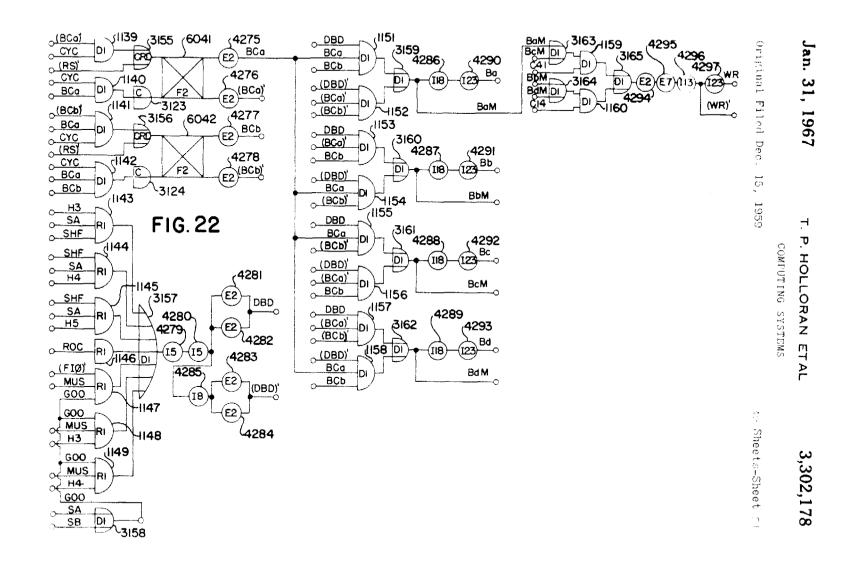

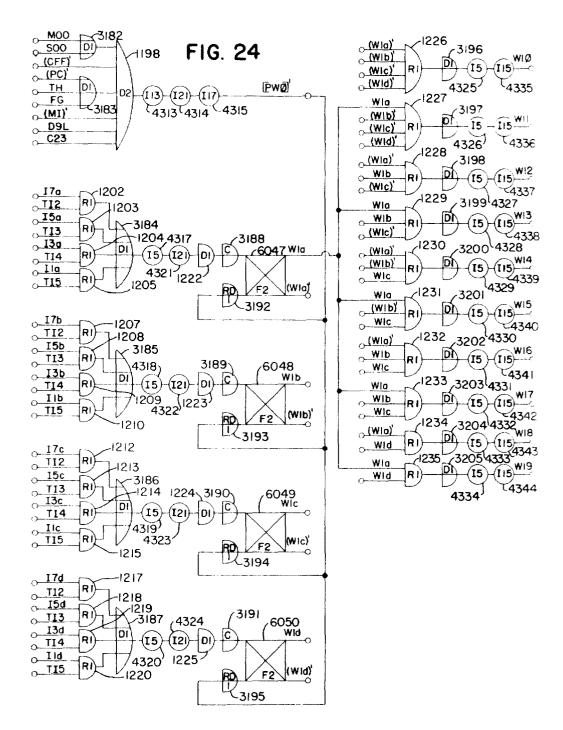

FIG. 25 is a logical diagram of the low-order section of the word-selecting register and a logical diagram of of the Y-drivers;

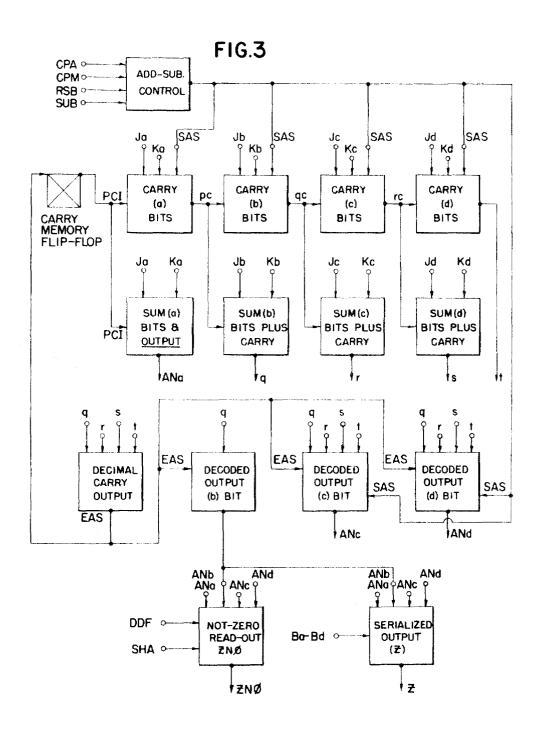

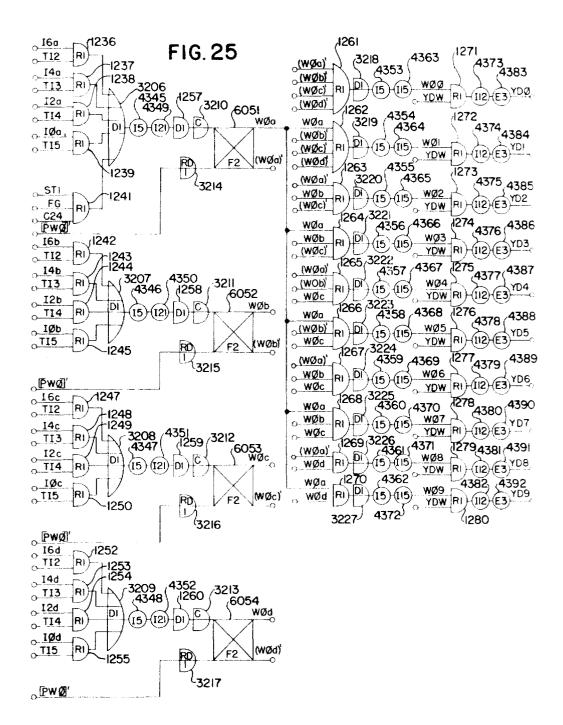

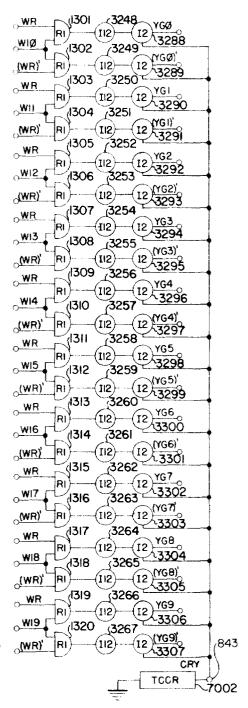

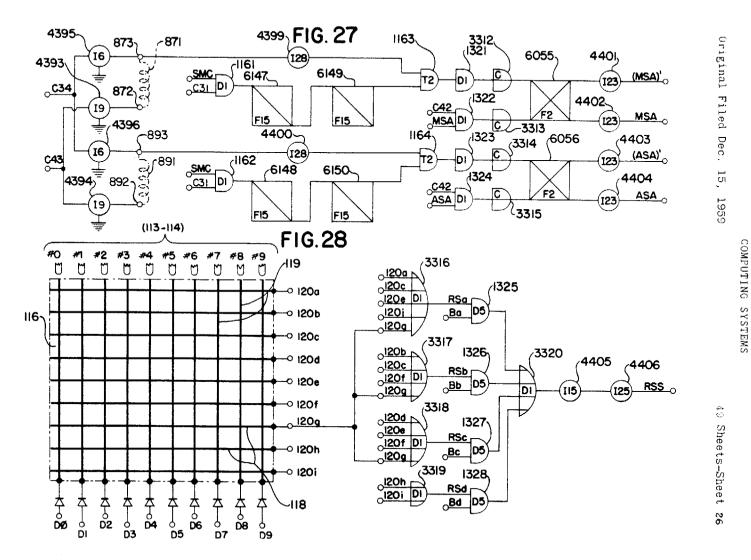

FIG. 26 is a logical diagram of the X and Y grounders; FIG. 27 is a logical diagram of the memory sense amplifiers;

FIG. 28 is a logical diagram of the rack-readout circuitry;

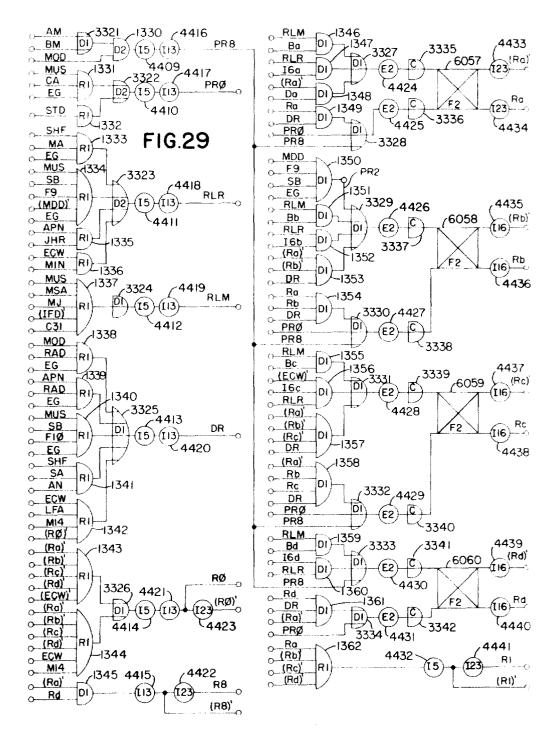

FIG. 29 is a logical diagram of the R-counter;

FIG. 30 is a logical diagram of a portion of the digitcycle initiating circuitry;

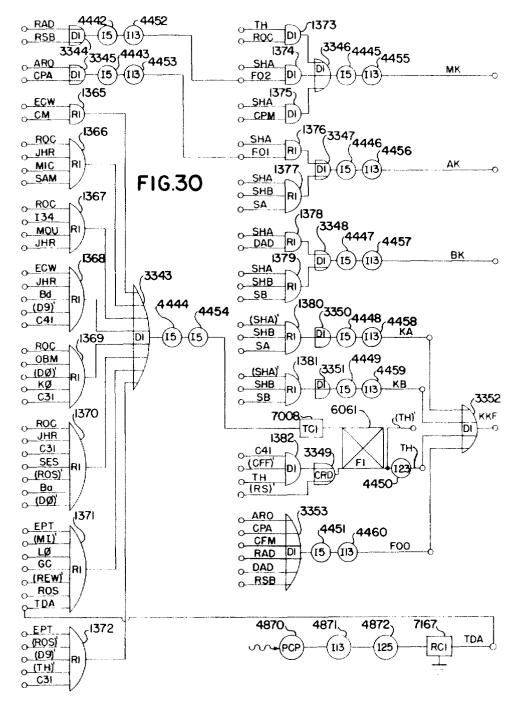

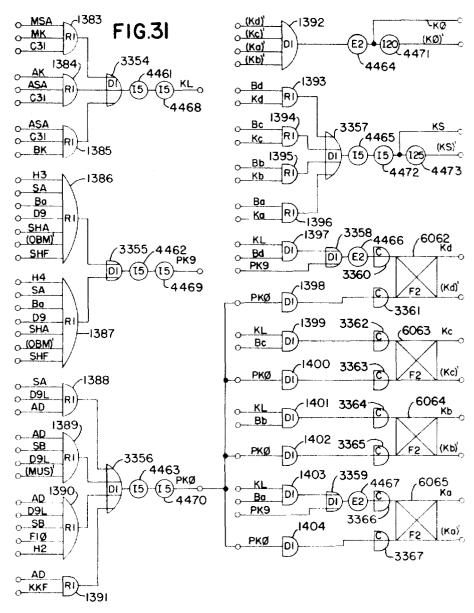

FIG. 31 is a logical diagram of the K digit-register and associated circuitry;

FIG. 32 is a logical diagram of the J digit-register 25 and associated circuitry;

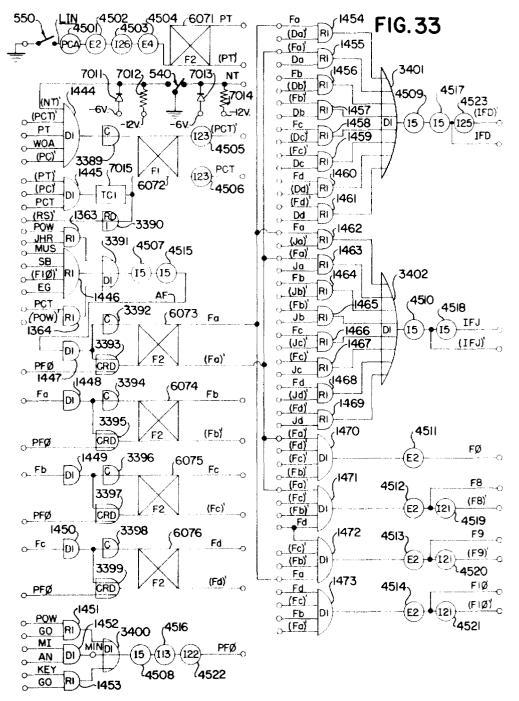

FIG. 33 is a logical diagram of the F-counter and compare circuitry;

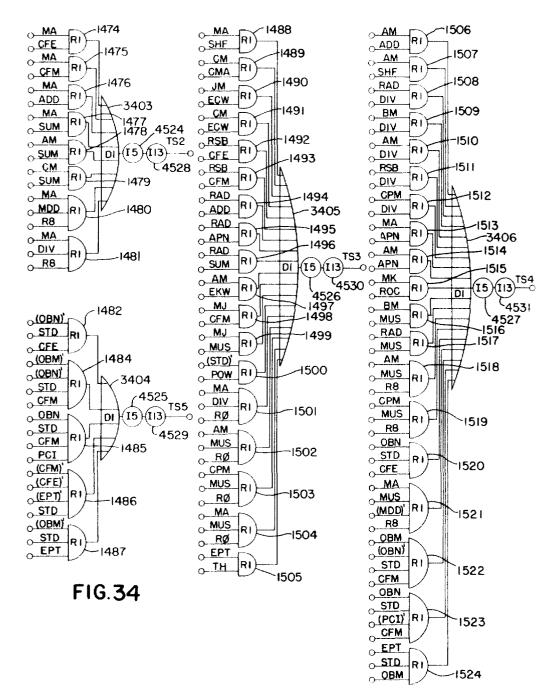

FIG. 34 is a logical diagram of the instruction register transfer circuitry;

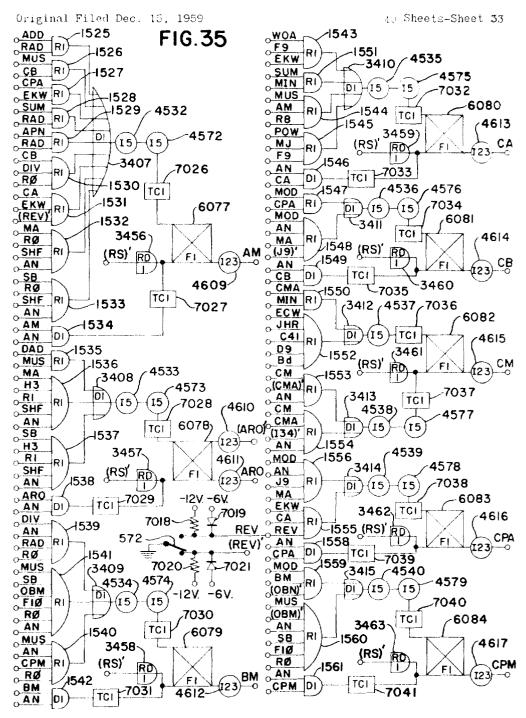

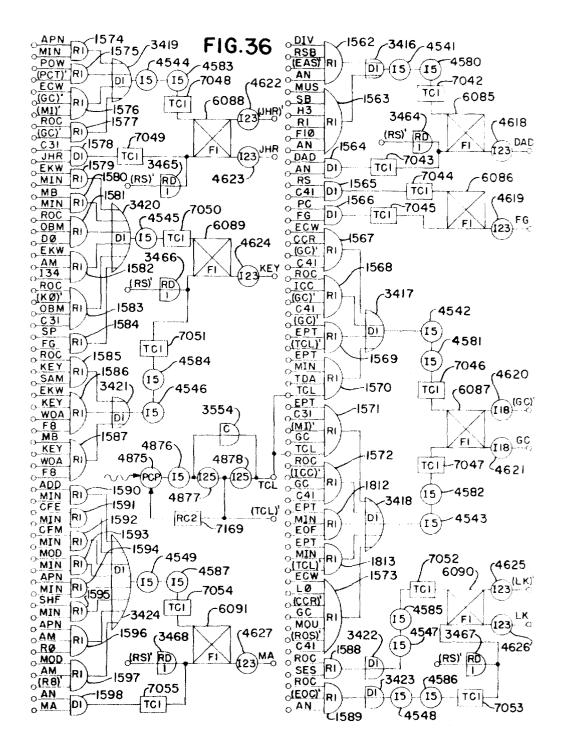

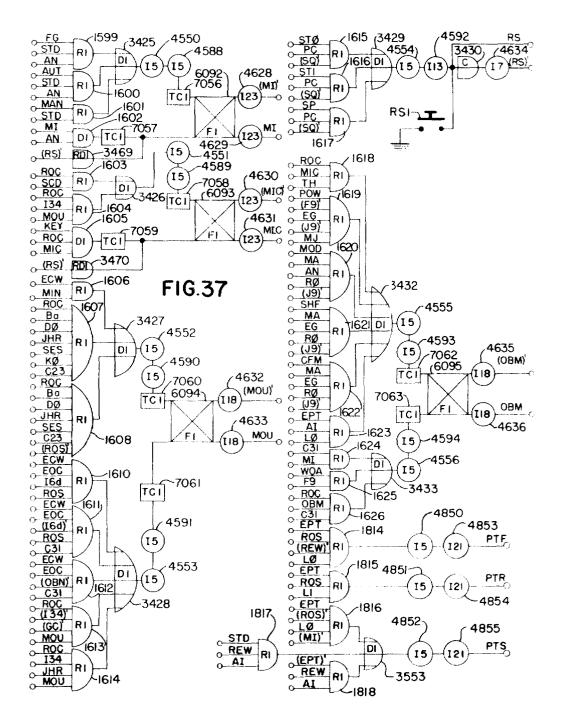

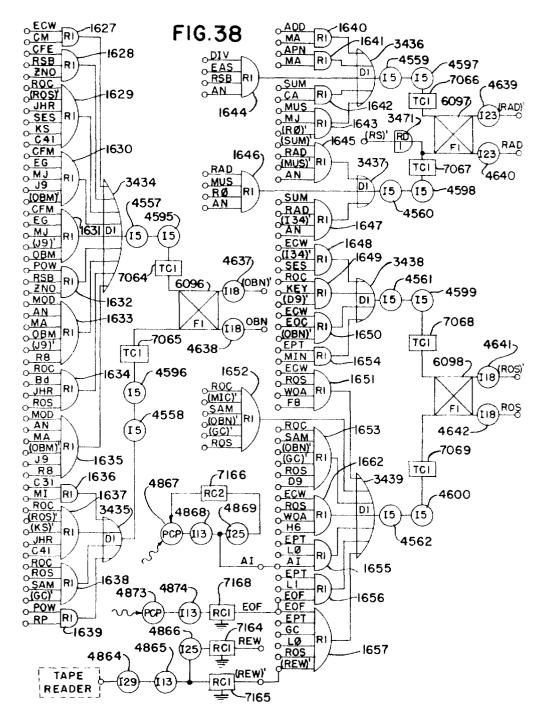

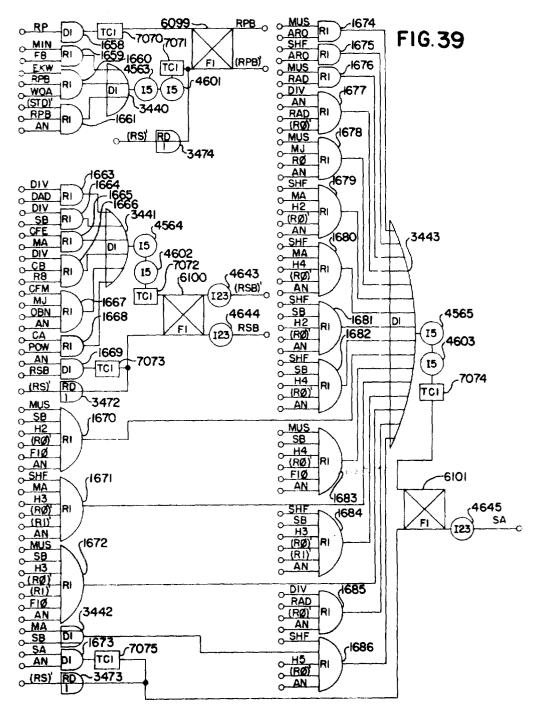

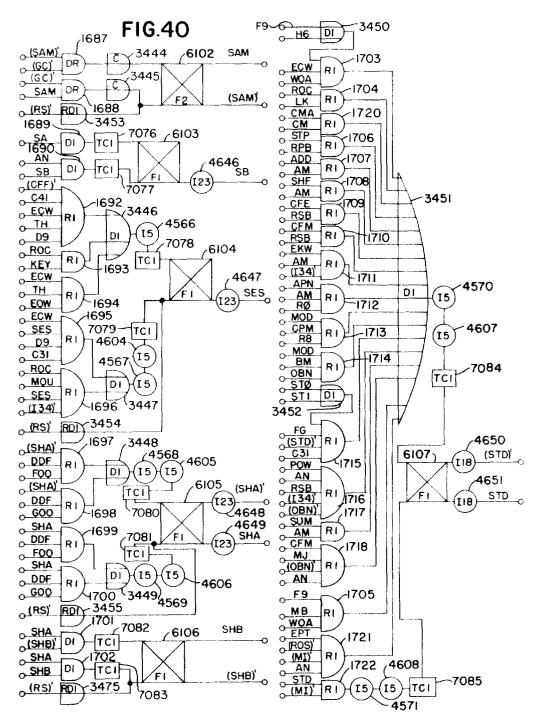

FIGS. 35 thru 40 are logical diagrams of the various word-cycle, time-delay and subcommand initiating flipflops;

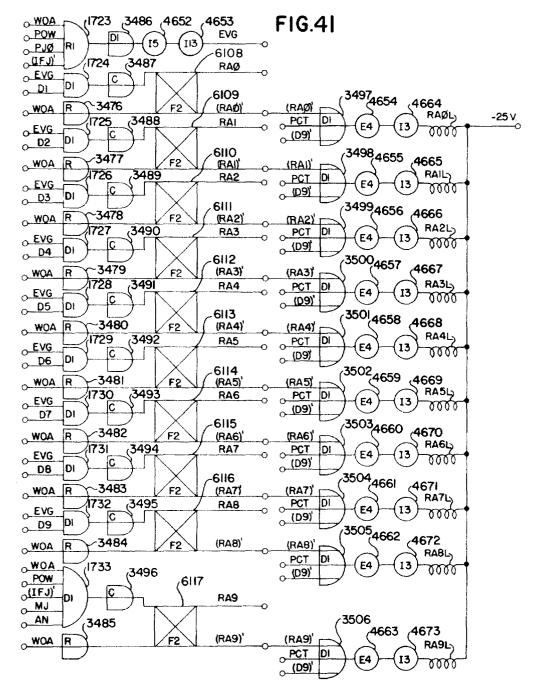

FIG. 41 is a logical diagram of the rack-stopping solenoids and flip-flops;

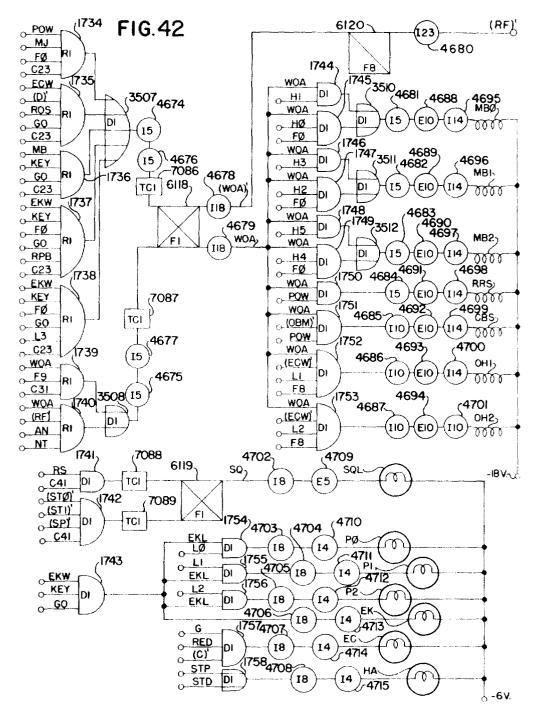

FIG. 42 is a logical diagram of various solenoid control and light indicating circuitry;

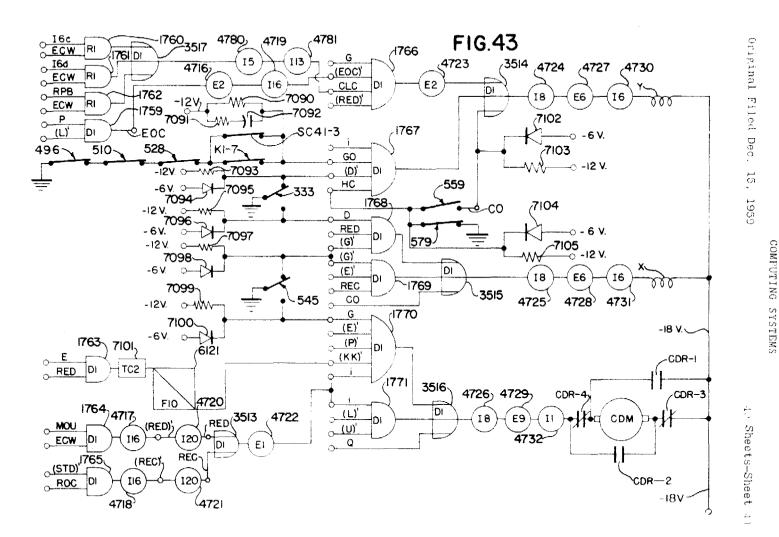

FIG. 43 is a portion of the logical diagram of the ledger card handling circuitry;

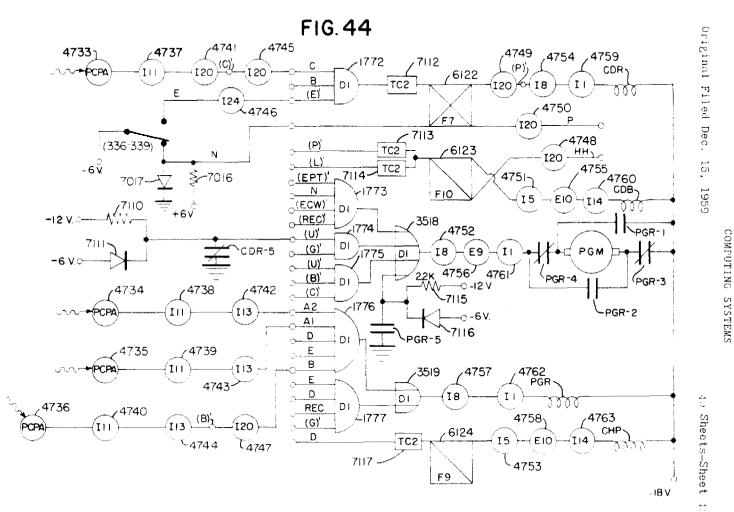

FIG. 44 is an additional portion of the logical diagram of the ledger card handling circuitry;

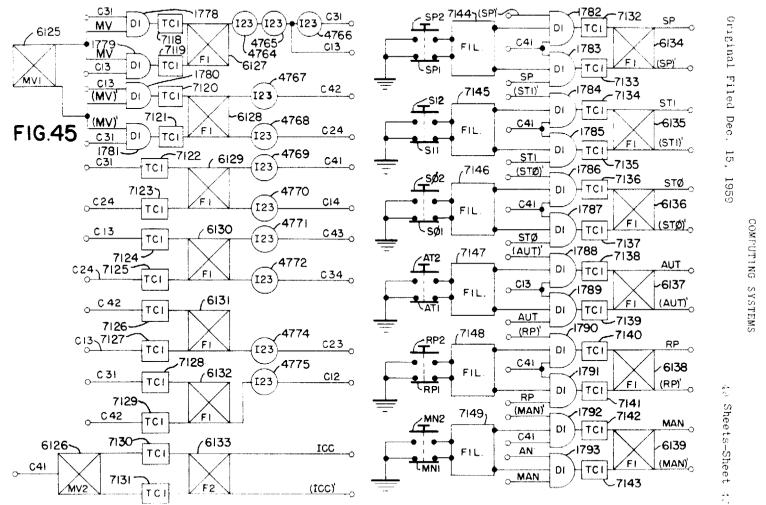

FIG. 45 is a logical diagram of the various timing clock and push-button control circuitry;

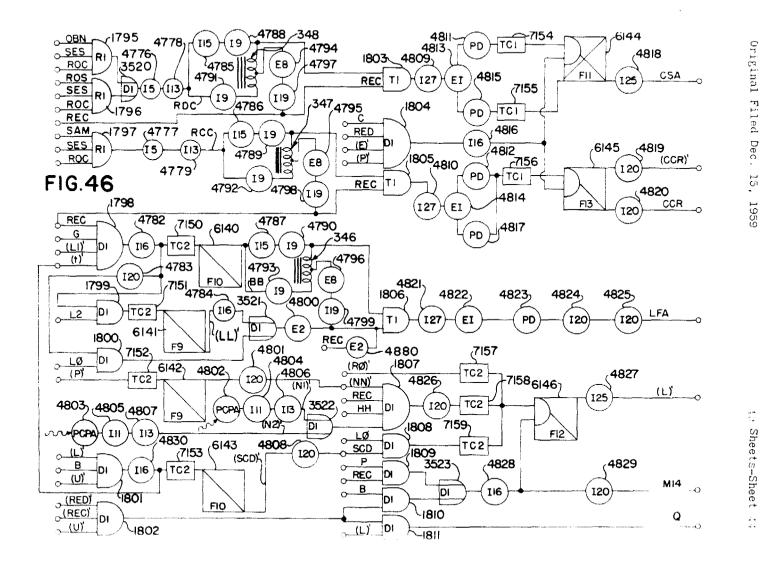

FIG. 46 is a logical diagram of the magnetic recording reproducing and control circuitry;

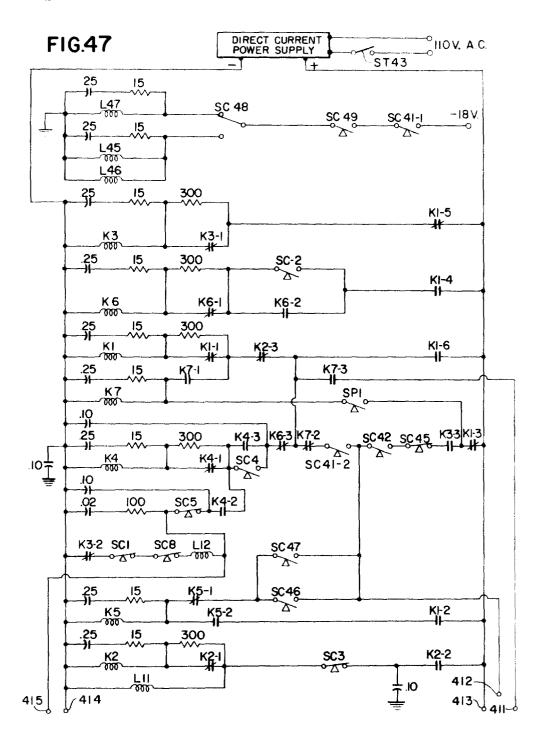

FIG. 47 is a schematic diagram of a portion of the tape punch control circuitry;

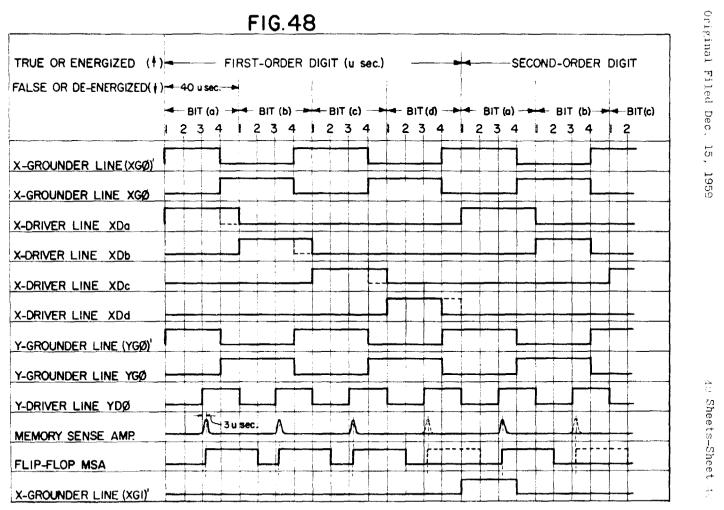

FIG. 48 is a timing chart illustrating the instantaneous logical states of the various control lines utilized during a memory read-write cycle of operation;

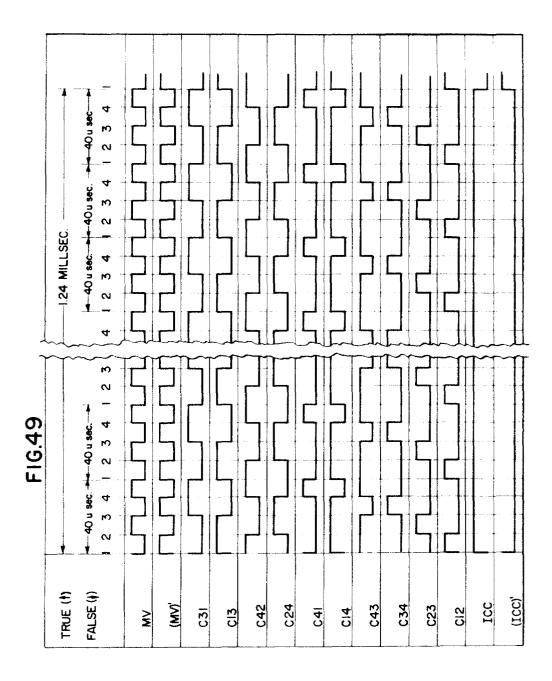

FIG. 49 is a timing chart illustrating the instantaneous logical states of the various synchronizing clock lines;

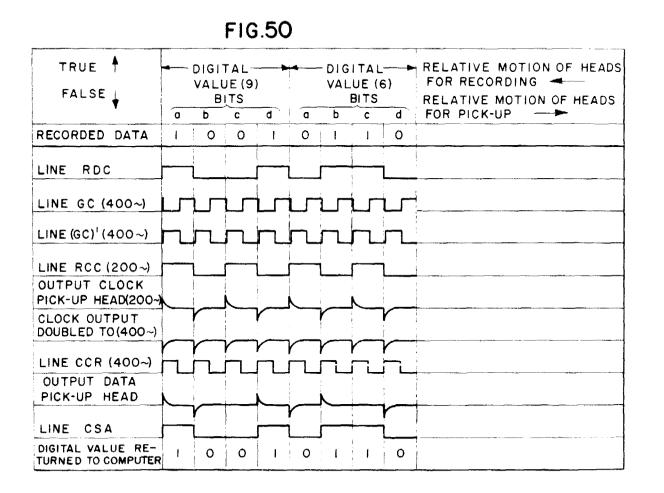

FIG. 50 is a timing chart illustrating the instantaneous logical states of the various control lines utilized during a magnetic recording and reproduction cycle of oper-

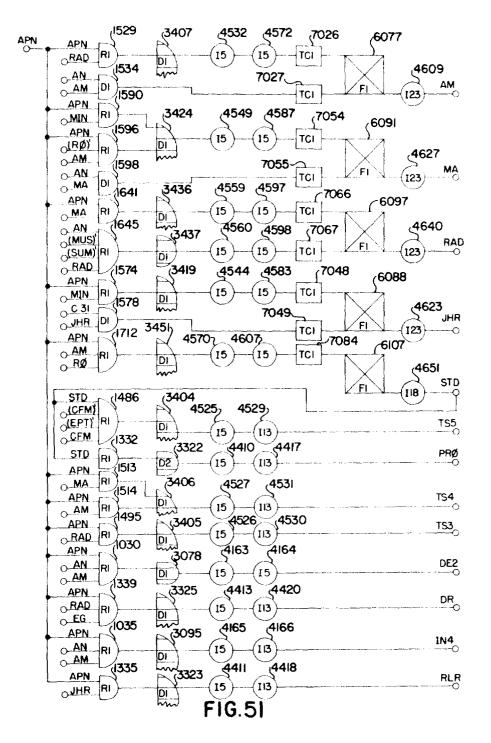

ation; FIG. 51 logically illustrates the various portions of the

circuitry utilized by the computer in carrying-out an addpairs-of-numbers (APN) instruction.

Inasmuch as the following description of a physical embodiment of the present invention is of considerable length and complexity, and is essentially divided into a multiplicity of separate sections, the various section headings are herein serially numbered and listed below in order to facilitate immediate reference to the various portions of the specification.

TABLE OF CONTENTS Col. No. 1. Building blocks generally \_\_\_\_\_ 3 3 2. Inverter building blocks \_\_\_\_\_ 3. Emitter-follower building blocks 5 4. Logical OR building blocks \_\_\_\_\_ 5

5. Logical AND building blocks \_\_\_\_\_ 6

| ABLE OF | CONTENTS—Continued |  |

|---------|--------------------|--|

|---------|--------------------|--|

T

|     | TABLE OF CONTENTS—Continued                 | Col. No. |   |

|-----|---------------------------------------------|----------|---|

| 6.  | Flip-flop and multivibrator building blocks | 9        |   |

|     | Miscellaneous building blocks               |          |   |

| 8.  | Magnetic core memory                        | 17       |   |

| 9.  | X-drivers                                   | 25       |   |

|     | Bit-counter                                 |          |   |

| 11. | X and Y grounders                           | 27       |   |

| 12. | Digit counter                               | 27       |   |

| 13. | Y-drivers                                   | 29       |   |

| 14. | Word-selecting register                     | 29       |   |

| 15. | Summary of word selection                   | 30       |   |

| 16. | Synchronizing clocks                        | 31       |   |

| 17. | Detailed read-write cycle                   | 32       |   |

|     | Sense-amplifier strobe                      |          |   |

| 19. | Format of instruction words generally       | 37       |   |

| 20. | Format of Add-Pairs-of-Numbers instruction  |          |   |

|     | word (APN-11)                               |          |   |

| 21. | Instruction register generally              | 40       |   |

| 22. | Section-1 of instruction register           | 41       |   |

| 23. | Section-2 of instruction register           | 42       |   |

| 24. | Section-3 of instruction register           | 44       |   |

| 25. | Section-4 of instruction register           | 45       |   |

| 26. | Section-5 of instruction register           | 45       |   |

| 27. | Instruction register presets                | 46       |   |

| 28. | Summary of instruction register             | 48       | 1 |

| 29. | R-counter                                   | . 48     |   |

| 30. | F-counter                                   | . 49     |   |

| 31. | Compare F-counter and digit-counter         | 50       |   |

| 32. | J digit-register                            | . 50     |   |

| 33. | Compare F-counter and J digit-register      | 51       |   |

| 34. | K digit-register                            | . 51     |   |

| 35. | Adder-subtracter                            | . 51     |   |

|     | Control counter generally                   |          |   |

| 37. | Detailed description of APN instruction     | 61       |   |

|     | 1. Building blocks generally                |          |   |

Before going into a detailed description of the individual units making up the electrical circuitry of the computer shown by the block diagram thereof in FIGS. 1 and 2, there will now be described the building blocks with which these individual units and interconnections therebetween are constructed. A building block is herein defined as a structure which is basic to the operation of the individual units of the computing system, and is used repeatedly in the system for amplification, logic, or other control purposes. By establishing a set of building blocks and understanding the rules for their interconnection, such a complex computing system as that heretofore generally described is more readily understood. The building blocks that are of particular importance are inverters, amplifiers, triggers, and logical circuits such as AND's and OR's, etc.

# 2. Inverter building blocks

The building block to be first described is the inverter, which, as the name implies, effects an inversion of the 55 signal applied to the input thereof. In a transistor circuit, the grounder-emitter amplifier is capable of performing such an operation. Thus, in order for the inverter to perform such a task, it must produce an output signal that is "up" when the input signal is "down," or, stated another way, it must produce a signal indicative of binary "one" upon the application of a signal to its input indicative of binary "zero"; conversely, it must produce a binary "zero" signal upon the application of a binary "one" to its input. However, throughout the following 65 description of the electrical circuitry of the instant computer, for the purposes of clarity, when the output signal is "up"-i.e., substantially at or above ground potential-it will be referred to as being "TRUE," indicative of a binary "one." However, when the output 70 signal is "down"-i.e., below ground potential at a potential of approximately -6 volts, it will be referred to as being "FALSE," indicative of a binary "zero."

With reference to FIG. 4A, there is shown a simple

having its base connected to input terminal 651 and its collector connected to output terminal 652. The symbol for this type of inverter is the notation "II" enclosed by a circle, as shown at the bottom of the block. When a negative potential is applied to the base of transistor 650 via input terminal 651, base current flows outwardly from the base thereof toward input terminal 651. If the collector electrode of transistor 650 is connected to a negative potential via output terminal 652, emitter current flows from the emitter to the collector of transisor 650. 10 Assuming a sufficient flow of base current, the resistance between the collector and the emitter becomes a very low value, and, as a result, output terminal 652 is essentially at ground potential, indicative of a TRUE signal. When 15 either ground or a positive potential is applied to the base of transistor 650, the resistance between the collector and the emitter, and the resistance between the base and the emitter, are all of a substantially high value. Consequently, the values of both the base and collector cur-20 rents go essentially to zero, and the voltage at output

terminal 652 is thereafter negative. Inverter (12) shown in FIG. 4B is substantially the same as inverter (11) of FIG. 4A, with the exception that the emitter electrode of transistor 650 is now returned 25 to terminal 663 instead of ground potential. Inverter (13) of FIG. 4C is essentially the same as inverter (11) but is additionally provided with a clamping diode 653, connected between the collector of transistor 650 and bias terminal 654, to "clamp" the collector to the negative op-30 erating potential at bias terminal 654. Inverter (I4) is essentially the same as (I1) but, additionally, has a dropping resistor 659 in its output circuit. Inverter (15) is essentially the same as (I1) but is additionally provided with a dropping resistor 655 connected between the col-35 lector of transistor 650 and bias terminal 656. (16) is substantially the same as (I1), with dropping resistor 660 in its input circuit. (19) is substantially the same as (16) but further includes resistor 661, connected between the base of transistor 650 and bias terminal 662, to insure that the transistor remains non-conductive when so rendered. Inverters (17), (18), (110), and (112) through (116) are substantially the same as (I1), except that they are additionally provided with various combinations of bias dropping resistors 655, 657, 658, and 661, clamping diodes 653, and input dropping resistor 660. (111) is substantially the same as (15), with dropping resistor 664 connected between the emitter of transistor 650 and ground potential. Inverter (I17) is substantially the same as (17), except for the addition of input coupling condenser 667 and base resistor 668. The purpose of condenser 50667 is to provide a large surge current in order to overdrive the transistor momentarily, to decrease the rise time of the output signal and thus increase switching speed. (118) through (123) and (125) utilize various combinations of the dropping resistors, clamping diodes, and coupling condensers previously described. In (124), diode 671 keeps the base of transistor 650 substantially at ground potential until the potential at terminal 651 becomes negative to render the transistor conductive. In (I26), bypass conductor 665, connected between collector 60 and ground of the transistor, provides a short circuit to eliminate or attenuate undesirable high frequencies. In (127), condenser 672 and resistor 670, each connected between collector and base of transistor 650, provide an inverse feedback to limit the gain of the stage at high frequencies. In (128), condenser 666 and resistor 664 provide a suitable negative feedback voltage proportional to emitter current to limit the gain of the inverter stage, and also provide a degree of temperature compensation thereof; resistors 655, 658, 668, and 670 provide the necessary operating bias potentials thereto; condensers 665, 672, and 680 function as filter condensers which remove unwanted extraneous signals; and condenser 667 functions as a coupling condenser which A.C. couples input tergrounded-emitter type inverter comprising transistor 650 75 minal 651 to the base of transistor 650. Inverter (129)

25

30

is essentially a conventional emitter-input grounded-base amplifier with a series dropping resistor 678 in its base circuit.

# 3. Emitter-follower building blocks

The next building block to be described is the emitter follower, which gets its name from its vacuum-tube counterpart, the cathode follower. The emitter follower type of amplifier provides power gain, has no phase inversion at low frequencies, has a slight attenuation of the input potential signal, and has a slight change in the D.C. level 10 of the signal from input to output. With reference to FIG. 6, there are shown various types of emitter follower circuit configurations, each having a symbol which com-prises the designation "E" normally followed by a numeral and both designations encompassed by a circle, as 15 shown at the bottom of each sub-section (a) through (k)of FIG. 6.

As shown in sub-section (a), emitter-follower (E1) comprises a transistor 650 having its emitter returned to 20ground or reference potential through resistor 664. The collector is connected to bias terminal 656 to normally receive a suitable negative D.C. operating potential therefrom. Input terminal 651 is connected to the base, and output terminal 652 is connected to the emitter, of the transistor.

In operation, if the input signal and consequently the base of the transistor are TRUE-i.e., at ground potential-the transistor 650 is rendered substantially non-conductive, and the output at terminal 652 is therefore substantially at ground potential, or TRUE. However, when the input signal is FALSE—i.e., at a potential of -6volts-the transistor is rendered conductive, and the potential at output terminal 652 is substantially equal to the negative potential on the base. Thus, when the input 35 is TRUE, the output is TRUE, and, when the input is FALSE, the output is FALSE. Emitter follower (E2) in sub-section (b) is essentially the same as (E1), with the exception that the lower end of resistor 664 is returned to bias terminal 663 instead of ground potential. In (E3), output terminal 652 is connected to the emitter of transistor 650 through series dropping resistor 664. (E4) is substantially the same as (E2) but for the addition of resistor 673 between output terminal 652 and the emitter of the transistor. (E5) is essentially the same as (E3), with the addition of resistor 661 connected between the base of the transistor and bias terminal 662. (E6) is substantially the same as (E2) but for the addition of bias dropping resistor 655. (E7) is substantially the same as (E4), except that, in this instance, resistor 673 is now paralleled with bypass condenser 666. Emitter followers 50(E8) through (E10) and (EI) utilize various combinations of dropping and bias resistors and coupling and bypass condensers, as previously described. (EI), however, functions somewhat as both an inverter and an 55emitter follower in that an inverted output appears at output terminal 674, while simultaneously an output potential appears at terminal 652 which is of the same polarity or phase as the input signal.

For the sake of simplicity and brevity, the preceding 60 building blocks were discussed but briefly. However, for a more detailed and comprehensive description thereof, reference is made to the "Handbook of Semiconductor Electronics," by L. P. Hunter, published by McGraw-Hill Book Company, Inc., wherein many similar circuit configurations are found.

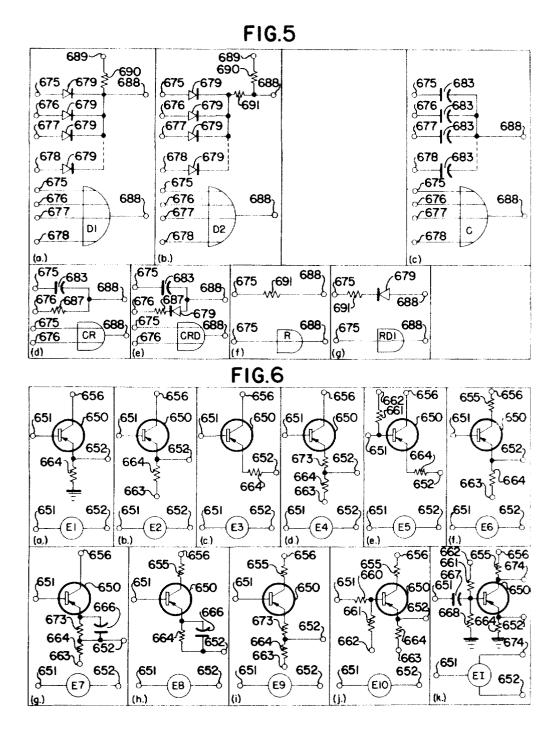

#### 4. Logical or building blocks

Performing logical operations is a well-known fundamental to the operation of a computer. The most basic logical operations are those of AND and OR. Even 70 though many of the logical operations performed in digital computers are concerned with arithmetic operations such as addition, subtraction, division, and multiplication, herein many of the logical operations are assembled into decision-making and information-routing circuits. In or- 75 der to perform such logical operations, it is generally necessary to utilize nonlinear circuit elements, such as diodes and transistors and the like.

With reference to sub-sections (a) through (g) of FIG. 5, there are shown various logical OR circuit configurations. In (a), there is illustrated a logical OR building block of type (D1) comprising a plurality of diodes 679, each having its cathode connected to the other. A "pull-down" resistor 690 is connected to the junction of the diodes 679 and to bias terminal 689, which normally has a negative D.C. operating potential applied thereto. A plurality of input terminals, in this instance shown as 675 through 678, are individually connected to the anode of a different one of diodes 679, and output terminal 688 is connected to the junction of the diodes.

In operation, if the input signal to any one or all of terminals 675 through 678 is TRUE, or at a positive potential, the corresponding diode in each instance is conductive, its internal impedance is reduced substantially to zero, and consequently the potential appearing at output terminal 688 is substantially equal to the input potential. However, if the input signals to all of input terminals 675 through 678 are each at a negative potential, the output signal at terminal 688 goes negative via the negative potential at terminal 689 and resistor 690. However, the negative potential at terminal 688 is not permitted to go more negative than the least negative potential at one of input terminals 675 through 678. Thus, it is evident that the output of a logical OR circuit is TRUE (or positive) if any of the input signals to terminals 675, 676, 677, or 678 is TRUE (or positive); the output is effectively FALSE only when all of the inputs are FALSE. The symbol used herein for a logical OR is circular segment designation having the representative input lines extending through the helf-circle and terminating at the circumference thereof, as illustrated at the bottom of each of sub-sections (a) through (g).

Logical OR of type (D2), shown in (b) of FIG. 5, is substantially the same as type (D1), but for the addi-40tion of dropping resistor 691 connected between the junction of diodes 679 and resistor 690. In (c), a type (C)logical OR comprises a plurality of condensers 683, each connected to the other and connected to output terminal 688. A plurality of input terminals, illustratively shown as 675 through 678, are each connected to the remaining end of one of the condensers 683. In a type (CR) logical OR, the condenser 683 and the resistor 687 are each connected to output terminal 688, input terminals 675 and 676 being individually connected to the remaining end of the condenser and the resistor. Type (CRD) logical element is similar to type (CR) except for the addition of diode 679 connected between resistor 687 and output terminal 688. Type (R) OR comprises but a single resistor 691 connected between input terminal 675 and output terminal 688, and type (RD1) OR comprises a series-connected resistor 691 and diode 679, connected between input terminal 675 and output terminal 688.

#### 5. Logical "and" building blocks

With reference to FIG. 7, there is illustrated a logical AND building block of type (D1) which comprises a plurality of diodes 679, each having their anodes connected together and connected to output terminal 628. A plurality of input terminals, illustratively shown as 675 65 through 678, are each individually connected to the cathode of a different one of diodes 679. A "pull-up" resistor 690 is connected to the junction of diodes 679 and to bias terminal 689, which is normally supplied with a suitable positive D.C. operating potential having a magnitude, in most instances, of 6 volts.

In operation, when the input signal to each of the input terminals 675 is TRUE-i.e., at zero or ground potential-the output signal at terminal 688 goes substantially to ground potential via the positive potential at bias terminal 689 and resistor 690. However, if any one or

more of the input signals goes FALSE (-6 volts), the corresponding diode is conductive, and, consequently, the output signal at terminal 688 is substantially at -6volts (FALSE). Therefore, it is seen that in a logical AND circuit, as just described, the output signal remains FALSE as long as any one or more of the input signals are FALSE; the output signal goes TRUE only when all of the input signals go TRUE and at no other time.

Type (D2) AND circuit shown in (b) is essentially the same as the (D1) type except for the addition of 10 dropping resistor 691 connected between the anodes of the diodes 679 and the output terminal 688. The (D3) type shown in (c) is substantially the same as the (D2)type but for the addition of bypass condenser 695 connected in parallel with the dropping resistor 691. In the 15 (D4) type of logical AND circuitry shown in (d), pullup resistor 690 has been omitted and replaced with a circuit comprising transistor 700, having its base connected to the junction of the diodes 679. The collector of the transistor 700 is connected to bias terminal 689, having 20 a negative D.C. operating potential of approximately 6 volts applied thereto. The emitter of transistor 700 is connected to output terminal 688 and is also connected to one end of resistor 701, the opposite end of resistor 701 being connected to bias terminal 702 having a posi- 25 tive D.C. operating potential of approximately 6 volts applied thereto. By the use of such an emitter follower type amplifier essentially as a pull-up resistor, a power gain of the output signal results, the input and output signals thereto being at all times of the same polarity as pre-30 viously described with respect to the emitter follower type building blocks.

The (D5) type AND circuit shown in (e) is substantially the same as the (D1) type except for the addition 35 of bias resistor 692, connected between input terminal 675 and bias terminal 693, which has applied thereto a negative D.C. operating potential. The (DR) type AND shown in (f) is somewhat different, in that resistor 696 now constitutes the pull-up resistor even though it is connected to one of the input terminals such as 675. In 40 operation, if the input signal to either or both of input terminals 675 and 676 is FALSE (-6 volts), the signal at output terminal 688 is likewise FALSE. However. if the input signal to both of the input terminals is TRUE (ground potential), the signal at output terminal 688 is 45 as amplified and inverted at output terminal 688. likewise TRUE, as in the logical AND circuits just described.

In (g) there is shown a resistor type of logical AND circuitry (R1) which comprises a plurality of resistors 696, each connected to output terminal 688 and having 50 the remaining end thereof individually connected to one of a plurality of input terminals, illustratively shown as 675 through 678. A pull-up resistor 690 is connected at one end to the junction of resistors 696 and is connected at its remaining end to bias terminal 689, which 55 has applied thereto a positive D.C. operating potential. This particular type of AND circuitry, however, does not render a TRUE or FALSE output signal respectively represented by a zero or a negative potential. In this instance, the TRUE or FALSE representation is by a posi- 60 tive or a negative output signal which is fed as an input signal to a suitable amplifier which re-establishes the proper voltage levels therefrom; i.e., zero and minus potentials indicative of TRUE and FALSE, respectively.

The operation of the device is as follows: The various 65 resistor values are properly chosen so that, when all of the input signals to terminals 675 through 678 are TRUE (ground potential), the output signal at terminal 638 is positive by an amount proportional to the resistor divider network. However, should any one or more of the input 70 signals be FALSE (negative), the output signal is also negative by an amount proportional to the resistor divider network, consequently FALSE also. AND circuit (R2) shown in (h) is substantially the same as type (R1) except for the addition of dropping resistor 691 connected 75

between the junction of resistors 696 and output terminal 688.

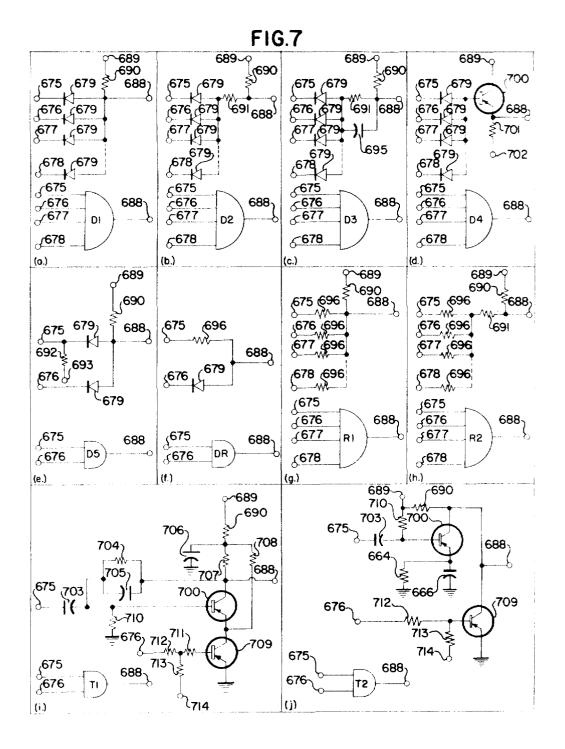

In (i) there is shown a transistor type logical AND (T1) which utilizes a pair of transistors 700 and 709. Input terminal 675 is connected to the base of transistor 700 through coupling condenser 703, whereas input terminal 676 is connected to the base of transistor 709 through series connected resistors 711 and 712. Bias resistor 713 is connected to the junction of resistors 711-712 and is connected to bias terminal 714, which has applied thereto a suitable positive D.C. operating potential. The base of transistor 700 is returned to ground potential through resistor 710 and is also connected to the collector thereof through parallel-connected resistor 704 and condenser 705. The emitter of transistor 700 is connected to the collector thereof through series-connected resistors The junction of resistors 707-708 is re-707 and 708. turned to A.C. ground through condenser 706 and is connected to bias terminal 689 through dropping resistor 690 connected therebetween, bias terminal 689 having applied thereto a suitable negative D.C. operating poten-The emitter of transistor 700 is directly connected tial. to the collector of transistor 709, whereas the emitter of transistor 709 is directly returned to ground potential. Output terminal 688 of the logical AND gate is directly connected to the collector of transistor 700.

In operation, if the input signal at terminal 676 is sufficiently negative, transistor 709 is rendered conductive and thus presents a very low resistance from the emitter of transistor 700 to ground. Consequently, transistor 700 functions in the same manner as a conventional "class A" inverter type amplifier such that A.C. signals of the proper frequency appearing at terminal 675 appear amplified and inverted at output terminal 688. However, if the input signal at terminal 676 is ground, transistor 709 is rendered non-conductive and thus appears as a very high resistance from the emitter of transistor 700 to ground. Consequently, since no emitter current can flow through transistor 700, signals appearing at input terminal 675 are not amplified by transistor 700. Thus it is seen that, when input terminal 676 is negative, A.C. signals appearing at terminal 675 appear amplified and inverted at output terminal 688; when input terminal 676 is ground, A.C. signals appearing at terminal 675 do not so appear

In (j) there is shown a second type of transistor logical AND (T2), which also utilizes a pair of transistors 700 and 709. Input terminal 675 is connected to the base of transistor 700 through coupling condenser 703, whereas input terminal 676 is connected to the base of transistor 709 through series-connected resistor 71. The emitter of transistor 709 is returned through series-dropping resistor 713 to bias terminal 714 having a suitable positive unidirectional operated potential applied thereto. The emitter of transistor 700 is returned to ground potential through a parallel-connected resistor and condenser network 664 and 666, whereas the base of transistor 700 is returned through series-dropping resistor 710 to bias terminal 689, which has a suitable negative unidirectional bias potential applied thereto. The collector of transistor 700 is connected to bias terminal 689 through series-dropping resistor 690 and is also connected to the collector of transistor 709 with both of the collectors of transistors 700 and 709 being connected to output terminal 688.

In operation, if the input signal at terminal 676 is TRUE, transistor 709 is rendered non-conductive and appears as a very high resistance from output terminal 688 to ground. Transistor 700 normally is conductivelybiased near saturation in such a manner that output terminal 688 is near ground potential. Thus, when positivegoing pulses appear at input terminal 675, they appear amplified and inverted at output terminal 688. However, if input terminal 676 is FALSE, transistor 709 is rendered conductive, and its collector current flows through resistor 690 to bias terminal 689. This collector current is of

sufficient magnitude that, even though no collector current were present in transistor 700, the potential at output terminal 688 is substantially ground. Thus, when posi-tive-going signals appear at terminal 675, the resulting change in collector current of transistor 700 produces essentially no appreciable change of potential of output terminal 688. Therefore, when input terminal 676 is TRUE, positive-going pulses at input terminal 675 appear as amplified and inverted at output terminal 688; however, when input terminal 676 is FALSE, output terminal 688 re- 10 mains essentially at ground potential, even though input positive-going signals appear at terminal 675.

### 6. Flipflop and multivibrator building blocks

The "flipflop" building block is normally composed of two inverters, as shown in FIG. 8, which are connected in cascade with the input of each one being connected to the output of the other. As shown in section (a) of FIG. 8, flipflop of the (F1) type consists of two 20 grounded emitter transistors 722 and 723 having input terminals 717 and 718 respectively connected to the base electrode, and output terminals 719 and 720 respectively connected to the collector electrode of transistors 722 and 723. The base of transistor 723 is connected to the 25 minal 719 the "reference output," and output terminal collector of transistor 722 through parallel connected resistor 734 and condenser 735, whereas the base of transistor 722 is connected to the collector of transistor 723 is returned to ground potential through resistors 729 and 728, respectively, whereas the collector thereof is respectively connected through dropping resistors 725 and 727 to bias terminals 724 and 726, which have applied tential.

In order to describe a mode of operation, it will first be assumed that transistor 722 is non-conductive and transistor 723 is conductive. Thus, when the input signal to terminal 717 goes negative, transistor 722 is now rendered conductive, the internal impedance thereof drops essentially to zero, and consequently the output signal at terminal 719 is thereafter TRUE (i.e., at ground potential). In addition, when transistor 722 is rendered conductive, the base of transistor 723 is momentarily driven positive via coupling condenser 735, and, consequently, transistor 723 is rendered non-conductive. Transistor 723 being non-conductive, the output signal at terminal 720 is FALSE. A negative bias potential applied from terminal 726 to the base of transistor 722 via resistor divider network 727-736-729 insures that transistor 722 remains conductive when the input signal to terminal 717 is no longer present. Consequently, as terminal 719 is essentially at ground potential, very little base current is supplied to transistor 723 via resistor 734, 55 and, as a result, transistor 723 remains non-conductive. Thus, the flipflop is now operating in one of its two stable states. It is to be noted at this point that during normal operation, a crystal diode, forming a part of a suitable triggering circuit, to be described later, is usually con-60 nected in series with each of input terminals 717 and 718 in such a manner that the states of both of transistors 722 and 723 remain unchanged even though the input signals to terminals 717 and 718, via their respective triggering circuit diode, effectively changes from FALSE back to a TRUE condition, respectively. In other words, the only time the states of transistors 722 and 723 change is only when the input signal to one of the terminals 717 and 718 goes from TRUE to FALSE. Now, when the input signal to terminal 718 goes negative, transistor 723 70is rendered conductive, the output at terminal 720 is now TRUE, and the base of transistor 722 is momentarily driven positive and thereby renders transistor 722 nonconductive. Transistor 722 being non-conductive, the

is applied from terminal 724 to the base of transistor 723 via network comprising resistors 725, 734, and 728, and coupling condenser 735, to insure that transistor 723 remains conductive. As before stated, insufficient base current is supplied to transistor 722, and, consequently, transistor 722 remains non-conductive. Thus, the flipflop is now operating in the other of its two stable states.

To summarize: When the input signal at terminal 717 momentarily goes negative, the flipflop is triggered to one of its two stable states, so that the output at the terminal 719 is TRUE (if not already TRUE) and the output at terminal 720 is FALSE; however, when the input to terminal 718 momentarily goes negative, the flipflop is

reset to its initial state, so that the output at terminal 15 719 is now FALSE and the output at terminal 720 is now TRUE. If, for some reason, the input signals to both of terminals 717 and 718 simultaneously go momentarily negative, the flipflop will change state regardless of the state in which it was initially.

In order to simplify the following description of the computer circuitry as much as possible, input terminal 717 will hereinafter be referred to as the "reference input,' ' input terminal 718 the "prime input," output ter-

- 720 the "prime output." In (c), flipflop of type (F3) is essentially the same as (F1) with the omission of base resistor 728, whereas, 723 through parallel connected resistor 736 and con-denser 737. The base of each of transistors 722 and 30 (F1) with the omission of base resistor 729. In (b), (d), and (f), flipflops of type (F2), (F4), and (F6) are essentially the same as flipflops (F1), (F3), and (F5), respectively, except for the addition of clamping diodes 731 and 733, which are utilized to fix the OFF level of thereto a suitable negative unidirectional operating po- 35 the collector voltages of transistors 722 and 723, respectively, as heretofore stated, when the transistor is nonconductive. In (g), flipflop of type (F7) is essentially the same as flipflop (F1) with the omission of coupling condensers 735 and 737.

- 40 With reference to (h), there is shown a "single-shot" type flipflop (F8) which is somewhat of the same circuit configuration as (F1), except that in (F8) there are omitted base resistors 728 and 729, resistor 736, prime input terminal 718, and reference output terminal 719. However, there have been added a bias resistor 739, 45 connecting the base of transistor 722 with bias terminal 738, which has a negative unidirectional operating potential applied thereto, and a coupling condenser 752, coupling the base of transistor 722 to reference input terminal 717. 50

The mode of operation of (F8) is not, however, as straightforward as the mode of operation of the justdescribed flipflops. In (F8), as a negative unidirectional bias potential from terminal 738 is normally maintained on the base of transistor 722, it is normally conductive and thus maintains the base of transistor 723 substantially at ground potential via resistor 734. The base of transistor 723 being at ground potential, the transistor is therefore normally non-conductive, and, consequently, the prime output at terminal 720 is normally FALSE. However, when the reference input goes from FALSE to TRUE (i.e., at ground potential), the base of transistor 722 is momentarily driven positive by condenser 752, and thus transistor 722 is immediately cut off and applies a negative potential spike via condenser 735 to turn on transistor 723. When transistor 723 is rendered conductive, the prime output at terminal 720 immediately goes TRUE. Since the charge on condenser 737 cannot change instantaneously, the base of transistor 722 is driven to some positive potential to maintain transistor 722 non-conductive even though the input signal at terminal 717 is no longer present. After a predetermined time delay, determined primarily by the discharge rate of condenser 737, a negative bias potential again appears on the base of tranoutput at terminal 719 is FALSE, and a negative bias 75 sistor 722 to render it conductive. When transistor 722 is

rendered conductive, the base of transistor 723 is momentarily driven positive and thereafter maintained essentially at ground potential by resistor 734 to turn off transistor 723, and thus the prime output at terminal 720 is again FALSE.

To summarize: The prime output is normally FALSE; a positive-going reference input gives an immediate TRUE prime output; however, after a predetermined time delay, the prime output changes from TRUE back to FALSE.

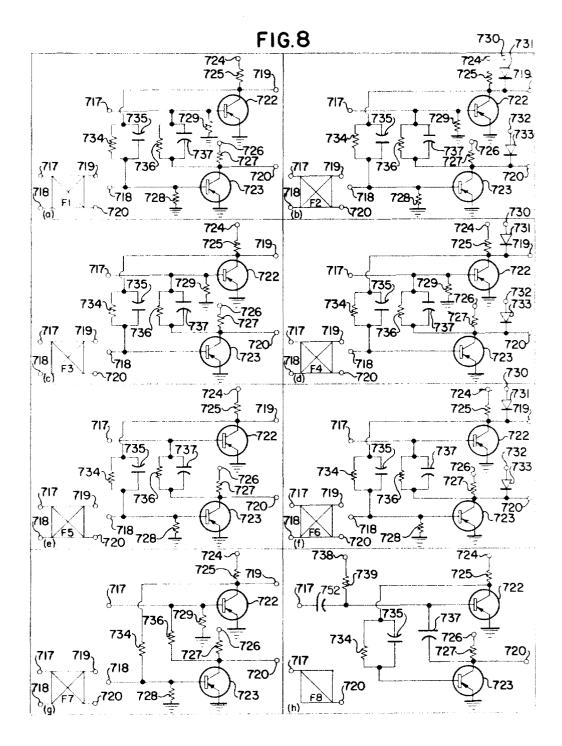

In section (a) of FIG. 9, there is shown a 50-kc. multi-10vibrator building block (MV1) which comprises two grounded-emitter transistors 722 and 723, each having its collector electrode respectively connected, through dropping resistors 725 and 727, to bias terminals 724 and 726, which have negative unidirection operating potentials 15 applied thereto. The collector output of transistor 722 is connected to the base input of transistor 723 via coupling condenser 735, whereas the collector output of transistor 723 is connected to the base input of transistor 722 via coupling condenser 737. The base of transistors 722 20 and 723 are respectively connected through dropping resistors 742 and 750 to bias terminals 741 and 749, each having a negative unidirectional operating potential applied thereto. The base of transistor 722 is connected to the cathode of crystal diode 748, whose anode is con- 25 nected to the junction of resistors 744 and 746. Resistor 744 is connected at its opposite end to bias terminal 743, which has a positive unidirectonal operating potential applied thereto, whereas resistor 746 is connected at its opposite end to bias terminal 745, which has a negative uni-30directional operating potential applied thereto.

The mode of operation of multivibrator (MV1) is as follows: When the circuit is first activated, the positive unidirectional operating potential at terminal 743 is the 35 first to be turned on to apply a positive bias to the base of transistor 722. Therefore, when the negative bias potentials at 724, 741, and 749 are simultaneously turned on, transistor 722 is rendered non-conductive, the reference output at terminal 719 is FALSE, and a negative potential 40 spike is applied to the base of transistor 723 via coupling condenser 735 to cause transistor 723 to be conductive. When transistor 723 is rendered conductive, the prime output at terminal 720 is TRUE, and condenser 737 begins to charge to a potential substantially equal to the negative bias potential at terminal 741. When condenser 737 is 45sufficiently charged, the potential on the base of transistor 722 is negative to the extent that transistor 722 is rendered conductive, the reference output goes from FALSE to TRUE, transistor 723 is rendered non-conductive, and consequently the prime output simultaneously goes from 50 TRUE to FALSE. When condenser 735 is sufficiently charged from the negative source at terminal 749, the base of transistor 723 is then negative to the extent that the transistor is rendered conductive, the prime output goes from FALSE back to TRUE, transistor 722 is ren- 55 dered non-conductive, and the reference output goes from TRUE back to FALSE. This sequence of events is repeated at a rate determined by the time constants in the charging and discharging paths of coupling condensers 735 and 737. In the instant computer, multivibrator 60 (MV1) operates at a frequency of 50 kilocycles.

In (b), multivibrator (MV2) is essentially the same as (MV1) except that bias resistors 744 and 746 and crystal diode 748 are omitted and replaced by coupling condensers 752 and 753 respectively connected to the base 65 of transistors 722 and 723. A dropping resistor 754 is connected at one end to the junction of condensers 752 and 753 and is connected at the remaining end thereof to input terminal 751.

Ignoring for the moment condensers 752 and 753 and 70 resistor 754, the mode of operation of multivibrator (MV2) is substantially the same as that of (MV1), the frequency of (MV2) being determined, as before, by the time constants in the charging and discharging paths of

puter, multivibrator (MV2) operates at a frequency of 400 cycles per second. However, in order to synchronize the change of state of the output of (MV2) with a "clocking" network, to be described hereinafter, a "clocking" signal from such network is fed as the input to terminal 751 of (MV2) and synchronization of the 400-cycle output of (MV2) with the "clocking" network takes place.

Assuming that transistor 723 has just been rendered conductive and transistor 722 has just been rendered nonconductive, the base of transistor 722 is driven positive via condenser 737, as previously described, and condenser 737 is now charging toward the negative potential at terminal 741. At the same time, a rectangularly-shaped clock pulse at input terminal 751 causes positive-going and negative-going potential spikes to be superimposed on the potential appearing on the base of transistor 722 in such a manner that, when the potential on the base of transistor 722 is approaching the value sufficient to render transistor 722 conductive, a succeeding negative-going potential spike, caused by the clock pulse at terminal 751, is sufficient to render transistor 722 conductive. Thus, even though the time period of (MV2) is much longer than that of the synchronizing clock pulse, the change of state of (MV2) takes place at the same time the clock input goes from TRUE to FALSE.

The single-shot flipflop of type (F9), as shown in (c), comprises a pair of grounded emitter transistors 722 and 723, whose collectors are individually returned to negative bias terminals 724 and 726 through dropping resistors 725 and 727, respectively. The base of transistor 722 is returned to ground potential through resistor 729 and is also connected to input terminal 717. The base of transistor 722 is further connected to the collector of transistor 723, whereas the base of transistor 723 is connected to the collector of transistor 722 through seriesconnected resistor 755 and condenser 735, the base of transistor 723 being further connected to a negative bias terminal 749.

The mode of operation of flipflop (F9) is essentially the same as that of the previously-described flipflop (F8), and, consequently, a further detailed description thereof is not deemed necessary. The essential difference between (F9) and (F8) is that in (F9) the mode of triggering is such that a momentary negative-going potential at input terminal 717 causes a change of state of the flipflop, whereas in flipflop (F8) a momentary positive-going potential at input terminal 717 causes a change of state thereof.

Flipflop of the (F10) type, as shown in (d), is of substantial identical circuit configuration with (F9), except for the addition of bypass condenser 756, which bypasses to ground undesirable extraneous signals. Flipflops (F11) through (F13) are essentially the same as the previously described flipflops. The main difference is the addition of a third transistor 758, which is connected in series with the emitter circuit of transistor 722. In a sense, transistors 722 and 758 operate together in the form of a transistor type of logical AND circuitry, in that it is necessary for both to be conductive in order for the reference output to be TRUE. As is evident from the previous description, this can happen only when the inputs to both of terminals 717 and 751 are simultaneously negative. Flipflop of type (F14), shown in (h), is essentially the same as the previously described (F1) type, except for the omission of base resistors **728** and **729**. Flipflop of type (F15) is essentially the same as flipflop of type (F8), except that in (F15) condenser 735 is removed.

# 7. Miscellaneous building blocks

With reference to (a) and (b) of FIG. 10, there are shown two types of pulse-shaping triggering circuits (TC1) and (TC2) which are utilized to provide "spiketype" triggering impulses for the various flipflops, in (c) coupling condensers 735 and 737. In the instant com- 75 and (d) are simple resistor-condenser networks, and in

(f) is shown a resistor-condenser filter and biasing circuit which is used in conjunction with the various pushbutton controls, all of which are to be further shown hereinafter. As the modes of operation of the various types of circuitry (a) through (d) and (f) are well known to those skilled in the art, a detailed description thereof is not deemed necessary for a full and complete understanding of the present invention.

In section (g) of FIG. 10 there is shown a photocell circuit configuration (PCA) utilizing photocell 160 as the 10 controlling element therein. In such circuitry, the anode of photocell 160 is grounded, and its cathode element is connected to output terminal 793. The cathode of photocell 160 is also connected through dropping resistor 797 to bias terminal 796 having a positive unidirectional oper- 15 ating potential applied thereto. The anode of crystal diode 795 is connected to the junction of output terminal 793, resistor 797, and photocell 160. Its cathode is bypassed to ground potential through condenser 799. The cathode of diode 795 is also connected to input terminal 20 792 through dropping resistor 794, and resistor 800 is connected between input terminal 792 and ground potential. As will be seen later, input terminal **792** is adapted to be selectively "open-circuited" or "short-circuited"; when open-circuited, the resistance between terminal 792 and 25 ground is determined by the value of resistor 800, whereas, when short-circuited, the resistance between terminal 792 and ground is zero.

The mode of operation of (PCA) is somewhat straightforward. Assuming that terminal 792 is open-circuited 30 and photocell 160 is non-exposed to the radiant energy from light source 164, the internal resistance of photocell 160 is at a maximum value such that the output potential at terminal 793 is at a maximum positive level. However, when photocell 160 is exposed to the radiant energy from light source 164, its internal impedance is decreased to a low value, and, consequently, the output at terminal 793 is decreased to a smaller value of positive potential. As will be seen later, the output from 40 terminal 793 is normally fed as an input to a previously described inverter type amplifier which establishes the proper TRUE and FALSE logic signal levels in a wellknown manner. The value of resistor 797 is properly chosen so as to be substantially greater than the value of resistor 794. Consequently, when input terminal 792 is 45 short-circuited to ground potential, the output signal level at terminal 793 drops essentially to zero potential whether or not photocell 160 is exposed to light source 164.

With reference to FIG. 10e, a second type of photocell circuit configuration includes a transistor 650 having 50 its emitter electrode connected to output terminal 652 and having its collector electrode connected through dropping resistor 655 to bias terminal 656, which has a negative unidirectional operating potential applied thereto. The base electrode of transistor 650 is connected to 55 the junction of the anode of photocell 681 and bias dropping resistor 661, the opposite end of resistor 661 being connected to bias terminal 662, which has a positive unidirectional operating potential applied thereto. The cathode of photocell 681 is connected directly to bias terminal 60 684, which has a negative unidirectional operating potential applied thereto.

The mode of operation of such a circuit configuration is as follows: When photocell 681 is non-exposed to radiant energy, so that its resistance is at a maximum 65 value, the potential on the base of transistor 650 is at a maximum positive value, and transistor 650 is thereby rendered non-conductive. However, when photocell 681 is exposed to radiant energy, its resistance is reduced to a substantially low value, so that a negative potential 70 from terminal 684 is applied to the base of transistor 650 and thereby renders transistor 650 conductive.

In section (h) there is shown a photocell pre-amplifier circuit configuration (PCPA) which comprises a transistor

nal 803, which has a negative unidirectional operating potential applied thereto. The emitter thereof is directly connected to output terminal 801 and is also connected through series dropping resistor 805 to bias terminal 804, which has a positive unidirectional operating potential appled thereto. The base electrode of transistor 802 is connected to one electrode of photoresistive element 806, whose remaining electrode is bypassed to ground potential through condenser 807. The junction of condenser 807 and photoresistor 806 is connected to the junction of resistors 808 and 809, remaining end of resistor 809 being grounded and the remaining end of resistor 808 being connected to bias terminal 810, which has applied thereto a negative unidirectional operating potential.

The mode of operation of photocell pre-amplifier (PCPA), again, is somewhat similar to the mode of operation of (PCA), previously described. When photoresistor 806 is exposed to radiant energy from a suitable light source, its internal resistance becomes a very low value, and, consequently, a negative potential is applied to the base of transistor 802, so that the output potential at terminal 801 is substantially that which appears on the base thereof, all in the same manner as previously described with respect to emitter-follower (E2) shown in section (b) of FIG. 6. However, when photoresistor 806 is not exposed to radiant energy, transistor 802 is virtually non-conductive, and the polarity of the output potential at terminal 801 is positive. As before stated with respect to photocell network (PCA), the output at terminal 801 appears as an input to a suitable amplifier which establishes the proper TRUE and FALSE logical signal levels.

With reference to section (i) of FIG. 10, there is illustrated a "peak-detector" circuit configuration (PD) which is utilized to detect the peaks of negative-going impulses, the reasons for which will become more apparent hereinafter. Such a detector comprises a groundedemitter transistor 813, whose collector electrode is connected to output terminal 812 and is also connected through dropping resistor 815 to bias terminal 814, which has a negative unidirectional operating potential applied thereto. The base input of transistor 813 is returned to ground potential through series-conected resistors 816 and 817, and is also connected to one end of a parallelconnected condenser and resistor network 818-819. The opposite end of the condenser-resistor network 818-819 is connected to the anode of crystal diode 820, whose cathode is coupled to input terminal 811 through condenser 825. The junction of condenser 825 and crystal diode 820 is connected through series-connected resistors 822 and 823 to bias terminal 824, which has a positive unidirectional operating potential applied thereto. Finally, a resistor 821 is connected between the junction of resistors 822-823 and the junction of resistors 816-817.

The relative values of the various resistor components are properly chosen so that a relatively small-valued positive bias appears on the base of transistor 813 to render the transistor normally non-conductive, so that the output at terminal 812 is normally FALSE (i.e., negative). However, a positive bias of slightly greater value appears on the cathode of crystal diode 820 to "back-bias" and thereby render diode 820 non-conductive. Thus, when the leading slope of a negative-going impulse appears at input terminal 811, crystal diode 820 remains nonconductive until the leading slope reaches a predetermined threshold level, thereby preventing any undesirable lowlevel noise impulses from entering the system. However, after the leading slope of the negative-going impulse exceeds the negative threshold level, diode 820 is rendered conductive, the incoming impulse is differentiated, and the negative-going potential "spike," derived from the differentiation, is applied to the base of transistor 813 and simultaneously begins to charge condenser 818. When 802 having its collector electrode connected to bias termi- 75 the negative-going spike is applied to the base of transistor

813, the transistor is rendered conductive, and the output at terminal 812 is thereafter TRUE. However, when the peak of the negative-going impulse begins to appear at terminal 811, the slope of the impulse is now much less than before, so that condenser 818 begins to discharge and 5 thereby decreases the magnitude of the negative bias potential on the base of transistor 813. When the peak of the incoming impulse appears at terminal 811, its slope being zero, condenser 818 is now fully discharged, and a positive bias is applied to the base of transistor 813 to 10 render the transistor non-conductive. As a result, the output at terminal 812 reverts from a TRUE condition back to a FALSE condition at a time coincidental with the arrival of the negative peak of the incoming impulse.

During operation of the memory of the present com- 15 puter, it was found that, when the ambient temperature of a ferromagnetic memory core is increased above normal room temperature, less drive current is needed to "switch" the core from one stable state of magnetic remanence to the other. Conversely, when its operating temperature 20 is decreased, a drive current of greater magnitude is necessary. Consequently, means are provided for automatically increasing and decreasing the drive current to the memory, depending upon whether its temperature has respectively decreased or increased above nominal room 25 temperature.

With reference to the final building block in section (j), there is shown a temperature-compensated current regulator (TCCR) which comprises a current control sec-30 tion 840, a regulator section 841, and a "dummy load" voltage section 842. The current control section 840 comprises a transistor 827, whose base is connected to the anode of a Zener diode 833, the cathode of diode 833 being returned to ground potential. The emitter of tran-35 sistor 827 is connected to terminal 867 and is also returned to ground potential through resistor 835. The collector and base electrodes of transistor 827 are respectively returned to bias terminal 832 through resistors 831 and 834, bias terminal 832 having a suitable negative 40 operating potential applied thereto. Two series-connected thermisters 829 and 830 are connected between terminal 868 and ground potential, whereas resistor 836 is connected between terminal 868 and the anode of Zener diode 837, the cathode of diode 837 being returned to ground potential. A dropping resistor 838 is connected between 45 the junction of resistor-diode 836-837 and bias terminal 839, which has a suitable negative unidirectional operating potential applied thereto.

Regulator section 841 comprises a transistor 828 having its collector electrode connected to terminal 867, 50 the base electrode connected to terminal 868, and the emitter electrode connected to the base of transistor 844. The emitter of transistor 844 is returned to ground potential through resistor 849 and also through series-connected resistor 850 and potentiometer 851. The collec- 55 tor of transistor 844 is connected to output terminal 843 through dropping resistor 845, and is also connected through dropping resistor 846 to the anodes of parallelconnected crystal diodes 847 and 848. Each cathode of diodes 847 and 848 is connected to terminal 869, which 60 is bypassed to ground potential by means of filter condenser 860.

The dummy-load voltage section 842 of the current regulator comprises transistor 852, whose emitter is connected to terminal 869 and is also returned to ground 65 potential through resistor 859, which is bypassed by condenser 866. The collector of transistor 852 is connected through dropping resistor 857 to bias terminal 856, which has a suitable negative unidirectional operating potential applied thereto. The base of transistor 852 is connected 70 to the emitter of transistor 853 and is also connected through dropping resistor 855 to bias terminal 854, which has a negative unidirectional operating potential applied thereto. The collector of transistor 853 is directly con-

directional operating potential applied thereto, whereas its base is connected to the movable arm of potentiometer 861. One end of potentiometer 861 is returned to ground potential through resistor 862, and its opposite end is connected through resistor 863 to bias terminal 864, which has a negative unidirectional operating potential applied thereto.

During operation, thermisters 829 and 830 are physically positioned in close proximity to the memory matrix, and, being in such contiguous relationship with respect to the ferrite cores of the memory, the resistance of each thermister either increases or decreases in response to a corresponding decrease or increase of the operating temperature of the memory cores. Zener diode 833 maintains a regulated bias potential of approximately -6 volts on the base of transistor 827, and, as transistor 827 is being operated as an emitter follower type amplifier, a regulated collector bias potential of approximately 6 volts is also applied to the collector of transistor 828, which is likewise operating as an emitter follower type amplifier. Zener diode 837 maintains a regulated bias potential of approximately -6 volts at the junction of resistors 836 and 838. Consequently, the variation of bias potential on the base of amplifier 828 is dependent solely upon the combined values of the resistances of thermisters 829 and 830, which, in turn, are dependent upon the operating temperature of the computer memory. Therefore, it is evident that the negative bias voltage on the base of transistor 844 is likewise dependent primarily upon the operating temperature of the computer memory.

During operation of the computer, there are times when there is no information either being "stored" or being "read out" of memory. Consequently, there are times when transistor 844 is not supplying any drive current to the memory. Due to the fact that the "alpha cutoff" characteristic of transistor 844 is less than one megacycle, its switching speed is not sufficient for the desirable switching requirements of the ferrite cores. Therefore, transistor 844 is maintained conductive at all times, and its output current is switched to the ferrite cores, when needed, or is adsorbed by dummy load 842, as the situation dictates.

The two emitter follower type amplifiers 852 and 853 of dummy load 842 function together essentially as a 600 ma. low impedance bias supply and provides a bias potential of approximately -8.5 volts at terminal 869, depending upon the setting of potentiometer 861, which adjusts the magnitude of the output voltage. Under the condition in which the various memory "driver" and 'grounder" amplifiers, which are to be described in detail hereinafter, are non-conductive, diodes 847 and 848 are biased in the forward direction by the negative potential at terminal 869, and, consequently, the drive current, delivered by transistor 844, passes through diodes 847 and 848 and is adsorbed by the dummy load. However, when the memory drivers and grounders are rendered conductive, the collector bias voltage on transistor 844 becomes approximately -10 volts and, consequently, is then more negative than the bias voltage at terminal 869. Therefore, diodes 847 and 848 are rendered non-conductive and prevent any further drive current from flowing therethrough. As a result, all of the drive current supplied by transistor 844 flows from terminal 843 and is delivered to the memory drivers and grounders.

The emitter bias on transistor 844 is adjusted by potentiometer 851 so that a "half-select" drive current of approximately 170 ma. is delivered thereby at a core operating temperature of 30 degrees centigrade. However, due to the action of thermisters 829 and 830 as previously described, the base bias on transistor 844 is automatically adjusted so that a range of "half-select" drive currents of from approximately 145 ma. at a temperature of 50 degrees centigrade to approximately 210 ma. at a temperature of 20 degrees centigrade is supplied to the memory cores via the driver and grounder amplinected to bias terminal 865, which has a negative uni- 75 fiers. Due to the fact that transistor 844 is operating

as a class A amplifier, a constant current is supplied thereby at a given temperature even with changing load conditions thereon. Thus it is seen that transistor 844 is continually supplying a constant current for a given temperature, which current is automatically switched from the memory drivers and grounders to the dummy load, and the magnitude of current not varying substantially with a switching of loads.

In the instant computer, it is necessary to utilize three such constant-current regulators: one is utilized to supply 10 half-select drive current to the ferrite cores located in addresses A and B of the memory; one is utilized to supply half-select drive current in the X direction through the memory cores located in each of the forty rows; and the other is utilized to supply half-select drive current in 15 the Y direction through memory cores in addresses  $\phi\phi$ through 99, all of which will be described in detail hereinafter. However, to avoid the necessity of constructing three identical temperature-compensated current regulators, as just described, it has been found expedient to 20 construct but a single current regulator which is substantially identical to the one shown and described, with the exception that three identical regulator sections 841 are utilized instead of one, and all three are connected in parallel at terminals 867, 868, and 859. Output termi- 25 nal 843 of each of the three regulator sections is connected to one of lines "CRA," "CRX," and "CRY" shown in FIGS. 20 and 26. However, for the sake of simplicity of description and illustration, each of the temperature-controlled current regulators 7000, 7001, and 30 7002 is illustrated as separate units even though, in fact, all are part of a composite unit as just described.

# 8. Magnetic core memory

As previously mentioned, binary information is mag- 35 netically stored in the computer in a ferrite core memory. The core memory consists of a muliplicity of toroidallyshaped cores which possess a substantially square magnetic hysteresis-loop characteristic. Each core has an outside diameter of .080 inch and an inner diameter of 40.050 inch, and is approximately .025 inch thick. It is well known to those skilled in the art that, due to the fact that the ferrite core possesses a substantially square hysteresis-loop characteristic, it therefore has two stable states of magnetic remanence, each of which is respec- 45 tively indicative of a binary "one" and a binary "zero." If a current-carrying conductor is threaded through the hole in the core, current in one direction through the conductor causes the core to be permanently magnetized in one direction, whereas current flow in the opposite direc- 50 tion through the conductor causes the core to be permanently magnetized in the opposite direction. Thus, a core is permanently magnetized in one direction or the other, depending upon the direction of current flow in the conductor threaded through the hole in the core. To summarize, 55 when a core is magnetized in one direction, it represents a binary "one," and when the core is magnetized in the other direction it represents a binary "zero." Four cores are utilized as a group to collectively represent a single decimal digit, although, with the use of the binary form 60 of notation, each group of four cores could possibly represent a number from "0" to "15." However, in the present computer, only the numbers "0" through "9" are actually stored in the memory.

In order to reverse the magnetic remanence of the core 65 from a binary one to a binary zero notation, or from a binary zero to a binary one by reversing the direction of magnetization thereof, a magnetomotive force of approximately three hundred and sixty milliampere turns is required at 25 degrees centrigrade. This is obtained by the 70 equivalent of passing 360 milliamperes of current through a single conductor threaded through the aperture of the core. A magnetomotive force of one-half this value-i.e., 180 milliampere-turns-does not appreciably disturb the magnetic remanence of the core.

After a core has been magnetized in a predetermined direction to represent a binary "one" or a binary "zero," it remains in that state of magnetic remanence indefinitely. The magnetic remanence state of the core is reversed only by a "full-amplitude" current impulse passing through the conductor threaded through the core. However, at certain predetermined times, it is necessary to "read" or determine the state of magnetic remanence of each core. Therefore, an additional conductor or "sense wire" is also threaded through the core aperture, so that, whenever the magnetic state of the core is changed from a binary "zero" to a binary "one" representation, or from a binary "one" to a binary "zero" representation, a voltage impulse is induced in the "sense wire" indicative of the reversal of magnetic remanence of the core. Thus it is seen that an impulse is induced in the "sense wire" only when the magnetic state of the core is reversed. In order to determine whether a particular core has been previously magnetically conditioned to represent a binary "one" or a binary "zero," a full-amplitude current of approximately 360 milliamperes is sent through the first-mentioned conductor in a direction to "set" the core to a binary "zero" representation. However, if the core had been previously set to a binary "zero" representation, a voltage impulse is not induced in the "sense wire." However, if the core was previously in a binary "one" representation, its magnetic remanent state is reversed, and, consequently, a voltage impulse is induced in the "sense wire" indicative of the reversal of the magnetic state of the core. After the magnetic state of the core is sensed, however, its magnetic state is immediately thereafter indicative of a binary "zero" representation regardless of its initial state. It is therefore necessary to restore the core to its original magnetic state normally by sensing a full-amplitude current impulse through the first-mentioned conductor to set the core back to a binary "one" representation if the core was previously in that particular state.

The core memory, utilized by the instant computer, has a capacity of one hundred ten-decimal-digit numbers which are hereinafter termed "words." Due to the fact that a negative word is stored in the memory as a positive complement, there is no need for a binary sign bit, as is conventional in most computers. A word is selectively stored in the memory in one of a hundred different locations which are called "addresses" and which are numbered from  $\phi\phi$  through 99. In addition to the one hundred normal addresses, there are two additional ad-dresses labeled A and B. The words stored in addresses  $\phi\phi$  through 99 not only represent arithmetic data, but also represent "instructions" which are utilized by the computer to dictate the sequence of operations therein. The words previously stored in addresses  $\phi\phi$  through 99 of the memory may be changed by instructions given by the computer; however, the words located in addresses A and B are used by the computer to store intermediate results during arithmetic computations and cannot be changed directly by instructions.

With reference to FIGS. 11 and 12, there is schematically shown the ferrite core memory utilized by the present computer. Such a memory comprises four thousand and eighty type N-400-080 ferrite cores at present manufactured by the assignee of the instant application.

The ferrite cores of the memory are selectively arranged in a pattern of rectangularly-shaped configuration having one hundred two vertical columns and forty horizontal rows thereof. The first one hundred columns, as viewed from left to right, respectively represent memory address locations  $\phi\phi$  through 99, whereas the two remaining rightmost columns respectively represent address locations A and B. In each of the columns. from the topmost to the bottommost core, the forty cores are arranged in a succession of ten groups, with each group containing four cores. Each group of four cores is representative of a decimal digit of a predetermined 75 order, whereas all of the groups of a particular column

collectively represent all of the orders of a word ten decimal digits in length. Each of the ten successive decimal digits of the word located in any address is respectively identified as the "first-order" digit through the "tenth-order" digit, where the first order is the lowest or Б "penny" digit and the tenth order is the highest order digit of the number or word. The four cores used to store the first-order digit of a word which is residing in an address in the memory are located in the first row through the fourth row, counting from bottom to top. 10 The four cores used to store the second-order digit of the word are located immediately above in the fifth through the eighth rows; in the drawing, only the fifth and eighth rows are shown, rows six and seven being omitted for the sake of simplicity. The four cores used 15 to store the third-order digit are located immediately above in rows nine through twelve, where rows nine and twelve are the only ones illustrated, rows ten and eleven being omitted for the reasons just mentioned. The location of each higher-order digit progresses upward, as 20 just described, so that the tenth or highest-order digit is located at the top of the column in the last four rows shown; i.e., thirty-seven through forty. Therefore, it is seen, the maximum storage in each memory address is a ten-digit number which will hereinafter be called a 25 ' the lowest-order digit thereof being located at "word,' the bottom of each address and the highest-order digit thereof being located at the top of each address.