# MVME2300-Series VME Processor Module Installation and Use

V2300A/IH2

#### **Notice**

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

No part of this material may be reproduced or copied in any tangible medium, or stored in a retrieval system, or transmitted in any form, or by any means, radio, electronic, mechanical, photocopying, recording or facsimile, or otherwise, without the prior written permission of Motorola, Inc.

It is possible that this publication may contain reference to, or information about Motorola products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

### **Restricted Rights Legend**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282

#### **Preface**

The MVME2300-Series VME Processor Module Installation and Use manual provides information you will need to install and use your MVME2300-series VME processor module. The MVME2300 VME processor module is based on an MPC603 or MPC604 PowerPC microprocessor, and features dual PCI Mezzanine Card (PMC) slots with front panel and/or P2 I/O. The MVME2300 is currently available in the following configurations:

| Model    | MPC       | Memory         |

|----------|-----------|----------------|

| MVME2301 | MPC603    | 16MB ECC DRAM  |

| MVME2302 | @ 200 MHz | 32MB ECC DRAM  |

| MVME2303 |           | 64MB ECC DRAM  |

| MVME2304 |           | 128MB ECC DRAM |

| MVME2305 | MPC604    | 16MB ECC DRAM  |

| MVME2306 | @ 300 MHz | 32MB ECC DRAM  |

| MVME2307 |           | 64MB ECC DRAM  |

| MVME2308 |           | 128MB ECC DRAM |

The MVME2300-series module is compatible with optional double-width or single-width PCI Mezzanine Cards (PMCs), and the PMCspan PCI expansion mezzanine module. By utilizing the two onboard PMC slots and stacking PMCspan(s), the MVME2300 provides support for up to six PMCs.

This manual includes hardware preparation and installation instructions for the MVME2300-series module, information about using the front panel, a functional description, information about programming the board, using the PPCBug debugging firmware, and advanced debugger topics. Other appendices provide the MVME2300-series specifications, connector pin assignments, and a glossary of terms. Additional manuals you may wish to obtain are listed in Appendix A, *Ordering Related Documentation*.

The information in this manual applies principally to the MVME2300-series module. The PMCspan and PMCs are described briefly here but are documented in detail in separate publications, furnished with those products. Refer to the individual product documentation for complete preparation and installation instructions. These manuals are listed in Appendix A, *Ordering Related Documentation*.

This manual is intended for anyone who wants to design OEM systems, supply additional capability to an existing compatible system, or work in a lab environment for experimental purposes. A basic knowledge of computers and digital logic is assumed.

### **Document Terminology**

Throughout this manual, a convention is used which precedes data and address parameters by a character identifying the numeric format as follows:

| \$ | Dollar    | Specifies a hexadecimal character |  |

|----|-----------|-----------------------------------|--|

| 0x | Zero-x    |                                   |  |

| %  | Percent   | Specifies a binary number         |  |

| &  | Ampersand | Specifies a decimal number        |  |

For example, "12" is the decimal number twelve, and "\$12" (hexadecimal) is the equivalent of decimal number eighteen. Unless otherwise specified, all address references are in hexadecimal.

An asterisk (\*) following the signal name for signals which are *level-significant* denotes that the signal is true or valid when the signal is low.

An asterisk (\*) following the signal name for signals which are *edge-significant* denotes that the actions initiated by that signal occur on high-to-low transition.

In this manual, assertion and negation are used to specify forcing a signal to a particular state. In particular, assertion and assert refer to a signal that is active or true; negation and negate indicate a signal that is inactive or false. These terms are used independently of the voltage level (high or low) that they represent.

Data and address sizes are defined as follows:

| Byte        | 8 bits, numbered 0 through 7, with bit 0 being the least significant.   |

|-------------|-------------------------------------------------------------------------|

| Half word   | 16 bits, numbered 0 through 15, with bit 0 being the least significant. |

| Word        | 32 bits, numbered 0 through 31, with bit 0 being the least significant. |

| Double word | 64 bits, numbered 0 through 63, with bit 0 being the least significant. |

### Safety Summary Safety Depends On You

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the equipment. Motorola, Inc. assumes no liability for the customer's failure to comply with these requirements.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. The equipment is supplied with a three-conductor AC power cable. The power cable must be plugged into an approved three-contact electrical outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards.

#### Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment constitutes a definite safety hazard.

#### Keep Away From Live Circuits.

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified maintenance personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### Do Not Service or Adjust Alone.

Do not attempt internal service or adjustment unless another person capable of rendering first aid and resuscitation is present.

#### Use Caution When Exposing or Handling the CRT.

Breakage of the Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, avoid rough handling or jarring of the equipment. Handling of the CRT should be done only by qualified maintenance personnel using approved safety mask and gloves.

### Do Not Substitute Parts or Modify Equipment.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that safety features are maintained.

### **Dangerous Procedure Warnings.**

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

This equipment generates, uses, and can radiate electro-magnetic energy. It may cause or be susceptible to electro-magnetic interference (EMI) if not installed and used in a cabinet with adequate EMI protection.

If any modifications are made to the product, the modifier assumes responsibility for radio frequency interference issues. Changes or modifications not expressly approved by Motorola Computer Group could void the user's authority to operate the equipment.

European Notice: Board products with the CE marking comply with the EMC Directive (89/336/EEC). Compliance with this directive implies conformity to the following European Norms:

EN55022 (CISPR 22) Radio Frequency Interference

EN50082-1 (IEC801-2, IEC801-3, IEC801-4) Electromagnetic Immunity

The product also fulfills EN60950 (product safety) which is essentially the requirement for the Low Voltage Directive (73/23/EEC).

This board product was tested in a representative system to show compliance with the above mentioned requirements. A proper installation in a CE-marked system will maintain the required EMC/safety performance.

For minimum RF emissions, it is essential that you implement the following conditions:

- 1. Install shielded cables on all external I/O ports.

- 2. Connect conductive chassis rails to earth ground to provide a path for connecting shields to earth ground.

- 3. Tighten all front panel screws.

All Motorola PWBs (printed wiring boards) are manufactured by UL-recognized manufacturers, with a flammability rating of 94V-0.

The computer programs stored in the Read Only Memory of this device contain material copyrighted by Motorola Inc., 1995, and may be used only under a license such as those contained in Motorola's software licenses.

The software described herein and the documentation appearing herein are furnished under a license agreement and may be used and/or disclosed only in accordance with the terms of the agreement.

The software and documentation are copyrighted materials. Making unauthorized copies is prohibited by law.

No part of the software or documentation may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means without the prior written permission of Motorola, Inc.

$Motorola^{ ext{\$}}$  and the Motorola symbol are registered trademarks of Motorola, Inc.  $PowerPC^{ ext{TM}}$  is a trademark of International Business Machines Corporation and is used by Motorola with permission.

All other products mentioned in this document are trademarks or registered trademarks of their respective holders.

© Copyright Motorola 1998 All Rights Reserved Printed in the United States of America April 1998

# **Contents**

| Chapter 1 Preparing and Installing the MVME2300-Series Modu | ıle         |

|-------------------------------------------------------------|-------------|

| Introduction                                                | 1-1         |

| MVME230x Description                                        |             |

| MVME230x Module                                             |             |

| PMCspan Expansion Mezzanine                                 |             |

| PCI Mezzanine Cards (PMCs)                                  |             |

| VMEsystem Enclosure                                         |             |

| System Console Terminal                                     |             |

| Overview of Start-Up Procedures                             |             |

| Unpacking the MVME230x Hardware                             |             |

| Preparing the MVME230x Hardware                             | 1-7         |

| MVME230 <i>x</i>                                            | 1-7         |

| Setting the Flash Memory Bank A/Bank B Reset Vector         |             |

| Header (J15)                                                | 1-10        |

| Setting the VMEbus System Controller Selection Header       | (J16) 1-10  |

| Setting the General-Purpose Software-Readable Header        |             |

| PMCs                                                        |             |

| PMCspan                                                     | 1-12        |

| System Console Terminal                                     | 1-12        |

| Installing the MVME230x Hardware                            | 1-13        |

| Taking ESD Precautions                                      | 1-13        |

| PMCs                                                        | 1-13        |

| Primary PMCspan                                             | 1-15        |

| Secondary PMCspan                                           | 1-18        |

| MVME230 <i>x</i>                                            |             |

| Installation Considerations                                 | 1-23        |

| Chapter 2 Operating Instructions                            |             |

| Introduction                                                | 2-1         |

| Applying Power                                              | 2-1         |

| MVME230x                                                    | 2-2         |

| Switches                                                    |             |

| ABT (S1)                                                    | <b>2-</b> 3 |

| RST (S2)                             | 2-3  |

|--------------------------------------|------|

| Status Indicators                    | 2-4  |

| BFL (DS1)                            | 2-4  |

| CPU (DS2)                            |      |

| PMC (DS3)                            | 2-4  |

| PMC (DS4)                            | 2-4  |

| 10/100 BASET Port                    | 2-4  |

| DEBUG Port                           | 2-5  |

| PMC Slots                            |      |

| PCI MEZZANINE CARD (PMC Slot 1)      | 2-6  |

| PCI MEZZANINE CARD (PMC Slot 2)      | 2-6  |

| PMCspan                              |      |

|                                      |      |

| Chapter 3 Functional Description     |      |

| Introduction                         | 3-1  |

| Features                             |      |

| General Description                  |      |

| Block Diagram                        |      |

| MPC603/604 Processor                 |      |

| PCI Bus Latency                      |      |

| DRAM Memory                          |      |

| DRAM Latency                         |      |

| Flash Memory                         |      |

| Flash Latency                        |      |

| Ethernet Interface                   | 3-12 |

| PCI Mezzanine Card (PMC) Interface   | 3-13 |

| PMC Slot 1 (Single-Width PMC)        | 3-14 |

| PMC Slot 2 (Single-Width PMC)        | 3-14 |

| PMC Slots 1 and 2 (Double-Width PMC) | 3-15 |

| PCI Expansion                        | 3-15 |

| VMEbus Interface                     | 3-15 |

| Asynchronous Debug Port              | 3-16 |

| PCI-ISA Bridge (PIB) Controller      |      |

| Real-Time Clock/NVRAM/Timer Function | 3-17 |

| PCI Host Bridge                      |      |

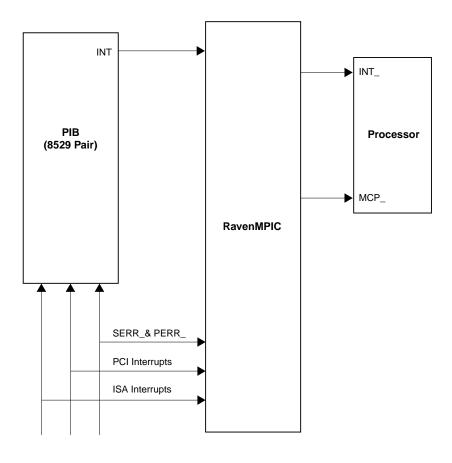

| Interrupt Controller (MPIC)          | 3-18 |

| Programmable Timers                  | 3-19 |

| Interval Timers                      | 3-19 |

|                                      |      |

|           | 16/32-Bit Timers                      | 3-19 |

|-----------|---------------------------------------|------|

| Chapter 4 | Programming the MVME230x              |      |

| Introd    | luction                               | 4-1  |

|           | ory Maps                              |      |

|           | ocessor Bus Memory Map                |      |

|           | Default Processor Memory Map          |      |

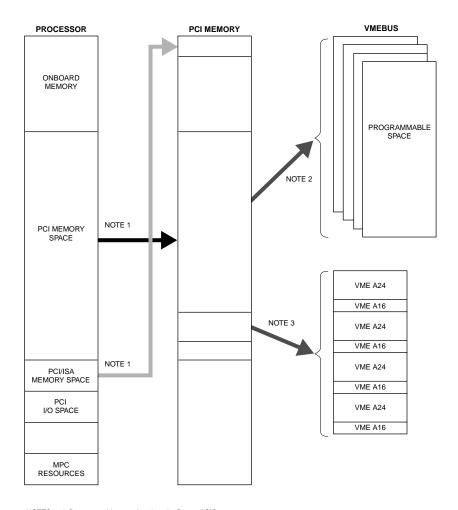

| PC        | CI Local Bus Memory Map               |      |

| VI        | MEbus Memory Map                      | 4-3  |

|           | amming Considerations                 |      |

| PC        | CI Arbitration                        | 4-4  |

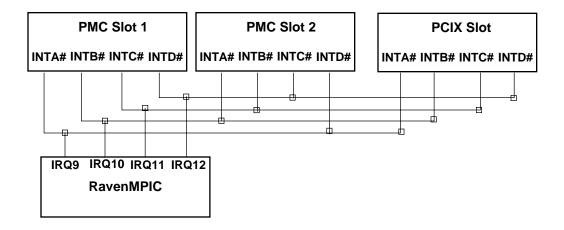

| In        | terrupt Handling                      | 4-6  |

| Di        | MA Channels                           | 4-8  |

| So        | ources of Reset                       | 4-8  |

| Er        | ndian Issues                          | 4-10 |

|           | Processor/Memory Domain               | 4-10 |

|           | PCI Domain                            | 4-10 |

|           | VMEbus Domain                         | 4-11 |

| -         | PPCBug                                |      |

|           | ug Overview                           |      |

|           | ug Basics                             |      |

|           | emory Requirements                    |      |

| PF        | PCBug Implementation                  | 5-3  |

|           | Hardware, and Firmware Initialization |      |

|           | PPCBug                                |      |

|           | ebugger Commands                      |      |

| Di        | iagnostic Tests                       | 5-10 |

| Chapter 6 | Modifying the Environment             |      |

| -         |                                       |      |

|           | view                                  |      |

|           | G - Configure Board Information Block |      |

|           | - Set Environment                     |      |

|           | onfiguring the PPCBug Parameters      |      |

|           | onfiguring the VMEbus Interface       |      |

| Motor     | rola Computer Group Documents         |      |

|           |                                       |      |

| Manufacturers' Documents                        | A-2  |

|-------------------------------------------------|------|

| Related Specifications                          | A-5  |

| Specifications                                  |      |

| Cooling Requirements                            | B-3  |

| EMC Regulatory Compliance                       | B-4  |

| Introduction                                    | C-1  |

| Pin Assignments                                 | C-1  |

| VMEbus Connector - P1                           | C-2  |

| VMEbus Connector - P2                           | C-4  |

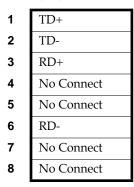

| Serial Port Connector - DEBUG (J2)              | C-6  |

| Ethernet Connector - 10BASET (J3)               | C-6  |

| CPU Debug Connector - J1                        | C-7  |

| PCI Expansion Connector - J18                   |      |

| PCI Mezzanine Card Connectors - J11 through J14 |      |

| PCI Mezzanine Card Connectors - J21 through J24 | C-18 |

| Solving Startup Problems                        | D-1  |

| Abbreviations, Acronyms, and Terms to Know      |      |

# **Figures**

| Figure 1-1. MVME230x Switches, LEDs, Headers, Co   | nnectors1-9 |

|----------------------------------------------------|-------------|

| Figure 1-2. General-Purpose Software-Readable Head | der1-12     |

| Figure 1-3. Typical Single-width PMC Module Placer | nent on     |

| MVME230x                                           | 1-15        |

| Figure 1-4. PMCspan-002 Installation on an MVME23  | 30x1-17     |

| Figure 1-5. PMCspan-010 Installation onto a        |             |

| PMCspan-002/MVME230x                               | 1-19        |

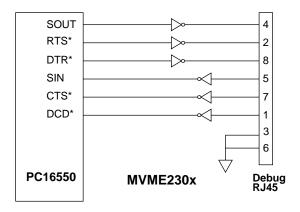

| Figure 2-1. MVME230x DEBUG Port Configuration      | 2-5         |

| Figure 3-1. MVME230x Block Diagram                 | 3-4         |

| Figure 3-2. Memory Block Diagram                   | 3-8         |

| Figure 4-1. VMEbus Master Mapping                  |             |

| Figure 4-2. MVME230x Interrupt Architecture        |             |

# **Tables**

| Table 1-1. MVME230x Models                                       | 1-2    |

|------------------------------------------------------------------|--------|

| Table 1-2. PMCspan Models                                        | 1-3    |

| Table 1-3. Start-Up Overview                                     | 1-4    |

| Table 3-1. MVME230x Features                                     | 3-1    |

| Table 3-2. Power Requirements                                    | 3-5    |

| Table 3-3. PowerPC 60x Bus to PCI Access Timing                  | 3-6    |

| Table 3-4. PCI to ECC Memory Access Timing                       | 3-7    |

| Table 3-5. PowerPC 60x Bus to DRAM Access Timing using 60ns Page |        |

| Devices                                                          | 3-9    |

| Table 3-6. PowerPC 60x Bus to DRAM Access Timing Using 50ns, EDO |        |

| Devices                                                          | .3-10  |

| Table 3-7. PowerPC 60x Bus to FLASH Access Timing for Bank B     |        |

| (16-bit Port)                                                    | .3-12  |

| Table 4-1. Processor Default View of the Memory Map              | 4-2    |

| Table 4-2. PCI Arbitration Assignments                           | 4-6    |

| Table 4-3. Classes of Reset and Effectiveness                    | 4-9    |

| Table 5-1. Debugger Commands                                     | 5-7    |

| Table 5-2. Diagnostic Test Groups                                | . 5-11 |

| Table A-1. Motorola Computer Group Documents                     | A-1    |

| Table A-2. Manufacturers' Documents                              | A-2    |

| Table A-3. Related Specifications                                | A-5    |

| Table B-1. MVME230x Specifications                               | B-1    |

| Table C-1. P1 VMEbus Connector Pin Assignments                   | C-2    |

| Table C-2. P2 Connector Pin Assignment                           | C-4    |

| Table C-3. DEBUG (J2)Connector Pin Assignments                   | C-6    |

| Table C-4. 10/100 BASET (J3) Connector Pin Assignments           | C-6    |

| Table C-5. Debug Connector Pin Assignments                       | C-7    |

| Table C-6. J18 - PCI Expansion Connector Pin Assignments         | C-12   |

| Table C-7. J11 - J12 PMC1 Connector Pin Assignments              | C-15   |

| Table C-8. J13 - J14 PMC1 Connector Pin Assignments    | C-16 |

|--------------------------------------------------------|------|

| Table C-9. J21 and J22 PMC2 Connector Pin Assignments  |      |

| Table C-10. J23 and J24 PMC2 Connector Pin Assignments |      |

| Table D-1. Troubleshooting MVME230x Modules            | D-2  |

## Introduction

This chapter provides a brief description of the MVME2300-Series VME Processor Module, and instructions for preparing and installing the hardware.

In this manual, the name MVME230*x* refers to all models of the MVME2300-series boards, unless otherwise specified.

# MVME230x Description

The MVME2300-series VME processor module is a PCI Mezzanine Card (PMC) carrier board. It is based on the PowerPC<sup>TM</sup> 603 or 604 microprocessor, MPC603 or MPC604.

Two front panel cutouts provide access to PMC I/O. One double-width or two single-width PMCs can be installed directly on the MVME230x. Optionally, one or two PMCspan PCI expansion mezzanine modules can be added to provide the capability of up to four additional PMC modules.

Two RJ45 connectors on the front panel provide the interface to 10/100Base-T Ethernet, and to a debug serial port.

The following list is of equipment that is appropriate for use in an MVME230x system:

- □ PMCspan PCI expansion mezzanine module

- □ Peripheral Component Interconnect (PCI) Mezzanine Cards (PMC)s

- □ VMEsystem enclosure

- □ System console terminal

- □ Disk drives (and/or other I/O) and controllers

- Operating system (and/or application software)

#### MVME230x Module

The MVME230x module is a powerful, low-cost embedded VME controller and intelligent PMC carrier board. The MVME230x is currently available in the configurations shown in Table 1-1.

The MVME230x includes support circuitry such as ECC DRAM, PROM/Flash memory, and bridges to the Industry Standard Architecture (ISA) bus and the VMEbus. The MVME230x's PMC carrier architecture allows flexible configuration options and easy upgrades. It is designed to support one or two PMCs, plus one or two optional PCI expansion mezzanine modules that each support up to two PMCs. It occupies a single VMEmodule slot, except when optional PCI expansion mezzanine modules are also used:

| MVME230x | MPC       | Type           |

|----------|-----------|----------------|

| MVME2301 | MPC603    | 16MB ECC DRAM  |

| MVME2302 | @ 200 MHz | 32MB ECC DRAM  |

| MVME2303 |           | 64MB ECC DRAM  |

| MVME2304 |           | 128MB ECC DRAM |

| MVME2305 | MPC604    | 16MB ECC DRAM  |

| MVME2306 | @ 300 MHz | 32MB ECC DRAM  |

| MVME2307 |           | 64MB ECC DRAM  |

| MVME2308 |           | 128MB ECC DRAM |

Table 1-1. MVME230x Models

The MVME230x interfaces to the VMEbus via the P1 and P2 connectors. It also draws +5V, +12V, and -12V power from the VMEbus backplane through these two connectors. The +3.3V power, used for the PCI bridge chip and possibly for the PMC mezzanine, is derived onboard from the +5V power.

Support for two IEEE P1386.1 PCI mezzanine cards is provided via eight 64-pin SMT connectors. Front panel openings are provided on the MVME230x board for the two PMC slots.

In addition, there are 64 pins of I/O from PMC slot 1 and 46 pins of I/O from PMC slot 2 that are routed to P2. The two PMC slots may contain two single-wide PMCs or one double-wide PMC.

## **PMCspan Expansion Mezzanine**

An optional PCI expansion mezzanine module or PMC carrier board, PMCspan, provides the capability of adding two additional PMCs. Two PMCspans can be stacked on an MVME230x, providing four additional PMC slots, for a total of six slots including the two onboard the MVME230x. Table 1-2 lists the PMCspan models that are available for use with the MVME230x.

Table 1-2. PMCspan Models

| <b>Expansion Module</b> | Description                                                                                                                                               |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMCSPAN-002             | Primary PCI expansion mezzanine module. Allows two PMC modules for the MVME230x. Includes 32-bit PCI bridge.                                              |

| PMCSPAN-010             | Secondary PCI expansion mezzanine module. Allows two additional PMC modules for the MVME230x. Does not include 32-bit PCI bridge; requires a PMCSPAN-002. |

## **PCI Mezzanine Cards (PMCs)**

The PMC slots on the MVME230x board are IEEE P1386.1 compliant. P2 I/O-based PMCs that follow the PMC committee recommendation for PCI I/O when using the 5-row VME64 extension connector will be pin-out compatible with the MVME230x.

The MVME230x board supports both front panel I/O and rear panel P2 I/O through either PMC slot 1 or PMC slot 2. 64 pins of I/O from slot 1 and 46 pins of I/O from slot 2 are routed directly to P2.

## **VMEsystem Enclosure**

Your MVME230x board must be installed in a VMEsystem chassis with both P1 and P2 backplane connections. It requires a single slot, except when PMCspan carrier boards are used. Allow one extra slot for each PMCspan.

## **System Console Terminal**

In normal operation, connection of a debug console terminal is required only if you intend to use the MVME230x's debug firmware, PPCBug, interactively. An RJ45 connector is provided on the front panel of the MVME230x for this purpose.

# **Overview of Start-Up Procedures**

The following table lists the things you will need to do before you can use this board, and tells where to find the information you need to perform each step. Be sure to read this entire chapter and read all Caution and Warning notes before beginning.

Table 1-3. Start-Up Overview

| What you need to do  | Refer to                                                                                | On page |

|----------------------|-----------------------------------------------------------------------------------------|---------|

| Unpack the hardware. | Unpacking the MVME230x Hardware                                                         | 1-7     |

| Set jumpers on the   | Preparing the MVME230x Hardware                                                         | 1-7     |

| MVME230x module.     | MVME230x                                                                                | 1-7     |

| Prepare the PMCs.    | PMCs                                                                                    | 1-14    |

|                      | For additional information on PMCs, refer to the PMC manuals provided with these cards. |         |

Table 1-3. Start-Up Overview (Continued)

| What you need to do                                                | Refer to                                                                                                                                                                                 | On page |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Prepare the PMCspan                                                | PMCspan                                                                                                                                                                                  | 1-14    |

| module(s).                                                         | For additional information on PMCspan, refer to the <i>PMCspan PMC Adapter Carrier Module Installation and Use</i> manual, listed in Appendix A, <i>Ordering Related Documentation</i> . | A-1     |

| Prepare a console terminal.                                        | System Console Terminal                                                                                                                                                                  | 1-15    |

| Prepare any other optional devices or equipment you will be using. | For more information on optional devices and equipment, refer to the documentation provided with that equipment.                                                                         |         |

| Install the PMCs on the                                            | PMCs                                                                                                                                                                                     | 1-15    |

| MVME230x module.                                                   | PMC Slots                                                                                                                                                                                | 2-6     |

|                                                                    | For additional information on PMCs, refer to the PMC manuals provided with these cards.                                                                                                  |         |

| Install the primary PMCspan                                        | Primary PMCspan                                                                                                                                                                          | 1-17    |

| module (if used).                                                  | For additional information on PMCspan, refer to the <i>PMCspan PMC Adapter Carrier Module Installation and Use</i> manual, listed in Appendix A, <i>Ordering Related Documentation</i> . | A-1     |

| Install the secondary                                              | Secondary PMCspan                                                                                                                                                                        | 1-19    |

| PMCspan module (if used).                                          | For additional information on PMCspan, refer to the <i>PMCspan PMC Adapter Carrier Module Installation and Use</i> manual, listed in Appendix A, <i>Ordering Related Documentation</i> . | A-1     |

| Install and connect the                                            | Installing the MVME230x Hardware                                                                                                                                                         | 1-14    |

| MVME230x module.                                                   | MVME230x                                                                                                                                                                                 | 1-22    |

|                                                                    | Installation Considerations                                                                                                                                                              | 1-24    |

| Connect a console terminal.                                        | MVME230x                                                                                                                                                                                 | 1-22    |

|                                                                    | Debug Port                                                                                                                                                                               | 2-5     |

**Table 1-3. Start-Up Overview (Continued)**

| What you need to do                                                           | Refer to                                                                                                                                                 | On page |

|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Connect any other optional                                                    | Connector Pin Assignments                                                                                                                                | C-1     |

| devices or equipment you will be using.                                       | For more information on optional devices and equipment, refer to the documentation provided with that equipment.                                         |         |

| Power up the system.                                                          | Installing the MVME230x Hardware                                                                                                                         | 1-14    |

|                                                                               | Status Indicators                                                                                                                                        | 2-4     |

|                                                                               | If any problems occur, refer to the section <i>Diagnostic Tests</i> in Chapter 5, <i>PPCBug</i> .                                                        | 5-10    |

|                                                                               | You may also wish to obtain the <i>PPCBug Diagnostics Manual</i> , listed in Appendix A, <i>Ordering Related Documentation</i> .                         | A-1     |

| Examine the environmental                                                     | ENV - Set Environment                                                                                                                                    | 6-3     |

| parameters and make any changes needed.                                       | You may also wish to obtain the <i>PPCBug Firmware Package User's Manual</i> , listed in Appendix A, <i>Ordering Related Documentation</i> .             | A-1     |

| Program the MVME230 <i>x</i> module and PMCs as needed for your applications. | Preparing the MVME230x Hardware                                                                                                                          | 1-7     |

|                                                                               | Programming the MVME230x                                                                                                                                 | 4-1     |

|                                                                               | For additional information on PMCs, refer to the PMC manuals provided with these cards.                                                                  |         |

|                                                                               | You may also wish to obtain the MVME2300-Series VME Processor Module Programmer's Reference Guide, listed in Appendix A, Ordering Related Documentation. | A-1     |

## **Unpacking the MVME230x Hardware**

Note

If the shipping carton(s) is/are damaged upon receipt, request that the carrier's agent be present during the unpacking and inspection of the equipment.

Unpack the equipment from the shipping carton(s). Refer to the packing list(s) and verify that all items are present. Save the packing material for storing and reshipping of equipment.

Avoid touching areas of integrated circuitry; static discharge can damage these circuits.

# **Preparing the MVME230x Hardware**

To produce the desired configuration and ensure proper operation of the MVME230x, you may need to carry out certain modifications before and after installing the modules.

The following paragraphs discuss the preparation of the MVME230x hardware components prior to installing them into a chassis and connecting them.

### MVME230x

The MVME230*x* provides software control over most options; by setting bits in control registers after installing the MVME230*x* in a system, you can modify its configuration. The MVME230*x* control registers are briefly described in Chapter 4, with additional information in the *MVME2300-Series VME Processor Module Programmer's Reference Guide* as listed in the table *Motorola Computer Group Documents* in Appendix A, *Ordering Related Documents*.

Some options, however, are not software-programmable. Such options are controlled through manual installation or removal of header jumpers or interface modules on the MVME230x or the associated modules.

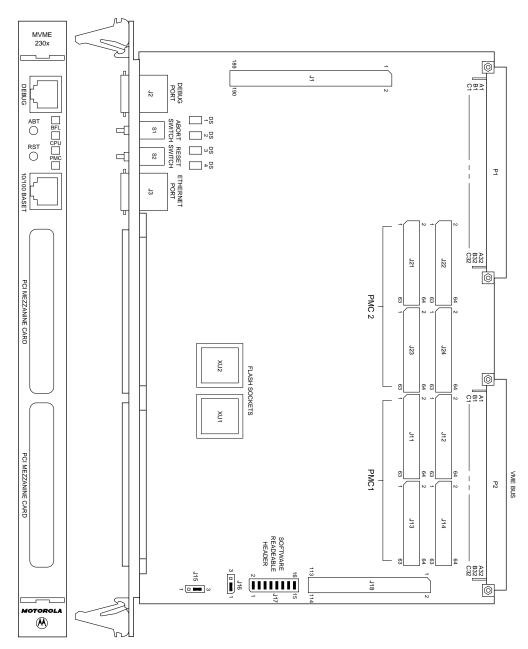

Figure 1-1 illustrates the placement of the switches, jumper headers, connectors, and LED indicators on the MVME230*x*. Manually configurable items on the MVME230*x* include:

- ☐ Flash memory bank A/bank B reset vector (J15)

- □ VMEbus system controller selection header (J16)

- □ General-purpose software-readable header (J17)

The MVME230*x* has been factory tested and is shipped with the configurations described in the following sections. The MVME230*x* factory-installed debug monitor, PPCBug, operates with those factory settings.

Figure 1-1. MVME230x Switches, LEDs, Headers, Connectors

2063 9708

1-9

#### Setting the Flash Memory Bank A/Bank B Reset Vector Header (J15)

Bank B consists of 1 MB of 8-bit Flash memory in two 32-pin PLCC 8-bit sockets.

Bank A consists of four 16-bit Smart Voltage SMT devices that can be populated with 8Mbit Flash devices (4 MB) or 4Mbit Flash devices (2 MB). A jumper header, J15, associated with the first set of four Flash devices provides a total of 64KB of hardware-protected boot block. Only 32-bit writes are supported for this bank of Flash. The address of the reset vector is jumper-selectable. A jumper must be installed either between J15 pins 1 and 2 for Bank A factory configuration, or between J15 pins 2 and 3 for Bank B. When the jumper is installed, the Falcon chipset maps 0xFFF00100 to the Bank B sockets...

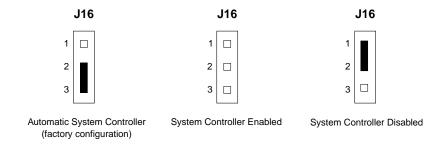

#### Setting the VMEbus System Controller Selection Header (J16)

The MVME230*x* is factory-configured in automatic system controller mode; i.e., a jumper is installed across pins 2 and 3 of header J16. This means that the MVME230*x* determines if it is system controller at system power-up or reset by its position on the bus; if it is in slot 1 on the VME system, it configures itself as the system controller.

Remove the jumper from J16if you intend to operate the MVME230x as system controller in all cases.

Install the jumper across pins 1 and 2 if the MVME230*x* is not to operate as system controller under any circumstances.

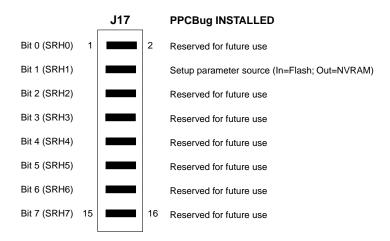

#### Setting the General-Purpose Software-Readable Header (J17)

Header J17 provides eight readable jumpers. These jumpers can be read as a register at ISA I/O address \$801 (hexadecimal). Bit 0 is associated with header pins 1 and 2; bit 7 is associated with pins 15 and 16. The bit values are read as a 0 when the jumper is installed, and as a 1 when the jumper is removed. The MVME230x is shipped from the factory with J17 set to all 0s (jumpers on all pins), as shown in Figure 1-2.

The PowerPC firmware, PPCBug, reserves all bits, SRH0 to SRH7.

With the jumper installed between pins 3 and 4 (factory configuration), the debugger uses the current user setup/operation parameters in Flash. When the jumper is removed (making the bit a 1), the debugger uses the default setup/operation parameters in NVRAM instead. Refer to the ENV command description in Chapter 6 for the NVRAM defaults.

Figure 1-2. General-Purpose Software-Readable Header

#### **PMCs**

For a discussion of any configurable items on the PMCs, refer to the user's manual for the particular PMCs.

## **PMCspan**

You will need to use an additional slot in the VME chassis for each PMCspan expansion module you plan to use. Before installing a PMCspan on the MVME230x, you must install the selected PMCs on the PMCspan. Refer to the PMCspan PMCAdapter Carrier Module Instillation and Use manual for instructions.

## **System Console Terminal**

Ensure that jumpers are installed on all bits on header J17 of the MVME230x board as shown in Figure 1-2. This is necessary when the PPCBug firmware is used. Connect the terminal via a cable to the RJ45 DEBUG connector J2. See Table C-3 for pin signal assignments. Set up the terminal as follows:

- Eight bits per character

- One stop bit per character

- Parity disabled (no parity)

- Baud rate = 9600 baud (default baud rate of the port at power-up); after power-up, you can reconfigure the baud rate with PPCBug's **PF** command

## Installing the MVME230x Hardware

The following paragraphs discuss installing PMCs onto the MVME230*x*, installing PMCspan modules onto the MVME230*x*, installing the MVME230*x* into a VME chassis, and connecting an optional system console terminal.

## **Taking ESD Precautions**

#### **Use ESD**

Wrist Strap

Motorola strongly recommends that you use an antistatic wrist strap and a conductive foam pad when installing or upgrading a system. Electronic components, such as disk drives, computer boards, and memory modules, can be extremely sensitive to Electro-Static Discharge (ESD). After removing the component from the system or its protective wrapper, place the component flat on a grounded, static-free surface (and in the case of a board, component side up). Do not slide the component over any surface.

If an ESD station is not available, you can avoid damage resulting from ESD by wearing an antistatic wrist strap (available at electronics stores) that is attached to an unpainted metal part of the system chassis.

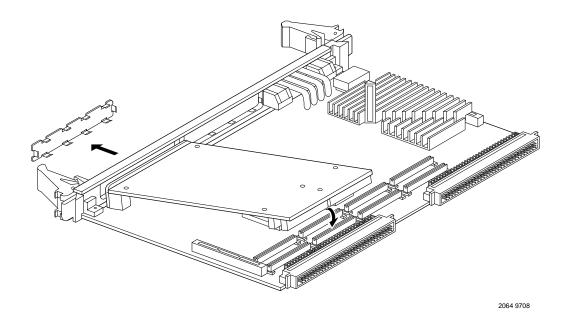

### **PMCs**

PCI mezzanine card (PMC) modules mount on top of the MVME230x module, and/or on a PMCspan. Refer to Figure 1-3 and perform the following steps to install a PMC on your MVME230x module. This procedure assumes that you have read the user's manual that came with your PMCs.

- 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure.

- 2. Perform an operating system shutdown. Turn the AC or DC power off and remove the AC cord or DC power lines from the system. Remove chassis or system cover(s) as necessary for access to the VMEmodules.

Inserting or removing modules with power applied may result in damage to module components.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

3. If the MVME230x has already been installed in a VMEbus card slot, carefully remove it. Lay the MVME230x flat, with connectors P1 and P2 facing you.

Avoid touching areas of integrated circuitry; static discharge can damage these circuits.

4. Remove the PCI filler plate from the selected PMC slot in the front panel of the MVME230x. If installing a double-width PMC, remove the filler plates from both PMC slots.

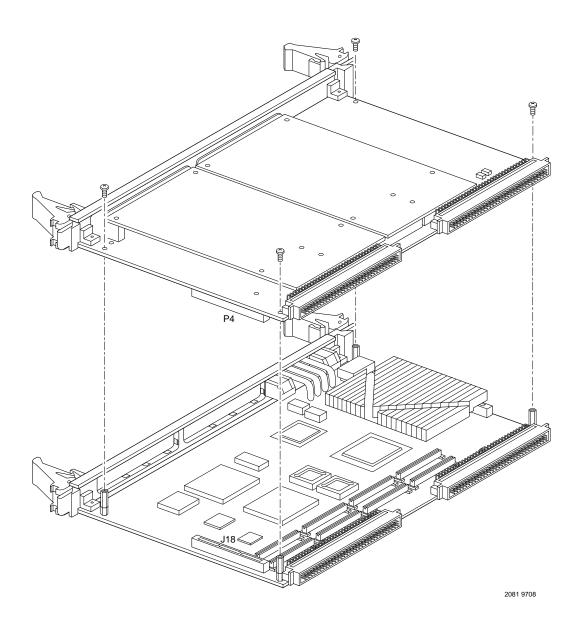

Figure 1-3. Typical Single-width PMC Module Placement on MVME230x

- 5. Slide the edge connector(s) of the PMC module into the front panel opening(s) from behind and place the PMC module on top of the MVME230x. The four connectors on the underside of the PMC module should then connect smoothly with the corresponding connectors for a single-width PMC (J11/J12/J13/J14 or J21/J22/J23/J24, all eight for a double-width PMC) on the MVME230x.

- 6. Insert the two short Phillips screws through the holes at the forward corners of the PMC module, into the standoffs on the MVME230x. Tighten the screws.

- 7. If installing two single-width PMCs, repeat the above procedure for the second PMC.

## **Primary PMCspan**

To install a PMCspan-002 PCI expansion module on your MVME230x, refer to Figure 1-4 and perform the following steps. This procedure assumes that you have read the user's manual that

was furnished with the PMCspan, and that you have installed the selected PMCs on the PMCspan according to the instructions given in the PMCspan and PMC manuals.

- 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground while you are performing the installation procedure.

- 2. Perform an operating system shutdown. Turn the AC or DC power off and remove the AC cord or DC power lines from the system. Remove chassis or system cover(s) as necessary for access to the VME module card cage.

Inserting or removing modules with power applied may result in damage to module components.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

3. If the MVME230x has already been installed in the chassis, carefully remove it from the VMEbus card slot and lay it flat, with connectors P1 and P2 facing you.

Avoid touching areas of integrated circuitry; static discharge can damage these circuits.

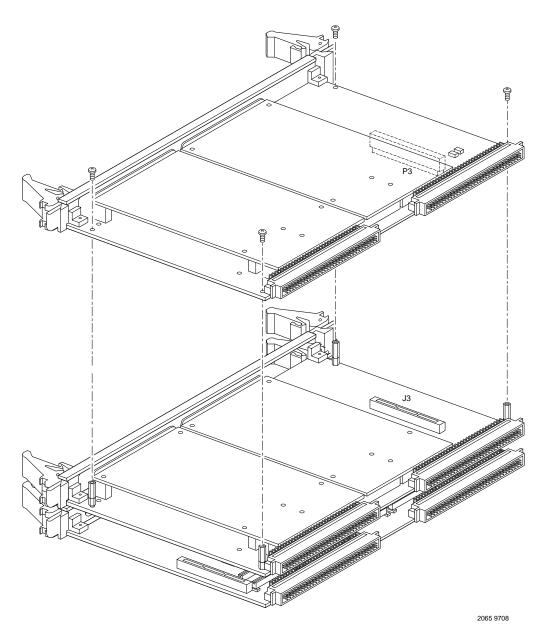

Figure 1-4. PMCspan-002 Installation on an MVME230x

- 4. Attach the four standoffs to the MVME230x module. For each standoff:

- Insert the threaded end into the standoff hole at each corner of the VME processor module.

- Thread the locking nuts onto the standoff tips.

- Tighten the nuts with a box-end wrench or a pair of needle nose pliers.

- 5. Place the PMCspan on top of the MVME230x module. Align the mounting holes in each corner to the standoffs, and align PMCspan connector P4 with MVME230x connector J18.

- 6. Gently press the PMCspan and MVME230x together, making sure that P4 is fully seated into J18.

- 7. Insert the four short Phillips screws through the holes at the corners of the PMCspan and into the standoffs on the MVME230x module. Tighten the screws.

**Note** The screws have two different head diameters. Use the screws with the smaller heads on the standoffs next to VMEbus connectors P1 and P2.

## Secondary PMCspan

The PMCspan-010 PCI expansion module mounts on top of a PMCspan-002 PCI expansion module. To install a PMCspan-010 on your MVME230x, refer to Figure 1-5 and perform the following steps. This procedure assumes that you have read the user's manual that was furnished with the PMCspan, and that you have installed the selected PMCs on the PMCspan according to the instructions given in the PMCspan and PMC manuals.

Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground while you are performing the installation procedure.

Figure 1-5. PMCspan-010 Installation onto a PMCspan-002/MVME230x

2. Perform an operating system shutdown. Turn the AC or DC power off and remove the AC cord or DC power lines from the system. Remove chassis or system cover(s) as necessary for access to the VME module card cage.

Inserting or removing modules with power applied may result in damage to module components.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

3. If the Primary PMC Carrier Module / MVME230x assembly is already installed in the VME chassis, carefully remove the two-board assembly from the VMEbus card slots and lay it flat, with the P1 and P2 connectors facing you.

Avoid touching areas of integrated circuitry; static discharge can damage these circuits.

- 4. Remove the four short Phillips screws from the standoffs in each corner of the primary PCI expansion module, PMCspan-002.

- 5. Attach the four standoffs to the PMCspan-002.

- Place the PMCspan-010 on top of the PMCspan-002. Align the mounting holes in each corner to the standoffs, and align PMCspan-010 connector P3 with PMCspan-002 connector J3.

- 7. Gently press the two PMCspan modules together, making sure that P3 is fully seated in J3.

- 8. Insert the four short Phillips screws through the holes at the corners of PMCspan-010 and into the standoffs on the primary PMCspan-002. Tighten the screws.

**Note** The screws have two different head diameters. Use the screws with the smaller heads on the standoffs next to VMEbus connectors P1 and P2.

### **MVME230***x*

Before installing the MVME230*x* into your VME chassis, ensure that the jumpers on the MVME230*x* J15, J16, and J17 headers are configured, as previously described. This procedure assumes that you have already installed the PMCspan(s) if desired, and any PMCs that you have selected.

Proceed as follows to install the MVME230x in the VME chassis:

- 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure.

- 2. Perform an operating system shutdown:

- a. Turn the AC or DC power off and remove the AC cord or DC power lines from the system.

Inserting or removing modules with power applied may result in damage to module components.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

- b. Remove chassis or system cover(s) as necessary for access to the VMEmodules.

- 3. Remove the filler panel from the card slot where you are going to install the MVME230x. If you have installed one or more PMCspan PCI expansion modules onto your MVME230x, you will need to remove filler panels from one additional card slot for each PMCspan, above the card slot for the MVME230x.

- If you intend to use the MVME230x as system controller, it must occupy the leftmost card slot (slot 1). The system controller must be in slot 1 to correctly initiate the busgrant daisy-chain and to ensure proper operation of the IACK daisy-chain driver.

- If you do not intend to use the MVME230x as system controller, it can occupy any unused card slot.

Avoid touching areas of integrated circuitry; static discharge can damage these circuits.

- 4. Slide the MVME230*x* (and PMCspans if used) into the selected card slot(s). Be sure the module or modules is/are seated properly in the P1 and P2 connectors on the backplane. Do not damage or bend connector pins.

- 5. Secure the MVME230*x* (and PMCspans if used) in the chassis with the screws provided, making good contact with the transverse mounting rails to minimize RF emissions.

Note Some VME backplanes (e.g., those used in Motorola "Modular Chassis" systems) have an auto-jumpering feature for automatic propagation of the IACK and BG signals. Step 6 does not apply to such backplane designs.

- 6. On the chassis backplane, remove the INTERRUPT ACKNOWLEDGE (IACK) and BUS GRANT (BG) jumpers from the header for the card slot occupied by the MVME230x.

- 7. If you intend to use PPCBug interactively, connect the terminal that is to be used as the PPCBug system console to the DEBUG port on the front panel of the MVME230x.

In normal operation the host CPU controls MVME230x operation via the VMEbus Universe registers.

- 8. Replace the chassis or system cover(s), cable peripherals to the panel connectors as appropriate, reconnect the system to the AC or DC power source, and turn the equipment power on.

- 9. The MVME230x's green **CPU** LED indicates activity as a set of confidence tests is run, and the debugger prompt PPC1-Bug> appears.

### **Installation Considerations**

The MVME230*x* draws power from the VMEbus backplane connectors P1 and P2. P2 is also used for the upper 16 bits of data in 32-bit transfers, and for the upper 8 address lines in extended addressing mode. The MVME230*x* may not function properly without its main board connected to VMEbus backplane connectors P1 and P2.

Whether the MVME230x operates as a VMEbus master or as a VMEbus slave, it is configured for 32 bits of address and 32 bits of data (A32/D32). However, it handles A16 or A24 devices in the address ranges indicated in Chapter 4. D8 and/or D16 devices in the system must be handled by the PowerPC processor software. Refer to the memory maps in Chapter 4.

The MVME230x contains shared onboard DRAM whose base address is software-selectable. Both the onboard processor and off-board VMEbus devices see this local DRAM at base physical address \$00000000, as programmed by the PPCBug firmware. This may be changed via software to any other base address. Refer to the MVME230x programmer's reference guide for more information.

If the MVME230x tries to access off-board resources in a nonexistent location and is not system controller, and if the system does not have a global bus timeout, the MVME230x waits forever for the VMEbus cycle to complete. This will cause the system to lock up. There is only one situation in which the system might lack this global bus timeout: when the MVME230x is not the system controller and there is no global bus timeout elsewhere in the system.

Multiple MVME230x boards may be installed in a single VME chassis. Each must have a unique Universe address, selected by setting jumpers on its J17 header, as described in *Preparing the MVME230x*. In general, hardware multiprocessor features are supported.

Other MPUs on the VMEbus can interrupt, disable, communicate with, and determine the operational status of the processor(s). One register of the Universe set includes four bits that function as location monitors to allow one MVME230x processor to broadcast a signal to any other MVME230x processors. All eight registers are accessible from any local processor as well as from the VMEbus.

# Introduction

This chapter provides information about powering up the MVME230x system, and functionality of the switches, status indicators, and I/O ports on the front panels of the MVME230x and PMCspan modules.

# **Applying Power**

After you have verified that all necessary hardware preparation has been done, that all connections have been made correctly, and that the installation is complete, you can power up the system. The MPU, hardware, and firmware initialization process is performed by the PPCBug firmware power-up or system reset. The firmware initializes the devices on the MVME230x module in preparation for booting the operating system.

The firmware is shipped from the factory with an appropriate set of defaults. In most cases there is no need to modify the firmware configuration before you boot the operating system. Refer to Chapter 6 for further information about modifying defaults.

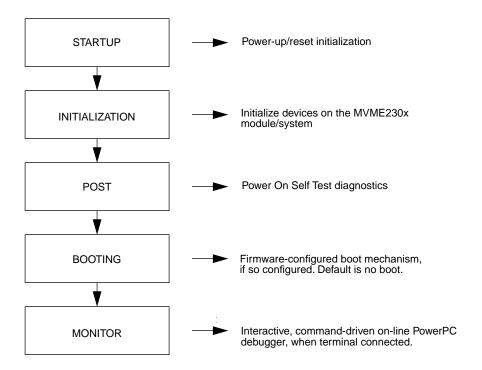

The following flowchart shows the basic initialization process that takes place during MVME230x system start-ups.

For further information on PPCbug, refer to Chapter 5, *PPCBug*; to Appendix D, *Troubleshooting the MVME230x*; or to the PPCBug documentation listed in Appendix A.

# MVME230x

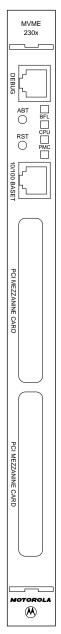

The front panel of the MVME230x module is shown on a following page.

### **Switches**

There are two switches (**ABT** and **RST**) and four LED (light-emitting diode) status indicators (**BFL**, **CPU**, **PMC** (two)) located on the MVME230x front panel.

### **ABT (S1)**

When activated by software, the Abort switch, ABT, can generate an interrupt signal from the base board to the processor at a user-programmable level. The interrupt is normally used to abort program execution and return control to the debugger firmware located in the MVME230x Flash memory. The interrupt signal reaches the processor module via ISA bus interrupt line IRQ8\*. The signal is also available from the general purpose I/O port, which allows software to poll the Abort switch after an IRQ8\* interrupt and verify that it has been pressed.

The interrupter connected to the **ABT** switch is an edge-sensitive circuit, filtered to remove switch bounce.

### **RST (S2)**

The Reset switch, **RST**, resets all onboard devices and causes HRESET\* to be asserted in the MPC603 or MPC604. It also drives a SYSRESET\* signal if the MVME230x VME processor module is the system controller.

The Universe ASIC includes both a global and a local reset driver. When the Universe operates as the VMEbus system controller, the reset driver provides a global system reset by asserting the VMEbus signal SYSRESET\*. A SYSRESET\* signal may be generated by the RESET switch, a power-up reset, a watchdog timeout, or by a control bit in the Miscellaneous Control Register (MISC\_CTL) in the Universe ASIC. SYSRESET\* remains asserted for at least 200 ms, as required by the VMEbus specification.

Similarly, the Universe ASIC supplies an input signal and a control bit to initiate a local reset operation. By setting a control bit, software can maintain a board in a reset state, disabling a faulty board from participating in normal system operation. The local reset driver is enabled even when the Universe ASIC is not system controller. Local resets may be generated by the RST switch, a power-up reset, a watchdog timeout, a VMEbus SYSRESET\*, or a control bit in the MISC\_CTL register.

2

### **Status Indicators**

There are four LED (light-emitting diode) status indicators located on the MVME230x front panel.: **BFL, CPU, PMC2,** and **PMC1**.

### BFL (DS1)

The *yellow* **BFL** LED indicates board failure; lights when the BRDFAIL\* signal line is active.

### CPU (DS2)

The *green* **CPU** LED indicates CPU activity; lights when the DBB\* (Data Bus Busy) signal line on the processor bus is active.

### PMC (DS3)

The top *green* **PMC** LED indicates PCI activity; lights when the PCI bus grant to PMC2 signal line on the PCI bus is active. This indicates that a PMC installed on slot 2 is active.

## PMC (DS4)

The bottom *green* **PMC** LED indicates PCI activity; lights when the PCI bus grant to PMC1 signal line on the PCI bus is active. This indicates that a PMC installed on slot 1 is active.

### 10/100 BASET Port

The RJ45 port on the front panel of the MVME230x labeled **10/100 BASET** supplies the Ethernet LAN 10BaseT/100Base TX interface, implemented with a DEC 21140/21143 device.

### **DEBUG Port**

The RJ45 port labeled **DEBUG** on the front panel of the MVME230x supplies the MVME230x serial communications interface, implemented via a UART PC16550 controller chip from National Semiconductor. It is asynchronous only. This serial port is configured for EIA-232-D DTE, as shown in Figure 2-1.

The **DEBUG** port may be used for connecting a terminal to the MVME230x to serve as the firmware console for the factory installed debugger, PPCBug. The port is configured as follows:

- □ 8 bits per character

- □ 1 stop bit per character

- □ Parity disabled (no parity)

- ☐ Baud rate = 9600 baud (default baud rate at power-up)

After power-up, the baud rate of the **DEBUG** port can be reconfigured by using the debugger's Port Format (**PF**) command. Refer to Chapters 5 and 6 for information about PPCBug.

Figure 2-1. MVME230x DEBUG Port Configuration

### **PMC Slots**

Two openings located on the front panel provide I/O expansion by allowing access to one or two 4-port single-wide or one 8-port double-wide PCI Mezzanine Card (PMC), connected to the PMC connectors on the MVME230x. For pin assignments for the PMC connectors, refer to Appendix C.

Do not attempt to install any PMC boards without performing an operating system shutdown and following the procedures given in the user's manual for the particular PMC.

### **PCI MEZZANINE CARD (PMC Slot 1)**

The right-most (lower) opening labeled **PCI MEZZANINE CARD** on the MVME230x front panel provides front panel I/O access to a PMC that is connected to the 64-pin connectors J11 through J14 on the MVME230x module. Connector J14 allows rear panel P2 I/O.

This slot is MVME230x Port 1.

### PCI MEZZANINE CARD (PMC Slot 2)

The left-most (upper)opening labeled **PCI MEZZANINE CARD** on the MVME230x front panel provides front panel I/O access to a PMC that is connected to the 64-pin connectors J21 through J24 on the MVME230x module. Connector J24 allows rear panel P2 I/O.

This slot is MVME230x Port 2.

# **PMCspan**

A PMCspan front panel is pictured at the right. The front panel is the same for all PMCspan models.

There are two PMC slots, labeled PCI MEZZANINE CARD, which support either two single-wide PMCs or one double-wide PMC.

The PMCspan board has two sets of three 32-bit connectors for PMC interface to secondary PCI bus and user-specific I/O. It also has a P1 connector and a 5-row P2 connector for power and VMEbus I/O.

The PMCspan has two green LEDs on its front panel, one for each PMC slot, labeled PMC2 and PMC1. Both LEDs are illuminated during reset. An individual LED is illuminated whenever a PMC has been granted bus mastership of the secondary PCI bus.

The right-most (lower) opening labeled **PCI MEZZANINE CARD** on the front panel is Port 1.

The left-most (upper)opening labeled **PCI MEZZANINE CARD** on the front panel is Port 2.

2

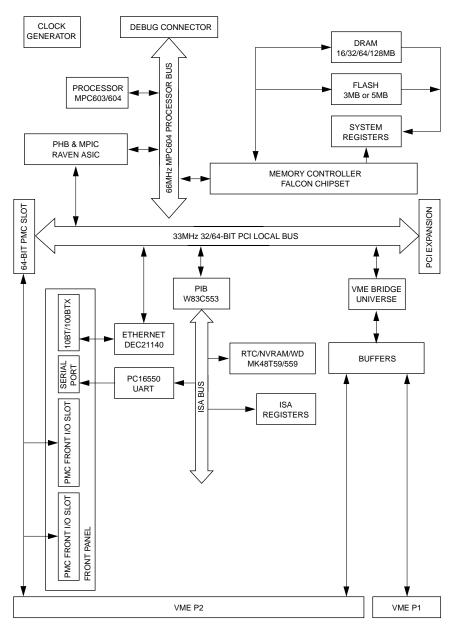

# Introduction

This chapter describes the MVME230x VME processor module on a block diagram level. The *General Description* provides an overview of the MVME230x, followed by a detailed description of several blocks of circuitry. Figure 3-1 shows a block diagram of the overall board architecture.

Detailed descriptions of other MVME230x blocks, including programmable registers in the ASICs and peripheral chips, can be found in the *MVME2300-Series VME Processor Module Programmer's Reference Guide* (part number V2300A/PG). Refer to it for a functional description of the MVME230x in greater depth.

# **Features**

The following table summarizes the features of the MVME230x VME processor module.

Table 3-1. MVME230x Features

| Feature        | Description                                                                                                                     |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| Microprocessor | 200 MHZ MPC603 PowerPC <sup>TM</sup> processor<br>(MVME2301 - 2304 models)                                                      |  |  |

| Wheroprocessor | 300 MHZ MPC604 PowerPC <sup>TM</sup> processor<br>(MVME2305 - 2308 models)                                                      |  |  |

| Form factor    | 6U VMEbus                                                                                                                       |  |  |

| ECC DRAM       | Two-way interleaved, ECC-protected 16MB, 32MB, 64MB, or 128MB                                                                   |  |  |

| Flash memory   | Bank B consists of two 32-pin PLCC sockets that can be populated with 1MB 8-bit Flash devices                                   |  |  |

| Trasit memory  | Bank A consists of four 16-bit Smart Voltage SMT devices that can<br>be populated with 8Mbit Flash devices (4MB) or 4Mbit (2MB) |  |  |

Table 3-1. MVME230x Features (Continued)

| Feature          | Description                                                                                     |  |  |

|------------------|-------------------------------------------------------------------------------------------------|--|--|

| Real-time clock  | 8KB NVRAM with RTC and battery backup (SGS-Thomson M48T59/T559)                                 |  |  |

| Switches         | Reset (RST) and abort (ABT)                                                                     |  |  |

| Status LEDs      | Four: Board fail (BFL), CPU, PMC (one for PMC slot 2, one for slot 1)                           |  |  |

| Timers           | One 16-bit timer in W83C553 ISA bridge; four 32-bit timers in Raven (MPIC) device)              |  |  |

|                  | Watchdog timer provided in SGS-Thomson M48T59                                                   |  |  |

| Interrupts       | Software interrupt handling via Raven (PCI-MPU bridge) and Winbond (PCI-ISA bridge) controllers |  |  |

| VME I/O          | VMEbus P2 connector                                                                             |  |  |

| Serial I/O       | One asynchronous debug port via RJ45 connector on front panel                                   |  |  |

| Ethernet I/O     | 10Base-T/100Base-TX connections via RJ45 connector on front panel                               |  |  |

|                  | Two IEEE P1386.1 PCI Mezzanine Card (PMC) slots for one double-width or two single-width PMCs   |  |  |

| PCI interface    | Front panel and/or VMEbus P2 I/O on both PMC slots                                              |  |  |

|                  | One 114-pin Mictor connector for optional PMCspan expansion module                              |  |  |

|                  | VMEbus system controller functions                                                              |  |  |

|                  | VME64 extension                                                                                 |  |  |

|                  | VMEbus-to-local-bus interface (A24/A32, D8/D16/D32/block transfer [D8/D16/D32/D64])             |  |  |

| VMEbus interface | Local-bus-to-VMEbus interface (A16/A24/A32, D8/D16/D32)                                         |  |  |

|                  | VMEbus interrupter                                                                              |  |  |

|                  | VMEbus interrupt handler                                                                        |  |  |

|                  | Global Control/Status Register (GCSR) for interprocessor communications                         |  |  |

|                  | DMA for fast local memory/VMEbus transfers (A16/A24/A32, D16/D32/D64)                           |  |  |

# **General Description**

The MVME230x is a VME processor module equipped with a PowerPC<sup>TM</sup> 603 or 604 microprocessor.

As shown in the *Features* section, the MVME230x offers many standard features desirable in a computer system—including Ethernet and debug ports, Boot ROM, Flash memory, DRAM, and interface for two PCI Mezzanine Cards (PMCs), contained in a one-slot VME package. Its flexible mezzanine architecture allows relatively easy upgrades of the I/O.

There are four standard buses on the MVME230x:

PowerPC Processor Bus ISA Bus PCI Local Bus VMEbus

As shown in Figure 3-1, a Raven PCI Bridge ASIC provides the interface from the Processor Bus to PCI. A W83C553 PCI/ISA Bridge (PIB) Controller device performs the bridge function between PCI and ISA. The Universe ASIC device provides the interface between the PCI Local Bus and the VMEbus. A Falcon chipset is the ECC memory controller.

The Peripheral Component Interface (PCI) local bus is a key feature. In addition to the on-board local bus peripherals, the PCI bus supports an industry-standard mezzanine interface, IEEE P1386.1 PMC (PCI Mezzanine Card).

# **Block Diagram**

Figure 3-1 is a block diagram of the MVME2300's overall architecture.

### MPC603/604 Processor

The MVME230x can be ordered with a PowerPC 603 or a PowerPC 604 processor chip with 16MB to 128MB of ECC DRAM, and up to 5MB of Flash memory.

2067 9708

Figure 3-1. MVME230x Block Diagram

The PowerPC 603 is a 64-bit processor with 16KB on-chip caches (16KB data cache and 16KB instruction cache). The PowerPC 604 is a 64-bit processor with 32 KB on-chip caches (32KB data cache and 32KB instruction cache).

The Raven bridge controller ASIC provides the bridge between the PowerPC microprocessor bus and the PCI local bus. Electrically, the Raven chip is a 64-bit PCI connection. Four programmable map decoders in each direction provide flexible addressing between the PowerPC microprocessor bus and the PCI local bus.

The power requirements for the MVME230x are shown in Table 3-2.

Configuration+5V Power+12V and -12V Power200MHz 6034.0A typical<br/>4.75A maximumPMC-dependent<br/>(Refer to Appendix B)300MHz 6044.5A typical<br/>5.5A maximum

**Table 3-2. Power Requirements**

### **PCI Bus Latency**

Writes to PCI can be posted. The read access latency for PCI-bound cycles initialted by the MPMC60x bus master consists of the following components:

| T <sub>start</sub> | Start-up time (TS# to PCI bus Request). <b>T</b> <sub>start</sub> is 6 system clocks. |

|--------------------|---------------------------------------------------------------------------------------|

| T <sub>arb</sub>   | PCI bus arbitration time                                                              |

| T <sub>ac</sub>    | PCI access time (FRAME# to TRDY#)                                                     |

| $T_{delay}$        | Delay time from TRDY# on PCI to TA# on 60X bus. $T_{delay}$ is 4 system clocks.       |

The following table shows the access timings for various types of transfers initiated by a 60X system bus master to PCI:

Table 3-3. PowerPC 60x Bus to PCI Access Timing

| Access Type                            | System Clock Periods Required For: |          |          |          | Total  |

|----------------------------------------|------------------------------------|----------|----------|----------|--------|

| Access Type                            | 1st Beat                           | 2nd Beat | 3rd Beat | 4th Beat | Clocks |

| 4-Beat Read (64-bit PCI<br>Target)     | 27                                 | 1        | 1        | 1        | 30     |

| 4-Beat Read (32-bit PCI<br>Target)     | 35                                 | 1        | 1        | 1        | 38     |

| 4-Beat Write (64-bit PCI<br>Target)    | 4                                  | 1        | 1        | 1        | 7      |

| 4-Beat Write (32-bit PCI<br>Target)    | 4                                  | 1        | 1        | 1        | 7      |

| 1-Beat Read (aligned, 4 bytes or less) | 20                                 | -        | -        | -        | 20     |

| 1-Beat Write                           | 4                                  | -        | -        | -        | 4      |

- **Notes** 1. Write cycles are posted by the Raven ASIC.

- 2. Assumes no pipeline. Pipelined cycles would improve these numbers.

- 3.  $T_{arb}$  is assumed to be 4 system clocks (2 PCI clocks).

- 4. T<sub>ac</sub> is assumed to be 6 system clocks (3 PCI clocks): Medium DEVSEL# target, zero wait PCI timing.

The following table shows the ECC memory access latency for PCIinitiated cycles.

PCI Clock Periods Required for: Maximum **Access Type** Bandwidth 3rd Beat 1st Beat 2nd Beat nth Beat 64-bit Burst Reads 10 1 1 1 64-bit Burst Writes 3 1 1 1 32-bit Burst Reads 10 1 1 1 32-bit Burst Writes 3 1 1 1 1-Beat Read 10 1-Beat Write 3

Table 3-4. PCI to ECC Memory Access Timing

- **Notes** 1. The latency assumes two system clocks for 60X system bus arbitration.

- 2. The latency is based on 60ns, fast-page DRAM timing. It is also assumed that L2 is either disabled or missed.

- 3. Write timings assume write posting FIFO is initially empty.

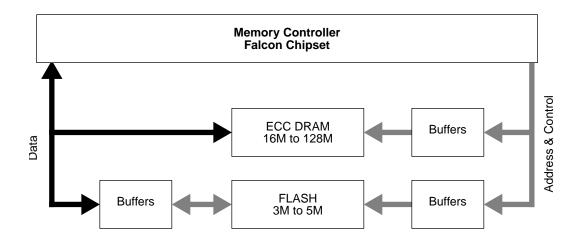

# **DRAM Memory**

The MVME2300 DRAM memory size can be 16MB, 32MB, 64MB, or 128MB.

The DRAM blocks are controlled by the Falcon chipset which performs two-way interleaving and provides single-bit error correction and double-bit error correction. ECC is calculated over 72-bits.

3

There are one or two blocks of DRAMs that provides 16M/32M or 64M/128M of ECC DRAM. The DRAM blocks consists of 9 devices each. Either 1Mx16 (Page) 50-pin TSOPII DRAM or 4Mx16 (EDO) 50-pin TSOPII DRAM are used to provide 16/32/64/128M. When populated, these blocks appears as Block A and Block B to the Falcon chipset.

Refer to the *MVME2300-Series VME Processor Module Programmer's Reference Guide* for additional information and programming details.

The block diagram for the memory interface is shown in the following figure:

Figure 3-2. Memory Block Diagram

### **DRAM Latency**

The ECC memory access latency times for 60ns, fast page DRAMs are shown in the following table.

Table 3-5. PowerPC 60x Bus to DRAM Access Timing using 60ns Page **Devices**

| A seess Tyres                                          | Clock Periods Required for: |          |          |          | Total  |

|--------------------------------------------------------|-----------------------------|----------|----------|----------|--------|

| Access Type                                            | 1st Beat                    | 2nd Beat | 3rd Beat | 4th Beat | Clocks |

| 4-Beat Read after Idle<br>(Quad-word aligned)          | 9                           | 1        | 2        | 1        | 13     |

| 4-Beat Read after Idle<br>(Quad-word misaligned)       | 9                           | 3        | 1        | 1        | 14     |

| 4-Beat Read after 4-Beat Read (Quad-word aligned)      | 7/3 1                       | 1        | 2        | 1        | 11/7   |

| 4-Beat Read after 4-Beat Read (misaligned)             | 6/21                        | 3        | 1        | 1        | 11/7   |

| 4-Beat Write after Idle                                | 4                           | 1        | 1        | 1        | 7      |

| 4-Beat Write after 4-Beat<br>Write (Quad-word aligned) | 7/3 1                       | 1        | 1        | 1        | 10/6   |

| 1-Beat Read after Idle                                 | 9                           | -        | -        | -        | 9      |

| 1-Beat Read after 1-Beat Read                          | 8/61                        | -        | -        | -        | 8/6    |

| 1-Beat Write after Idle                                | 4                           | -        | -        | -        | 4      |

| 1-Beat Write after 1-Beat<br>Write                     | 12/10                       | -        | -        | -        | 12/10  |

- **Notes** 1. These numbers assume that the PowerPC 60x bus master is doing address pipelining with TS\* occurring at the minimum time after AACK\* is asserted. Also the two numbers shown in the 1st beat column are for page miss/page hit.

- 2. In some cases, the numbers shown are averages and specific instances may be longer or shorter.

If all blocks of DRAMs are 50ns, EDO devices then the latency times for the ECC memory would be as follows:

Table 3-6. PowerPC 60x Bus to DRAM Access Timing Using 50ns, EDO **Devices**