# MVME162 Embedded Controller User's Manual

(MVME162/D2)

#### Notice

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

No part of this material may be reproduced or copied in any tangible medium, or stored in a retrieval system, or transmitted in any form, or by any means, radio, electronic, mechanical, photocopying, recording or facsimile, or otherwise, without the prior written permission of Motorola, Inc.

It is possible that this publication may contain reference to, or information about Motorola products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

#### **Restricted Rights Legend**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282

#### **Preface**

The *MVME162 User's Manual* provides general information, hardware preparation and installation instructions, operating instructions, and a functional description for the MVME162 Embedded Controller.

This manual is intended for anyone who wants to design OEM systems, supply additional capability to an existing compatible system, or work in a lab environment for experimental purposes.

A basic knowledge of computers and digital logic is assumed.

To use this manual, you should be familiar with the publications listed in the *Related Documentation* section in Chapter 1 of this manual.

The computer programs stored in the Read Only Memory of this device contain material copyrighted by Motorola Inc., first published 1990, and may be used only under a license such as the License for Computer Programs (Article 14) contained in Motorola's Terms and Conditions of Sale, Rev. 1/79.

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the documentation for this product, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A Computing Device pursuant to Subpart J of Part 15 of FCC rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user, at the user's own expense, will be required to take whatever measures necessary to correct the interference.

Motorola<sup>®</sup> and the Motorola symbol are registered trademarks of Motorola, Inc.

Delta Series™, MC68040™, VMEmodule™, VMEsystem™, VMEexec™, and 162Bug™ are trademarks of Motorola, Inc.

$IndustryPack^{\scriptscriptstyle{TM}}$  and  $IP^{\scriptscriptstyle{TM}}$  are trademarks of GreenSpring Computers, Inc.

$\label{topological} \mbox{Timekeeper}^{\mbox{\tiny TM}} \mbox{ and Zeropower}^{\mbox{\tiny TM}} \mbox{ are trademarks of Thompson Components.}$

All other products mentioned in this document are trademarks or registered trademarks of their respective holders.

© Copyright Motorola 1993, 1994

All Rights Reserved

Printed in the United States of America

July 1994

## Safety Summary Safety Depends On You

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the equipment. Motorola, Inc. assumes no liability for the customer's failure to comply with these requirements.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. The equipment is supplied with a three-conductor AC power cable. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter, with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards.

#### Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment constitutes a definite safety hazard.

#### **Keep Away From Live Circuits.**

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified maintenance personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### Do Not Service or Adjust Alone.

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### Use Caution When Exposing or Handling the CRT.

Breakage of the Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, avoid rough handling or jarring of the equipment. Handling of the CRT should be done only by qualified maintenance personnel using approved safety mask and gloves.

#### Do Not Substitute Parts or Modify Equipment.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that safety features are maintained.

#### **Dangerous Procedure Warnings.**

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

# **Contents**

#### **CHAPTER 1 GENERAL INFORMATION**

| Introduction1-1                                              |   |

|--------------------------------------------------------------|---|

| Models1-1                                                    |   |

| Features1-2                                                  | ) |

| Specifications1-3                                            | j |

| Cooling Requirements1-4                                      | į |

| Special Considerations for Elevated Temperature Operation1-4 |   |

| FCC Compliance1-5                                            | , |

| General Description1-6                                       |   |

| Input/Output1-6                                              | j |

| VMEbus Interface1-7                                          |   |

| No-VMEbus-Interface Option1-7                                | 1 |

| MCchip1-7                                                    | 1 |

| Flash Memory and EPROM1-7                                    |   |

| IndustryPack Modules1-8                                      |   |

| Optional SCSI Interface1-8                                   |   |

| Optional LAN Ethernet Transceiver Interface1-8               | ; |

| Required Equipment1-8                                        | í |

| MVME162Bug Firmware1-8                                       | ) |

| MVME712 Series Transition Modules1-9                         | ) |

| Available Software1-9                                        | ) |

| Related Documentation1-10                                    | ) |

| Support Information1-11                                      |   |

| Manual Terminology1-12                                       | ) |

#

| Unpacking Instructions                                                                                                                                                                                                                                                                                                                             | 2-1                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Hardware Preparation                                                                                                                                                                                                                                                                                                                               | 2-1                                                    |

| SIM Selection                                                                                                                                                                                                                                                                                                                                      | 2-2                                                    |

| Removal of Existing SIM                                                                                                                                                                                                                                                                                                                            | 2-4                                                    |

| Installation of New SIM                                                                                                                                                                                                                                                                                                                            | 2-5                                                    |

| System Controller Select Header (J1)                                                                                                                                                                                                                                                                                                               | 2-5                                                    |

| Synchronous Clock Select Header (J11) for Serial Port 1/Console                                                                                                                                                                                                                                                                                    | 2-6                                                    |

| Clock Select Header (J12) for Serial Port 2                                                                                                                                                                                                                                                                                                        |                                                        |

| SRAM Battery Backup Source Select Header (J20)                                                                                                                                                                                                                                                                                                     |                                                        |

| EPROM Size Select Header (J21)                                                                                                                                                                                                                                                                                                                     |                                                        |

| General-Purpose Readable Jumpers Header (J22)                                                                                                                                                                                                                                                                                                      | 2-8                                                    |

| Installation Instructions                                                                                                                                                                                                                                                                                                                          |                                                        |

| IP Installation on the MVME162                                                                                                                                                                                                                                                                                                                     | 2-9                                                    |

| MVME162 Module Installation                                                                                                                                                                                                                                                                                                                        | 2-10                                                   |

| System Considerations                                                                                                                                                                                                                                                                                                                              | 2-12                                                   |

|                                                                                                                                                                                                                                                                                                                                                    |                                                        |

| CHAPTER 3 OPERATING INSTRUCTIONS                                                                                                                                                                                                                                                                                                                   |                                                        |

|                                                                                                                                                                                                                                                                                                                                                    |                                                        |

| Introduction                                                                                                                                                                                                                                                                                                                                       | 3-1                                                    |

|                                                                                                                                                                                                                                                                                                                                                    |                                                        |

| Introduction                                                                                                                                                                                                                                                                                                                                       | 3-1                                                    |

| Introduction                                                                                                                                                                                                                                                                                                                                       | 3-1<br>3-1                                             |

| Introduction                                                                                                                                                                                                                                                                                                                                       | 3-1<br>3-1<br>3-1                                      |

| Introduction                                                                                                                                                                                                                                                                                                                                       | 3-1<br>3-1<br>3-2                                      |

| Introduction                                                                                                                                                                                                                                                                                                                                       | 3-1<br>3-1<br>3-1<br>3-2<br>3-3                        |

| Introduction                                                                                                                                                                                                                                                                                                                                       | 3-1<br>3-1<br>3-1<br>3-2<br>3-3                        |

| Introduction Switches and LEDs ABORT Switch (S1) RESET Switch (S2) Front Panel Indicators (DS1 - DS4) Memory Maps Local Bus Memory Map                                                                                                                                                                                                             | 3-1<br>3-1<br>3-2<br>3-3<br>3-3                        |

| Introduction Switches and LEDs ABORT Switch (S1) RESET Switch (S2) Front Panel Indicators (DS1 - DS4) Memory Maps Local Bus Memory Map Normal Address Range                                                                                                                                                                                        | 3-1<br>3-1<br>3-2<br>3-3<br>3-3<br>3-3                 |

| Introduction Switches and LEDs ABORT Switch (S1) RESET Switch (S2) Front Panel Indicators (DS1 - DS4) Memory Maps Local Bus Memory Map Normal Address Range Detailed I/O Memory Maps IPIC Overall Memory Map BBRAM, TOD Clock Memory Map                                                                                                           | 3-1<br>3-1<br>3-2<br>3-3<br>3-3<br>3-7<br>3-17<br>3-21 |

| Introduction Switches and LEDs ABORT Switch (S1) RESET Switch (S2) Front Panel Indicators (DS1 - DS4) Memory Maps Local Bus Memory Map Normal Address Range Detailed I/O Memory Maps IPIC Overall Memory Map                                                                                                                                       | 3-1<br>3-1<br>3-2<br>3-3<br>3-3<br>3-7<br>3-17<br>3-21 |

| Introduction Switches and LEDs ABORT Switch (S1) RESET Switch (S2) Front Panel Indicators (DS1 - DS4) Memory Maps Local Bus Memory Map Normal Address Range Detailed I/O Memory Maps IPIC Overall Memory Map BBRAM, TOD Clock Memory Map Interrupt Acknowledge Map VMEbus Memory Map                                                               | 3-13-13-23-33-33-73-173-213-24                         |

| Introduction Switches and LEDs ABORT Switch (S1) RESET Switch (S2) Front Panel Indicators (DS1 - DS4) Memory Maps Local Bus Memory Map Normal Address Range Detailed I/O Memory Maps IPIC Overall Memory Map BBRAM, TOD Clock Memory Map Interrupt Acknowledge Map VMEbus Memory Map VMEbus Accesses to the Local Bus                              | 3-13-13-23-33-33-73-173-213-243-24                     |

| Introduction Switches and LEDs ABORT Switch (S1) RESET Switch (S2) Front Panel Indicators (DS1 - DS4) Memory Maps Local Bus Memory Map Normal Address Range Detailed I/O Memory Maps IPIC Overall Memory Map BBRAM, TOD Clock Memory Map Interrupt Acknowledge Map VMEbus Memory Map VMEbus Accesses to the Local Bus VMEbus Short I/O Memory Map. | 3-13-13-23-33-33-73-173-213-243-24                     |

| Introduction Switches and LEDs ABORT Switch (S1) RESET Switch (S2) Front Panel Indicators (DS1 - DS4) Memory Maps Local Bus Memory Map Normal Address Range Detailed I/O Memory Maps IPIC Overall Memory Map BBRAM, TOD Clock Memory Map Interrupt Acknowledge Map VMEbus Memory Map VMEbus Accesses to the Local Bus                              | 3-13-13-23-33-33-73-173-213-243-24                     |

| Introduction Switches and LEDs ABORT Switch (S1) RESET Switch (S2) Front Panel Indicators (DS1 - DS4) Memory Maps Local Bus Memory Map Normal Address Range Detailed I/O Memory Maps IPIC Overall Memory Map BBRAM, TOD Clock Memory Map Interrupt Acknowledge Map VMEbus Memory Map VMEbus Accesses to the Local Bus VMEbus Short I/O Memory Map. | 3-13-13-23-33-33-73-173-213-243-243-243-243-24         |

#### **CHAPTER 4 FUNCTIONAL DESCRIPTION**

| Introduction                              | 4-1  |

|-------------------------------------------|------|

| MVME162 Functional Description            | 4-1  |

| Data Bus Structure                        | 4-1  |

| MC68040/MC68LC040 MPU                     | 4-2  |

| EPROM and Flash Memory                    | 4-2  |

| SRAM                                      |      |

| About the Battery                         | 4-3  |

| Onboard DRAM                              |      |

| Battery Backed Up RAM and Clock           | 4-5  |

| VMEbus Interface and VMEchip2             |      |

| I/O Interfaces                            |      |

| Serial Communications Interface           |      |

| IndustryPack (IP) Interfaces              |      |

| Ethernet Interface                        |      |

| SCSI Interface                            |      |

| SCSI Termination                          |      |

| Local Resources                           |      |

| Programmable Tick Timers                  |      |

| Watchdog Timer                            |      |

| Software-Programmable Hardware Interrupts |      |

| Local Bus Timeout                         |      |

| Timing Performance                        |      |

| Local Bus to DRAM Cycle Times             |      |

| EPROM/Flash Cycle Times                   |      |

| SCSI Transfers                            |      |

| LAN DMA Transfers                         |      |

| Remote Status and Control                 | 4-12 |

|                                           |      |

| APPENDIX A SERIAL INTERCONNECTIONS        |      |

| Introduction                              | A-1  |

| EIA-232-D Connections                     | A-1  |

| Interface Characteristics                 | A-3  |

| EIA-530 Connections                       |      |

| Interface Characteristics                 |      |

| Proper Grounding                          |      |

| 1                                         |      |

# **List of Figures**

| Figure 2-1. MVME162 Switch, Header, Connector, Fuse,      |      |

|-----------------------------------------------------------|------|

| and LED Locations                                         | 2-3  |

| Figure 2-2. Serial Interface Module, Connector Side       | 2-4  |

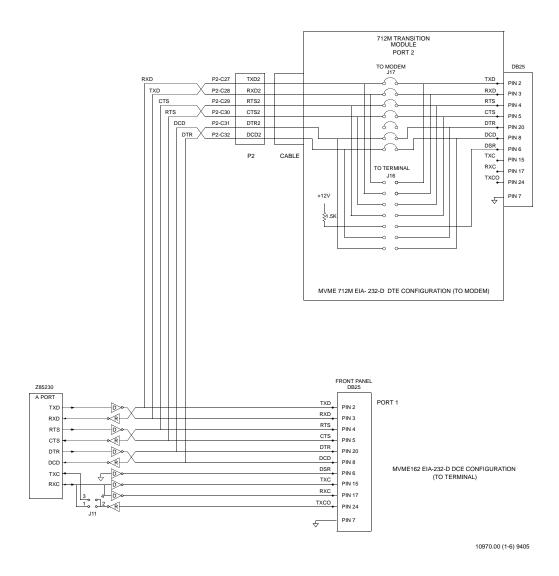

| Figure 2-3. MVME162/MVME712M EIA-232-D Connection Diagram | 2-14 |

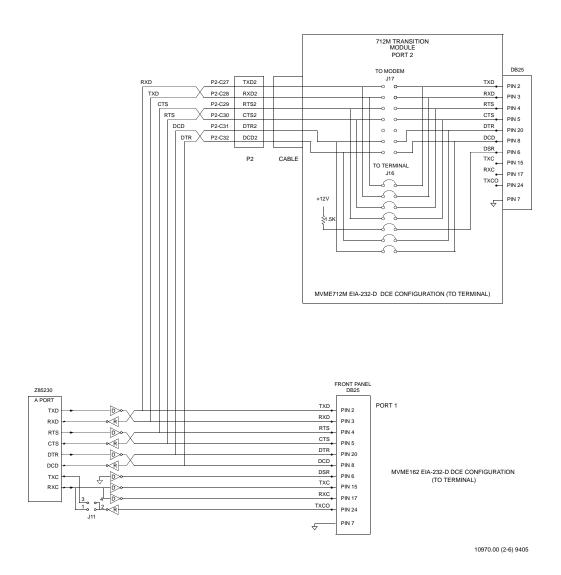

| Figure 2-4. MVME162/MVME712x EIA-232-D Connection Diagram | 2-20 |

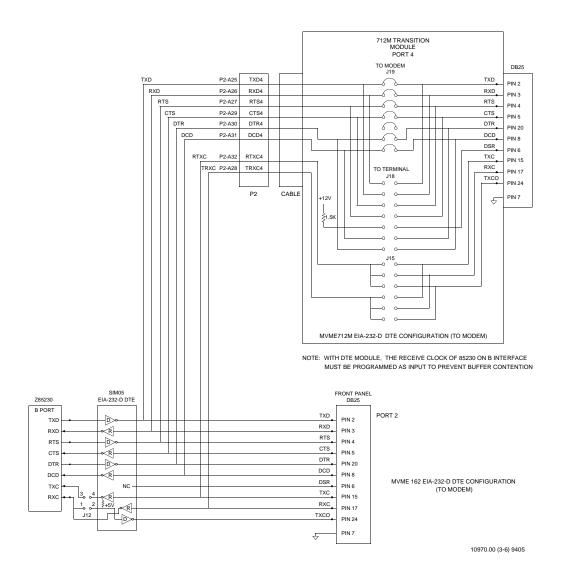

| Figure 2-5. MVME162 EIA-530 Connection Diagram            | 2-24 |

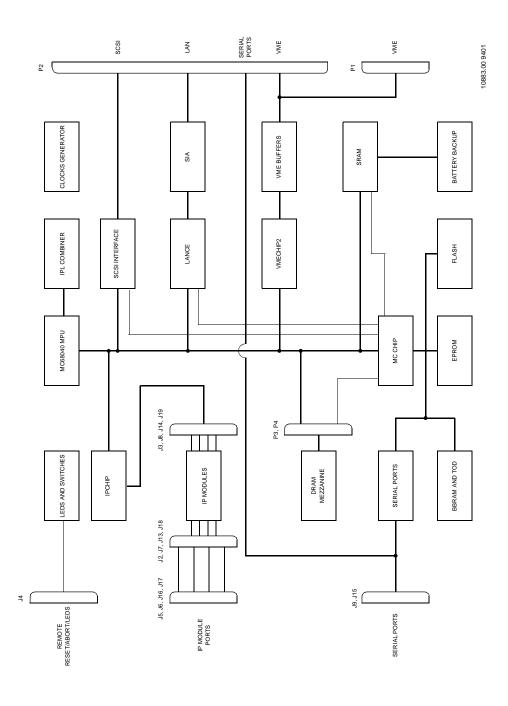

| Figure 4-1. MVME162 Main Module Block Diagram             | 4-13 |

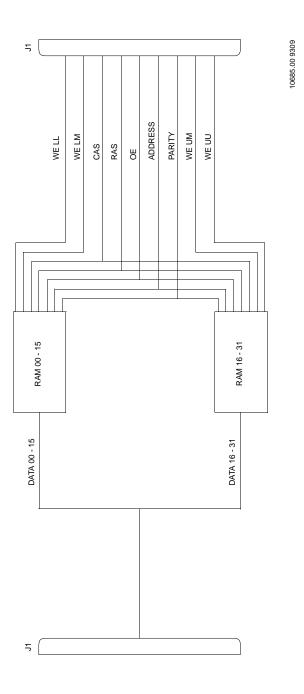

| Figure 4-2. Parity DRAM Mezzanine Module Block Diagram    | 4-14 |

# **List of Tables**

| Table 1-1. MVME162 Models                                  | 1-1  |

|------------------------------------------------------------|------|

| Table 1-2. MVME162 Specifications                          | 1-3  |

| Table 2-1. Serial Interface Module Part Numbers            |      |

| Table 3-1. Local Bus Memory Map                            | 3-4  |

| Table 3-2. Local I/O Devices Memory Map                    | 3-5  |

| Table 3-3. VMEchip2 Memory Map                             |      |

| Table 3-4. MCchip Register Map                             | 3-14 |

| Table 3-5. Z85230 SCC Register Addresses                   | 3-15 |

| Table 3-6. 82596CA Ethernet LAN Memory Map                 | 3-15 |

| Table 3-7. 53C710 SCSI Memory Map                          | 3-16 |

| Table 3-8. IPIC Overall Memory Map                         | 3-17 |

| Table 3-9. IPIC Memory Map—Control and Status Registers    | 3-18 |

| Table 3-10. MK48T08 BBRAM/TOD Clock Memory Map             | 3-19 |

| Table 3-11. BBRAM Configuration Area Memory Map            | 3-19 |

| Table 3-12. TOD Clock Memory Map                           | 3-20 |

| Table 4-1. DRAM Performance                                | 4-11 |

| Table A-1. EIA-232-D Interconnections                      | A-2  |

| Table A-2. EIA-232-D Interface Transmitter Characteristics | A-3  |

| Table A-3. EIA-232-D Interface Receiver Characteristics    | A-4  |

| Table A-4. Serial Port B EIA-530 Interconnect Signals      | A-4  |

| Table A-5. EIA-530 Interface Transmitter Characteristics   | A-7  |

| Table A-6. EIA-530 Interface Receiver Characteristics      |      |

#### Introduction

This manual provides general information, hardware preparation and installation instructions, operating instructions, and a functional description of the MVME162 Embedded Controller (referred to as the MVME162 throughout this manual).

#### **Models**

The MVME162 is available in several models, which are listed in Table 1-1.

Table 1-1. MVME162 Models

| Model | Description                                                    |

|-------|----------------------------------------------------------------|

| -001  | MC68LC040 microprocessor, 1MB DRAM, 512KB SRAM                 |

| -001  | MC68040 microprocessor, 1MB DRAM, 512KB SRAM                   |

| -003  | MC68LC040 microprocessor, 1MB DRAM, 512KB SRAM, no VMEbus      |

| -010  | MC68LC040 microprocessor, 4MB DRAM, 512KB SRAM                 |

| -010  | MC68LC040 microprocessor, 4MB DRAM, SCSI, 512KB SRAM           |

| -011  | MC68LC040 microprocessor, 4MB DRAM, Ethernet, 512KB SRAM       |

| -012  | MC68LC040 microprocessor, 4MB DRAM, SCSI, Ethernet, 512KB SRAM |

| -013  | MC68LC040 microprocessor, 4MB DRAM, Ethernet, no VMEbus        |

| -014  |                                                                |

|       | MC68040 microprocessor, 4MB DRAM, 512KB SRAM                   |

| -021  | MC68040 microprocessor, 4MB DRAM, SCSI, 512KB SRAM             |

| -022  | MC68040 microprocessor, 4MB DRAM, Ethernet, 512KB SRAM         |

| -023  | MC68040 microprocessor, 4MB DRAM, SCSI, Ethernet, 512KB SRAM   |

| -026  | MC68040 microprocessor, 4MB DRAM, Ethernet, no VMEbus          |

| -030  | MC68LC040 microprocessor, 8MB DRAM, 512KB SRAM                 |

| -031  | MC68LC040 microprocessor, 8MB DRAM, SCSI, 512KB SRAM           |

| -032  | MC68LC040 microprocessor, 8MB DRAM, Ethernet, 512KB SRAM       |

| -033  | MC68LC040 microprocessor, 8MB DRAM, SCSI, Ethernet, 512KB SRAM |

| -040  | MC68040 microprocessor, 8MB DRAM, 512KB SRAM                   |

| -041  | MC68040 microprocessor, 8MB DRAM, SCSI, 512KB SRAM             |

| -042  | MC68040 microprocessor, 8MB DRAM, Ethernet, 512KB SRAM         |

| -043  | MC68040 microprocessor, 8MB DRAM, SCSI, Ethernet, 512KB SRAM   |

#### **Features**

Features of the MVME162 include:

- □ 25MHz 32-bit Microprocessor: either an MC68LC040 Enhanced 32-bit Microprocessor with 8KB of cache and MMU, or an optional 25MHz MC68040 32-bit Microprocessor with 8KB of cache, MMU, and FPU

- ☐ 1MB, 4MB, or 8MB of shared Dynamic Random Access Memory (DRAM) with programmable parity

- □ 512KB of Static Random Access Memory (SRAM) with battery backup

- ☐ One JEDEC standard 32-pin PLCC EPROM socket (EPROMs may be shipped separately from the MVME162)

- ☐ 1MB Flash memory: either one Intel 28F008SA (for older boards) or four Intel 28F020s (for newer boards)

- ☐ Four 32-bit programmable timers and programmable Watchdog Timer (MCchip)

- ☐ Two 32-bit programmable timers and programmable Watchdog Timer (optional VMEchip2)

- 8K by 8 Non-Volatile Random Access Memory (NVRAM) and Time of Day (TOD) clock with battery backup (Thompson MK48T08)

- ☐ Input/Output

- Two serial ports (one EIA-232-D DCE; one EIA-232-D or EIA-530 DCE/DTE)

- Serial port controller (Zilog Z85230)

- Optional Small Computer Systems Interface (SCSI) bus interface with 32-bit local bus burst Direct Memory Access (DMA) (NCR 53C710 controller)

- Optional LAN Ethernet transceiver interface with 32-bit local bus DMA (Intel 82596CA controller)

- Four MVIP IndustryPack interfaces

- ☐ VMEbus interface (VMEchip2)—non-VMEbus version optional

- VMEbus system controller functions

- VMEbus interface to local bus (A24/A32, D8/D16/D32 (D8/D16/D32/D64BLT) (BLT = Block Transfer)

- Local bus to VMEbus interface (A16/A24/A32, D8/D16/D32)

- VMEbus interrupter

- VMEbus interrupt handler

- Global CSR for interprocessor communications

- DMA for fast local memory-VMEbus transfers (A16/A24/A32, D16/D32[D16/D32/D64BLT])

- ☐ Switches and Light-Emitting Diodes (LEDs)

- Two pushbutton switches (ABORT and RESET)

- Eight LEDs (FAIL, STAT, RUN, SCON, LAN, FUSE, SCSI, and VME)

# **Specifications**

Table 1-2, *MVME162 Specifications*, lists the specifications for an MVME162 without IndustryPacks. The subsequent sections detail cooling requirements and FCC compliance.

Table 1-2. MVME162 Specifications

| Characteristics                                                      | Specifications                                                                                               |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Power requirements<br>(with PROM; without IPs)                       | +5V (± 5%), 3.5 A typical, 4.5 A maximum<br>+12 Vdc (± 5%), 100 mA maximum<br>-12 Vdc (± 5%), 100 mA maximum |

| Operating temperature                                                | 0° to 70° C exit air with forced air cooling (see NOTE)                                                      |

| Storage temperature                                                  | -40° to +85° C                                                                                               |

| Relative humidity                                                    | 5% to 90% (noncondensing)                                                                                    |

| Physical dimensions PC board with mezzanine module only Height Depth | Double-high VMEboard  9.2 inches (233 mm) 6.3 inches (160 mm)                                                |

| Thickness PC board with connectors                                   | 0.66 inch (17 mm)                                                                                            |

| and front panel<br>Height                                            | 10.3 inches (262 mm)                                                                                         |

| Depth                                                                | 7.4 inches (188 mm)                                                                                          |

| Thickness                                                            | 0.80 inch (20.32 mm)                                                                                         |

Refer to the following sections on Cooling Requirements and Special Considerations for Elevated Temperature Operation.

MVME162/D2 1-3

#### **Cooling Requirements**

The Motorola MVME162 Embedded Controller is specified, designed, and tested to operate reliably with an incoming air temperature range from 0° to 55° C (32° to 131° F) with forced air cooling at a velocity typically achievable by using a 100 CFM axial fan. Temperature qualification is performed in a standard Motorola VMEsystem 3000 chassis. Twenty-five watt load boards are inserted in two card slots, one on each side, adjacent to the board under test, to simulate a high power density system configuration. An assembly of three axial fans, rated at 100 CFM per fan, is placed directly under the VME card cage. The incoming air temperature is measured between the fan assembly and the card cage, where the incoming airstream first encounters the controller under test. Test software is executed as the controller is subjected to ambient temperature variations. Case temperatures of critical, high power density integrated circuits are monitored to ensure component vendors specifications are not exceeded.

While the exact amount of airflow required for cooling depends on the ambient air temperature and the type, number, and location of boards and other heat sources, adequate cooling can usually be achieved with 10 CFM and 490 LFM flowing over the controller. Less airflow is required to cool the controller in environments having lower maximum ambients. Under more favorable thermal conditions, it may be possible to operate the controller reliably at higher than 55° C with increased airflow. It is important to note that there are several factors, in addition to the rated CFM of the air mover, which determine the actual volume and speed of air flowing over the controller.

#### **Special Considerations for Elevated Temperature Operation**

The following information is for users whose applications for the MVME162 may subject it to high temperatures.

The MVME162 uses commercial grade devices. Therefore, it can operate in an environment with ambient air temperatures from  $0^{\circ}$  C to  $70^{\circ}$  C. Several factors influence the ambient temperature seen by components on the MVME162. Among them are inlet air temperature; air flow characteristics; number, types, and locations of IndustryPack (IP) modules; power dissipation of adjacent boards in the system, etc.

A temperature profile of the MVME162-023 was developed in an MVME945 12-slot VME chassis. This board was loaded with one GreenSpring IP-Dual P/T module (position a) and three GreenSpring IP-488 modules (positions b, c, and d). One twenty-five-watt load board was installed adjacent to each side of the board under test. The exit air velocity was approximately 200 LFM

between the MVME162 and the IP-Dual P/T module. Under these conditions, a  $10^{\circ}$  C rise between the inlet and exit air was observed. At  $70^{\circ}$  C exit air temperature ( $60^{\circ}$  C inlet air), the junction temperatures of devices on the MVME162 were calculated (from the measured case temperatures) and did not exceed  $100^{\circ}$  C.

# Caution

For elevated-temperature operation, the user must perform similar measurements and calculations to determine what operating margin exists in a specific environment.

The following are some steps that the user can take to help make elevated-temperature operation possible:

- 1. Position the MVME162 board in the chassis for maximum airflow over the component side of the board.

- 2. Avoid placing boards with high power dissipation adjacent to the MVME162.

- 3. Use low-power IP modules only. The preferred locations for IP modules are position a (J2 and J3) and position d (J18 and J19).

#### **FCC Compliance**

The MVME162 was tested *without* IndustryPacks in an FCC-compliant chassis and meets the requirements for Class A equipment. FCC compliance was achieved under the following conditions:

- 1. Shielded cables on all external I/O ports.

- 2. Cable shields connected to earth ground via metal shell connectors bonded to a conductive module front panel.

- 3. Conductive chassis rails connected to earth ground. This provides the path for connecting shields to earth ground.

- 4. Front panel screws properly tightened.

For minimum RF emissions, it is essential that the conditions above be implemented. Failure to do so could compromise the FCC compliance of the equipment containing the module.

MVME162/D2 1-5

## **General Description**

The MVME162 is a double-high VMEmodule equipped with an MC68LC040 or optional MC68040 microprocessor. (The MC68040 microprocessor has a floating-point coprocessor; the MC68LC040 does not.)

The MVME162 has 1MB, 4MB, or 8MB of parity-protected DRAM; 512KB SRAM (with battery backup); a TOD clock (with battery backup); an optional LAN Ethernet transceiver interface with DMA, two serial ports (EIA-232-D and EIA-232-D/EIA-530); six tick timers with watchdog timer(s); optional SCSI bus interface with DMA; VMEbus interface (local bus to VMEbus/VMEbus to local bus, with A16/A24/A32, D8/D16/D32 bus widths and a VMEbus system controller).

## Input/Output

Input/Output (I/O) signals are routed through backplane connector P2. A P2 adapter board or LCP2 adapter board routes the signals and grounds from connector P2 to an MVME712 series transition module (MVME712-12, MVME712-13, MVME712A, MVME712AM, or MVME712M). The transition module routes the signals to the appropriate configuration headers and industry-standard connectors. Refer to the MVME712-12, MVME712-13, MVME712A, MVME712AM, and MVME712B Transition Modules and LCP2 Adapter Board User's Manual or the MVME712M Transition Module and P2 Adapter Board User's Manual for more information.

# Notes

When used with the MVME162, only serial ports 2 and 4 on the MVME712 are available for use. Serial ports 1 and 3 and the printer port are not connected to any MVME162 circuits and should not be used.

An I/O device may be connected to serial port 1 (or 2) on the MVME162 or to serial port 2 (or 4) on the MVME712, but not both. (That is, if an I/O device is connected to MVME162 port 1, no other I/O device should be connected to MVME712 port 2; they are functionally the same port.)

#### **VMEbus Interface**

The optional VMEchip2 ASIC is the VMEbus interface for the MVME162. (This option is a factory build and cannot be added in the field.) VMEchip2 features include:

Two programmable 32-bit tick timers

| Two programmable 32-bit tick timers                            |

|----------------------------------------------------------------|

| A programmable watchdog timer                                  |

| Programmable map decoders for the master and slave interfaces  |

| A VMEbus to/from local bus DMA controller                      |

| A VMEbus to/from local bus non-DMA programmed access interface |

| A VMEbus interrupter                                           |

| A VMEbus system controller                                     |

| A VMEbus interrupt handler                                     |

☐ A VMEbus requester

Processor-to-VMEbus transfers can be D8, D16, or D32. VMEchip2 DMA transfers to the VMEbus, however, can be D16, D32, D16/BLT, D32/BLT, or D64/MBLT.

#### **No-VMEbus-Interface Option**

If desired, the MVME162 can function as an embedded controller without a VMEbus interface (i.e., without the optional VMEchip2). Contact your local Motorola sales office for ordering information.

## **MCchip**

The Memory Controller (MCchip) ASIC provides four 32-bit programmable tick timers and an interface to the LAN chip, SCSI chip, serial port chip, BBRAM, PROM/Flash, SRAM, DRAM, reset control, watchdog timers, access timers, and interrupter logic.

#### Flash Memory and EPROM

The MVME162 is equipped with 1MB of Flash memory and an EPROM socket ready for the installation of the EPROM, which may be ordered separately. Flash memory is either a single device organized in a 1Mbit x 8 configuration or four devices organized in a 256Kbit x 8 configuration. The EPROM location is a standard JEDEC 32-pin PLCC capable of four Mbit densities (128 Kbit x 8;

MVME162/D2 1-7

256 Kbit x 8; 512 Kbit x 8; 1 Mbit x 8) organized as a 512Kbit x 8 device. A jumper allows reset code to be fetched either from Flash memory or from the EPROM.

#### **IndustryPack Modules**

Up to four IndustryPack (IP) modules may be installed on the MVME162. The interface between the IPs and MVME162 is the IndustryPack Interface Controller (IPIC) ASIC. Access to the IPs is provided by four 3M connectors located behind the MVME162 front panel.

#### **Optional SCSI Interface**

An NCR 53C710 coprocessor provides the SCSI interface for the MVME162.

#### **Optional LAN Ethernet Transceiver Interface**

An Intel 82596CA controller provides the LAN Ethernet transceiver interface for the MVME162.

# **Required Equipment**

|  | is required to complete an MVME162 system: |

|--|--------------------------------------------|

|--|--------------------------------------------|

- □ System console terminal

- ☐ Disk drives and controllers

- Operating system

- MVME712 series transition module (MVME712-12, MVME712-13, MVME712A, MVME712AM, MVME712B, or MVME712M); P2 Adapter Board or LCP2 Adapter Board; and cable

The MVME712B is an optional device used with MVME712-12, MVME712-13, MVME712A, and MVME712AM modules only.

# **MVME162Bug Firmware**

The 162Bug package, MVME162BUG, is a powerful evaluation and debugging tool for systems built around the MVME162 CISC-based microcomputers. Facilities are available for loading and executing user programs under complete operator control for system evaluation. 162Bug includes commands for display and modification of memory, breakpoint and tracing capabilities, a powerful assembler/disassembler useful for patching programs, and a self-

test at power-up feature which verifies the integrity of the system. Various 162Bug routines that handle I/O, data conversion, and string functions are available to user programs through the TRAP #15 system calls.

MVME162Bug occupies the first half (512KB) of Flash memory.

#### **MVME712 Series Transition Modules**

The MVME712 series transition modules provide an interface between the MVME162 and peripheral devices such as EIA-232-D serial devices, SCSI devices, and LAN Ethernet devices. A P2 Adapter Board or LCP2 Adapter Board and cable are required.

# Caution

Connect peripheral devices to MVME712 serial ports 2 and 4 only. (Serial port 2 is the terminal or bug interface.) Do not connect peripheral devices to serial ports 1 and 3, or to the printer port.

An I/O device may be connected to serial port 1 (or 2) on the MVME162 or to serial port 2 (or 4) on the MVME712, but not to both ports. (That is, if an I/O device is connected to MVME162 port 1, no other I/O device should be connected to MVME712 port 2; they are functionally the same port.)

#### **Available Software**

Available software for the MVME162 includes the on-board debugger/monitor firmware, VMEexec driver packages for various IndustryPack modules, and numerous third-party applications for MC680x0-based systems. Contact your local Motorola sales office for more information.

MVME162/D2 1-9

#### **Related Documentation**

The following publications are applicable to the MVME162 and may provide additional helpful information. If not shipped with this product, they may be purchased by contacting your local Motorola sales office. Non-Motorola documents may be purchased from the sources listed.

| Document Title                                                                                                    | Motorola<br>Publication<br>Number |

|-------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| M68040 Microprocessors User's Manual                                                                              | M68040UM                          |

| MVME162 Embedded Controller Support Information (Refer to the <i>Support Information</i> section in this chapter) | SIMVME162                         |

| MVME162Bug Debugging Package User's Manual                                                                        | MVME162BUG                        |

| Debugging Package for Motorola 68K CISC CPUs User's<br>Manual, Parts 1 and 2                                      | 68KBUG1/2                         |

| Single Board Computers SCSI Software User's Manual                                                                | SBCSCSI                           |

| MVME162 Embedded Controller Programmer's Reference<br>Guide                                                       | MVME162PG                         |

| MVME712-12, MVME712-13, MVME712A, MVME712AM, and MVME712B Transition Modules and LCP2 Adapter Board User's Manual | MVME712A                          |

| MVME712M Transition Module and P2 Adapter Board User's Manual                                                     | MVME712M                          |

| MVME1x7 Data Sheet Package (for use with the MVME162[LX] and the MVME166/MVME167/MVME187)                         | 68-1X7DS                          |

# Notes

Although not shown in the above list, each Motorola Computer Group manual publication number is suffixed with characters which represent the revision level of the document, such as "/D2" (the second revision of a manual); a supplement bears the same number as a manual but has a suffix such as "/D2A1" (the first supplement to the second edition of the manual).

The MVME1x7 Data Sheet Package is composed of vendorsupplied data sheets and manuals for the peripheral controllers used on the MVME162 and other boards. The following publications are available from the sources indicated.

Versatile Backplane Bus: VMEbus, ANSI/IEEE Std 1014-1987, The Institute of Electrical and Electronics Engineers, Inc., 345 East 47th Street, New York, NY 10017 (VMEbus Specification). This is also available as *Microprocessor system bus for 1 to 4 byte data, IEC 821 BUS*, Bureau Central de la Commission Electrotechnique Internationale; 3, rue de Varembé, Geneva, Switzerland.

ANSI Small Computer System Interface-2 (SCSI-2), Draft Document X3.131-198X, Revision 10c; Global Engineering Documents, P.O. Box 19539, Irvine, CA 92714.

*IndustryPack Logic Interface Specification*, Revision 1.0; GreenSpring Computers, Inc., 1204 O'Brien Drive, Menlo Park, CA 94025.

82596CA Local Area Network Coprocessor data sheet, order number 290218; and 82596 User's Manual, order number 296853; Intel Corporation, Literature Sales, P.O. Box 58130, Santa Clara, CA 95052-8130.

NCR 53C710 SCSI I/O Processor Data Manual, order number NCR53C710DM; and NCR 53C710 SCSI I/O Processor Programmer's Guide, order number NCR53C710PG; NCR Corporation, Microelectronics Products Division, Colorado Springs, CO.

MK48T08(B) Timekeeper™ and 8Kx8 Zeropower™ RAM data sheet in *Static RAMs Databook*, Order Code DBSRAM71; SGS-THOMPSON Microelectronics Group; North & South American Marketing Headquarters, 1000 East Bell Road, Phoenix, AZ 85022-2699.

Z85230 Serial Communications Controller data sheet, Zilog Inc., 210 Hacienda Ave., Campbell, CA 95008-6609.

28F008SA Flash Memory Data Sheet, Order Number 290435-001; Intel Literature Sales, P.O. Box 7641, Mt. Prospect, IL 60056-7641.

28F020 Flash Memory Data Sheet, Order Number 290245-003; Intel Literature Sales, P.O. Box 7641, Mt. Prospect, IL 60056-7641.

# **Support Information**

You can obtain connector interconnect signal information, parts lists, and schematics for the MVME162 free of charge by contacting your local Motorola sales office.

MVME162/D2 1-11

# **Manual Terminology**

Throughout this manual, a convention is used which precedes data and address parameters by a character identifying the numeric format as follows:

\$ dollar specifies a hexadecimal character

\$ percent specifies a binary number

\$ ampersand specifies a decimal number

Unless otherwise specified, all address references are in hexadecimal.

An asterisk (\*) following the signal name for signals which are level-significant denotes that the signal is true or valid when the signal is low.

An asterisk (\*) following the signal name for signals which are edge-significant denotes that the actions initiated by that signal occur on high-to-low transition.

In this manual, *assertion* and *negation* are used to specify forcing a signal to a particular state. In particular, *assertion* and *assert* refer to a signal that is active or true; *negation* and *negate* indicate a signal that is inactive or false. These terms are used independently of the voltage level (high or low) that they represent.

In this manual, *MVME712 series transition module* refers generically to the MVME712-12, MVME712-13, MVME712A, MVME712AM, or MVME712M. *MVME712x transition module* refers to the closely related MVME712-12, MVME712-13, MVME712A, or MVME712AM (not to the MVME712M). References to a specific module use the complete designation of that module.

Data and address sizes are defined as follows:

significant.

- □ A byte is eight bits, numbered 0 through 7, with bit 0 being the least significant.

□ A word is 16 bits, numbered 0 through 15, with bit 0 being the least

- ☐ A longword is 32 bits, numbered 0 through 31, with bit 0 being the least significant.

#### Introduction

This chapter provides unpacking instructions, hardware preparation guidelines, and installation instructions for the MVME162 Embedded Controller. Hardware preparation for the MVME712 series transition modules is described in separate manuals; refer to the *Related Documentation* section in Chapter 1.

# **Unpacking Instructions**

If the shipping carton is damaged upon receipt, request that the carrier's agent be present during the unpacking and inspection of the equipment.

Unpack the equipment from the shipping carton. Refer to the packing list and verify that all items are present. Save the packing material for storing and reshipping of equipment.

Avoid touching areas of integrated circuitry; static discharge can damage circuits.

# **Hardware Preparation**

To produce the desired configuration and ensure proper operation of the MVME162, you may need to carry out certain modifications before installing the module.

The MVME162 provides software control over most options: by setting bits in control registers after installing the MVME162 in a system, you can modify its configuration. (The MVME162 registers are described in Chapter 4, and/or in the MVME162 Embedded Controller Programmer's Reference Guide as listed in Related Documentation in Chapter 1.)

Some options, however, are not software-programmable. Such options are controlled by manual installation or removal of header jumpers or interface modules.

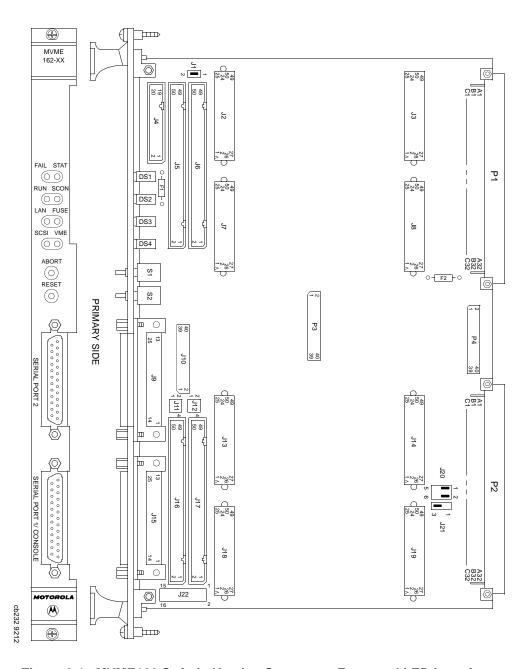

Figure 2-1 illustrates the placement of the switches, jumper headers, connectors, and LED indicators on the MVME162. Manually configurable items include:

| ) | SIM selection for serial port B configuration (J10)         |

|---|-------------------------------------------------------------|

| ב | System controller selection (J1)                            |

| ) | Synchronous clock selection (J11) for Serial Port 1/Console |

| ) | Synchronous clock selection (J12) for Serial Port 2         |

| ) | SRAM backup power source selection (J20)                    |

| ) | EPROM size selection (J21)                                  |

| ) | General-purpose readable register configuration (J22)       |

The MVME162 has been factory tested and is shipped with the configurations described in the following sections. The MVME162's required and factory-installed Debug Monitor, MVME162Bug (162Bug), operates with those factory settings.

#### SIM Selection

Port B of the MVME162's Z85230 serial communications controller is configurable via a serial interface module (SIM) which is installed at connector J10 on the MVME162 board. Four serial interface modules are available:

| EIA-232-D (DCE and DTE |

|------------------------|

| EIA-530 (DCE and DTE)  |

You can change Port B from an EIA-232-D to an EIA-530 interface (or viceversa) by mounting the appropriate serial interface module. Port B is routed (via the SIM at J10) to the 25-pin DB25 front panel connector marked SERIAL PORT 2.

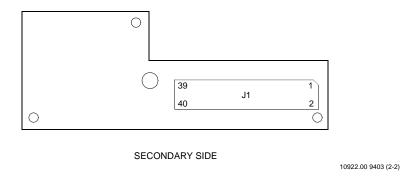

For the location of SIM connector J10 on the MVME162, refer to Figure 2-1. Figure 2-2 illustrates the secondary side (bottom) of a serial interface module, showing the J1 connector which plugs into SIM connector J10 on the MVME162. Figure 2-3 (sheets 3-6), Figure 2-4 (sheets 3-4), and Figure 2-5 illustrate the configurations available for Port B.

For the part numbers of the serial interface modules, refer to Table 2-1. The part numbers are ordinarily printed on the primary side (top) of the SIMs, but may be found on the secondary side in some versions.

If you need to replace an existing serial interface module with a SIM of another type, go to *Removal of Existing SIM* below. If there is no SIM on the main board, skip to *Installation of New SIM*.

Figure 2-1. MVME162 Switch, Header, Connector, Fuse, and LED Locations

MVME162/D2 2-3

EIA Model Configuration **Part Number** Standard Number EIA-232-D DTE 01-W3846B SIM05 DCE 01-W3865B SIM<sub>06</sub> EIA-530 DTE 01-W3868B SIM07 DCE 01-W3867B SIM08

Table 2-1. Serial Interface Module Part Numbers

Figure 2-2. Serial Interface Module, Connector Side

# Removal of Existing SIM

- 1. Each serial interface module is retained by two 4-40 x  $^3$ /16 " Phillips-head screws in opposite corners. Remove the two screws and store them in a safe place for later use.

- 2. Grasp opposite sides of the SIM and gently lift straight up.

# Avoid lifting the SIM by one side only, as the connector can be damaged on the SIM or the main board.

3. Place the SIM in a static-safe container for possible reuse.

#### Installation of New SIM

- 1. Observe the orientation of the connector keys on SIM connector J1 and MVME162 connector J10. Turn the SIM so that the keys line up and place it gently on connector J10, aligning the mounting holes at the SIM corners with the matching standoffs on the MVME162.

- Gently press the top of the SIM to seat it on the connector. If the SIM does not seat with gentle pressure, recheck the orientation. If the SIM connector is oriented incorrectly, the mounting holes will not line up with the standoffs.

# Caution

Do not attempt to force the SIM on if it is oriented incorrectly.

3. Place the two 4-40 x  $^3$ /16" Phillips-head screws that you previously removed (or that were supplied with the new SIM) into the two opposite-corner mounting holes. Screw them into the standoffs but do not overtighten them.

The signal relationships and signal connections in the various serial configurations available for ports A and B are illustrated in Figures 2-3, 2-4, and 2-5.

#### System Controller Select Header (J1)

The MVME162 is factory-configured as a VMEbus system controller (i.e., a jumper is installed across pins 1 and 2 of header J1). Remove the J1 jumper if the MVME162 is not to be the system controller. Note that when the MVME162 is functioning as system controller, the SCON LED is turned on.

For MVME162s without the optional VMEbus interface (i.e., no VMEchip2), the jumper may be installed or removed without affecting normal operation.

System Controller (factory configuration)

Not System Controller

MVME162/D2 2-5

## Synchronous Clock Select Header (J11) for Serial Port 1/Console

The MVME162 is shipped from the factory with the SERIAL PORT 1/CONSOLE header configured for asynchronous communications (i.e., jumpers removed). To select synchronous communications for the SERIAL PORT 1/CONSOLE connection, install jumpers across pins 1 and 2 and pins 3 and 4.

Internal Clock (factory configuration)

External Clock

## Clock Select Header (J12) for Serial Port 2

The MVME162 is shipped from the factory with the SERIAL PORT 2 header configured for asynchronous communications (i.e., jumpers removed). To select synchronous communications for the SERIAL PORT 2 connection, install jumpers across pins 1 and 2 and pins 3 and 4.

Internal Clock (factory configuration)

External Clock

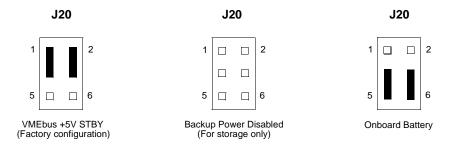

#### **SRAM Battery Backup Source Select Header (J20)**

The MVME162 is factory-configured to use VMEbus +5V standby power as a backup power source for the SRAM (i.e., jumpers are installed across pins 1 and 3 and 2 and 4). To select the onboard battery as the backup power source, install the jumpers across pins 3 and 5 and 4 and 6.

For MVME162s without the optional VMEbus interface (i.e., without the VMEchip2 ASIC), you must select the onboard battery as the backup power source.

Removing all jumpers may temporarily disable the SRAM. Do not remove all jumpers from J20, except for storage.

#### **EPROM Size Select Header (J21)**

The MVME162 is factory-configured for a 4Mbit EPROM (i.e., a jumper is installed across pins 2 and 3). This is the only size currently available; if a larger EPROM becomes available, this jumper will allow it to be selected.

MVME162/D2 2-7

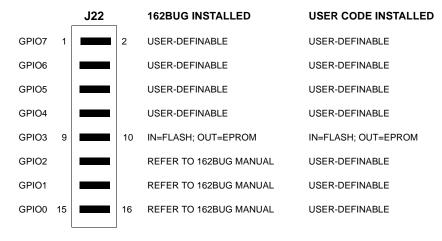

#### **General-Purpose Readable Jumpers Header (J22)**

Header J22 provides eight readable jumpers. These jumpers can be read as a register (at \$FFF4202D) in the MCchip LCSR (local control/status register). The bit values are read as a zero when the jumper is installed, and as a one when the jumper is removed.

If the MVME162BUG firmware is installed, four jumpers are user-definable (pins 1-2, 3-4, 5-6, 7-8). If the MVME162BUG firmware is not installed, seven jumpers are user-definable (pins 1-2, 3-4, 5-6, 7-8, 11-12, 13-14, 15-16).

Pins 9-10 (GPIO3) are reserved to select either the Flash memory map (jumper installed) or the EPROM memory map (jumper removed). They are not user-definable.

The MVME162 is shipped from the factory with J22 set to all zeros (jumpers on all pins).

EPROMs Selected (factory configuration)

#### Installation Instructions

The following sections discuss the installation of IndustryPacks (IPs) on the MVME162, the installation of the MVME162 into a VME chassis, and the system considerations relevant to the installation. Before installing IndustryPacks, ensure that the serial ports and all header jumpers are configured as desired.

#### **IP Installation on the MVME162**

Up to four IndustryPack (IP) modules may be installed on the MVME162. Install the IPs on the MVME162 as follows:

- 1. Each IP has two 50-pin connectors that plug into two corresponding 50-pin connectors on the MVME162: J2/J3, J7/J8, J13/J14, J18/J19. See Figure 2-1 for the MVME162 connector locations.

- Orient the IP(s) so that the tapered connector shells mate properly.

Plug IP\_a into connectors J2 and J3; plug IP\_b into J7 and J8. Plug IP\_c into J13 and J14; plug IP\_d into J18 and J19. If a double-sized IP is used, plug IP\_ab into J2, J3, J7, and J8; plug IP\_cd into J13, J14, J18, and J19.

- 2. Four additional 50-pin connectors (J6, J5, J17, and J16) are provided behind the MVME162 front panel for external cabling connections to the IP modules. There is a one-to-one correspondence between the signals on the cabling connectors and the signals on the associated IP connectors (i.e., J6 has the same IP\_a signals as J2; J5 has the same IP\_b signals as J7; J17 has the same IP c signals as J13; and J16 has the same IP d signals as J18.

- Connect user-supplied 50-pin cables to J6, J5, J17, and J16 as needed.

Because of the varying requirements for each different kind of IP,

Motorola does not supply these cables.

- Bring the IP cables out the narrow slots in the MVME162 front panel and attach them to the appropriate external equipment, depending on the nature of the particular IP(s).

MVME162/D2 2-9

#### **MVME162 Module Installation**

With EPROM and IndustryPacks installed and headers properly configured, proceed as follows to install the MVME162 in the VME chassis:

1. Turn all equipment power OFF and disconnect the power cable from the AC power source.

# Caution

Inserting or removing modules while power is applied could result in damage to module components.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

- 2. Remove the chassis cover as instructed in the user's manual for the equipment.

- 3. Remove the filler panel from the card slot where you are going to install the MVME162.

- If you intend to use the MVME162 as system controller, it must occupy

the leftmost card slot (slot 1). The system controller must be in slot 1

to correctly initiate the bus-grant daisy-chain and to ensure proper

operation of the IACK daisy-chain driver.

- If you do not intend to use the MVME162 as system controller, it can occupy any unused double-height card slot.

- 4. Slide the MVME162 into the selected card slot. Be sure the module is seated properly in the P1 and P2 connectors on the backplane. Do not damage or bend connector pins.

- 5. Secure the MVME162 in the chassis with the screws provided, making good contact with the transverse mounting rails to minimize RF emissions.

- 6. Install the MVME712 series transition module in the front or the rear of the VME chassis. (To install an MVME712M, which has a double-wide front panel, you may need to shift other modules in the chassis.)

- 7. On the chassis backplane, remove the INTERRUPT ACKNOWLEDGE (IACK) and BUS GRANT (BG) jumpers from the header for the card slot occupied by the MVME162.

Connect the P2 Adapter Board or LCP2 Adapter Board and cable(s) to MVME162 backplane connector P2. This provides a connection point for terminals or other peripherals at the EIA-232-D serial ports, SCSI ports, and LAN Ethernet port.

For information on installing the P2 or LCP2 Adapter Board and the MVME712 series transition module(s), refer to the manuals listed in *Related Documentation* in Chapter 1 (the *MVME162 Embedded Controller Programmer's Reference Guide* provides some connection diagrams).

# Note

If you intend to use the MVME162 with Port B in an EIA-530 configuration, do not install the P2 or LCP2 Adapter Board and the MVME712 series transition module. They are incompatible with the EIA-530 interface (refer to MVME162 Serial Port 2 in Chapter 4, Functional Description).

- 9. Connect the appropriate cable(s) to the panel connectors for the EIA-232-D serial ports, SCSI port, and LAN Ethernet port.

- Note that some cables are not provided with the MVME712 series module and must be made or purchased by the user. (Motorola recommends shielded cable for all peripheral connections to minimize radiation.)

- 10. Connect the peripheral(s) to the cable(s). Appendix A supplies detailed information on the EIA-232-D signals supported. Appendix B describes the Ethernet LAN (*Local Area Network*) port connections. Appendix C describes the SCSI (*Small Computer System Interface*) I/O bus connections.

- 11. Install any other required VMEmodules in the system.

- 12. Replace the chassis cover.

- 13. Connect the power cable to the AC power source and turn the equipment power ON.

## **System Considerations**

The MVME162 draws power from VMEbus backplane connectors P1 and P2. P2 is also used for the upper 16 bits of data in 32-bit transfers, and for the upper 8 address lines in extended addressing mode. The MVME162 may not function properly without its main board connected to VMEbus backplane connectors P1 and P2.

Whether the MVME162 operates as a VMEbus master or as a VMEbus slave, it is configured for 32 bits of address and 32 bits of data (A32/D32). However, it handles A16 or A24 devices in the address ranges indicated in Chapter 3. D8 and/or D16 devices in the system must be handled by the MC68040/MC68LC040 software. Refer to the memory maps in Chapter 3.

The MVME162 contains shared onboard DRAM whose base address is software-selectable. Both the onboard processor and offboard VMEbus devices see this local DRAM at base physical address \$0000000, as programmed by the MVME162Bug firmware. This may be changed via software to any other base address. Refer to the MVME162 Embedded Controller Programmer's Reference Guide for more information.

If the MVME162 tries to access offboard resources in a nonexistent location and is not system controller, and if the system does not have a global bus timeout, the MVME162 waits forever for the VMEbus cycle to complete. This will cause the system to lock up. There is only one situation in which the system might lack this global bus timeout: when the MVME162 is not the system controller and there is no global bus timeout elsewhere in the system.

Multiple MVME162s may be installed in a single VME chassis. In general, hardware multiprocessor features are supported.

If you are installing multiple MVME162s in an MVME945 chassis, do not install an MVME162 in slot 12. The height of the IP modules may cause clearance difficulties in that slot position.

Other MPUs on the VMEbus can interrupt, disable, communicate with, and determine the operational status of the processor(s). One register of the GCSR (global control/status register) set includes four bits that function as location monitors to allow one MVME162 processor to broadcast a signal to any other MVME162 processors. All eight registers are accessible from any local processor as well as from the VMEbus.

The MVME162 provides +5 Vdc power to the remote LED/switch connector (J4) through a 1A fuse (F1) located near J4. Connector J4 is the interface for a remote control and indicator panel. If none of the LEDs light and the ABORT and RESET switches do not operate, check fuse F1.

The MVME162 provides +12 Vdc power to the Ethernet transceiver interface through a 1A fuse (F2) located near diode CR1. The FUSE LED lights to indicate that +12 Vdc is available. When the MVME712M module is used, the yellow DS1 LED on the MVME712M illuminates when LAN power is available, which indicates that the fuse is good. If the Ethernet transceiver fails to operate, check fuse F2.

The MVME162 provides SCSI terminator power through a 1A fuse (F1) located on the P2 Adapter Board or LCP2 Adapter Board. If the fuse is blown, the SCSI device(s) may function erratically or not at all. When the P2 Adapter Board is used with an MVME712M and the SCSI bus is connected to the MVME712M, the green DS2 LED on the MVME712M front panel illuminates when SCSI terminator power is available. If the green DS2 LED flickers during SCSI bus operation, check P2 Adapter Board fuse F1.

Figure 2-3. MVME162/MVME712M EIA-232-D Connection Diagram (Sheet 1 of 6)

Figure 2-3. MVME162/MVME712M EIA-232-D Connection Diagram (Sheet 2 of 6)

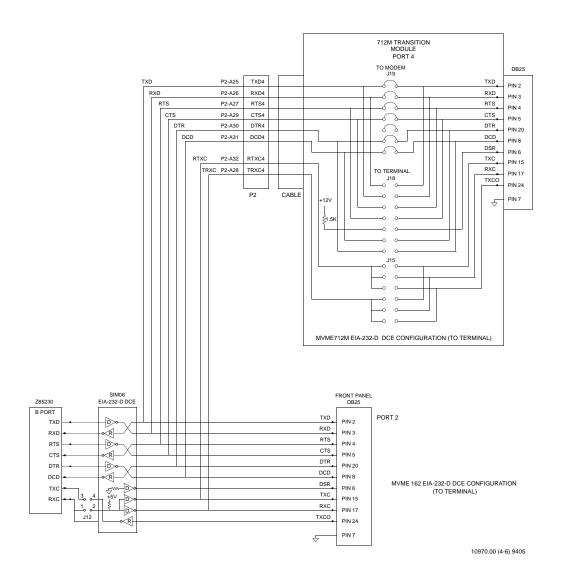

Figure 2-3. MVME162/MVME712M EIA-232-D Connection Diagram (Sheet 3 of 6)

Figure 2-3. MVME162/MVME712M EIA-232-D Connection Diagram (Sheet 4 of 6)

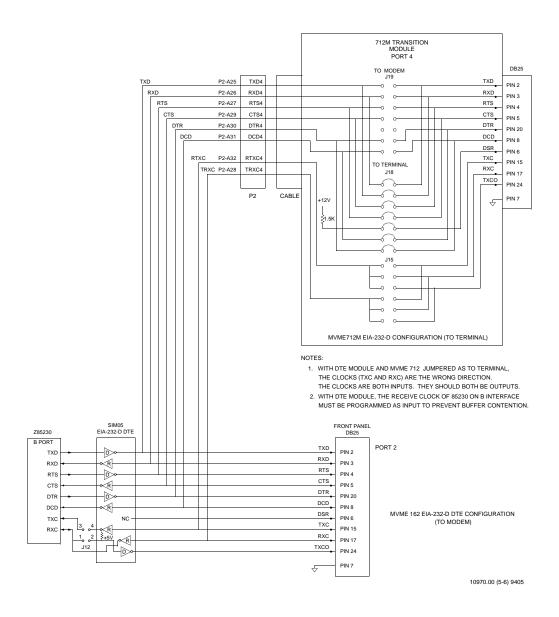

Figure 2-3. MVME162/MVME712M EIA-232-D Connection Diagram (Sheet 5 of 6)

Figure 2-3. MVME162/MVME712M EIA-232-D Connection Diagram (Sheet 6 of 6)

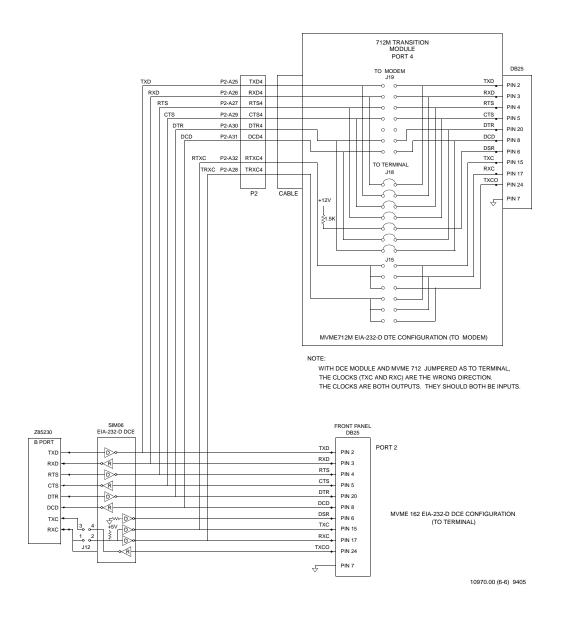

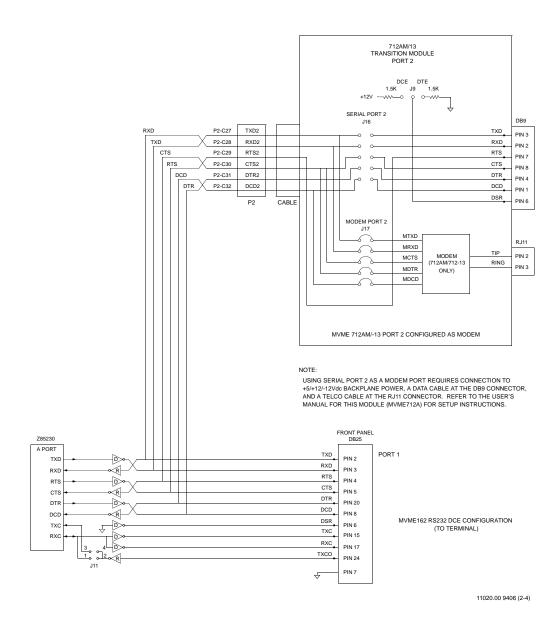

Figure 2-4. MVME162/MVME712x EIA-232-D Connection Diagram (Sheet 1 of 4)

Figure 2-4. MVME162/MVME712x EIA-232-D Connection Diagram (Sheet 2 of 4)

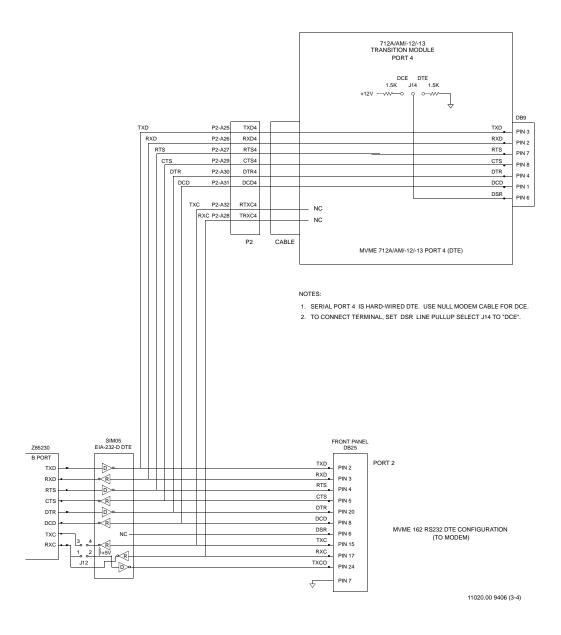

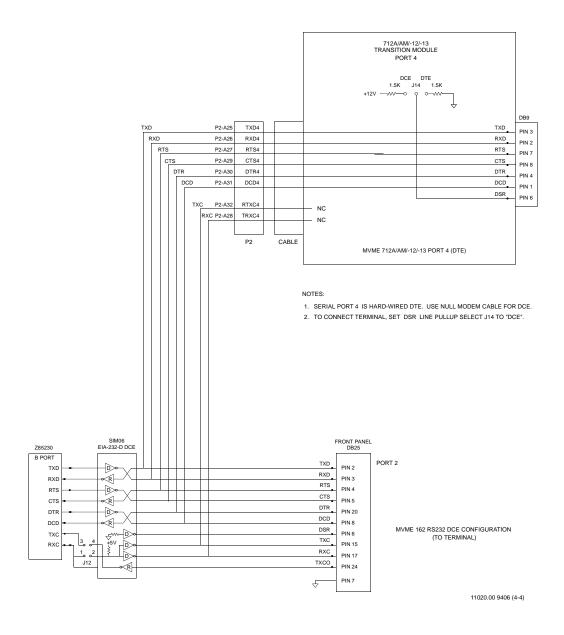

Figure 2-4. MVME162/MVME712x EIA-232-D Connection Diagram (Sheet 3 of 4)

Figure 2-4. MVME162/MVME712x EIA-232-D Connection Diagram (Sheet 4 of 4)

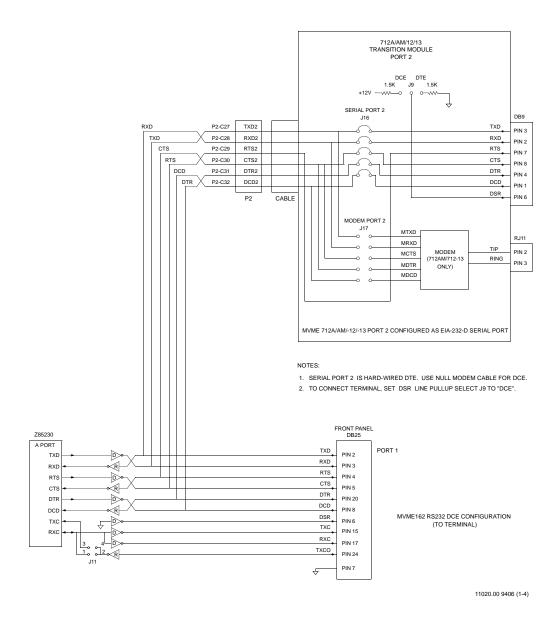

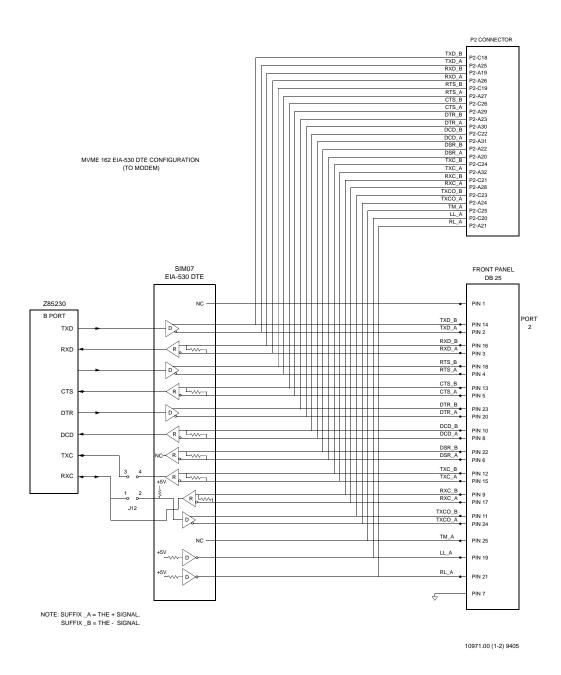

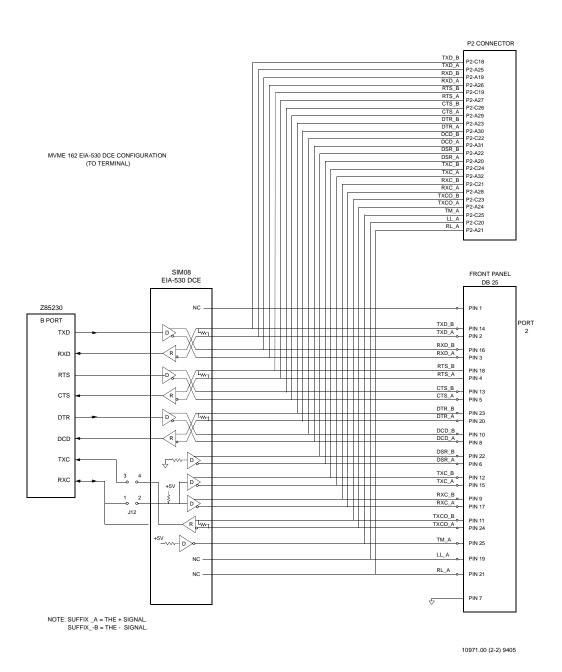

Figure 2-5. MVME162 EIA-530 Connection Diagram (Sheet 1 of 2)

Figure 2-5. MVME162 EIA-530 Connection Diagram (Sheet 2 of 2)

### Introduction

This chapter provides information necessary to use the MVME162 in a system configuration. This includes a description of the switches and LEDs, memory maps, and software initialization of the module.

#### Switches and LEDs

The MVME162 front panel has ABORT and RESET switches and eight LED (light-emitting diode) indicators (FAIL, STAT, RUN, SCON, LAN, FUSE, SCSI, VME).

## **ABORT Switch (S1)**

When enabled by software, the ABORT switch generates an interrupt at a user-programmable level. It is normally used to abort program execution and return to the 162Bug debugger firmware located in the MVME162 EPROM and Flash memory.

The ABORT switch interrupter in the MCchip ASIC is an edge-sensitive interrupter connected to the ABORT switch. This interrupter is filtered to remove switch bounce.

## **RESET Switch (S2)**

The RESET switch resets all onboard devices; it also drives SYSRESET\* if the MVME162 is the system controller. The RESET switch may be disabled by software.

The VMEchip2 includes both a global and a local reset driver. When the VMEchip2 operates as the VMEbus system controller, the reset driver provides a global system reset by asserting the VMEbus signal SYSRESET\*. A SYSRESET\* may be generated by the RESET switch, a power-up reset, a watchdog timeout, or by a control bit in the LCSR in the VMEchip2. SYSRESET\* remains asserted for at least 200 ms, as required by the VMEbus specification.

Similarly, the VMEchip2 provides an input signal and a control bit to initiate a local reset operation. By setting a control bit, software can maintain a board in a reset state, disabling a faulty board from participating in normal system operation. The local reset driver is enabled even when the VMEchip2 is not the

system controller. A local reset may be generated by the RESET switch, a power-up reset, a watchdog timeout, a VMEbus SYSRESET\*, or a control bit in the GCSR.

# Note

For an MVME162 without the VMEbus option (i.e., with no VMEchip2), the LCSR control bit is not available to reset the module. In this case, the watchdog timer is allowed to time out to reset the MVME162.

### Front Panel Indicators (DS1 - DS4)

There are eight LEDs on the MVME162 front panel: FAIL, STAT, RUN, SCON, LAN, FUSE, SCSI, and VME.

- □ FAIL LED (red). Lights when the BRDFAIL\* signal line is active. Part of DS1.

- □ STAT LED (yellow). Driven by the MC68040 status lines on the MVME162. Lights when a halt condition from the processor is detected. Part of DS1.

- □ RUN LED (green). Lights when the local bus TIP\* signal line is low. This indicates one of the local bus masters is executing a local bus cycle. Part of DS2.

- □ SCON LED (green). Lights when the VMEchip2 in the MVME162 is the VMEbus system controller. Part of DS2.

- □ LAN LED (green). Lights when the LAN chip is local bus master. Part of DS3.

- □ FUSE LED (green). Lights when power is available to the transceiver interface (the MVME162 supplies +12V power to the LAN Ethernet transceiver interface through a fuse). Part of DS3.

- □ SCSI LED (green). Lights when the SCSI chip is local bus master. Part of DS4.

- □ VME LED (green). Lights when the board is using the VMEbus (VMEbus AS\* line asserted by the VMEchip2) or when the board is accessed by the VMEbus (VMEchip2 is the local bus master). Part of DS4.

3-2 User's Manual

## **Memory Maps**

There are two points of view for memory maps:

- ☐ The mapping of all resources as viewed by local bus masters (local bus memory map)

- ☐ The mapping of onboard resources as viewed by VMEbus masters (VMEbus memory map)

## **Local Bus Memory Map**

The local bus memory map is split into different address spaces by the Transfer Type (TT) signals. The local resources respond to the normal access and interrupt acknowledge codes.

#### **Normal Address Range**

The memory map of devices that respond to the normal address range is shown in the following tables. The normal address range is defined by the TT signals on the local bus. For the MVME162, transfer types 0, 1, and 2 define the normal address range. Table 3-1 defines the entire map (\$00000000 to \$FFFFFFFF). Many areas of the map are user-programmable, and suggested uses are shown in the table. The cache inhibit function is programmable in the MC68xx040 MMU. The onboard I/O space must be marked "cache inhibit" and serialized in its page table. Table 3-2 further defines the map for the local I/O devices.

Table 3-1. Local Bus Memory Map

| Address Range         | Devices Accessed                           | Port Width | Size       | Software<br>Cache<br>Inhibit | Notes |

|-----------------------|--------------------------------------------|------------|------------|------------------------------|-------|

| Programmable          | DRAM on Board                              | D32        | 1MB-8MB    | N                            | 2     |

| Programmable          | SRAM                                       | D32        | 128KB-2MB  | N                            | 2     |

| Programmable          | VMEbus A32/A24                             | D32/D16    |            | ?                            | 4     |

| Programmable          | IP_a Memory                                | D32-D8     | 64 KB-8 MB | ?                            | 2, 4  |

| Programmable          | IP_b Memory                                | D32-D8     | 64 KB-8 MB | ?                            | 2, 4  |

| Programmable          | IP_c Memory                                | D32-D8     | 64 KB-8 MB | ?                            | 2, 4  |

| Programmable          | IP_d Memory                                | D32-D8     | 64 KB-8 MB | ?                            | 2, 4  |

| \$FF800000-\$FF9FFFFF | Flash/EPROM                                | D32        | 2 MB       | N                            | 1, 5  |

| \$FFA00000-\$FFBFFFFF | EPROM/Flash                                | D32        | 2 MB       | N                            | 6     |

| \$FFC00000-\$FFCFFFFF | Not Decoded                                | D32        | 1 MB       | N                            | 7     |

| \$FFD00000-\$FFDFFFF  | Not Decoded                                | D32        | 1 MB       | N                            | 7     |

| \$FFE00000-\$FFE7FFF  | SRAM default                               | D32        | 512 KB     | N                            |       |

| \$FFE80000-\$FFEFFFF  | Not Decoded                                |            | 512 KB     | N                            | 7     |

| \$FFF00000-\$FFFEFFF  | Local I/O Devices<br>(Refer to next table) | D32-D8     | 878 KB     | Y                            | 3     |

| \$FFFF0000-\$FFFFFFF  | VMEbus A16                                 | D32/D16    | 64 KB      | ?                            | 2, 4  |

# Notes

- 1. Reset enables the decoder for this space of the memory map so that it will decode address spaces \$FF800000 \$FF9FFFFF and \$00000000 \$003FFFFF. The decode at 0 must be disabled in the MCchip before DRAM is enabled. DRAM is enabled with the DRAM Control Register at address \$FFF42048, bit 24. PROM/Flash is disabled at the low address space with PROM Control Register at address \$FFF42040, bit 20.

- 2. This area is user-programmable. The DRAM and SRAM decoder is programmed in the MCchip, the local-to-VMEbus decoders are programmed in the VMEchip2, and the IP memory space is programmed in the IPIC.

- 3. Size is approximate.

- 4. Cache inhibit depends on devices in area mapped.

3-4 User's Manual