# MVME162LX

# **Embedded Controller**

# **Programmer's Reference Guide**

(MVME162LXPG/D1)

### Notice

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

No part of this material may be reproduced or copied in any tangible medium, or stored in a retrieval system, or transmitted in any form, or by any means, radio, electronic, mechanical, photocopying, recording or facsimile, or otherwise, without the prior written permission of Motorola, Inc.

It is possible that this publication may contain reference to, or information about Motorola products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

### **Restricted Rights Legend**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282

### Preface

The *MVME162LX Embedded Controller Programmer's Reference Guide* provides board level information, and detailed ASIC chip information including register bit descriptions for the MVME162LX Embedded Controller.

This manual is intended for anyone who wants to program these boards in order to design OEM systems, supply additional capability to an existing compatible system, or work in a lab environment for experimental purposes.

A basic knowledge of computers, and digital logic is assumed.

To use this manual, you should be familiar with the publications listed in the *Related Documentation* section in Chapter 1 of this manual.

The following conventions are used in this document:

#### bold

is used for user input that you type just as it appears. Bold is also used for commands, options and arguments to commands, and names of programs, directories, and files.

#### italic

is used for names of variables to which you assign values. Italic is also used for comments in screen displays and examples.

courier

is used for system output (e.g., screen displays, reports), examples, and system prompts.

#### <RETURN>

represents the carriage return key.

#### CTRL

represents the Control key. Execute control characters by pressing the **CTRL** key and the letter simultaneously, e.g., **CTRL-d**.

Motorola<sup>®</sup> and the Motorola symbol are registered trademarks of Motorola, Inc.

Delta Series, SYSTEM V/68, VME module, VME system, and 162Bug are trademarks of Motorola, Inc.

IndustryPack and IP are trademarks of GreenSpring Computers, Inc.

Timekeeper and Zeropower are trademarks of Thompson Components.

All other products mentioned in this document are trademarks or registered trademarks of their respective holders.

© Copyright Motorola 1993

All Rights Reserved

### Printed in the United States of America

November 1993

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the documentation for this product, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A Computing Device pursuant to Subpart J of Part 15 of FCC rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user, at the user's own expense, will be required to take whatever measures necessary to correct the interference.

### Safety Summary Safety Depends On You

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the equipment. Motorola, Inc. assumes no liability for the customer's failure to comply with these requirements.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. The equipment is supplied with a three-conductor ac power cable. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter, with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards.

## Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment constitutes a definite safety hazard.

# Keep Away From Live Circuits.

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified maintenance personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

## Do Not Service or Adjust Alone.

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

# Use Caution When Exposing or Handling the CRT.

Breakage of the Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, avoid rough handling or jarring of the equipment. Handling of the CRT should be done only by qualified maintenance personnel using approved safety mask and gloves.

# Do Not Substitute Parts or Modify Equipment.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that safety features are maintained.

## **Dangerous Procedure Warnings.**

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

# Contents

### **BOARD LEVEL HARDWARE DESCRIPTION**

| Introduction                              | 1-1  |

|-------------------------------------------|------|

| Overview                                  | 1-1  |

| Related Documentation                     | 1-3  |

| Requirements                              | 1-4  |

| Features                                  | 1-5  |

| Manual Terminology                        |      |

| Block Diagram                             |      |

| Functional Description                    |      |

| Front Panel Switches and Indicators       |      |

| Data Bus Structure                        |      |

| MC68040 or MC68LC040 MPU                  |      |

| MC68xx040 Cache                           |      |

| No VMEbus Interface Option                |      |

| Memory Options                            |      |

| DRAM Options                              | 1-11 |

| SRAM Options                              |      |

| About the Batteries                       | 1-12 |

| EPROM and Flash Memory                    | 1-13 |

| Battery Backed Up RAM and Clock           |      |

| VMEbus Interface and VMEchip2             |      |

| I/O Interfaces                            |      |

| Serial Communications Interface           | 1-14 |

| IndustryPack (IP) Interfaces              | 1-15 |

| Ethernet Interface                        | 1-15 |

| SCSI Interface                            | 1-16 |

| SCSI Termination                          | 1-16 |

| Local Resources                           | 1-16 |

| Programmable Tick Timers                  | 1-16 |

| Watchdog Timer                            | 1-17 |

| Software-Programmable Hardware Interrupts |      |

| Local Bus Timeout                         |      |

| Local Bus Arbiter                         | 1-18 |

| Connectors                                | 1-18 |

|                                           |      |

| Fuses                                             | 1-18 |

|---------------------------------------------------|------|

| Configuration Jumpers                             | 1-19 |

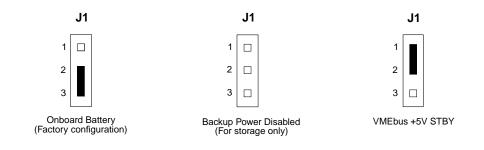

| System Controller Select Header (J1)              | 1-19 |

| General-Purpose Readable Jumpers Header (J11)     | 1-20 |

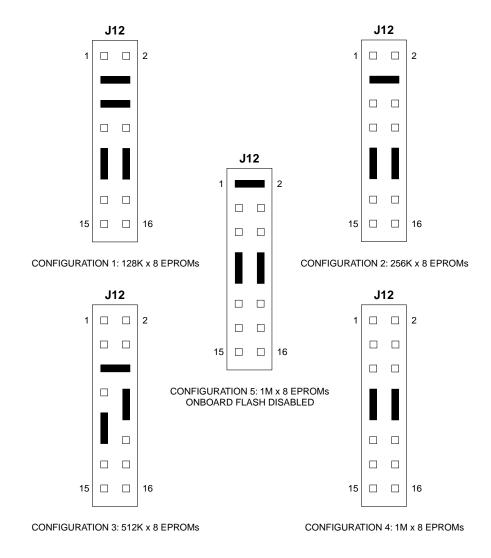

| EPROM/Flash Configuration Header (J12)            | 1-21 |

| SRAM Backup Power Source Select Headers (J13, J1) |      |

| SCSI Terminator Enable Header J14                 |      |

| Memory Maps                                       |      |

| Local Bus Memory Map                              | 1-27 |

| Normal Address Range                              |      |

| Detailed I/O Memory Maps                          | 1-32 |

| BBRAM, TOD Clock Memory Map                       |      |

| Interrupt Acknowledge Map                         |      |

| VMEbus Memory Map                                 |      |

| VMEbus Accesses to the Local Bus                  |      |

| VMEbus Short I/O Memory Map                       |      |

| Software Support Considerations.                  |      |

| Interrupts                                        | 1-50 |

| Cache Coherency                                   | 1-51 |

| Sources of Local BERR*                            | 1-51 |

| Local Bus Timeout                                 |      |

| VMEbus Access Timeout                             | 1-51 |

| VMEbus BERR*                                      | 1-52 |

| Local DRAM Parity Error                           | 1-52 |

| VMEchip2                                          | 1-52 |

| Bus Error Processing                              | 1-52 |

| Description of Error Conditions on the MVME162LX  | 1-52 |

| MPU Parity Error                                  |      |

| MPU Offboard Error                                |      |

| MPU TEA - Cause Unidentified                      | 1-53 |

| MPU Local Bus Timeout                             | 1-54 |

| DMAC VMEbus Error                                 | 1-54 |

| DMAC Parity Error                                 |      |

| DMAC Offboard Error                               |      |

| DMAC LTO Error                                    | 1-55 |

| DMAC TEA - Cause Unidentified                     | 1-55 |

| LAN Parity Error                                  |      |

| LAN Offboard Error                                | 1-56 |

| LAN LTO Error                                                |            |

|--------------------------------------------------------------|------------|

| SCSI Parity Error                                            | 1-57       |

| SCSI Offboard Error                                          |            |

| SCSI LTO Error                                               |            |

| Example of the Proper Use of Bus Timers                      | 1-58       |

| MVME162LX MC68040 Indivisible Cycles                         | 1-59       |

| Illegal Accesses to the IP Modules from an External VMEbus M | aster 1-60 |

### VMEchip2

| Introduction                                               | 2-1  |

|------------------------------------------------------------|------|

| Summary of Major Features                                  | 2-1  |

| Functional Blocks                                          |      |

| Local Bus to VMEbus Interface                              | 2-5  |

| Local Bus to VMEbus Requester                              | 2-7  |

| VMEbus to Local Bus Interface                              | 2-8  |

| Local Bus to VMEbus DMA Controller                         | 2-9  |

| No Address Increment DMA Transfers                         | 2-10 |

| DMAC VMEbus Requester                                      | 2-11 |

| Tick and Watchdog Timers                                   |      |

| Prescaler                                                  |      |

| Tick Timer                                                 | 2-13 |

| Watchdog Timer                                             | 2-13 |

| VMEbus Interrupter                                         |      |

| VMEbus System Controller                                   |      |

| Arbiter                                                    |      |

| IACK Daisy-Chain Driver                                    |      |

| Bus Timer                                                  | 2-15 |

| Reset Driver                                               |      |

| Local Bus Interrupter and Interrupt Handler                | 2-15 |

| Global Control and Status Registers                        |      |

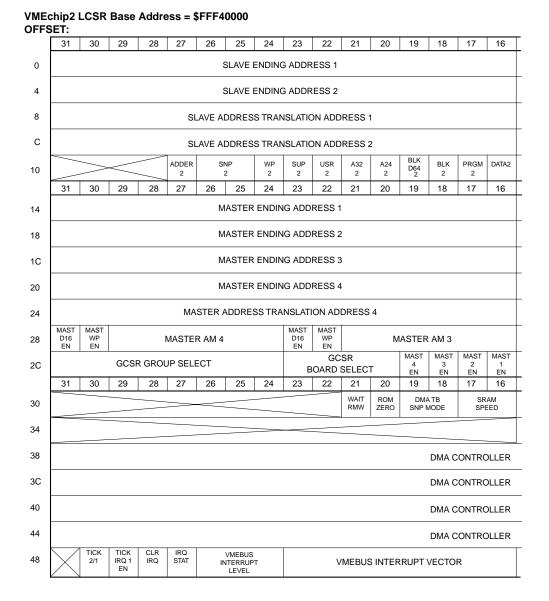

| LCSR Programming Model                                     |      |

| Programming the VMEbus Slave Map Decoders                  |      |

| VMEbus Slave Ending Address Register 1                     |      |

| VMEbus Slave Starting Address Register 1                   |      |

| VMEbus Slave Ending Address Register 2                     |      |

| VMEbus Slave Starting Address Register 2                   |      |

| VMEbus Slave Address Translation Address Offset Register 1 |      |

| VMEbus Slave Address Translation Select Register 1         |      |

| VMEbus Slave Address Translation Address Offset Register 2     | . 2-27 |

|----------------------------------------------------------------|--------|

| VMEbus Slave Address Translation Select Register 2             | . 2-27 |

| VMEbus Slave Write Post and Snoop Control Register 2           | . 2-28 |

| VMEbus Slave Address Modifier Select Register 2                | . 2-29 |

| VMEbus Slave Write Post and Snoop Control Register 1           | . 2-30 |

| VMEbus Slave Address Modifier Select Register 1                | . 2-31 |

| Programming the Local Bus to VMEbus Map Decoders               |        |

| Local Bus Slave (VMEbus Master) Ending Address Register 1      |        |

| Local Bus Slave (VMEbus Master) Starting Address Register 1    | . 2-34 |

| Local Bus Slave (VMEbus Master) Ending Address Register 2      |        |

| Local Bus Slave (VMEbus Master) Starting Address Register 2    | . 2-35 |

| Local Bus Slave (VMEbus Master) Ending Address Register 3      | . 2-35 |

| Local Bus Slave (VMEbus Master) Starting Address Register 3    | . 2-35 |

| Local Bus Slave (VMEbus Master) Ending Address Register 4      | . 2-36 |

| Local Bus Slave (VMEbus Master) Starting Address Register 4    | . 2-36 |

| Local Bus Slave (VMEbus Master) Address Translation Address    |        |

| ister 4                                                        | . 2-36 |

| Local Bus Slave (VMEbus Master) Address Translation Select Reg | ister  |

| 4                                                              |        |

| Local Bus Slave (VMEbus Master) Attribute Register 4           | . 2-37 |

| Local Bus Slave (VMEbus Master) Attribute Register 3           | . 2-38 |

| Local Bus Slave (VMEbus Master) Attribute Register 2           |        |

| Local Bus Slave (VMEbus Master) Attribute Register 1           |        |

| VMEbus Slave GCSR Group Address Register                       |        |

| VMEbus Slave GCSR Board Address Register                       | . 2-41 |

| Local Bus To VMEbus Enable Control Register                    | . 2-42 |

| Local Bus To VMEbus I/O Control Register                       | . 2-43 |

| ROM Control Register                                           | . 2-44 |

| LCSR Programming Model                                         |        |

| Programming the VMEchip2 DMA Controller                        | . 2-45 |

| DMAC Registers                                                 |        |

| PROM Decoder, SRAM and DMA Control Register                    | . 2-47 |

| Local Bus To VMEbus Requester Control Register                 |        |

| DMAC Control Register 1 (bits 0-7)                             | . 2-49 |

| DMAC Control Register 2 (bits 8-15)                            | . 2-50 |

| DMAC Control Register 2 (bits 0-7)                             | . 2-51 |

| DMAC Local Bus Address Counter                                 | . 2-52 |

| DMAC VMEbus Address Counter                                    | . 2-52 |

| DMAC Byte Counter                                           | .2-53 |

|-------------------------------------------------------------|-------|

| Table Address Counter                                       | .2-53 |

| VMEbus Interrupter Control Register                         | .2-54 |

| VMEbus Interrupter Vector Register                          |       |

| MPU Status and DMA Interrupt Count Register                 |       |

| DMAC Status Register                                        |       |

| Programming the Tick and Watchdog Timers                    | .2-57 |

| VMEbus Arbiter Timeout Control Register                     | .2-57 |

| DMAC Ton/Toff Timers and VMEbus Global Timeout Control      | Reg-  |

|                                                             |       |

| VME Access, Local Bus and Watchdog Timeout Control Register | r2-59 |

| Prescaler Control Register                                  |       |

| Tick Timer 1 Compare Register                               | .2-61 |

| Tick Timer 1 Counter                                        |       |

| Tick Timer 2 Compare Register                               | .2-62 |

| Tick Timer 2 Counter                                        |       |

| Board Control Register                                      | .2-63 |

| Watchdog Timer Control Register                             |       |

| Tick Timer 2 Control Register                               | .2-65 |

| Tick Timer 1 Control Register                               | .2-66 |

| Prescaler Counter                                           | .2-66 |

| Programming the Local Bus Interrupter                       |       |

| Local Bus Interrupter Status Register (bits 24-31)          | .2-69 |

| Local Bus Interrupter Status Register (bits 16-23)          | .2-70 |

| Local Bus Interrupter Status Register (bits 8-15)           | .2-71 |

| Local Bus Interrupter Status Register (bits 0-7)            | .2-72 |

| Local Bus Interrupter Enable Register (bits 24-31)          | .2-73 |

| Local Bus Interrupter Enable Register (bits 16-23)          | .2-74 |

| Local Bus Interrupter Enable Register (bits 8-15            | .2-75 |

| Local Bus Interrupter Enable Register (bits 0-7)            | .2-76 |

| Software Interrupt Set Register (bits 8-15)                 | .2-77 |

| Interrupt Clear Register (bits 24-31)                       | .2-78 |

| Interrupt Clear Register (bits 16-23)                       | .2-79 |

| Interrupt Clear Register (bits 8-15)                        | .2-80 |

| Interrupt Level Register 1 (bits 24-31)                     | .2-81 |

| Interrupt Level Register 1 (bits 16-23)                     | .2-81 |

| Interrupt Level Register 1 (bits 8-15)                      | .2-82 |

| Interrupt Level Register 1 (bits 0-7)                       | .2-82 |

| Interrupt Level Register 2 (bits 24-31) |              |

|-----------------------------------------|--------------|

| Interrupt Level Register 2 (bits 16-23) |              |

| Interrupt Level Register 2 (bits 8-15)  |              |

| Interrupt Level Register 2 (bits 0-7)   |              |

| Interrupt Level Register 3 (bits 24-31) |              |

| Interrupt Level Register 3 (bits 16-23) |              |

| Interrupt Level Register 3 (bits 8-15)  |              |

| Interrupt Level Register 3 (bits 0-7)   |              |

| Interrupt Level Register 4 (bits 24-31) |              |

| Interrupt Level Register 4 (bits 16-23) |              |

| Interrupt Level Register 4 (bits 8-15)  |              |

| Interrupt Level Register 4 (bits 0-7)   | 2-88         |

| Vector Base Register                    |              |

| I/O Control Register 1                  |              |

| I/O Control Register 2                  |              |

| I/O Control Register 3                  |              |

| Miscellaneous Control Register          |              |

| GCSR Programming Model                  |              |

| Programming the GCSR                    | 2-95<br>2_96 |

| VMEchip2 Revision Register              |              |

| VMEchip2 ID Register                    |              |

|                                         |              |

| VMEchip2 LM/SIG Register                |              |

| VMEchip2 Board Status/Control Register  |              |

| General Purpose Register 0              |              |

| General Purpose Register 1              |              |

| General Purpose Register 2              |              |

| General Purpose Register 3              |              |

| General Purpose Register 4              |              |

| General Purpose Register 5              | 2-102        |

| 1 0                                     |              |

# MCchip

| Introduction              |  |

|---------------------------|--|

| Summary of Major Features |  |

| Functional Description    |  |

| MCchip Initialization     |  |

| Flash and PROM Interface  |  |

| BBRAM Interface           |  |

| 82596CA LAN Interface     |  |

|                           |  |

| MPU Port and MPU Channel Attention               | 3-3  |

|--------------------------------------------------|------|

| MC68040-Bus Master Support for 82596CA           | 3-3  |

| LANC Bus Error                                   |      |

| LANC Interrupt                                   |      |

| 53C710 SCSI Controller Interface                 |      |

| SRAM Memory Controller                           | 3-5  |

| DRAM Memory Controller                           | 3-5  |

| Z85230 SCC Interface                             | 3-6  |

| Tick Timers                                      | 3-6  |

| Watchdog Timer                                   | 3-6  |

| Local Bus Timer                                  |      |

| Memory Map of the MCchip Registers               | 3-7  |

| Programming Model                                | 3-9  |

| MCchip ID Register                               | 3-9  |

| MCchip Revision Register                         | 3-10 |

| General Control Register                         | 3-10 |

| Interrupt Vector Base Register                   | 3-11 |

| Programming the Tick Timers                      | 3-13 |

| Tick Timer 1 and 2 Compare and Counter Registers | 3-13 |

| LSB Prescaler Count Register                     |      |

| Prescaler Clock Adjust Register                  |      |

| Tick Timer 1 and 2 Control Registers             | 3-16 |

| Tick Timer Interrupt Control Registers           | 3-17 |

| DRAM Parity Error Interrupt Control Register     |      |

| SCC Interrupt Control Register                   | 3-20 |

| Tick Timer 3 and 4 Control Registers             | 3-21 |

| DRAM and SRAM Memory Controller Registers        | 3-22 |

| DRAM Space Base Address Register                 | 3-22 |

| SRAM Space Base Address Register                 |      |

| DRAM Space Size Register                         |      |

| DRAM/SRAM Options Register                       |      |

| SRAM Space Size Register                         |      |

| LANC Error Status Register                       |      |

| 82596CA LANC Interrupt Control Register          | 3-27 |

| LANC Bus Error Interrupt Control Register        | 3-28 |

| SCSI Error Status Register                       | 3-29 |

| General Purpose Inputs Register                  |      |

| MVME162 Version Register                         | 3-31 |

| SCSI Interrupt Control Register                  |  |

|--------------------------------------------------|--|

| Tick Timer 3 and 4 Compare and Counter Registers |  |

| Bus Clock Register                               |  |

| PROM Access Time Control Register                |  |

| Flash Access Time Control Register               |  |

| ABORT Switch Interrupt Control Register          |  |

| RESET Switch Control Register                    |  |

| Watchdog Timer Control Register                  |  |

| Access and Watchdog Time Base Select Register    |  |

| DRAM Control Register                            |  |

| MPU Status Register                              |  |

| 32-bit Prescaler Count Register                  |  |

### MCECC

| Introduction                                                      | 4-1 |

|-------------------------------------------------------------------|-----|

| Features                                                          | 4-1 |

| Functional Description                                            | 4-1 |

| General Description                                               | 4-2 |

| Performance                                                       | 4-2 |

| Cache Coherency                                                   | 4-3 |

| ECC                                                               |     |

| Cycle Types                                                       | 4-4 |

| Error Reporting                                                   |     |

| Single Bit Error (Cycle Type = Burst Read or Non-Burst Read)      | 4-5 |

| Double Bit Error (Cycle Type = Burst Read or Non-Burst Read)      | 4-5 |

| Triple (or Greater) Bit Error (Cycle Type = Burst Read or Non-Bur | st  |

| Read)                                                             |     |

| Cycle Type = Burst Write                                          |     |

| Single Bit Error (Cycle Type = Non-Burst Write)                   | 4-5 |

| Double Bit Error (Cycle Type = Non-Burst Write)                   | 4-6 |

| Triple (or Greater) Bit Error (Cycle Type = Non-Burst Write)      | 4-6 |

| Single Bit Error (Cycle Type = Scrub)                             |     |

| Double Bit Error (Cycle Type = Scrub)                             | 4-6 |

| Triple (or Greater) Bit Error (Cycle Type = Scrub)                | 4-6 |

| Error Logging                                                     | 4-7 |

| Scrub                                                             | 4-7 |

| Refresh                                                           |     |

| Arbitration                                                       | 4-7 |

| Chip Defaults                        | 4-8  |

|--------------------------------------|------|

| Programming Model                    | 4-9  |

| Chip ID Register                     | 4-12 |

| Chip Revision Register               | 4-12 |

| Memory Configuration Register        | 4-13 |

| Dummy Register 0                     | 4-14 |

| Dummy Register 1                     | 4-14 |

| Base Address Register                | 4-15 |

| DRAM Control Register                | 4-15 |

| BCLK Frequency Register              | 4-17 |

| Data Control Register                |      |

| Scrub Control Register               |      |

| Scrub Period Register Bits 15-8      | 4-21 |

| Scrub Period Register Bits 7-0       | 4-21 |

| Chip Prescaler Counter               | 4-21 |

| Scrub Time On/Time Off Register      | 4-22 |

| Scrub Prescaler Counter (Bits 21-16) |      |

| Scrub Prescaler Counter (Bits 15-8)  |      |

| Scrub Prescaler Counter (Bits 7-0)   |      |

| Scrub Timer Counter (Bits 15-8)      |      |

| Scrub Timer Counter (Bits 7-0)       |      |

| Scrub Address Counter (Bits 26-24)   |      |

| Scrub Address Counter (Bits 23-16)   |      |

| Scrub Address Counter (Bits 15-8)    | 4-25 |

| Scrub Address Counter (Bits 7-4)     | 4-25 |

| Error Logger Register                |      |

| Error Address (Bits 31-24)           |      |

| Error Address (Bits 23-16)           | 4-27 |

| Error Address Bits (15-8)            | 4-27 |

| Error Address Bits (7-4)             | 4-27 |

| Error Syndrome Register              | 4-28 |

| Defaults Register 1                  | 4-28 |

| Defaults Register 2                  | 4-30 |

| Initialization                       | 4-31 |

| Syndrome Decode                      | 4-32 |

### IPIC

| Introduction                                                     | 5-1      |

|------------------------------------------------------------------|----------|

| Features                                                         | 5-1      |

| Functional Description                                           | 5-2      |

| General Description                                              | 5-2      |

| Performance                                                      | 5-2      |

| Cache Coherency                                                  | 5-2      |

| Error Reporting                                                  | 5-2      |

| Interrupts                                                       | 5-3      |

| Overall Memory Map                                               | 5-4      |

| Programming Model                                                | 5-5      |

| Chip ID Register                                                 | 5-8      |

| Chip Revision Register                                           | 5-8      |

| IP_a, IP_b, IP_c, IP_d Memory Base Address Registers             | 5-8      |

| IP_a or Double Size IP_ab Memory Base Address Registers          | 5-9      |

| IP_b Memory Base Address Registers                               | 5-9      |

| IP_c or Double Size IP_cd Memory Base Address Registers          |          |

| IP_d Memory Base Address Registers                               |          |

| IP_a, IP_b, IP_c, IP_d Memory Size Registers                     |          |

| IP_a, IP_b, IP_c, and IP_d; IRQ0 and IRQ1 Interrupt Control Regi | sters.5- |

| 11                                                               |          |

| IP_a, IP_b, IP_c, and IP_d; General Control Registers            | 5-12     |

| IP RESET Register                                                | 5-14     |

| Local Bus to IndustryPack Addressing                             | 5-15     |

| 8-Bit Memory Space                                               | 5-15     |

| 16-Bit Memory Space                                              | 5-15     |

| 32-Bit Memory Space                                              | 5-16     |

| IP_a I/O Space                                                   | 5-17     |

| IP_ab I/O Space                                                  | 5-17     |

| IP_a ID Space                                                    | 5-18     |

| IP to Local Bus Data Routing                                     | 5-19     |

|                                                                  | E 10     |

| Memory Space Accesses<br>I/O and ID Space Accesses               |          |

| SERIAL PORT CONNECTIONS           |     |

|-----------------------------------|-----|

| Introduction                      | 6-1 |

|                                   |     |

| USING INTERRUPTS ON THE MVME162LX |     |

| Introduction                           | A-1 |

|----------------------------------------|-----|

| VMEchip2 Tick Timer 1 Periodic Interru |     |

| Figure 1-1. MVME162LX Block Diagram  | . 1-7 |

|--------------------------------------|-------|

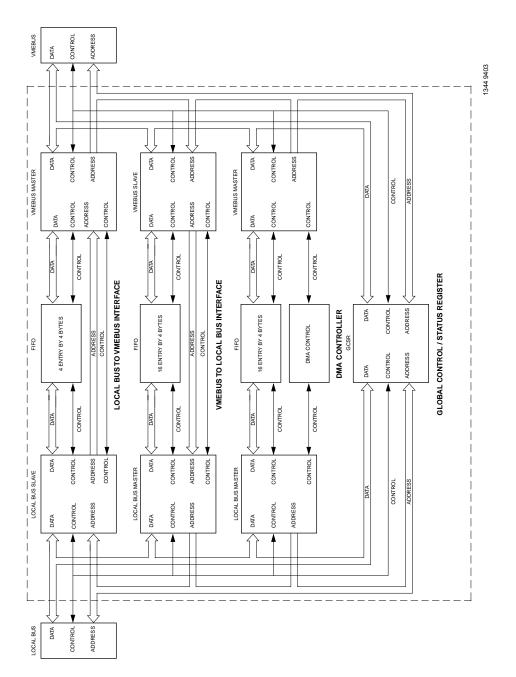

| Figure 2-1. VMEchip2 Block Diagram   |       |

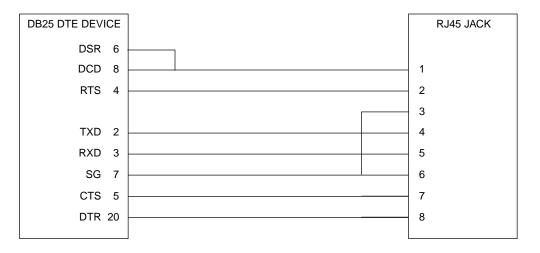

| Figure 6-1. DB25-DTE-to-RJ45 Adapter |       |

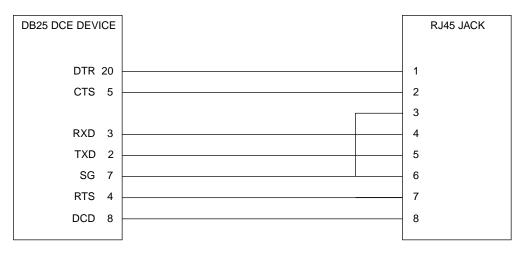

| Figure 6-2. DB25-DCE-to-RJ45 Adapter |       |

| Table 1-1. Redundant Functions in the VMEchip2 and MCchip              | 1-10     |

|------------------------------------------------------------------------|----------|

| Table 1-2. Local Bus Arbitration Priority                              | 1-18     |

| Table 1-3. EPROM/Flash Mapping—128K x 8 EPROMs                         | 1-22     |

| Table 1-4. EPROM/Flash Mapping —256K x 8 EPROMs                        | 1-22     |

| Table 1-5. EPROM/Flash Mapping—512K x 8 EPROMs                         | 1-23     |

| Table 1-6. EPROM/Flash Mapping—1M x 8 EPROMs                           | 1-23     |

| Table 1-7. EPROM/Flash Mapping—1M x 8 EPROMs, On-Board Flash           | Disabled |

| 1-24                                                                   |          |

| Table 1-8. Local Bus Memory Map                                        | 1-28     |

| Table 1-9. Local I/O Devices Memory Map                                | 1-30     |

| Table 1-10. VMEchip2 Memory Map (sheet 1 of 3)                         | 1-33     |

| Table 1-10. VMEchip2 Memory Map (sheet 2 of 3)                         | 1-36     |

| Table 1-10. VMEchip2 Memory Map (sheet 3 of 3)                         | 1-38     |

| Table 1-11. MCchip Register Map                                        |          |

| Table 1-12. MCECC Internal Register Memory Map                         | 1-40     |

| Table 1-13. IPIC Overall Memory Map                                    |          |

| Table 1-14. IPIC Memory Map - Control and Status Registers (Sheet 1 of | £ 2)1-42 |

| Table 1-14. IPIC Memory Map - Control and Status Registers (Sheet 2 of |          |

| Table 1-15. Z85230 SCC Register Addresses                              | 1-44     |

| Table 1-16. 82596CA Ethernet LAN Memory Map                            | 1-44     |

| Table 1-17. 53C710 SCSI Memory Map                                     |          |

| Table 1-18. MK48T08 BBRAM, TOD Clock Memory Map                        | 1-46     |

| Table 1-19. BBRAM Configuration Area Memory Map                        | 1-46     |

| Table 1-20. TOD Clock Memory Map                                       | 1-46     |

| Table 2-1. VMEchip2 Memory Map - LCSR Summary                          |          |

| Table 2-2. DMAC Command Table Format                                   |          |

| Table 2-3. Local Bus Interrupter Summary                               |          |

| Table 2-4. VMEchip2 Memory Map - GCSR Summary                          | 2-97     |

| Table 3-1. DRAM Performance                                            |          |

| Table 3-2. MCchip Register Map                                         |          |

| Table 3-3. Interrupt Vector Base Register Encoding and Priority        | 3-12     |

| Table 3-4. DRAM Size Control Bit Encoding                              | 3-23     |

| Table 3-5. DRAM Size Control Bit Encoding                              | 3-24     |

| Table 3-6. SRAM Size Control Bit Encoding                              | 3-24     |

|                                                                        |          |

| Table 3-7. SRAM Size Control Bit Encoding                                | 3-25 |

|--------------------------------------------------------------------------|------|

| Table 4-1. MCECC Specifications                                          | 4-3  |

| Table 4-2. MCECC Internal Register Memory Map, Part 1                    | 4-10 |

| Table 4-3. MCECC Internal Register Memory Map, Part 2                    | 4-11 |

| Table 5-1. IPIC Overall Memory Map                                       | 5-4  |

| Table 5-2. IPIC Memory Map - Control and Status Registers (Sheet 1 of 2) | 5-6  |

| Table 5-2. IPIC Memory Map - Control and Status Registers (Sheet 2 of 2) | 5-7  |

# BOARD LEVEL HARDWARE DESCRIPTION

# Introduction

This manual provides programming information for the MVME162LX Embedded Controller. Extensive programming information is provided for the Application-Specific Integrated Circuit (ASIC) devices used on the board. Reference information is included for the Large Scale Integration (LSI) devices used on the board and sources for additional information are provided.

This chapter describes the board level hardware features of the MVME162LX Embedded Controller. The chapter is organized with a board level overview and features list in this introduction, followed by a more detailed hardware functional description. Front panel switches and indicators are included in the detailed hardware functional description. Memory maps are next, and the chapter closes with some general software considerations such as cache coherency, interrupts, and bus errors.

All programmable registers in the MVME162LX that reside in ASICs are covered in the chapters on those ASICs. Chapter 2 covers the VMEchip2, Chapter 3 covers the MCchip, Chapter 4 covers the MCECC, and Chapter 5 covers the IPIC. Chapter 6 covers certain serial port connections. Appendix A details using interrupts. For those interested in programmable register bit definitions and less interested in hardware functionality, focus on Chapters 2, 3, 4, and 5. In some cases, however, Chapter 1 gives related background information.

### Overview

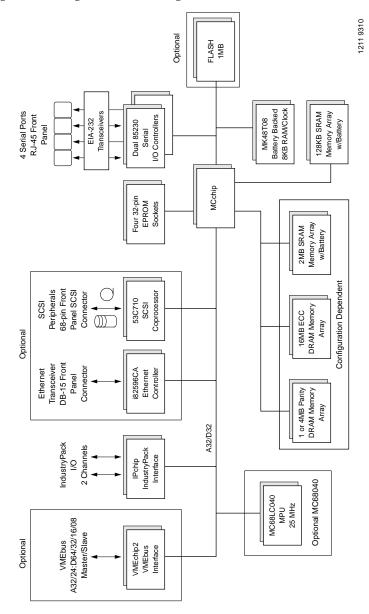

The MVME162LX is based on the MC68040 or MC68LC040 microprocessor. Various versions of the MVME162LX have 1 or 4 MB of parity-protected DRAM or 16 MB of ECC-protected DRAM,128 KB of SRAM (with battery backup) or 2 MB SRAM on a mezzanine board, time of day clock (with battery backup), an optional LAN Ethernet transceiver interface, four serial ports with EIA-232-D interface, six tick timers with watchdog timer(s), four EPROM sockets, 1 MB Flash memory (one Flash device), two IndustryPack (IP) interfaces, optional SCSI bus interface with DMA, optional VMEbus interface (local bus to VMEbus/VMEbus to local bus, with A16/A24/A32, D8/D16/D32 bus widths and a VMEbus system controller). 1

The I/O on the MVME162LX is connected to the front panel by connectors. The MVME162LX uses no transition boards.

The I/O connection for the serial ports on the MVME162LX is provided by four RJ45 front panel I/O connectors. (Refer to the section on the Serial Communications Interface, later in this chapter, for more information.)

The VMEbus interface is provided by an ASIC called the VMEchip2. The VMEchip2 includes two tick timers, a watchdog timer, programmable map decoders for the master and slave interfaces, and a VMEbus to/from local bus DMA controller, a VMEbus to/from local bus non-DMA programmed access interface, a VMEbus interrupter, a VMEbus system controller, a VMEbus interrupt handler, and a VMEbus requester.

Processor-to-VMEbus transfers can be D8, D16, or D32. VMEchip2 DMA transfers to the VMEbus, however, can be D16, D32, D16/BLT, D32/BLT, or D64/MBLT.

The MCchip ASIC provides four tick timers, the interface to the LAN chip, SCSI chip, serial port chip, BBRAM, EPROM/Flash, DRAM and SRAM.

The MCECC memory controller ASIC provides the programmable interface for the ECC-protected 16 MB DRAM mezzanine board.

The IndustryPack Interface Controller (IPIC) ASIC provides control and status information for up to two single size IndustryPacks (IPs) or one double size IP that can be plugged into the MVME162LX main module.

### **Related Documentation**

The following publications are applicable to the MVME162LX and may provide additional helpful information. If not shipped with this product, they may be purchased by contacting your local Motorola sales office. Non-Motorola documents may be obtained from the sources listed.

| Document Title                                                                            | Motorola<br>Publication Number |  |

|-------------------------------------------------------------------------------------------|--------------------------------|--|

| MVME162LX Embedded Controller User's Manual                                               | MVME162LX/D                    |  |

| MVME162LX Embedded Controller Installation Guide                                          | MVME162LXIG/D                  |  |

| MVME162LX Embedded Controller Programmer's Reference Guide                                | MVME162LXPG/D                  |  |

| MVME162Bug Diagnostics User's Manual                                                      | V162DIAA/UM                    |  |

| Debugging Package for Motorola 68K CISC CPUs User's Manual                                | 68KBUG1/D<br>and<br>68KBUG2/D  |  |

| Single Board Computers SCSI Software User's Manual                                        | SBCSCSI                        |  |

| M68040 Microprocessors User's Manual                                                      | M68040UM                       |  |

| M68000 Family Reference Manual                                                            | M68000FR                       |  |

| MVME1x7 Data Sheet Package (for use with the MVME162[LX] and the MVME166/MVME167/MVME187) | 68-1X7DS                       |  |

Notes

Although not shown in the above list, each Motorola Computer Group manual publication number is suffixed with characters which represent the revision level of the document, such as "/D2" (the second revision of a manual); a supplement bears the same number as a manual but has a suffix such as "/D2A1" (the first supplement to the second edition of the manual). 1

The following publications are available from the sources indicated.

*Versatile Backplane Bus: VMEbus, ANSI/IEEE Std 1014-1987,* The Institute of Electrical and Electronics Engineers, Inc., 345 East 47th Street, New York, NY 10017 (VMEbus Specification). This is also available as *Microprocessor system bus for 1 to 4 byte data, IEC 821 BUS,* Bureau Central de la Commission Electrotechnique Internationale; 3, rue de Varembé, Geneva, Switzerland.

ANSI Small Computer System Interface-2 (SCSI-2), Draft Document X3.131-198X, Revision 10c; Global Engineering Documents, P.O. Box 19539, Irvine, CA 92714.

*IndustryPack Logic Interface Specification,* Revision 1.0; GreenSpring Computers, Inc., 1204 O'Brien Drive, Menlo Park, CA 94025.

82596CA Local Area Network Coprocessor Data Sheet, Order Number 290218; and 82596 User's Manual, Order Number 296853-001; Intel Corporation, Literature Sales, P.O. Box 58130, Santa Clara, CA 95052-8130.

*NCR 53C710 SCSI I/O Processor, Data Manual Document #SCSIP-53C710;* NCR Corporation, Microelectronics Products Division, Colorado Springs, CO.

MK48T08(B) Timekeeper<sup>™</sup> and 8Kx8 Zeropower<sup>™</sup> RAM data sheet in *Static RAMs Databook*, Order Code DBSRAM71; SGS-THOMPSON Microelectronics Group; North & South American Marketing Headquarters, 1000 East Bell Road, Phoenix, AZ 85022-2699.

Z85230 Serial Communications Controller Data Sheet; Zilog Inc., 210 Hacienda Avenue, Campbell, CA 95008-6609.

28F008SA FLASH Memory Data Sheet, Order Number 290435-001; Intel Literature Sales, P.O. Box 7641, Mt. Prospect, IL 60056-7641.

### Requirements

These boards are designed to conform to the requirements of the following documents:

- □ VMEbus Specification (IEEE 1014-87)

- □ EIA-232-D Serial Interface Specification, EIA

- □ SCSI Specification, ANSI

- □ IndustryPack Specification, GreenSpring

### Features

- □ 25 MHzMC68040 or MC68LC040 Microprocessor

- □ 1 or 4 MB of DRAM with parity protection on a mezzanine module, or 16 MB ECC DRAM on a mezzanine board

- □ 128 KB of SRAM with battery backup, or 2 MB SRAM on a mezzanine board with battery backup

- □ Four JEDEC standard 32-pin DIP PROM sockets

- □ One Intel 28F008SA 1M x 8 Flash memory device with write protection. Optional

- □ Status LEDs for FAIL, RUN, SCON, and FUSES

- □ 8K by 8 Non-Volatile RAM (NVRAM) and time of day (TOD) clock with battery backup

- □ RESET and ABORT switches

- □ Four 32-bit Tick Timers and Watchdog Timer (in the MCchip ASIC) for periodic interrupts

- □ Two 32-bit Tick Timers and Watchdog Timer (in the VMEchip2 ASIC) for periodic interrupts

- □ Eight software interrupts (for MVME162LX versions that have the VMEchip2)

- **I** I/O

- Optional SCSI Bus interface with DMA

- Four serial ports with EIA-232-D interface (serial port controllers are the Z85230s

- Optional Ethernet transceiver interface with DMA

- Two IndustryPack interfaces

- □ VMEbus interface

- VMEbus system controller functions

- VMEbus interface to local bus (A24/A32, D8/D16/D32 (D8/D16/D32/D64 BLT) (BLT = Block Transfer)

- Local bus to VMEbus interface (A16/A24/A32, D8/D16/D32)

- VMEbus interrupter

- VMEbus interrupt handler

- Global CSR for interprocessor communications

- DMA for fast local memory VMEbus transfers (A16/A24/A32, D16/D32 (D16/D32/D64 BLT)

### **Manual Terminology**

Throughout this manual, a convention is used which precedes data and address parameters by a character identifying the numeric format as follows:

| \$ | dollar    | specifies a hexadecimal character |

|----|-----------|-----------------------------------|

| %  | percent   | specifies a binary number         |

| &  | ampersand | specifies a decimal number        |

For example, "12" is the decimal number twelve, and "\$12" is the decimal number eighteen.

Unless otherwise specified, all address references are in hexadecimal.

An asterisk (\*) following the signal name for signals which are level significant denotes that the signal is true or valid when the signal is low.

An asterisk (\*) following the signal name for signals which are edge significant denotes that the actions initiated by that signal occur on high to low transition.

In this manual, assertion and negation are used to specify forcing a signal to a particular state. In particular, assertion and assert refer to a signal that is active or true; negation and negate indicate a signal that is inactive or false. These terms are used independently of the voltage level (high or low) that they represent.

Data and address sizes are defined as follows:

- □ A byte is eight bits, numbered 0 through 7, with bit 0 being the least significant.

- □ A word is 16 bits, numbered 0 through 15, with bit 0 being the least significant.

- □ A longword is 32 bits, numbered 0 through 31, with bit 0 being the least significant.

The terms control bit and status bit are used extensively in this document. The term control bit is used to describe a bit in a register that can be set and cleared under software control. The term true is used to indicate that a bit is in the state that enables the function it controls. The term false is used to indicate that the bit is in the state that disables the function it controls. In all tables, the terms 0 and 1 are used to describe the actual value that should be written to the bit, or the value that it yields when read. The term status bit is used to describe a bit in a register that reflects a specific condition. The status bit can be read by software to determine operational or exception conditions.

1

# **Block Diagram**

Figure 1-1 is a general block diagram of the MVME162LX.

# **Functional Description**

This section contains a functional description of the major blocks on the MVME162LX Embedded Controller.

### **Front Panel Switches and Indicators**

There are switches and LEDs on the front panel of the MVME162LX. The switches are RESET and ABORT. The RESET switch resets all onboard devices and drives SYSRESET\* if the board is system controller. The RESET switch may be disabled by software. Refer to the MCchip description in Chapter 3.

When enabled by software, the ABORT switch generates an interrupt at a userprogrammable level. It is normally used to abort program execution and return to the 162Bug debugger. Refer to the MCchip description in Chapter 3 for more information.

There are four LEDs on the MVME162LX front panel: FAIL, RUN, SCON, and FUSES.

- □ FAIL LED (red). Lights when the BRDFAIL\* signal line is active or when the processor is halted. Part of DS1.

- RUN LED (green or amber). Lights when the local bus TIP\* signal line is low. This indicates one of the local bus masters is executing a local bus cycle. Part of DS1.

- □ SCON LED (green). Lights when the VMEchip2 in the MVME162LX is the VMEbus system controller. Part of DS2.

- □ FUSES LED (green). Lights when +5 Vdc, +12 Vdc, and -12 Vdc power is available to the LAN and SCSI interfaces and IP connectors. Part of DS2.

### **Data Bus Structure**

The local bus on the MVME162LX is a 32-bit synchronous bus that is based on the MC68040 bus, and supports burst transfers and snooping. The various local bus master and slave devices use the local bus to communicate. The local bus is arbitrated by priority type arbiter and the priority of the local bus masters from highest to lowest is: 82596CA LAN, 53C710 SCSI, VMEbus, and MPU. In the general case, any master can access any slave; however, not all combinations pass the common sense test. Refer to the specific section of this manual and to the user's guide for each device to determine its port size, data bus connection, and any restrictions that apply when accessing the device.

### MC68040 or MC68LC040 MPU

The MC68040 or MC68LC040 processor is used on the MVME162LX. The MC68040 has on-chip instruction and data caches and a floating point processor. The major difference between the two processors is that the MC68040 has a floating point coprocessor. Refer to the M68040 user's manual for more information.

### MC68xx040 Cache

The MVME162LX local bus masters (VMEchip2, MC68xx040, 53C710 SCSI controller, and 82596CA Ethernet controller) have programmable control of the snoop/caching mode. The MVME162LX local bus slaves which support MC68xx040 bus snooping are defined in the Local Bus Memory Map table later in this chapter.

### **No VMEbus Interface Option**

The MVME162LX can be operated as an embedded controller without the VMEbus interface. To support this feature, certain logic in the VMEchip2 has been duplicated in the MCchip. The following table defines the location of the redundant logic. This logic is inhibited in the MCchip if the VMEchip2 is present. The enables for these functions are controlled by software and MCchip hardware initialization.

| VMEchip2                  |               | MCchip       |               |       |

|---------------------------|---------------|--------------|---------------|-------|

| Address                   | Bit #         | Address      | Bit #         | Notes |

| \$FFF40060                | 28 - 24       | \$FFF42044   | 28 - 24       | 1,5   |

| \$FFF40060                | 22 - 19,17,16 | \$FFF42044   | 22 - 19,17,16 | 2,5   |

| \$FFF4004C                | 13 - 8        | \$FFF42044   | 13 - 8        | 3,5   |

| \$FFF40048                | 7             | \$FFF42048   | 8             | 4     |

| \$FFF40048                | 9             | \$FFF42048   | 9             | 4,5   |

| \$FFF40048                | 10            | \$FFF42048   | 10            | 4,5   |

| \$FFF40048                | 11            | \$FFF42048   | 11            | 4,5   |

| \$FFF40064                | 31 - 0        | \$FFF4204C   | 31 - 0        | 8     |

|                           |               | \$FFF42040   | 6 - 0         | 6     |

| \$FF800000-               | 31 - 0        | \$FF800000-  | 31 - 0        | 7     |

| \$FFBFFFFF                |               | \$FFBFFFFF   |               |       |

| \$FFE00000-<br>\$FFEFFFFF | 31 - 0        | programmable | 31 - 0        | 7     |

Table 1-1. Redundant Functions in the VMEchip2 and MCchip

### NOTES:

- 2. Watchdog timer control.

- 3. Access and watchdog timer parameters.

- 4. MPU TEA (bus error) status.

- 5. Bit numbering for VMEchip2 and MCchip have a one-to-one correspondence.

- 6. The ABORT switch interrupt control is implemented in the VMEchip2 but with a different bit organization. Refer to the VMEchip2 description in Chapter 2. The ABORT switch is wired to the MCchip and not the VMEchip2 in the MVME162LX implementation.

- 7. The SRAM and PROM decoder in the VMEchip2 (version 2) must be disabled by software before any accesses are made to these address spaces.

- 8. 32-bit prescaler. The prescaler can also be accessed at \$FFF40064 when the optional VMEbus is not enabled.

### **Memory Options**

The following memory options are used on the different versions of MVME162LX boards.

### **DRAM Options**

The MVME162LX offers three DRAM options: either 1 MB or 4 MB shared DRAM with programmable parity on a mezzanine module, or 16 MB ECC DRAM on a mezzanine board. The DRAM architecture is non-interleaved for 1MB and interleaved for 4MB and 16MB. Parity protection can be enabled with interrupts or bus exception when a parity error is detected. DRAM performance is specified in the section on the DRAM Memory Controller in the MCchip Programming Model in Chapter 3.

The DRAM map decoder can be programmed to accommodate different base address(es) and sizes of mezzanine boards. The onboard DRAM is disabled by a local bus reset and must be programmed before the DRAM can be accessed. Refer to the MCchip and MCECC descriptions in Chapters 3 and 4, respectively, for detailed programming information.

Most DRAM devices require some number of access cycles before the DRAMs are fully operational. Normally this requirement is met by the onboard refresh circuitry and normal DRAM initialization. However, software should insure a minimum of 10 initialization cycles are performed to each bank of RAM.

### SRAM Options

The MVME162LX provides 128 KB of 32-bit-wide onboard static RAM in a single non-interleaved architecture with onboard battery backup. As an option, a 2 MB SRAM mezzanine module with its own battery backup is available as well. When installed, the SRAM mezzanine disables the onboard SRAM to eliminate conflicts. Further details on SRAM configuration and specifics on SRAM performance can be found in the section on the SRAM Memory Controller in the MCchip Programming Model in Chapter 3. The SRAM arrays are not parity protected.

The battery backup function for the onboard SRAM and the mezzanine SRAM is provided by a Dallas DS1210S device that supports primary and secondary power sources. In the event of a main board power failure, the DS1210S checks power sources and switches to the source with the higher voltage.

If the voltage of the backup source is less than two volts, the DS1210S blocks the second memory cycle; this allows software to provide an early warning to avoid data loss. Because the second access may be blocked during a power failure, software should do at least two accesses before relying on the data. 1

The MVME162LX provides jumpers (on J13) that allow either power source of the DS1210S to be connected to the VMEbus +5V STDBY pin or to one cell of the onboard battery. For example, the primary system backup source may be a battery connected to the VMEbus +5V STDBY pin and the secondary source may be the onboard battery. If the system source should fail or the board is removed from the chassis, the onboard battery takes over.

**Caution** For proper operation of the SRAM, some jumper combination must be installed on the respective Backup Power Source Select Header. Refer to the *Configuration Jumpers* section later in this chapter. If one of the jumpers is used to select the battery, the battery must be installed on the MVME162LX. The SRAM may malfunction if inputs to the DS1210S are left unconnected.

The SRAM is controlled by the MCchip, and the access time is programmable. Refer to the MCchip description in Chapter 3 for more detail.

### About the Batteries

The power source for the onboard SRAM is a RAYOVAC FB1225 battery with two BR1225 type lithium cells which is socketed for easy removal and replacement. The power source for the mezzanine SRAM is a Sanyo CR2430 battery. Small capacitors are provided so that the batteries can be quickly replaced without data loss.

The lifetime of the batteries is very dependent on the ambient temperature of the board and the power-on duty cycle. The lithium batteries supplied on the MVME162LX and on the SRAM mezzanine module should provide at least two years of backup time with the board powered off and with an ambient temperature of 40° C. If the power-on duty cycle is 50% (the board is powered on half of the time), the battery lifetime is four years. At lower ambient temperatures, the backup time is significantly longer and may approach the shelf life of the battery.

When a board is stored, the battery should be disconnected to prolong battery life. This is especially important at high ambient temperatures. The MVME162LX is shipped with the batteries disconnected (i.e., with VMEbus +5V standby voltage selected as both primary and secondary power source). If you intend to use the battery as a power source, whether primary or secondary, it is necessary to reconfigure the jumpers on J13 before installing the module. Refer to *SRAM Backup Power Source Select Header J13* later in this chapter for available jumper configurations

1-12

The power leads from the battery are exposed on the solder side of the board. The board should not be placed on a conductive surface or stored in a conductive bag unless the battery is removed.

Lithium batteries incorporate inflammable materials such as lithium and organic solvents. If lithium batteries are mistreated or handled incorrectly, they may burst open and ignite, possible resulting in injury and/or fire. When dealing with lithium batteries, carefully follow the precautions listed below in order to prevent accidents.

- □ Do not short circuit.

- Do not disassemble, deform, or apply excessive pressure.

- Do not heat or incinerate.

- Do not apply solder directly.

- Do not use different models, or new and old batteries together.

- Do not charge.

- □ Always check proper polarity.

To remove the battery from the module, carefully pull the battery from the socket.

Before installing a new battery, ensure that the battery pins are clean. Note the battery polarity and press the battery into the socket. When the battery is in the socket, no soldering is required.

### EPROM and Flash Memory

The MVME162LX can be ordered with 1 MB of Flash memory and four EPROM sockets ready for the installation of the EPROMs, which may be ordered separately. Flash memory is a single Intel 28F008SA device organized in a 1Mbit x 8 configuration. The EPROM locations are standard JEDEC 32-pin DIP sockets accommodating four jumper-selectable densities (128 Kbit x 8; 256 Kbit X 8; 512 Kbit x 8; 1 Mbit x8). A jumper setting (GPIO3, pins 7-8 on J11), allows reset code to be fetched either from Flash memory (GPIO3 installed) or from EPROMs (GPIO3 removed).

### **Battery Backed Up RAM and Clock**

An MK48T08 RAM and clock chip is used on the MVME162LX. This chip provides a time-of-day clock, oscillator, crystal, power fail detection, memory write protection, 8KB of RAM, and a battery in one 28-pin package. The clock

provides seconds, minutes, hours, day, date, month, and year in BCD 24-hour format. Corrections for 28-, 29- (leap year), and 30-day months are automatically made. No interrupts are generated by the clock. Although the MK48T08 is an 8 bit device, the interface provided by the MCchip supports 8-, 16-, and 32-bit accesses to the MK48T08. Refer to the MCchip in Chapter 3 and to the MK48T08 data sheet for detailed programming and battery life information.

### VMEbus Interface and VMEchip2

The local bus to VMEbus interface, the VMEbus to local bus interface, and the DMA controller functions of the local VMEbus are provided by the VMEchip2. The VMEchip2 can also provide the VMEbus system controller functions. Refer to the VMEchip2 in Chapter 2 for detailed programming information.

Note that the ABORT switch logic in the VMEchip2 is not used. The GPI inputs to the VMEchip2 which are located at \$FFF40088 bits 7-0 are not used. The ABORT switch interrupt is integrated into the MCchip ASIC at location \$FFF42043. The GPI inputs are integrated into the MCchip ASIC at location \$FFF4202C bits 23-16.

### I/O Interfaces

The MVME162LX provides onboard I/O for many system applications. The I/O functions include serial ports and optional interfaces for IndustryPack (IP) modules, LAN Ethernet transceivers, and SCSI mass storage devices.

### **Serial Communications Interface**

The MVME162LX uses two Zilog Z85230 serial port controllers to implement the four serial communications interfaces. Each interface supports CTS, DCD, RTS, and DTR control signals; as well as the TXD and RXD transmit/receive data signals. Because the serial clocks are omitted in the MVME162LX implementation, serial communications are strictly asynchronous. The MVME162LX hardware supports serial baud rates of 110b/s to 38.4Kb/s.

The Z85230 supplies an interrupt vector during interrupt acknowledge cycles. The vector is modified based upon the interrupt source within the Z85230. Interrupt request levels are programmed via the MCchip. Refer to the Z85230 data sheet listed in this chapter, and to the MCchip Programming Model in Chapter 3, for information.

The Z85230s are interfaced as DTE (data terminal equipment) with EIA-232-D signal levels. The four serial ports are routed to four RJ45 telephone connectors on the MVME162LX front panel.

#### IndustryPack (IP) Interfaces

Up to two IndustryPack (IP) modules may be installed on the MVME162LX as an option. The interface between the IPs and MVME162LX is the IndustryPack Interface Controller (IPIC) ASIC. Access to the IPs is provided by two 3M connectors located behind the MVME162LX front panel.Refer to Chapter 5 on the IPIC for detailed features of the IP interface.

#### **Ethernet Interface**

The MVME162LX uses the 82596CA to implement the Ethernet transceiver interface. The 82596CA accesses local RAM using DMA operations to perform its normal functions. Because the 82596CA has small internal buffers and the VMEbus has an undefined latency period, buffer overrun may occur if the DMA is programmed to access the VMEbus. Therefore, the 82596CA should not be programmed to access the VMEbus.

Every MVME162LX that has the Ethernet interface is assigned an Ethernet Station Address. The address is \$08003E2XXXX where XXXXX is the unique 5-nibble number assigned to the board (i.e., every MVME162LX has a different value for XXXXX).

Each board has an Ethernet Station Address displayed on a label attached to the VMEbus P2 connector. In addition, the six bytes including the Ethernet address are stored in the configuration area of the BBRAM. That is, 08003E2XXXXX is stored in the BBRAM. At an address of \$FFFC1F2C, the upper four bytes (08003E2X) can be read. At an address of \$FFFC1F30, the lower two bytes (XXXX) can be read. Refer to the BBRAM, TOD Clock memory map description later in this chapter. The MVME162 debugger has the capability to retrieve or set the Ethernet address.

If the data in the BBRAM is lost, the user should use the number on the label on backplane connector P2 to restore it.

The Ethernet transceiver interface is located on the MVME162LX main board, and the industry standard connector is located on its front panel

Support functions for the 82596CA are provided by the MCchip ASIC. Refer to the 82596CA user's guide and to the MCchip in Chapter 3 for detailed programming information.

#### SCSI Interface

The MVME162LX supports mass storage subsystems through the industrystandard SCSI bus. These subsystems may include hard and floppy disk drives, streaming tape drives, and other mass storage devices. The SCSI interface is implemented using the NCR 53C710 SCSI I/O controller.

Support functions for the 53C710 are provided by the MCchip ASIC. Refer to the NCR 53C710 user's guide and to the MCchip in Chapter 3 for detailed programming information.

#### **SCSI** Termination

The individual configuring the system must ensure that the SCSI bus is properly terminated at both ends.

The MVME162LX main module provides terminators for the SCSI bus. The SCSI terminators are enabled / disabled by a jumper on header J14. If the SCSI bus ends at the MVME162LX module, then a jumper must be installed between J14 pins 1 and 2.

The MVME162LX provides +5 Vdc to the SCSI bus TERMPWR signal through fuse F4, located near J7. The FUSES LED (part of DS2) on the MVME162LX front panel monitors the SCSI bus TERMPWR signal in addition to LAN power; with the MVME162LX connected to an SCSI bus, the FUSES LED lights when SCSI terminator power is present.

Because any device on the SCSI bus can provide TERMPWR, the FUSES LED does not directly indicate the condition of the fuse. If the LED is not illuminated during SCSI bus operation, however, the fuse should be checked.

#### Local Resources

The MVME162LX includes many resources for the local processor. These include tick timers, software-programmable hardware interrupts, watchdog timer, and local bus timeout.

#### **Programmable Tick Timers**

Four 32-bit programmable tick timers with 1  $\mu$ s resolution are provided in the MCchip and two 32-bit programmable tick timers are provided in the optional VMEchip2. The tick timers can be programmed to generate periodic interrupts to the processor. Refer to the VMEchip2 and MCchip in Chapters 2 and 3, respectively, for detailed programming information.

#### Watchdog Timer

A watchdog timer is provided in both the MCchip and the optional VMEchip2. The timers operate independently but in parallel. When the watchdog timers are enabled, they must be reset by software within the programmed time or they will time out. The watchdog timers can be programmed to generate a SYSRESET signal, local reset signal, or board fail signal if they time out. Refer to the VMEchip2 in Chapter 2 and the MCchip in Chapter 3 for detailed programming information.

The watchdog timer logic is duplicated in the VMEchip2 and MCchip ASICs. Because the watchdog timer function in the VMEchip2 is a superset of that function in the MCchip (system reset function), the timer in the VMEchip2 is used in all cases except for the version of the MVME162LX which does not include the VMEbus interface ("No VMEbus Interface" option).

#### Software-Programmable Hardware Interrupts

Eight software-programmable hardware interrupts are provided by the VMEchip2. These interrupts allow software to create a hardware interrupt. Refer to the VMEchip2 in Chapter 2 for detailed programming information.

#### Local Bus Timeout

The MVME162LX provides timeout functions in the VMEchip2 and the MCchip for the local bus. When the timer is enabled and a local bus access times out, a Transfer Error Acknowledge (TEA) signal is sent to the local bus master. The timeout value is selectable by software for 8  $\mu$ sec, 64  $\mu$ sec, 256  $\mu$ sec, or infinite. The local bus timer does not operate during VMEbus bound cycles. VMEbus bound cycles are timed by the VMEbus access timer and the VMEbus global timer. Refer to the VMEchip2 in Chapter 2 and the MCchip in Chapter 3 for detailed programming information.

The MCchip also provides local bus timeout logic for MVME162LXs without the optional VMEbus interface (i.e., without the VMEchip2).

The access timer logic is duplicated in the VMEchip2 and MCchip ASICs. Because the local bus timer in the VMEchip2 can detect an offboard access and the MCchip local bus timer cannot, the timer in the VMEchip2 is used in all cases except for the version of the MVME162LX which does not include the VMEbus interface ("No VMEbus Interface option").

### Local Bus Arbiter

The local bus arbiter implements a fixed priority which is described in the following table.

| Device    | Priority | Note        |

|-----------|----------|-------------|

| LAN       | 0        | Highest     |

| SCSI      | 1        |             |

| VMEbus    | 2        | Next Lowest |

| MC68xx040 | 3        | Lowest      |

Table 1-2. Local Bus Arbitration Priority

## Connectors

The MVME162LX has two 96-position DIN connectors: P1 and P2. P1 rows A, B, C, and P2 row B provide the VMEbus interconnection. P2 rows A and C are not used. The MVME162LX has a 20-pin connector J2 mounted behind the front panel. When the MVME162LX board is enclosed in a chassis and the front panel is not visible, this connector allows the reset, abort and LED functions to be extended to the control panel of the system, where they are visible. The serial ports on the MVME162LX are connected to four 8-pin RJ45 female connectors (J17) on the front panel. The two IPs connect to the MVME162LX by two pairs of 50-pin connectors. Two 50-pin connectors behind the front panel are for external connections to IP signals. The memory mezzanine board is plugged into two 100-pin connectors.

## Fuses

The MVME162LX boards supply power to various I/O devices. The power sources are fused by pico fuses on the main board. The fuses are included to protect the board in case any of the power sources are shorted. If a fuse is blown, the board may behave in a erratic manner or stop functioning completely. If any of the onboard I/O devices behave this way, the fuses should be checked. There are several LEDs to monitor the status of the fuses.

The MVME162LX provides +5V power to the 20-pin remote reset connector J2 through fuse F1 located near the connector. This voltage source is only used when the LED functions are extended and there is no onboard monitor.

The MVME162LX provides +5V to SCSI bus TERMPWR signal through a fuse. There is a monitor LED on the MVME162LX for this fuse.

## **Configuration Jumpers**

The MVME162LX was designed to provide software control for most options. Some options can not be done in software, so they are done by jumpers on headers. This section describes the jumpers used on the MVME162LX.

The MVME162LX has been factory tested and is shipped with the factory jumper settings described in the following sections. The MVME162LX operates with its required and factory-installed Debug Monitor, MVME162Bug (162Bug), with these factory jumper settings. Settings can be made for:

- □ System controller selection (J1)

- General-purpose readable register configuration (J11)

- □ EPROM/Flash configuration (J12)

- SRAM backup power source selection (for onboard SRAM: J13 on the MVME162LX main module. For the SRAM mezzanine: J1 on the SRAM mezzanine)

- □ SCSI bus termination (J14)

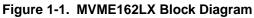

#### System Controller Select Header (J1)

The MVME162LX is factory-configured as a VMEbus system controller (i.e., a jumper is installed across pins 1 and 2 of header J1). Remove the J1 jumper if the MVME162LX is not to be the system controller. Note that when the MVME162LX is functioning as system controller, the SCON LED is turned on.

## Note

# For MVME162LXs without the optional VMEbus interface (i.e., with no VMEchip2), the jumper may be installed or removed without affecting normal operation.

System Controller (factory configuration)

Not System Controller

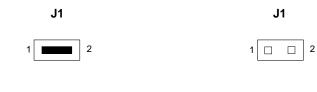

#### General-Purpose Readable Jumpers Header (J11)

Header J11 provides eight readable jumpers. These jumpers can be read as a register (at \$FFF4202D) in the MCchip LCSR. The bit values are read as a zero when the jumper is installed, and as a one when the jumper is removed.

If the MVME162BUG firmware is installed, four jumpers are user-definable (pins 9-10, 11-12, 13-14, 15-16). If the MVME162BUG firmware is not installed, seven jumpers are user-definable (pins 1-2, 3-4, 5-6, 9-10, 11-12, 13-14, 15-16).

## Note

#### Pins 7-8 (GPIO3) are reserved to select either the Flash memory map (jumper installed) or the EPROM memory map (jumper removed). They are not user-definable. The address ranges for the various EPROM/Flash configurations appear in the next section of this chapter.

The MVME162LX is shipped from the factory with J11 set to all zeros (jumpers on all pins) except for GPIO3.

EPROMs Selected (factory configuration)

#### EPROM/Flash Configuration Header (J12)

The MVME162LX can be ordered with 1 MB of Flash memory and four EPROM sockets ready for the installation of the EPROMs, which may be ordered separately. The EPROM locations are standard JEDEC 32-pin DIP sockets that accommodate four jumper-selectable densities (128 Kbit x 8; 256 Kbit x 8; 512 Kbit x 8; 1 Mbit x 8) and permit disabling of the Flash memory.

Header J12 provides eight jumpers to configure the EPROM sockets.

The next five tables show the address range for each EPROM socket in all five configurations. GPIO3 (J11 pins 7-8) is a control bit in the MCchip ASIC that allows reset code to be fetched either from Flash memory or from EPROMs.

| GPIO3     |   | Address Range           | Device Accessed |  |  |  |

|-----------|---|-------------------------|-----------------|--|--|--|

|           |   | \$FF800000 - \$FF81FFFF | EPROM A (XU24)  |  |  |  |

|           |   | \$FF820000 - \$FF83FFFF | EPROM B (XU23)  |  |  |  |

| Removed   | 1 | \$FF840000 - \$FF85FFFF | EPROM C (XU22)  |  |  |  |

|           |   | \$FF860000 - \$FF87FFFF | EPROM D (XU21)  |  |  |  |

|           |   | \$FFA00000 - \$FFBFFFFF | On-Board Flash  |  |  |  |

|           |   | \$FF800000 - \$FF9FFFFF | On-Board Flash  |  |  |  |

|           |   | \$FFA00000 - \$FFA1FFFF | EPROM A (XU24)  |  |  |  |

| Installed | 0 | \$FFA20000 - \$FFA3FFFF | EPROM B (XU23)  |  |  |  |

|           |   | \$FFA40000 - \$FFA5FFFF | EPROM C (XU22)  |  |  |  |

|           |   | \$FFA60000 - \$FBA7FFFF | EPROM D (XU21)  |  |  |  |

Table 1-3. EPROM/Flash Mapping—128K x 8 EPROMs

| GPIO3     |   | Address Range           | Device Accessed |  |  |  |

|-----------|---|-------------------------|-----------------|--|--|--|

|           |   | \$FF800000 - \$FF83FFFF | EPROM A (XU24)  |  |  |  |

|           |   | \$FF840000 - \$FF87FFFF | EPROM B (XU23)  |  |  |  |

| Removed   | 1 | \$FF880000 - \$FF8BFFFF | EPROM C (XU22)  |  |  |  |

|           |   | \$FF8C0000 - \$FF8FFFFF | EPROM D (XU21)  |  |  |  |

|           |   | \$FFA00000 - \$FFBFFFFF | On-Board Flash  |  |  |  |

|           |   | \$FF800000 - \$FF9FFFFF | On-Board Flash  |  |  |  |

|           |   | \$FFA00000 - \$FFA3FFFF | EPROM A (XU24)  |  |  |  |

| Installed | 0 | \$FFA40000 - \$FFA7FFFF | EPROM B (XU23)  |  |  |  |

|           |   | \$FFA80000 - \$FFABFFFF | EPROM C (XU22)  |  |  |  |

|           |   | \$FFAC0000 - \$FBAFFFFF | EPROM D (XU21)  |  |  |  |

1

| GPIO3     |   | Address Range           | Device Accessed |  |  |  |

|-----------|---|-------------------------|-----------------|--|--|--|

|           |   | \$FF800000 - \$FF87FFFF | EPROM A (XU24)  |  |  |  |

|           |   | \$FF880000 - \$FF8FFFFF | EPROM B (XU23)  |  |  |  |

| Removed   | 1 | \$FF900000 - \$FF97FFFF | EPROM C (XU22)  |  |  |  |

|           |   | \$FF980000 - \$FF9FFFFF | EPROM D (XU21)  |  |  |  |

|           |   | \$FFA00000 - \$FFBFFFFF | On-Board Flash  |  |  |  |

|           |   | \$FF800000 - \$FF9FFFFF | On-Board Flash  |  |  |  |

|           |   | \$FFA00000 - \$FFA7FFFF | EPROM A (XU24)  |  |  |  |

| Installed | 0 | \$FFA80000 - \$FFAFFFFF | EPROM B (XU23)  |  |  |  |

|           |   | \$FFB00000 - \$FFB7FFFF | EPROM C (XU22)  |  |  |  |

|           |   | \$FFB80000 - \$FBF7FFFF | EPROM D (XU21)  |  |  |  |

Table 1-5. EPROM/Flash Mapping—512K x 8 EPROMs