MVME050/D3

# MVME050 System Controller Module User's Manual

MVMEO50 SYSTEM CONTROLLER MODULE USER'S MANUAL (MVMEO50/D3) The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, Motorola reserves the right to make changes to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights or the rights of others.

# PREFACE

This manual provides general information, hardware preparation, installation instructions, operating instructions, functional description, and support information for the MVME050 System Controller Module.

This manual is intended for anyone who wants to design OEM systems, supply additional capability to an existing compatible system, or in a lab environment for experimental purposes.

A basic knowledge of computers and digital logic is assumed.

To use this manual, you should be familiar with the publications listed in the *Related Documentation* paragraph in Chapter 1 of this manual.

Throughout this manual the paragraph headings conform to the following convention:

HARDWARE PREPARATION

(this is a main topic heading)

Controller Module Headers

(this is a subordinate topic heading under a main topic)

The computer programs stored in the programmed array logic chips of this device contain material copyrighted by Motorola Inc., first published 1984, and may be used only under a license such as the License for Computer Programs (Article 14) contained in Motorola's Terms and Conditions of Sale, Rev. 1/79.

# WARNING

THIS EQUIPMENT GENERATES, USES, AND CAN RADIATE RADIO FREQUENCY ENERGY AND IF NOT INSTALLED AND USED IN ACCORDANCE WITH THE INSTRUCTIONS MANUAL, MAY CAUSE INTERFERENCE TO RADIO COMMUNICATIONS. IT HAS BEEN TESTED AND FOUND TO COMPLY WITH THE LIMITS FOR A CLASS A COMPUTING DEVICE PURSUANT TO SUBPART J OF PART 15 OF FCC RULES, WHICH ARE DESIGNED TO PROVIDE REASONABLE PROTECTION AGAINST SUCH INTERFERENCE WHEN OPERATED IN A COMMERCIAL ENVIRONMENT. OPERATION OF THIS EQUIPMENT IN A RESIDENTIAL AREA IS LIKELY TO CAUSE INTERFERENCE IN WHICH CASE THE USER, AT HIS OWN EXPENSE, WILL BE REQUIRED TO TAKE WHATEVER MEASURES NECESSARY TO CORRECT THE INTERFERENCE.

SYSTEM V/68, VERSAdos, VMEmodule, and VMEsystem 1000 are trademarks of Motorola, Inc.

First Edition April 1989

Copyright 1989 by Motorola, Inc.

# SAFETY SUMMARY SAFETY DEPENDS ON YOU

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the equipment. Motorola inc. assumes no liability for the customer's failure to comply with these requirements. The safety precautions listed below represent warnings of certain dangers of which we are aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safet operation of the equipment in your operating environment.

# GROUND THE INSTRUMENT.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. The equipment is supplied with a three-conductor ac power cable. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter, with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards.

# DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE.

Do not operate the equipment in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment constitutes a definite safety hazard.

# KEEP AWAY FROM LIVE CIRCUITS.

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified maintenance personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

# DO NOT SERVICE OR ADJUST ALONE.

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

## USE CAUTION WHEN EXPOSING OR HANDLING THE CRT.

Breakage of the Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, avoid rough handling or jarring of the equipment. Handling of the CRT should be done only by qualified maintenance personnel using approved safety mask and gloves.

# DO NOT SUBSTITUTE PARTS OR MODIFY EQUIPMENT.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the equipment. Contact Motorola Field Service Division for service and repair to ensure that safety features are maintained.

## DANGEROUS PROCEDURE WARNINGS.

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

#### WARNING

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

SPD 15163 R-1 (1/88)

| INTRODUCTION          | 1-1 |

|-----------------------|-----|

| FEATURES              | 1-1 |

| SPECIFICATIONS        | 1-1 |

| GENERAL DESCRIPTION   | 1-3 |

| RELATED DOCUMENTATION | 1-3 |

| MANUAL TERMINOLOGY    | 1-3 |

# CHAPTER 2 - HARDWARE PREPARATION AND INSTALLATION INSTRUCTIONS

| INTRODUCTION                                                                 | 2-1  |

|------------------------------------------------------------------------------|------|

| UNPACKING INSTRUCTIONS                                                       | 2-1  |

| HARDWARE PREPARATION                                                         | 2-1  |

| EPROM Base Address Select Header (J1,J2)                                     | 2-4  |

| RAM Base Address Select Header (J9, J10)                                     | 2-6  |

| EPROM Size Select Header (J8)                                                | 2-7  |

| RAM Size Select Header (J15)                                                 | 2-7  |

| EPROM Quad Enable Select Header (J13)                                        | 2-8  |

| RAM Quad Enable Select Header (J14)                                          | 2-8  |

| EPROM Access Time Select Header (J27)                                        | 2-9  |

| RAM Access Time Select Header (J26)                                          | 2-9  |

| AM1E Enable Select (Quad 2), AM16 Enable Select (Quad 1)                     |      |

| Header (J12)                                                                 | 2-10 |

| Header (J12)                                                                 | 2-11 |

| Bus Time-Out Select Header (J4)                                              | 2-30 |

| Clock Damping Shorting Select Headers (J5, J6)                               | 2-30 |

| System Controller Select Header (J7)                                         | 2-31 |

| I/O Base Address Select Header (512 Byte Boundaries) (J2O) .                 | 2-31 |

| Time-of-Day Clock Power Select and Battery Charge Header                     |      |

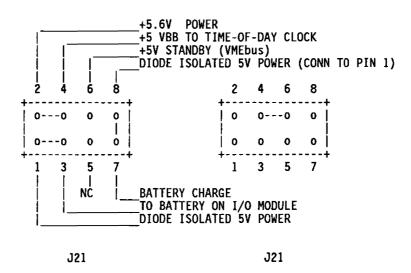

| (J21)                                                                        | 2-32 |

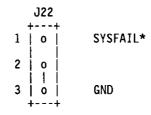

| System Fail (SYSFAIL*) or GND Select for Interrupt Source                    |      |

| Header (J22).                                                                | 2-33 |

| Header (J22)<br>Internal/External Transmit Clock Serial Port 1 Select Header |      |

| (J23)                                                                        | 2-33 |

| Internal/External Transmit Clock Serial Port 2 Select Header                 |      |

| (J24)                                                                        | 2-33 |

| Display Blanking Enable Select Header (J25)                                  | 2-34 |

| RESET Switch Disable Select Header (J28)                                     | 2-34 |

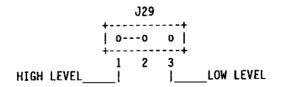

| Printer Acknowledge Level Select Header (J29)                                | 2-34 |

| INSTALLATION INSTRUCTIONS                                                    | 2-35 |

| Module Installation                                                          | 2-35 |

| VMEmodule Chassis Backplane Daisy-Chained Headers                            | 2-36 |

| · •                                                                          |      |

# CHAPTER 3 - OPERATING INSTRUCTIONS

| INTRODUCTION                            | 3-1 |

|-----------------------------------------|-----|

| CONTROLS AND INDICATORS                 | 3-1 |

| RESET Switch                            | 3-1 |

| RUN Indicator                           | 3-1 |

| FAIL Indicator                          | 3-1 |

| User Status Display                     |     |

| User 8-Section Software-Readable Switch |     |

| I/O MEMORY MAP                          | 3-2 |

# CHAPTER 4 - FUNCTIONAL DESCRIPTION

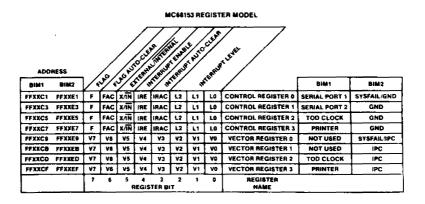

| INTRODUCTION                     | 4 - |

|----------------------------------|-----|

| GENERAL DESCRIPTION              | 4 - |

| BLOCK DIAGRAM DESCRIPTION        | 4 - |

| Time-of-Day Clock                | 4 - |

| EPROM/RAM Sockets                | 4 - |

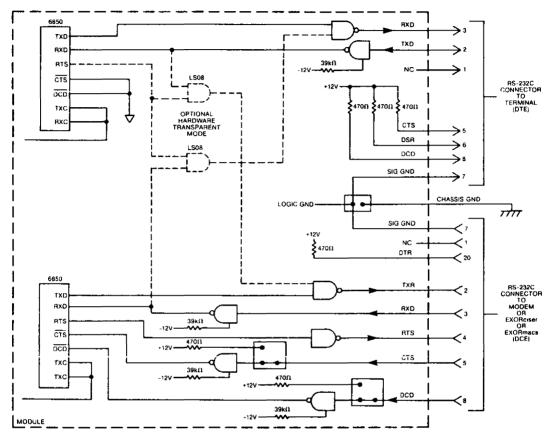

| Serial Ports                     | 4 - |

| Centronics Parallel Printer Port | 4 - |

| SYSFAIL Register                 | 4 - |

| User Display Blanking Register   | 4 - |

| Global Interrupter               | 4 - |

| Battery Backup                   | 4 - |

| Bus Arbiter                      | 4-  |

| System Clock Generator           | 4-  |

| Serial Bus Clock Generator       | 4-1 |

| Bus Time-Out Generator           | 4-1 |

| Power-Up Reset                   | 4-1 |

| RESET Switch                     | 4-1 |

| VMEbus Interface                 | 4-1 |

| User Display                     | 4-1 |

| Front Panel Indicators           | 4-1 |

# CHAPTER 5 - SUPPORT INFORMATION

| INTRODUCTION<br>INTERCONNECT SIGNALS<br>Connector P1 Interconnect Signals<br>Connector P2 Interconnect Signals<br>PARTS LIST<br>SCHEMATIC DIAGRAM | 5-1<br>5-1<br>5-6<br>5-9<br>5-17 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| APPENDIX A - TIME-OF-DAY CLOCK COMPENSATION                                                                                                       | A-1                              |

| APPENDIX B - RS-232C INTERCONNECTIONS                                                                                                             | B-1                              |

| APPENDIX C - PROGRAMMABLE ARRAY LOGIC                                                                                                             | C-1                              |

viii

# LIST OF ILLUSTRATIONS

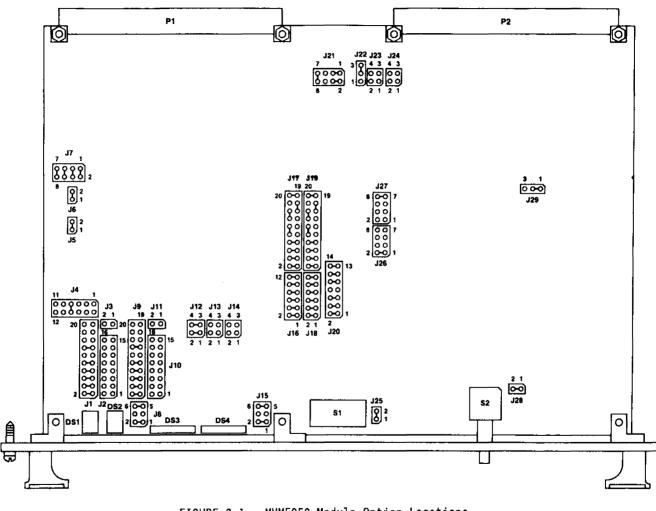

| FIGURE 2-1. | MVME050 Module Option Locations          | 2-3  |

|-------------|------------------------------------------|------|

| FIGURE 4-1. | MVME050 Block Diagram                    | 4-13 |

| FIGURE 5-1. | MVME050 Parts Location                   | 5-15 |

| FIGURE 5-2. | MVME050 Schematic Diagram                | 5-19 |

| FIGURE B-1. | Middle-of-the-Road RS-232C Configuration | B-4  |

| FIGURE B-2. | Minimum RS-232C Connection               | B-5  |

# LIST OF TABLES

| TABLE 1-1. | MVME050 Module Specifications          | 1-2  |

|------------|----------------------------------------|------|

| TABLE 2-1. | Allowable EPROM and RAM Memory Devices | 2-12 |

| TABLE 4-1. | Standard Baud Selection                | 4-6  |

| TABLE 4-2. | Supported Cycle Types                  | 4-11 |

| TABLE 5-1. | Connector Pl Interconnect Signals      | 5-1  |

| TABLE 5-2. | Connector P2 Interconnect Signals      | 5-6  |

|            | MVME050 Module Parts List              |      |

|            | RS-232C Interconnections               |      |

# CHAPTER 1 - GENERAL INFORMATION

# INTRODUCTION

This manual provides general information, preparation for use and installation instructions, operating instructions, functional description, and support information for the MVME050 System Controller Module.

#### FEATURES

The features of the MVME050 module include:

. System controller functions:

4-level priority bus arbiter

Power up reset/front panel reset

System clock and serial clock generators

Bus time-out generator

- . Eight 28-pin sockets for EPROM/RAM

- . Time-of-day clock

- . Global interrupter

- . User-defined/controlled front panel display

- . A32/A24:D8/D16/D32 VMEbus slave interface

- . Front panel RESET switch

- . Front panel FAIL LED and RUN LED

# SPECIFICATIONS

The MVME050 module specifications are identified in Table 1-1.

|                                                     | VME050 Module Spec                                                                                                          | ifications                                     |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|

| CHARACTERISTICS                                     | SPECIFICATIONS                                                                                                              |                                                |  |

| Performance<br>RAM (J26) EPROM (J27)                | Access time<br>Typ Max                                                                                                      | Cycle time<br>Typ Max                          |  |

| Select Speed<br>150 ns<br>250<br>350<br>450         | 375 ns 400 ns<br>475 550<br>575 675<br>650 700                                                                              | 455 ns 520 ns<br>555 670<br>655 785<br>730 820 |  |

| Interface (I/O)                                     |                                                                                                                             |                                                |  |

| Serial ports, printer,<br>switches, LED             | 350 ns 400 ns                                                                                                               | 540 ns 650 ns                                  |  |

| VBIM                                                | 500 ns 550 ns                                                                                                               | 580 ns 675 ns                                  |  |

| Time-of-day clock                                   | 1100 us 1300 u                                                                                                              | s 1180 us 1420 us                              |  |

| Bus arbitration time                                | Typical 75 ns                                                                                                               | Maximum 125 ns                                 |  |

| Temperature                                         |                                                                                                                             |                                                |  |

| Operating                                           | 0 degrees to 55                                                                                                             | degrees C                                      |  |

| Storage                                             | -40 degrees to                                                                                                              | 85 degrees C                                   |  |

| Relative humidity                                   | 5% to 90% (non-                                                                                                             | condensing)                                    |  |

| Physical characteristics<br>(excluding front panel) |                                                                                                                             |                                                |  |

| Height<br>Depth<br>Thickness                        | 9.187 in. (233.35 mm)<br>6.299 in. (160.00 mm)<br>0.63 in. (1.6 mm)                                                         |                                                |  |

| Power requirements                                  | +5 Vdc @ 3.7 A (typical) 4.4 A (max.)<br>-12 Vdc @ 35 mA (typical) 42 mA (max.)<br>+12 Vdc @ 140 mA (typical) 170 mA (max.) |                                                |  |

|                                                     |                                                                                                                             |                                                |  |

TABLE 1-1. MVME050 Module Specifications

•

#### **GENERAL DESCRIPTION**

The MVME050 is a combination system controller and debug/diagnostics module for VME systems. The module is designed to offload the system controller functions from computer type modules, also to provide the typical one-per-system type features such as the time-of-day clock, printer/parallel port, and a serial port for downline loading of programs from a host system. The module is capable of holding a system diagnostics and debug monitor for enduse in-system trouble shooting and maintenance. A global interrupter provides the ability to have tightly coupled task/message passing between intelligent modules in multiprocessor systems. The controller module allows extended addressing for supporting the expanded (32 bit) VMEbus. Both 32-bit data and address are supported on EPROM/RAM sockets.

#### RELATED DOCUMENTATION

The following publications may provide additional helpful information. If not shipped with this product, the manual may be purchased from Motorola Literature Distribution Center, 616 W. 24th Street, Tempe, Arizona 85282; telephone (602) 994-6561.

\_\_\_\_\_ MOTOROLA DOCUMENT TITLE PUBLICATION NUMBER

### MVME701A Transition Module

\*-----NOTE: Although not shown in the above list, each Motorola MCD manual publication number is suffixed with characters which represent the revision level of the document, such as "/D2" (the second revision of a manual); supplement bears the same number as the manual but has a suffix such as "/Al" (the first supplement to the manual).

The following publication is available from the source indicated.

ANSI/IEEE Std 1014-1987 Versatile Backplane Bus: The Institute of Electrical and Electronics Engineers, Inc., 345 East 47th Street, New York, NY 10017, USA.

#### MANUAL TERMINOLOGY

Throughout this manual, a convention has been maintained whereby data and address parameters are preceded by a character which specifies the numeric format as follows:

| \$<br>dollar | specifies | a | hexadecima | l number |

|--------------|-----------|---|------------|----------|

|              |           |   |            |          |

- %

- percent specifies a binary number ampersand specifies a decimal number 8

1-3

MVME701A

Unless otherwise specified, all address references are in hexadecimal throughout this manual.

An asterisk (\*) following the signal name for signals which are level significant denotes that the signal is true or valid when the signal is low.

An asterisk (\*) following the signal name for signals which are edge significant denotes that the actions initiated by that signal occur on high to low transition.

In this manual, assertion and negation are used to specify forcing a signal to a particular state. In particular, assertion and assert refer to a signal that is active or true; negation and negate indicate a signal that is inactive or false. These terms are used independently of the voltage level (high or low) that they represent. CHAPTER 2 - HARDWARE PREPARATION AND INSTALLATION INSTRUCTIONS

# INTRODUCTION

This chapter provides unpacking, hardware preparation, and installation instructions for the MVME050.

#### UNPACKING INSTRUCTIONS

# NOTE

If shipping carton is damaged upon receipt, request carrier's agent be present during unpacking and inspection of equipment.

Unpack equipment from shipping carton. Refer to packing list and verify that all items are present. Save packing material for storing or reshipping the equipment.

#### HARDWARE PREPARATION

To select the desired configuration and ensure proper operation of the MVME050 module, certain changes may be made before installation. These changes are made through jumper arrangements on the headers. The location of the headers, LEDs, RESET switch, and connectors are illustrated in Figure 2-1. The module has been factory tested and is shipped with factory-installed jumper configurations that are also shown in the illustration. The module is operational with the factory-installed jumpers. The MVME050 module is configured to provide all the system controller functions required for a VMEbus system. It is necessary to make changes in the jumper arrangements for the following:

- a. EPROM base address select (J1,J2)

- b. EPROM/RAM configuration select (quad 2) (J3)

- c. Bus time-out select (J4)

- d. Clock damping shorting select (J5, J6)

- e. System controller select (J7)

- f. EPROM size select (J8)

- g. RAM base address select (J9,J10)

- h. EPROM/RAM configuration select (quad 1) (J11)

- i. Address Modifier (AM1E) enable select (EPROM bank 1); AM16 enable select (EPROM bank 2) (J12)

- j. EPROM bank enable select (J13)

- k. RAM bank enable select (J14)

- 1. RAM size select (J15)

- m. EPROM/RAM configuration select (quad 1 and 2) (J16, J17, J18, J19)

- n. I/O base address select (512 byte boundaries) (J2O)

- o. Time-of-day clock power select and battery charge (J21)

- p. SYSFAIL\* or GND select for interrupt source (J22)

- q. Internal/external transmit clock serial port 1 select (J23)

- r. Internal/external transmit clock serial port 2 select (J24)

- s. Display blanking enable select (J25)

- t. RAM access time select (J26)

- u. EPROM access time select (J27)

- v. RESET switch disable select (J28)

- w. Printer acknowledge edge select (J29)

N

自

ਸ਼

2-3

The configuration options of the MVME050 module headers are discussed in the following paragraphs.

The VMEbus base address for accessing EPROM/RAM is set by jumper position on the appropriate headers. If both socket quads (refer to the EPROM/RAM Configuration Select Headers J3, J11, J16-J19 paragraph in this Chapter) are populated with RAM, the RAM base address is set with the RAM headers (J9. J10), and the RAM addressing becomes contiguous across the socket quad boundary. The EPROM base address headers (J1, J2) are ignored. If both socket quads are populated with EPROM, the base address is set with the EPROM headers (J1, J2), and the addressing becomes contiguous across the socket quad boundary. When both RAM and EPROM populations are used, the RAM base address is set by the RAM headers (J9, J10) and the EPROM base address is set by the EPROM headers (J1, J2). If EPROM devices are installed in the high numbered socket quad (2), they are capable of being accessed when a bus master initiates a VMEbus transfer using Address Modifier (AM) code 1E (J12). If EPROM devices are installed in the low numbered socket quad (1), they are capable of being accessed when a bus master initiates a VMEbus transfer using AM code 16. When this type of access occurs, no other devices on the module are accessed and the EPROM base address circuitry is disabled. This feature may be disabled by removing the jumpers from J12.

#### EPROM Base Address Select Header (J1,J2)

The base address may be selected anywhere within the 16Mb of the system memory map with address modifier codes 39, 3A, 3D, 3E for standard addressing; or anywhere within the 4 gigabyte map with address modifier codes 09, 0A, 0D, 0E for extended addressing.

#### NOTE

Addressing (AM codes 09, 0A, 0D, 0E) require a backplane motherboard with a P2 connector.

Installing a jumper enables the appropriate line. As shown below, header J1 is associated with address lines A14-A23 and header J2 with lines A24-A31. The base address selected must be on a boundary that is eight times the size of the devices used regardless of the quantity installed, as shown below.

For each quad used, a four-way split of data must be used. Let's assume the four sections of the quad were numbered as follows:

D0-D7 = 1 D8-D15 = 2 D16-D23 = 3 D24-D31 = 4

As an example, the four-way split would be:

| <u>ADDRESS</u> | <u>DATA</u> | SECTION NUMBER |

|----------------|-------------|----------------|

| 0              | 01          | 1              |

| 1              | 02          | 2              |

| 2              | 03          | 3              |

| 3              | 04          | 4              |

| 4              | 05          | 1              |

| 5              | 06          | 2              |

| 6              | 07          | 3              |

| 7              | 08          | 4              |

|    | J1/J9     |     |    | J2,   | /J10 |     |

|----|-----------|-----|----|-------|------|-----|

| 1  | 00        | A14 | 1  | 0     | 0    | A24 |

| 3  | 00        | A15 | 3  | 0     | 0    | A25 |

| 5  | 00        | A16 | 5  | 0     | 0    | A26 |

| 7  | 00        | A17 | 7  | 0     | 0    | A27 |

| 9  | 00        | A18 | 9  | 0     | 0    | A28 |

| 11 | 0 0       | A19 | 11 | 0     | 0    | A29 |

| 13 | 00        | A20 | 13 | 0     | 0    | A30 |

| 15 | 0 0       | A21 | 15 | 0     | 0    | A31 |

| 16 | 0 0       | A22 |    | <br>+ |      | +   |

| 17 | 0 0       | A23 |    |       |      |     |

| -  | T <b></b> | F   |    |       |      |     |

# JUMPER IN = ADDRESS LINE LOW

DEFAULT SHOWN = E80000 24-BIT ADDRESS FFE80000 32-BIT ADDRESS 2

| DEV       | ICE SIZE                                                           | BOUNDARY                                  |         |

|-----------|--------------------------------------------------------------------|-------------------------------------------|---------|

| 3         | 2K x 8<br>4K x 8<br>8K x 8<br>6K x 8<br>2K x 8<br>2K x 8<br>2K x 8 | 16K<br>32K<br>64K<br>128K<br>256K<br>512K |         |

| EPROM QUA | AD 2                                                               | EPROM QU                                  | AD 1    |

| RAM QUAL  | ) 1                                                                | RAM QUA                                   |         |

| XU33      | XU25                                                               | XU16                                      | XU8     |

| D8-D15    | D0-D7                                                              | D8-D15                                    | D0-D7   |

| CS2*      | CS1*                                                               | CS6*                                      | CS5*    |

| XU36      | XU28                                                               | XU19                                      | XU11    |

| D24-D31   | D16-D23                                                            | D24-D31                                   | D16-D23 |

| CS4*      | CS3*                                                               | CS8*                                      | CS7*    |

## RAM Base Address Select Header (J9, J10)

RAM base address is configured the same as EPROM with the exception that the headers used are J9 and J10. If RAM and EPROM devices are mixed in the sockets, do not select the same base address for RAM and EPROM. One overwrites the other. The base address defines the starting address for quad 1, and the starting address for quad 2 is offset by four times the part size. This also depends on the ROM quad enable header configuration and the RAM quad enable header configuration.

# EPROM Size Select Header (J8)

Header J8 allows the user to configure the module to operate with the devices installed in the sockets. Jumpers are positioned according to the table and illustration below. The size of the device (i.e.,  $2K \times 8$ ) determines the position of the jumpers. Devices must all be the same size. The as-shipped configuration is shown below.

|                 |      | J8  | 1                    |        |

|-----------------|------|-----|----------------------|--------|

|                 | 1    | 00  | 2                    |        |

|                 | 3    | 0 0 | 4                    |        |

|                 | 5    | 00  | 6                    |        |

|                 | +    |     | r                    |        |

|                 |      |     |                      |        |

| SIZE OF<br>PART | 1    |     | DER PINS<br>3 TO 4 5 | TO 6   |

|                 | ==== |     |                      | ****** |

| 2K              |      | X   | X                    | X      |

| 4K              |      | 0   | x                    | X      |

| 8K              |      | X   | 0                    | X      |

| 16K             |      | 0   | 0                    | X      |

| 32K             |      | x   | X                    | 0      |

| 64K             |      | 0   | X                    | 0      |

| X = jumper      |      |     |                      | ====== |

# RAM Size Select Header (J15)

Refer to paragraph above. RAM size is configured the same as EPROM with the exception that the header is J15. All other information applies.

#### EPROM Quad Enable Select Header (J13)

Header J13 allows the user to select quad 1 or quad 2 according to the installation of the EPROM devices. Refer to table below for quad information. To enable quad 1, install a jumper between pins 1 and 2. To enable quad 2, install a jumper between pins 3 and 4. If all EPROM in both quads, install both jumpers.

|           | J1      | 3                                       |                  |

|-----------|---------|-----------------------------------------|------------------|

|           | 1   O   | 0 2 EN/                                 | BLE EPROM QUAD 1 |

|           | 3 0     | 0 4 EN/                                 | BLE EPROM QUAD 2 |

|           | +       | +                                       |                  |

| EPROM QUA | .D 2    | EPROM (                                 | UAD 1            |

|           |         |                                         |                  |

| XU33      | XU25    | XU16                                    | XU8              |

| D8-D15    | D0-D7   | D8-D15                                  | D0-D7            |

| CS2*      | CS1*    | CS6*                                    | CS5*             |

| VUDC      | VIIAO   | VUIDO                                   | VII11            |

| XU36      | XU28    | XU19                                    | XU11             |

| D24-D31   | D16-D23 | D24-D31                                 | D16-D23          |

| CS4*      | CS3*    | CS8*                                    | CS7*             |

|           |         | ======================================= |                  |

## RAM Quad Enable Select Header (J14)

Header J14 allows the user to select quad 1 or quad 2 according to the installation of the RAM devices. Refer to the table below for quad information. To enable quad 1, install a jumper between pins 1 and 2. To enable quad 2, install a jumper between pins 3 and 4. If all RAM in both quads, install both jumpers.

J14 1 | 0 0 | 2 ENABLE RAM QUAD 1 3 | 0 0 | 4 ENABLE RAM QUAD 2 +-----+

2

| RAM QUA | RAM QUAD 1 |         | D 2     |

|---------|------------|---------|---------|

| XU33    | XU25       | XU16    | XU8     |

| D8-D15  | D0-D7      | D8-D15  | D0-D7   |

| CS2*    | CS1*       | CS6*    | CS5*    |

| XU36    | XU28       | XU19    | XU11    |

| D24-D31 | D16-D23    | D24-D31 | D16-D23 |

| CS4*    | CS3*       | CS8*    | CS7*    |

# EPROM Access Time Select Header (J27)

Header J27 is used to select the appropriate delay to compensate for the access times of the EPROM memory devices that are installed in the sockets. The access times of the EPROM devices installed should be compared with the access times in the illustration below. Install a jumper between pins that correspond to the access required by the EPROM device. Default is 450 ns as shown below:

| - | Já | 27 | L |        |

|---|----|----|---|--------|

| 1 | 0  | 0  | 2 | 150ns  |

| 3 | 0  | 0  | 4 | 250n s |

| 5 | 0  | 0  | 6 | 350ns  |

| 7 | 0  | 0  | 8 | 450ns  |

|   | +  |    | t |        |

#### RAM Access Time Select Header (J26)

Refer to paragraph above. RAM access time is selected the same as EPROM access time except that the header is J26. All other information applies. Default is 150 ns.

# AMIE Enable Select (Quad 2), AM16 Enable Select (Quad 1) Header (J12)

If EPROM devices are installed in EPROM quad 2, they are capable of being accessed when a bus master initiates a VMEbus transfer using AM code 1E. To enable this signal, a jumper must be installed on header J12 between pins 1 and 2. See illustration and table below. If EPROM devices are installed in EPROM quad 1, they are capable of being accessed when a bus master initiates a VMEbus transfer using AM code 16. To enable this signal, a jumper must be installed between pins 3 and 4.

|                         | J12                     | 2                       |                         |

|-------------------------|-------------------------|-------------------------|-------------------------|

|                         | 1 0                     | -o   2 ENAB             | LE FOR AM CODE 1E       |

|                         | 3 0                     | o 4 ENAB                | LE FOR AM CODE 16       |

|                         | +                       | +                       |                         |

| EPROM QU                | AD 2                    | EPROM QU                |                         |

|                         |                         |                         | **********              |

| XU33<br>D8-D15<br>CS2*  | XU25<br>D0-D7<br>CS1*   | XU16<br>D8-D15<br>CS6*  | XU8<br>D0-D7<br>CS5*    |

| XU36<br>D24-D31<br>CS4* | XU28<br>D16-D23<br>CS3* | XU19<br>D24-D31<br>CS8* | XU11<br>D16-D23<br>CS7* |

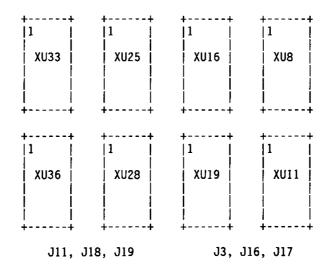

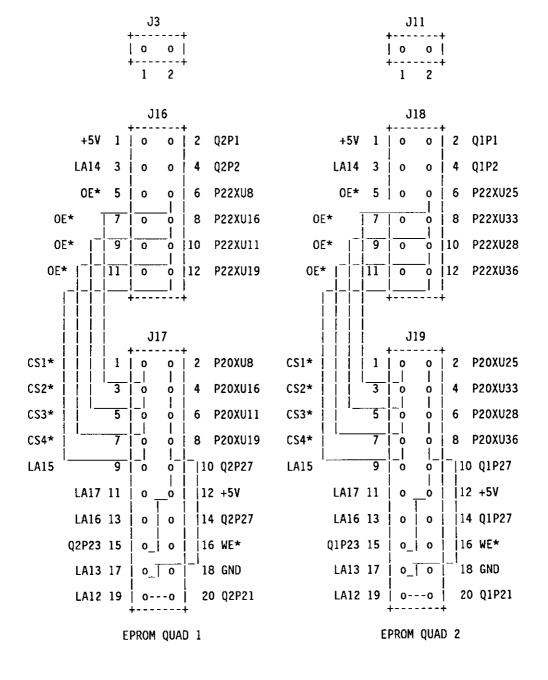

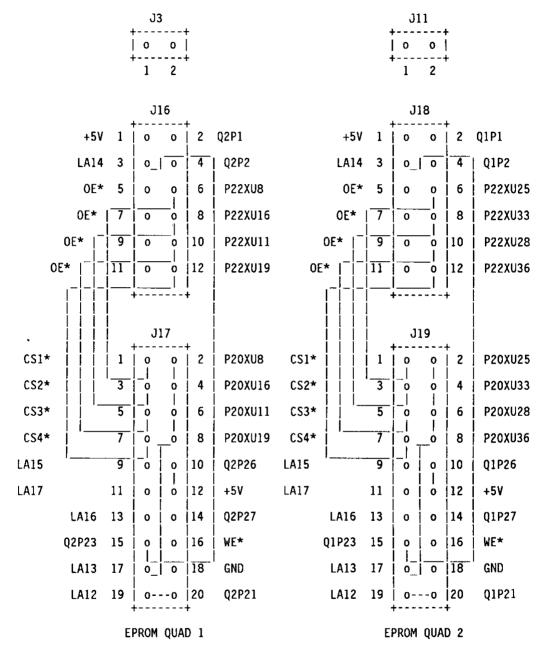

#### EPROM/RAM Configuration Select Headers (J3, J11, J16-J19)

Eight, 28-pin sockets may be populated by the user with 24-pin or 28-pin RAM or EPROM devices. ROM devices may be used provided the CS line is masked as true low. RAM and EPROM populations may be mixed. RAMs are installed into the sockets starting at RAM quad 1. EPROMs are installed into the sockets starting at EPROM quad 1 (refer to table in paragraph above). Configuration headers (J3,J11,J16-J19) are provided to configure each socket quad for RAM or EPROM and the type of device (i.e.,  $2K \times 8$ ). The socket layout on the module is illustrated below showing the corresponding headers for configuration of the sockets. Refer to the EPROM Base Address Select Header paragraph for four-way split information.

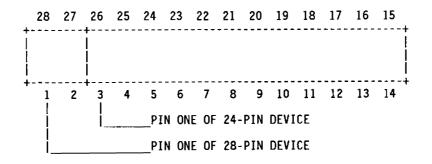

Each quad may be individually configured to accept a wide range of industry standard 24-pin and 28-pin RAM and EPROM devices. The user must provide and install the appropriate memory devices to suit the specific application intended. Devices with 28 pins are inserted with pins 1 through 28 of the device matching pins 1 through 28 of the socket. Devices with 24 pins are inserted with pins 3 through 26 of the socket as illustrated below.

Associated with each socket quad are three local memory configuration headers. The headers must be configured for each quad that contains memory devices. Each figure shows the as-shipped factory configuration. The factory configuration is the same for both quads assuming 8K x 8 EPROMs.

Several RAM and EPROM devices that may be installed in the socket quads are listed in Table 2-1. The jumpering of pins on the headers for some of the configurations can be performed with the jumpers provided; other configurations may have to be done with wire wrap. Some wire wrap is necessary between pins of different headers.

|                |                            |                |        | ============= |

|----------------|----------------------------|----------------|--------|---------------|

| PART<br>NUMBER | MANUFACTURER               | DEVICE<br>Type | SIZE   | PINS          |

| AM2716         | Advanced Micro Devices     | EPROM          | 2K x 8 | 24            |

| AM9716         | Advanced Micro Devices     | EPROM          | 2K x 8 | 24            |

| HM6716         | Harris                     | EPROM          | 2K x 8 | 24            |

| HN462716       | Hitachi                    | EPROM          | 2K x 8 | 24            |

| 12716          | Intel                      | EPROM          | 2K x 8 | 24            |

| MBM2716        | Fujitsu                    | EPROM          | 2K x 8 | 24            |

| MCM2716        | Motorola                   | EPROM          | 2K x 8 | 24            |

| MK2716         | Mostek                     | EPROM          | 2K x 8 | 24            |

| MM2716         | National Semiconductor     | EPROM          | 2K x 8 | 24            |

| MN2716         | Panasonic                  | EPROM          | 2K x 8 | 24            |

| MSM2716        | OKI Electric Industry      | EPROM          | 2K x 8 | 24            |

| S4716          | American Microsystems Inc. | EPROM          | 2K x 8 | 24            |

| SM2716         | Siemens                    | EPROM          | 2K x 8 | 24            |

| SY2716         | Synertek                   | EPROM          | 2K x 8 | 24            |

| TMS2516        | Texas Instruments          | EPROM          | 2K x 8 | 24            |

| TMM323         | Toshiba                    | EPROM          | 2K x 8 | 24            |

| UPD2716        | Nippon Electric Company    | EPROM          | 2K x 8 | 24            |

|                |                            |                |        |               |

TABLE 2-1. Allowable EPROM and RAM Memory Devices

|                | 2-1. Allowable EPROM and RA |                |        |      |

|----------------|-----------------------------|----------------|--------|------|

| PART<br>NUMBER | MANUFACTURER                | DEVICE<br>Type | SIZE   | PINS |

| HN462532       | Hitachi                     | EPROM          | 4K x 8 | 24   |

| HN462732       | Hitachi                     | EPROM          | 4K x 8 | 24   |

| 12732          | Intel                       | EPROM          | 4K x 8 | 24   |

| MBM2732        | Fujitsu                     | EPROM          | 4K x 8 | 24   |

| MCM2532        | Motorola                    | EPROM          | 4K x 8 | 24   |

| NMC2532        | National Semiconductor      | EPROM          | 4K x 8 | 24   |

| NMC2732        | National Semiconductor      | EPROM          | 4K x 8 | 24   |

| TMM2732        | Toshiba                     | EPROM          | 4K x 8 | 24   |

| TMS2532        | Texas Instruments           | EPROM          | 4K x 8 | 24   |

| UPD2732        | Nippon Electric Company     | EPROM          | 4K x 8 | 24   |

| MCM68764       | Motorola                    | EPROM          | 8K x 8 | 24   |

| MCM68766       | Motorola                    | EPROM          | 8K x 8 | 24   |

| AM2764         | Advanced Micro Devices      | EPROM          | 8K x 8 | 28   |

| HN2764         | Hitachi                     | EPROM          | 8K x 8 | 28   |

| MBM482764      | Fujitsu                     | EPROM          | 8K x 8 | 28   |

| MK2764         | Mostek                      | EPROM          | 8K x 8 | 28   |

| MSM2764        | OKI Electric Industry       | EPROM          | 8K x 8 | 28   |

| NMC2564        | National Semiconductor      | EPROM          | 8K x 8 | 28   |

| TMM2764        | Toshiba                     | EPROM          | 8K x 8 | 28   |

| TMS2564        | Texas Instruments           | EPROM          | 8K x 8 | 28   |

| UPD2764        | Nippon Electric Company     | EPROM          | 8K x 8 | 28   |

|                | 2-1. Allowable EPROM and R/ |                |         |      |

|----------------|-----------------------------|----------------|---------|------|

| PART<br>NUMBER | MANUFACTURER                | DEVICE<br>TYPE | SIZE    | PINS |

| AM27128        | Advanced Micro Devices      | EPROM          | 16K x 8 | 28   |

| 127128         | Intel                       | EPROM          | 16K x 8 | 28   |

| MBM27128       | Fujitsu                     | EPROM          | 16K x 8 | 28   |

| TMS27128       | Texas Instruments           | EPROM          | 16K x 8 | 28   |

| AM27256        | Advanced Micro Devices      | EPROM          | 32K x 8 | 28   |

| 127256         | Intel                       | EPROM          | 32K x 8 | 28   |

| MK27256        | Mostek                      | EPROM          | 32K x 8 | 28   |

| TMS27256       | Texas Instruments           | EPROM          | 32K x 8 | 28   |

| AM27512        | Advanced Micro Devices      | EPROM          | 64K x 8 | 28   |

| 127512         | Intel                       |                | 64K x 8 | 28   |

| AM9218         | Advanced Micro Devices      | RAM            | 2K x 8  | 24   |

| HM6116         | Harris                      | RAM            | 2K x 8  | 24   |

| HM6516         | Harris                      | RAM            | 2K x 8  | 24   |

| HM6116         | Hitachi                     | RAM            | 2K x 8  | 24   |

| MB2128         | Fujitsu                     | RAM            | 2K x 8  | 24   |

| MB8418         | Fujitsu                     | RAM            | 2K x 8  | 24   |

| MCM4016        | Motorola                    | RAM            | 2K x 8  | 24   |

| MCM65116       | Motorola                    | RAM            | 2K x 8  | 24   |

| MSM5116        | Mitsubishi                  | RAM            | 2K x 8  | 24   |

| MSM2128        | OKI Electric Industry       | RAM            | 2K x 8  | 24   |

| NMC2116        | National Semiconductor      | RAM            | 2K x 8  | 24   |

| SY2128         | Synertek                    | RAM            | 2K x 8  | 24   |

| TABLE          | 2-1. Allowable EPROM and | I RAM Memory De | vices (cont | 'd)  |

|----------------|--------------------------|-----------------|-------------|------|

| PART<br>NUMBER | MANUFACTURER             | DEVICE<br>TYPE  | SIZE        | PINS |

| TC5516         | Toshiba                  | RAM             | 2K x 8      | 24   |

| TC5517         | Toshiba                  | RAM             | 2K x 8      | 24   |

| TC5518         | Toshiba                  | RAM             | 2K x 8      | 24   |

| TMM2016        | Toshiba                  | RAM             | 2K x 8      | 24   |

| TMS4016        | Texas Instruments        | RAM             | 2K x 8      | 24   |

| 8148           | Mostek                   | RAM             | 4K x 8      | 28   |

| HM6264         | Hitachi                  | RAM             | 8K x 8      | 28   |

| TC5564         | Toshiba                  | RAM             | 8K x 8      | 28   |

| TC5565         | Toshiba                  | RAM             | 8K x 8      | 28   |

| J3<br>++<br>  0 0  <br>++<br>1 2 |    |              |    |    |         |

|----------------------------------|----|--------------|----|----|---------|

|                                  |    | J            | 16 | L  |         |

| +5V                              | 1  | 0            | 0  | 2  | Q2P1    |

| LA14                             | 3  | 0            | 0  | 4  | Q2P2    |

| 0E*                              | 5  | 0            | 0  | 6  | P22XU8  |

| 0E*                              | 7  | 0            | -0 | 8  | P22XU16 |

| 0E*                              | 9  | 0            | -0 | 10 | P22XU11 |

| 0E*                              | 11 | <br>  0<br>+ | -0 | 12 | P22XU19 |

| J11  |    |   |   |    |         |

|------|----|---|---|----|---------|

|      |    | 0 | 0 | +  |         |

|      | -  | + |   | +  |         |

|      |    | 1 | 2 |    |         |

| J18  |    |   |   |    |         |

| +5¥  | 1  | 0 | 0 | 2  | Q1P1    |

| LA14 | 3  | 0 | 0 | 4  | Q1P2    |

| 0E*  | 5  | 0 | 0 | 6  | P22XU25 |

| 0E*  | 7  | 0 | 0 | 8  | P22XU33 |

| 0E*  | 9  | 0 | 0 | 10 | P22XU28 |

| 0E*  | 11 | 0 | 0 | 12 | P22XU36 |

|      |    |   |   |    |         |

J17 J19 CS1\* o---o | 2 P20XU8 1 CS1\* 1 o---o | 2 P20XU25 CS2\* 3 o---o | 4 P20XU16 CS2\* 3 0---0 4 P20XU33 CS3\* 5 0---0 6 P20XU11 CS3\* 5 0---0 6 P20XU28 CS4\* 7 j o---o j 8 P20XU19 CS4\* 7 | 0---0 | 8 P20XU36 LA15 9 jo o 10 Q2P26 LA15 9 0 0 10 Q1P26 L LA17 11 0 -0 12 +5V LA17 11 0 -0 12 +5V LA16 13 | 0 | 0 |14 Q2P27 LA16 13 j o j14 Q1P27 0 Q2P23 15 Q1P23 15 | o- o | 16 WE\* o- o 16 WE\* LA13 17 0 0 18 GND LA13 17 | o o 18 GND LA12 19 | 0---0 | 20 Q2P21 LA12 19 | 0---0 |20 Q1P21 ----+ --+ +

EPROM QUAD 1

EPROM QUAD 2

Header configuration for 4K x 8 EPROM memory devices (I2732, MBM2732, NMC2732, TMM2732, UPD2732) is shown below:

| J | • |

|---|---|

| 0 |   |

| + | 2 |

| т. | J | 11 | . <b>.</b> . |

|----|---|----|--------------|

| İ  | 0 |    | İ            |

| Τ. | 1 | 2  | Ŧ            |

| J16  |    |   |   |    |         |  |

|------|----|---|---|----|---------|--|

|      | +  | + |   | ł  |         |  |

| +5V  | 1  | 0 | 0 | 2  | Q2P1    |  |

| LA14 | 3  | 0 | 0 | 4  | Q2P2    |  |

| 0E*  | 5  | 0 | 0 | 6  | P22XU8  |  |

| 0E*  | 7  | 0 | 0 | 8  | P22XU16 |  |

| 0E*  | 9  | 0 | 0 | 10 | P22XU11 |  |

| 0E*  | 11 | 0 | 0 | 12 | P22XU19 |  |

| J18  |    |    |   |             |         |  |

|------|----|----|---|-------------|---------|--|

| +5V  | 1  | 0  | 0 | +<br>  2    | Q1P1    |  |

| LA14 | 3  | 0  | 0 | 4           | Q1P2    |  |

| 0E*  | 5  | 0- | 0 | 6           | P22XU25 |  |

| 0E*  | 7  | 0- | 0 | 8           | P22XU33 |  |

| 0E*  | 9  | 0  | 0 | 10          | P22XU28 |  |

| 0E*  | 11 | 0  | 0 | <br> 12<br> | P22XU36 |  |

| J17   |    |    |   |    |         |  |

|-------|----|----|---|----|---------|--|

| CS1*  | 1  | 0- | 0 | 2  | P20XU8  |  |

| CS2*  | 3  | 0- | 0 | 4  | P20XU16 |  |

| CS3*  | 5  | 0- | 0 | 6  | P20XU11 |  |

| CS4*  | 7  | 0- | 0 | 8  | P20XU19 |  |

| LA15  | 9  | 0  | 0 | 10 | Q2P26   |  |

| LA17  | 11 | 0  | 0 | 12 | +5V     |  |

| LA16  | 13 | 0  | o | 14 | Q2P27   |  |

| Q2P23 | 15 | 0  | 0 | 16 | WE*     |  |

| LA13  | 17 |    | 0 | 18 | GND     |  |

| LA12  | 19 | 0- | 0 | 20 | Q2P21   |  |

|       |    |    |   | T  |         |  |

EPROM QUAD 1

| J19   |    |    |       |    |         |  |

|-------|----|----|-------|----|---------|--|

| CS1*  | 1  | 0  | 0     | 2  | P20XU25 |  |

| CS2*  | 3  | 0  | 0     | 4  | P20XU33 |  |

| CS3*  | 5  | 0  | 0     | 6  | P20XU28 |  |

| CS4*  | 7  | 0  | 0     | 8  | P20XU36 |  |

| LA15  | 9  | 0  | 0     | 10 | Q1P26   |  |

| LA17  | 11 | 0  | <br>0 | 12 | +5V     |  |

| LA16  | 13 | 0  | 0     | 14 | Q1P27   |  |

| Q1P23 | 15 | o  | o     | 16 | WE*     |  |

| LA13  | 17 | 0  | 0     | 18 | GND     |  |

| LA12  | 19 | 0- | 0     | 20 | Q1P21   |  |

| ++    |    |    |       |    |         |  |

EPROM QUAD 2

Header configuration for 4K x 8 EPROM memory devices (HN462532, HN462732, MCM2532, NMC2532, TMS2532) is shown below:

Header configuration for 8K x 8 EPROM memory devices (MCM68764, MCM68766) is shown below:

Header configuration for 8K x 8 EPROM memory devices (AM2764, HN2764, I2764, MBM48764, MK2764, MSM2764, TMM2764, UPD2764) is shown below:

| J3 |   |

|----|---|

| +  | + |

| 0  | 0 |

| +  | + |

| 1  | 2 |

| J11 |   |   |  |  |

|-----|---|---|--|--|

| İ   | 0 |   |  |  |

| +.  |   | 2 |  |  |

| J16  |    |    |              |         |  |

|------|----|----|--------------|---------|--|

| +5V  | 1  | 00 | 2            | Q2P1    |  |

| LA14 | 3  | 00 | 4            | Q2P2    |  |

| 0E*  | 5  | 00 | 6            | P22XU8  |  |

| 0E*  | 7  | 00 | 8            | P22XU16 |  |

| 0E*  | 9  | 00 | 10           | P22XU11 |  |

| 0E*  | 11 | 00 | <br> 12<br>+ | P22XU19 |  |

|    | J | 1 | 7 |   |   |   |

|----|---|---|---|---|---|---|

| +- |   | _ | - | - | - | ÷ |

CS1\* 1 | 0---0 | 2 P20XU8

CS2\* 3 0---0 4 P20XU16

CS3\* 5 0---0 6 P20XU11

CS4\* 7 0---0 8 P20XU19

0 L

o |10 Q2P26

|12 +5V

o 14 Q2P27

GND

0 16 WE\*

o |18

LA15 9 0

LA17 11 | 0

LA16 13 | o

Q2P23 15

LA13 17

| J18  |    |    |    |         |  |  |

|------|----|----|----|---------|--|--|

| +5V  | 1  | 00 | 2  | Q1P1    |  |  |

| LA14 | 3  | 00 | 4  | Q1P2    |  |  |

| 0E*  | 5  | 00 | 6  | P22XU25 |  |  |

| 0E*  | 7  | 00 | 8  | P22XU33 |  |  |

| 0E*  | 9  | 00 | 10 | P22XU28 |  |  |

| 0E*  | 11 | 00 | 12 | P22XU36 |  |  |

| ++   |    |    |    |         |  |  |

| J19                 |    |    |   |    |         |  |

|---------------------|----|----|---|----|---------|--|

| CS1*                | 1  | 0- | 0 | 2  | P20XU25 |  |

| CS2*                | 3  | 0- | 0 | 4  | P20XU33 |  |

| CS3*                | 5  | 0- | 0 | 6  | P20XU28 |  |

| CS4*                | 7  | 0- | 0 | 8  | P20XU36 |  |

| LA15                | 9  | o  | ο | 10 | Q1P26   |  |

| LA17                | 11 | 0  | 0 | 12 | +5V     |  |

| LA16                | 13 | 0  | 0 | 14 | Q1P27   |  |

| Q1P23               | 15 | 0  | o | 16 | WE*     |  |

| LA13                | 17 | 0  | o | 18 | GND     |  |

| LA12 19 00 20 Q1P21 |    |    |   |    |         |  |

| EPROM QUAD 2        |    |    |   |    |         |  |

| EPR |  |  |

|-----|--|--|

|     |  |  |

+----+ ųu

LA12 19 0---0 20 Q2P21

0 1

0

Header configuration for 8K x 8 EPROM memory devices (NMC2564, TMS2564) is shown below:

| J3 |   |   |  |  |

|----|---|---|--|--|

| +- |   | + |  |  |

|    | 0 | 0 |  |  |

| +- |   | + |  |  |

|    | 1 | 2 |  |  |

| J16   |       |            |        |      |         |  |  |  |

|-------|-------|------------|--------|------|---------|--|--|--|

| +5V   | 1     | 0          | -0     | 2    | Q2P1    |  |  |  |

| LA14  | 3     | 0          | 0      | 4    | Q2P2    |  |  |  |

| 0E*   | 5     | _1<br>  0  | 0      | 6    | P22XU8  |  |  |  |

| 0E*   | 7     | 0          | 0      | 8    | P22XU16 |  |  |  |

| 0E*   | 9     | 00         |        | 10   | P22XU11 |  |  |  |

| 0E*   | 11    | 0          | 0      | 12   | P22XU19 |  |  |  |

|       | -<br> | +          |        |      |         |  |  |  |

|       |       | JI         | 1      |      |         |  |  |  |

| CS1*  |       | 0          | 0<br>  | 2    | P20XU8  |  |  |  |

| CS2*  | 3     | 0          | 0      | 4    | P20XU16 |  |  |  |

| CS3*  | 5     | 0          | 0      | 6    | P20XU11 |  |  |  |

| CS4*  | 7     | 0          | _0     | 8    | P20XU19 |  |  |  |

| LA15  | 9     | 0          | o      | 10   | Q2P26   |  |  |  |

| LA17  | 11    | 0          | 0      | 12   | +5V     |  |  |  |

| LA16  | 13    | o          | 0      | 14   | Q2P27   |  |  |  |

| Q2P23 | 15    | 0          | 0      | <br> | WE*     |  |  |  |

| LA13  | 17    | _ <br>  o_ | 0      | 18   | GND     |  |  |  |

| LA12  | 19    | 0          | ا<br>0 | 20   | Q2P21   |  |  |  |

|       |       | r          |        | F    |         |  |  |  |

EPROM QUAD 2

J11 | 0 0 | +----+ 1 2

| J18   |    |             |        |    |         |  |  |  |

|-------|----|-------------|--------|----|---------|--|--|--|

| +5V   | 1  | 0           | 0      | 2  | Q1P1    |  |  |  |

| LA14  | 3  | 0           | 0      | 4  | Q1P2    |  |  |  |

| 0E*   | 5  | _ <br>  0-· | 0      | 6  | P22XU25 |  |  |  |

| 0E*   | 7  | 0           | 0      | 8  | P22XU33 |  |  |  |

| 0E*   | 9  | 00          |        | 10 | P22XU28 |  |  |  |

| 0E*   | 11 | 00          |        | 12 | P22XU36 |  |  |  |

|       |    |             |        |    |         |  |  |  |

|       |    | J           | ļ      |    |         |  |  |  |

| CS1*  | 1  | 0           | o<br>o | 2  | P20XU25 |  |  |  |

| CS2*  | 3  | 0           | 0      | 4  | P20XU33 |  |  |  |

| CS3*  | 5  | 0           | 0      | 6  | P20XU28 |  |  |  |

| C\$4* | 7  | 0           | 0      | 8  | P20XU36 |  |  |  |

| LA15  | 9  | o           | 0      | 10 | Q1P26   |  |  |  |

| LA17  | 11 | 0           | 0      | 12 | +5V     |  |  |  |

| LA16  | 13 | 0           | o      | 14 | Q1P27   |  |  |  |

| Q1P23 | 15 | 0           | 0      | 16 | WE*     |  |  |  |

| LA13  | 17 | _ <br>  0_  | 0      | 18 | GND     |  |  |  |

| LA12  | 19 | 0           | 0      | 20 | Q1P21   |  |  |  |

| ++    |    |             |        |    |         |  |  |  |

2

Header configuration for 16K x 8 EPROM memory devices (AM27128, I27128, MBM27128) is shown below:

| + |

|---|

| 0 |

| + |

| 2 |

|   |

| J16  |    |    |     |         |  |  |

|------|----|----|-----|---------|--|--|

|      |    |    | ŧ.  |         |  |  |

| +5V  | 1  | 00 | 2   | Q2P1    |  |  |

| LA14 | 3  | 00 | 4   | Q2P2    |  |  |

|      | •  |    | i ' | 4-1-    |  |  |

| 0E*  | 5  | 00 | 6   | P22XU8  |  |  |

|      | _  |    | ļ   |         |  |  |

| 0E*  | 7  | 00 | 8   | P22XU16 |  |  |

| 0F*  | 9  | 00 | 10  | P22XU11 |  |  |

| UL.  | 5  | 00 | 10  | 1227011 |  |  |

| 0E*  | 11 | 00 | 12  | P22XU19 |  |  |

|      | -  | +  | F   |         |  |  |

|       |    |     | +  |         |

|-------|----|-----|----|---------|

| CS1*  | 1  | 00  | 2  | P20XU8  |

| CS2*  | 3  | 00  | 4  | P20XU16 |

| CS3*  | 5  | 00  | 6  | P20XU11 |

| CS4*  | 7  | 00  | 8  | P20XU19 |

| LA15  | 9  | 00  | 10 | Q2P26   |

| LA17  | 11 | 0 0 | 12 | +5V     |

| LA16  | 13 | 0 0 | 14 | Q2P27   |

| Q2P23 | 15 | 0 0 | 16 | WE*     |

| LA13  | 17 | 0 0 | 18 | GND     |

| LA12  |    | 00  | 20 | Q2P21   |

|       | -  |     | Ŧ  |         |

|       |    |     |    |         |

EPROM QUAD 1

OE\* 7 0---0 8 P22XU33 OE\* 9 0---0 10 P22XU28

|       |    | J | 19 |          |         |  |

|-------|----|---|----|----------|---------|--|

| CS1*  | 1  | 0 | 0  | +<br>  2 | P20XU25 |  |

| CS2*  | 3  | 0 | 0  | 4        | P20XU33 |  |

| CS3*  | 5  | 0 | 0  | 6        | P20XU28 |  |

| CS4*  | 7  | 0 | 0  | 8        | P20XU36 |  |

| LA15  | 9  | 0 | 0  | 10       | Q1P26   |  |

| LA17  | 11 | 0 | 0  | 12       | +5V     |  |

| LA16  | 13 | 0 | 0  | 14       | Q1P27   |  |

| Q1P23 | 15 | 0 | 0  | 16       | WE*     |  |

| LA13  | 17 | 0 | 0  | 18       | GND     |  |

| LA12  | 19 | 0 | 0  | 20       | Q1P21   |  |

|       |    |   |    |          |         |  |

J11 +----+ | 0 0 | +----+ 1 2

J18 +5V 1 | 0---0 | 2 Q1P1 LA14 3 | 0---0 | 4 Q1P2

OE\* 5 | 0---0 | 6 P22XU25

0E\* 11 | 0---0 | 12 P22XU19

+----+

EPROM QUAD 2

J11 +----+ | 0 0 | +---+ 1 2

Header configuration for  $16K \times 8$  EPROM memory devices (TMS27128) is shown below:

|   | J3        |   |

|---|-----------|---|

| İ | <br>0<br> | 0 |

| • |           | 2 |

|       |     |   | JI         | 16      |    |         |       |                |   | J        | 18      |    |         |

|-------|-----|---|------------|---------|----|---------|-------|----------------|---|----------|---------|----|---------|

|       | +5V | 1 | 0          | 0       | 2  | Q2P1    |       | +5V            | 1 | 0-       | 0       | 2  | Q1P1    |

| LA14  | 3   |   | _0         | 0       | 4  | Q2P2    | LA14  | 3_             |   | _0       | o       | 4  | Q1P2    |

| 0E*   | 5   |   | 0          | <br>·-0 | 6  | P22XU8  | 0E*   | 5              | Ţ | 0        | 0       | 6  | P22XU25 |

| 0E*   | 7   |   | 0          | 0       | 8  | P22XU16 | 0E*   | 7              |   | 0        | 0       | 8  | P22XU33 |

| 0E*   | 9   |   | 0          | -0      | 10 | P22XU11 | 0E*   | 9              |   | 0        | 0       | 10 | P22XU28 |

| 0E*   | 11  |   | 0          | -0      | 12 | P22XU19 | 0E*   | 11             |   | 0        | 0       | 12 | P22XU36 |

|       |     |   |            |         | r  |         |       |                |   |          |         | F  |         |

|       |     |   | JI         | 17      |    |         |       |                |   | J        | 9       |    |         |

| CS1*  | 1   |   | 0          | 0       | 2  | P20XU8  | CS1*  | 1              |   | 0        | 0       | 2  | P20XU25 |

| CS2*  | 3   |   | 0          | 0       | 4  | P20XU16 | CS2*  | 3              |   | 0        | 0       | 4  | P20XU33 |

| C\$3* | 5   |   | 0          | 0       | 6  | P20XU11 | CS3*  | 5              |   | o        | 0       | 6  | P20XU28 |

| CS4*  | 7   |   | o          | 0       | 8  | P20XU19 | CS4*  | 7              |   | o        | 0       | 8  | P20XU36 |

| LA15  | 9   |   | _0         | 1_<br>0 | 10 | Q2P26   | LA15  | 9              |   | _0       | 1_<br>0 | 10 | Q1P26   |

| LA17  | 11  |   | о          | 0       | 12 | +5V     | LA17  | 11             |   | ο        | 0       | 12 | +5V     |

| LA16  | 13  |   | 0          | _0      | 14 | Q2P27   | LA16  | 13             |   | o        | ,_0     | 14 | Q1P27   |

| Q2P23 | 15  | l | _0         | o       | 16 | WE*     | Q1P23 | 15             |   | _0       | 0       | 16 | WE*     |

| LA13  | 17  |   | 0          | _0      | 18 | GND     | LA13  | 17             |   | 0        | <br> _0 | 18 | GND     |

| LA12  | 19  |   | _<br>  0-· | 0       | 20 | Q2P21   | LA12  | 1 <del>9</del> |   | _<br>  0 | 0       | 20 | Q1P21   |

|       |     | - |            |         | ۲  |         |       |                | - | +        |         | +  |         |

EPROM QUAD 1

EPROM QUAD 2

Header configuration for 32K x 8  $\ensuremath{\mathsf{EPROM}}$  memory devices (AM27256, I27256) is shown below:

| J3 |   |

|----|---|

| +  | + |

| 0  |   |

| +  | + |

| 1  | 2 |

| J16  |    |    |    |         |  |  |  |

|------|----|----|----|---------|--|--|--|

| +5V  | 1  | 00 | 2  | Q2P1    |  |  |  |

| LA14 | 3  | 00 | 4  | Q2P2    |  |  |  |

| 0E*  | 5  | 00 | 6  | P22XU8  |  |  |  |

| 0E*  | 7  | 00 | 8  | P22XU16 |  |  |  |

| 0E*  | 9  | 00 | 10 | P22XU11 |  |  |  |

| 0E*  | 11 | 00 | 12 | P22XU19 |  |  |  |

|      |    |    | г  |         |  |  |  |

|      |    | J18 |    |         |  |  |  |

|------|----|-----|----|---------|--|--|--|

| +5V  | 1  | 00  | 2  | Q1P1    |  |  |  |

| LA14 | 3  | 00  | 4  | Q1P2    |  |  |  |

| 0E*  | 5  | 00  | 6  | P22XU25 |  |  |  |

| 0E*  | 7  | 00  | 8  | P22XU33 |  |  |  |

| 0E*  | 9  | 00  | 10 | P22XU28 |  |  |  |

| 0E*  | 11 | 00  | 12 | P22XU36 |  |  |  |

| ++   |    |     |    |         |  |  |  |

J11 +----+ | 0 0 | +---+ 1 2

| J1 | 7 |

|----|---|

|    |   |

| 017          |           |     |    |         |  |  |  |

|--------------|-----------|-----|----|---------|--|--|--|

| CS1*         | 1         | 00  | 2  | P20XU8  |  |  |  |

| CS2*         | 3         | 00  | 4  | P20XU16 |  |  |  |

| CS3*         | 5         | 00  | 6  | P20XU11 |  |  |  |

| CS4*         | 7         | 00  | 8  | P20XU19 |  |  |  |

| LA15         | 9         | 00  | 10 | Q2P26   |  |  |  |

| LA17         | 11        | 0 0 | 12 | +5V     |  |  |  |

| LA16         | 13        | 00  | 14 | Q2P27   |  |  |  |

| Q2P23        | 15        | 0 0 | 16 | WE*     |  |  |  |

| LA13         | 17        | 00  | 18 | GND     |  |  |  |

| LA12         | 19        | 00  | 20 | Q2P21   |  |  |  |

|              | <b>+-</b> |     |    |         |  |  |  |

| EPROM QUAD 1 |           |     |    |         |  |  |  |

| J19   |    |     |    |         |  |  |  |

|-------|----|-----|----|---------|--|--|--|

| CS1*  | 1  | 00  | 2  | P20XU25 |  |  |  |

| CS2*  | 3  | 00  | 4  | P20XU33 |  |  |  |

| CS3*  | 5  | 00  | 6  | P20XU28 |  |  |  |

| CS4*  | 7  | 00  | 8  | P20XU36 |  |  |  |

| LA15  | 9  | 00  | 10 | Q1P26   |  |  |  |

| LA17  | 11 | 0 0 | 12 | +5V     |  |  |  |

| LA16  | 13 | 00  | 14 | Q1P27   |  |  |  |

| Q1P23 | 15 | 0 0 | 16 | WE*     |  |  |  |

| LA13  | 17 | 0 0 | 18 | GND     |  |  |  |

| LA12  | 19 | 00  | 20 | Q1P21   |  |  |  |

|       | ++ |     |    |         |  |  |  |

EPROM QUAD 2

Header configuration for  $32K \times 8$  EPROM memory devices (TMS27256) is shown below:

| J3       |   |

|----------|---|

| +<br>  0 | 0 |

| +        | 2 |

|       |     |           | J1       | 6         |    |            |       |     |   | J18  |     |         |

|-------|-----|-----------|----------|-----------|----|------------|-------|-----|---|------|-----|---------|

|       | +51 | V 1       | 0        | -0        | 2  | Q2P1       |       | +5V | 1 | 00   | 2   | Q1P1    |

| LA14  | 3   |           | _0       | 0         | 4  | Q2P2       | LA14  | 3 _ |   | _0 0 | 4   | Q1P2    |

| 0E*   | 5   |           | 0        | _ <br>·-0 | 6  | P22XU8     | 0E*   | 5   | Ţ | 00   | 6   | P22XU25 |

| 0E*   | 7   |           | 0        | -0        | 8  | P22XU16    | 0E*   | 7   |   | oc   | 8   | P22XU33 |

| 0E*   | 9   |           | 0        | -0        | 10 | P22XU11    | 0E*   | 9   |   | 00   | 10  | P22XU28 |

| 0E*   | 11  |           | 0        | -0        | 12 | P22XU19    | 0E*   | 11  |   | 00   | 12  | P22XU36 |

|       |     |           | <b>+</b> |           | ł  |            |       |     |   |      | -+  |         |

|       |     |           | J1       |           |    |            |       |     |   | J19  |     |         |

| CS1*  | 1   |           | 0        | 0         | +  | P20XU8     | CS1*  | 1   |   | 0 0  | 2   | P20XU25 |

| CS2*  | 3   |           | 0        | 0         | 4  | P20XU16    | CS2*  | 3   |   | 0    | 4   | P20XU33 |

| CS3*  | 5   |           | 0        | 0         | 6  | P20XU11    | CS3*  | 5   |   | 0    | 6   | P20XU28 |

| CS4*  | 7   |           | 0        | 0         | 8  | P20XU19    | CS4*  | 7   |   | 0    | 8   | P20XU36 |

| LA15  | 9   |           | _0       | 1_<br>0   | 10 | Q2P26      | LA15  | 9   |   | _0 0 | 10  | Q1P26   |

| LA17  | 11  |           | 0        | 0         | 12 | +5V        | LA17  | 11  |   | 0 0  | 12  | +5V     |

| LA16  | 13  |           | 0        | -0        | 14 | Q2P27      | LA16  | 13  |   | 0C   | 14  | Q1P27   |

| Q2P23 | 15  | <br> <br> | _0       | 0         | 16 | WE*        | Q1P23 | 15  |   | _0 0 | 16  | WE*     |

| LA13  | 17  |           | 0        | 0         | 18 | GND        | LA13  | 17  |   | 0    |     | GND     |

| LA12  | 19  |           | <br>  0  | -0        | 20 | 1<br>Q2P21 | LA12  | 19  |   | 00   | 20  | Q1P21   |

|       |     | -         | +        |           | t  |            |       |     | - | +    | •-+ |         |

EPROM QUAD 1

EPROM QUAD 2

|       |    | J3<br>++    |              |          | J11         |            |

|-------|----|-------------|--------------|----------|-------------|------------|

|       |    | 0 0  <br>++ |              | -        | 0 0  <br>++ |            |

|       |    | 12          |              |          | 12          |            |

|       |    | J16         |              | _        | J18         |            |

| +5V   | 1  | 0 0_        | 2 Q2P1       | +5V 1    | 0 0         | 2 Q1P1     |

| LA14  | 3  | 00          | 4 Q2P2       | LA14 3   | 00          | 4 Q1P2     |

| 0E*   | 5  | 00          | 6 P22XU8     | 0E* 5    | 00          | 6 P22XU25  |

| 0E*   | 7  | 00          | 8 P22XU16    | 0E* 7    | 00          | 8 P22XU33  |

| 0E*   | 9  | 00          | 10 P22XU11   | 0E* 9    | 00          | 10 P22XU28 |

| 0E*   |    | 00          | 12 P22XU19   | 0E* 11   |             | 12 P22XU36 |

|       |    | ++          |              |          | ++          |            |

|       |    | J17         |              |          | J19         |            |

| CS1*  | 1  | 00          | 2 P20XU8     | CS1* 1   | 00          | 2 P20XU25  |

| CS2*  | 3  | 00          | 4 P20XU16    | CS2* 3   | 00          | 4 P20XU33  |

| CS3*  | 5  | 00          | 6 P20XU11    | CS3* 5   | 00          | 6 P20XU28  |

| CS4*  | 7  | 00          | 8 P20XU19    | CS4* 7   | 00          | 8 P20XU36  |

| LA15  | 9  | 00          | 10 Q2P26     | LA15 9   | 00          | 10 Q1P26   |

| LA17  | 11 | 0 0         | 12 +5V       | LA17 11  | 0 0         | 12 +5V     |

| LA16  | 13 | 0 0         | 14 Q2P27     | LA16 13  | 0 0 I       | 14 Q1P27   |

| Q2P23 | 15 | 0 0         | _ <br>16 WE* | Q1P23 15 | 0 0         | 16 WE*     |

| LA13  | 17 | 0 0         | 18 GND       | LA13 17  | 0 0         | 18 GND     |

| LA12  |    | 00          |              | LA12 19  | 00          | 20 Q1P21   |

|       |    |             |              |          | DOM ALLAD 2 |            |

Header configuration for  $32K \times 8$  EPROM memory devices (MK27256) is shown below:

Header configuration for 64K x 8 EPROM memory devices is shown below:

| J3 |    |

|----|----|

| +  | +  |

| 0  | -0 |

| +  | +  |

| 1  | 2  |

| J11 |

|-----|

| ++  |

| 00  |

| ++  |

| 12  |

| J16  |    |   |    |    |         |  |

|------|----|---|----|----|---------|--|

| +5V  | 1  | 0 | 0  | 2  | Q2P1    |  |

| LA14 | 3  | 0 | -0 | 4  | Q2P2    |  |

| 0E*  | 5  | 0 | 0  | 6  | P22XU8  |  |

| 0E*  | 7  | 0 | 0  | 8  | P22XU16 |  |

| 0E*  | 9  | 0 | 0  | 10 | P22XU11 |  |

| 0E*  | 11 | 0 | 0  | 12 | P22XU19 |  |

|      |    |   |    |    |         |  |

| J18  |    |          |   |         |         |

|------|----|----------|---|---------|---------|

| +5V  | 1  | +<br>  0 | 0 | 2       | Q1P1    |

| LA14 | 3  | 0        | 0 | 4       | Q1P2    |

| 0E*  | 5  | o        | 0 | 6       | P22XU25 |

| 0E*  | 7  | <br>  o  | 0 | 8       | P22XU33 |

| 0E*  | 9  | <br>  0  | 0 | 10      | P22XU28 |

| 0E*  | 11 | 0-       | 0 | <br> 12 | P22XU36 |

| ++   |    |          |   |         |         |

J19

CS1\*

1

o---o

2

P20XU25

CS2\*

3

o---o

4

P20XU33

CS3\*

5

o---o

6

P20XU28

CS4\*

7

o---o

8

P20XU36

LA15 9 0---0 10 Q1P26

LA16 13 | 0---0 | 14 Q1P27

LA17 11 0 0 12 +5V

Q1P23 15 0 0 16 WE\*

LA13 17 0 0 18 GND

J17

| C\$1* | 1  | 00  | +<br>  2 | P20XU8  |  |  |

|-------|----|-----|----------|---------|--|--|

| CS2*  | 3  | 00  | 4        | P20XU16 |  |  |

| CS3*  | 5  | 00  | 6        | P20XU11 |  |  |

| CS4*  | 7  | 00  | 8        | P20XU19 |  |  |

| LA15  | 9  | 00  | 10       | Q2P26   |  |  |

| LA17  | 11 | 0 0 | 12       | +5V     |  |  |

| LA16  | 13 | 00  | 14       | Q2P27   |  |  |

| Q2P23 | 15 | 0 0 | 16       | WE*     |  |  |

| LA13  | 17 | 0 0 | 18       | GND     |  |  |

| LA12  | 19 | 00  | 20       | Q2P21   |  |  |

| ++    |    |     |          |         |  |  |

| +     | +    |   |

|-------|------|---|

| EPROM | QUAD | 2 |

LA12 19 0---0 20 Q1P21

Header configuration for 2K x 8 RAM memory devices is shown below:

| JS       | 3  |

|----------|----|

| +<br>  0 | οΪ |

| +        | 2  |

| J11 |   |       |   |  |  |

|-----|---|-------|---|--|--|

|     | 0 | <br>0 |   |  |  |

| +·  | 1 | 2     | + |  |  |

|      | J16 |   |   |        |         |  |  |  |

|------|-----|---|---|--------|---------|--|--|--|

| +5V  | 1   | 0 | 0 | 2      | Q2P1    |  |  |  |

| LA14 | 3   | 0 | 0 | 4      | Q2P2    |  |  |  |

| 0E*  | 5   | o | 0 | 6      | P22XU8  |  |  |  |

| 0E*  | 7   | 0 | 0 | 8      | P22XU16 |  |  |  |

| 0E*  | 9   | 0 | 0 | 10     | P22XU11 |  |  |  |

| 0E*  | 11  | 0 | 0 | 12<br> | P22XU19 |  |  |  |

| J18  |    |   |   |    |         |

|------|----|---|---|----|---------|

| +5V  | 1  | 0 | 0 | 2  | Q1P1    |

| LA14 | 3  | 0 | 0 | 4  | Q1P2    |

| 0E*  | 5  | o | 0 | 6  | P22XU25 |

| 0E*  | 7  | 0 | 0 | 8  | P22XU33 |

| 0E*  | 9  | 0 | 0 | 10 | P22XU28 |

| 0E*  | 11 | 0 |   | 12 | P22XU36 |

| ++   |    |   |   |    |         |

|       | 4  | L       | r. |         |

|-------|----|---------|----|---------|

| CS1*  | 1  | 00      | 2  | P20XU8  |

| CS2*  | 3  | 00      | 4  | P20XU16 |

| CS3*  | 5  | 00      | 6  | P20XU11 |

| CS4*  | 7  | 00      | 8  | P20XU19 |

| LA15  | 9  | 0 0     | 10 | Q2P26   |

| LA17  | 11 | 0 0     | 12 | +5V     |

| LA16  | 13 | 0 0     | 14 | Q2P27   |

| Q2P23 | 15 | 00      | 16 | WE*     |

| LA13  | 17 | 0 0     | 18 | GND     |

| LA12  | 19 | 00      | 20 | Q2P21   |

|       |    | <b></b> | г  |         |

RAM QUAD 2

J19

CS1\*

1

0---0

2

P20XU25

CS2\*

3

0---0

4

P20XU33

CS3\*

5

0---0

6

P20XU38

CS4\*

7

0---0

8

P20XU36

LA15

9

0

0

10

Q1P26

LA17

11

0

0

12

+5V

LA16

13

0

0

14

Q1P27

Q1P23

15

0---0

16

WE\*

LA13

17

0

0

18

GND

LA12

19

0---0

20

Q1P21

RAM QUAD 1

Header configuration for 8K x 8 RAM memory devices is shown below:

|   | J3 |   |  |

|---|----|---|--|

| + |    | + |  |

| 0 | 0  | 1 |  |

| + |    | + |  |

| 1 | 2  |   |  |

| J11 |   |  |

|-----|---|--|

| +   | + |  |

| 0   | 0 |  |

| +   | + |  |

| 1   | 2 |  |

|       |    | J16 | L  |         |       |    | J18 |    |        |

|-------|----|-----|----|---------|-------|----|-----|----|--------|

| +5٧   | 1  | 00  | 2  | Q2P1    | +5V   | 1  | 00  | 2  | Q1P1   |

| LA14  | 3  | 00  | 4  | Q2P2    | LA14  | 3  | 00  | 4  | Q1P2   |

| 0E*   | 5  | 00  | 6  | P22XU8  | 0E*   | 5  | 00  | 6  | P22XU2 |

| 0E*   | 7  | 00  | 8  | P22XU16 | 0E*   | 7  | 00  | 8  | P22XU3 |

| 0E*   | 9  | 00  | 10 | P22XU11 | 0E*   | 9  | 00  | 10 | P22XU2 |

| 0E*   | 11 | 00  | 12 | P22XU19 | 0E*   | 11 | 00  | 12 | P22XU3 |

|       |    |     |    |         |       | -  |     | T  |        |

|       |    | J17 | ÷  |         |       | _  | J19 | L  |        |

| CS1*  | 1  | 00  | 2  | P20XU8  | CS1*  | 1  | 00  | 2  | P20XU2 |

| CS2*  | 3  | 00  | 4  | P20XU16 | CS2*  | 3  | 00  | 4  | P20XU3 |

| CS3*  | 5  | 00  | 6  | P20XU11 | CS3*  | 5  | 00  | 6  | P20XU2 |

| CS4*  | 7  | 00  | 8  | P20XU19 | CS4*  | 7  | 00  | 8  | P20XU3 |

| LA15  | 9  | 0 0 | 10 | Q2P26   | LA15  | 9  | 0 0 | 10 | Q1P26  |

| LA17  | 11 |     | 12 | +5¥     | LA17  | 11 | 0 0 | 12 | +5V    |

| LA16  | 13 | 0 0 | 14 | Q2P27   | LA16  | 13 | 0 0 | 14 | Q1P27  |

| Q2P23 | 15 |     | 16 | WE*     | Q1P23 | 15 | 0 0 | 16 | WE*    |

| LA13  | 17 | 0 0 | 18 | GND     | LA13  | 17 | 0 0 | 18 | GND    |

| LA12  | 19 | 00  | 20 | Q2P21   | LA12  | 19 | 00  | 20 | Q1P21  |

|       |    | T   | т  |         |       | •  |     | т  |        |

RAM QUAD 2

> +----+ RAM QUAD 1

# Bus Time-Out Select Header (J4)

Header J4 allows the user to select the bus time-out time after Data Strobe 0 (DSO) or Data Strobe 1 (DSI) is asserted. A time-out asserts Bus Error (BERR\*). A time-out time in microseconds is selected by positioning a jumper on the desired time. Only one jumper may be installed at a time. If the controller module is not selected as the system controller, the bus time-out should be OFF. A jumper may be installed between pins 11 and 12 to turn the time-out off. Header J4 is illustrated below:

|    | J | ŧ |          |        |     |          |

|----|---|---|----------|--------|-----|----------|

| 1  | 0 | 0 | +<br>  2 | 2.7 us | -+  |          |

| 3  | o | 0 | 4        | 5.5 us |     |          |

| 5  | 0 | 0 | 6        | 11 us  | BUS | TIME-OUT |

| 7  | 0 | 0 | 8        | 44 us  |     |          |

| 9  | 0 | 0 | 10       | 178 us |     |          |

| 11 | 0 | 0 | 12       | OFF    | -+  |          |

| -  | + |   | t        |        |     |          |

## Clock Damping Shorting Select Headers (J5, J6)

An 11 ohm damping resistor may be placed in series with the driver for the Serial Clock (SERCLK) by removing the jumper from header J5. An 11 ohm damping resistor may be placed in series with the driver for the System Clock (SYSCLK) by removing the jumper from header J6. As shown below, the module is shipped with jumpers on the headers.

| J5                 | J6                 |

|--------------------|--------------------|

| ++<br>  00  <br>++ | ++<br>  00  <br>++ |

| 1 2                | 1 2                |

| SERCLK             | SYSCLK             |

# System Controller Select Header (J7)

This module may be selected as the system controller by installing all four jumpers on the header as shown below. If the module is not to be the system controller, all four jumpers must be removed from the header and header J4 pins 11 and 12 jumpered. The module is factory-configured as the system controller. If the bus arbiter is disabled, bus arbitration signals must be configured on the backplane as though the controller was an empty slot as shown in the VMEmodule Chassis Backplane Daisy-Chained Headers paragraph. The IACK bypass jumper must remain open.

|   | J7 |   |                    |

|---|----|---|--------------------|

| 1 | 00 | 2 | BCLR*              |

| 3 | 00 | 4 | BUS ARBITER ENABLE |

| 5 | 00 | 6 | SERCLK             |

| 7 | 00 | 8 | SYSCLK             |

| - | +  | F |                    |

I/O Base Address Select Header (512 Byte Boundaries) (J2O)

The address line must be low to correspond with a jumper installed. As shown below, the base address is FF1000.

|    | J20 |    | ADDRESS | LINE |

|----|-----|----|---------|------|

| 1  | 00  | 2  | A9      |      |

| 3  | 00  | 4  | A10     |      |

| 5  | 00  | 6  | A11     |      |

| 7  | 0 0 | 8  | A12     |      |

| 9  | 00  | 10 | A13     |      |

| 11 | 00  | 12 | A14     |      |

| 13 | 00  | 14 | A15     |      |

| -  | +   | +  |         |      |

#### JUMPER IN = ADDRESS LINE LOW

DEFAULT SHOWN = 10XX WITHIN SHORT ADDRESSING RANGE AM CODES = 2D OR 29

#### Time-of-Day Clock Power Select and Battery Charge Header (J21)