Division 6 - Lincoln Laboratory Massachusetts Institute of Technology Cambridge 39, Massachusetts

SUBJECT: MAGNETIC CORE SHIFT REGISTER EVALUATOR

To:

N. H. Taylor

From:

Carl J. Schultz

Date:

May 3, 1954

ABSTRACT:

The problem of evaluation of magnetic core shift register is presented from the point of view of minimizing the time required to determine operating margins. A brief description of the operation of a shift register is given, together with the procedure involved in determining the operating margins. The method of evaluation used in the system is outlined and an example of the results obtained is shown. No attempt is made to establish criteria for optimizing shift register operating margins - that is a judgment which is reserved for a consideration of the shift register application and requirements.

## A. Introduction

The realization of working magnetic core shift registers in the 100 KC range has been in the past a product of the art of combining engineering calculations with intuitively guided experimentation. The determination of the goodness of the product has been a particularly difficult job of evaluation because of the large number of variables involved. Every element in a magnetic core shift register is a factor which affects its operation, and in order that a useful register be born out of the labor of almost endless substitutions and time consuming investigations, it is desirable that a rapid method of experimentation be used. The automatic Evaluator described in this note performs the task of furnishing operating margins for a particular shift register in a small fraction of the time that would be required to find the information under the guidance of a human operator.

# B. Shift Register Characteristics

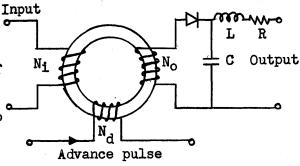

The type of register that is currently being investigated consists of the elements shown in Fig. 1 for the typical stage. The magnetic material that is used for operation at shifting frequencies of 100 KC and above is Mo-Permalloy tape. The magnetic flux of the core must first be set in one direction by a flow of current through the input winding, which is connected to the output winding terminals of the previous stage.

Memorandum M-2803 Page 2

Then an advance current pulse applied through the advance winding will set the magnetic flux in the opposite direction and will induce a voltage in the output winding. This voltage will cause current to flow in the forward direction of the diode. The capacitor will become charged through the forward resistance of the diode and the core output winding. However, it will discharge through the inductor, resistor, and the input winding of the succeeding stage of the shift register, thereby setting the magnetic flux of that core to the direction that may be defined as "zero". The condition of a core may be sensed at the time of application of the advance pulse. If the core had previously been set to "one," then the voltage induced in the output winding will be large during the advance pulse. If the core had been set to "zero" previously, only a small voltage will be induced in the output winding. The advance current pulse must be of such a duration that it will have ended soon enough in a particular stage of the register to allow the input current supplied from the coupling circuit of the preceding stage to be of sufficient amplitude and duration to set the flux to "one". This depends upon the capacitor discharge current magnitude and duration, which in turn is related to the selected values of R,L,C, the diode, the number of turns on the windings, and upon the previous advance current pulse amplitude and length. The coupling circuit serves to transfer the energy required to switch the succeeding core, and also to prevent energy from flowing in the backward direction to set the previous core to "one".

## C. Shift Register Operating Margins

The successful operation of the register depends upon the effective transfer of information from the core originally containing either a "one" or "zero" to the succeeding core. This transfer must be realized by means of the coupling circuit between the two cores. Every element in the coupling circuit, in addition to the advance pulse characteristics and the magnetic core characteristics, becomes a variable which makes the operation of the register either more or less successful. The timeconsuming task of combining these variables into an optimized working register can be resolved into a procedure which involves the following steps: (a) Design a coupling circuit for use with cores having particular flux change and switching time characteristics; (b) Construct at least four stages, connected so that the information circulates in the register; (c) Change the advance current pulse amplitude, length, and rise time and observe the limits for which the register continues to store and transfer all combinations of information successfully; (d) Becide whether the resulting margins represent a register which might be useful in a particular application (upon consideration of (1) the effects of advance pulse current driver tube deterioration, and (2) the required operating speed; (e) In the event that the operating margins do not represent a useful register, then, judicious changes of the variables should be made in order to shift the margins in the direction to fulfill the desired requirements, and (f) Retrace parts b, c, d, and e as many times as are necessary to obtain satisfactory limits of operation.

## D. Methods of Iteration

One method of obtaining the data outlined in the preceding paragraph involves the complete manual manipulation of all variables, in addition to the manual injection into the register of all possible combinations of "ones" and "zeros" that constitute the storage and transfer pattern of information. This primitive method, when associated with the necessary changing of many patterns of information and of many variables in many stages of the register, places considerable strain upon the mental and physical capabilities of the human control element during the long period of time involved.

Another method involves the use of an electronic control system, which brings about an appreciable reduction in the time consumed and in operator fatigue. The system automatically varies the advance current pulse amplitude and length at a rapid rate and presents, on an oscilloscope, a matrix pattern of intensified spots to indicate successful operations of the shift register. Patterns of information are also changed automatically. All other parameters must still be varied manually, but since that part of the total data-accumulation time is small, little could be gained by further automatizing the procedure.

## E. Automatic Evaluation

# E.l System timing

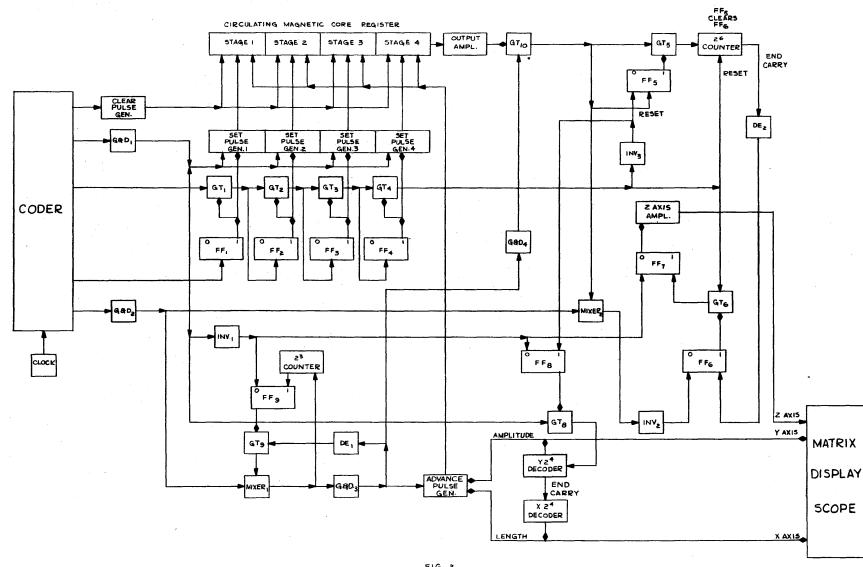

Figure 2 shows the block diagram of the system. An outline of the kind and the order of events that occur after each clock pulse is as follows (numbers indicate events displaced in time, and letters indicate events occurring simultaneously).

# 1. Time t<sub>1</sub> (clock pulse)

(A) "Clear" pulse occurs - this places the four cores of the register in the "zero" flux condition.

(B) Information "set" counter changes

- (a) Counter end carry pulse occurs if the previous counter number was llll and the display scope intensifies if the register output counter (FF5-GT5, 26 counter) had sensed the proper number (26) of mones shifted out of the register during all the combinations of binary numbers since the previous llll.

- (b) "Set" pulse generators 1, 2, 3, and 4 (standard 7AK7 gate tube circuit) are open or closed according to the configuration of "ones" held by the Information "Set" counter flip-flops.

- 2. Time  $t_1 + t_2$  ( $t_2$  determined by G +  $D_1$ )

- (A) "Set" pulse generators drive into the magnetic core register and set the cores to the same configuration of "ones" as contained in the Information "Set" counter.

- (B) "Advance" pulse burst generator ring (MX1, G + D3, DE1,  $GT_Q$ ) closes as a result of the change of state of  $FF_Q$ .

- (C) "Y" Decoder is pulsed if the last number held by the Information "Set" counter was llll and the end carry from that counter had opened GT8. The change of output of the "Y" decoder then causes the following.

- (a) Matrix Display scope y-position is changed.

- (b) "Advance" current pulse amplitude is changed to its next highest value, or to its minimum value if the Y decoder is reset (in this case, the Y decoder produces an end carry and changes the X decoder output, which in turn controls the advance current pulse width and also the Matrix Display 'scope x-position).

- (D) Z axis amplifier input is changed by FF, this ends the 'scope intensification pulse which presented a visual indication (on the Matrix Display 'scope) of the successful transfer and storage of information in the shift register.

- 3. Time  $t_1 + t_3 (t_3 > t_2, t_3$  determined by  $G + D_2$ )

- (A) A pulse passes through MX, and INV, and appears at the zero input of FF. This closes GT at the beginning of each burst of eight advance current pulses.

- (B) A series of eight pulses is generated in the advance pulse burst generator ring. This pulse burst serves two functions:

- (1) It initiates eight advance current pulses that transfer information twice around the 4-stage register (two complete cycles provide greater assurance of successful operation than only one cycle).

- (2) After the delay due to G + D,, the pulses are used as strobe pulses which sense the presence of "one" and "zero" output signals from the shift register as they appear at the grid of GT<sub>10</sub>. The output of GT<sub>10</sub> then goes to the register output counter (FF5, GT5, 2<sup>6</sup> counter) and through MX<sub>2</sub> and INV<sub>2</sub> to FF<sub>6</sub>.

## E.2 Error Detection

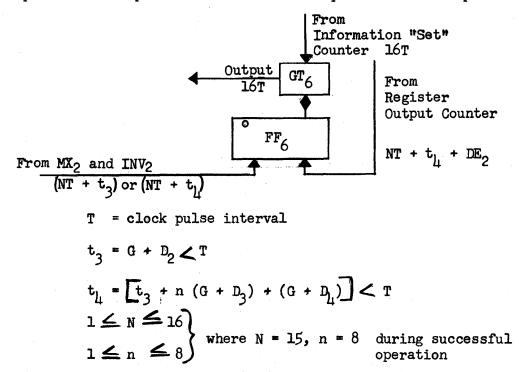

The successful transfer and storage of information in the shift register is determined by the occurrance of an end carry pulse from the Register Output counter just preceding an end carry pulse from the Information "Set" counter. The figure below shows the error detection system with its three inputs, one output, and associated timing. The cycle of operation is repetitive for intervals equal to 16 clock pulses.

The above arrangment assures that out of any number of shift register output pulses up to  $2^{12}$  - 1, only a precise count of  $2^6$  at the proper time will be detected and converted into an intensifying pulse on the Matrix Display 'scope. The occurance of  $2^{12}$  shift register output pulses is eliminated from becoming an indication of a successful operation by a toggle switch setting on the  $2^0$  lowspeed counter (Register Output Counter) by which FF5 clears FF6 and does not permit the generation of more than a single end carry from the Register Output Counter.

# F. Alternate Use of Evaluator

The application of the Evaluator has been extended to include the testing of a magnetic core counter employing the previously described shift register circuitry plus other circuits which perform the logical functions necessary for counting. This application eliminates the use of the Information "Set" counter and three of the "Set" pulse generators, since the number which is held by the magnetic core counter must be changed by a count of "l" for each operation and that is done by the core circuitry. In the testing of the circulating shift register, it is

necessary to change the information by control external to the register in order to completely determine the successful operation for all patterns of binary information. The magnetic core counter is tested for the successful storage and progressive counting through all the combination of four bits of information. If 25 "ones" are properly shifted out of the counter, the Matrix Display 'scope will indicate a successful operation for a particular value of current pulse length and amplitude.

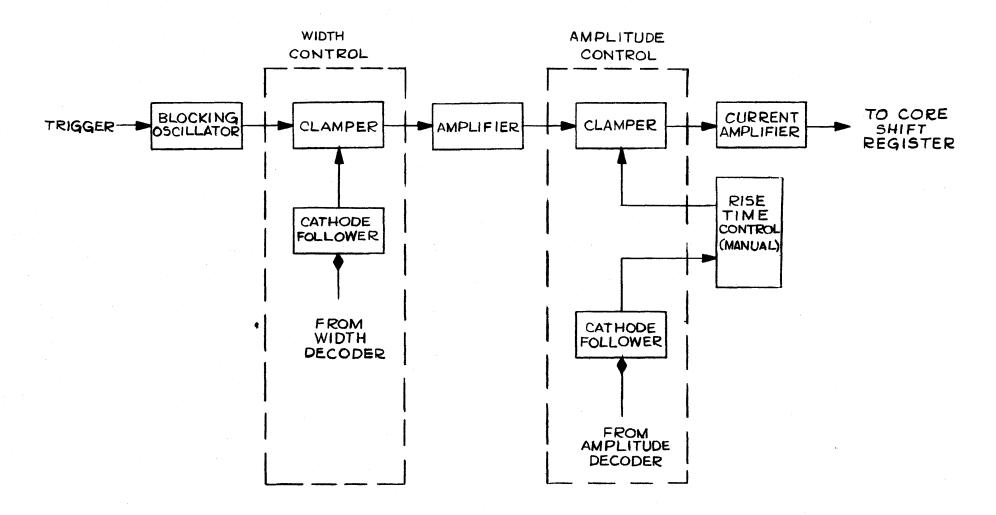

## G. Equipment

Standard test equipment is used for gate and delayed pulse generators, mixers, delays, 26 lowspeed counters, flip-flops and gates. The Matrix display 'scope is a DuMont 304-H. The "X" and "Y" decoders are made of plug-in type flip-flops. The Advance Pulse Generator is shown in block diagram form in Figure 3. The Clear Pulse Generator is similar to Figure 3, except that the "X" and "Y" decoder inputs and associated cathode fellowers are substituted for by manually operated amplitude and width controls. The Set Pulse Generators are similar to the Clear Pulse Generator, except that they contain 7AK7 current amplifiers rather than 6CD6's.

A feature of the Evaluator which increases its value as a time saver is the flexible arrangement of R, L, and C components. A wide range of values of each of the components has been assembled on rotary selector switches. Values of Resistance can be varied between 33 and 15,000 ohms with 26 intermediate values, C between 220 and 169,000 µµfd, and L between 0.033 and 25 mh. This adequately covers the widest range of values of these components that can be presently expected to be used. Connections between components are made through plug-in type terminal boards and leads. Magnetic cores and associated windings are mounted on minature tube socket assemblies, and diodes are mounted in spring clips. All of these connections and assemblies allow easy replacement and rearrangement of the component parts.

#### H. Results

The sketch below shows a sample pattern that appeared in the Matrix Display 'scope during the testing of a 4-stage shift register made of 1/8 mil Mo-Permalloy cores (5/16" diameter, 1/8" wide, 20 wraps). The coupling circuit is of the same configuration as that shown in Figure 1. The component values are:

C = 1000 μμfd, L = 15 mh,

R = 4700 ohms, N<sub>o</sub> = 100 turns,

N<sub>i</sub> = 150 turns, N<sub>d</sub> = 25 turns.

The rise time of the pulse was 0.3  $\mu$ sec and the fall time was 0.4  $\mu$ sec. The intensified spots indicate the coordinates at which the shift register successfully stores and transfers all combinations of four bits of binary information. The shifting rate was 100 KC and a complete display of the matrix appeared at minimum intervals of approximately two seconds.

## CONVERSION TABLE

|       | 16 | ١. |   | ٠ |              |     |     |   |    | 9        | •  | 9  | •   | 0  | •  |    |     |  |

|-------|----|----|---|---|--------------|-----|-----|---|----|----------|----|----|-----|----|----|----|-----|--|

|       | 15 | •  |   | • |              |     | •-  | 0 | •  | •        | •  |    |     |    | •  |    | •   |  |

| Į,,   | 14 |    | • | • | ٠            |     | •   | • | •  | 0        | ٠  | 0  | •   |    | •  | •  | • , |  |

| 3     | 13 | •  |   | - | •            | •   | 0   | • | •  | •        | 9. | •  | •   | •  |    | •  |     |  |

| ITUDE | 12 | •  | ٠ | • |              | •   | •   | • | •  | 0        | •  | •  | •   |    | •  | •  |     |  |

| 1     | 11 | •  | • | • | •            | ٠   | •   | • | •  | •        | •  | 0  | 6   |    | •  | •  | ٠   |  |

| 4     | 10 | •  | • | • | •            | •   | •   | • | •  | •        | •  |    | ٠.  |    | •  | •  | •   |  |

| 2     | 9  | ٠  | • | • | •            | •   | •   | • | 0  | •        | •  | •  | •   |    | ٠  | •  | •   |  |

| ST.   | B  | ٠  | ٠ | ٠ | 4            | •   | •   | Ø | •  | •        | 0  | •  | . • | •  | ٠  | ٠  | •   |  |

| •     | 7  | •  | ٠ | ٠ | •            | •   | •   | • | •  |          | ٠  | •  | •   | •  | •  | •  |     |  |

| lie.  | 6  | ٠  | ٠ | • | •            | •   | •   | • | •  | •        | ٠  |    | •   | •  | ٠  | •  | •   |  |

| SE    | 5  | ٠  |   | • |              | •   | •   | • | •  | •        | •  | •  | •   | •  | •  | •  | •   |  |

| 2     | 4  | ٠  | ٠ | • |              | ٠   | ٠   | ٠ |    | •        | •  | •  | •   | •  | ٠  | •  | •   |  |

| J     | 3  | ٠  | ٠ | ٠ | •            | •   | •   | ٠ | ٠  | ٠        | •  | •  | ٠   | •  | •  | •  | •   |  |

| •     | 2  | ÷  | ٠ | • | ٠            | •   | ٠   | • | •  | ٠        | ٠  | •  | ٠   | •  | •  | •  | •   |  |

|       | /  | ٠, | : | ; | ;            | ۰   | ;   | : | i  | ÷        |    | ;, | i   | in | ٠  | ;  | 16  |  |

|       |    | 1  | 1 | 3 | <del>"</del> | 9   | 0   | / | 0, | <b>y</b> | N) | // | KZ  | 13 | 14 | 10 | 10  |  |

|       |    |    |   | / | رر           | ٧., | 5/5 |   | 1  | Ξ,       | NG | 77 | 4   |    |    |    |     |  |

|       |    |    |   |   |              |     |     |   |    |          |    |    |     |    |    |    |     |  |

| Unit | Pulse<br>Length | Pulse<br>Amplitude |

|------|-----------------|--------------------|

| 1    | 1.3 μsec.       | 2.8 Amp. Turns     |

| 2    | 1.5             | 3.7                |

| 3    | 1.8             | 4.5                |

| 4    | 2.1             | 5.6                |

| 5    | 2.4             | 6.8                |

| 6    | 2.8             | 8.2                |

| 7    | 3.2             | 9.6                |

| 8    | 3.6             | 10.9               |

| 9    | 2• <del>1</del> | 11.8               |

| 10   | 7•8             | 13.2               |

| 11   | 7•0             | 14.4               |

| 12   | 70              | 16.3               |

| 13   | 5.9             | 18.0               |

| 14   | 6.4             | 19.8               |

| 15   | 6.9             | 21.3               |

| 16   | 7.3             | 22.5               |

# I. Discussion of Results

Upon consideration of the results presented on the display 'scope there might arise the question: "How reliable is the information?" The degree of reliability is dependent upon the accuracy of the method of detecting the successful operation of the shift register. That is done in the Evaluator by counting the number of "ones" that are shifted serially past a particular point in the register during the storage and transfer of all possible combinations of four bits of binary information. The error detection system shown on page 5 then allows an indication of successful operation only when precisely the correct number of "ones" have been counted. Although this method does not preclude the possibility that a correct count might occur upon the transfer of one or several incorrect patterns of information during a cycle of operation, the possibility appears to be an extremely remote one. The observer can easily verify the successful operation at any particular value of advance pulse amplitude and width by (a) stopping the X and Y decoders from changing with each clock pulse, (b) displaying the 16 groups of shift register binary outputs during a cycle of operation, and (c) visually checking the number, sequence, and arrangments of the output pulses.

Signed: C.J. Schultz

Approved: Fresh

CJS/rb

Drawings: C-47094

A-47095

FIG. 2

MAGNETIC CORE SHIFT REGISTER EVALUATOR

FIG. 3

# Distribution List for N. Taylor (When M-Notes are addressed to him)

# Internal Distribution

#### D. Arden

The author

R. Best

D. Brown

C. Corderman

R. Callahan

W. Thomas

A. Heineck

J. Jacobs

W. Linvill

R. Mayer-

P. Bagley

R. Nelson

K. Olsen

W. Papian

N. Taylor

R. von Buelow

## H. Wainwright

C. W. Watt

J. W. Forrester

R. R. Everett

S. H. Dodd

A. F. Falcione

Division 6-Library (15 to 20 Copies) M's by B. Paine--1 copy to V. Savio

A's--1 copy to R. Nelson

# External Distribution

A. P. Kromer (10 Copies of M-Notes for I.B.M.)

Bldg. 32 - Library

Air Force Cambridge Research Center Attention: Document Room--CRQ-SL-1. 230 Albany Street