# Maps: A Compiler-Managed Memory System for Software-Exposed Architectures

by

# Rajeev Barua

B.Tech., Computer Science and Engineering Indian Institute of Technology, New Delhi, 1992

S.M., Electrical Engineering and Computer Science Massachusetts Institute of Technology, 1994

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

January 2000

© 2000 Massachusetts Institute of Technology. All rights reserved.

| Signature of Author: _ |                                                                               |

|------------------------|-------------------------------------------------------------------------------|

| O                      | Department of Electrical Engineering and Computer Science<br>January 21, 2000 |

|                        | Juliani, 21, 2000                                                             |

| Certified by:          |                                                                               |

|                        | Saman Amarasinghe                                                             |

|                        | Assistant Professor of Computer Science and Engineering                       |

|                        | Thesis Supervisor                                                             |

| Certified by:          |                                                                               |

| v                      | Anant Agarwal                                                                 |

|                        | Professor of Computer Science and Engineering                                 |

|                        | Thesis Supervisor                                                             |

| Accepted by:           |                                                                               |

| 1 0                    | Arthur C. Smith                                                               |

|                        | Chairman, Departmental Graduate Committee                                     |

## Maps: A Compiler-Managed Memory System for Software-Exposed Architectures

by Rajeev Barua

Submitted to the Department of Electrical Engineering and Computer Science on January 21, 2000 in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in Electrical Engineering and Computer Science

#### ABSTRACT

Microprocessors must exploit both instruction-level parallelism (ILP) and memory parallelism for high performance. Sophisticated techniques for ILP have boosted the ability of modern-day microprocessors to exploit ILP when available. Unfortunately, improvements in memory parallelism in microprocessors have lagged behind. This thesis explains why memory parallelism is hard to exploit in microprocessors and advocate bank-exposed architectures as an effective way to exploit more memory parallelism. Bank-exposed architectures are a kind of software-exposed architecture: one in which the low-level details of the hardware are visible to the software. In a bank-exposed architecture, the memory banks are visible to the software, enabling the compiler to exploit a high degree of memory parallelism in addition to ILP. Bank-exposed architectures can be employed by general-purpose processors, and by embedded chips, such as those used for digital-signal processing.

This thesis presents Maps, an enabling compiler technology for bank-exposed architectures. Maps solves the problem of bank-disambiguation, i.e., how to distribute data in sequential programs among several banks to best exploit memory parallelism, while retaining the ability to disambiguate each data reference to a particular bank. Two methods for bank disambiguation are presented: equivalence-class unification and modulo unrolling. Taking a sequential program as input, a bank-disambiguation method produces two outputs: first, a distribution of each program object among the memory banks; and second, a bank number for every reference that can be proven to access a single, known bank for that data distribution. Finally, the thesis shows why non-disambiguated accesses are sometimes desirable. Dependences between disambiguated and non-disambiguated accesses are enforced through explicit synchronization and software serial ordering.

The MIT Raw machine is an example of a software-exposed architecture. Raw exposes its ILP, memory and communication mechanisms. The Maps system has been implemented in the Raw compiler. Results on Raw using sequential codes demonstrate that using bank disambiguation in addition to ILP improves performance by a factor of 3 to 5 over using ILP alone.

Thesis Advisors: S. Amarasinghe, Assistant Professor, Computer Science & Engineering A. Agarwal, Professor, Computer Science & Engineering

# Dedication

To my wife, Alpana.

Thank you for your love, support and patience!

# Acknowledgments

There are several people I would like to thank, the foremost among them are my two advisors, Saman Amarasinghe and Anant Agarwal; and my fellow student, Walter Lee. Saman became my advisor three years ago, but his impact on my thesis has been great. My research benefited tremendously from his enthusiasm, and his willingness to put in many hours on discussions, brainstorming and giving comments. His deep knowledge of compilers helped find innovative solutions to many of the problems we tackled in the Raw compiler. He discovered many of the ideas in this thesis during our many brainstorming sessions. His passion for perfection pushed me to strive for high standards in talks and papers. His help, advice and support have been invaluable in many matters, from writing papers to applying for a job.

Anant Agarwal has been my advisor throughout my years in graduate school. One of the smartest people I know, Anant has the uncanny ability to spot what is important amongst a myriad of possibilities, and state it in one or two sentences. There have been innumerable instances when I have walked into his office, depressed about some experiment not going well; then after hearing me out, he finds a way out, or suggests a new direction – and suddenly, the problem seems more tractable. His feel for what makes for a worthwhile direction of research is unparalleled. His boundless energy, positive attitude and fantastic people skills have made it a pleasure to work with him.

I would like to thank Walter Lee, my collaborator in designing and implementing the Raw compiler. I have very much enjoyed working with Walter. We worked closely on all aspects of the Raw compiler; his ideas have left their mark on virtually every aspect of this thesis. Though Walter was primarily responsible for the back-end spacetime scheduler, and I for the front-end memory system, we collaborated extensively on both parts. In this thesis, Walter first suggested mapping each alias equivalence class to a single node yielding equivalence class unification. Walter was invaluable in many brainstorming sessions that ultimately yielded several other ideas in Maps. He was also a co-author on all the papers that led to this thesis. Finally, Walter wrote a great deal of the common infrastructure that went into the Raw compiler.

Martin Rinard and Radu Rugina were key contributors to Maps. Martin first explained to me the power and capabilities of pointer analysis. My early discussions with Martin were invaluable in realizing how pointer analysis might be leveraged in the Raw compiler. Since then, Radu has been extremely helpful in providing his powerful pointer analysis package, as well as customizing it to interface to Raw. He has always made himself available for implementing new functionality in Raw and for bug fixes. I am grateful for his time and efforts. Martin, besides helping in technical matters, has been a friend and an informal advisor; his down-to-earth advice have been a great resource in navigating my job-search and planning my future career.

The concept of software-exposed architectures, and the Raw Machine in particular, was the result of the efforts of several people listed as the authors of [1]. Among these, I

would like to thank Elliot Waingold and Michael Taylor for the development of the Raw simulator. This simulator has been used to obtain all the timing results in this thesis. Jonathan Babb helped revamp the Raw compiler directory structure and provided several makefiles to make it easy to run benchmarks. He also provided the Raw benchmark suite [2] which we used to evaluate the Raw compiler. Devabhaktuni Srikrishna wrote the unrolling and renaming passes for the Raw compiler. Matthew Frank was helpful in many related discussions, and he provided several benchmarks. He also gave valuable feedback on my talks and papers. Benjamin Greenwald, who knows more about Unix systems than anyone else I know, bailed us out of infrastructure-related trouble on many occasions. Andras Moritz provided detailed and useful feedback on many of my talks.

My thesis reader, Charles Leiserson, helped me become a better writer. He taught me things about presentation, organization and formatting that I never knew before, and might have never known but for him. His feedback on the thesis helped improve the draft almost beyond recognition. I will never forget his advice; I am sure it will help me in whatever I write in the future.

Krste Asanovic and Arvind have been very helpful in providing feedback and outside perspective on this work. Both discussed my work with me for hours, and helped improve its presentation. Krste helped me understand vector machine compilers better, and their relationship to compilation in Maps.

I thank my parents and sisters for their constant love, support and encouragement. My parents instilled in me the work ethic and integrity that have enabled me to work hard on a doctorate program. I can never repay them for all that they have done for me; I can only give my heartfelt thanks. To my friends in Boston: thank you for your companionship and support.

Finally, I thank my wife, Alpana, for her friendship, love and understanding; she makes life worth looking forward to. She has patiently gone through most of my long, hard years in graduate school; always cheerfully and with love; cheering me when I did well, and making me feel better when things were down. She, more than anyone else, gave me the strength to complete a doctoral program. She has been very understanding in the many instances I have been too busy and unavailable while working on my thesis; I promise to do better in the future!

# Contents

| 1 | Intr | oduction 1                                       | 13 |

|---|------|--------------------------------------------------|----|

|   | 1.1  | Unified memory: a hardware vs. compiler approach | 15 |

|   | 1.2  | Bank-exposed architectures                       | 20 |

|   | 1.3  | Bank disambiguation                              | 24 |

|   | 1.4  | Non-disambiguated accesses                       | 3( |

|   | 1.5  | Compiler flow                                    | 34 |

|   | 1.6  |                                                  | 36 |

| 2 | Soft | ware-exposed architectures                       | 36 |

|   | 2.1  | Exposing ILP                                     | 40 |

|   | 2.2  | Exposing the memory system                       | 42 |

|   | 2.3  | Exposing communication                           | 47 |

|   | 2.4  | Raw architecture                                 | 48 |

|   | 2.5  | Summary                                          | 52 |

| 3 | Equ  | ivalence-class unification                       | 53 |

|   | 3.1  | Pointer analysis                                 | 53 |

|   | 3.2  | Equivalence-class unification method             | 54 |

|   | 3.3  | Quality of the disambiguation                    | 57 |

|   | 3.4  | Summary                                          | 58 |

| 4 | Mo   | dulo unrolling                                   | 56 |

|   | 4.1  | Motivation and example                           | 59 |

|   | 4.2  | Modulo unrolling method                          | 32 |

|   | 4.3  | Deriving the unroll factors                      | 34 |

|   | 4.4  | Code growth: bounds and the padding optimization | 36 |

|   | 4.5  | An additional transformation                     | 72 |

|   | 4.6  | Affine code generation                           | 74 |

|   | 4.7  | Other optimizations for array accesses           | 75 |

|   | 4.8  | Summary                                          | 76 |

| 5 | Nor  | n-disambiguated or dynamic accesses              | 7  |

|   | 5.1  | Uses for dynamic references                      | 78 |

| 8 | CONTENTS |

|---|----------|

|    | 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8 | Enforcing dependences                        | 79<br>79<br>81<br>83<br>87<br>90 |

|----|-----------------------------------------------|----------------------------------------------|----------------------------------|

| 6  | Map                                           | os implementation                            | 93                               |

|    | 6.1                                           | Platform used                                | 93                               |

|    | 6.2                                           | Detailed compiler flow and description       | 94                               |

| 7  | Mer                                           | nory allocation and address management       | 107                              |

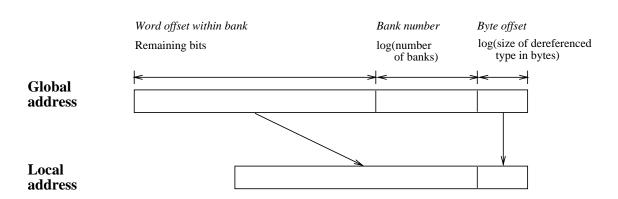

|    | 7.1                                           | Address representation and handling          | 107                              |

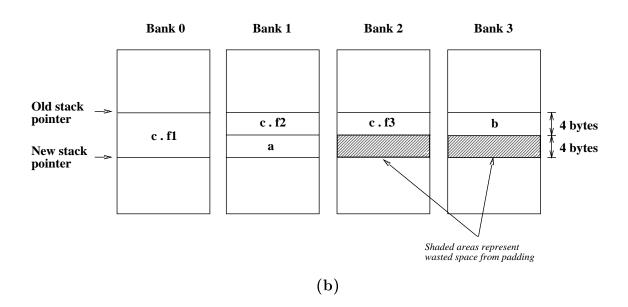

|    | 7.2                                           | Aggregate objects and distributed stacks     | 110                              |

|    | 7.3                                           | Global and local addresses                   | 112                              |

|    | 7.4                                           | Effectiveness of pointer analysis            | 113                              |

| 8  | Lan                                           | guage and environment features               | 115                              |

|    | 8.1                                           | Procedure Calls                              | 115                              |

|    | 8.2                                           | Handling libraries                           | 116                              |

|    |                                               | 8.2.1 Pointer analysis stubs                 | 118                              |

|    |                                               | 8.2.2 Library calls with pointer arguments   | 119                              |

|    | 8.3                                           | Array reshapes in FORTRAN                    | 119                              |

| 9  | Res                                           | ults                                         | 123                              |

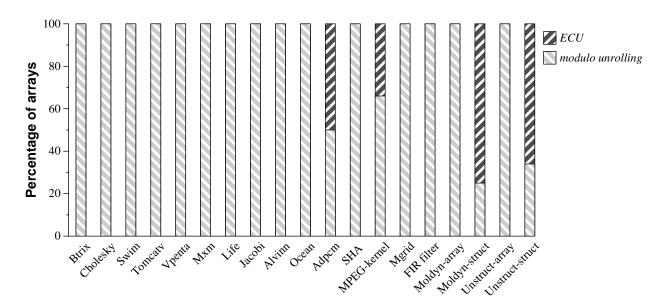

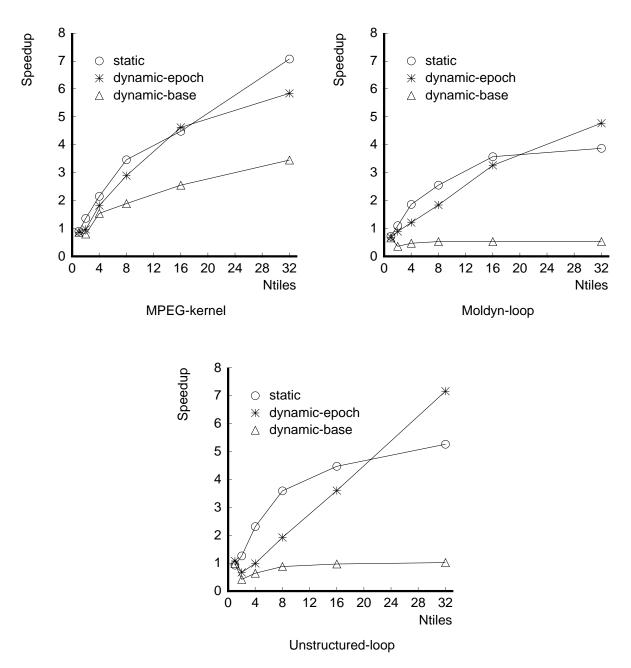

|    | 9.1                                           | Bank disambiguation results                  | 126                              |

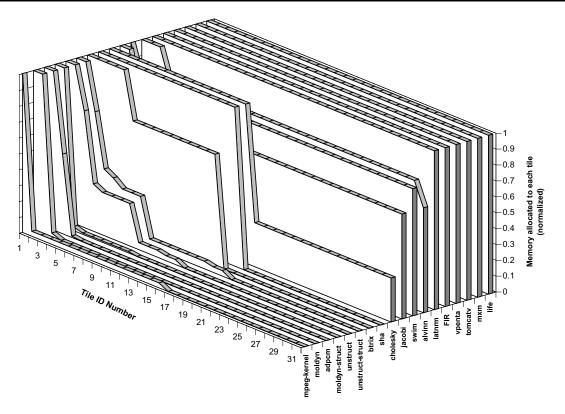

|    | 9.2                                           | Memory distribution and utilization          | 131                              |

|    | 9.3                                           | Static vs. dynamic accesses                  | 134                              |

|    | 9.4                                           | Summary                                      | 138                              |

| 10 | Rela                                          | ated work                                    | 139                              |

|    | 10.1                                          | Bank disambiguation                          | 139                              |

|    |                                               | Other kinds of memory disambiguation         | 141                              |

|    |                                               | Modulo addressing and streaming applications | 143                              |

|    |                                               | Multiprocessor compilers                     | 144                              |

|    |                                               | Compilers for vector machines                | 146                              |

|    |                                               | Compilers for systolic arrays                | 148                              |

| 11 | Con                                           | clusion                                      | 151                              |

# List of Figures

| 1.1  | ILP and memory parallelism for microprocessors, 1980-99                 | 13 |

|------|-------------------------------------------------------------------------|----|

| 1.2  | Hardware-managed memory system                                          | 16 |

| 1.3  | Wire delay across chip, future prediction                               | 17 |

| 1.4  | Illustration of why arbitration logic does not scale                    | 18 |

| 1.5  | Exposed vs. non-exposed memory systems                                  | 21 |

| 1.6  | Raw Architecture                                                        | 23 |

| 1.7  | Example illustrating modulo unrolling                                   | 27 |

| 1.8  |                                                                         | 29 |

| 1.9  | Benefits of bank disambiguation                                         | 30 |

| 1.10 | Example illustrating software serial ordering                           | 32 |

| 1.11 | Example showing independent epochs                                      | 34 |

| 1.12 | Structure of the Raw compiler                                           | 35 |

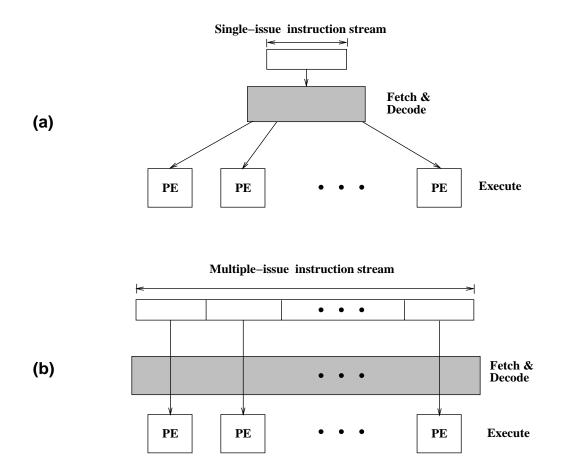

| 2.1  | Instruction interface without and with exposed ILP                      | 41 |

| 2.2  | Memory system without and with bank-exposure                            | 43 |

| 2.3  | 1                                                                       | 45 |

| 2.4  |                                                                         | 46 |

| 2.5  | Raw Architecture                                                        | 48 |

| 2.6  | Anatomy of a dynamic load                                               | 51 |

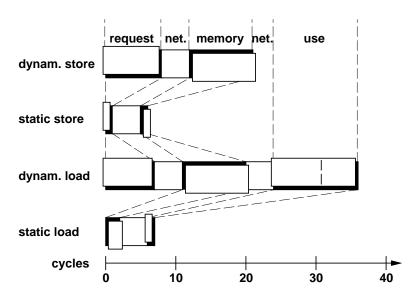

| 2.7  | Memory operation cost breakdown                                         | 52 |

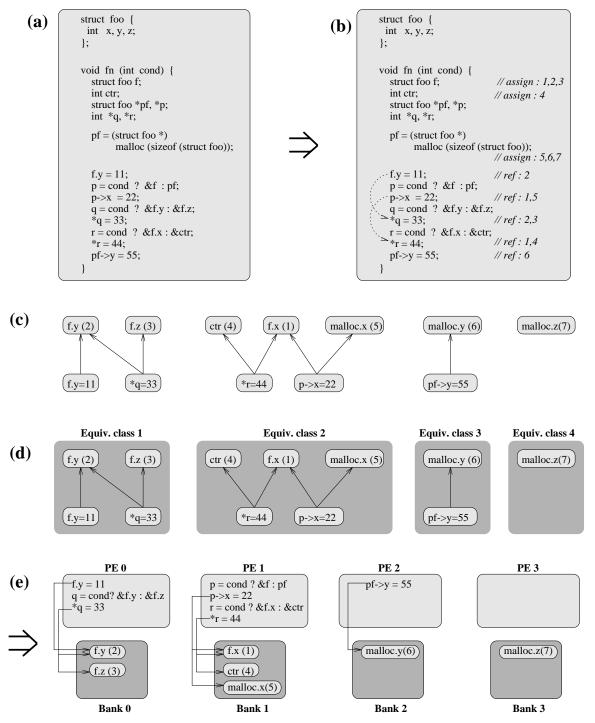

| 3.1  | Example showing equivalence-class unification                           | 55 |

| 4.1  |                                                                         | 61 |

| 4.2  |                                                                         | 73 |

| 4.3  | Sample loop with unknown lower bound and non-unit step size             | 73 |

| 4.4  | Code transformed for disambiguation (4 bank system) for example in fig- |    |

|      | ure 4.3                                                                 | 74 |

| 4.5  | Bank-disambiguated code for example in figure 1.7                       | 75 |

| 5.1  | Illustration of software serial ordering                                | 32 |

| 5.2  | 1 0                                                                     | 34 |

| 5.3  | Transition between scheduling units without and with a barrier 8        | 86 |

| 5.4  |                                                                         | 88 |

| 5.5  | Example code benefiting from updates                                    | 39 |

10 LIST OF FIGURES

| 6.1 | Detailed Rawcc compiler flow                                      | 95  |

|-----|-------------------------------------------------------------------|-----|

| 6.2 | Example showing forward-propagation to array indices              | 96  |

| 6.3 | Example showing unrolling in Maps                                 | 98  |

| 6.4 | Example showing several tasks on code with affine accesses        | 99  |

| 6.5 | Example showing several tasks on code with dynamic accesses       | 101 |

| 7.1 | Address representation in Rawcc                                   | 108 |

| 7.2 | Sample layout of aggregate objects and stacks                     | 111 |

| 8.1 | Example of a parallel procedure                                   | 117 |

| 8.2 | Example of a pointer analysis stub                                | 119 |

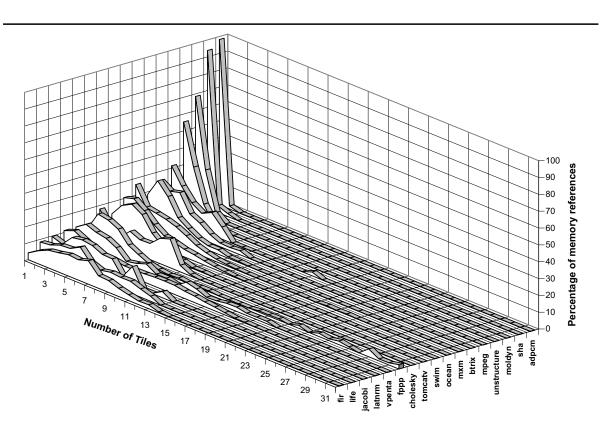

| 9.1 | Benefits of ECU and modulo unrolling                              | 127 |

| 9.2 | Percentage of arrays disambiguated using ECU vs. modulo unrolling | 130 |

| 9.3 | Distribution of primary data on a 32-tile Raw machine             | 132 |

| 9.4 | Weighted bandwidth utilization of the memory system               | 133 |

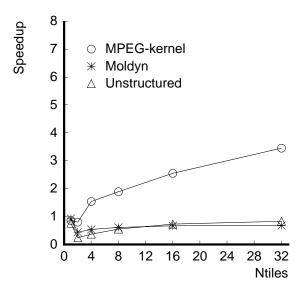

| 9.5 | Benchmark speedup with all arrays distributed                     | 135 |

| 9.6 | Speedups of benchmarks with selective use of dynamic accesses     | 136 |

# List of Tables

| 2.1 | Cost of memory operations in processor cycles                             | 51  |

|-----|---------------------------------------------------------------------------|-----|

| 9.1 | Experimentally measured cost of memory operations in processor cycles for |     |

|     | simulated Raw design                                                      | 124 |

| 9.2 | Benchmark characteristics                                                 | 125 |

| 9.3 | Benchmark speedup with memory disambiguation                              | 129 |

| 9.4 | Performance improvement using software serial ordering                    | 137 |

12 LIST OF TABLES

# Chapter 1

# Introduction

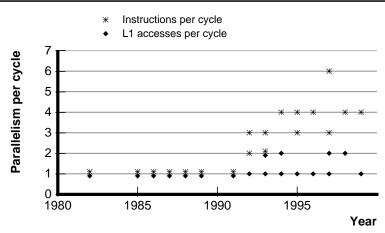

Microprocessors over the last two decades have made great strides in their ability to exploit instruction-level parallelism (ILP). During the same period, however, parallelism in accessing primary memory has improved at a much slower rate. Consequently, memory has become a major bottleneck in processor design and threatens to become an even bigger problem. Dick Sites, the chief designer of Alpha microprocessors at the time, warns in his 1996 column titled, "It's the memory, stupid!" [3] that future performance gains are in jeopardy unless memory performance improves. Figure 1.1 shows the trend over the last two decades [4]. The figure shows that ILP rates have improved from 1 instruction per cycle in the early 1980s, to 4 to 6 instructions per cycle today. Yet, the number of independent words that can be accessed per cycle from primary L1 cache has remained virtually unchanged, from 1 per cycle in the early 1980s, to 1, or at most 2 per cycle today. For example, the Alpha 21364 [5, 6], expected to ship in mid-2000, supports up to 6 instructions and 2 cache accesses per cycle.

Figure 1.1: ILP and memory parallelism for various microprocessors over the last two decades. Points in the graph represent commercial microprocessors from that year. Each microprocessor contributes two points, one for its maximum number of instructions per cycle (ILP), and one for its maximum number of primary cache (L1) accesses per cycle (memory parallelism). Memory parallelism has remained at 1 or 2 accesses per cycle, while ILP has improved much more.

Even though microprocessors have become increasingly complex over the last decade, the abstraction microprocessors provide to the software has remained the same. Most microprocessors provide the abstraction of a single processing element (PE) accessing a single memory bank. This simple view in software, however, comes at a price: the overhead of a providing a hardware-based unified view of memory has resulted in memory parallelism remaining stagnant over the last two decades. Section 1.1 shows why hardware-based unified memory systems limit memory parallelism and prevent scaling to a larger number of banks.

Although it is desirable, for ease of programming, to provide a unified view of memory to the programmer, the hardware need not provide the unified view; instead this thesis explores how the *compiler* can provide a unified view of memory to the programmer on top of distributed memory hardware. The performance of the architecture can be vastly improved if it does not need to provide a unified view of memory. The hardware can, instead, expose its multiple memory banks to the low-level software by eliminating the unified memory hardware. Such architectures with exposed memory banks are called bank-exposed architectures. In such architectures, the abstraction presented to low-level software is not that of a monolithic memory; instead load/store instructions target particular memory banks encoded in the software. The user continues to program in a convenient sequential model – sequential programs are desirable since they are easier to write, debug and port to different architectures.

This thesis presents compiler technology that provides a unified view of memory in the compiler on top of the distributed memory hardware of bank-exposed machines. Banks are exposed to the low-level software, but not to the programmer. The Maps compiler system presented in this thesis provides a convenient sequential programming model, yet it exploits a high degree of memory parallelism on a bank-exposed architecture.

We show that bank disambiguation is the main compiler technique for obtaining good performance on bank-exposed architectures. A memory reference instruction in a program is said to be bank-disambiguated when the compiler guarantees that every dynamic instance of that instruction references the same compile-time-known bank. We show that bank disambiguation allows accesses on bank-exposed architectures to avoid the complex hardware that provides a unified view of memory, and reduces the wire delay incurred by memory references. This thesis presents two methods for bank disambiguation: modulo unrolling and equivalence-class unification. Bank disambiguation may not disambiguate all accesses: this thesis shows how non-disambiguated accesses can be handled. The major challenge for non-disambiguated accesses is that, for good performance, their long access latencies should be overlapped with computation and other communication as much as possible, while respecting all dependences. This thesis presents a general scheme for overlapping access latencies of non-disambiguated accesses called software serial ordering. Two optimizations on software serial ordering, namely independent epochs and updates, are also presented.

An outline of this chapter follows. Section 1.1 compares the hardware and compilerdirected approaches to providing a unified view of memory to the programmer. It explains why it is difficult to scale hardware-based unified memory, and highlights opportunities available in the compiler to improve scalability and performance. Section 1.2 advocates the bank-exposed class of architectures; such architectures rely on a compiler-directed approach to improve memory performance. Section 1.3 shows why bank disambiguation is the key compiler technology needed for bank-exposed architectures, and outlines our two techniques for bank disambiguation. The section previews results showing performance improvements from using our techniques for bank disambiguation on a particular bank-exposed design, the MIT Raw machine [1]. Results show that using bank disambiguation in addition to ILP improves performance by a factor of 3 to 5 over using ILP alone. Section 1.4 illustrates the challenge in efficiently handling accesses that are not disambiguated by bank disambiguation, and outlines our techniques for handling non-disambiguated accesses. Section 1.5 shows one possible compiler flow for a bank-exposed architecture. Section 1.6 provides an brief overview of the thesis by outlining the scope of our methods, the contributions of the thesis, and the organization of the thesis.

# 1.1 Unified memory: a hardware vs. compiler approach

This section begins by describing how conventional microprocessors provide a unified view of memory using hardware. This section then explains why delay through the arbitration logic and wire delay make it difficult to scale hardware-based unified memory to a high degree of memory parallelism. Finally, it outlines opportunities available in using the compiler instead of complex hardware to provide a unified view of memory; thus setting the stage for the compiler-directed solution outlined in the rest of this chapter.

# Difficulties scaling hardware-based unified memory

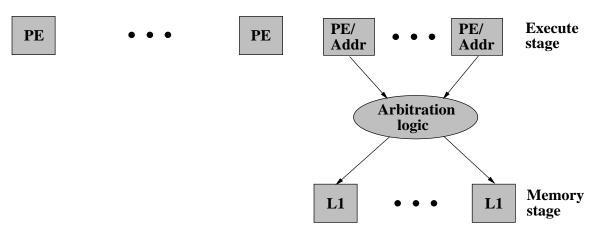

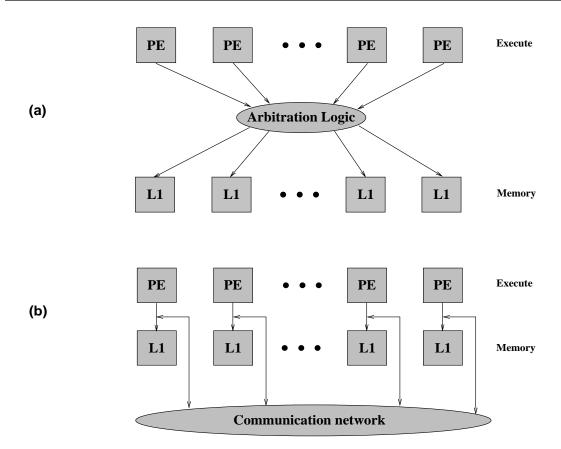

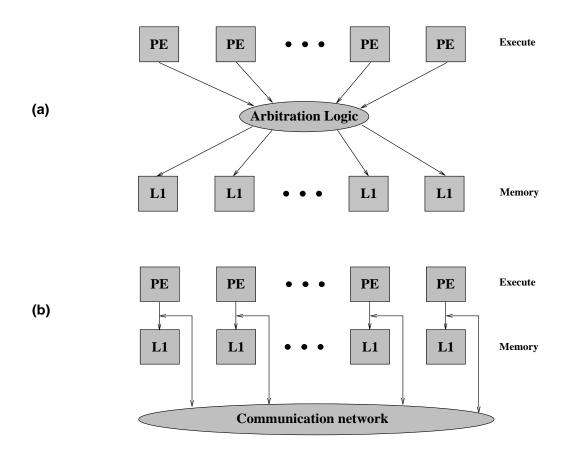

This sub-section describes the hardware-based unified memory systems of conventional microprocessors, and discusses how the design prevents scaling to a higher level of memory parallelism. Figure 1.2 shows the typical organization of a hardware-based unified memory system in a conventional microprocessor. Processing elements (PEs) refer to elementary ALUs present on the chip; the memory banks (L1) refer to the multiple banks in the primary level-1 cache. Figure 1.2 does not show the complete layout of the chip, only the interface between the processing elements and memory. A unified view of memory is provided by a layer of hardware we call arbitration logic. The memory semantics provided by the arbitration logic is that of a single monolithic memory bank accessed sequentially, although the arbitration logic actually connects to multiple memory banks in an effort to exploit memory parallelism. Typically, the arbitration logic consists of routing hardware for requests to and replies from memory banks, as well as a write buffer with associated hardware to enforce memory dependences between outstanding memory requests. To achieve sequential memory semantics, the arbitration logic stores all outstanding requests, routes each request to the bank on which the requested data resides, ensures sequentiality between accesses to the same bank, and routes back results

to the requesting processing elements. The results to any one processing element are returned in the order they were requested. Correct sequential semantics are maintained while aiming to overlap requests to different banks as much as possible.

Figure 1.2: Hardware-managed memory system in conventional microprocessors. Processing elements (PE) are of two kinds. Some PEs can compute the effective address of load/store instructions (PE/Addr), and are connected to primary cache banks (L1) through the arbitration logic. Others (PE) are specialized to non-memory instructions alone, and do not interface with the memory system. The number of PE/Addr and L1 are kept small to restrict the complexity of, and delay through, the arbitration logic.

While unified memory hardware simplifies the compiler's task, such hardware has two costs associated with scaling the memory system. First, unified memory hardware does not scale well with the degree of memory parallelism desired. Increasing memory parallelism requires more PEs to be connected to the arbitration logic to issue requests and more memory banks connected to satisfy the requests. Unfortunately, greater connectivity with the arbitration logic increases its delay. Since the arbitration logic delay is a part of the hit time of the primary cache, the delay must be small. To minimize the arbitration logic delay, all commercial microprocessors today limit their memory parallelism to 1 or at most 2 parallel L1-cache accesses per cycle.

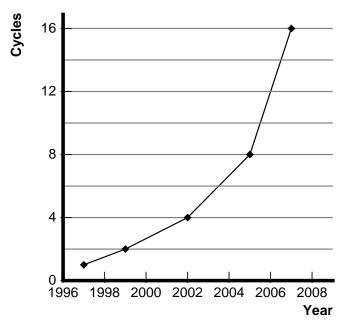

A second cost of a unified view of memory in hardware is that it implies the use of long wires to access memory, resulting in poor on-chip locality. Long wires result from the use of a single gateway, i.e., the arbitration logic, to access the different banks. Processing elements and cache banks, connected through the arbitration logic, are in general distributed over far-flung areas of the chip, implying long wires. Thus, cache hits, which go through the arbitration logic, may on average traverse half the chip diameter each way. In a billion-transistor, several-gigahertz processor of the future, such a cache hit will become a multi-cycle operation from the wire delay alone. Figure 1.3 illustrates the trend of increasing wire delays by plotting expected cross-chip wire-delay over the

next decade<sup>1</sup>. The figure shows that it will take four cycles to cross a chip by 2002 and sixteen cycles by 2007, up from just one cycle in 1997. With increasing wire delay, the primary cache hit time will grow rapidly if the memory system is organized as a monolithic unit accessed from far corners of the chip. Further, the access time within a monolithic cache will also grow as cache sizes grow with VLSI generations.

Figure 1.3: Predicted wire delay in cycles for a signal to cross the chip diameter over the coming decade.

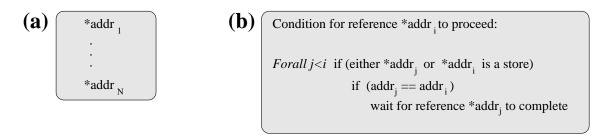

Figure 1.4 further illustrates why arbitration logic does not scale with the degree of memory parallelism desired. Let N be the number of PE/Addr in the conventional microprocessor design in figure 1.2; consequently N is also the number of memory instructions that can issue in parallel in one cycle. Figure 1.4(a) shows a sample code with N memory reference instructions, each of which may be either a load or a store. Assume that these N references are issued in parallel to the arbitration logic on a machine with N PE/Addr units. Figure 1.4(b) shows the condition that needs to be hardware-executed in the arbitration logic at run-time before reference  $addr_i$  ( $i \in [1, N]$ ) can proceed to its memory bank. The condition shows that for a reference to proceed, it must compare its address with all references issued in the same cycle that are earlier in program order. No check is

<sup>&</sup>lt;sup>1</sup>Figure 1.3 is derived by combining Matzke's prediction for cross-chip delay versus processor feature size [7] with the Semiconductor Roadmap's prediction for feature size versus year [8]. Matzke assumes that as feature sizes reduce, wires will become thinner, increasing their resistance and hence delay. He also assumes that clock cycle times will reduce with feature size as predicted, thus further increasing the number of cycles for any fixed wire delay.

necessary when both the reference and the previous reference in consideration are loads. A reference proceeds only when all its preceding references in program order that conflict with it have completed<sup>2</sup>. Unfortunately, the implementation of this check in hardware is not scalable with N. In particular, the minimum delay through the logic is  $O(\log N)$  by the time all the N references have issued. To see this, consider that for the last reference to proceed, it must perform a binary inclusive or of the results of address checks with all N-1 previous references; an  $O(\log(N-1)) = O(\log N)$  operation. Further, the silicon area of arbitration logic increases with N, reducing scalability; it is possible to achieve  $O(\log N)$  delay with O(N) silicon area using a prefix tree scheme [9], or with  $O(N^2)$  area using all-to-all checks that improve the delay by a constant factor. In either case, the minimum area is O(N) and the minimum delay is  $O(\log N)$ ; thus the area and delay both increase with N. The wire delay and power consumption also increase with N in any such scheme.

Figure 1.4: Illustration of why arbitration logic does not scale. (a) Code fragment with N memory reference instructions, assumed issued in parallel to the arbitration logic in a conventional microprocessor with N PE/Addr (see figure 1.2). (b) Condition for  $addr_i$  ( $i \in [1, N]$ ) to proceed to its memory bank. Executing the condition in hardware requires delay and area that increase with N.

The non-scalable delay and latency of unified memory systems threatens continuing improvements in microprocessor performance. Already, the effects are becoming visible. The primary cache hit time for the Alpha 21264 [6] has increased to 2 cycles, up from 1 cycle for the 21164, because of increased wire delay in bank access. At the same time, the number of concurrent memory accesses allowed has stagnated at 1 or 2 per cycle. Bill Dally of Stanford University recognized the memory-limited nature of today's designs in his 1996 column [10] by saying:

"Computers in 2006 will be memory, not processor, dominated. Cost will be driven by memory capacity, and performance by memory latency and bandwidth."

<sup>&</sup>lt;sup>2</sup>Optimizations are possible in certain cases, for example, when a load follows a store in program order, and they refer to the same location. It is possible to implement a hardware scheme in which the load need not wait for the store to complete; instead the load returns the value being stored by the store, without going to memory. Nevertheless, even with such optimizations, the number of checks in figure 1.4(b) does not decrease.

Dick Sites, the chief designer of Alpha chips at the time, takes the same position in his 1996 column [3] by concluding:

"Over the coming decade, memory subsystem design will be the *only* important design issue for microprocessors."

## Opportunities in software

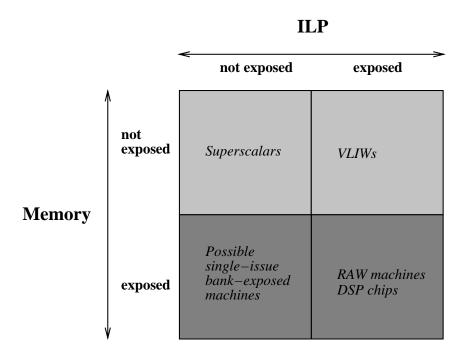

Information discovered by the compiler provides an opportunity to improve microprocessor performance, including memory performance. Compilers have highly detailed information about ILP, memory parallelism and locality that instruction sets of conventional machines fail to take advantage of. For instance, superscalar architectures discover ILP in hardware, while presenting a single-issue instruction-stream interface to software. Compilers often know which instructions can execute in parallel, but there is no way for them to convey this ILP information to the hardware through a superscalar instruction-set architecture (ISA). As a result, superscalar hardware must rediscover ILP information at the cost of considerable area, delay, and power. VLIWs expose their instruction-issue slots to the software, and can exploit somewhat more compiler information. Although VLIWs do not exploit compiler-known memory parallelism information, they do exploit compiler-known ILP information. Interest in VLIWs has resurged recently, fueled by their avoidance of costly ILP-discovering hardware, combined with the increasing sophistication of compilers. Recent VLIW-like processors include the Intel/HP EPIC architecture [11, 12], Transmeta's x86 chip [13], Tensilica's Xtensa embedded CPU [14], and the MAJC chip from Sun Microsystems [15].

Even VLIWs, however, cannot exploit much of the information that compilers can provide, and compilers can potentially discover far more information. In particular, they can optimize for both memory parallelism and on-chip locality. First, compilers can provide information about which memory instructions can execute in parallel. VLIW and superscalar machines cannot exploit memory-parallelism information, as such machines use hardware-based unified-memory systems that do not scale. Second, compilers can provide information about data access patterns. Access-pattern information can be used to derive data layouts and instruction schedules that optimize for on-chip locality. Conventional architectures fail to exploit on-chip locality because they use long wires.

# Exposing resources to software

The inability of conventional architectures to use all available compiler information provides an opportunity to improve performance if new kinds of architecture can fully exploit compiler information. One way to exploit more compiler knowledge is to expose more hardware resources to the software. Resources that can be exposed include processing elements, memory banks and the communication network (wires) on chip. Architectures that expose their resources to software are given the generic name of software-exposed architectures [1]. VLIWs are partially software-exposed since they expose processing elements.

ements through multiple instruction-issue slots. In this thesis we focus on bank-exposed architectures.

# 1.2 Bank-exposed architectures

This section advocates the bank-exposed class of architecture, a class of architecture that exposes its memory banks to the low-level software. The section explains how bank-exposed architectures enable scaling to a high degree of memory parallelism. Next, examples of bank-exposed designs from the past are presented. The MIT Raw machine, a bank-exposed architecture being designed in our research group, is also presented. Finally, a comparison with multiprocessors is made, showing the differences of bank-exposed microprocessors with multiprocessors that also expose their memory banks.

The minimum architectural feature required to exploit the compiler methods in this thesis is that the architecture be a bank-exposed architecture. A bank-exposed architecture is a software-exposed architecture with two defining features: first, several disjoint software-visible address spaces, corresponding to different memory banks; and second, memory references that can be directed at compile-time to particular address spaces. Compile-time resolution of the bank number is the key characteristic of bank-exposed machines. Run-time resolution, in contrast, implies a hardware-based unified memory system.

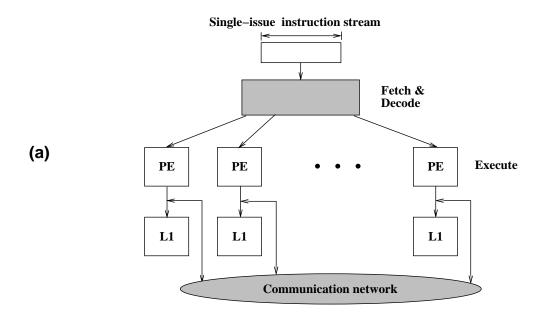

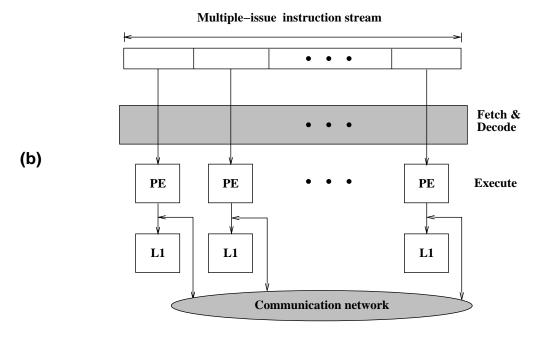

Figure 1.5 compares the memory system of a bank-exposed architecture with a hardware-based unified memory system. Figure 1.5(a) shows a hardware-based unified memory system. Every access goes through the arbitration logic. Figure 1.5(b) shows a bank-exposed architecture. Figures 1.5(a) and (b) do not show the complete architecture, but only the interface between PEs and memory. In figure 1.5(b), there are two ways to access memory. First, memory reference instructions accessing compile-time-known banks travel over an on-chip communication network, avoiding run-time arbitration. Second, memory instructions to compile-time-unknown banks need run-time arbitration, and hence they go through the slower arbitration logic (not shown). Bank-exposed architectures are advantageous only if most memory instructions reference banks known at compile-time. The compile-time task of discovering a bank number for each reference is called bank disambiguation, which is discussed in section 1.3.

A motivating advantage for bank-exposed designs is that they can potentially overcome the two costs of hardware-based unified memory: non-scalable delay through arbitration logic and poor on-chip locality. These advantages are gained, however, only when most memory instructions access compile-time-known banks. The advantages of such accesses to known banks, over accesses in a conventional memory system, are as follows. First, accesses to compile-time-known banks avoid going through the arbitration logic, and so they do not suffer the logic's delay. Consequently, the number of banks can be increased without increasing the cache hit time for local accesses. Second, accesses to compile-time-known banks can exploit on-chip locality, as the compiler can place the memory reference close to the bank where the reference's data resides. In the best case,

Figure 1.5: Exposed vs. non-exposed memory systems. (a) A hardware-based unified memory system (non-exposed). (b) A bank-exposed architecture. Memory instructions that access a compile-time-known bank complete over an on-chip communication network. Only memory instructions accessing compile-time-unknown banks need to go through the arbitration logic (not shown).

the compiler places the load/store instruction on the PE local to the bank on which the reference's data resides. In this manner, the wire-delay incurred is optimized by the compiler. The L1 cache is split into many small and independently accessed banks, instead of one or two large banks as in a conventional memory system. Accesses to known banks need only go to a small, nearby bank with low access delay, instead of a larger, far-away bank with higher access delay.

We revisit figure 1.4 to see how bank-exposed architectures eliminate the cost of arbitration logic. Figure 1.4(a) shows a code fragment with N memory instructions; figure 1.4(b) shows the condition that the arbitration logic needs to evaluate before it can proceed with issuing the ith reference. Bank-exposed architectures, in contrast, avoid the arbitration logic and its delay for memory instructions to compile-time-known banks. The reason why the arbitration logic is avoided is that accesses proven by the compiler to go to different banks cannot be dependent; hence they need not be checked for dependence at run-time. In addition, accesses known to go to the same bank are serialized at the bank anyway, so checks provide little benefit and are not done. Consequently, accesses to compile-time-known banks require no run-time arbitration whatsoever – the  $O(\log N)$  delay through arbitration logic is thus avoided, allowing N to be increased to many banks without increasing the cache hit time.

#### Examples of bank-exposed architectures

Bank-exposed architectures are not a new idea. Bank-exposed general-purpose microprocessors date back to at least 1983 when Josh Fisher proposed the ELI-512 VLIW machine [16]. The ELI-512 is an unusual VLIW that uses a point-to-point network, rather than a bus, to connect its different processing elements, each having its own memory bank. The ELI-512 supports two ways of accessing memory. Accesses to compile-time-known banks use a "front door" to memory, while accesses to compile-time-unknown banks use a slower "back door" to memory. The iWarp machine [17] is another bank-exposed design: it exposes not only memory, but also its processing elements and network. Digital-signal processing (DSP) chips, such as the Motorola DSP56000 family [18], have also used bank-exposed designs. DSP chips usually have 2 to 3 software-exposed banks, called X, Y, and Z memories. DSP chips usually provide no arbitration logic; all accesses must be to compile-time-known banks. Shortcomings in bank-exposed compilers have meant that, even today, most DSP chips are hand programmed.

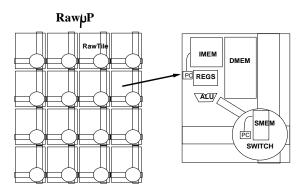

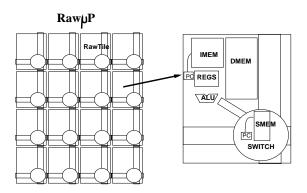

The MIT Raw machine [1], being developed in our research group at MIT, is the latest in the line of bank-exposed general-purpose designs. The methods in this thesis apply, however, to any bank-exposed design. The Raw machine exposes not only its memory, but also its processing elements and networks. The Raw architecture is shown in figure 1.6. A Raw architecture consists of a 2-dimensional mesh of tiles. Each tile is composed of a processing element and a cache memory bank. A switch is provided on each tile to communicate with other tiles. Two communication networks connect the tiles: the *static network* and the *dynamic network*. The static network is a fast register-level network. Accesses to compile-time-known banks complete over the static network,

or are local from a PE to its local bank. The dynamic network is a slower memory-level network that replaces the arbitration logic. Accesses to compile-time-unknown banks complete over the dynamic network. Details of the Raw architecture, along with the reasons for using two networks, are presented in section 2.4.

Figure 1.6: A Raw microprocessor is a mesh of tiles, each with a processing element, some memory and a switch. The processing element contains both registers and an ALU. The processing element interfaces with its local instruction memory, local data memory and local switch. The switch contains its own instruction memory.

For any bank-exposed architecture, as in figure 1.5(b), the term *tile* is naturally defined as a memory bank with all its associated functional units. The Raw machine has only one processing element per bank, and hence a tile is a single processing element with its associated memory bank.

# Comparison with multiprocessors

Distributed memory multiprocessors, such as Flash [19], Alewife [20] and IBM's SP2 [21], have multiple memory banks exposed to the software. To date, however, the relatively long remote-access latencies of multiprocessors have restricted them to exploiting coarse-grain parallelism rather than ILP.

The reason for the slow access times on multiprocessors is their lack of hardware support for static scheduling of memory accesses. Memory accesses can be statically (at compile-time) scheduled if their access patterns are known and the architecture provides a way of statically ordering memory accesses on each bank. Statically ordered references on each bank provide dependence enforcement without expensive overheads. An architecture can provide references that are statically ordered in two ways. Either the architecture guarantees a predictable access time to every bank, or it provides a network that guarantees that messages are delivered in the order specified at compile-time. The Raw architecture takes the second approach by providing the compiler-routed static network. Predictable ordering of messages reduces the overheads of run-time routing. In multiprocessors, the inherent unpredictability in the arrival order and timing

of messages requires expensive reception mechanisms such as polling or interrupts, and expensive run-time congestion-control schemes that arise due to the unpredictable ordering of messages. The consequently faster communication on bank-exposed architectures enables their compilers to focus on ILP, instead of coarse-grained parallelism.

Compilers for multiprocessors aim to discover coarse-grain parallelism from sequential programs. Unfortunately, discovering coarse-grained parallelism in the compiler involves complex whole-program analysis, which has thus far proven successful only for dense matrix applications [22, 23]. An alternative to automatic parallelization for multiprocessors is programming them using an explicitly parallel language. This approach, however, has not found widespread acceptance outside a small group of programmers, mostly in the scientific community. Thus, while the ideas in this thesis apply equally to parallel programs, we focus on sequential programs alone.

# 1.3 Bank disambiguation

This section explains bank disambiguation, and shows why it is the central challenge for extracting good performance from bank-exposed architectures. Bank disambiguation enables memory instructions to go to compile-time-known banks. Bank disambiguation is motivated, and the quality criteria required for bank disambiguation are explained. An important benefit of bank disambiguation, static scheduling of memory instructions, is illustrated. Our two methods for bank-disambiguation, modulo unrolling and equivalence-class unification are outlined. Finally, results demonstrating performance improvements from using our bank disambiguation methods are presented.

#### Motivation and definition

Bank disambiguation is motivated by the existence of two ways to access memory on a bank-exposed architecture. First, memory instructions that access a compile-time-known bank avoid arbitration logic, using a communication network for access instead. Second, memory instructions that access a compile-time-unknown bank must use the slower arbitration logic. Accesses to compile-time-known banks are preferable as they avoid non-scalable run-time arbitration and exploit on-chip locality. Hence, the compiler aims to find a fixed bank number, known at compile-time, for as many memory instructions as possible.

**Definition 1.1** A particular load or store memory-reference instruction in the program is said to be **bank disambiguated** to a particular bank if the instruction accesses the same compile-time predictable bank in every dynamic instance.

Success in bank disambiguation critically depends on the data distributions used. The methods in this thesis carefully choose data distributions so that bank disambiguation is possible for most accesses, resulting in a high degree of memory parallelism. Poorly selected data distributions may imply that most memory instructions in the program go

to different banks in different dynamic instances, thus failing disambiguation, even if the distribution provides memory parallelism.

## Quality criteria

Not all bank disambiguation methods are of equal quality: some schemes are better than others. Specifically, bank disambiguation needs to be achieved while optimizing for two factors:

- Memory parallelism The bank disambiguation scheme should achieve a high degree of memory parallelism. It is easy to bank-disambiguate without memory parallelism: all program data can be allocated to a single bank, thus trivially disambiguating all references to that bank. Better bank disambiguation methods allocate data to several tiles so that different memory instructions can be issued in parallel, yet most memory instructions go to a fixed bank predictable at compile-time.

- Code size Some bank disambiguation schemes require program transformations, such as loop unrolling, that increase the code size of the program. Good disambiguation schemes keep code growth to a minimum. The modulo unrolling example presented later in this section shows that a naive scheme for bank disambiguation involves fully unrolling loops. Full unrolling is expensive, however, if the range of loop-bounds is large, and is not possible for unknown loop bounds. The methods in this thesis keep the code growth bounded by a constant factor, independent of the loop bounds.

# Bank disambiguation aids static scheduling

A major advantage of bank disambiguation is that it enables the static scheduling of memory references. Static scheduling of memory references requires that the hardware provide a way of statically ordering memory accesses on each bank, either using banks having compile-time-guaranteed latencies, or by providing a compiler-routed network with compiler-specified ordering of messages. Even with hardware that allows static ordering of memory references, without bank disambiguation the banks accessed for each reference are not known, making it impossible to guarantee the ordering of accesses on each bank, thereby making static scheduling impossible. Thus, bank disambiguation is a necessary for static scheduling.

Further, bank disambiguation is also sufficient for static scheduling if the assignment of memory instructions to PEs is under compiler control. A compile-time-known PE for a memory instruction implies that a compiler-routed message can be used from the memory instruction to its bank. Alternatively, if the hardware provides a guaranteed latency to each bank, knowing the PE for the memory instruction provides a guaranteed

latency for the entire memory access from PE to the bank. Either way, a compiler-time-known PE assignment for each memory instruction, along with bank disambiguation, is sufficient for static scheduling.

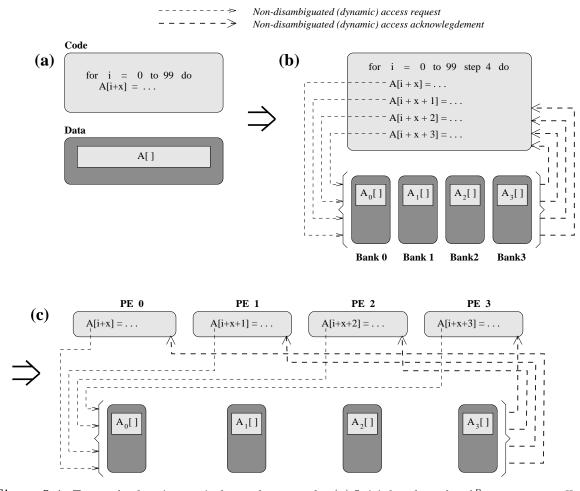

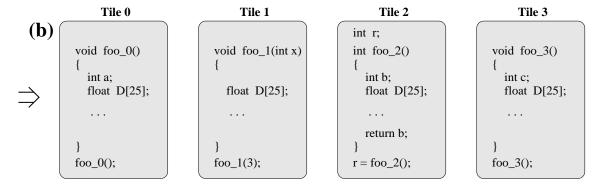

#### Modulo unrolling

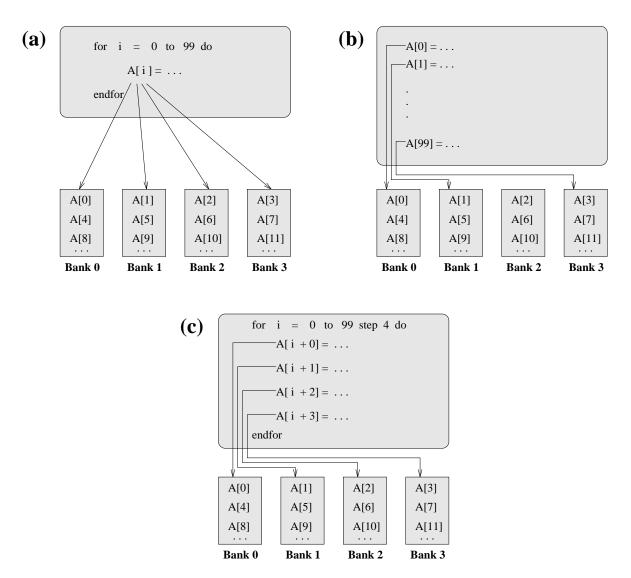

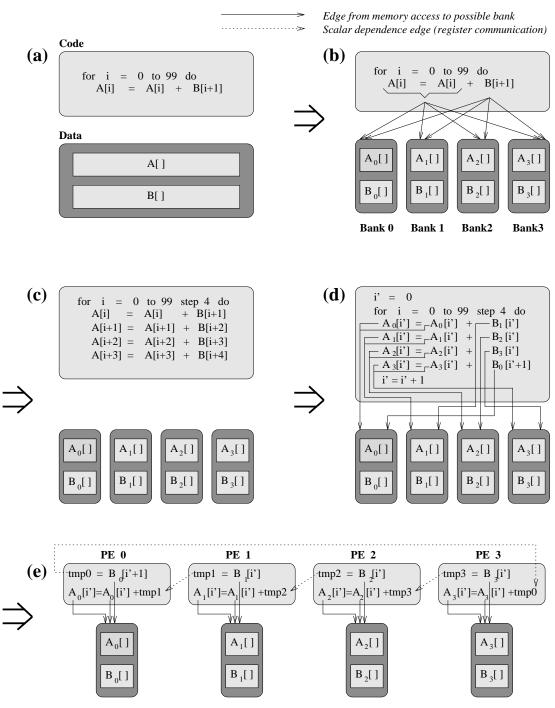

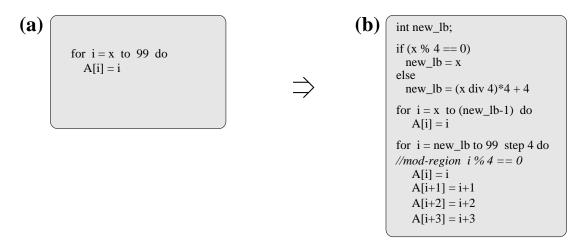

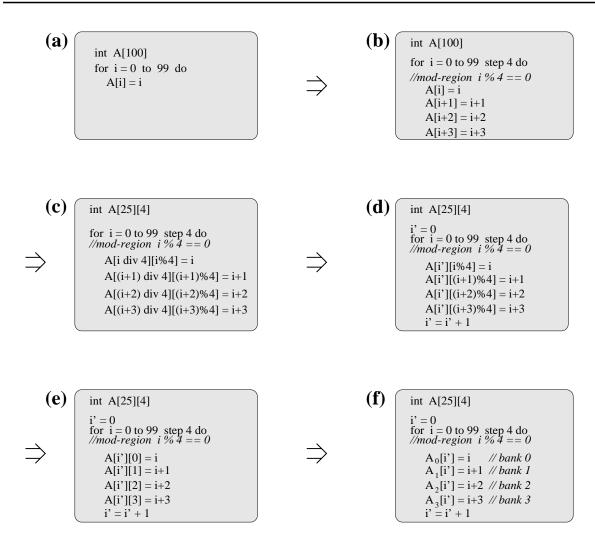

To understand bank disambiguation, consider figure 1.7. The figure shows an example of how bank disambiguation is done using modulo unrolling, one of the two bank disambiguation schemes presented in this thesis. Figure 1.7(a) shows the code fragment forming the compiler input, consisting of a simple **for** loop containing a single array reference A[i]. The array A[] is assumed to range from 0 to 99. The array A[] is shown distributed among 4 memory banks using low-order interleaving<sup>3</sup>.

Now, suppose we want to bank-disambiguate the A[i] memory instruction on a bank-exposed architecture with 4 banks. For disambiguation, an array reference instruction must access the same bank in every dynamic instance. If the array A[] is distributed in any way at all, then by the definition of distribution, the different dynamic instances of A[i] go to different banks in different iterations, thus failing disambiguation. For example, assume that array A[] is distributed using low-order interleaving, as depicted in figure 1.7(a). The A[i] reference accesses all 4 banks for different values of i, as depicted by the arrows from the reference to all 4 banks. The A[i] reference has the bank-access pattern of 0, 1, 2, 3, 0, 1, 2, 3, ... in successive loop iterations. Since the reference instruction goes to more than one bank, it fails disambiguation.

A naive way to attain bank disambiguation and memory parallelism is to fully unroll the loop. Figure 1.7(b) shows the sample loop in figure 1.7(a) fully unrolled, i.e., unrolled by a factor of 100. Full unrolling makes all the array-reference indices constant in the unrolled code, and hence all the array references in the unrolled loop are trivially disambiguated to the bank holding the known array element. For example, the reference  $A[99] = \ldots$  is disambiguated to bank 99 mod 4 = 3. Full unrolling provides disambiguation with memory parallelism, but full unrolling is prohibitively expensive in terms of code-size increase. Full unrolling is not even possible for compile-time-unknown loop bounds. Consequently, the Maps system never uses full unrolling.

Fortunately, in this case, there is a way to attain both memory parallelism and bank disambiguation without a huge increase in code size. The solution involves transforming the program using loop unrolling. Figure 1.7(c) shows the result of unrolling the code in figure 1.7(a) by a factor of 4. Now, each access always refers to elements on the same memory bank. Specifically, A[i] always refers to tile 0, A[i+1] to tile 1, A[i+2] to tile 2, and A[i+3] to tile 3. Therefore, all 4 new references are bank disambiguated. Furthermore, the 4 references in figure 1.7(c) can proceed in parallel, thus providing memory parallelism.

<sup>&</sup>lt;sup>3</sup>Low-order interleaving is a data layout in which array elements are interleaved among the N different banks in a round-robin manner, beginning at bank 0. That is, for array A[], element A[i] is allocated on bank  $i \mod N$ . The array A[] is thus broken up into N sub-arrays,  $A_0[]$  to  $A_{N-1}[]$ , such that A[i] maps to  $A_{i \mod N}[i \text{ div } N]$ .

Figure 1.7: Example of modulo unrolling. (a) Original code. Array A is low-order interleaved on a 4-bank bank-exposed machine. The A[i] memory reference instruction goes to different banks for different values of i. (b) Code after full unrolling. Disambiguation is attained, i.e., each reference goes to a single bank, but code size is huge. (c) Code after unrolling by factor 4. Disambiguation is attained with limited code size increase.

The program transformation in figure 1.7 is not a one-instance special case. Rather, it is a specific application of a fully automated general technique for bank disambiguation called *modulo unrolling*. Presented in this thesis, modulo unrolling is a technique that provably disambiguates any array reference in a nested loop if the indices of the array reference are affine functions<sup>4</sup> of the index variables of the enclosing loops. The modulo unrolling transformation provides both bank disambiguation and memory parallelism. Chapter 4 presents details on how modulo unrolling is automated. Affine array accesses are common in scientific codes and some multimedia codes, and are present even in some irregular programs. Modulo unrolling provides a significant performance improvement for such programs.

#### Equivalence-class unification

Equivalence-class unification (ECU) is the second of the two techniques for bank disambiguation presented in this thesis. ECU is applicable in all cases that modulo unrolling is not applicable; *i.e.*, ECU aims to disambiguate all accesses other than affine array accesses. ECU handles all kinds of accesses in an integrated framework, including non-affine array accesses, pointer dereferences, structure references, and heap references, in programs with arbitrary memory-aliasing.

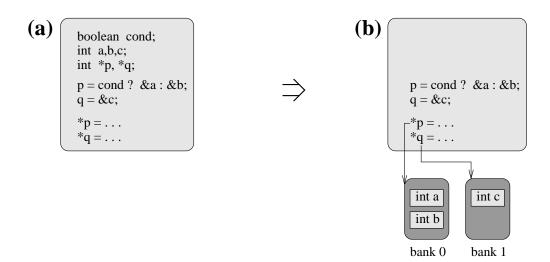

Figure 1.8 demonstrates ECU through an example. Figure 1.8(a) shows the original code input to the compiler. There are three integers -a, b and c – and two pointer references -\*p and \*q. The value of boolean variable cond is assumed to be unknown at compile-time. Figure 1.8(b) shows the code and data after ECU on a 2-banked bank-exposed machine. In order to bank-disambiguate the \*p and \*q references, ECU places a and b on bank 0, and c on bank 1. With this data allocation, both references go to only one bank, irrespective of the run-time value of cond, thus bank disambiguating both references.

Chapter 3 shows how the ECU method can be generalized to handle any input program, and it describes the general method. The ECU method aims for memory parallelism across data objects, rather than within. Arrays are allocated to a single tile; structures, however, are distributed as ECU considers structure fields as individual data objects. A drawback of ECU is that it does not exploit memory parallelism within arrays and array-like heap-allocated memory blocks accessed by non-affine accesses. Modulo unrolling overrules ECU for arrays accessed primarily by affine functions, so arrays are placed on one node only if they are primarily accessed by non-affine accesses.

<sup>&</sup>lt;sup>4</sup>An affine function of a set of variables is defined as a linear combination of those variables, plus a constant. As an example, given i and j as enclosing loop variables, A[i+2j+3][2j] is an affine access, but A[i\*j+4] is not.

Figure 1.8: Example showing equivalence-class unification (ECU). (a) Original code. (b) Code and data after ECU on a 2-banked bank-exposed machine. The data declarations are not repeated. With integers a, b and c allocated as shown, both pointer references each go to only one bank, enabling disambiguation.

#### Results

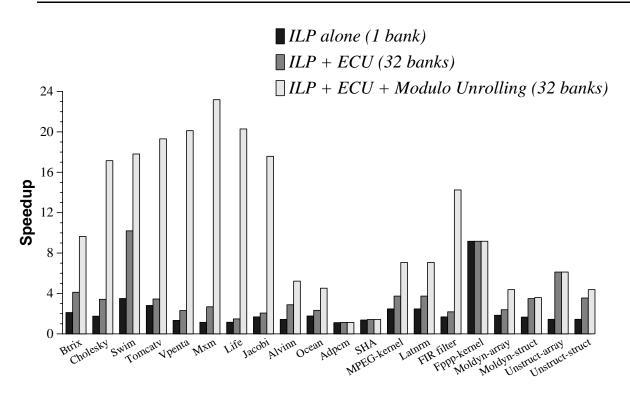

To demonstrate the effectiveness of our bank disambiguation methods, we now preview some results. Maps, including techniques for bank disambiguation and for handling non-disambiguated accesses, has been implemented in a SUIF-based compiler [24] for the Raw machine, called Rawcc. The Maps system is a part of the Raw project's common infrastructure. The Maps infrastructure has been used by at least 6 members of the Raw group. Rawcc accepts as input, ordinary sequential programs with no special user-directives or pragmas. Rawcc automatically detects and exploits both ILP and memory parallelism. Evaluation is performed on a cycle-accurate simulator of the Raw microprocessor.

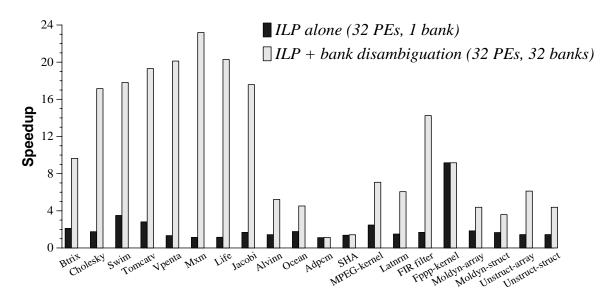

Figure 1.9 compares the speedup for various programs on a 32-tile Raw machine for two cases: a compiler using ILP alone versus a compiler using ILP augmented with the bank disambiguation methods in this thesis. The baseline for both strategies is the sequential program running on one tile with a speedup of 1. In both sets of numbers, ILP is exploited by compiler-discovery, as in VLIW machines. Our techniques for extracting ILP are described in [25]. The ILP alone numbers use 32 PEs, but only one memory bank, as they have no way of disambiguating memory. The ILP + bank disambiguation numbers use 32 PE-memory bank pairs. The benefit from bank disambiguation is the improvement in performance of the ILP + bank disambiguation numbers over the ILP alone numbers. Figure 1.9 demonstrates that using bank disambiguation improves performance over using ILP alone by a factor of 3 to 5 for a broad spectrum of programs<sup>5</sup>.

<sup>&</sup>lt;sup>5</sup>Adpcm, SHA and fppp-kernel are exceptions; see chapter 9 for reasons why.

Figure 1.9: Benefits of bank disambiguation. Comparison of 32-tile speedups using instruction-level parallelism (ILP) alone, versus ILP combined with our bank disambiguation techniques.

The results show that ILP alone is not enough; exploiting memory parallelism dramatically improves performance over using ILP alone. This result has significance beyond Raw. Although this thesis makes no direct comparison with machines other than Raw, the configuration for the *ILP alone* numbers approximates a conventional microprocessor: it has a large number of PEs (32) and a monolithic L1 cache that supports 1 memory access per cycle. The results argue that using a bank-exposed architecture, coupled with bank disambiguation, improves performance over using a conventional architecture with a hardware-based unified memory system.

# 1.4 Non-disambiguated accesses

This section outlines how non-disambiguated accesses are handled efficiently in the Maps compiler system. First, the need of non-disambiguated accesses is motivated. Second, the challenges in efficiently handling non-disambiguated accesses are illustrated. Finally, methods for handling non-disambiguated accesses efficiently in Maps are presented. A baseline method for handling non-disambiguated accesses called *software serial ordering* is presented; an optimization called independent epochs, applicable in certain cases, is also outlined.

#### Motivation

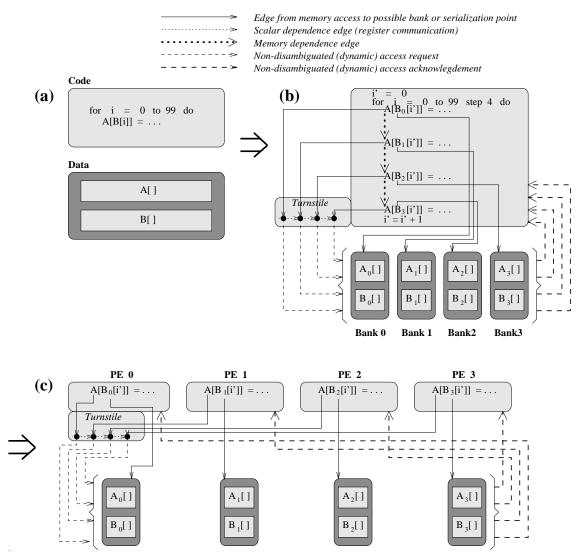

Although ECU alone can provably disambiguate all memory reference instructions, there are cases where it is not desirable to disambiguate all references. Figure 1.10(a) illustrates one such situation. The figure shows two references, \*p and \*q. The values of variables x and y are assumed to be unknown at compile-time. The pointers p and q point to unknown locations within the array A[] and potentially alias to the same location when x = y. Assume that the array A[] is accessed by only affine accesses in the rest of the program and that the affine accesses make up the performance-critical portions of the code. Strict application of ECU would place the array on one tile because of the two non-affine pointer accesses, destroying performance in the performance-critical portions that have affine accesses. Rather than using ECU, it might be better to keep array A distributed, use modulo unrolling in the performance critical portions, and use slow non-disambiguated accesses for the \*p and \*q references. Therefore, an efficient way to deal with non-disambiguated (dynamic) accesses is needed. Amdahl's law predicts that even a small fraction of the program running slowly can significantly degrade the overall performance. Other scenarios where dynamic accesses are helpful are outlined in chapter 5.

### Challenges in handling non-disambiguated accesses

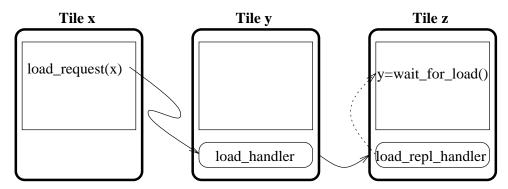

To efficiently implement dynamic accesses, their comparatively long access latencies should be overlapped with each other and with computation as much as possible, while respecting memory dependences. If the arbitration logic is hardware-managed, as in most microprocessors, the task of overlapping latencies is done by the arbitration logic hardware. Although sophisticated write-buffers aim to overlap as much latency as possible, the scalability of arbitration logic is limited. Consequently, the Raw machine investigates the use of a scalable, distributed and point-to-point dynamic network in place of the arbitration logic. The lack of run-time arbitration in such networks means that the task of providing correct memory semantics while overlapping latencies is left to the compiler.

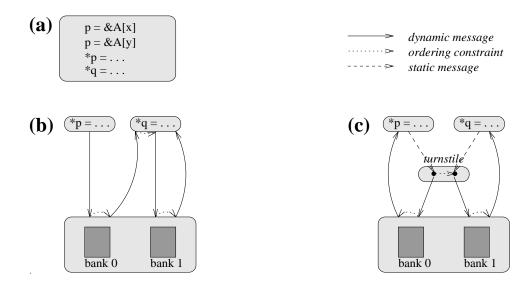

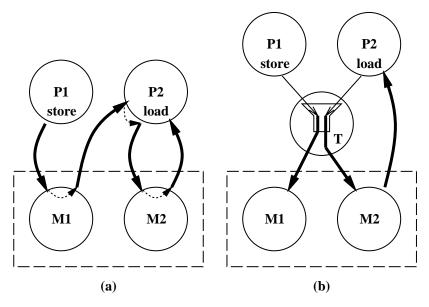

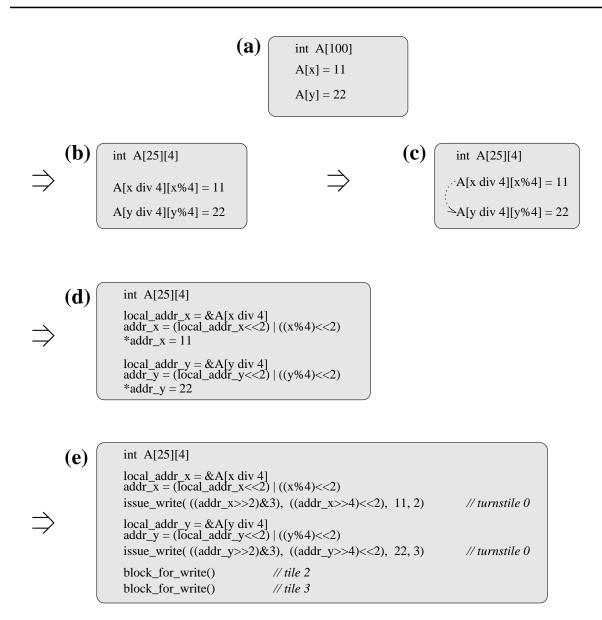

Figure 1.10(b) depicts complete serialization, the most obvious way of implementing the code in figure 1.10(a) using dynamic accesses on Raw. Serialization ensures that the possible dependence between the \*p and \*q references is satisfied. Each dynamic store consists of a non-disambiguated request message to a bank that is unknown at compile-time, followed by an acknowledgment message to the PE scheduled to receive the acknowledgment. In complete serialization, the \*q access does not start until the \*p access receives its reply. The long latencies of dynamic accesses imply that complete serialization is expensive, as complete serialization fails to overlap the dynamic latencies. Overlapping latencies is tricky, because there are no timing guarantees on a distributed dynamic network, such as on Raw. Simply issuing the requests from different banks in

<sup>&</sup>lt;sup>6</sup>From this point on, the terms "non-disambiguated" and "dynamic" are used interchangeably. Non-disambiguated accesses resolve their bank numbers dynamically, *i.e.*, at run-time, hence the term dynamic. The dynamic network on Raw is used to complete dynamic accesses.

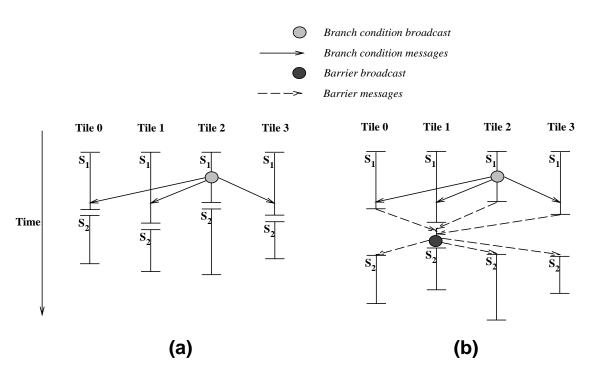

Figure 1.10: Example showing software serial ordering (SSO). (a) Input code. Variables x and y have values unknown at compile-time. (b) Possible dependence enforced through complete serialization. The actual locations accessed are unknown at compile-time. To enforce the possible dependence, the \*q reference does not proceed until the \*p reference is complete. (c) Dependence enforced through software serial ordering. The only serialization is at the turnstile node. Much of the dynamic latencies are overlapped.

program order using explicit synchronization may violate correctness. Request messages might arrive at a memory bank out of order, even if they are issued in order from different banks.

# Software serial ordering

This thesis proposes a method called *software serial ordering* (SSO) to overlap access latencies on distributed dynamic networks while maintaining dependences. SSO relies upon the *in-order*, *wire-like* property between every pair of tiles, offered by many dynamic networks, including the dynamic network on Raw. This property states that if two or more messages are sent between the same source and destination, they appear at the destination tile in the same order as they were launched at the source.

Figure 1.10(c) shows the code in figure 1.10(a) implemented using SSO on a Raw-like distributed dynamic network. SSO involves serializing accesses at a special turnstile node, which may be placed on any of the PEs. The \*p and \*q references make requests to the turnstile node using statically scheduled messages on the static network. The requests are issued in order, from the turnstile to the memory banks, on the dynamic network. At the destination memory bank, whose number is resolved only at run-time, the access is performed and a store-acknowledgment message is sent back to a compile-time known PE, different for different acknowledgments. Correctness is ensured, because

request messages from the turnstile to any one memory bank arrive in program order; in-order delivery follows from the pair-wise in-order property of the network. Hence, if the two references, \*p and \*q, actually alias to the same location at run-time, the request messages arrive at the memory bank containing the location in program order. Finally, when all the acknowledgments are received, the control moves to the next scheduling unit of code after the current scheduling unit. A scheduling unit is the code-granularity at which the Raw compiler performs instruction scheduling; it is defined more precisely in section 1.5.

SSO is slower than ECU. The \*p and \*q references are faster if array A[] is placed on one node. SSO is slower, because the accesses in SSO are serialized, just as in the ECU case, and they also suffer from dynamic overhead. The advantage of SSO is not in the portion of code it is used. Rather, SSO may allow other portions of code elsewhere in the program to run faster, because, unlike ECU, SSO uses distributed arrays. Consequently, other parts of the program can use modulo unrolling if affine accesses are present, improving the performance of those accesses. SSO has been implemented in the Rawcc compiler, and results are presented in chapter 9.

#### Independent epochs

It is possible, in certain cases, to implement dynamic accesses without the turnstile's serialization. If the compiler can prove that accesses to a set of data objects in a region of code are all dynamic and are all independent, then the accesses proceed in parallel without a turnstile. Such a region of code is called an *independent epoch*. A trivial example of an independent epoch is a region whose dynamic accesses to a set of data objects are all loads. Otherwise, independent accesses are found using dependence analysis [26]. Dependence analysis is aided by pointer analysis, array-index analysis, and dataflow analysis.

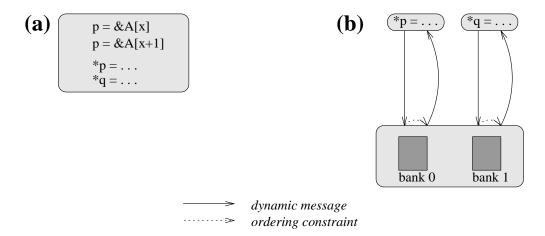

Figure 1.11 shows an example of an independent epoch. Figure 1.11(a) shows the initial code. The code is very similar to that in figure 1.10(a), except that the pointers p and q point to consecutive unknown locations in array A[] instead of any two unknown locations. Dependence analysis reveals that the \*p and \*q references are always independent, irrespective of the value of variable x. Hence, the two references are issued in parallel without a turnstile. Parallel dynamic accesses are depicted in figure 1.11(b). Turnstile serialization is avoided because the references cannot alias at run-time.

One additional step must be taken to ensure correctness for independent epochs: memory barriers must be placed before and after each independent epoch region. A memory barrier is a construct that guarantees that all outstanding memory requests up to that point have been completed. Memory barriers are needed before and after an independent epoch to isolate the epoch from the accesses elsewhere in the program. Without isolation, an access from inside the epoch could be incorrectly reordered at runtime with a dependent access outside the epoch. Implementation of memory barriers is discussed in section 5.5.

Figure 1.11: Example showing independent epochs. (a) Initial code. (b) References implemented as an independent epoch. Dependence analysis reveals that the \*p and the \*q reference are independent, and hence the references are issued as an independent epoch, without serialization.

# 1.5 Compiler flow

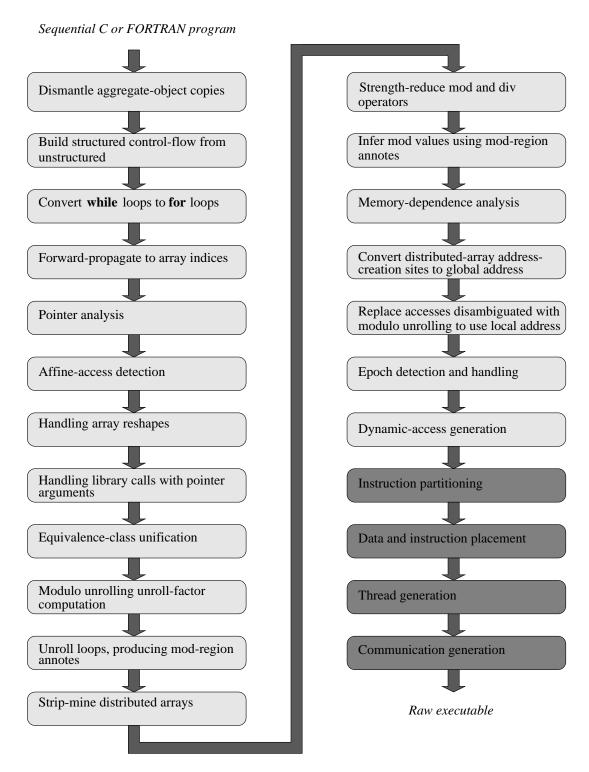

This section shows one possible compiler flow of a compiler for a software-exposed architecture. While other organizations are possible, this is the structure adopted by our compiler for the MIT Raw machine, Rawcc.

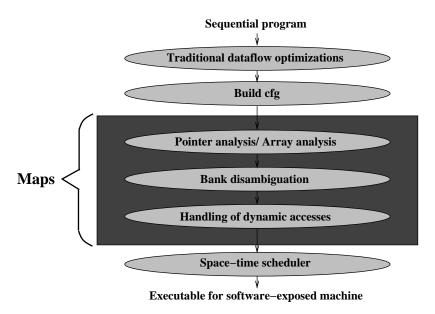

Figure 1.12 shows one possible structure for a compiler targeting a software-exposed architecture. The compiler accepts sequential programs, and automatically extracts parallelism from them for a software-exposed architecture. Rawcc has two main parts. The first part performs tasks related to the management of an exposed memory system. The Maps memory system presented in this thesis comprises this first part. The second part of the compiler is the space-time scheduler [25]. The space-time scheduler performs instruction scheduling and partitioning, as well as routing of static messages. Both Maps and the space-time scheduler are discussed in this section. Taken together, Maps and the space-time scheduler provide a unified view of distributed resources to the user, without requiring a unified view from the hardware.

The Maps memory system begins with pointer analysis and array-specific analysis, and then it performs bank disambiguation. Bank disambiguation first defines a layout of all the data objects in the program, and then tries to specify a fixed bank number, known at compile-time, for every load/store memory reference. Accesses for which a fixed bank number is found at compile-time are annotated with that bank number, and are called disambiguated accesses. Disambiguated accesses translate to fast, local accesses on a bank-exposed machine. Since their results are routed on the static network for Raw, disambiguated accesses are also called static accesses. The remaining accesses to unknown banks are called non-disambiguated accesses and complete over the fall-back

Figure 1.12: Structure of the Raw compiler.

arbitration logic. In the case of Raw, the arbitration logic is replaced by the dynamic network. Hence, non-disambiguated accesses are also called *dynamic accesses*. While disambiguation can be attained at the cost of memory parallelism by mapping all the data to one bank, our techniques provide bank disambiguation while distributing data to several banks.

Following bank disambiguation, Maps ensures that non-disambiguated (dynamic) accesses are handled efficiently. The greatest challenge to improving performance of dynamic accesses is overlapping their long access latencies with other computation and communication while respecting all dependences. This thesis presents methods to aggressively schedule dynamic accesses while respecting dependences. Methods for non-disambiguated accesses include software-serial ordering, independent epochs, and updates.

The second part of the compiler, the space-time scheduler [25], follows the analysis and code transformations in Maps. The space-time scheduler parallelizes the computation in each scheduling unit across the processing elements. A scheduling unit is the code granularity the space-time scheduler considers at one time. Scheduling units are basic blocks or larger; control-localization [25] extends scheduling units to regions of code with forward-control-flow only. Space-time scheduling uses the data distribution and disambiguation information provided by Maps, respecting any dependence and serialization requirements of Maps. Parallelization is achieved by statically distributing the instructions across the tiles and orchestrating any necessary communication at the register level over the static network. The decision of how to map instructions considers the tradeoffs between locality, parallelism and communication cost. Individual instruction streams proceed in a loosely synchronous manner, communicating only when there are register

dependences and at the end of the scheduling units. For more details on the space-time scheduler, please refer to [25].

This compiler structure has been implemented in Rawcc, the Raw compiler built on top of SUIF [24]. Rawcc accepts a sequential program written in C or FORTRAN, and produces a Raw executable. Results in this thesis were obtained by evaluating the Rawcc compiler.

#### 1.6 Overview of the thesis

This section presents a brief overview of the thesis. First, the scope of our compiler methods, in terms of the architectures to which they apply, is presented. Second, the contributions of this thesis are summarized as a list. Third, the organization of the thesis is presented.

#### Scope of our methods