#### Synchronized MIMD Computing

by

Bradley C. Kuszmaul

S.B. (mathematics), Massachusetts Institute of Technology (1984) S.B. (computer science and engineering), Massachusetts Institute of Technology (1984) S.M. (electrical engineering and computer science), Massachusetts Institute of Technology (1986)

#### Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

#### May 1994

© Massachusetts Institute of Technology 1994. All rights reserved.

May 22, 1994

Certified by .....

Charles E. Leiserson Professor of Computer Science and Engineering Thesis Supervisor

#### Synchronized MIMD Computing

by Bradley C. Kuszmaul

Submitted to the Department of Electrical Engineering and Computer Science on May 22, 1994, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

Fast global synchronization provides simple, efficient solutions to many of the system problems of parallel computing. It achieves this by providing composition of both performance and correctness. If you understand the performance and meaning of parallel computations A and B, then you understand the performance and meaning of "A; barrier; B".

To demonstrate this thesis, this dissertation first describes the architecture of the Connection Machine CM-5 supercomputer, a synchronized MIMD (multiple instruction stream, multiple data stream) computer for which I was a principal architect. The CM-5 was designed to run programs written in the data-parallel style by providing fast global synchronization. Fast global synchronization also helps solve many of the system problems for the CM-5, including clock distribution, diagnostics, and timesharing.

Global barrier synchronization is used frequently in data-parallel programs to guarantee correctness, but the barriers are often viewed as a performance overhead that should be removed if possible. By studying specific mechanisms for using the CM-5 data network efficiently, the second part of this dissertation shows that this view is incorrect. Interspersing barriers during message sending can dramatically improve performance of many important message patterns. Barriers are compared to two other mechanisms, bandwidth matching and managing injection order, for improving the performance of sending messages.

The last part of this dissertation explores the benefits of global synchronization for MIMD-style programs, which are less well understood than data-parallel programs. To understand the programming issues, I engineered the StarTech parallel chess program. Computer chess is a resource-intensive irregular MIMD-style computation, providing a challenging scheduling problem. Global synchronization allows us to write a scheduler which runs unstructured computations efficiently and predictably. Given such a scheduler, the run time of a dynamic MIMD-style program on a particular machine becomes simply a function of the critical path length C and the total work W. I empirically found that the StarTech program executes in time  $T \approx 1.02W/P + 1.5C + 4.3$  seconds, which, except for the constant-term of 4.3 seconds, is within a factor of 2.52 of optimal.

Thesis Supervisor: Charles E. Leiserson Title: Professor of Computer Science and Engineering

## Contents

| Contents |                                               |                                                     |    |  |

|----------|-----------------------------------------------|-----------------------------------------------------|----|--|

| Li       | st of l                                       | Figures                                             | 7  |  |

| 1        | Intr                                          | oduction                                            | 9  |  |

| 2        | The                                           | Network Architecture of the Connection Machine CM-5 | 23 |  |

|          | 2.1                                           | The CM-5 Network Interface                          | 25 |  |

|          | 2.2                                           | The CM-5 Data Network                               | 26 |  |

|          | 2.3                                           | The CM-5 Control Network                            | 32 |  |

|          | 2.4                                           | The CM-5 Diagnostic Network                         | 37 |  |

|          | 2.5                                           | Synchronized MIMD Goals                             | 41 |  |

|          | 2.6                                           | CM-5 History                                        | 43 |  |

| 3        | Mechanisms for Data Network Performance       |                                                     |    |  |

|          | 3.1                                           | Introduction                                        | 45 |  |

|          | 3.2                                           | CM-5 Background                                     | 47 |  |

|          | 3.3                                           | Timing on the CM-5                                  | 49 |  |

|          | 3.4                                           | Using Barriers Can Improve Performance              | 50 |  |

|          | 3.5                                           | Packets Should Be Reordered                         | 53 |  |

|          | 3.6                                           | Bandwidth Matching                                  | 55 |  |

|          | 3.7                                           | Programming Rules of Thumb                          | 57 |  |

| 4        | The StarTech Massively Parallel Chess Program |                                                     |    |  |

|          | 4.1                                           | Introduction                                        | 59 |  |

|          | 4.2                                           | Negamax Search Without Pruning                      | 62 |  |

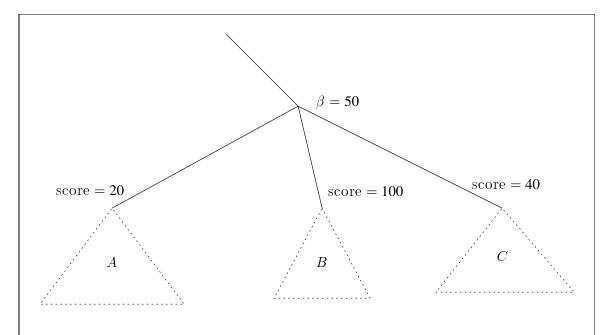

|          | 4.3                                           | Alpha-Beta Pruning                                  | 63 |  |

|          | 4.4                                           | Scout Search                                        | 65 |  |

|          | 4.5                                           | Jamboree Search                                     | 66 |  |

|          | 4.6                                           | Multithreading with Active Messages                 | 67 |  |

|          | 4.7                                           | The StarTech Scheduler                              | 70 |  |

| 5        | The Performance of the StarTech Program 7     |                                                     |    |  |

|          | 5.1                                           | Introduction                                        | 73 |  |

|          | 5.2                                           | Analysis of Best-Ordered Trees                      | 76 |  |

|          | 5.3                                           | Analysis of Worst-Ordered Game Trees                | 81 |  |

|          | 5.4                                           | Jamboree Search on Real Chess Positions             | 84 |  |

|          | 5.5                                           | Scheduling Parallel Computer Chess is Demanding     | 93 |  |

|    | 5.6               | Performance of the StarTech Scheduler                        | 96  |  |  |  |  |

|----|-------------------|--------------------------------------------------------------|-----|--|--|--|--|

|    | 5.7               | Swamping                                                     | 101 |  |  |  |  |

|    | 5.8               | A Space-Time Tradeoff                                        | 109 |  |  |  |  |

| 6  | Tun               | ing the StarTech Program                                     | 113 |  |  |  |  |

|    | 6.1               | Introduction                                                 | 113 |  |  |  |  |

|    | 6.2               | What is the Right Way to Measure Speedup of a Chess Program? | 113 |  |  |  |  |

|    | 6.3               | The Global Transposition Table                               | 116 |  |  |  |  |

|    | 6.4               | Improving the Transposition Table Effectiveness              | 120 |  |  |  |  |

|    | 6.5               | Efficiency Heuristics for Jamboree Search                    | 127 |  |  |  |  |

|    | 6.6               | How Time is Spent in StarTech                                | 128 |  |  |  |  |

| 7  | Con               | clusions                                                     | 133 |  |  |  |  |

| Ac | Acknowledgments   |                                                              |     |  |  |  |  |

| Bi | Bibliography      |                                                              |     |  |  |  |  |

| Bi | Biographical Note |                                                              |     |  |  |  |  |

# **List of Figures**

| 1-1 | The organization of a SIMD computer                                                 | 11 |

|-----|-------------------------------------------------------------------------------------|----|

| 1-2 | The organization of a synchronized MIMD computer.                                   | 11 |

| 1-3 | A fragment of data-parallel code.                                                   | 14 |

| 1-4 | Naive synchronized-MIMD code.                                                       | 14 |

| 1-5 | Optimized synchronized-MIMD code.                                                   | 14 |

| 1-6 | Exploiting the split-phase barrier via code transformations.                        | 15 |

| 2-1 | The organization of the Connection Machine CM-5.                                    | 24 |

| 2-2 | A binary fat-tree                                                                   | 26 |

| 2-3 | The interconnection pattern of the CM-5 data network.                               | 27 |

| 2-4 | The format of messages in the data network.                                         | 29 |

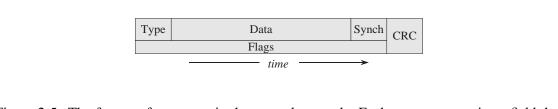

| 2-5 | The format of messages in the control network.                                      | 35 |

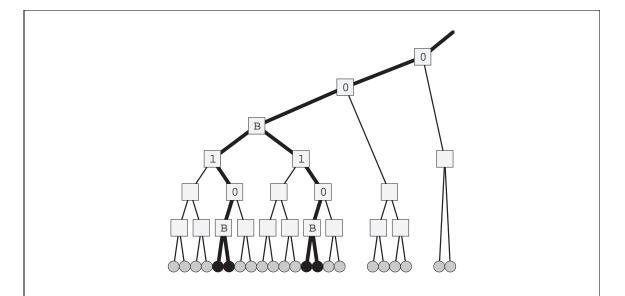

| 2-6 | Steering a token down the diagnostic network.                                       | 40 |

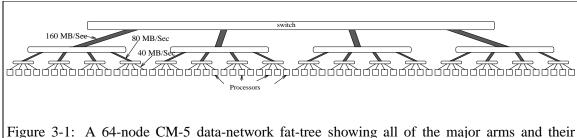

| 3-1 | A 64-node CM-5 data-network fat-tree showing all of the major arms and their        |    |

|     | bandwidths (in each direction).                                                     | 47 |

| 3-2 | The CM-5 operating system inflates time when the network is full                    | 49 |

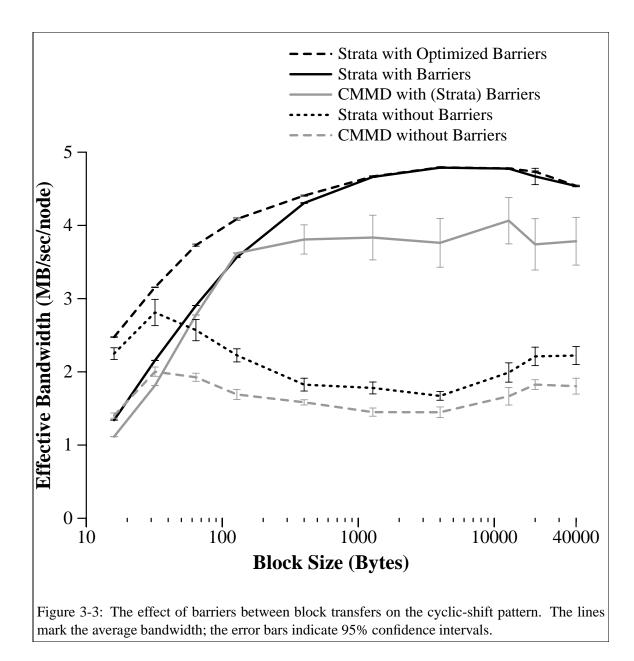

| 3-3 | The effect of barriers between block transfers on the cyclic-shift pattern.         | 51 |

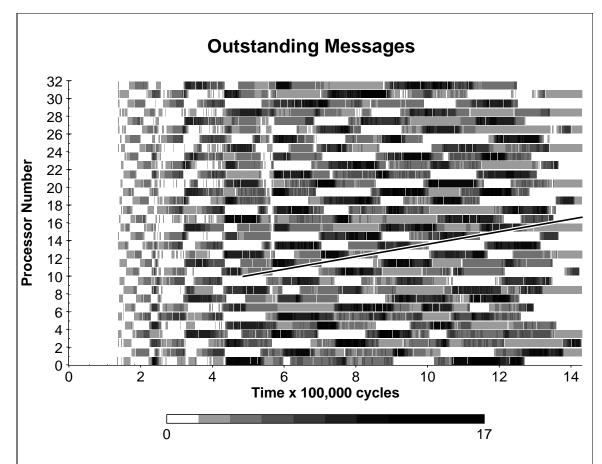

| 3-4 | The total number of packets in the network headed to any given processor at any     |    |

|     | given time.                                                                         | 52 |

| 3-5 | Big blocks also suffer from target collisions.                                      | 53 |

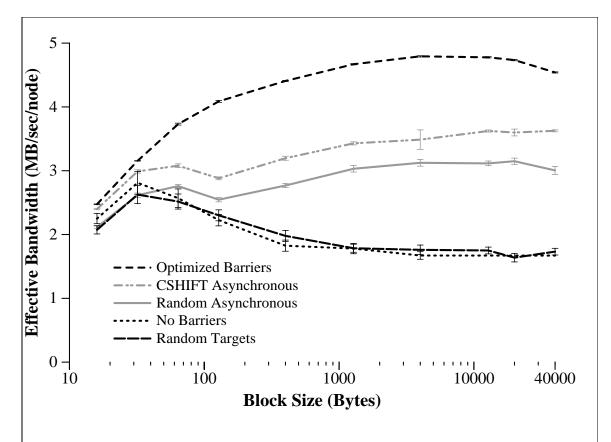

| 3-6 | The effect on performance of interleaving messages.                                 | 54 |

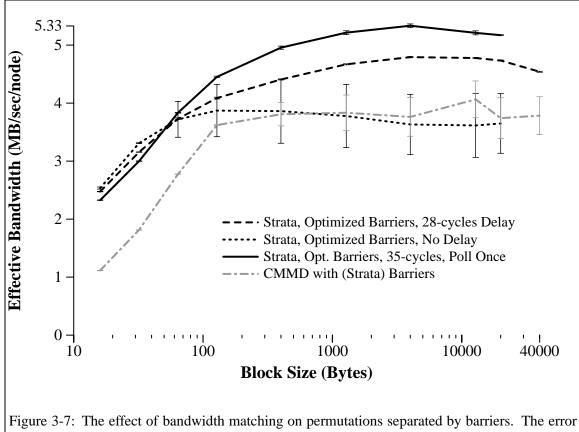

| 3-7 | The effect of bandwidth matching on permutations separated by barriers              | 56 |

| 4-1 | Algorithm negamax.                                                                  | 63 |

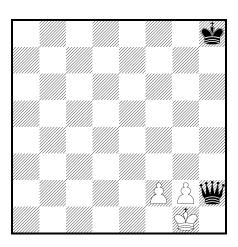

| 4-2 | Practical pruning: White to move and win.                                           | 64 |

| 4-3 | Algorithm absearch.                                                                 | 64 |

| 4-4 | Algorithm scout.                                                                    | 65 |

| 4-5 | Algorithm jamboree.                                                                 | 66 |

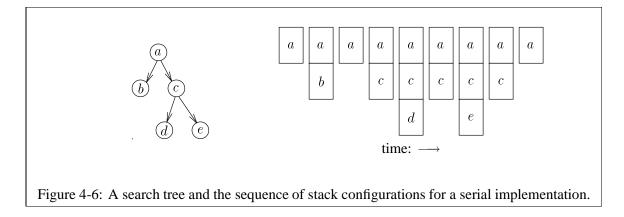

| 4-6 | A search tree and the sequence of stack configurations for a serial implementation. | 67 |

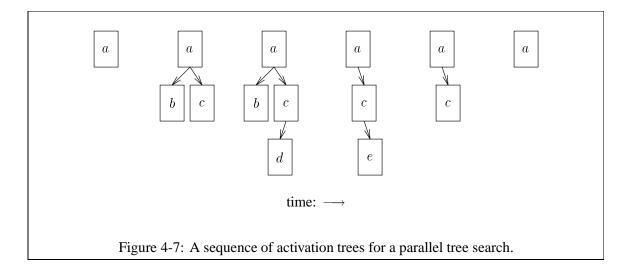

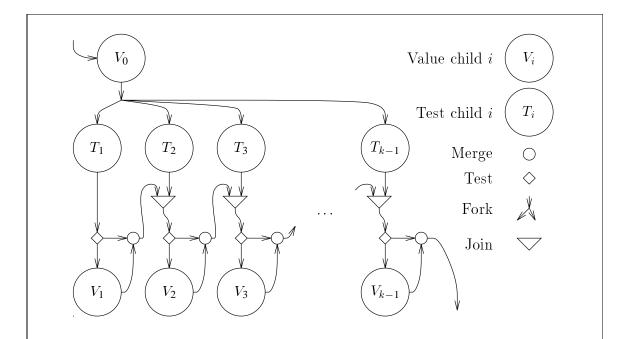

| 4-7 | A sequence of activation trees for a parallel tree search.                          | 68 |

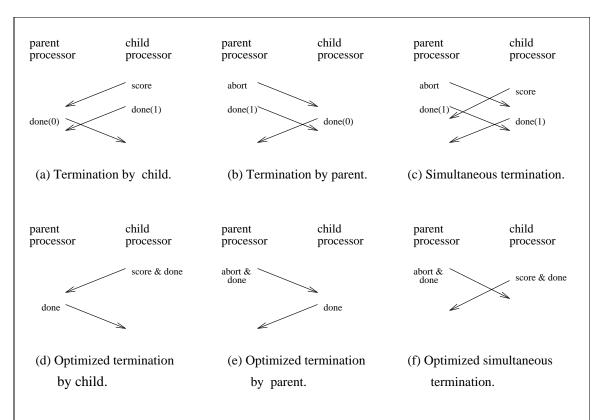

| 4-8 | Three possible ways to for a frame to terminate.                                    | 69 |

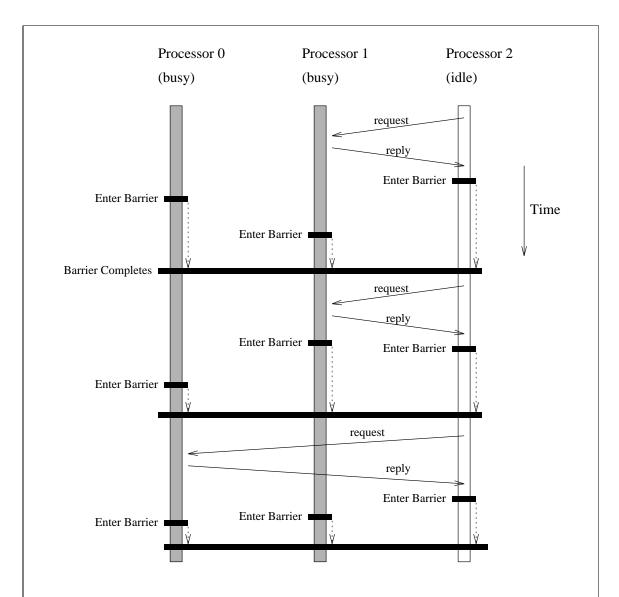

| 4-9 | Busy processors keep working while the split-phase barrier completes.               | 72 |

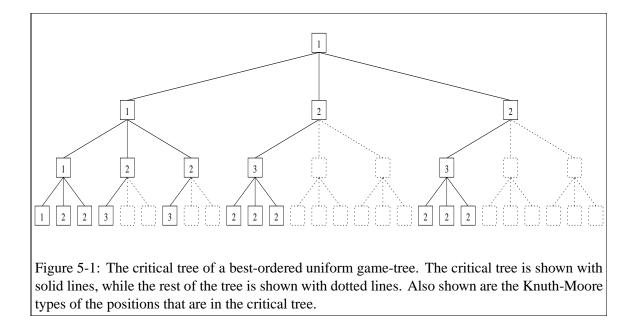

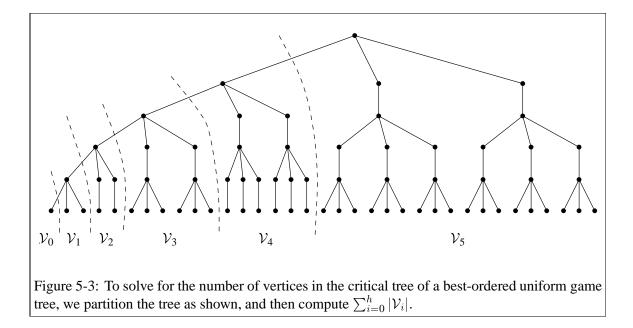

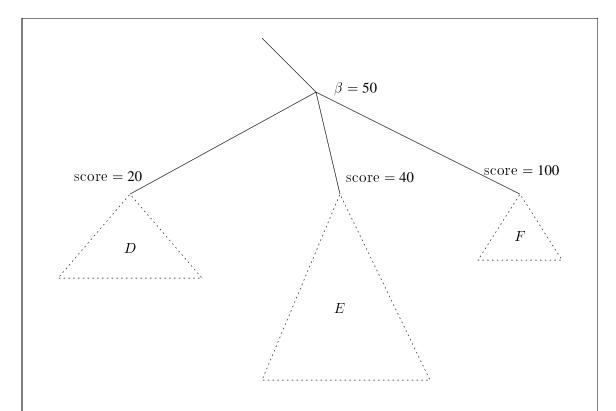

| 5-1 | The critical tree of a best-ordered uniform game-tree.                              | 77 |

| 5-2 | Numerical values for average available parallelism.                                 | 78 |

| 5-3 | Partitioning the critical tree to solve for the number of vertices.                 | 79 |

| 5-4 | Performance metrics for worst-ordered game trees.                                   | 82 |

| 5-5 | Jamboree search sometimes does more work than a serial algorithm.                   | 85 |

| 5-6  | Jamboree search sometimes does less work than a serial algorithm.                    | 86  |  |

|------|--------------------------------------------------------------------------------------|-----|--|

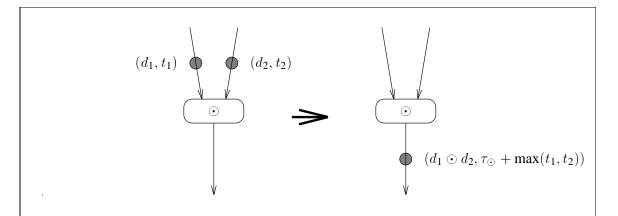

| 5-7  | The dataflow graph for Jamboree search.                                              |     |  |

| 5-8  | Computing the estimated critical path length using timestamping.                     |     |  |

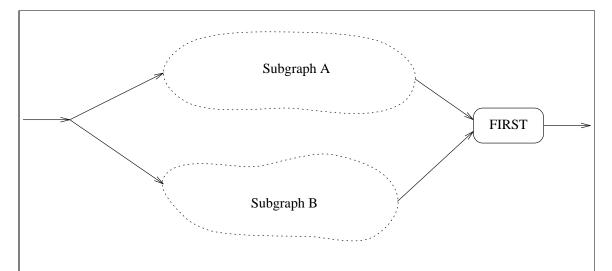

| 5-9  | -9 The critical path of a computation that includes parallel-or.                     |     |  |

| 5-10 |                                                                                      |     |  |

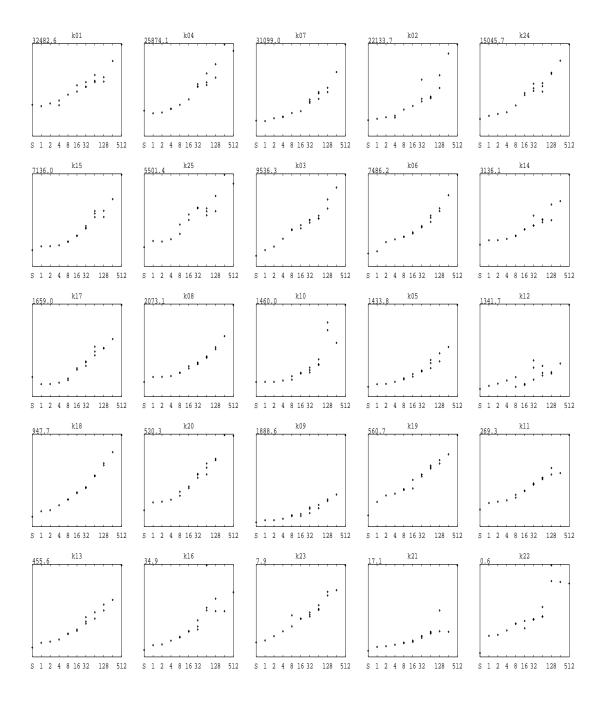

| 5-11 | 11 The critical path of each of 25 chess positions.                                  |     |  |

| 5-12 | 2 Serial run time versus work efficiency.                                            |     |  |

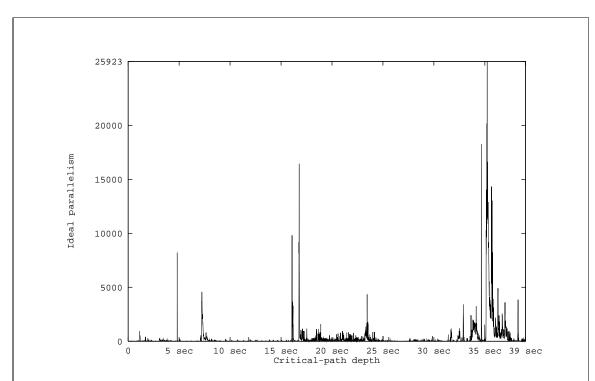

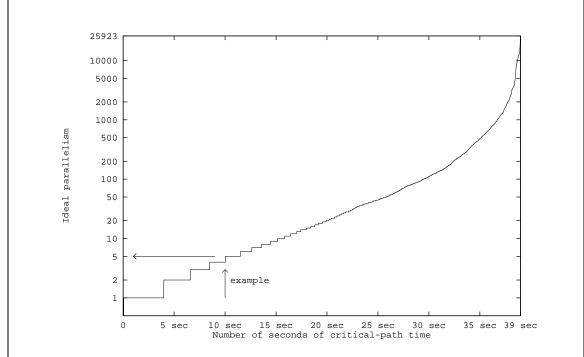

| 5-13 | 3 The ideal-parallelism profile of a typical chess position.                         |     |  |

| 5-14 | 4 The sorted ideal-parallelism profile.                                              |     |  |

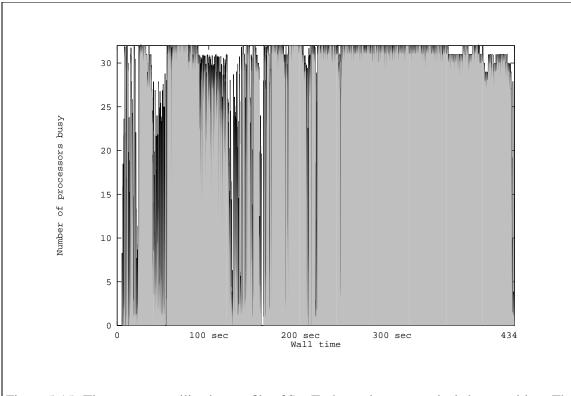

| 5-15 | 15 The processor utilization profile of a typical chess position.                    |     |  |

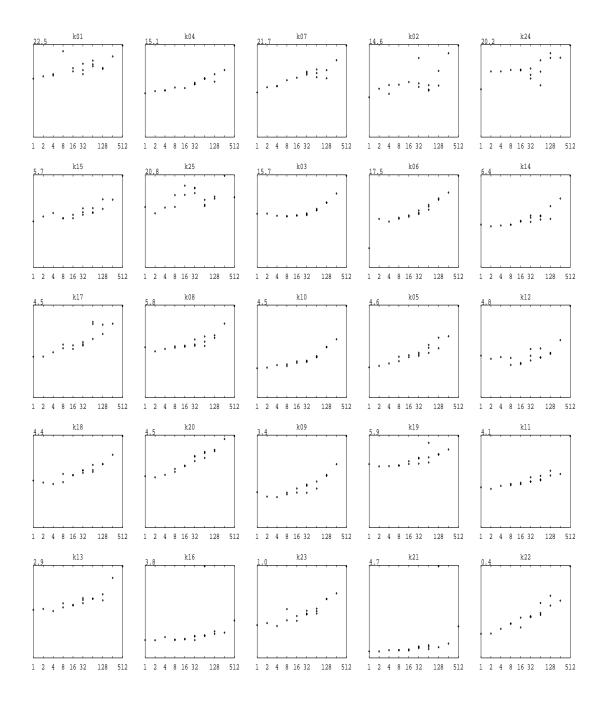

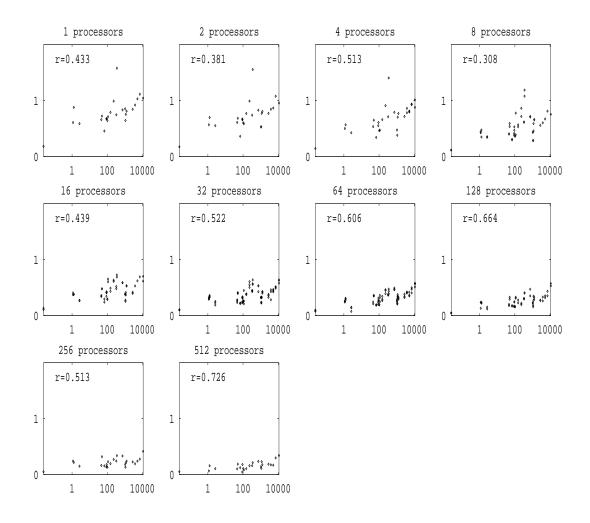

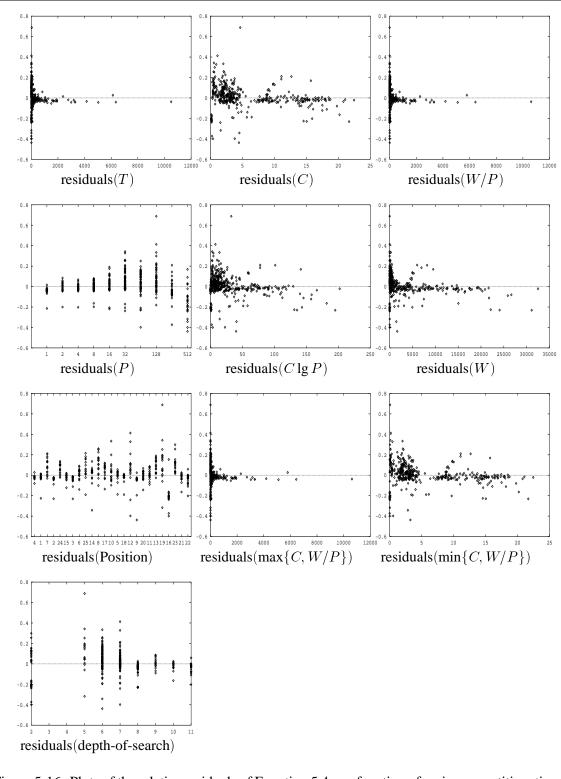

|      | 6 Residual plots of the performance model as a function of various quantities.       |     |  |

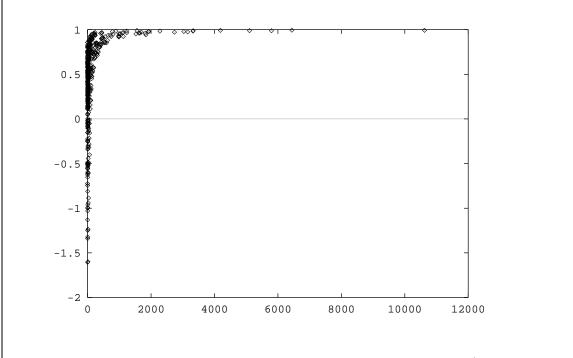

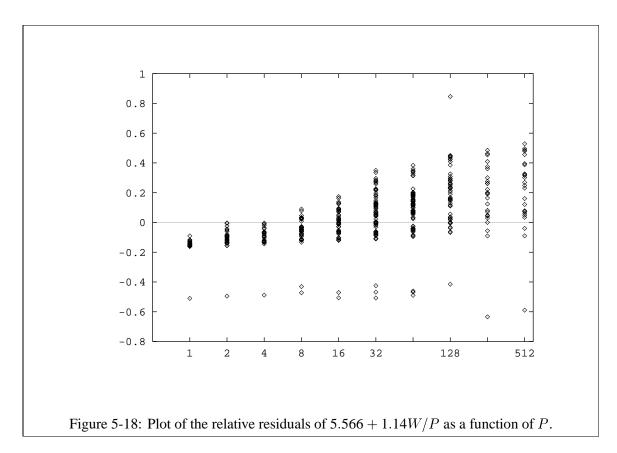

| 5-17 | Residual plot for a model that is too simple.                                        | 100 |  |

| 5-18 | Residual plot for another model that is too simple.                                  | 101 |  |

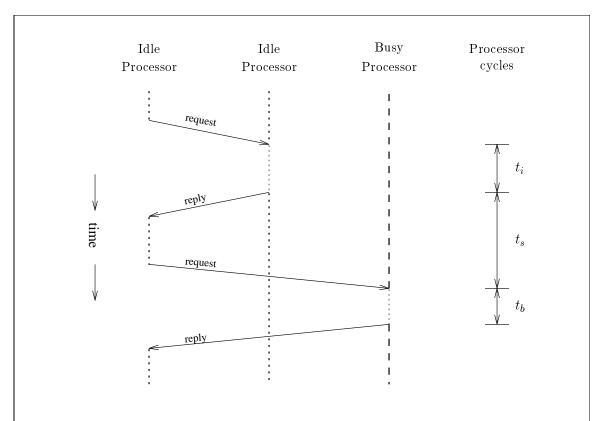

| 5-19 | The relationship of $t_b$ , $t_i$ and $t_s$ in the SWAMP program.                    | 103 |  |

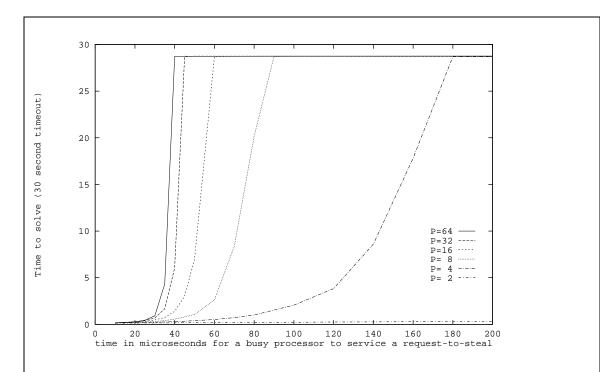

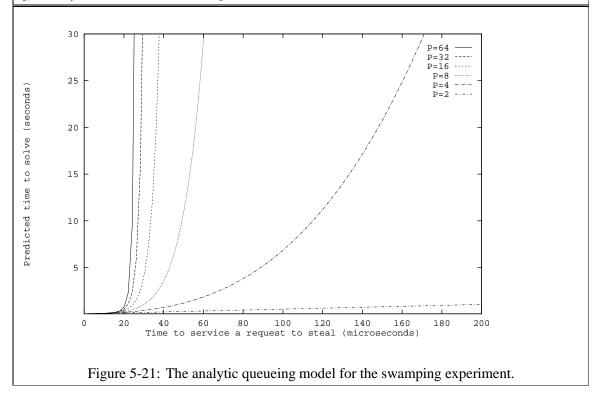

| 5-20 | Results for the isolated swamping experiment.                                        | 104 |  |

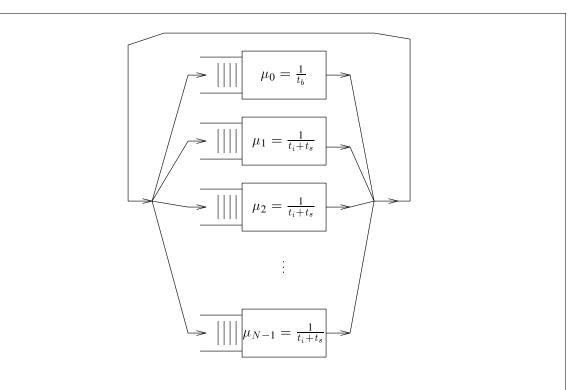

| 5-21 | The analytic queueing model for the swamping experiment.                             | 104 |  |

| 5-22 | A Jackson network that models the swamping problem.                                  | 105 |  |

| 5-23 | Examples of $p_{(0,*)}$ expanded for a few machine sizes.                            | 108 |  |

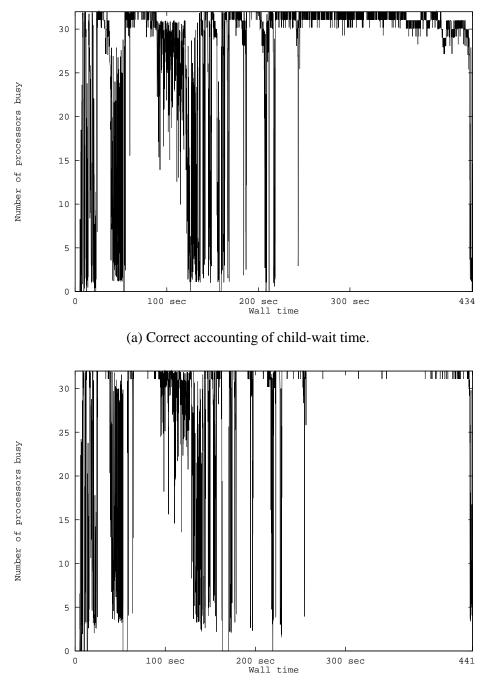

| 5-24 | Waiting for children to complete causes most of the inefficiency during processor-   |     |  |

|      | saturation.                                                                          | 111 |  |

| 6-1  | Serial performance versus transposition table size.                                  | 115 |  |

| 6-2  | Parallel performance versus number of processors.                                    | 116 |  |

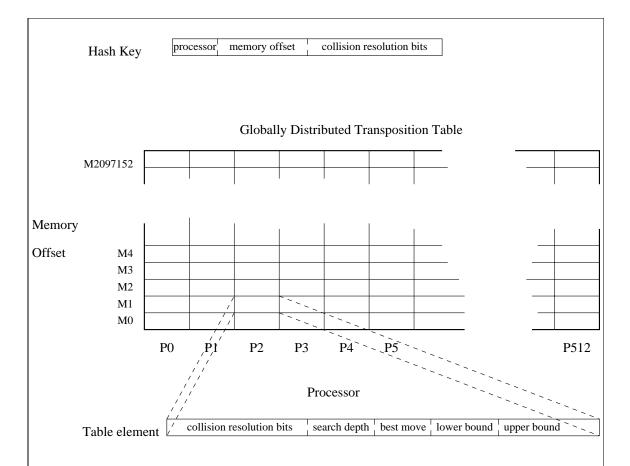

| 6-3  | The Startech transposition table is globally distributed.                            | 117 |  |

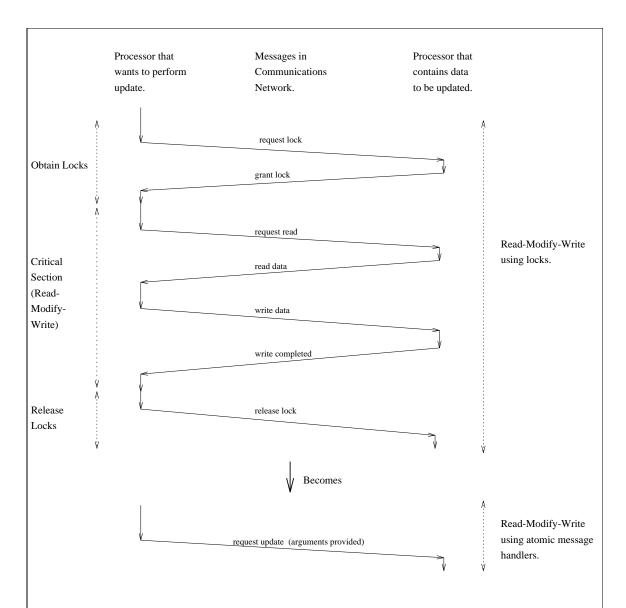

| 6-4  | Transforming a protocol that uses locks into an active-message protocol.             | 119 |  |

| 6-5  | The effect of recursive iterative deepening (RID) on the serial program.             | 122 |  |

| 6-6  | The effect of deferred reads and recursive iterative deepening using 512 processors. | 124 |  |

| 6-7  | The effect of deferred reads and recursive iterative deepening using 128 processors. | 125 |  |

| 6-8  | The effect of deferred reads and recursive iterative deepening using 256 processors. | 126 |  |

| 6-9  | How processor cycles are spent.                                                      | 129 |  |

| 6-10 | A breakdown of the 'chess work'.                                                     | 129 |  |

## **Chapter 1**

## Introduction

#### The Synchronized MIMD Thesis

Fast global synchronization can solve many of the system problems of parallel computing.

To demonstrate that fast global synchronization solves many of the system problems of parallel computing, this dissertation first describes hardware and then software, both of which are organized around fast global synchronization. Fast global synchronization is not the only way to solve the system problems of parallel computing, but it provides simple solutions to them. This thesis describes in detail the Connection Machine CM-5 supercomputer and the StarTech massively parallel chess program, treating these systems as example points in the design space of parallel systems. I explain the systems, and rather than systematically comparing various ways to solve the problems, I show simple solutions to problems that have been difficult to solve previously.

# The Connection Machine CM-5: Architectural Support for Data-Parallel Programming.

The idea of using fast global synchronization to solve system problems grew out of the CM-5 project which started in 1987 at Thinking Machines Corporation. The primary design goal of the CM-5 was to support the *data-parallel* programming model [HS86, Ble90]. Data-parallel programs run efficiently on the Connection Machine CM-2 computers, which is a *SIMD* (single-instruction stream, multiple-data stream) machine. It was of prime importance for any new machine to continue to run such programs well. As one of the principal architects of the CM-5,<sup>1</sup> I helped design a *MIMD* (multiple-instruction stream, multiple-data stream) machine to execute data-parallel programs.<sup>2</sup>

The data-parallel style of programming is successful because it is simple and programmers can

<sup>&</sup>lt;sup>1</sup>I was the first member of the CM-5 design team, which eventually grew to include Charles E. Leiserson, Zahi S. Abuhamdeh, David C. Douglas, Carl R. Feynman, Mahesh N. Ganmukhi, Jeffrey V. Hill, W. Daniel Hillis, Margaret A. St. Pierre, David S. Wells, Monica C. Wong, Shaw-Wen Yang, and Robert Zak. All told, about 500 people participated in the implementation of the CM-5.

<sup>&</sup>lt;sup>2</sup>The SIMD/MIMD terminology was developed by Flynn [Fly66].

reason about it. A data-parallel program is an ordinary serial program with vector primitives.<sup>3</sup> Vector primitives include

- elementwise operations,

- bulk data communications operations, and

- global reductions and scans.

In the following, we denote vectors by upper-case letters and scalars by lower case letters. Elementwise operations are exemplified by vector addition, which can be expressed as  $A \leftarrow B + C$ (which means that for each j, B[j] + C[j] is stored into A[j].) Bulk data communications can be expressed, for example, as  $A[I] \leftarrow B$  (which means that each j, B[j] is stored into A[I[j]].) Global reductions and scans can be expressed, for example as GLOBAL\_OR(A) (which returns the logical 'or' of all the elements of A.) In addition, data-parallel programming languages typically provide a conditional execution construct, the WHERE statement, that looks like this:

In the body of the WHERE, all vector operations are conditionally executed depending on the value of the expression. For example

where

$$(B < 0)$$

$B \leftarrow B + C;$

has the effect of incrementing B[j] by C[j] for each j such that B[j] < 0.

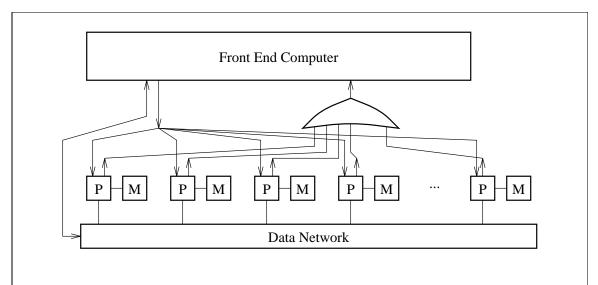

Data parallel programs have traditionally been run on SIMD machines. In fact, the SIMD machines engendered the data-parallel style of programming [Chr83, Las85, HS86, Ble90]. Examples of SIMD machines include the Illiac-IV [BBK\*68], the Goodyear MPP [Bat80], and the Connection Machine CM-1 and CM-2 [Hil85]. Such machines provide a collection of processors and their memories that are controlled by a front-end computer (see Figure 1-1.) The front-end broadcasts each instruction to all of the processors, which execute the instruction synchronously. The broadcast network is embellished with an 'or' network that can take a bit from every processor, combine them using logical or, and deliver the bit to the front end (and optionally to all the processors.) The data network allows data to be moved, in parallel, between pairs of processors by sending messages from one processor to another. The data network is also synchronously controlled by the front-end, which can determine when all messages in the data network have been delivered. The SIMD architecture is synchronous down to the clock cycle.

To execute a data parallel program on a SIMD machine is straightforward. The SIMD machine has a single instruction counter, which matches the program's single thread of control. The vectors are distributed across the machine. The program is executed on the front-end computer with each standard serial statement executed as for a serial program. To execute a vector elementwise operation, the instructions encoding the operation are broadcast, and each processor manipulates its part of the vectors. To execute bulk communications operations, instructions are broadcast to move the data through the data network of the machine. To execute a global scan, instructions are

<sup>&</sup>lt;sup>3</sup>Examples of of SIMD vector primitives include PARIS, the Parallel Instruction Set developed for the CM-2 [Thi86b], and CVL, a C vector library intended to be portable across a wide variety of parallel machines [BCH\*93].

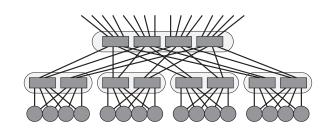

Figure 1-1: The organization of a SIMD computer. The front-end computer controls the processormemory pairs, through a broadcast network, on a clock-cycle by clock-cycle basis. The 'or' network accepts a bit from each processor and delivers the logical 'or' of all the bits to the front-end. The front-end also controls the data network.

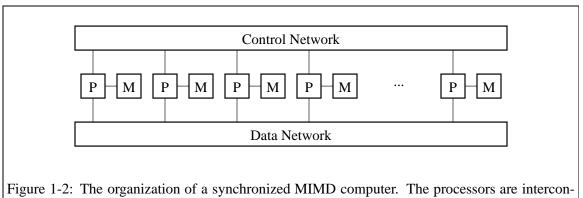

nected by two networks: a data network and a control network.

broadcast to implement a parallel-prefix reduction. The execution of a reduction is similar to a scan, except that the reduced value is communicated to the host through the global 'OR' network. To execute conditional operations, a context mask is maintained in each processor. Each processor conditionally executes the broadcast instructions based on this mask. The WHERE statement simply manipulates the context mask.

In the CM-5, we departed from the SIMD approach and built a *synchronized MIMD* machine. A synchronized MIMD machine consists of a collection of processors, a data network, and a control network (see Figure 1-2.) The processors' job is to perform traditional operations on local data, e.g., floating point operations. The data network's job is to move data from one processor to another via message passing. The control network's job is to synchronize an entire set of processors quickly, and to implement certain multiparty communication primitives such as broadcast, reduction, and parallel prefix.

To execute a data parallel program on a synchronized MIMD machine, we simulate the SIMD machine. If a synchronized MIMD machine can simulate a SIMD machine efficiently enough, then we can use the synchronized MIMD machine to execute both MIMD-style and data-parallel

computations, instead of using different machines for different styles of computation. A SIMD computation can be simulated on a synchronized MIMD machine by transforming the serial SIMD program that runs on the front-end of the SIMD machine into a program that runs in parallel on every processor of the synchronized MIMD machine. The vectors are laid out across the machine as for a SIMD machine. Each vector primitive is implemented as a subroutine that performs the 'local' part of the primitive for a processor. The 'serial' part of the data-parallel code executes redundantly on every processor, calling the subroutines to perform the local part of each vector primitive.<sup>4</sup> Bulk data transfers are accomplished using the data network. Global scans and reductions use the control network. For conditional operations a context mask is maintained, just as for SIMD machines. To keep the processors in step, the machine is globally synchronized between nearly every vector primitive, which justifies the hardware for a control network.<sup>5</sup>

Without frequent global synchronization the program would execute incorrectly. Consider the following code fragment:

| (R1) | $A[I] \leftarrow B;$  |

|------|-----------------------|

| (R2) | $A \leftarrow A + C;$ |

Line R1 calls for interprocessor communication, and then Line R2 uses the result of the communication, A, as the operand to a vector multiply, and then stores the result back into A. Consider what happens if we do not insert a synchronization between Lines R1 and R2. Processor 0 might finish sending its local parts of B to the appropriate places in A, and then Processor 0 could race ahead to start executing Line R2. There would be no guarantee that the local copy of A had been completely updated, however, since some other processor might still be sending data to Processor 0, so the values provided to the vector addition could be wrong. To add insult to injury, after doing the vector multiply, the data being sent to Processor 0 data could then arrive and modify the local part

<sup>&</sup>lt;sup>4</sup>The idea of distributing a single program to multiple processors has been dubbed "SPMD," for *single-program, multiple data* [DGN\*86]. H. Jordan's language, The Force, was an early SPMD programming language dating from about 1981 [JS94] and appearing a few years later in the literature [Jor85, Jor87, AJ94]. S. Lundstrom and G. Barnes describe the idea of copying a program and executing it on every processor of the Burroughs Flow Model Processor (FMP) [LB80]. Here, however, we focus on how to execute a data-parallel program rather than how to generally program in a SPMD style. In Chapter 4 we will consider the problem of running more general MIMD programs.

<sup>&</sup>lt;sup>5</sup>The idea of building a MIMD machine with a synchronization network is not original with the CM-5. The Burroughs Flow Model Processor (FMP), proposed in 1979, included a control network and a data network that connected processors to memories [LB80]. The barrier network of the FMP was a binary tree that could synchronize subtrees using split-phase barriers. The proposed method of programming the FMP was to broadcast a single program to all the processors, which would then execute it, using global shared memory and barrier synchronization to communicate. The FMP was not built. however. The DADO machine [SS82] of S. Stolfo and D. Shaw provides a control network for a SIMD/MIMD machine. In SIMD mode, the control network broadcasts instructions, while in MIMD mode a processor is disconnected from 'above' in the control network so that it can act as the front-end computer for a smaller SIMD machine. The DADO machine performs all communication in its binary-tree control network. The DATIS-P machine [PS91] of W. Paul and D. Scheerer provides a permutation network and a synchronization network. The DATIS-P permutation network provides no way of recovering from collisions of messages. Routing patterns must be precompiled, and synchronization between patterns is required to ensure the correct operation of the permutation network. The CM-5 design team developed the idea of using split-phase global synchronization hardware [TMC88], and carried it to a working implementation. In independent work, C. Polychronopoulos proposed hardware that would support a small constant number of split-phase barriers that each processor could enter in any order it chose [Pol88]. R. Gupta independently described global split-phase barriers in which arbitrary subsets of processors could synchronize, using the term *fuzzy barrier* [Gup89]. Gupta's proposed implementation is much more expensive than a binary tree. The term *split-phase* describes the situation more accurately than does the term *fuzzy*. M. O'Keefe and H. Dietz [OD90] discuss using hardware barriers that have the additional property that all processors exit the barrier simultaneously. Such barriers allow the next several instructions on each processor to be globally scheduled using, for example, VLIW techniques [Ell85].

of A, overwriting the result of the vector addition. The easiest way to solve this problem is to place a barrier synchronization between Lines R1 and R2.

In *barrier synchronization*, a point in the code is designated as a barrier. No processor is allowed to cross the barrier until all processors have reached the barrier.<sup>6</sup> One extension of this idea is the *split-phase barrier*, in which the barrier is separated into two parts. A point in the code is designated as the *entry-point* to the barrier, and another point is designated as the *completion-point* of the barrier. No processor is allowed to cross the completion point of the barrier until all processors have reached the entry-point. Split-phase barriers allow processors to perform useful work while waiting for the barrier to complete.<sup>7</sup>

Barriers that synchronize only the processors are inadequate for some kinds of bulk communication. During the execution of Line R1 above, each processor may receive zero, one, or more messages. Every processor may have sent all its messages, but no processor can proceed to execute Line R2 until all its incoming messages, some of which may still be in the network, have arrived. To address this problem, the CM-5 provides a *router-done* barrier synchronization that informs all processors of the termination of message routing in the data network.

The router-done barrier is implemented using *Kirchhoff counting* at the boundary of the data network. Each network interface keeps track of the difference between the number of messages that have arrived and the number that have departed. Each processor notifies the network interface when it has finished sending messages, and then the control network continuously sums up the differences from each network interface. When the sum reaches zero, the "router-done" barrier completes.<sup>8</sup>

Kirchhoff counting has the several advantages over the other approaches to computing routerdone.<sup>9</sup> Irrelevant messages (such as operating-system messages) can be ignored, allowing routerdone to be computed on user messages only. Kirchhoff counting can detect lost or created messages, because the sum never converges to zero. It is independent of the topology of the data network. Finally, Kirchhoff counting is fast, completing in the same time as it takes for a barrier, independently of the congestion in the data network.

Even with hardware support to execute global synchronization quickly, we would like to avoid doing more synchronization than we need. Each synchronization costs processor cycles to manipulate the control network, and also costs the time it takes for all the processors to synchronize. If one processor has more work to do than the others, that processor makes the others wait. This inefficiency is related to the inefficiency of executing conditional instructions on a SIMD machine, since in both cases processors sit idle so that other processors can get work done.

There are several ways to further reduce the cost of synchronization, including removing synchronization and weakening the synchronization. To remove synchronization we can observe that not every vector primitive requires a synchronization at the end of the operation. Synchronization is only required when processors communicate. To weaken synchronization, we can observe that processors could do something useful while waiting for synchronization to complete.

<sup>&</sup>lt;sup>6</sup>B. Smith credits H. Jordan with the invention of the term "barrier synchronization" [Smi94]. According to Smith, Jordan says that the name comes from the barrier used to start horse races. Jordan used barriers to synchronize programs for the Finite Element Machine described in [Jor78]. Smith states that Jordan later used the idea in The Force, an early SPMD programming language. Other descriptions of barriers can be found in [TY86, DGN\*86].

<sup>&</sup>lt;sup>7</sup>Hardware for split-phase barriers was designed for the proposed FMP [LB80]. R. Gupta proposed split-phase barriers in which arbitrary subsets of processors could synchronize, using the term *fuzzy barrier* [Gup89].

<sup>&</sup>lt;sup>8</sup>The name "Kirchhoff counting" is related to Kirchhoff's current law (see, for example, [SW75]).

<sup>&</sup>lt;sup>9</sup>Other approaches to computing router-done include software and hardware. In software one can acknowledge all messages, and then use a normal processor-only barrier. Such an approach can double the message traffic, or requires modifications to the data network. [PC90] The Connection Machine CM-1 uses a hardware global-or network to determine when the router is empty [Hil85].

(D1)  $A \leftarrow B \cdot C;$ (D2)  $D \leftarrow B + E;$

Figure 1-3: A fragment of data-parallel code.

Figure 1-4: The naive translation, of the data-parallel code fragment, into the local code to run on a synchronized MIMD processor. We use the notation  $A_l$  to denote the part of array A that is kept locally on the processor. The value of localindices() is the set of indices of the arrays that are kept on a single processor (we assume here that the arrays are all aligned.) The code updates the local part of A, performs a barrier, updates the local part of D, and performs a barrier.

Figure 1-5: The optimized synchronized MIMD code. We removed the barrier on Line (N3), collapsed the loops, and performed common subexpression analysis to avoid loading  $B_l[i]$  twice from memory.

One can remove barriers between statements that have only local effects. For example, if we have the data parallel code shown in Figure 1-3, and if we assume that the arrays are all the same size and are aligned so that A[i], B[i], C[i], D[i], and E[i] are all on the same processor, then the naive per-processor code would look like Figure 1-4. We observe that the barrier on Line (N3) is not needed because there are no dependencies between Lines (D1) and (D2) in the original code. We can also collapse the loops so that only one pass is needed, and we can avoid loading the value of B[i] twice, resulting in the code of Figure 1-5. By transforming the code containing synchronizations, we have not only reduced the amount of synchronization, but we have exposed additional opportunities for code optimization.

Removing barriers from code that has only local effects is straightforward, but the situation is more complex when there is interprocessor communication. For example, when executing a *send*, expressed as  $A[I] \leftarrow B$ , a synchronization is required after the operation to make sure all the updates have taken place. When performing a *get*, expressed as  $B \leftarrow A[I]$ , a synchronization is required before the operation to make sure that the value of A is globally up-to-date before fetching the data. One simple rule is to include a barrier before and after any code that communicates.

Often, simply expressing a barrier as a split-phase barrier makes an optimization obvious. Figure 1-6 shows how a while loop controlled by a global 'sum' operation might be translated into

$\begin{array}{c|c} (\text{M1}) & \text{while} (\texttt{global\_sum}(v)) \\ (\text{M2}) & \cdots \end{array} \Rightarrow$

Figure 1-6: By transforming the monolithic global 'sum' operation on the left into the split-phase global 'sum' operations on the right, we can expose opportunities to hide the latency of the global 'sum' operation.

split-phase operations.<sup>10</sup> First, the global sum operation is initialized, providing the value of v to the control network. Then, the global sum is completed and the result is used to control the while loop. Before the next iteration of the while loop, the next global sum is started. Now, we have the opportunity to start the global 'sum' on Line (S4) sooner. We could move Line (S4) to just after the last modification of v in the elided code of Line (S3). By transforming the code, we can hide the latency of the global synchronization.

Sometimes barriers should not be removed or weakened. A split-phase barrier does not provide the performance composition property provided by a monolithic barrier. To understand the performance of

A; enter-barrier; B; complete-barrier; C;

requires that you understand how A and B can interact and how B and C can interact.<sup>11</sup> This is more difficult to understand than the case

#### A; barrier; B;

where the the two parts of the program are completely separated by a monolithic barrier. We will see several examples in this dissertation where barriers are not needed for the correct execution of a program, but are needed to achieve high performance. In Chapter 3 we show that barriers can improve the performance of interprocessor communication, and in Chapter 5 we show that barriers are useful in a dynamic-MIMD program to keep idle processors from swamping busy processors.

Thus, fast global synchronization hardware allows straightforward and efficient execution of data parallel programs on MIMD machines. It also turns out that by using global synchronization as the underlying organizing strategy of the CM-5, we were also able to solve many other system problems of parallel computing such as time-sharing, diagnostics, and clock distribution.

We also used the global synchronization mechanism to support the operating system in the CM-5. The timesharing system globally schedules the processors so that they are all running the same user program at the same time.<sup>12</sup> We treat the messages in the network as part of the process state, and at the time of a process-switch, the entire network state is saved in the process descriptor. Because the network state is swapped out, the performance of each process is independent of the

<sup>&</sup>lt;sup>10</sup>One can perform a split-phase scan or reduction using the CM-5 control network. Such an operation implicitly includes a split-phase barrier, since the reduction does not complete until all processors have provided a value.

<sup>&</sup>lt;sup>11</sup>Before the split phase barrier completes, some processors may be executing A, and some may be executing B. After every processor has entered the barrier and the barrier has completed, some of the processors may still be executing Bwhile others have started to execute C.

<sup>&</sup>lt;sup>12</sup>The CM-5 is also divided into partitions with each partition operating independently. Here we focus on the behavior of a single partition.

behavior of other processes. In order to be able to quickly empty the data network and to evenly distribute the network state among the processors, we developed the *all-fall-down* mechanism, in which all the messages in the network are immediately delivered to a nearby processor.

This context-switching decision also solves a problem with user-level messages. To provide high-performance protected network access to the user, the processor-network interface includes address-translation hardware, which allows user-mode code to be given direct access to the interface. Thus messages can be directly sent from user-code in one processor to user-code in another, without giving the user access to any other process. No operating-system call is required. Since the user has direct access to the network, the user also must take care not to deadlock the network. It does not hurt the operating system if the user deadlocks the network, since the operating system empties the network on every context-switch. Deadlocking the network has the same effect on the user as if the user had written an infinite loop.<sup>13</sup>

#### How to Get Good Performance from the CM-5 Data Network

Compiling data-parallel programs for the CM-5 introduces many opportunities for optimizing the performance of the code. Optimizing the code sometimes turns out to be tricky, however. Steve Heller of Thinking Machines Corporation had noticed that a sequence of cyclic shifts separated by barriers actually runs faster than if the barriers are removed [Hel92]. I had expected such a communications operation to run faster without the barriers, since up to that point I generally thought of barriers as overhead that should be removed if possible. Thus, Heller's observation was surprising. A study was embarked on, at MIT, to to understand how best to program the data network of a machine such as the CM-5.<sup>14</sup>

We concluded that programmers of the Connection Machine CM-5 data network can improve the performance of their data movement code more than a factor of three by selectively using global barriers, by limiting the rate at which messages are injected into the network, and by managing the order in which they are injected. Barriers eliminate target-processor congestion, and provide a kind of bulk end-to-end flow control that allows the programmer to schedule communications globally. Injection-reordering improves the statistical independence of the various packets in the network at any given time. Barriers and tuned injection rates provide forms of flow control. Although we only experimented with the CM-5, we expect these techniques to apply to other parallel machines.

Why do barriers speed up a sequence of cyclic shifts? We demonstrated that, without any barriers, some processors fall behind the others. The work from later phases of the computation systematically interferes with uncompleted work from earlier phases. We are able to see what was going on because the CM-5 processors have access to a clock that is globally consistent to within a single 33 megahertz clock cycle. We recorded, for each message, the time it is injected into the network and the time it is delivered. For cyclic shift, the receivers are the bandwidth bottleneck, so it is important to keep all the receivers busy. We saw with our timestamping experiment, however, for hundreds of thousands of cycles at a stretch, that some receivers had no messages waiting to be delivered, and some receivers had over ten messages waiting to be delivered. The imbalance among receivers systematically gets worse over time. By periodically synchronizing all the processors,

<sup>&</sup>lt;sup>13</sup>The CM-5 makes it easy, however, to implement protocols such as remote-fetch without deadlocking and without incurring a large bookkeeping overhead. The CM-5 accomplishes this by providing two independent networks that comprise the data network.

<sup>&</sup>lt;sup>14</sup>Eric A. Brewer and I performed the performance study. Brewer, with R. Blumofe, was developing a CM-5 communications library called Strata [BB94b]. Strata's goal is to improve the programming interface and performance of message passing as compared to Thinking Machines' CMMD [Thi93] and Berkeley's CMAM [vCG\*92].

the imbalance among receivers is removed, allowing the machine to operate at peak performance. Barriers improve the performance of a sequence of cyclic shifts by a factor of 2 to 3. Thus, not only is global synchronization useful for writing *correct* programs, but it can also help us to improve and to understand the performance of a program.

We knew that the order in which messages are injected could affect the performance of the data network. For example, a bad way to implement all-to-all communication is for every processor to send a block of messages to Processor 0, then to have every processor send a block to Processor 1, and then to Processor 2, and so on. That order dramatically reduces the performance of the program, because there are always only a few processors receiving the data that all the processors are trying to send. We had hypothesized that if on step i, processor j sent a block of messages to processor  $i + j \mod P$ , then we would achieve near-optimal performance. We found instead that if the messages that form the blocks are sent in an interleaved or random order, that the performance was better, sometimes by more than a factor of two as compared to the unsynchronized, uninterleaved, cyclic-shifts that had seemed so reasonable. For a synchronized sequence of cyclic shifts, interleaving only adds overhead without improving performance, but for message patterns about which less is known, it may often pay to interleave the order in which messages are sent.

We also found that by artificially slowing down the rate at which messages are injected into the network to exactly match the rate at which messages can be removed from the network, that we were able to achieve an additional 25% performance improvement because the network remains busy, but uncongested.

In summary, global synchronization is not only useful for correct execution of programs, it also helps improve the performance. A programmer must be careful about removing barriers because of the performance implications. Also, global synchronization in the form of a globally consistent clock makes it possible to study the performance of the system.

#### **Massively Parallel Chess**

Having designed the CM-5 to support data-parallel programming, I wanted to explore how to exploit the MIMD characteristics of the machine fully. I looked for an application that did not fit well into the data-parallel approach, and hit upon computer chess. Surprisingly, global synchronization solves problems of dynamic MIMD-style programming in addition to problems of data-parallel programming.

Computer chess provides a good testbed for understanding dynamic MIMD-style computations. The parallelism of the application derives from a dynamic expansion of a highly irregular game-tree. Thus computer chess is difficult to express as a data-parallel program. The trees being searched are orders of magnitude too large to fit into the memory of our machines, and yet serial programs can run game-tree searches depth-first with very little memory, since the search tree is at most 20 to 30 ply deep. Computer chess requires interesting global and local data structures. Computer chess is demanding enough to present engineering challenges to be solved and to provide for some interesting results, yet it is not so difficult that one cannot hope to make any progress at all. Since there is an absolute measure of performance ('How well does the program play chess?'), there is no percentage in cheating, e.g., by reporting parallel speedups as compared to a really bad serial algorithm. In addition to those technical advantages, computer chess is also fun.

To investigate the programming issues, I engineered a parallel chess program, StarTech. StarTech is based on H. Berliner's serial Hitech program [BE89] and runs on a Connection Machine CM-5 supercomputer. The program, running on the 512-node CM-5 at the National Center for

Supercomputing Applications at University of Illinois, tied for third place at the 1993 ACM International Computer Chess Championship, and has an informally estimated rating of 2450 USCF.<sup>15</sup>

The StarTech chess program is conceptually divided into two parts: The parallel game tree algorithm, which specifies *what* can be done in parallel; and the scheduler, which specifies *when* and *where* the work will actually be performed.

I found that chess places great demands on a scheduler. I found, by measuring the ideal parallelism histogram, that sometimes there is plenty of parallel work to do, and sometimes there is very little. I typically saw average available parallelism of at least several hundred, but for about a quarter of the run-time on an infinite processor machine, the available parallelism was less than 4. It is crucial that the scheduler do a good job when there is very little to do, so that the program can get back to the highly parallel parts.

To distribute work among CM-5 processors, StarTech uses a work-stealing approach, in which idle processors request work. I noticed that sometimes during a run, when the available parallelism is low, the idle processors swamp the busy processors with requests for work. This is a serious problem, since it can arbitrarily stretch out the time it takes to execute the portions of the program that have low parallelism. The swamping problem has been previously reported for work-stealing schedulers [FM87, FM93]. I provide a queueing theory explanation of how the swamping problem arises and offer a *global-throttle* mechanism to avoid the swamping problem. The global throttle organizes the computation into a series of globally synchronous phases separated by split-phase barriers. During each phase, each idle processor is allowed to make only one request to steal work. Thus the expected number of incoming requests to a busy processor scontinue to do useful work regardless of how long it takes for the global throttle to complete each phase.<sup>16</sup> Thus, the CM-5's global synchronization network is useful for dynamic MIMD programs too.

Given my scheduler, I found that two numbers, the critical path length and the total parallel work, can be used to predict the performance of StarTech. The critical path length C is the time it would take for the program to run on an infinite processor machine with no scheduling overheads. It is a lower bound to the runtime of the program. The total work W is the number of processor cycles spent doing useful work. W does not include cycles spent idle when there is not enough work to keep all the processors busy. On P processors, I define W/P to be the *linear speedup term*. The linear speedup term is also a lower bound to the runtime on P processors. Another way to think about it is to consider the program to be a dataflow graph. The critical path length is the depth of the graph, and the total work is the size of the graph. The values for C and W can be derived analytically or measured empirically. I measure the effectiveness of our scheduler by comparing it to these lower bounds. I found that the run-time on P processors of our chess program is accurately modeled as

$$T_P \approx 1.02 \frac{W}{P} + 1.5C + 4.3 \text{ seconds.}$$

(1.1)

Except for the constant term of 4.3 seconds, this is within a factor of 2.52 of the lower bound given by the maximum of C and W/P.<sup>17</sup>

<sup>&</sup>lt;sup>15</sup>The StarTech team has included, at various times, Hans Berliner, Mark Bromley, Roger Frye, Charles E. Leiserson, Chris McConnell, Ryan Rifkin, James Schuyler, Kurt Thearling, Richard Title, and David Waltz.

<sup>&</sup>lt;sup>16</sup>Another way to solve the swamping problem is to provide separate hardware to deal with incoming requests. Such an approach could be used on the Alewife processor [ACD\*91], for example. I could not add special hardware to the machine, so I had to find a software solution. Alternatively, one can use a backoff backoff strategy, such as is found in Ethernet [MB76], DIB [FM87], and PCM [HZJ94, Hal94]. The global throttle requires less tuning than does adaptive backoff, and is easy to analyze.

<sup>&</sup>lt;sup>17</sup>For comparison, Brent's theorem [Bre74, Lemma 2] states that with no scheduling overhead, the runtime can be

The StarTech program uses *Jamboree* search, a parallelization of Scout search, in which at every node of the search tree, the program searches the first child to determine its value, and then tries to prove, in parallel, that all of the other children of the node are worse alternatives than the first child. This approach to parallelizing game tree search is quite natural and has been used by several other parallel chess programs [HSN89, FMM91]. While no other parallel game program uses an algorithm that is identical to StarTech's Jamboree search, I do not claim that the search algorithm is a new contribution. Instead, I view the algorithm as a testbed for testing mechanisms needed for the design of scalable, predictable, asynchronous parallel programs.

I analyzed the computational complexity of the Jamboree search algorithm, using critical path length and total work. For two special cases, best-ordered uniform trees and worst-ordered uniform trees, I used analytic methods. For best-ordered trees the critical path length is short and the amount of work performed is the same as for a good serial game-tree search. For worst-ordered trees the critical path is long, so that even on an infinite number of processors the Jamboree search achieves no speedup compared with a good serial implementation. For real chess trees I measured the critical path length and work of the program as it actually ran. I found that the quality of the move-ordering heuristics strongly affects the critical path length and the total work. I found that for tournament time controls on large machines searching real chess trees, the critical path is important but that it does not dominate the runtime. For small machines the critical path is not an issue at all.

A naive application of Jamboree search achieves work efficiencies of between 33% and 50%. The work efficiency of a parallel program on a problem is the ratio of the time for one processor to solve the problem, using the best serial code, to the total work generated by the parallel program. I found three strategies to improve the performance of StarTech, two of which exploit StarTech's global transposition table. StarTech uses a global transposition table, which memoizes results from earlier searches in order to improve move ordering for, and hence the efficiency of, later searches.<sup>18</sup> The first strategy for improving performance is to perform recursive iterative deepening.<sup>19</sup> When searching a chess position to depth k, the first thing StarTech does is to lookup the position in the global transposition table to determine if anything from a previous search has been saved. If a move for a search of depth k-1 or deeper is found, then StarTech uses that move as its guess for the first child. If no such move is found, then StarTech recursively searches the position to depth k-1 in order to find the move. By so doing, StarTech greatly improves the probability that the best move is searched first. The second strategy for improving performance is to perform *deferred-reads* on the transposition table in order to prevent more than one position from searching the same position redundantly. When a processing node starts searching a chess position, StarTech records in the global transposition table that the position is being searched. If another processor starts searching the same position, the processor waits until the first processor finishes. It is much better for the second processor to sit idle than to work on the tree, since this prevents the second processor from generating work which may then be stolen by other processors, causing an explosion of redundant work. The third strategy is to serialize Jamboree search slightly. Instead of searching one child serially and then the rest in parallel, as basic Jamboree search does, our variation sometimes searches two children serially. The precise conditions for searching two children serially are that the node be

brought down to no more than C + W/P. The StarTech scheduler guarantees that the memory required per processor within not much more than the memory required by the serial depth-first search. R. Blumofe and C. Leiserson studied several scheduling strategies to simultaneously achieve good time and space bounds. Some of the scheduling tradeoffs made in StarTech were strongly influenced by discussions with Blumofe and Leiserson. (See Section 5.8.)

<sup>&</sup>lt;sup>18</sup>Most other programs use additional move-ordering mechanisms such as the killer table [GEC67] and the history table [MOS86]. StarTech does not currently use these additional move-ordering heuristics.

<sup>&</sup>lt;sup>19</sup>Recursive iterative deepening was used in T. Truscott's unpublished checkers program in the early 1980's [Tru92], and was briefly explored for the Hitech program by H. Berliner and his students in the late 1980's [Ber93].

of Knuth-Moore type-2 [KM75], that recursive iterative search of the node had a value greater than the  $\alpha$  parameter of the subtree, and that the search of the first child yielded a score that is less than or equal to the  $\alpha$  parameter. This serialization improves the work efficiency of StarTech without substantially increasing the critical path length.<sup>20</sup>

By separating the search algorithm and the scheduler, the problems of each could be solved separately. By exploiting fast global synchronization, the problems of scheduling dynamic MIMD-style computations were simplified. I neither needed to perform arcane tuning of the scheduler nor did I need to worry about pathological search trees. Thus, I was able to focus my attention on the application, analyzing and improving the performance of the underlying search algorithm. Without the mechanisms provided by the CM-5, including global synchronization, and fast user-level messages, it would have been much more difficult to implement a competitive chess program such as StarTech.

#### Contributions

Global synchronization mechanisms include barriers, split-phase barriers, router-done barriers, gang scheduling, and synchronous instruction broadcast, and globally consistent clocks. What do all these have in common? Global synchronization asserts that something is true of every processor p. For example it might assert that "every processor has finished the kth step of algorithm", or "at this moment, the local clock at every processor says that the time is t".

Global synchronization provides powerful enough invariants to provide simple solutions to system problems ranging from clock distribution, diagnostics, timesharing, and spacesharing, to the correct execution of data-parallel programs, high-performance execution of dynamic MIMD-style programs, and fast bulk data transfers.

My contributions include

- Fast global synchronization is a simple, effective, efficient, solution to many system of parallel computing.

- The network architecture of the Connection Machine CM-5, a synchronized MIMD computer. The CM-5 provides three networks: a control network, a data network, and a diagnostic network. The system includes user-level network access, split-phase barriers, a router-done primitive implemented with "Kirchhoff counting", a split data network to allow commonly used protocols to be implemented without deadlock or bookkeeping, an "all-fall-down" mechanism that quickly empties the routing network for timesharing, and a parallel diagnostics strategy. The system efficiently supports data-parallel programming and dynamic MIMDstyle programming.

- Three strategies for obtaining good performance from a data network: periodic barriers, injection reordering, and bandwidth matching.

- StarTech, a competitive parallel chess program that runs on the CM-5. StarTech employs a work-stealing scheduler, which uses the CM-5 control network to throttle processors that are looking for work. The StarTech scheduler achieves good performance relative to optimal scheduling. StarTech uses Jamboree search, a parallel game tree search algorithm. I analyze the performance of Jamboree search on special case game trees, and measure the performance

<sup>&</sup>lt;sup>20</sup>Charles E. Leiserson and I together designed the serialization heuristic for Jamboree search.

on real chess trees. I systematically employ the critical path length and total work to understand the performance of StarTech, which is a dynamic MIMD-style program. I demonstrate a heuristic that improves the work efficiency of the Jamboree algorithm on real chess trees. StarTech uses a global transposition table, the performance of which is improved by using recursive iterative deepening and deferred lookups. StarTech uses several active message protocols that may be useful in a wider context to avoid dangling references and reduce message traffic for atomic access to global data-structures.

#### A Road Map

This dissertation is organized into three, mostly independent, parts.

- The first part (Chapter 2) describes the network architecture of the CM-5.

- The second part (Chapter 3) describes how to get good performance from the CM-5 data network, especially for the kinds of message traffic that show up in data-parallel programs.

- The third part (Chapters 4–6) describes the StarTech massively parallel chess program.

While the three parts of the thesis together provide evidence that fast global synchronization is useful for MIMD computation, the ideas described in each part stand alone, and the parts can be read independently. Many of the mechanisms of Part I can be employed to solve system-level problems in other kinds of parallel machines. Such problems include deadlock avoidance, timesharing, and detecting the termination of a computation. The mechanisms of Part II can be used to improve the performance of data transfers on almost any machine, although machines without fast global synchronization are at a disadvantage compared to synchronized MIMD machines. The results of Part III include an algorithm, with analysis, for parallel game tree search, and mechanisms for scheduling work on parallel machines.

Chapter by chapter, this dissertation is organized as follows:

- Chapter 2 describes the CM-5, a specific instance of the synchronized MIMD architecture. Beginning with an explanation of how data-parallel code can be compiled for and executed on a synchronized MIMD machine, the chapter proceeds to explain the network architecture of the CM-5. The CM-5 includes three networks, a data network, a control network, and a diagnostics network. The CM-5 includes mechanisms to support time-sharing, and spacesharing; to detect the completion of computations that use the data network; and to help the user program the data network without deadlocking. The diagnostics network can quickly test a large CM-5 in parallel.

- Chapter 3 continues the study of the CM-5 by examining how to get good performance from the CM-5 data network. The chapter starts with an explanation of the problem, that removing barriers can sometimes slow down a computation, and reviews some of the issues that arise when measuring performance on the CM-5. The chapter then shows how and why programmers can improve the performance of their data movement code by more than a factor of three by selectively using global barriers; by limiting the rate at which messages are injected into the network; and by managing the order in which they are injected.

- Chapter 4 begins the second part of this dissertation by explaining how the StarTech chess program works. The chapter describes the Jamboree search algorithm, starting with a review of game tree search, and explains how Jamboree search is related to the serial  $\alpha$ - $\beta$  and Scout

search algorithms. The chapter then describes the StarTech work-stealing scheduler, which employs global synchronization to help guarantee good performance. The Jamboree algorithm employs speculative expansion of the tree, and sometimes the algorithm discovers that a partially expanded subtree is no longer needed. Startech employs a simple active-message protocol that avoids dangling references to frames that are aborted in mid-computation.

- Chapter 5 studies the performance of the StarTech program, beginning with a discussion of Brent's theorem. The chapter presents a study of the Jamboree algorithm, analyzing two special cases: best-ordered uniform game trees and worst-ordered uniform game trees. Expressions are produced for the critical path length, the parallel work, and the work efficiency of Jamboree search on such trees. An empirical study of the Jamboree algorithm is presented, focusing on the critical path length and parallel work of the algorithm when search real chess trees. Having examined the Jamboree algorithm, the chapter moves on to study the StarTech scheduler, starting with a demonstration that our parallel chess program places great demands on the scheduler. The scheduler's performance is then analyzed in relation to critical path length and linear-speedup lower bounds to performance, showing that Equation 1.1 accurately models the performance of StarTech. In particular, one can measure the performance of the program on a small machine, and predict its performance on a large machine. A study of the swamping problem yields justification for the global throttling strategy of the StarTech scheduler. Using a simple experimental setup, the swamping problem is demonstrated, and an analytic queueing model is developed that provides a good match to the empirical measurements. The chapter concludes with an analysis of the space-time tradeoffs associated with fixing each position of the chess tree on a particular processor rather than allowing the work to migrate from one processor to another.

- Chapter 6 explains how I used the critical path length and parallel work measurements to improve the performance of StarTech. Chapter 6 describes our global transposition table, and explains how recursive iterative deepening and deferred-reads are implemented and what are the performance implications of those mechanisms. I analyze where the extra work is coming from that leads to StarTech's modest work inefficiency. Using that analysis, I construct a modification to the basic Jamboree search that sometimes serializes the search. That modification, when used, has effect of significantly decreasing the total parallel work while increasing the critical path length only slightly. The chapter concludes with a study of how the processor-cycles are spent by StarTech, with an eye to understanding how to improve the performance of the program in the future.

- Chapter 7 concludes by reviewing the relationship of this work to previous work, and discussing the merits of the mechanisms that I describe, both with respect to today's technology and to that of the future.

### **Chapter 2**

# The Network Architecture of the Connection Machine CM-5<sup>1</sup>

In the design of a parallel computer, the engineering principle of *economy of mechanism* suggests that the machine should employ only a single communication network to convey information among the processors in the system. Indeed, many parallel computers contain only a single network: typically, a hypercube or a mesh. The Connection Machine Model CM-5 Supercomputer has three networks, however, and none is a hypercube or a mesh. This chapter describes the architecture of each of these three networks and the rationale behind them.

The CM-5 is a *synchronized MIMD* machine, which combines the best aspects of SIMD (single instruction path, multiple data path) and MIMD (multiple instruction path, multiple data path) machines [Fly66]. Each processor in the CM-5 executes its own instructions, providing the flexibility of a typical MIMD machine. And, like many MIMD machines, the CM-5 is a distributed memory machine (as opposed to shared memory machine [DT90, GGK\*83]) in which processors communicate among themselves by sending messages [Sei85, SAD\*86] through the *data network* of the machine. A deficiency of typical MIMD machines, especially as compared with their SIMD cousins, however, is that they provide little or no support for coordinating and synchronizing sets of processors. To offset this deficiency, the CM-5 also contains a *control network*, which makes synchronization and multiparty communication primitives competitive with comparable functions on SIMD machines. These primitives include the fast broadcasting of data, barrier synchronization [Jor78, TY86, DGN\*86], and parallel prefix (scan) operations [Ble90].

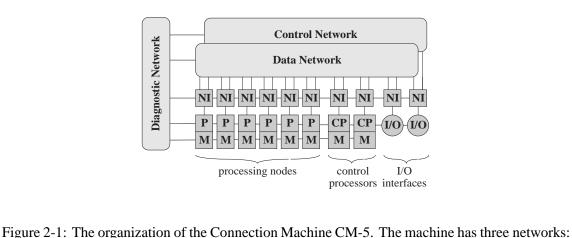

Figure 2-1 shows a diagram of the the CM-5 organization. The machine contains between 32 and 16,384 *processing nodes*, each of which contains a 32-megahertz SPARC processor, 32 megabytes of memory, and a 128-megaflops vector-processing unit capable of processing 64-bit floating-point and integer numbers. System administration tasks and serial user tasks are executed by a collection of *control processors*, which are Sun Microsystems workstation computers. There are from 1 to several tens of control processors in a CM-5, each configured with memory and disk according to the customer's preference. Input and output is provided via high-bandwidth *I/O interfaces* to graphics devices, mass secondary storage, and high-performance networks. Additional low-speed I/O is provided by Ethernet connections to the control processors. The largest machine, configured with up to 16,384 processing nodes, occupies a space of approximately 30 meters by 30 meters, and is capable of over a teraflops (10<sup>12</sup> floating-point operations per second).

<sup>&</sup>lt;sup>1</sup>The research in this chapter represents joint work with Charles E. Leiserson, Zahi S. Abuhamdeh, David C. Douglas, Carl R. Feynman, Mahesh N. Ganmukhi, Jeffrey V. Hill, W. Daniel Hillis, Margaret A. St. Pierre, David S. Wells, Monica

Figure 2-1: The organization of the Connection Machine CM-5. The machine has three networks: a data network, a control network, and a diagnostic network. The data and control networks are connected to processing nodes, control processors, and I/O channels via a network interface.

The processing nodes, control processors, and I/O interfaces are interconnected by three networks: the data network, the control network, and a diagnostic network. The data network provides high-performance point-to-point data communications between system components. The control network provides cooperative operations, including broadcast, synchronization, and *scans* (parallel prefix and suffix). It also provides system management operations, such as error reporting. The diagnostic network allows "back-door" access to all system hardware to test system integrity and to detect and isolate errors.

The system operates as one or more user *partitions*. Each partition consists of a control processor, a collection of processing nodes, and dedicated portions of the data and control networks. Access to system functions is classified as either *privileged* or *nonprivileged*. All nonprivileged system functions, including access to the data and control networks, can be executed directly by user code without system calls. Consequently, network communication within a user task occurs without operating system overhead. Access to the diagnostics network, to shared system calls. Protection and addressing mechanisms ensure that no user can interfere with the function or performance of another user in another partition. If the system administrator so desires, a single partition can be timeshared among a group of users, where each user gets a fair portion of the available time and cannot otherwise be interfered with by any other user.

This chapter describes the CM-5 synchronized MIMD hardware and how to use it to run data parallel programs. The rest of this chapter then focuses on the details of the network architecture of the CM-5, and is organized as follows. Section 2.1 describes the network interface which provides the user's view of the data and control networks. Section 2.2 then describes the data network, Section 2.3 describes the control network, and the diagnostic network is described in Section 2.4. Section 2.5 discusses how global synchronization helped solve many system problems in the CM-5. The chapter closes with Section 2.6, which gives a short history of our development project.

Further details about the CM-5 system can be found in the CM-5 Technical Summary [TMC91]. The reader should be aware that the performance specifications quoted in this chapter apply only to the initial release of the CM-5 system. Because of our ability to reengineer pieces of the system easily, these numbers represent only a snapshot of an evolving implementation of the architecture.

C. Wong, Shaw-Wen Yang, and Robert Zak. Much of the work in this chapter was originally reported in [LAD\*92].

The machine has recently been revised to include faster processors and data networks.

#### 2.1 The CM-5 Network Interface

Early on in the design process, we, the CM-5 development team at Thinking Machines Corporation, decided to specify an interface between the processing nodes and the networks that isolates each from the details of the other. This interface provides three features. First, the interface gives the processors a simple and uniform view of the networks (and the networks get a simple and uniform view of the processors). Second, the interface provides support for time-sharing, space-sharing, and mapping out of failed components. Third, the interface provides a contract for the implementors which decouples the design decisions made for the networks from those of the processors.

The processor's view of the interface is as a collection of memory-mapped registers. By writing to or reading from fixed physical memory addresses, data is transferred to or from the networks, and the interface interprets the particular address as a command.

A memory mapped interface allows us to use many of the memory-oriented mechanisms found in off-the-shelf processors to deal with network interface issues. To access the network, a user or compiler reads from or writes to locations in memory. We regarded the prospect of executing a system supervisor call for every communication as unacceptable, in part because we wished to support the fine-grain communication needs of data-parallel computation. A memory-mapped interface allows the operating system to deny users access to certain network operations by placing the corresponding memory-mapped registers on protected pages of the processor's address space. The processor's memory management unit enforces protection without any additional hardware.

The interface is broadly organized as a collection of memory-mapped FIFO's. Each FIFO is either an *outgoing* FIFO to provide data to a network, or an *incoming* FIFO to retrieve data from a network. Status information can be accessed through memory-mapped registers. For example, to send a message over a network, a processor pushes the data into an outgoing FIFO by writing to a suitable memory address. When a message arrives at a processor, the event is signaled by interrupting the processor, or alternatively, the processor can poll a memory-mapped status bit. The data in the message can then be retrieved by reading from the appropriate incoming FIFO. This paradigm is identical for both the data and control networks.

The network interface provides the mechanisms needed to allow context switching of user tasks. Each user partition in the CM-5 system can run either batch jobs or a timesharing system. When a user is swapped out during timesharing, the processors must save the computation state. Some of this state information is retrieved from the network interface, and the rest is garnered from the networks. The context-switching mechanism also supports automatic checkpointing of user tasks.

The interface provides processor-address mapping so that the user sees a 0-based contiguous address space for the processor numbers within a partition. Each processor can be named by its *physical* address or by its *relative* address within the partition. A physical address is the actual network address as interpreted by the hardware inside the networks. A relative address gives the index of a processor relative to the start of a user partition, where failed processors are mapped out. All processor addresses in user code are relative addresses. To specify physical addresses requires supervisor privileges. Relative addresses are bounds checked, so that user code cannot specify addresses outside its partition.

The user's view of the networks is independent of a network's topology. Users cannot directly program the wires of the networks, as they could on our previous machine, the CM-2. The reason is simple: the wires might not be there! Because the CM-5 is designed to be resilient in the presence of faults, we cannot allow the user to rely on a specific network topology. One might

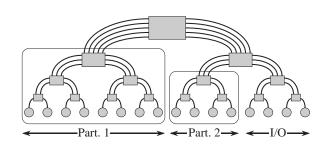

Figure 2-2: A binary fat-tree. Processors are located at the leaves, and the internal nodes are switches. Unlike an ordinary binary tree, the channel capacities of a fat-tree increase as we ascend from leaves to root. The hierarchical nature of a fat-tree can be exploited to give each user partition a dedicated subnetwork which cannot be interfered with by any other partition's message traffic. The CM-5 data network uses a 4-ary tree instead of a binary tree.

think topology independence would hurt network performance, but we found this presumption to be less true than we initially imagined. Because we did not provide the user with access to the wires of the network, we were able to apply more resources to generic network capabilities. A further advantage of topology independence is that the network technology becomes decoupled from processor technology. Any future network enhancements are independent of user code and processor organization.

An important ramification of the decoupling of the processors from the networks is that the networks must assume full responsibility for performing their functions. The data network, for example, does not rely on the processors to guarantee end-to-end delivery. The processors assume that delivery is reliable. Nondelivery implies a broken system, since there is no protocol for retransmission. By guaranteeing delivery, additional error-detection circuitry must be incorporated into the network design, which slightly reduces its performance, but since the processor does not need to deal with possible network failures, the overall performance as seen by a user is much better.

The CM-5 network interface is implemented in large measure by a single 1-micron standardcell CMOS chip, with custom macro cells to provide high-performance circuits where needed. The interface chip is clocked by both the 32-megahertz processor clock and the 40-megahertz networks clock. Asynchronous arbiters synchronize the processor side of the interface with the network side.