# MLSI-DB11-R AND MLSI-DB11-RA Q-BUS REPEATER ASSEMBLIES

For use with DEC<sup>TM</sup> LSI-11<sup>TM</sup> Computers

INSTRUCTION MANUAL

## MLSI-DB11-R AND MLSI-DB11-RA **Q-BUS REPEATER ASSEMBLIES**

For use with DEC<sup>TM</sup> LSI-11<sup>TM</sup> Computers

**INSTRUCTION MANUAL**

1995 North Batavia Street Box 5508 Orange, CA 92267-0508 (714) 998-6900 SYSTEMS INC. TWX 910-593-1339

#### Document Part Number: 80034032 Document Revision Level: A

#### Copyright © 1983 by MDB Systems, Inc. All rights reserved. Printed in U.S.A.

This document, and all subject matter disclosed herein, are proprietary items of which MDB Systems, Inc. retains the exclusive rights of reproduction, manufacture, and sale. Permission for further disclosure must be granted in writing by MDB Systems, Inc. The information supplied in this document is subject to change without notice.

The postage-prepaid READER'S COMMENTS page at the end of this instruction manual requests the user's critical evaluation to assist us in preparing future documentation.

DEC and LSI-11 are registered trademarks of Digital Equipment Corporation.

Price: \$10.00

1

### TABLE OF CONTENTS

Page

| Α. | Scope of Manual 1                           |

|----|---------------------------------------------|

| Β. | Product Description1                        |

| c. | Physical Description/Specification Summary2 |

|    | <ol> <li>Mechanical</li></ol>               |

| D. | Installation                                |

| E. | General Operation                           |

| F. | Repeated Q-bus Signals                      |

| G. | Repair                                      |

#### LIST OF ILLUSTRATIONS

| Figure |                  |                                          | Page |

|--------|------------------|------------------------------------------|------|

| 1      | System Block Die | agram                                    | 2    |

| 2      | Block Diagram:   | Bus Repeater Assembly, General Operation | 5    |

| 3      | Block Diagram:   | DMA Bus Master on Repeated Bus           | 6    |

#### LIST OF TABLES

# Table Page 1 Functional Description of Q-bus Signals 8

#### Scope of Manual

This technical manual provides instruction and information for installing and utilizing the MDB Systems' MLSI-DB11-R and MLSI-DB11-RA Q-bus Repeater Assemblies. These Bus Repeater Assemblies are to be used with Digital Equipment Corporation (DEC) LSI-11 Q-bus computers.

Since the MLSI-DB11-R and MLSI-DB11-RA differ only in the length of their interconnection cables and installation, and have identical operating characteristics, the general term "Bus Repeater" will be used throughout this instruction manual to represent both bus repeater assemblies. Specific differences between the MLSI-DB11-R and MLSI-DB11-RA will be indicated where appropriate.

#### Product Description

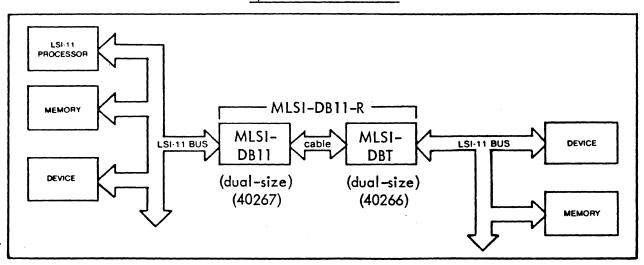

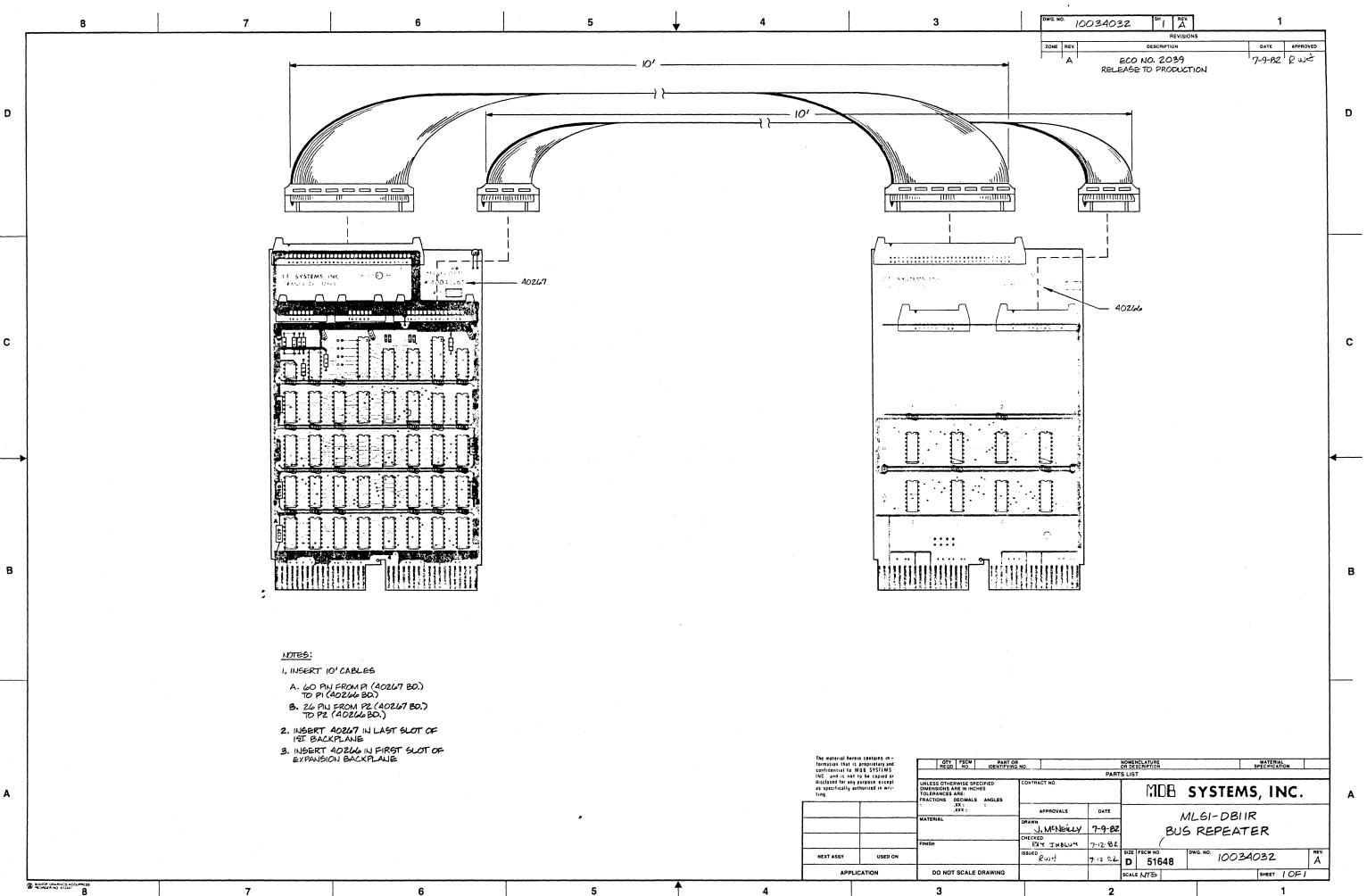

The Bus Repeater Assembly consists of two dual-size modules (MLSI-DB11 and MLSI-DBT) and two 10-foot (3.05m) flat ribbon interconnection cables. When the MLSI-DB11-RA is used, the interconnection cables are only 1-foot (30.48 cm) long.

When installed (MLSI-DB11 in main Q-bus and MLSI-DBT in expansion bus), the Repeater receives and re-drives (rejuvinates) all Q-bus signals. Therefore, the Bus Repeater allows the Q-bus to be extended beyond twenty (20) DC bus loads.

The Bus Repeater appears to the primary CPU segment of the Q-bus as one DC bus load, and drives a new bus segment (expansion bus) capable of handling an additional set of DC bus loads, essentially doubling the total number of module loads that one processor can accommodate. The Repeater is counted as one DC load on each Q-bus segment, and drives an additional nineteen (19) loads on the repeated bus. (The system may then accommodate 40 total DC loads, including the Bus Repeater modules.)

The Bus Repeater is completely compatible with the DEC LSI-11 family and repeats the appropriate Q-bus signals to support 22-bit addressing, 4-level priority interrupt, DMA transfers, and parity, as well as all other Q-bus signals. (Refer to Table 1 for a complete listing of Q-bus signals.)

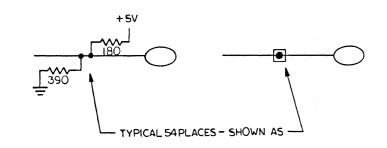

The Bus Repeater also provides complete 120 ohm termination in the primary CPU Q-bus, and matching 120 ohm impedance for the beginning of the repeated bus in the expansion backplane. Termination for the repeated bus must be accomplished by means of an appropriate terminator module (i.e., MLSI-TEV-003, or equivalent).

Figure 1 on the following page is a block diagram showing the position of the Bus Repeater in a typical repeated bus system.

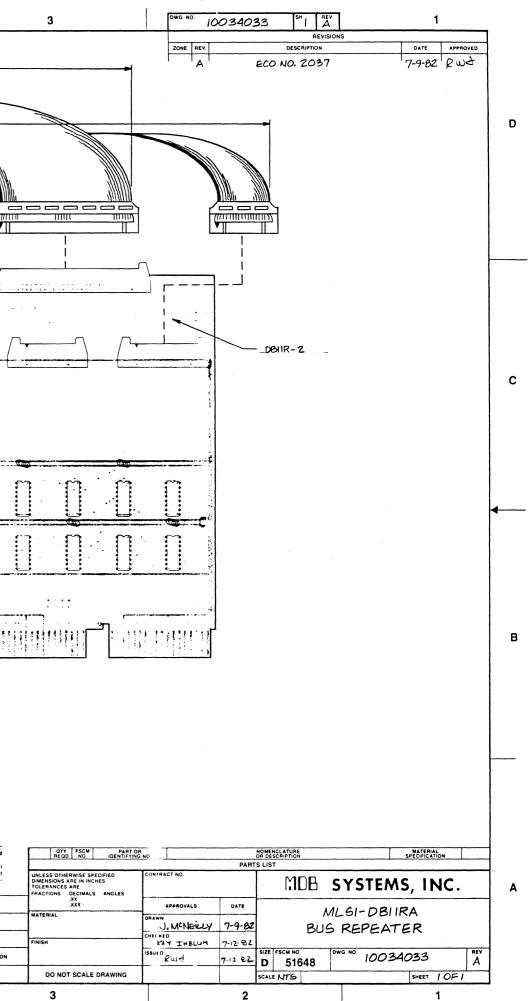

Figure 1 System Block Diagram

#### Physical Description/Specification Summary

This section provides a brief description of the mechanical and electrical specifications of the MDB Bus Repeater Assembly.

1. Mechanical

Ь.

a. Logic Modules:

Interconnection Cables:

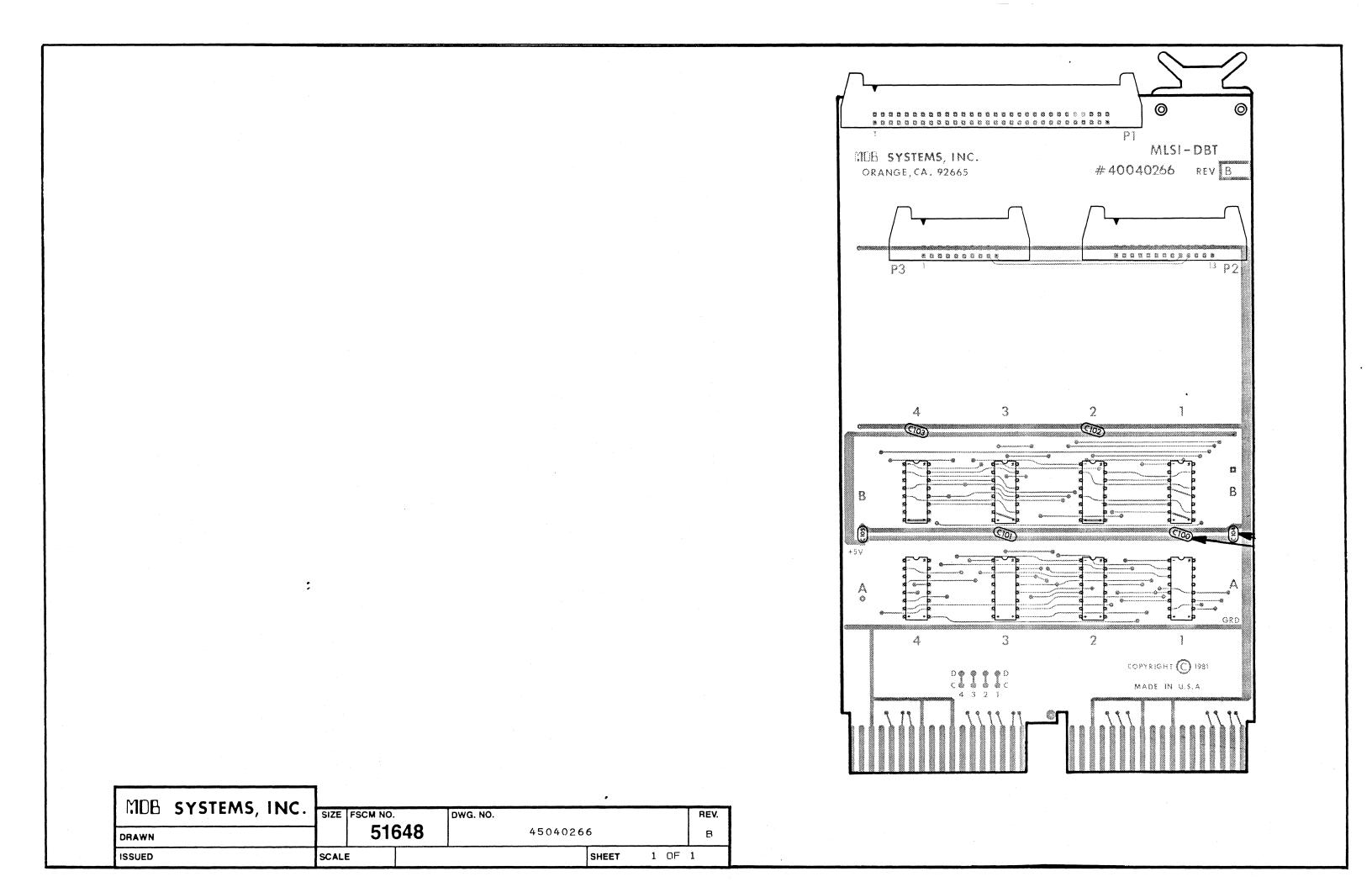

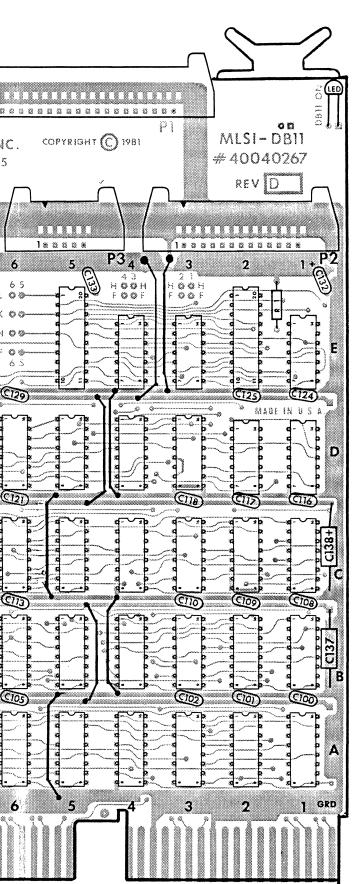

One (1) dual-size MLSI-DB11 module (p/n 45040267).

One (1) dual-size MLSI-DBT module (p/n 45040266).

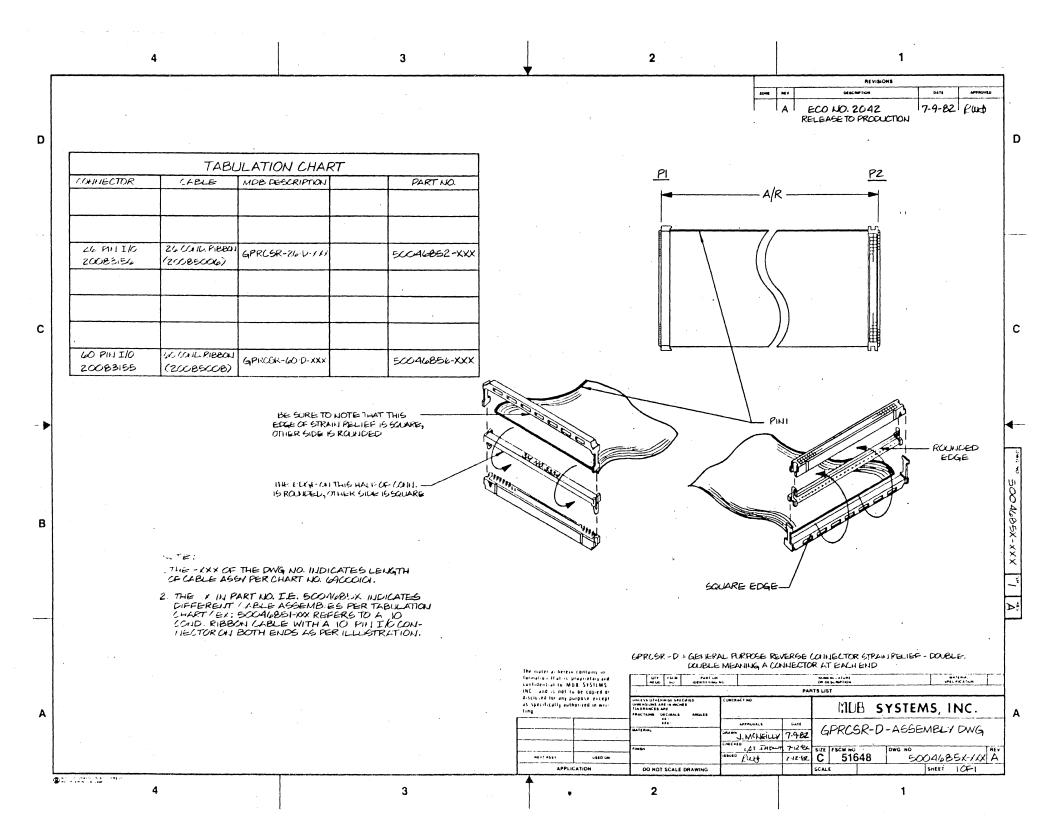

One (1) 10-foot (3.05m), 60-pin, flat ribbon cable (GPRCSR-60-D, p/n 500-46856-XXX).

One (1) 10-foot, 26-pin, flat ribbon cable (GPRCSR-26-D, p/n 50046852-XXX).

- <u>Note</u>: When the MLSI-DB11-RA is used, the interconnection cables are only 1-foot (30.48 cm) long. (Model and part numbers are identical to those listed above.)

- c. LED Indicators:

One (1) red LED indicator is mounted on the edge of the MLSI-DB11 module. When lighted, indicates Repeater active.

|    | d.    | Jumpers:           | Jumper plugs are factory-installed on the MLSI-DB11<br>module, as follows:                                                                                                                                           |

|----|-------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |       |                    | 1 F-H and 2 F-H (location 3E).<br>3 F-H and 4 F-H (location 4E).                                                                                                                                                     |

|    |       |                    | No jumper modifications are necessary for operation.                                                                                                                                                                 |

| 2. | Elect | rical              |                                                                                                                                                                                                                      |

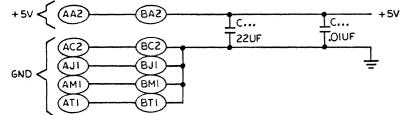

|    | a.    | Power Required:    | +5V DC at 3.0 amperes, maximum, from the backplane.                                                                                                                                                                  |

|    | Ь.    | Bus Loading:       | The MLSI-DB11 module places one DC bus load on the primary CPU Q-bus, and the MLSI-DBT module places one DC load on the repeated segment of the Q-bus.                                                               |

|    |       |                    | The Repeater drives an additional nineteen (19) DC<br>loads on the repeated bus for system expansion.                                                                                                                |

|    | c.    | Cable Loading:     | The CPU bus segment ends where the MLSI-DB11 module<br>is installed; the repeated bus segment begins at the<br>MLSI-DB11 and appears as 10 feet of cable length.                                                     |

|    | d.    | Bus Compatibility: | LSI-11/23 bus with 22-bit addressing and 4-level inter-<br>rupt capability. If any of these signals are dedicated<br>to special wiring on an LSI-11/2, etc., they must be<br>disconnected from the MLSI-DB11 module. |

#### Installation

To install the Bus Repeater, perform the following steps:

- 1. Install the MLSI-DB11 module in the last slot of the primary CPU backplane assembly (i.e., slot 8 A-B if an MDB MLSI-BA11-600 Series Chassis is used.)

- 2. Install the MLSI-DBT module in the first slot of the expansion backplane assembly (i.e., slot 1 A-B if an MDB MLSI-BA11-700 Series Expansion Chassis is used).

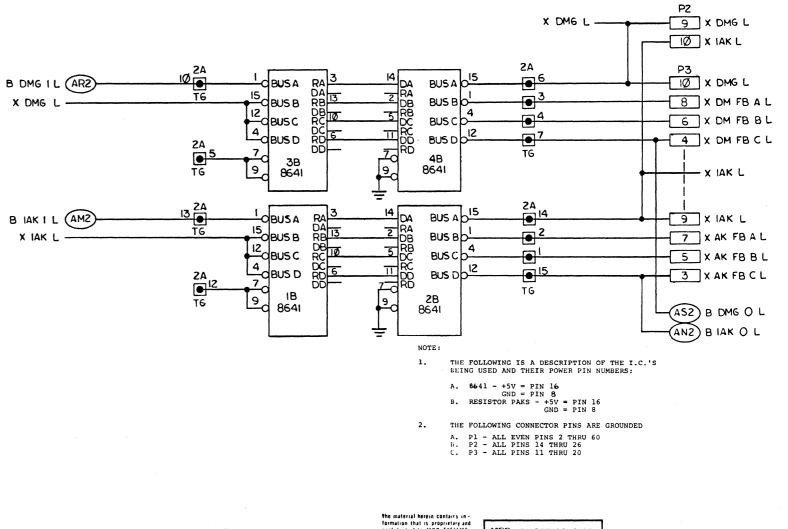

- 3. Connect the 10-foot, 60-pin, flat ribbon interconnection cable between connector P1 of the MLSI-DB11 and connector P1 of the MLSI-DBT modules.

- 4. Connect the 10-foot, 26-pin, flat ribbon interconnection cable between connector P2 of the MLSI-DB11 and connector P2 of the MLSI-DBT modules.

Note: The 10-foot Repeater interconnection cables must be considered part of the repeated bus length. The drivers and termination are provided on the MLSI-DB11 module, while the MLSI-DBT is primarily a cable connect module.

When using the MLSI-DB11-RA Bus Repeater Assembly, installation is slightly different than that for the MLSI-DB11-R, as explained below.

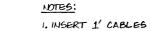

The purpose and features of the MLSI-DB11-RA are identical to those of the MLSI-DB11-R; however, whereas the MLSI-DB11-R was designed to be used to interconnect two separate backplanes, the MLSI-DB11-RA was designed specifically for use in an MDB MLSI-BA11-1000 Series Chassis Assembly.

The MLSI-BA11-1000 contains two backplanes, joined together, in a single chassis assembly. The MLSI-BA11-1000 provides sixteen (16) quad-size (32 dual) slots. Since the two backplanes contained in the chassis are connected together, a 1-foot cable is all that is needed to pass the Q-bus signals, through the MLSI-DB11-RA, from the top segment of the chassis backplane to the bottom segment. Thus, the shorter cable is supplied with the MLSI-DB11-RA. (The MLSI-DB11-RA Bus Repeater should be used in the MLSI-BA11-1000 if the total number of DC loads in the system exceeds twenty (20) loads.)

To install the MLSI-DB11-RA Bus Repeater Assembly, perform the following steps:

- 1. Install the MLSI-DB11 module in slot 8 A-B of the MLSI-BA11-1000 chassis backplane assembly.

- 2. Install the MLSI-DBT module in slot 9 A-B of the MLSI-BA11-1000 chassis backplane assembly.

- Connect the 1-foot, 60-pin, cable between connector P1 of the MLSI-DB11 and connector P1 of the MLSI-DBT modules.

- 4. Connect the 1-foot, 26-pin, cable between connector P2 of the MLSI-DB11 and connector P2 of the MLSI-DBT modules.

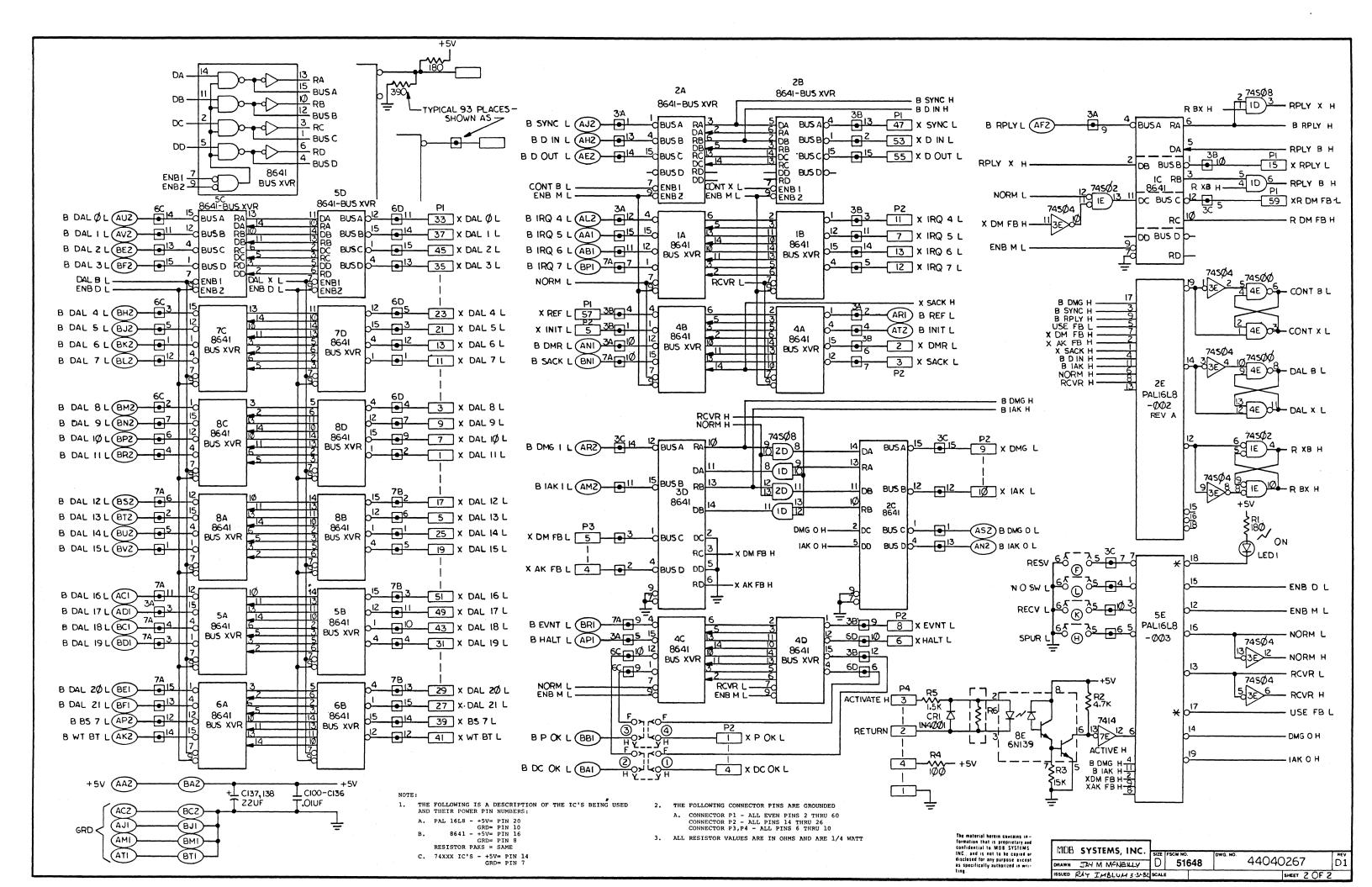

#### General Operation

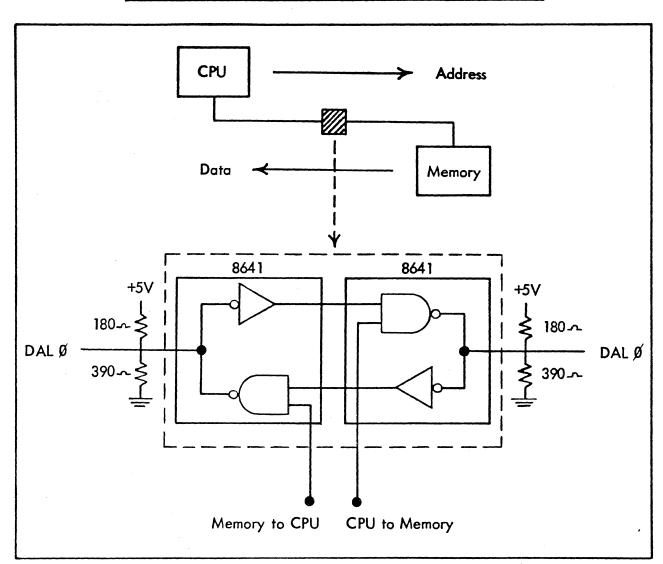

The Bus Repeater receives and re-drives all Q-bus signals. Most of the signals are bidirectional; that is, they can be driven by the LSI-11 processor and received by a device and, in turn, be re-driven by the device and received by the processor. In fact, the signal direction may change several times for each bus cycle, as shown in Figure 2 on the following page. When the processor reads data from a location in memory:

- 1. The processor drives the DAL signal lines to specify the memory address (CPU to Memory).

- 2. The memory device receives the DAL signal lines and responds to its address and the proper control signals by driving the DAL signal lines with the data contents of the addressed memory location (Memory to CPU).

- 3. The processor receives the DAL signal lines as data.

Figure 2 Block Diagram: Bus Repeater Assembly, General Operation

When the Bus Repeater is inserted into the system between the processor and memory (as shown in Figure 2 on the preceding page), it will:

- 1. Drive the DAL signal lines first in one direction (CPU to Memory), and then in the opposite direction (Memory to CPU).

- 2. Monitor bus control signals to determine what signals to drive in which direction, during which phase of each cycle.

- 3. Drive specific control signals associated with each bus cycle in the proper direction (i.e., SYNC, DIN, DOUT, RPLY, etc.).

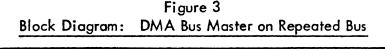

In addition to memory read cycles, the Q-bus also performs memory write cycles, read-modify-write cycles, interrupt cycles, DMA bus mastership arbitration cycles, and DMA transfer cycles. Each of these cycles has its own unique set of requirements to enable signal flow. For example, when a DMA device is bus master on the repeated bus, the direction of data flow is opposite that of the cycle shown in Figure 2. The illustration below is a block diagram of data flow when a DMA device on the repeated segment of the bus holds bus master status.

The Bus Repeater switches signal flow direction for various signals at precise phase times during cycles to ensure proper timing relationships between Q-bus signals. This is accomplished by an array of logic elements in the Repeater which monitors bus control signals and issues gating commands to several independent receiver and driver structures (see Figure 2).

In this way, the address, data, bus control, interrupt, and DMA control signals are handled so that the CPU is "unaware" that any device has been placed between the CPU and other devices or memory in the system. In other words, the Bus Repeater is transparent to the hardware and the system software.

Note: Since the Repeater is software transparent, it is non-programmable. Proper initial operation may be verified by running a diagnostic on memory or an I/O device on the main CPU Q-bus, and then moving the same device to the repeated bus and repeating the diagnostic.

#### Repeated Q-bus Signals

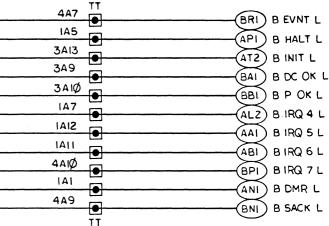

Table 1 on the following pages lists and defines all Q-bus signals that are repeated by the Bus Repeater Assembly, and provides pin assignments at the backplane for each bus signal.

# Table 1Functional Description of Q-bus Signals

Note: An asterisk (\*) denotes a Q-bus pin that is not used on this module assembly.

| Bus Pin    | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                     |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AA1 (CA1)  | BIRQ5L   | Priority Level 5 interrupt request.                                                                                                                                                                                                                                                                                                             |

| AB1 (CB1)  | BIRQ6L   | Priority Level 6 interrupt request.                                                                                                                                                                                                                                                                                                             |

| AC1 (CC1)  | BDAL 16L | Extended address bit 16.                                                                                                                                                                                                                                                                                                                        |

| AD1 (CD1)  | BDAL17L  | Extended address bit 17.                                                                                                                                                                                                                                                                                                                        |

| *AE1 (CE1) | SSPARE   | Spare pin. Not assigned. This pin is available for user connection.                                                                                                                                                                                                                                                                             |

| *AF1 (CF1) | SRUNL    | Run light signal.                                                                                                                                                                                                                                                                                                                               |

| *AH1 (CH1) | SRUNL    | Run light signal.                                                                                                                                                                                                                                                                                                                               |

| (ILD) ILA  | GND      | Signal ground.                                                                                                                                                                                                                                                                                                                                  |

| *AK1 (CK1) | MSPAREA  | Maintenance spare. Normally connected to bus pin AL1 (CL1) on the backplane.                                                                                                                                                                                                                                                                    |

| *AL1 (CL1) | MSPAREA  | Maintenance spare. Normally connected to bus pin AK1 (CK1) on the backplane.                                                                                                                                                                                                                                                                    |

| AM1 (CM1)  | GND      | Signal ground.                                                                                                                                                                                                                                                                                                                                  |

| ANI (CNI)  | BDMRL    | Direct Memory Access (DMA) Request. Asserted<br>by a device to request control of the bus (bus<br>master). If the processor is not the bus master,<br>and it is not asserting BSYNCL, it grants bus<br>master status to the requesting device by asserting<br>BDMGOL. The requesting device responds by<br>negating BDMRL and asserting BSACKL. |

| AP1 (CP1)  | BHALTL   | Processor Halt. A device will cause the processor<br>to halt normal program execution by asserting<br>BHALTL.                                                                                                                                                                                                                                   |

| Bus Pin    | Mn <b>e</b> monic | Description                                                                                                                                                                                                                                                                                 |

|------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AR1 (CR1)  | BREFL             | Memory Refresh. When BREFL is asserted, the<br>processor will perform as memory refresh that<br>forces all dynamic memory devices to be activated<br>for each BSYNCL/BDINL bus transaction.                                                                                                 |

| *AS1 (CS1) | +12B              | +12V battery power.                                                                                                                                                                                                                                                                         |

| AT1 (CT1)  | GND               | Signal ground.                                                                                                                                                                                                                                                                              |

| *AU1 (CU1) | PSPARE            | Power Spare. Not assigned. This pin is not recommended for use.                                                                                                                                                                                                                             |

| *AV1 (CV1) | +5B               | +5V battery power.                                                                                                                                                                                                                                                                          |

| AA2 (CA2)  | +5V               | +5V DC power.                                                                                                                                                                                                                                                                               |

| *AB2 (CB2) | -12V              | -12V DC power.                                                                                                                                                                                                                                                                              |

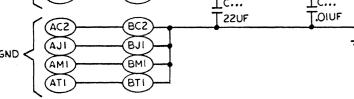

| AC2 (CC2)  | GND               | Signal ground.                                                                                                                                                                                                                                                                              |

| *AD2 (CD2) | +12V              | +12V DC power.                                                                                                                                                                                                                                                                              |

| AE2 (CE2)  | BDOUTL            | Data Output. Implies that valid data is available<br>on lines BDALOL through BDAL15L and, with<br>reference to the bus master device, that an output<br>transfer is in process. The slave device that<br>responds to the BDOUTL signal must assert BRPLYL<br>to complete the data transfer. |

| AF2 (CF2)  | BRPLYL            | Reply. Asserted in response to BDINL or BDOUTL.<br>The signal indicates that input data is available on<br>the BDAL bus, or that output data has been<br>accepted from the bus.                                                                                                             |

| AH2 (CH2)  | BDINL             | Data Input. When BSYNCL is asserted, BDINL<br>indicates an input transfer from the active bus<br>master. When BSYNCL is not asserted, it implies<br>that an interrupt operation is in process.                                                                                              |

| AJ2 (CJ2)  | BSYNCL            | Synchronize. Asserted by the bus master device<br>when it has placed an address on lines BDALOL<br>through BDAL21L.                                                                                                                                                                         |

Table 1Functional Description of Q-bus Signals

Table 1Functional Description of Q-bus Signals

| Bus Pin   | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AK2 (CK2) | BWTBTL   | Write/Byte. Controls the bus cycle in either of<br>two ways, as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           |          | <ol> <li>Asserted with leading edge of BSYNCL<br/>to indicate that an output sequence<br/>will follow (DATO or DATOB).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           |          | 2. Asserted, while BDOUTL is asserted,<br>for byte addressing in a DATOB cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AL2 (CL2) | BIRQ4L   | Priority Level 4 interrupt request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AM2 (CM2) | BIAKIL   | Interrupt Acknowledge. Asserted by the processor<br>in response to BIRQL. Causes the device to put<br>an interrupt vector address on the bus.                                                                                                                                                                                                                                                                                                                                                                                                          |

| AN2 (CN2) | BIAKOL   | Interrupt Acknowledge Out. Normally asserted<br>to the device having the next-lower priority on<br>the interrupt chain, and appears at BIAKIL input<br>to that device. If the module stores an interrupt<br>request, BIAKOL is negated at the next device.                                                                                                                                                                                                                                                                                             |

| AP2 (CP2) | BBS7L    | Bank 7 Select. Indicates that the address on the<br>bus is for the upper 4K bank. When BSYNCL is<br>asserted, BBS7L will remain active until the<br>addressing of the bus cycle is completed.                                                                                                                                                                                                                                                                                                                                                          |

| AR2 (CR2) | BDMGIL   | DMA Bus Grant Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AS2 (CS2) | BDMGOL   | DMA Bus Grant Output. This processor-generated<br>signal is daisy-chained through all DMA devices<br>on the bus. When asserted, BDGMIL grants bus<br>master status to the DMA device requesting the<br>bus that has the highest priority. If a higher-<br>priority DMA device has no active bus request,<br>BDMGOL passes from that device to the BDMGIL<br>input of the next DMA device. If the higher-<br>priority device has an active bus request, that<br>device inhibits its BDMGOL output. A DMA<br>device requests the bus by asserting BDMRL. |

| AT2 (CT2) | BINITL   | Initialize. Generated by the processor during a power-up or reset operation. Clears all devices on the I/O bus.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Bus Pin     | Mnemonic | Description                                                                                                                                                                           |  |  |  |  |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AU2 (CU2)   | BDALOL   | Bit 0. One of the data/address bus lines used<br>to transfer all address and data information.<br>Bidirectional.                                                                      |  |  |  |  |

| AV2 (CV2)   | BDALIL   | Bit 1. Data/Address bit.                                                                                                                                                              |  |  |  |  |

| BA1 (DA1)   | BDCOKH   | DC Power OK. Asserted when the DC voltage<br>level is suitable for reliable system operation.                                                                                         |  |  |  |  |

| BB1 (DB1)   | врокн    | AC Power OK. Asserted when primary power is within limits assuring reliable system operation.                                                                                         |  |  |  |  |

| BC1 (DC1)   | BDAL 18L | Bit 18. One of the extended address bus lines used to transfer address information.                                                                                                   |  |  |  |  |

| BD1 (DD1)   | BDAL 19L | Extended address bit 19.                                                                                                                                                              |  |  |  |  |

| BE1 (DE1)   | BDAL20L  | Extended address bit 20.                                                                                                                                                              |  |  |  |  |

| BF1 (DF1)   | BDAL21L  | Extended address bit 21.                                                                                                                                                              |  |  |  |  |

| *BH1 (DH1)  | SSPARE   | Special spare. Not assigned. This pin is available for user connection.                                                                                                               |  |  |  |  |

| BJI (ILQ)   | GND      | Signal ground.                                                                                                                                                                        |  |  |  |  |

| * BK1 (DK1) | MSPAREB  | Maintenance spare. Normally connected to bus pin BL1 (DL1) on the backplane.                                                                                                          |  |  |  |  |

| * BL1 (DL1) | MSPAREB  | Maintenance spare. Normally connected to bus pin BK1 (DK1) on the backplane.                                                                                                          |  |  |  |  |

| BM1 (DM1)   | GND      | Signal ground.                                                                                                                                                                        |  |  |  |  |

| BN1 (DN1)   | BSACKL   | Bus Grant Acknowledge. Asserted by a DMA<br>device in response to the processor's BDMGOL<br>signal, indicating that the device is now the bus<br>master.                              |  |  |  |  |

| BP1 (DP1)   | BIRQ7L   | Priority Level 7 interrupt request.                                                                                                                                                   |  |  |  |  |

| BR1 (DR1)   | BEVNTL   | External Event Interrupt Request. Using BEVNTL,<br>Line Time Clock interrupts occur every 16–2/3<br>msec for a 60 Hz line frequency, and every 20<br>msec for a 50 Hz line frequency. |  |  |  |  |

Table 1Functional Description of Q-bus Signals

|            | Т      | able 1   |         |         |

|------------|--------|----------|---------|---------|

| Functional | Descri | ption of | F Q-bus | Signals |

| Bus Pin     | Mnemonic | Description                                                                                                      |

|-------------|----------|------------------------------------------------------------------------------------------------------------------|

| * BS1 (DS1) | +12B     | +12V battery power.                                                                                              |

| BTI (DTI)   | GND      | Signal ground.                                                                                                   |

| *BU1 (DU1)  | PSPARE   | Power spare. Not assigned. This pin is not recommended for use.                                                  |

| *BV1 (DV1)  | +5V      | +5V DC power.                                                                                                    |

| BA2 (DA2)   | +5V      | +5V DC power.                                                                                                    |

| * BB2 (DB2) | -12V     | -12V DC power.                                                                                                   |

| BC2 (DC2)   | GND      | Signal ground.                                                                                                   |

| *BD2 (DD2)  | +12V     | +12V DC power.                                                                                                   |

| BE2 (DE2)   | BDAL2L   | Bit 2. One of the data/address bus lines used<br>to transfer all address and data information.<br>Bidirectional. |

| BF2 (DF2)   | BDAL3L   | Bit 3. Data/Address bit.                                                                                         |

| BH2 (DH2)   | BDAL4L   | Bit 4. Data/Address bit.                                                                                         |

| BJ2 (DJ2)   | BDAL5L   | Bit 5. Data/Address bit.                                                                                         |

| BK2 (DK2)   | BDAL6L   | Bit 6. Data/Address bit.                                                                                         |

| BL2 (DL2)   | BDAL7L   | Bit 7. Data/Address bit.                                                                                         |

| BM2 (DM2)   | BDAL8L   | Bit 8. Data/Address bit.                                                                                         |

| BN2 (DN2)   | BDAL9L   | Bit 9. Data/Address bit.                                                                                         |

| BP2 (DP2)   | BDAL 10L | Bit 10. Data/Address bit.                                                                                        |

| BR2 (DR2)   | BDAL11L  | Bit 11. Data/Address bit.                                                                                        |

| BS2 (DS2)   | BDAL 12L | Bit 12. Data/Address bit.                                                                                        |

| BT2 (DT2)   | BDAL 13L | Bit 13. Data/Address bit.                                                                                        |

| BU2 (DU2)   | BDAL14L  | Bit 14. Data/Address bit.                                                                                        |

| BV2 (DV2)   | BDAL15L  | Bit 15. Data/Address bit.                                                                                        |

#### Repair

In the event of apparent Bus Repeater malfunction, refer to the assembly drawings and logic diagrams contained in the rear of this manual. Check to be sure that all connectors are secured and that both Repeater modules are seated tightly in their respective back-plane assemblies.

Repair the Bus Repeater using appropriate skills, techniques, and materials. If you wish MDB Systems to repair the assembly, contact the Customer Service Department and request a Return Material Authorization (RMA) number. Once return authorization is obtained, pack the Bus Repeater Assembly carefully, along with your best evaluation of trouble symptoms, and ship it, prepaid, to MDB Systems, Inc.

Ľ

DBLIR-L\_\_\_

054

6

4040267 🛥

...........

С

В

7

A. 60 PN FROM PI (DEI IR-1 BD.) TO PI (DBI IR-2 BD.)

S ...

٩

\_\_\_\_\_

. .....

$\cap$

::

ILE SYSTEMS INC

TRANCE CA 97665

.....

VII

- B. 26 PN FROM PZ (DEIIR-1 BD.) TO PZ (DBIIR-2 BD.)

- 2. INSERT DBIIR-1 IN LAST SLOT OF IST BACKPLANE

- 3. INSERT DEI IR-2 IN FIRST SLOT OF EXPANSION BACKPLANE

- 4. THIS CONFIGURATION INTENDED FOR USE IN THE BAIL-1000 CHASSIS

7171

mit

| The material herei<br>formation that is<br>confidential to M<br>INC , and is not t | proprietary and<br>DB SYSTEMS |        | QTY<br>REQD | FSCM<br>NO                                 | PART    |

|------------------------------------------------------------------------------------|-------------------------------|--------|-------------|--------------------------------------------|---------|

| disclosed for any p<br>as specifically au<br>ting                                  | urpose except                 | DIMENS | NCES ONS I  | WISE SPE<br>RE IN INCH<br>ARE:<br>DECIMALS | HES     |

|                                                                                    |                               | MATER  | AL          |                                            |         |

| NEXT ASSY                                                                          | USED ON                       | FINISH |             |                                            |         |

| APPLIC                                                                             | CATION                        | D      | O NOT       | SCALE                                      | DRAWING |

|                                                                                    |                               |        | 3           |                                            |         |

BISHOP GRAPHICS ACCUPRESS RECROPER NO A 2447

4

5

.

|   | 8                                             | 7 | 6 | 5      | 4 |                                                                                                                                                                                                     | 3                                                                                                                   | <sup>dwg. no.</sup> 44040266 <sup>sh</sup> l                             |                                                                                 |

|---|-----------------------------------------------|---|---|--------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| D |                                               |   |   |        |   |                                                                                                                                                                                                     |                                                                                                                     | A ECO NO. 1255<br>B ECO NO. 1515<br>B RELEASE TO PRODUCT<br>ECO NO. 1832 | لاسة 18-29-81<br>12-29-81                                                       |

|   |                                               |   |   |        |   |                                                                                                                                                                                                     |                                                                                                                     |                                                                          |                                                                                 |

| С |                                               |   |   |        |   |                                                                                                                                                                                                     |                                                                                                                     |                                                                          | C                                                                               |

|   |                                               |   |   | -<br>- |   |                                                                                                                                                                                                     |                                                                                                                     |                                                                          |                                                                                 |

| В |                                               |   |   |        |   |                                                                                                                                                                                                     |                                                                                                                     |                                                                          | В                                                                               |

|   |                                               |   |   |        |   | The material herein contains in-<br>formation that is progretary and<br>confeential to MOB SYSTEMS<br>INC and is not to be copied or<br>do so to be copied or<br>do specifically authorized in wri- | OTY FSCM PART OR<br>REOD NO. IDENTFYING NO.                                                                         | PARTS LIST                                                               |                                                                                 |

| Α | B RENTER SATURATESS<br>REORDER NO 212417<br>8 | 7 | 6 | ,<br>5 | 4 | NEXT ASSY USED ON                                                                                                                                                                                   | DIMENSIONS ARE IN INCHES<br>TOLERANCES ARE:<br>PRACTIONS DECIMALS ANGLES<br>Z. XXX =<br>XXX =<br>MATERIAL<br>PINISH | I'IUB                                                                    | ATER TERMINATOR BOARD<br>MLSI-DB T<br>0WG. NO. 44040266 B<br>ISHEET 1 OF 2<br>1 |

| PI            | <b>T</b> T TT             |         |                  |

|---------------|---------------------------|---------|------------------|

| X DAL ØL 33   | 3A14                      |         | (AUZ) B DAL Ø L  |

| X DAL IL 37   | 3A15                      |         | (AV2) B DAL I L  |

| X DAL 2 L 45  | 3A5                       |         | BEZ B DAL 2 L    |

| X DAL 3 L 35  | 3A3                       |         | (BF2) B DAL 3 L  |

| X DAL 4 L 23  | 3A1                       |         | (BHZ) B DAL 4 L  |

| X DAL 5L 21   | 4AZ                       |         |                  |

| X DAL 6 L 13  | 4415                      |         | BKZ) B DAL 6 L   |

| X DAL 7 L 11  | 4414                      |         | BL2 B DAL 7 L    |

| X DAL 8 L 3   | 4413                      |         | BMZ) B DAL 8 L   |

| X DAL 9 L 9   | 4412                      |         | BNZ) B DAL 9 L   |

| X DAL ØL 7    | 4411                      |         | BPZ B DAL IØL    |

|               | 4A1                       |         | BR2 B DAL IIL    |

| X DAL 12 L 17 | 446                       |         | BS2) B DAL 12L   |

| X DAL 13 L 5  | 445                       |         | (BT2) B DAL 13 L |

| X DAL 14 L 25 | 444                       |         | (BUZ) B DAL 14 L |

| X DAL 15 L 19 | 4A3                       |         | (BV2) B DAL IS L |

|               | $1 \land 1 \land \square$ |         | ACI ) B DAL IG L |

|               | IA9                       | ,       | $\succ$          |

| X DAL 17 L 49 | 3A7                       | D_U_C   | $\leq$           |

| X DAL 18 L 43 | 3A6                       | D 2 C   | (BCI) B DAL 18 L |

| X DAL 19 L 31 | 3A4                       | D 3 C   | BDI B DAL 19 L   |

| X DAL 20 L 29 | 3AZ                       | D (4) C | BEI B DAL ZOL    |

| X DAL ZI L Z7 | IA13                      |         | BFI B DAL 21 L   |

| X D OUT L 55  | 1A14                      |         | AEZ B D OUT L    |

| X RPLY L      | 3A12                      |         | (AF2) B RPLY L   |

| X REF L 57    | IA6.                      | j       | ARI B REF L      |

| x es 7 L 39   | 142                       |         | (AP2) B BS 7 L   |

| X SYNC L 47   | 143                       |         | (AJ2) B SYNC L   |

| X WT BT L 41  | 1415                      |         | AK2 B WT BT L.   |

| X D IN L 53   | IAI5                      |         | AHZ B D IN L     |

,

The material herein contains in-formation that is proprietary and confidential to MDB SYSTIMS INC , and is not to be copied or disclosed for any purpose except as specifically authorized in wri-ting

.

| proprietary and<br>ND8 SYSIEMS                         | MDB      | SYSTEMS,   | INC |      |                   |  | -                          |  |       |      |   |

|--------------------------------------------------------|----------|------------|-----|------|-------------------|--|----------------------------|--|-------|------|---|

| to be copied or<br>purpose except<br>athorized in wri- | DRAWN    |            |     | D    | FSCM NO.<br>51648 |  | <sup>DWG. NO.</sup> 440402 |  | 266   |      | B |

|                                                        | ISSUED R | w w Imlele | ~   | SCAL | E                 |  |                            |  | SHEET | 2 OF | 2 |

|   | 8                                         | 7 | 6 | 5 | 4 |                                                                                                                                                                                                                          | 3                                                                                                                                                 | <sup>dwg. no.</sup> 44040267                                                     |                                                                                                                                                                                                                                                                                                                                                                       |   |

|---|-------------------------------------------|---|---|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| D |                                           |   |   |   |   |                                                                                                                                                                                                                          |                                                                                                                                                   | C ECO<br>C RELEASE TO<br>ECO I<br>D ECO I<br>D RELEASE T                         | REVISIONS           DESCRIPTION         DATE         APPRIN           NO. 1474         12–15-81         12 L           NO. 1788         3–29-82         Rux           D PRODUCTION         4–5-82         Rux           NO. 1925         5–13–82         Rux           TO PRODUCTION         7–29-82         R <sup>C</sup> NO. 2021         NO. 2661         1–18–84 | 4 |

|   |                                           |   |   |   |   |                                                                                                                                                                                                                          |                                                                                                                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                       |   |

| C |                                           |   |   |   |   |                                                                                                                                                                                                                          |                                                                                                                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                       | с |

| • |                                           |   |   |   |   |                                                                                                                                                                                                                          |                                                                                                                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                       |   |

| В |                                           | ; |   |   |   |                                                                                                                                                                                                                          |                                                                                                                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                       | В |

|   |                                           |   |   |   |   | The material herein contains in -<br>formation that is proprietary and<br>confidential to MDB SYSTEMS                                                                                                                    | OTY FSCM PART OR READ FOR NO.                                                                                                                     | NO                                                                               | MERCLATURE MATERIAL<br>DESCRIPTION SPECIFICATION<br>IST                                                                                                                                                                                                                                                                                                               |   |

| A |                                           |   | 1 | • |   | The material herein contains in-<br>formation that is proprietary and<br>confidential to MDB SYSTEMS<br>INC and is not to be copied or<br>disclosed for any purpose except<br>as specifically authorized in wri-<br>ting | UNLESS OTHERWISE SPECIFIED<br>DIMENSIONS ARE IN INCRES<br>TOLERANCES ARE:<br>FRACTIONS DECIMALS ANGLES<br>= .XX = .<br>MATERIAL<br>FINISH<br>CHEC | APPROVALS         DATE           N         J. MC.         12-15-81           KED | MDB SYSTEMS, INC.                                                                                                                                                                                                                                                                                                                                                     |   |

|   | B STORE NO ALEND<br>RECROES NO ALEND<br>B | 7 | 6 | 5 | 4 |                                                                                                                                                                                                                          | 3                                                                                                                                                 | 2                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                     |   |

|     | SYSTEMS | , INC. | SIZE | FSCM NO.<br>516 | <br>/ Q | DWG. NO. | 450402 |  | REV. |  |                                 |

|-----|---------|--------|------|-----------------|---------|----------|--------|--|------|--|---------------------------------|

| MDD |         |        | ]    |                 |         |          |        |  |      |  |                                 |

|     |         |        |      |                 |         |          |        |  |      |  | 8,7                             |

|     |         |        |      |                 |         |          |        |  |      |  |                                 |

|     |         |        |      |                 |         |          |        |  |      |  | A                               |

|     |         |        |      |                 |         |          |        |  |      |  |                                 |

|     |         | ;      |      |                 |         |          |        |  |      |  |                                 |

|     |         |        |      |                 |         |          |        |  |      |  | +5V                             |

|     |         |        |      |                 |         |          |        |  |      |  |                                 |

|     |         |        |      |                 |         |          |        |  |      |  |                                 |

|     |         |        |      |                 |         |          |        |  |      |  |                                 |

|     |         |        |      |                 |         |          |        |  |      |  |                                 |

|     |         |        |      |                 |         |          |        |  |      |  |                                 |

|     |         |        |      |                 |         |          |        |  |      |  |                                 |

|     |         |        |      |                 |         |          |        |  |      |  | <u>1*888</u><br>+ 8 7           |

|     |         |        |      |                 |         |          |        |  |      |  |                                 |

|     |         |        |      |                 |         |          |        |  |      |  | MDB <b>system</b><br>orange,ca. |

|     |         |        |      |                 |         |          |        |  |      |  |                                 |

|     |         |        |      |                 |         |          |        |  |      |  | /                               |

MDB SYSTEMS, INC. 1995 North Batavia Street Box 5508 Orange, California 92667-0508 (714) 998-6900 TWX: 910-593-1339