**VME-68K30**

**Hardware Reference Manual**

**Integrated Solutions**

**VME-68K30**

**Hardware Reference Manual**

**Integrated Solutions**

1140 Ringwood Court

San Jose, CA 95131

(408) 943-1902

**UNIX** is a registered trademark of AT&T in the USA and other countries.

**4.3BSD** was developed by the Regents of the University of California (Berkeley), Electrical Engineering and Computer Sciences Departments.

**490247 Rev. A**

**November 1988**

Copyright © 1988 by Integrated Solutions, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means (e.g., electronic, mechanical, photocopying, recording) without the prior permission of Integrated Solutions.

The information in this publication is subject to change without notice.

## PREFACE

This manual describes the Integrated Solutions VME-68K30 processor board. The text includes a product overview, specifications, and configuration and programming information. The manual has six sections, the content of which are briefly described in the following.

Section 1 describes the features and architecture of the VME-68K30 from both the single end user and the OEM point of view. Hardware features are described in terms of the functionality and operation of on-board modules, such as the VDMA and VATM addressing maps, the VME and PVSB bus interfaces, and the OCTART communications port. Special attention is given to the on-chip and on-board caches, since the CPU cache is a new feature in the ISI product line.

No details are given about PAL logic, timing diagrams, and board level signals. These must be obtained separately from engineering schematics and timing diagrams from ISI.

Section 2 describes the VSB (PVSB) developed by ISI for VME-68K30 access to high speed memory. Information about configuring the memory board with jumper and switch settings is contained in this section. This information is applicable to 4, 8, and 16 MB versions of the board.

Section 3 describes VME-68K30 addressing space which includes both VMEbus space and PVSB space.

Section 4 describes ISI defined space on the PVSB. On-board devices are addressed through this space. Their location and register descriptions to the bit level are described in this section along with programming information.

Section 5 describes jumper and switch settings used to configure the VME-68K30. Pin assignments for all connectors are also described.

Section 6 describes the PROM monitor and diagnostics.

# Table of Contents

|                                                    |                |

|----------------------------------------------------|----------------|

| <b>SECTION 1: Introduction .....</b>               | <b>1-1</b>     |

| 1.1    Features .....                              | 1-1            |

| 1.2    Performance Comparisons .....               | 1-1            |

| 1.3    System Level Overview .....                 | 1-2            |

| 1.4    MC68030 Hardware Overview .....             | 1-2            |

| 1.4.1    MC68030 CPU .....                         | 1-3            |

| 1.4.2    Floating Point Coprocessor .....          | 1-4            |

| 1.4.3    Caches .....                              | 1-4            |

| 1.4.4    Cache Operation .....                     | 1-6            |

| 1.4.5    Cache Coherency .....                     | 1-6            |

| 1.4.6    Cache Constructions .....                 | 1-6            |

| 1.4.7    Cache Burst Fill .....                    | 1-8            |

| 1.4.8    MMU .....                                 | 1-8            |

| 1.4.9    EPROM .....                               | 1-8            |

| 1.4.10    Serial Ports .....                       | 1-8            |

| 1.4.11    Battery Backed Clock .....               | 1-9            |

| 1.5    VMEbus Interface .....                      | 1-9            |

| 1.6    VMEbus Address .....                        | 1-11           |

| 1.7    VMEbus Address Translation Map (VATM) ..... | 1-12           |

| 1.8    VDMA Map .....                              | 1-12           |

| 1.9    Programming Devices on the PVSB .....       | 1-12           |

| 1.10    Resets .....                               | 1-13           |

| 1.11    Indicators .....                           | 1-13           |

| <br><b>SECTION 2: PVSB High Speed Memory .....</b> | <br><b>2-1</b> |

| 2.1    Introduction .....                          | 2-1            |

| 2.2    PVSB Features .....                         | 2-1            |

| 2.3    The VME-68K30 as PVSB Master .....          | 2-2            |

| 2.3.1    Functional Modules .....                  | 2-2            |

| 2.3.2    PVSB Arbitration .....                    | 2-2            |

| 2.3.3    Address Lines and Control Signals .....   | 2-3            |

| 2.4    PVSB Initialization .....                   | 2-5            |

| 2.5    ISI Defines Space .....                     | 2-7            |

| 2.6    Memory Board Initialization .....           | 2-9            |

| 2.6.1    Status Register .....                     | 2-9            |

| 2.6.1    Write Control Register .....              | 2-11           |

| 2.7    Initialized PVSB Address Space .....        | 2-11           |

| 2.8    System Space .....                          | 2-12           |

| 2.9    PVSB Access .....                           | 2-13           |

| 2.10    PVSB Configuration .....                   | 2-15           |

| 2.10.1    E1: GA2-0 Input Enable .....             | 2-16           |

| 2.10.2    E2-E3: Bank Interleave .....             | 2-16           |

| 2.10.3    E4: Number of Banks .....                | 2-17           |

| 2.10.4    E5-E6: Refresh Cycle Length .....        | 2-17           |

|                                                    |                                                      |            |

|----------------------------------------------------|------------------------------------------------------|------------|

| 2.10.5                                             | E7: RAM Size .....                                   | 2-17       |

| 2.10.6                                             | E8: Base Address on PVSB .....                       | 2-17       |

| 2.11                                               | LEDs .....                                           | 2-18       |

| 2.12                                               | PVSB Bus Signals on P2 .....                         | 2-19       |

| <b>SECTION 3: VME-68K30 Addressing Space .....</b> |                                                      | <b>3-1</b> |

| 3.1                                                | Introduction .....                                   | 3-1        |

| 3.2                                                | Function Codes and A31 .....                         | 3-3        |

| 3.3                                                | CPU Space (FC-7) .....                               | 3-5        |

| 3.4                                                | VATM Map (FC=1, 2, 5, 6) .....                       | 3-5        |

| 3.5                                                | Access to PVSB .....                                 | 3-5        |

| 3.6                                                | Programming the VATM Map .....                       | 3-5        |

| 3.7                                                | Programming the VDMA Registers .....                 | 3-7        |

| 3.8                                                | Direct PVSB Access: Extended Space .....             | 3-8        |

| 3.9                                                | Virtual DMA Access to PVSB Memory .....              | 3-8        |

| 3.10                                               | Virtual PVSB Access: Standard Space .....            | 3-9        |

| 3.10                                               | Virtual PVSB Access: Extended Space .....            | 3-10       |

| <b>SECTION 4: ISI Defined Space .....</b>          |                                                      | <b>4-1</b> |

| 4.1                                                | Introduction .....                                   | 4-1        |

| 4.2                                                | ISI Defined Space 0000 0000-FFFF FFFF .....          | 4-2        |

| 4.3                                                | Cache Invalidate Space 0000 0000-7FFF FFFF .....     | 4-2        |

| 4.4                                                | Register Access on the PVSB .....                    | 4-2        |

| 4.5                                                | I/O & System Space 8000 0000-BFFF FFFF .....         | 4-2        |

| 4.5.1                                              | PVSB IACK Space .....                                | 4-3        |

| 4.5.2                                              | PVSB Alternate Space .....                           | 4-3        |

| 4.5.3                                              | PVSB I/O Space .....                                 | 4-3        |

| 4.5.4                                              | PVSB System Space .....                              | 4-3        |

| 4.6                                                | On-Board Device Registers: C000 0000-EFFF FFFF ..... | 4-3        |

| 4.6.1                                              | OCTART .....                                         | 4-3        |

| 4.6.2                                              | SRAM/Real Time Clock .....                           | 4-7        |

| 4.6.3                                              | Control Register .....                               | 4-7        |

| 4.6.4                                              | VMEbus Master Address Translation Map (VATM) .....   | 4-9        |

| 4.6.5                                              | VATM Programming .....                               | 4-10       |

| 4.6.6                                              | EPROM .....                                          | 4-11       |

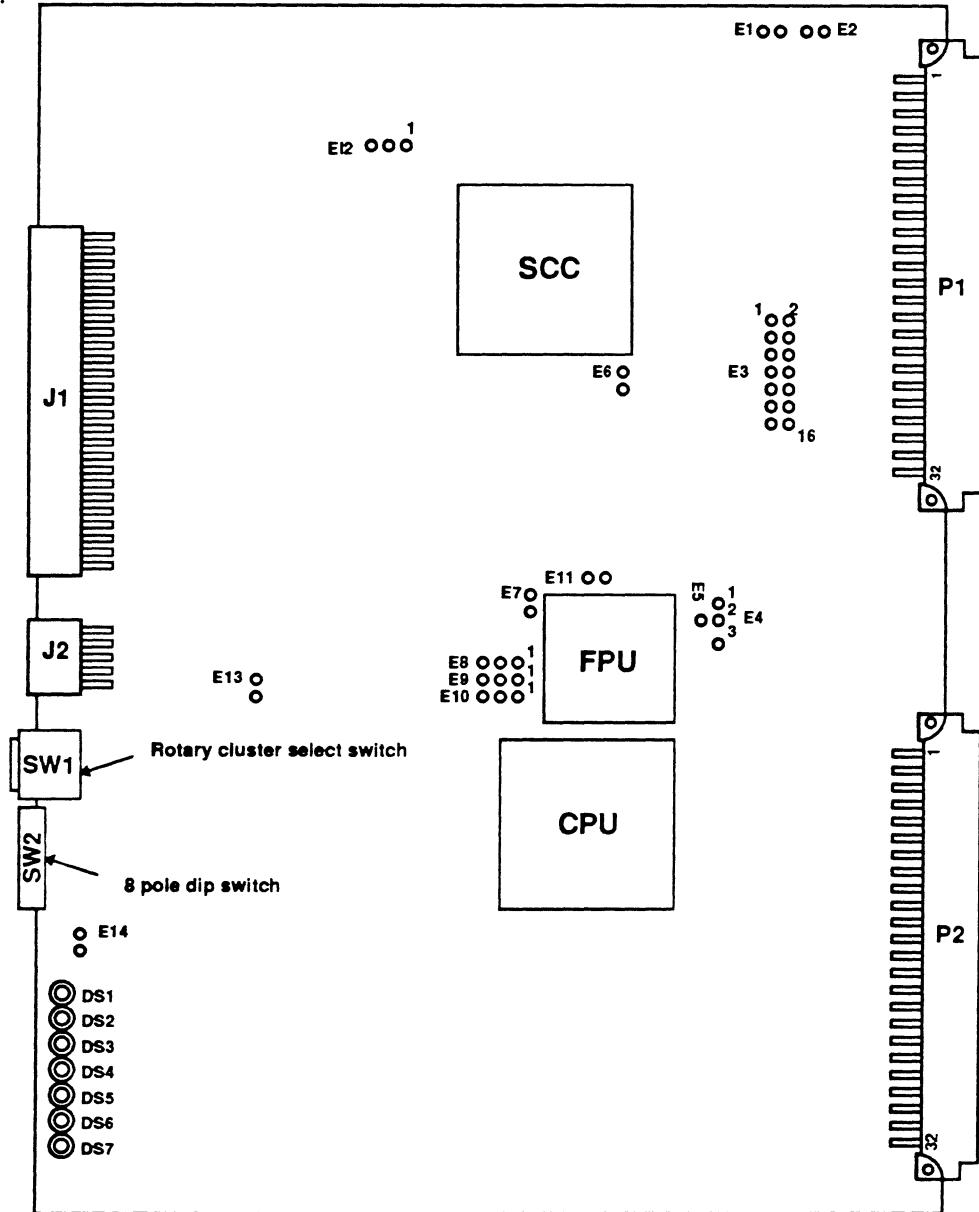

| <b>SECTION 5: Configuration .....</b>              |                                                      | <b>5-1</b> |

| 5.1                                                | Introduction .....                                   | 5-1        |

| 5.2                                                | Jumper Selections .....                              | 5-2        |

| 5.2.1                                              | E1-E2: Bus Request/Grant Level .....                 | 5-2        |

| 5.2.2                                              | E3: VMEbus Interrupt Request Level .....             | 5-2        |

| 5.2.3                                              | E4-E5: Floating Point .....                          | 5-3        |

| 5.2.4                                              | E6: PROFILE .....                                    | 5-3        |

| 5.2.5                                              | E7: MMU Disable .....                                | 5-4        |

| 5.2.6                                              | E8-E9-E10: EPROM .....                               | 5-4        |

| 5.2.7                                              | E11: Cache Disable .....                             | 5-4        |

| 5.2.8                                              | E12: VME Arbitration .....                           | 5-5        |

| 5.2.9                                              | E13: External Reset .....                            | 5-5        |

| 5.2.10                                             | E14: Watchdog Timer .....                            | 5-5        |

|                                              |                                                     |      |

|----------------------------------------------|-----------------------------------------------------|------|

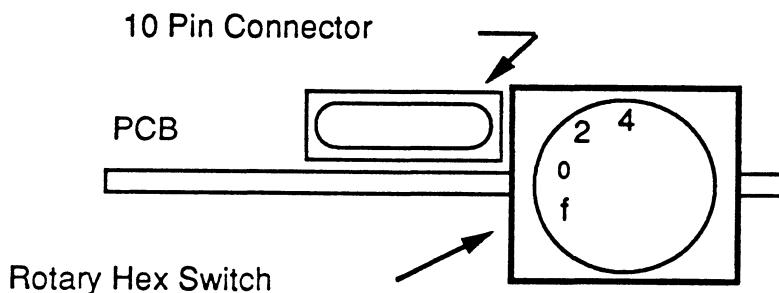

| 5.3                                          | SW1 Set Cluster Numbered .....                      | 5-5  |

| 5.4                                          | General Purpose Switch .....                        | 5-6  |

| 5.5                                          | LED Indicators .....                                | 5-7  |

| 5.6                                          | Connectors .....                                    | 5-8  |

| 5.6.1                                        | Signal Line States .....                            | 5-8  |

| 5.6.2                                        | VMEbus Connector P1 .....                           | 5-9  |

| 5.6.3                                        | PVSB Bus Signals on P2 .....                        | 5-10 |

| 5.6.4                                        | PVSB Bus Signal Definitions .....                   | 5-10 |

| 5.6.5                                        | Serial Port Connectors .....                        | 5-11 |

| 5.7                                          | VMEbus Specifications .....                         | 5-12 |

| 5.8                                          | Environmental Specifications .....                  | 5-13 |

| <br>SECTION 6: Monitor and Diagnostics ..... |                                                     | 6-1  |

| 6.1                                          | Introduction .....                                  | 6-1  |

| 6.2                                          | Capabilities .....                                  | 6-1  |

| 6.3                                          | Power On/Reset Initialization .....                 | 6-1  |

| 6.4                                          | Initialization .....                                | 6-2  |

| 6.5                                          | ISI Banner Display .....                            | 6-3  |

| 6.6                                          | Loading a Program From the Distribution Tape .....  | 6-4  |

| 6.7                                          | Monitor Commands at the PROM Prompt .....           | 6-4  |

| 6.8                                          | PROM Diagnostics .....                              | 6-9  |

| 6.9                                          | Tape Diagnostics .....                              | 6-10 |

| 6.10                                         | Brief Description of Available Diagnostics .....    | 6-10 |

| 6.11                                         | ISI Stand Alone Diagnostics Executive (sadie) ..... | 6-11 |

| 6.11.1                                       | User Level sadie Menu .....                         | 6-11 |

| 6.11.2                                       | Expert Level sadie Menu .....                       | 6-12 |

## List of Figures

|             |                                                |      |

|-------------|------------------------------------------------|------|

| Figure 1-1. | VME-68K30 on VMEbus and PVSB .....             | 1-2  |

| Figure 1-2. | VME-68K30 Block Diagram .....                  | 1-3  |

| Figure 1-3. | Cache Data and Disk Data .....                 | 1-5  |

| Figure 1-4. | External Cache .....                           | 1-7  |

| Figure 1-5. | Format of Cache Tag Entry .....                | 1-7  |

| Figure 2-1  | Clusters and PVSB Memory Boards .....          | 2-1  |

| Figure 2-2  | Block Diagram of PVSB Memory Board .....       | 2-3  |

| Figure 2-3  | PVSB Address Space Before Initialization ..... | 2-6  |

| Figure 2-4  | ISI Defined Space .....                        | 2-8  |

| Figure 2-5  | PVSB Memory Board Status Register .....        | 2-10 |

| Figure 2-6  | PVSB Control/Status Register .....             | 2-11 |

| Figure 2-7  | PVSB Address Space After Initialization .....  | 2-13 |

| Figure 2-8  | PVSB Memory Board Jumper Positions .....       | 2-15 |

| Figure 2-9  | Connector P2 Pin Assignments .....             | 2-19 |

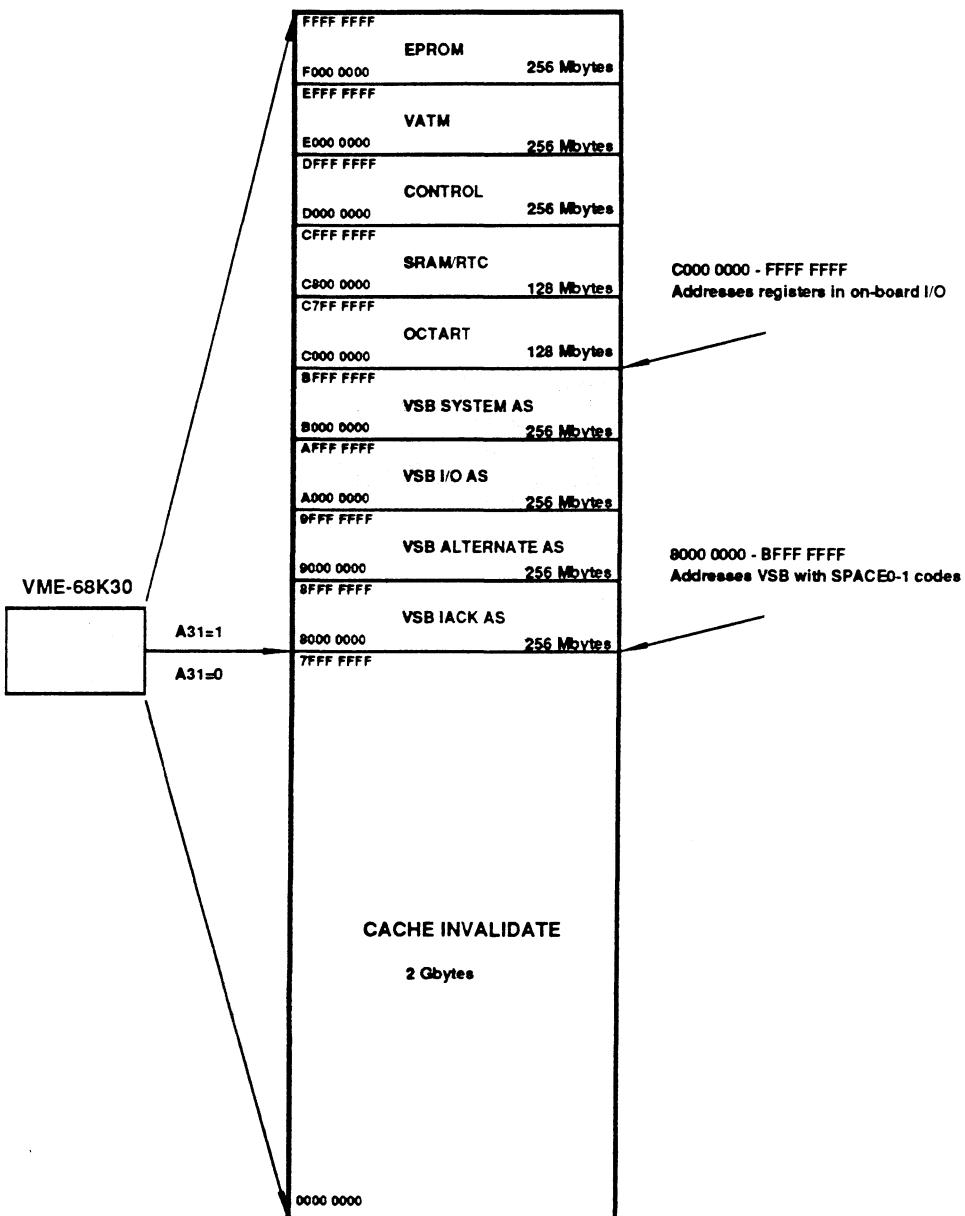

| Figure 3-1  | VME-68K30 Addressing Space .....               | 3-1  |

| Figure 3-2  | VME-68K30 Bus Access .....                     | 3-3  |

| Figure 3-3  | Local Access to VATM .....                     | 3-5  |

| Figure 3-4  | Base Address of Cluster .....                  | 3-6  |

| Figure 3-5  | VDMA Register Bit Pattern .....                | 3-7  |

| Figure 3-6  | Direct Access from VME Master to PVSB .....    | 3-8  |

| Figure 3-7  | Standard Virtual DMA Access .....              | 3-9  |

| Figure 3-7  | Extended Virtual DMA Access .....              | 3-9  |

|            |                                    |      |

|------------|------------------------------------|------|

| Figure 4-1 | ISI Defined Space .....            | 4-1  |

| Figure 4-2 | Loading VATM Registers .....       | 4-11 |

| Figure 5-1 | VME-68K30 Board Layout .....       | 5-1  |

| Figure 5-2 | Rotary Switch Settings .....       | 5-6  |

| Figure 5-3 | Connector P1 Pin Assignments ..... | 5-9  |

| Figure 5-4 | Connector P2 Pin Assignments ..... | 5-10 |

| Figure 5-4 | Connector J1 Pin Assignments ..... | 5-11 |

| Figure 5-4 | Connector J2 Pin Assignments ..... | 5-12 |

| Figure 6-1 | Interpretation of LEDs .....       | 6-1  |

## List of Tables

|             |                                                     |      |

|-------------|-----------------------------------------------------|------|

| Table 1-1.  | Cluster and Slave Functional Modules .....          | 1-11 |

| Table 1-2.  | Reset Sources in Master and Slave Mode .....        | 1-13 |

| Table 2-1.  | SPACE1-0 Code Interpretation .....                  | 2-7  |

| Table 2-2.  | Memory Board I/O: SPACE1-0 .....                    | 2-9  |

| Table 2-3.  | PVSB Addressing Modes .....                         | 2-14 |

| Table 2-4.  | Jumper Descriptions .....                           | 2-16 |

| Table 2-5.  | E1: GA2-0 Input Enable .....                        | 2-16 |

| Table 2-6.  | E2-E3: Bank Interleave .....                        | 2-16 |

| Table 2-7.  | E4: Number of Banks .....                           | 2-17 |

| Table 2-8.  | E5-E6: Refresh Cycle Length .....                   | 2-17 |

| Table 2-9.  | E7: RAM Size .....                                  | 2-17 |

| Table 2-10. | E8: Base Address on PVSB .....                      | 2-18 |

| Table 2-11. | LED Interpretation .....                            | 2-18 |

| Table 3-1.  | A31 and Function Codes FC0-2 .....                  | 3-4  |

| Table 3-2.  | Cluster ID in VME Standard and Extended Space ..... | 3-7  |

| Table 3-3.  | Direct and Virtual Translation Values .....         | 3-8  |

| Table 4-1.  | PVSB SPACE0-1 Address Qualifiers .....              | 4-2  |

| Table 4-2.  | Input PortA. C000 000D .....                        | 4-4  |

| Table 4-3.  | Input PortB. C000 001D .....                        | 4-5  |

| Table 4-4.  | Input PortC. C000 002D .....                        | 4-5  |

| Table 4-5.  | Input PortD. C000 003D .....                        | 4-6  |

| Table 4-6.  | Real Time Clock Register Addresses .....            | 4-7  |

|            |                                        |      |

|------------|----------------------------------------|------|

| Table 4-7. | Status Register .....                  | 4-7  |

| Table 4-8. | Control Register Address .....         | 4-8  |

| Table 4-9. | VME Address Translation Register ..... | 4-10 |

| Table 5-1. | Jumper Number and Function .....       | 5-1  |

| Table 5-2. | VMEbus Request/Grant Level .....       | 5-3  |

| Table 5-3. | VMEbus Interrupt Request Level .....   | 5-3  |

| Table 5-4. | Floating Point Clock Speed .....       | 5-4  |

| Table 5-5. | On-Board EPROM Size .....              | 5-4  |

| Table 5-6. | Cluster Select Switch .....            | 5-6  |

| Table 5-7. | General Purpose Register Switch .....  | 5-7  |

| Table 5-8. | LED Indicators .....                   | 5-6  |

# Section 1: Introduction

## 1.1 VME-68K30 Features

The VME-68K30 is a double-wide, VME based CPU card with a high-performance MC68030 CPU. The VME-68K30 implements the following features in the latest VLSI technology:

- 25MHz CPU Operation

- Supports 64 Mbytes of high speed memory through a private VME Subsystem Bus (PVSB)

- VMEbus compatible with full implementation of all functional modules

- Configurable for single or multiprocessor environments

- Floating point coprocessor strapped to microprocessor speed

## 1.2 Performance Comparisons

Table 1-1 compares the read/write speed of a VME-68K30 with its MC68030 microprocessor to the speed of other ISI boards that use a MC68020 processor. The improved access time of the MC68030 with two internal caches and a write pipeline is further enhanced by an external, 64 Kbyte cache on the VME-68K30. The large external cache allows the K30 to continuously outperform earlier CPU boards even when multiple processes and rapid context switching are normal system parameters.

As Table 1-1 shows, the write pipeline reduces sequential write time by more than 50 percent. A single write takes 3 clocks (120 $\eta$ s) but a subsequent pipelined write requires only one additional clock for a 140 $\eta$ s average.

If a read operand is found in cache, the K30 will fetch it in less than half the time that other boards require to go to memory. When a read operand is not found in cache, performance is slightly degraded, but the large, external cache reduces the need for frequent memory accesses under almost all operating conditions. The table is included only to show the how the pipeline and caches can affect access time. No conclusions about improved system performance or efficiency should be attempted without complete system analysis.

**Table 1-1.** Comparison of MC68030 with MC68020

| Board     | Processor | MHz   | Write1       | Write2       | Read         | Cache Read Hit | Cache Read Miss | Non-Cache Read |

|-----------|-----------|-------|--------------|--------------|--------------|----------------|-----------------|----------------|

| VME-68K20 | MC68020   | 16.67 | 180 $\eta$ s | 360 $\eta$ s | 240 $\eta$ s |                |                 |                |

| VME-68225 | MC68020   | 25    | 160 $\eta$ s | 320 $\eta$ s | 200 $\eta$ s |                |                 |                |

| VME-68K30 | MC68030   | 25    | 120 $\eta$ s | 140 $\eta$ s |              | 80 $\eta$ s    | 280 $\eta$ s    | 280 $\eta$ s   |

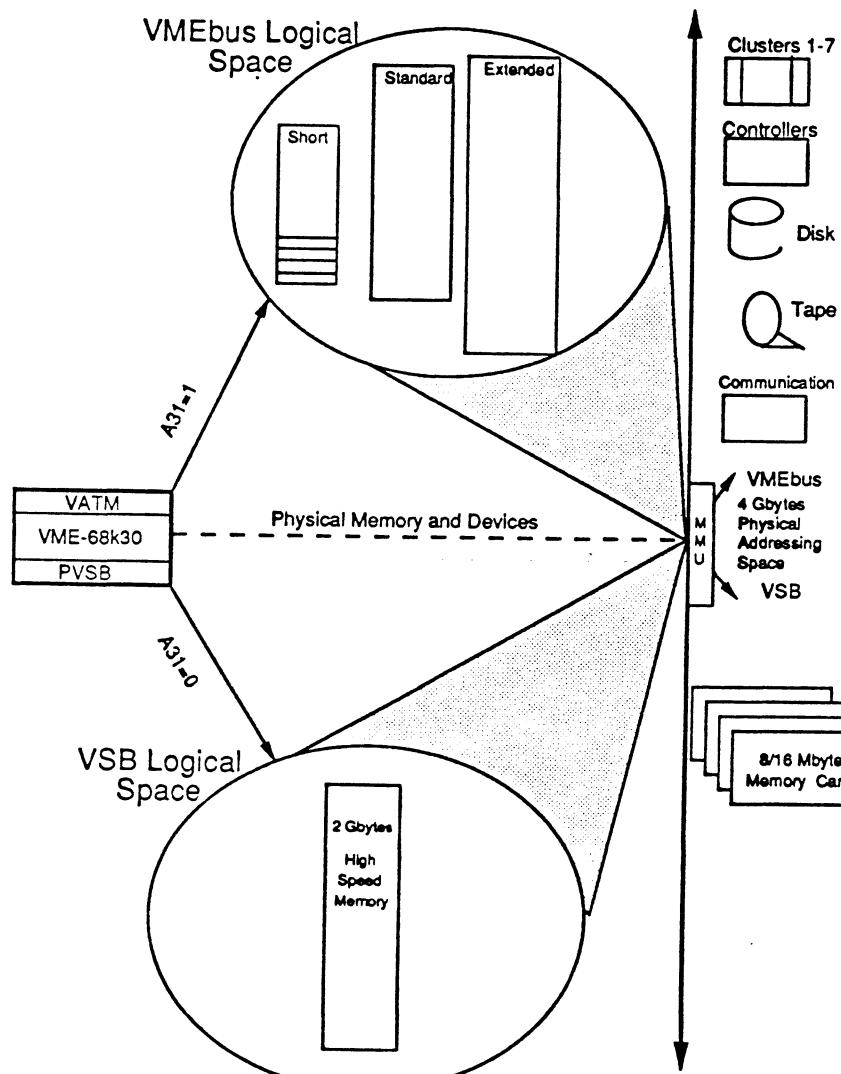

### 1.3 System Level Overview

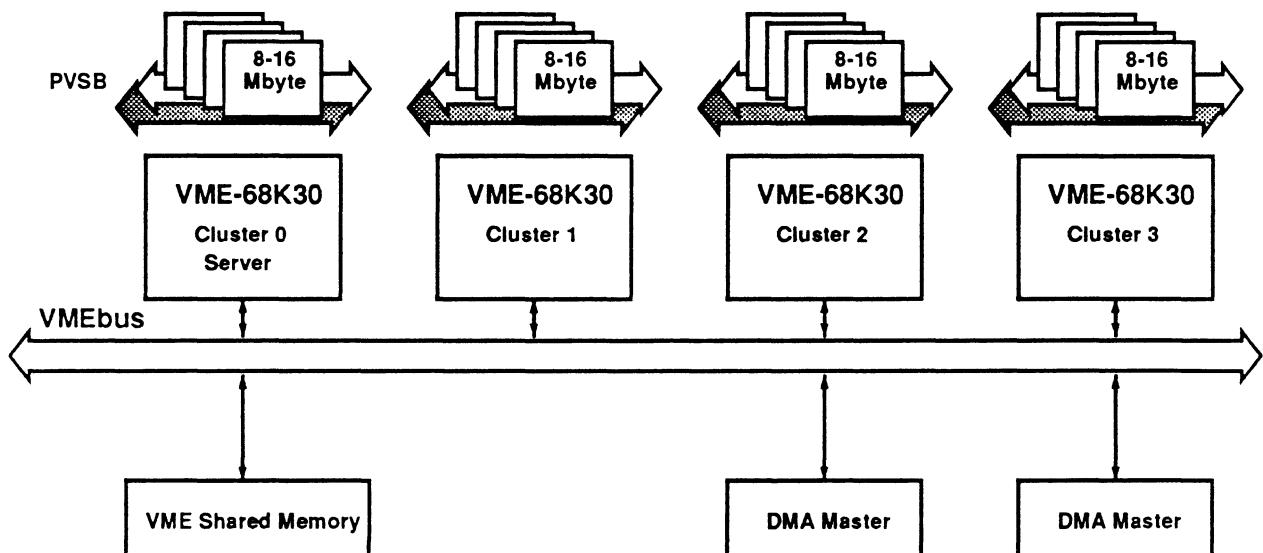

The VME-68K30 is configurable for either single processor or multiprocessor operation, and can be used as either a cluster or server node in cluster installations. Any cluster in an installation has access to both its own high-speed memory and to the high speed memory of all other clusters.

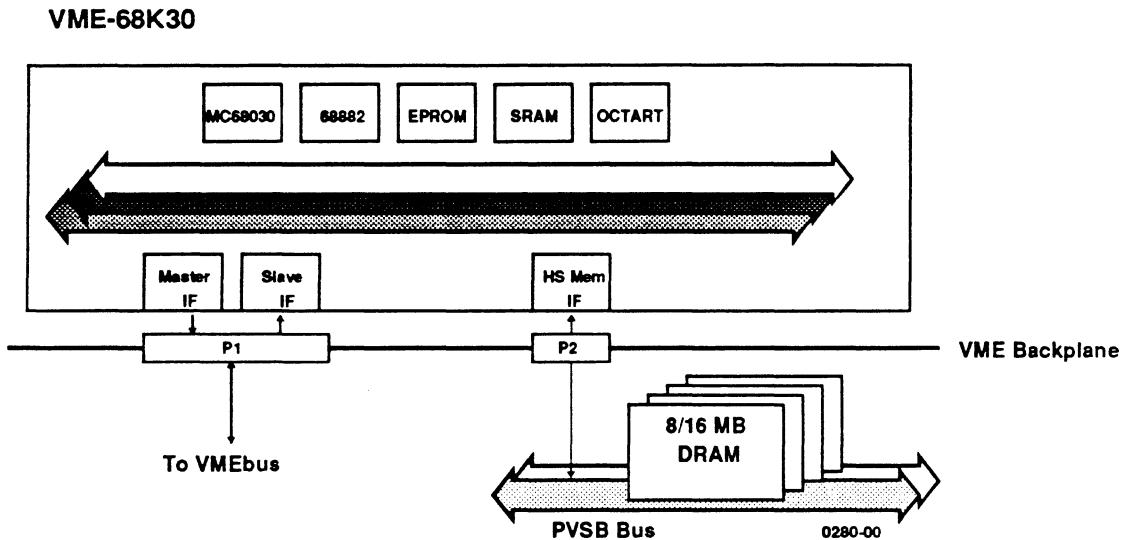

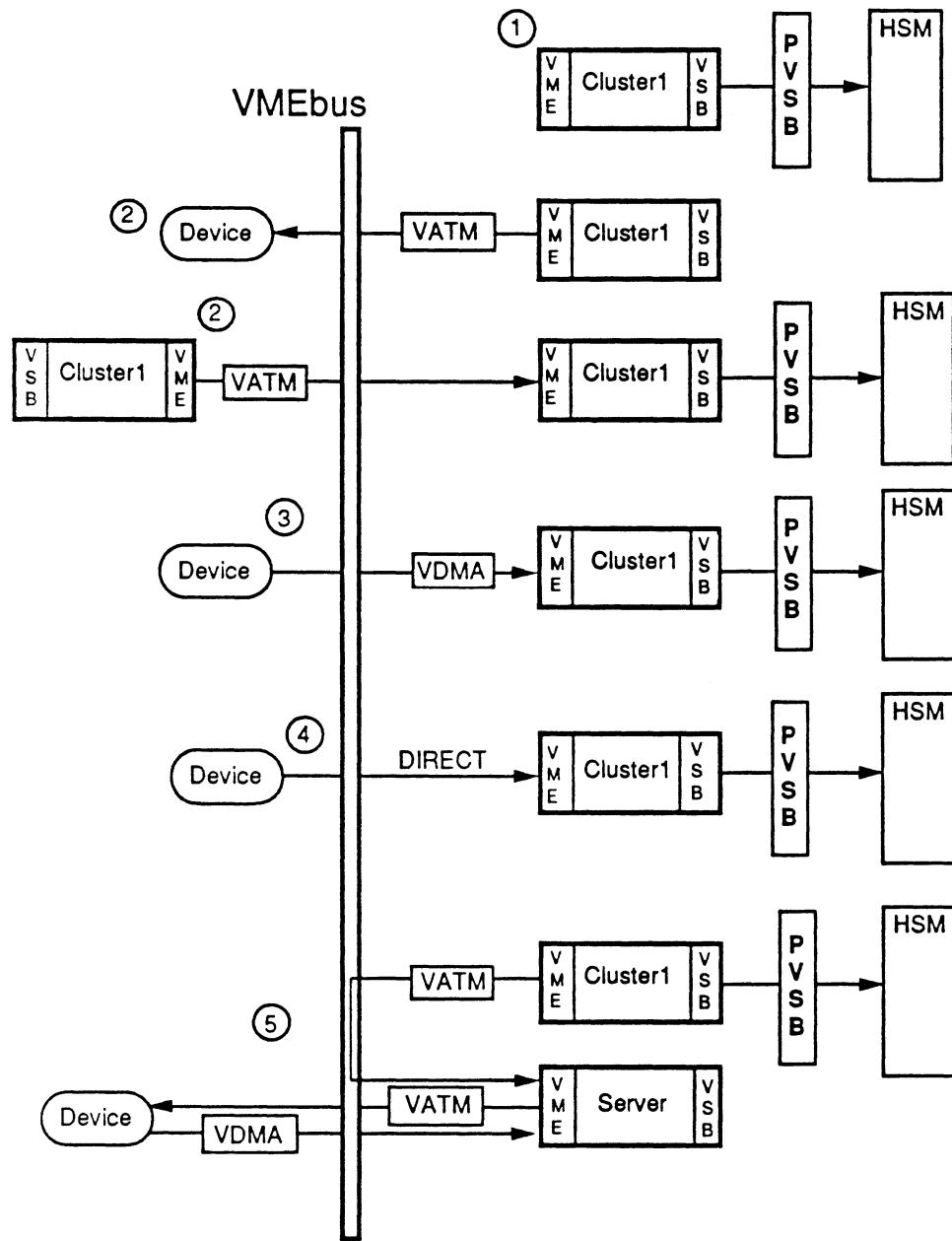

The state-of-the art MC68030 gives the VME-68K30 board its processing power. The true functionality of the board in multiprocessor systems derives from its dual interface to the global VMEbus and its own PVSB. The PVSB is a high speed bus used only for memory access. Figure 1-1 shows the relation between these two buses and the processor board.

Figure 1-1. VME-68K30 on VMEbus and PVSB

### 1.4 VME-68K30 Hardware Overview

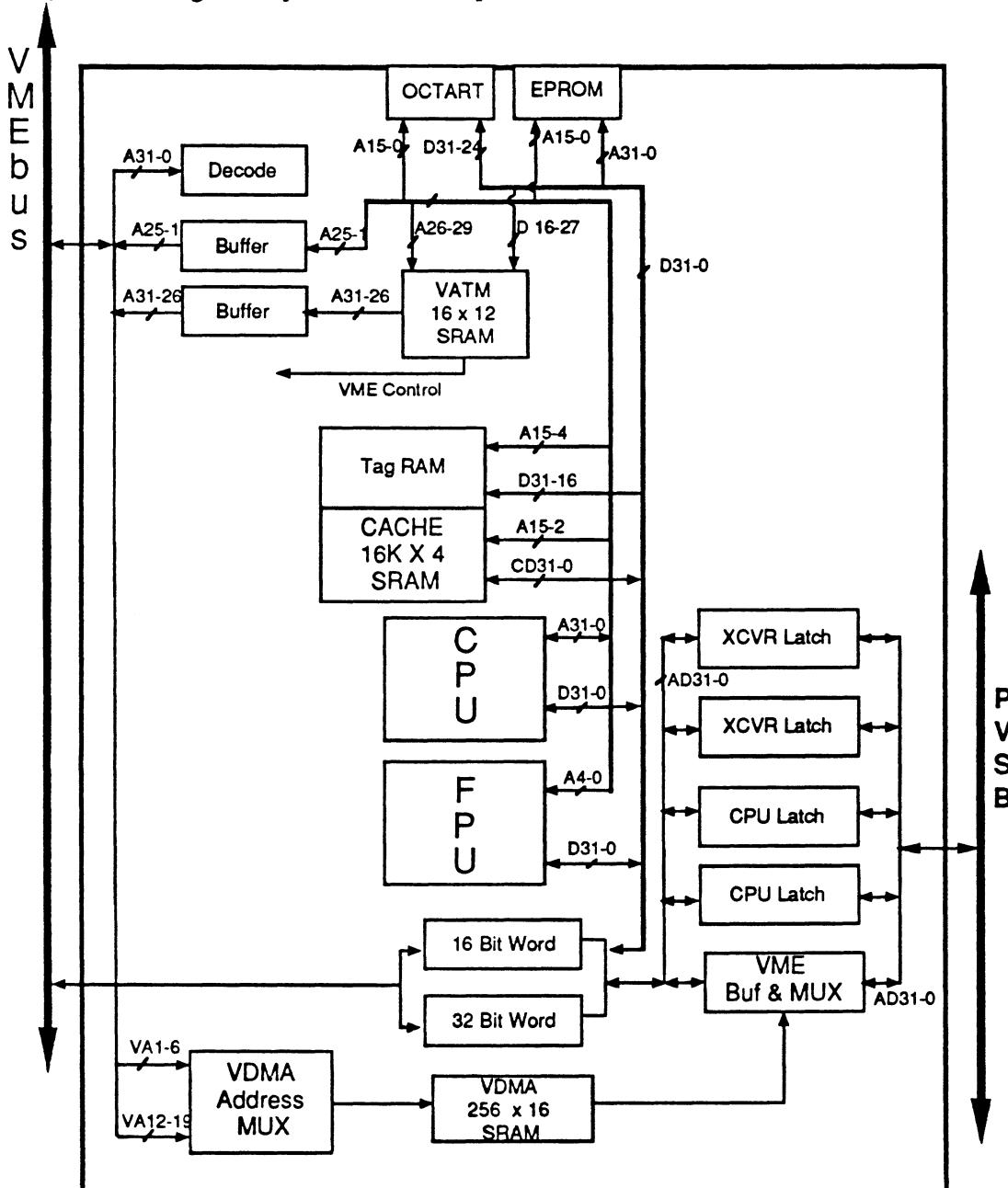

The basic hardware units on the VME-68K30 include:

- A MC68030 CPU

- A MC68882 floating point coprocessor

- A 64 Kbyte on-board cache

- Memory access through a high Performance VMEbus Subsystem Bus (PVSB)

- A global VMEbus address translation map (VATM)

- Socket for variable sized PROM (128 Kbytes standard)

- A single IC provides eight RS-232-C serial ports and four, 16-bit counter/timers

- A 2 Kbyte static RAM (SRAM)

- A Battery backed real-time clock

- A word swap buffer that accommodates 16 and 32-bit VMEbus ports

- Soft and hard resets

- Six LED indicators identify accesses and diagnostic failures

A block diagram showing the major hardware components is shown in Figure 1-2.

Figure 1-2. VME-68K30 Block Diagram

#### 1.4.1 MC68030 CPU

The MC68030 CPU is capable of processing six million instructions per second (6 MIPS). It is the most advanced of Motorola's 68000 microprocessor series and is code compatible with

previous versions.

The following list briefly summarizes the MC68030 features:

1. 32 addressing lines access a 4 gigabyte physical addressing range.

2. 256 byte caches store most recently used data and instruction.

3. A write pipeline has space for three sequential writes to I/O or memory.

4. The inter-processor interrupts operate in multiprocessor environments.

5. An internal MMU translates logical to physical address in hardware and protects each addressing region from illegal access.

6. Read-Modify-Write cycles are implemented to insure data integrity.

7. Dynamic bus sizing automatically determines device port sizes on a cycle by cycle basis.

The Harvard architecture is implemented on multiple internal buses in the MC68030 which allows internal caches, MMU, and external bus controller to operate in parallel. The individual steps required for instruction execution are thus overlapped to increase processing speed.

#### 1.4.2 Floating Point Coprocessor

In select benchmark tests, the MC68882 floating point coprocessor performs four times as fast as the MC68881. On average, it provides over 1.5 times the performance of the MC68881 at the same clock frequency. In ISI systems the floating point unit operates at CPU speed, typically 25 MHz.

The MC68882 is a full implementation of the *IEEE Standard for Binary Floating-Point Arithmetic* (754) with the addition of a full set of trigonometric and transcendental functions, on chip constants, and a full 80-bit extended precision real-time data format. Since all data transfers are performed by the main processor after an MC68882 request, memory management, bus errors, and bus arbitration instructions function as if they were executed by the MC68030.

Communication between coprocessors is asynchronous.

#### 1.4.3 Caches

Internally, the MC68030 has two 256 byte instruction and data caches which are described in *Motorola User's Manual, MC68030UM/AD*, from Motorola Inc, 1987.

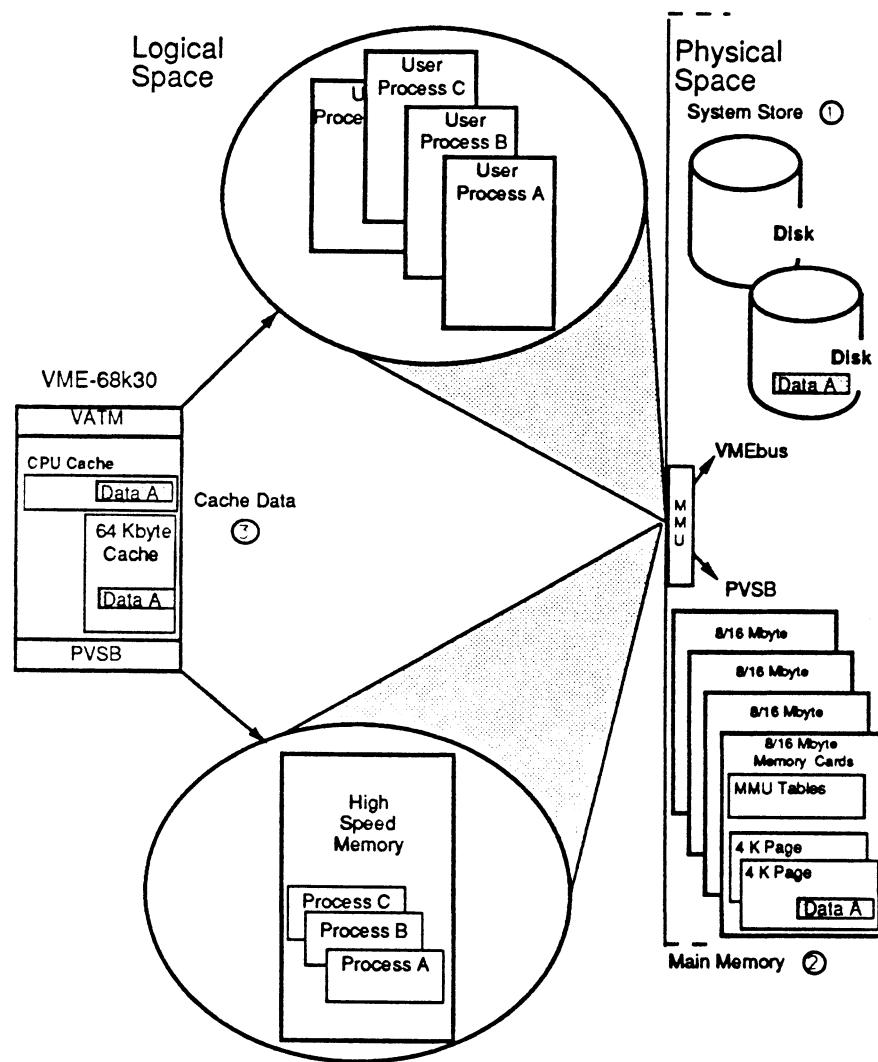

External to the microprocessor, the VME-68K30 has a 64 Kbyte on-board cache that combines instructions and data. The external cache is briefly described in the following. Its relation to system memory and main memory is shown in Figure 1-3.

Figure 1-3. Cache Data and Disk Data

The on-board cache is a one-way set associative or direct mapped cache implemented in high speed DRAM. Figure 1-3 shows the relation of CPU and on-board cache to system memory and disks.

As Figure 1-3 illustrates, data - which is represented in the figure as Data A - can reside simultaneously in four places in an ISI system with VME-68K30 processors. All data that is related to all processes resides on disks or system store which is shown as (1) in the figure. Data that is related to a running process is taken from disk and transferred to main memory where it is stored in DRAM as shown in (2). The kernel is responsible for moving data from disk where the access is very slow to DRAM where the access is much faster. It moves data on a demand basis. When a running process calls for data, the kernel moves it from disk to the faster access DRAM one page at a time. Each page has 4K of data. When the process is no longer running, or requires more than the 4K page, the kernel swaps out the old page and brings new data from disk to the main memory in DRAM.

As the process uses data, again say Data A in the figure, it does not simply replace it, but maintains it in cache, which is shown in part (3) of the figure. The assumption is that if a process requires data once, it will require the same data again. If it is cached on-board it can be fetched much more quickly than if it were stored in main memory or disk. When many processes are running, data in the small 256 byte internal caches on the MC68030 are quickly swapped out. But a copy is retained for a much longer period in the 64K external cache and can quickly be retrieved when the process runs again.

#### 1.4.4 Cache Operation

To avoid initiating a memory cycle during a CPU read or write cycle, hardware first searches the internal and then the external cache for the required instruction operand.

If the operand is found in either cache, the access to main memory is inhibited, the operand is given to the CPU, and the next instruction is executed. Finding the operand in either cache constitutes a cache hit which reduces the number of memory cycles required to fetch operands from main memory and greatly improves system efficiency. A status register bit allows a cumulative record of hits to be maintained for accounting purposes and system analysis.

A cache miss occurs if the operand is not found in either cache and the memory cycle must be executed. Successive misses tend to reduce overall system efficiency because of the cache search.

#### 1.4.5 Cache Coherency

A cache contributes to system efficiency if it maintains a high ratio of hits to misses. This requires that the cache be coherent, which means data in the cache is related to the processes being run, rather than to I/O transfers or other data not related to instruction operands.

To maintain cache coherency, ISI has provided three different areas in high speed memory that— when they are written— cause the cache to be updated in different ways or not be updated at all. The following briefly describes each area while maps are presented in Section 2:

1. Cache Invalidate. Data written to cache invalidate is not cached. Moreover, any operands located on the same tag line as the written data are invalidated when the cache invalidate area is written.

2. Write allocate. When data is written to this space the cache is updated whether it contained an entry before or not, and regardless of the state of that entry.

3. No-write allocate. When this space is written the cache is updated only if a previous entry existed in the cache. Otherwise it is not updated

#### 1.4.6 Cache Construction

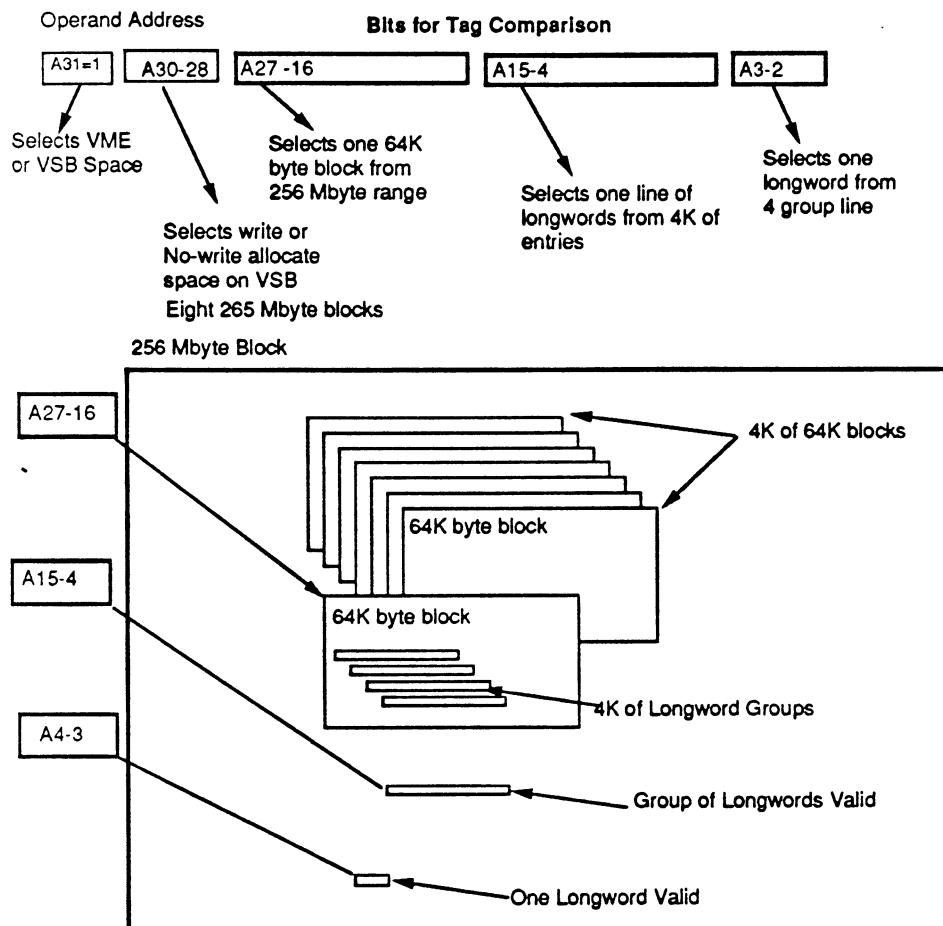

Cache hardware compares operand addresses with cached data addresses at three levels. Operand address bits A27-16 are compared to cache addresses to determine if a cache entry exists for the 256 Mbyte block that the CPU accesses. Simultaneously, operand addresses A15-A4 are compared to cache entries to determine if an entry exists within a 64K block of the current access. If these two comparisons match, valid bits in the cache tag RAM are checked against A3-2 to see if the cache contains the specific 32-bit long word that matches the operand address. If all matches are true a cache hit occurs.

Figure 1-4 shows the logical construction of the cache.

**Figure 1-4. External Cache**

Each cache tag entry contains complete information about cache data for the hardware comparators. Its format is shown in Figure 1-5.

| Address of Cached Data |        |       | Cached Data |       |       |       |

|------------------------|--------|-------|-------------|-------|-------|-------|

| Valid Bit              | Index  | Index | LWord       | LWord | LWord | LWord |

| XXXX                   | A27-16 | A15-4 | 32-0        | 32-0  | 32-0  | 32-0  |

**Figure 1-5. Format of Cache Tag Entry**

If the valid bit is clear, signifying no cache entry to match the CPU access, a bus error is asserted by cache logic and the the bus interface unit (BIU) in the CPU initiates a memory cycle. The internal and external caches are updated after a miss, unless a no write allocate or cache invalidate area of high speed memory is being written.

#### 1.4.7 Cache Burst Fill

Burst mode may or may not be implemented on your version of the VME-68K30 and it may or may not enhance processing speed, depending on how much context switching is done and how the applications are written. In general burst mode enhances performance if a program progresses linearly through data, but degrades performance when the program often jumps to different instruction sets. If your processor is capable of burst mode fills, you will be notified of that option in the PROM prompt when the system is first booted. Whether burst mode enhances performance can only be determined by time trials or experience in using this mode of operation.

If burst mode is set during a write cycle, the four long words in a single cache tag entry are updated in cache fill burst mode. A burst fill updates the entire cache line. The burst is allocated by the Motorola 2-1-1-1 synchronous cache fill. The first pipelined write to cache requires two clock states; subsequent writes require one.

All cache writes except synchronous burst fill consume 3 clock cycles. This includes a write through cycle where the cache is not updated, the write allocate cycle, where it is, and write misses where the address of an operand is not found in the cache.

Only the most recently used operands are maintained in the limited space of the internal cache. The CPU continually over writes them to make room for new data during processing. The advantage of the larger external cache is that it extends the store of recently used operands and rapidly restores internal cache contexts in a multi-processing environment.

#### 1.4.8 MMU

When the MMU is enabled, it translates logical addresses into physical addresses. The MMU concludes a translation when it has searched the translation tree and matched a logical address to its physical equivalent. An on board jumper is provided to activate the MMUDIS.

There are two accesses that do not require the MMU.

1. CPU space is always mapped from the logical to the physical 1:1.

2. Logical addresses in a transparently translated block are used as physical addresses, without modification, and without protection checking. Two translation registers (TT0 and TT1), each capable of defining a 16 Mbyte address space are available to define transparent blocks. The MMU and translation registers are fully described in Section 9 of the *Motorola User's Manual, MC68030UM/AD*, from Motorola, 1987.

#### 1.4.9 EPROM

A single, 32-pin EPROM socket accepts standard 27XXX series devices with 32 to 512 Kbytes of storage. The EPROM contains a monitor, limited diagnostics, initialization instructions and boot strap loading. Initialization is described in Section 4 of this manual. The diagnostics are described in Section 6.

#### 1.4.10 Serial Ports

The Signetics SCC2698A is a single MOS-LSI chip with eight universal, asynchronous communication channels. It is the primary user and peripheral devices interface to the VME-68K30. The chip also has four programmable timer/counters, all of which are used by the ISI kernel. The *SCC 2698 Octal Universal Asynchronous Receiver/Transmitter Product*

*Specification Guide, 853-1267 9872* from Signetics gives complete programming information for the chip. The programmable registers are located in ISI defined space beginning at C000 0000. For details see Section 4 of this manual.

In terms of signals generated, the channels provide RS-232-C request to send (RTS), clear to send (CTS), receive data (RxD), and transmit data (TxD) signal lines in data terminal equipment (DTE) mode. All outputs are TTL compatible. Channel operating modes include full-duplex, automatic echo, and local and remote loop back. One channel has full modem control.

The baud rate of each receiver/transmitter channel is independent and can be selected from one of the following:

- One of eighteen internal clocks speeds with a 50 to 38.4K baud range.

- A 16x, clock derived, programmable counter/timer.

The current configuration allows jumper selection from 1200, 2400, 9600, or 19200 baud for the console. Section 5 describes jumper selection.

The baud rate generator and counter/timer are driven by an external crystal.

The chip also has a power down mode in which oscillator inputs are not processed, but all command, status and data registers are saved.

Error detection includes parity, framing and overruns, false start bit, and line break detection and generation.

For pin assignments see the J1 connector description in Section 5 of this manual.

#### 1.4.11 Battery Backed Clock

A 2K byte static RAM maintains such information as the machine serial number, board serial number, base art work number, board revision level, auto boot arguments, and the machine internet address.

The on-board, real-time clock has an internal crystal, power-failure detection, and battery. It maintains the date in year, month, day, hour, minute and seconds. The battery backed clock and 2Kx8 SRAM are both on a single chip. Calibration is controlled by software, and worst case battery storage life is 11 years, at 70°C. The clock automatically corrects for 28, 29, 30 and 31 day months.

Typical accuracy is  $\pm 1$  minute per month. Writing the clock to update the current time registers does not disturb clock operations.

Power fail circuitry detects supply voltages within 4.75 to 4.5 volt window and write protects RAM after asserting unselect. The same circuitry tests battery voltage and sets a flag if voltage falls too low for dependable operation.

The clock is programmed in ISI defined space. See Section 4 of this manual for details.

## 1.5 VMEbus Interface

Functional modules on the VME-68K30 provide the following VMEbus interfaces.

1. A full function location monitor generates an on-board interrupt when its assigned addresses are detected on the VMEbus. The location monitor recognizes Short I/O, Standard, and Extended addressing so the board can be located anywhere on the VMEbus.

2. Master/slave modules:

- a. The master functional module initiates and directs data transfer bus (DTB) cycles to slave modules.

- b. The slave functional module detects and responds to DTB cycles initiated by a master and directed to it. When the VME-68K30 is in slave mode, other VMEbus masters can access its PVSB memory.

3. Bus grant and request modules:

- a. A four level arbiter that accepts requester signals BR0\*-BR3\* and grants the bus to one requester at a time is enabled by jumpers on the VME-68K30. In a cluster installation only one processor designated "cluster 0" or "server" has the bus arbiter enabled.

- b. On all processors in a system, a four level requester arbitrates for master status and accepts the appropriate bus grant (BGIN0-3) in signal to acknowledge its request. The processors also propagate both the bus grant in and bus grant out (BGOUT0-3) signals if arbitration is being granted on a request level other than its own, or if it has no on-board requests.

4. Interrupts:

- a. An interrupter module generates an interrupt request and provides Status/ID when acknowledged.

- b. An interrupt handler module detects interrupt requests from other bus masters and responds with a request for status identification (Status/ID).

- c. A daisy chain driver generates an interrupt acknowledge (IACK) when an interrupt handler acknowledges a request.

5. The VME-68K30 responds to system reset (SYSRESET\*) signals from other masters when in slave mode or generates the SYSRESET signal when configured as a server and in master mode.

As the foregoing suggests, in a multiprocessor environment such as a cluster installation, the responsibility for generating or responding to standard VMEbus signals is different for a server (cluster 0) and individual clusters (cluster1-7). Table 1-2 illustrates the differences in functional modules implemented on a VME-68K30 when it is used as a server rather than a cluster.

A brief summary of functional modules on cluster and server CPUs is presented in Table 1-2.

**Table 1-2.** Cluster and Slave Functional Modules

| VMEbus<br>Functional Module | Activated |             |

|-----------------------------|-----------|-------------|

|                             | Cluster 0 | Cluster 1-7 |

| IACK Daisy Chain Driver     | Yes       | Yes         |

| Interrupt Handler           | Yes       | No          |

| System Clock Driver         | Yes       | No          |

| Power Monitor               | Yes       | No          |

| Bus Timer                   | Yes       | No          |

| Arbiter                     | Yes       | No          |

| Master                      | Yes       | Yes         |

| Slave                       | Yes       | Yes         |

| Serial Clock Driver         | No        | No          |

| Location Monitor            | No        | No          |

| Requester                   | Yes       | Yes         |

| Interrupter                 | Yes       | Yes         |

**NOTES**

1. System clock (SYSCLK) signals are generated on the VME-68K30 when it is the server (Cluster 0). An ISI slot jumper card also generates this signal. Use only one system clock in a system. Disable all other sources.

2. AC failure detection and signaling (ACFAIL) is available in ISI systems on a separate board that does not require a VMEbus slot.

3. Serial Data (SERDAT\*), Serial Clock (SERCLK), and System Failure (SYSFAIL) are not generated or used by ISI systems or boards.

**1.6 VMEbus Address**

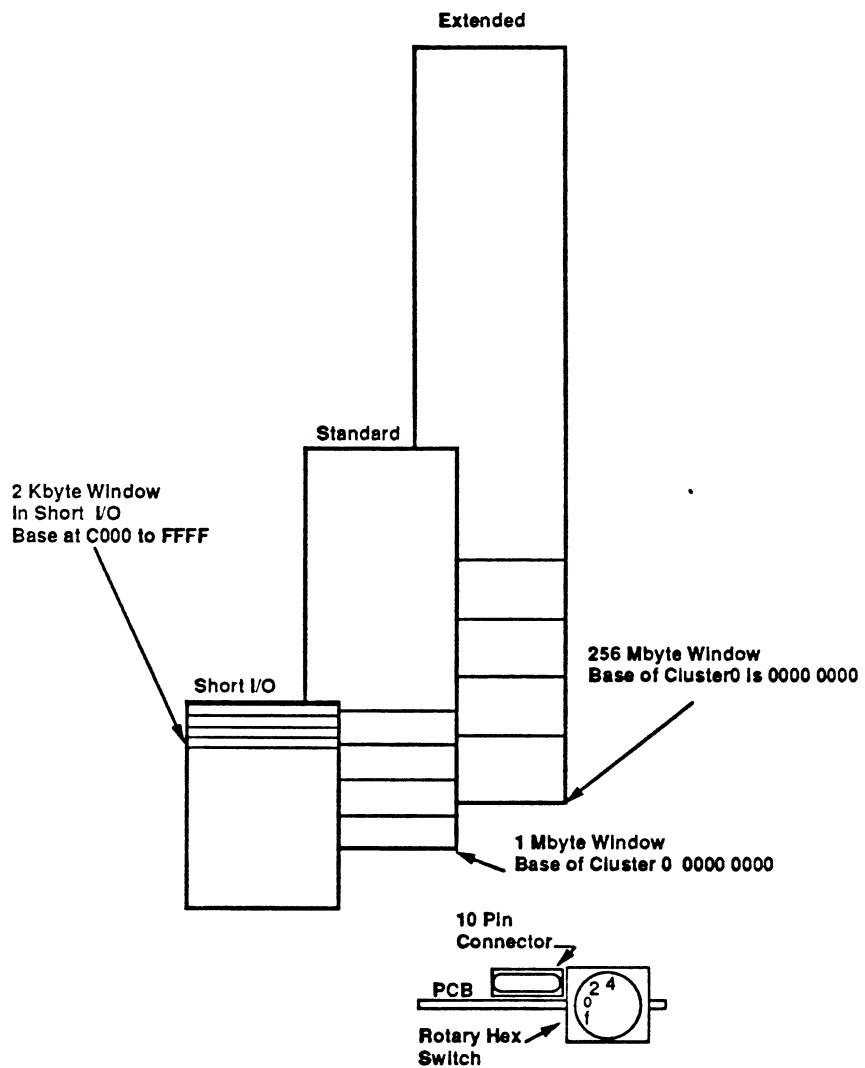

A number of parameters are associated with the VME-68K30 address in VMEbus space, all of which are selected by a single rotary switch. The switch sets the address of the processor board in three VME spaces simultaneously by creating the following windows into the board address space.

1. A 2 Kbyte window in VMEbus Short I/O space which includes the boards 256 VDMA registers used for programmable access to PVSB space.

2. A 1 Mbyte window into VMEbus Standard address space.

3. A 255 Mbyte window into VMEbus Extended address space.

If the rotary switch is set to "0" it tells the software that the board is the server in a cluster system, and that its base address will be VMEbus address 0000 0000. It also enables the on-board arbiter so the board will grant bus requests for the VME to other clusters and DMA masters in the system.

Other clusters in the system will be set with the same size windows as the server, but the rotary switch setting will increase the base address by the size of the window allocated each cluster by the hardware setting of the switch. For more details on the switch setting, see Section 5 in this manual.

## 1.7 VMEbus Address Translation Map (VATM)

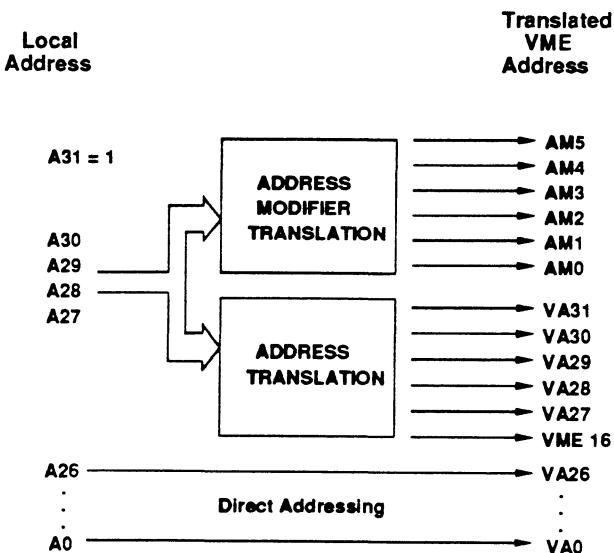

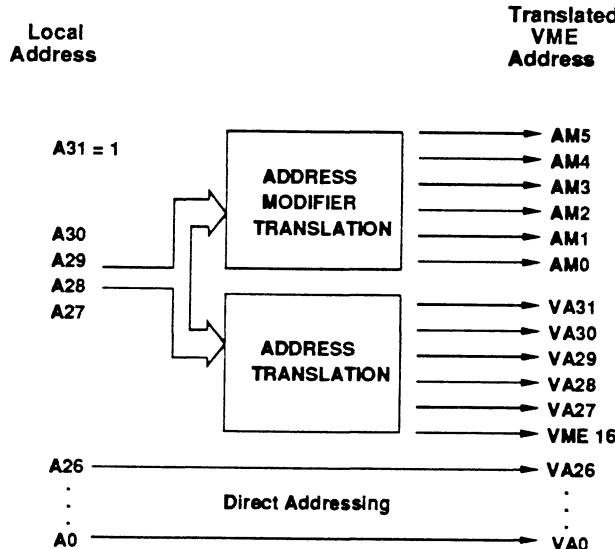

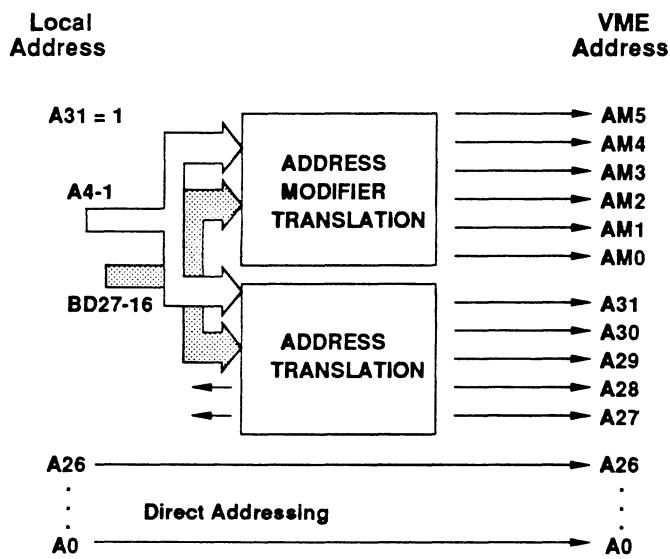

The MC68030 uses a map shown in block diagram in Figure 1-6 to access the VMEbus. The map is loaded with sixteen offset addresses that include address modifiers AM5-0. An access to the VMEbus selects one of the sixteen offsets which are then sent out on the VMEbus with local address lines A26-0.

The map is built in three  $16 \times 4$  bit static RAMs. After programming, all accesses to the VMEbus go through the map. Section 4 of this manual contains programming details.

After the VATM hardware is programmed, local bus addresses A30-27 select one of the sixteen offsets that include VME AM5-0 and VA31-27. Within VMEbus space, the offsets access a 128 Mbyte block and local address lines A26-0 select one address within that block.

Signal VME 16 enables a word swap buffer when the CPU is writing data to the VMEbus. When VME 16 is set to "1" the buffer breaks a 32-bit long word into two 16-bit words for devices that can only accept word wide transfers.

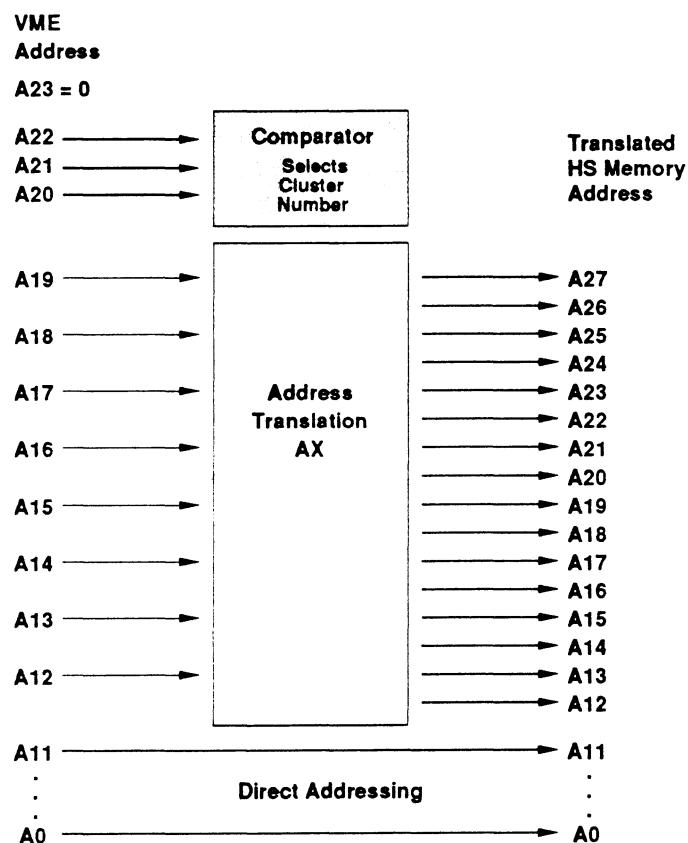

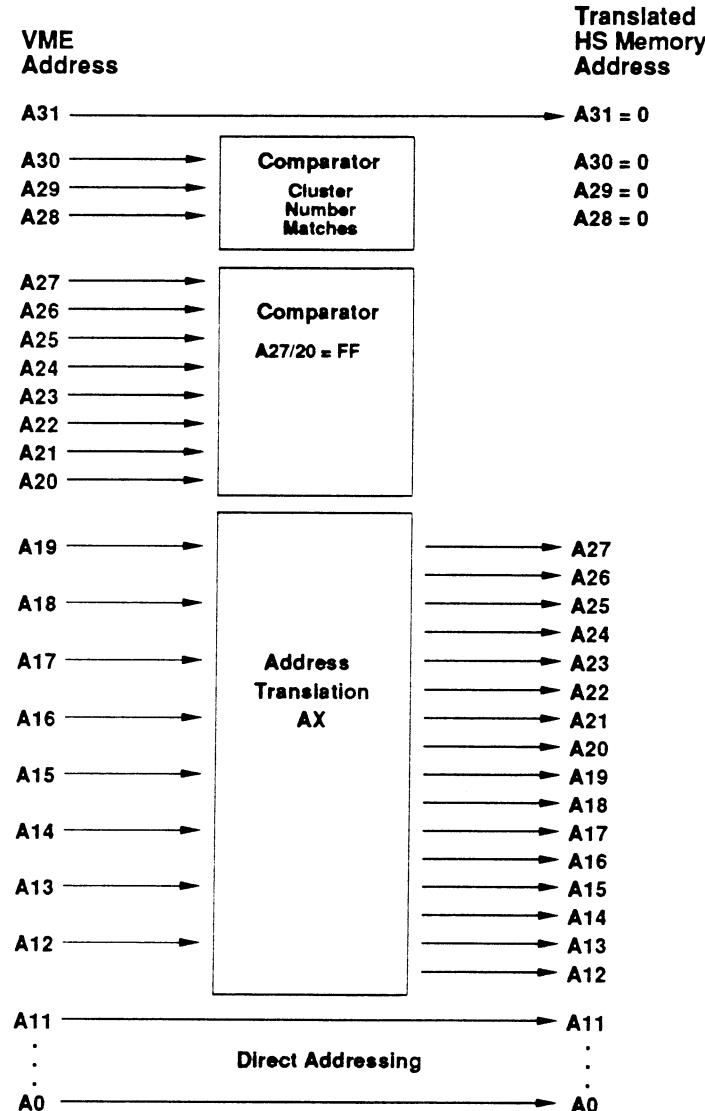

Figure 1-6. MC68030 Accesses to VMEbus

## 1.8 VDMA Map

The VDMA is a map onto the PVSB that is implemented in a  $256 \times 16$  SRAM. The SRAM registers are physically located on-board, but the map is loaded by writing registers in VME Short I/O space.

When the map is loaded, its registers allow any DMA bus master, including another cluster, to access a 256 Mbyte region of contiguous memory through a 1 Mbyte window in Standard I/O or through a 256 Mbyte window in extended I/O. Details on programming the map and illustrations of the mapping access of the VDMA are located in Section 2 in this manual.

## 1.9 Programming Devices on the PVSB

The PVSB is a local bus designed to off load main memory accesses from the global VMEbus. It has 32-bit multiplexed data and address lines and separate lines for bus arbitration and control. On the PVSB, the memory cards function as slaves. However, the cards do not provide full slave functionality, so all accesses from the MC68030 or remote VMEbus masters are arbitrated through VME-68K30 logic. Section 2 gives a complete description of the PVSB.

## 1.10 Resets

Microprocessor reset and System Bus reset are configurable for master or slave operation.

Each CPU board recognizes power on reset (POR), cluster reset, and VME reset. On-board stake pins allow for an optional push button reset.

VME-68K30 boards configured for master mode supply reset to the VMEbus as well as software resets.

Slaves pass bus reset to their CPU. Sources for the various resets on-board or from the bus are shown in Table 1-3.

**Table 1-3.** Reset Sources in Master and Slave Mode

| Reset Source           | Master | Slave             |

|------------------------|--------|-------------------|

| Power on Reset         | yes    | yes               |

| VME Reset              | yes    | yes               |

| Push Button Stake Pins | yes    | yes               |

| Generate VME Reset     | yes    | no                |

| CPU HALT               | option | option            |

| Cluster                | yes    | yes               |

| Software Generated     | yes    | yes<br>(not used) |

After a reset, the sequence of operations is as follows:

1. EPROM is enabled

2. The MC68030 fetches the initial SSP and PC from location 0000 0000.

3. The OCTART, sio, and baud rate are checked and initialized. This includes printing the ISI logo to the console screen with such SRAM contents as version number, CPU operating speed, and PVS or VSB memory type.

4. Memory is probed and configured which includes printing the size of configured memory to the screen.

5. EPROM contents are copied into RAM duplicate space.

6. Program execution jumps into duplicate space, which transfers EPROM execution to PVS DRAM.

7. Normally EPROM is disabled at this point and UNIX is booted. However, if the on-board switches have been set for extended diagnostic testing, the diagnostics run out of duplicate space. (See Sections 5 and 6 to set the board for diagnostic options.)

## 1.11 Indicators

- DS1 CPU HALT indicator (puce)

- DS2 VMEbus Slave indicator (yellow)

- DS3 VMEbus Master indicator (green)

- DS4 VSYSFAIL indicator

- DS5 Diagnostic code

- DS6 Diagnostic code

- DS7 Diagnostic code

The diagnostic codes are described in Section 6.

## Section 2: High Performance PVSB

### 2.1 Introduction

PVSB<sup>†</sup> memory cards provides up to 64 Mbytes of main memory for a VME-68K30 processor. The memory cards are populated with 4, 8, or 16 Mbytes of high speed DRAM. In a multiprocessor installation, all memory cards can be accessed by any DMA device or any cluster in the installation. The relation between four VME-68K30s and their PVSB memory boards to the VMEbus is shown in Figure 2-1.

### 2.2 PVSB Features

- 32 multiplexed address and data lines (AD31-0)

- Proprietary subset of *standard* VSB signals

- Block transfers into ISI defined space<sup>††</sup>

- Supports 256 Mbyte addressing range (A27-0)

- Supports direct and virtual DMA from other VMEbus masters

Figure 2-1. Clusters and PVSB Memory Boards

0284-00

<sup>†</sup> PVSB stands for the high Performance VSB bus and memory cards that are proprietary to ISI. ISI memory cards can only be used on the PVSB bus. The bus does not support other types of VSB cards.

<sup>††</sup> While the MC68030 does not support block transfers, hardware modules on the VME-68K30 and PVSB 8/16 M boards make transfers appear to be in block mode for DMA devices on the VMEbus.

## 2.3 The VME-68K30 as PVSB Master

Viewed from the VME-68K30, the PVSB is a local bus with one function: it offloads high-speed memory accesses from the global VMEbus.

Since the PVSB is dedicated to high speed memory, access is streamlined and memory cards do not require full slave functionality. By eliminating complicated handshaking protocols the PVSB reduces access time and enhances system performance. Functional modules such as bus grant/request are not needed since the VME-68K30 is the only master. Wait states are not needed because the processor knows the memory timing cycle. Interrupts are limited to one signal (IRQ\*) that indicates a parity error.

The VME-68K30 identifies memory boards by slot position on the PVSB. The position of each board is set by geographical address jumpers (GA0-2) and cannot be overridden by software.

Devices on the VMEbus identify and access memory boards directly by the cluster number of their associated processor or through the VDMA map on the VME-68K30. The remainder of this section describes how a cluster accesses its own PVSB memory and how a DMA device on the VME, which includes another cluster, can access all available DRAM memory in a cluster configuration.

### 2.3.1 Functional Modules

Functional modules implemented on the VME-68K30 to access the PVSB include a bus arbiter with prioritized refresh, a bus control module, and an address translation map (VDMA).

### 2.3.2 PVSB Arbitration

In order of descending priority, arbitration between the processor and other VMEbus masters for PVSB access is resolved as follows:

1. A VME-68K30 generated refresh cycle

2. VME-68K30 access

3. Access from a VMEbus master while the VME-68K30 is in slave mode

The refresh cycle is interleaved between each processor or bus master access, as well as being guaranteed access when the refresh timer has timed out.

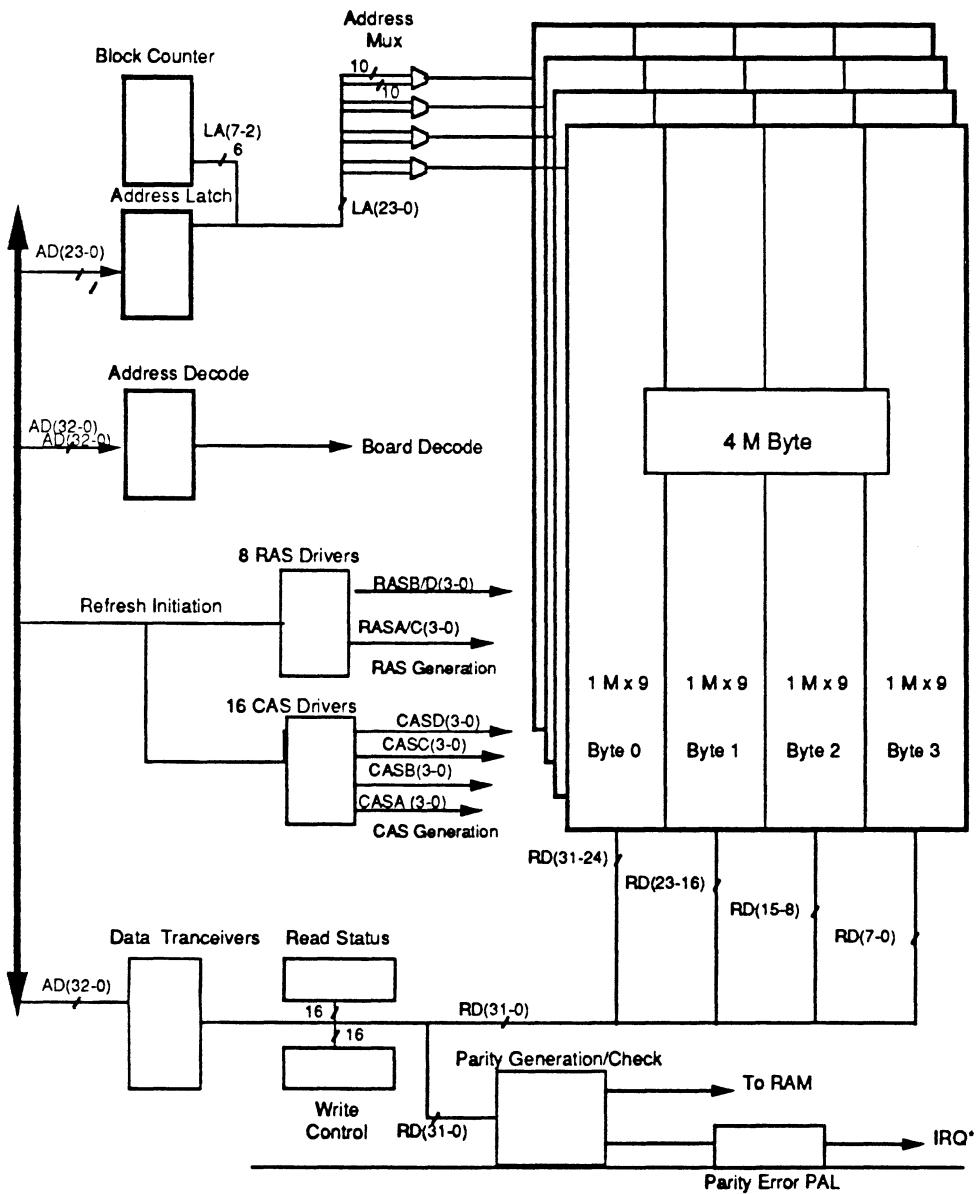

A block diagram of the functional modules on the PVSB-8/16 MB memory board is shown in Figure 2-2.

Figure 2-2. Block Diagram of PVSB Memory Board

### 2.3.3 Address Lines and Control Signals

The VME-68K30 implements the following subset of VSB address lines and control signals for the PVSB.

**AD00-AD31** Address/Data Lines. The AD02-AD31 lines determine the address of a long word in memory. Lines AD0-AD1 determine byte position. SIZE0-1 signals determine the number of bytes

| Byte Accessed | AD01 | AD00 |

|---------------|------|------|

| Byte 0        | low  | low  |

| Byte 1        | low  | high |

| Byte 2        | high | low  |

| Byte 3        | high | high |

**BG3-0**

Since the PVSB is dedicated to high speed memory, bus request and grant protocols required to accommodate a variety of bus slaves and masters were eliminated in favor of faster memory access. Memory boards simply decode their address from AD31-0.

**SPACE0-1**

In ISI defined space accesses to address range 8000 0000 to BFFF FFFF are detected by hardware that generates the SPACE0-1 codes. These in turn select one of four address regions on the PVSB:

| SPACE0 | SPACE1 | 256 Mbyte Block Access             |

|--------|--------|------------------------------------|

| 0      | 0      | Interrupt Acknowledge (not used)   |

| 0      | 1      | Block Transfer (not used)          |

| 1      | 0      | I/O Space (memory board addresses) |

| 1      | 1      | System Space                       |

**SIZE1-0**

SIZE1-0 codes are used in conjunction with address and data lines A0-1 to determine the size and position of byte transfers. Size codes specify a one to four byte transfer. Byte locations in storage must be consecutive. The SIZE and A1-0 codes are decoded from the DS0-1\* and A1\* lines of the MC68030.

| Data Type   | Size1 | Size0 | Address Space Location |       |       |       |

|-------------|-------|-------|------------------------|-------|-------|-------|

|             |       |       | Data0                  | Data1 | Data2 | Data3 |

| Quad Byte   | 0     | 0     |                        |       |       |       |

| Triple Byte | 1     | 1     |                        | Data1 | Data2 | Data3 |

| Double Byte | 1     | 0     |                        |       | Data2 | Data3 |

| Single Byte | 0     | 1     |                        |       |       | Data3 |

**ASACK0-1**

**Not used.** The PVSB generates \*ACK for all accesses.

**GA2-0**

Jumpers set the geographical address on each memory board. The board recognizes its address when decode logic compares registers containing GA2-0 settings with address lines AD23-16.

**Control Lines****PAS\***

The VME-68K30 drives the physical address strobe (PAS) low to start the address broadcast phase of a PVSB cycle. It remains low during the cycle. In response, the card drives ACK low when it has captured an address.

To end a cycle, the master drives PAS high, and the slave responds by driving its ASACK signal high.

**AC**

**Not implemented** The Address decode Complete (AC) signal used with WAIT allows the slave to prolong the address broadcast phase to fit their decode timing.

|        |                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WR*    | The processor drives the WR* line during the address broadcast phase to inform slave memory boards of the direction of data transfer. WR* is high when the processor retrieves data from the responding slave and low when the processor writes to the responding board.                                                                                                            |

| LOCK*  | The LOCK signal on the ISI implementation of the VSB generates a REFRESH signal on the memory board that inhibits its address latches and thus prevents the board from being accessed when DRAM is being refreshed.                                                                                                                                                                 |

| DS*    | The processor drives DS* low to indicate to the selected slave board that the address broadcast phase is complete and that the data transfer phase is in progress.                                                                                                                                                                                                                  |

| WAIT*  | <b>Not implemented</b> This signal allows boards with different response times to force a bus master to wait until the slave responds to an access. With a dedicated PVSB, the signal is not required.                                                                                                                                                                              |

| ACK*   | During write cycles, the memory drives ACK* low to inform the processor that it has captured the data on AD31-AD00. During read cycles the responding memory board drives ACK* low to inform the processor that valid data has been placed on all or some of the address/data lines. The processor monitors the falling edge of the ACK* signal for the completion of either cycle. |

| ERR*   | <b>Not implemented</b> The ERR* signal is not required for parity errors. IRQ* is reserved for that function.                                                                                                                                                                                                                                                                       |

| IRQ*   | The memory board drives IRQ* low to generate an interrupt to the processor, and the processor responds by polling each board to find parity error information. In the ISI implementation of the PVSB, this is the only function of IRQ*.                                                                                                                                            |

| CACHE* | <b>Not Implemented</b>                                                                                                                                                                                                                                                                                                                                                              |

## 2.4 PVSB Initialization

On power up, the VME-68K30 CPU masks all interrupts and goes into supervisory mode. To access and initialize the memory boards, it sets the function code to 3. It then enables the internal cache and checks the status of main memory on the PVSB.

PVSB memory before initialization is shown in Figure 2-3.

Figure 2-3. PVSB Address Space Before Initialization

**NOTE**

In Figure 2-3, AX is Address Translation, IF is Interface, SRAM is Static RAM, and EPROM is Erasable Read Only Memory.

## 2.5 ISI Defined Space

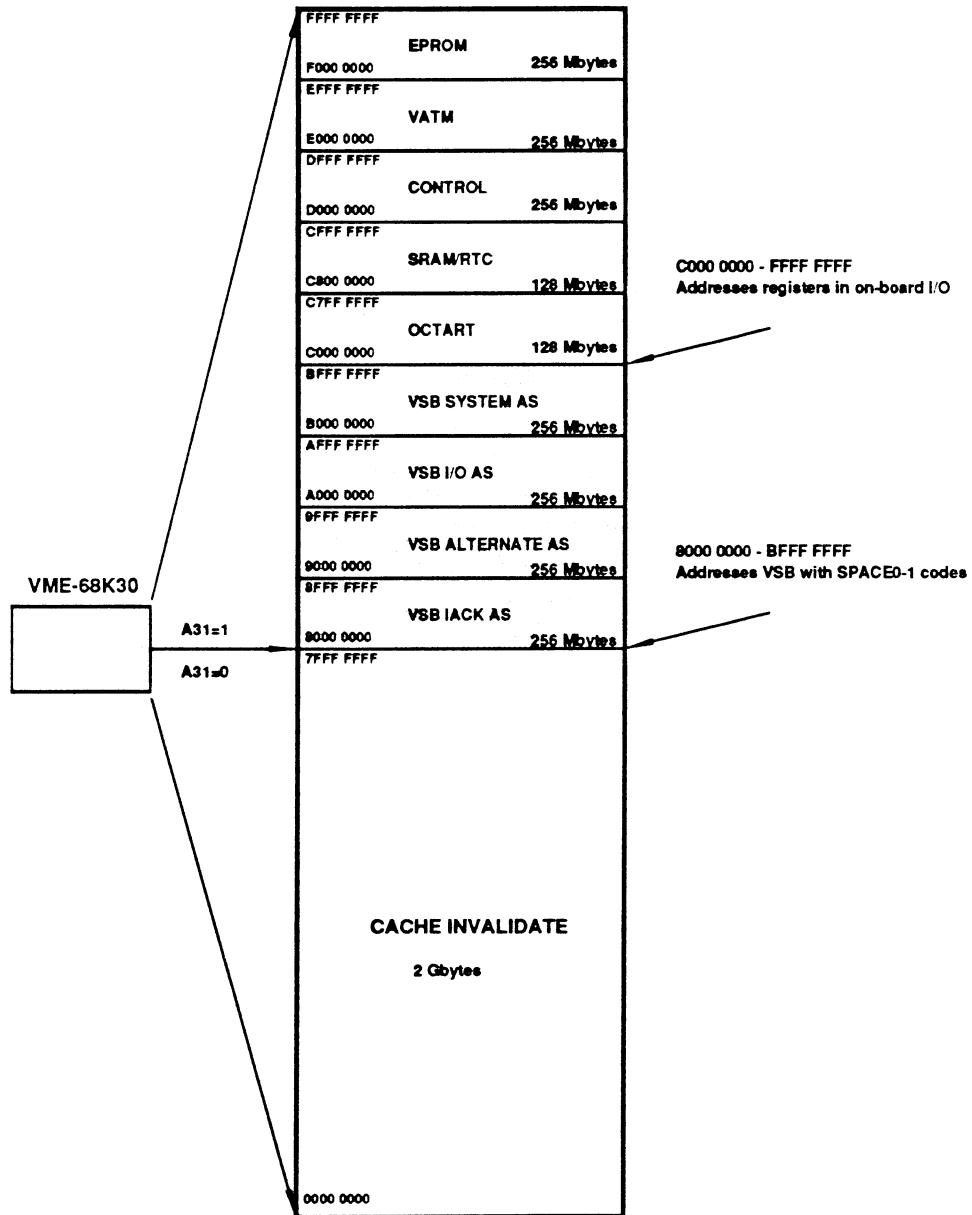

ISI defined space includes PVSB I/O space, local I/O space, and cache invalidate space. These regions are accessed when the function code in the MC68030 is set to 3 (FC=3). If A31=0 and the function code is 3, cache invalidate space is accessed. Any write to this space will invalidate all four corresponding entries in a cached line. This is the only time an entire line rather than a single valid entry is invalidated. Cache invalidate space is shown in Figure 2-4.

If A31=0 and the CPU accesses ISI defined space in the address range 8000 0000—BFFF FFFF, the access is to one of four contiguous memory blocks on the PVSB. If the access is to C000 000—FFFF FFFF, the access is to local I/O devices that are programmed on the PVSB.

The four contiguous memory blocks are defined as follows:

1. ADDRESS SPACE R/W 8000 0000 - 8FFF FFFF

IACK space is not used by the VME-68K30

2. ADDRESS SPACE R/W 9000 0000 - 9FFF FFFF<sup>†</sup>

Alternate space is not used by the VME-68K30.

3. I/O ADDRESS SPACE R/W A000 0000 - AFFF FFFF

I/O address space is used by the CPU to set parameters on the PVSB boards. The write control and read status registers for each memory board are located in this space.

4. SYSTEM ADDRESS SPACE R/W B000 0000 - BFFF FFFF

The system address space stores user and supervisory programs and data.

The standard VSB SPACE0-1 codes are generated in hardware when addresses in the range 8000 0000—BFFF FFF are detected. The PVSB interprets SPACE0-1 codes as shown in Table 2-1.

**Table 2-1. SPACE1-0 Code Interpretation**

| SPACE0 | SPACE1 | Access Space                    |

|--------|--------|---------------------------------|

| 0      | 0      | Not used by the VME-68K30       |

| 0      | 1      | Not used by VME-68K30           |

| 1      | 0      | I/O Address Space (PVSB I/OAS)  |

| 1      | 1      | System Address Space (PVSB SAS) |

As shown in Figure 2-4, I/O address space is a 256 Mbyte region that begins at A000 0000 and extends to AFFF FFFF. The bottom 8 Mbytes of this region are reserved for memory board addresses.

<sup>†</sup> Alternate address space within the ISI defined region is reserved for block transfers. The MC68030 does not support block transfers, but accepts them from VMEbus masters, so it appears to support them.

Within the 8 Mbyte region reserved for board addresses, memory boards reside on one of eight possible 64 Kbyte boundaries. The total address space reserved for boards is 512 Kbytes (64K x 8), but due to electrical limitations on the backplane, only four memory boards are allowed with each processor.

Figure 2-4. ISI Defined Space on the PVSB

## 2.6 Memory Board Initialization

On the PVSB, each board recognizes that it is being accessed through address decode logic. The logic compares PVSB address/data lines AD23-16 to on-board geographic address jumpers (GA2-0). The jumpers are set during hardware configuration and cannot be overridden by software.

While the VME-68K30 probes memory boards, it displays the a message similar to the following on the screen:

```

Probe and configure PVSB memory

A00N 0000 0000 000Y

A00N+1 0000 0000 000Y

A00N+2 0000 0000 000Y

```

The slot number is designated *N* in the display. The processor looks for 16 Mbyte cards first, 8 Mbyte cards next, and 4 Mbyte cards last. Since cards can be placed in any slot position, the first 16 Mbyte card that the CPU finds may not be in slot one, but it will be the first slot displayed. The total memory found on each card is displayed in the position designated by *Y* in the example. Memory is counted in 4 Mbyte units so a 16 Mbyte card would be shown with a 3 (0-3 units) in the *Y* position. In the example, three lines are displayed which tells you three slots have been found with memory cards.

The initialization message concludes with a line that indicates memory is initialized. A dot is displayed for each 4 Mbyte unit located.

Initialize all memory.....

A status and control register is located on each memory board addressing boundary. As the CPU polls through each status register it determines whether a memory card is present. If a slot does not respond, the processor assumes the slot is empty. If a card is present, the CPU determines how much memory it contains.

The location of the registers on each board is shown in Table 2-2.

**Table 2-2. Memory Board I/O: SPACE0-1 = (10<sub>b</sub>)**

| Register      | # Bytes | R/W | Addresses | Range Reserved        |

|---------------|---------|-----|-----------|-----------------------|

| Write Control | 64K     | W   | XX0Z 0000 | XX0Z 0000 - XX0Z FFFF |

| Read Status   | 64K     | R   | XX0Z 0000 | XX0Z 0000 - XX0Z FFFF |

| Full Range    | 512K    | R/W | NA        | XX00 0000 - XX07 FFFF |

In Table 2-1, the actual value of *Z* for each memory board is determined by geographic addressing jumpers GA2-0. Values of "Z" range from 0-7.

### 2.6.1 Status Register

The bit assignments for the status register on each memory board are shown in Figure 2-5. The register is read only and one word wide.

| Bit # | 15       | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5   | 4   | 3  | 2   | 1  | 0  |                  |

|-------|----------|----|----|----|----|----|---|---|---|---|-----|-----|----|-----|----|----|------------------|

|       | Board ID |    |    |    |    |    |   |   |   |   | RS1 | RS0 | PE | EBT | MG | MB | PEB <sub>n</sub> |

**Figure 2-5. PVSB Memory Board Status Register (Read Only)**

The upper byte of the status register identifies the board as a PVSB memory board and indicates the amount of on board DRAM.

**ID** Bits D15-10 are always set low to identify the board in this slot as PVSB memory.

**RS0-1** These two bits show the presence of 4, 8 or 16 Mbytes of DRAM. The bits are set by jumper E-7 and interpreted as follows:

| Size | RS1 | RS0 | Total Memory          |

|------|-----|-----|-----------------------|

| 0    | 0   | 0   | 4 Mbyte DRAM, 1M x 1  |

| 1    | 0   | 1   | 8 Mbyte DRAM, 1M x 1  |

| 2    | 1   | 1   | 16 Mbyte DRAM, 1M x 1 |

The lower byte in the status register provides parity error information. A parity error is signaled by IRQ\* on the PVSB and results in a level 7 interrupt on the VME-68K30. Reading the lower byte of the control status registers on the PVSB identifies the board that produced the error and the group, bank, and byte which caused it. Parity must be disabled and re-enabled by software to remove the IRQ assertion. The group, bank, and byte location of an error is sufficient to identify which zig-zag inline package (ZIP) caused the error.

**PE** Parity Enable, indicates whether parity has been set.

**EBT** Error Block Transfer, indicates a block or byte transfer was in progress.

**MG** Memory Group, indicates the group in which the error occurred.

**MG** Memory Bank, indicates the bank in which the error occurred. The memory group (MG) and memory bank (MB) bits are interpreted as follows:

| Memory Group | Bank | Offset Memory Bank | 1M x 1 DRAM |

|--------------|------|--------------------|-------------|

| 0            | 0    | A                  | xx0x xxxx   |

| 0            | 1    | B                  | xx4x xxxx   |

| 1            | 0    | C                  | xx8x xxxx   |

| 1            | 1    | D                  | xxCx xxxx   |

**PEB3** Indicates a Parity Error in Byte 3 (D7-0). Active low.

**PEB2** Indicates a Parity Error in Byte 2 (D15-8). Active low.

**PEB1** Indicates a Parity Error in Byte 1 (D23-16) Active low.

**PEB0** Indicates a Parity Error in Byte 0 (D31-24). Active low.

## 2.6.2 Write Control Register in PVSB I/O

The write control register indicates both the 16 MB address range which the board will decode and the offset within that range where decoding will begin. The offset is restricted to the size of RAM available.

Bit assignments for the 16 bit control register on each memory board are shown in Figure 2-6. CPU bit assignments refer to MC68030 internal register bits. The CPU bits are stored as D15-8 in the memory board register as shown. The register is one word wide. It is cleared on VME Reset.

| CPU Bit # | 31     | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19                  | 18  | 17 | 16 |

|-----------|--------|----|----|----|----|----|----|----|----|----|----|----|---------------------|-----|----|----|

| Reg Bit # | 15     | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3                   | 2   | 1  | 0  |

| PE        | Unused |    |    |    |    |    |    |    |    |    |    |    | Base Address (Megs) | BOA |    |    |

Figure 2-6. PVSB Control/Status Register Write

|              |                                                                                                                                                                                                                                                                                                           |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PE           | Parity is enabled by setting the most significant bit (#15) in this register.                                                                                                                                                                                                                             |

| Unused       | Control bits 14-10 have no assigned function.                                                                                                                                                                                                                                                             |

| Base Address | The base address of each PVSB memory board is set on a 4 Mbyte boundary starting with 0000 0000. Boards are cumulative for each processor. As an example, if two 16 Mbyte boards are installed with a processor, the address of the first would be set to 0, the address of the second would be set to 4. |

| BOA          | The base offset address bits are interpreted as shown. PVSB address bits A/D 31-24 are compared with BS1-0 bits to decode a 16M range.                                                                                                                                                                    |

| Base | BS1 | BS0 | Base Offset Address |

|------|-----|-----|---------------------|

| 0    | 0   | 0   | XX00 0000           |

| 1    | 0   | 1   | XX40 0000           |

| 2    | 1   | 0   | XX80 0000           |

| 3    | 1   | 1   | XXC0 0000           |

Note: The eight bit pattern stored in register bits 9-2 is represented by XX.

Firmware on each memory card writes the amount of on-board memory into BOA1-0. The CPU reads the value for each card and keeps a cumulative count of all memory present. Each card is recorded on the boundary reached by the highest address of the last card read, so all cards have contiguous addressing in PVSB.

## 2.7 Initialized PVSB Address Space

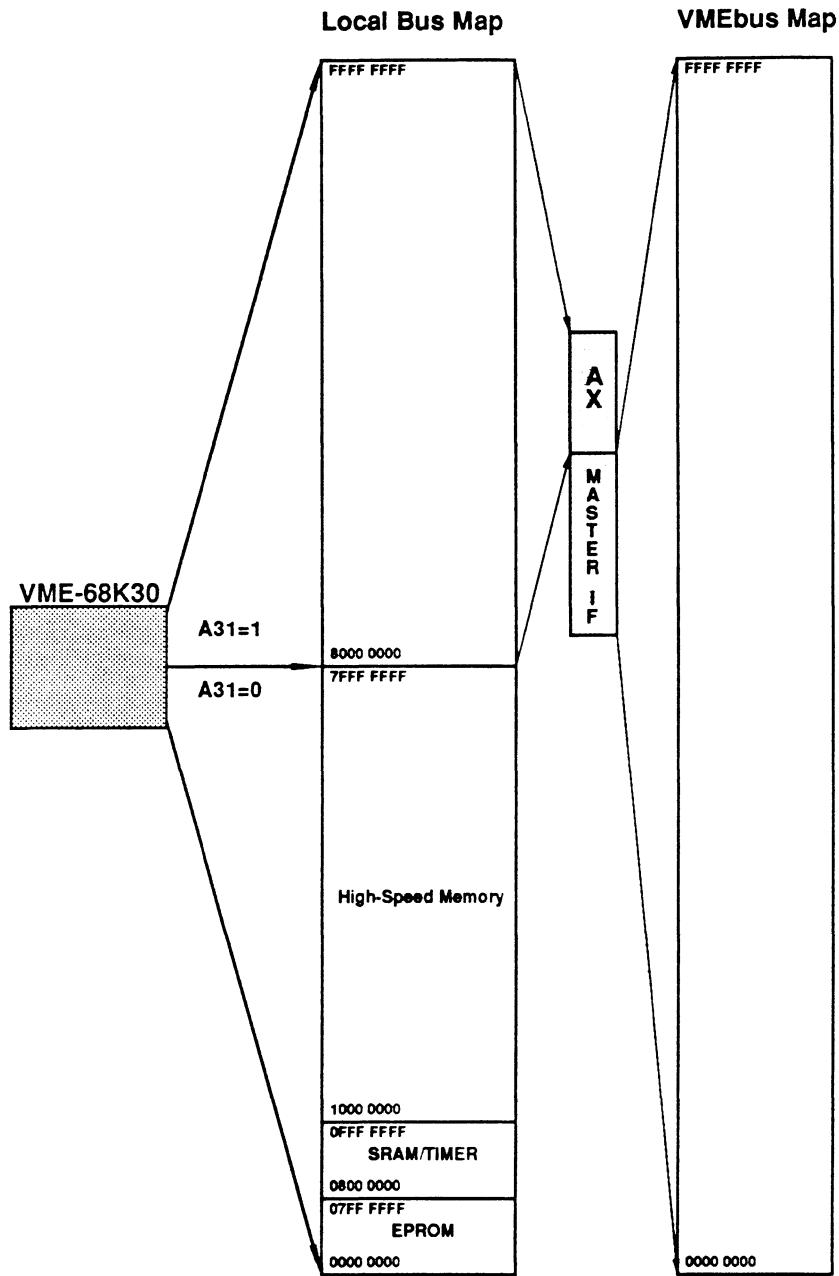

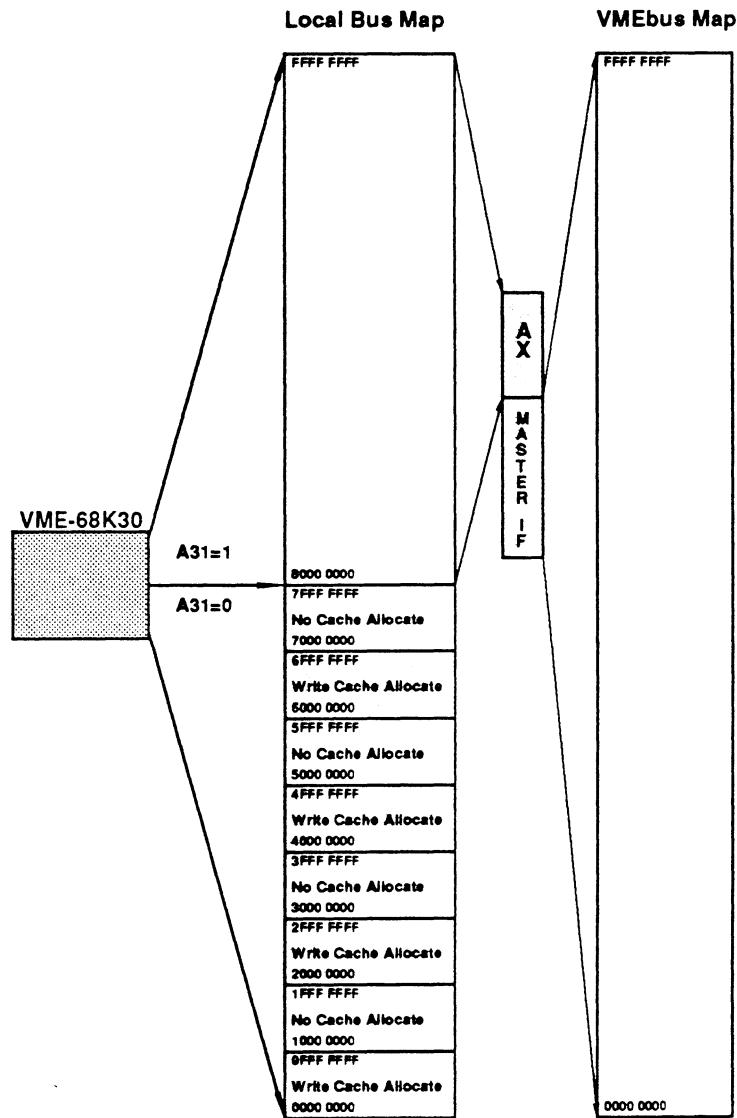

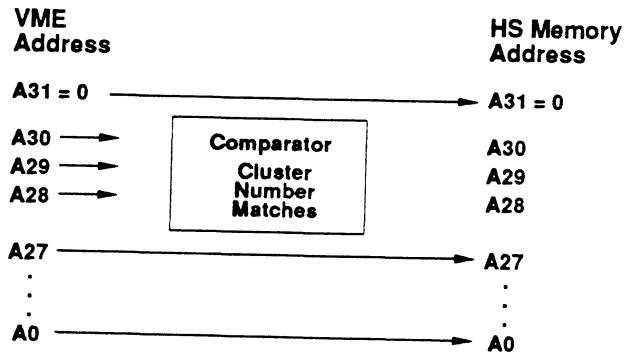

Figure 2-7 shows PVSB space (0000 0000 to 7FFF FFFF), the space accessed after memory initialization is complete and function codes are set to 1, 2, 5 or 6.

## 2.8 System Space: FC=1,3,5, and 6

The MC68030 uses ISI Defined Space for I/O activity. System space is reserved for user and supervisory data and programs, and is shown in Figure 2-7. System Space is divided into eight 256 Mbyte blocks as shown, and the blocks alternate between allocate and no-allocate writes to cache. The differences are defined as follows.

- **Write allocate.** When hardware on the VME-68K30 detects an access to an address in write allocate space, the cache is updated regardless if it contained an entry before or not, and regardless of the state of that entry.

- **No-write allocate.** When hardware on the VME-68K30 detects an access to this space it updates the cache only if a previous entry existed in the cache for this space, otherwise not.

**Figure 2-7. PVSB Address Space After Initialization**

## 2.9 PVSB Access

After initialization VME-68K30 accesses to PVSB memory occur under two conditions. The first is when A31=1 and the Motorola function code is three (FC=3). The second is when A31=0 and the function code is 2, 3, 5, or 6. The settings of function codes and A31 are summarized in Table 2-3.

**Table 2-3. PVSB Addressing Modes**

| VME-68K30 Accesses          |             |               |                                        |

|-----------------------------|-------------|---------------|----------------------------------------|

| Bus I/D                     | Cluster I/D | Function Code | Address Description                    |

| A31=1                       | —           | FC=3          | ISI Defined Address Space              |

| A31=0                       | —           | FC=1, 2, 5, 6 | System Address Space                   |

| Virtual DMA (VDMA) Accesses |             |               |                                        |

| A31=0                       | A22-20      | FC=1, 2, 5, 6 | Virtual VMEbus Standard Address access |

| A31=0                       | A30-28      | FC=1, 2, 5, 6 | Virtual VMEbus Extended Address access |

| A31=0                       | A30-28      | FC=1, 2, 5, 6 | Direct Extended Address access         |

Details on virtual and direct accessing into the PVSB are given in Section 3 which discusses VME-68K30 addressing space.

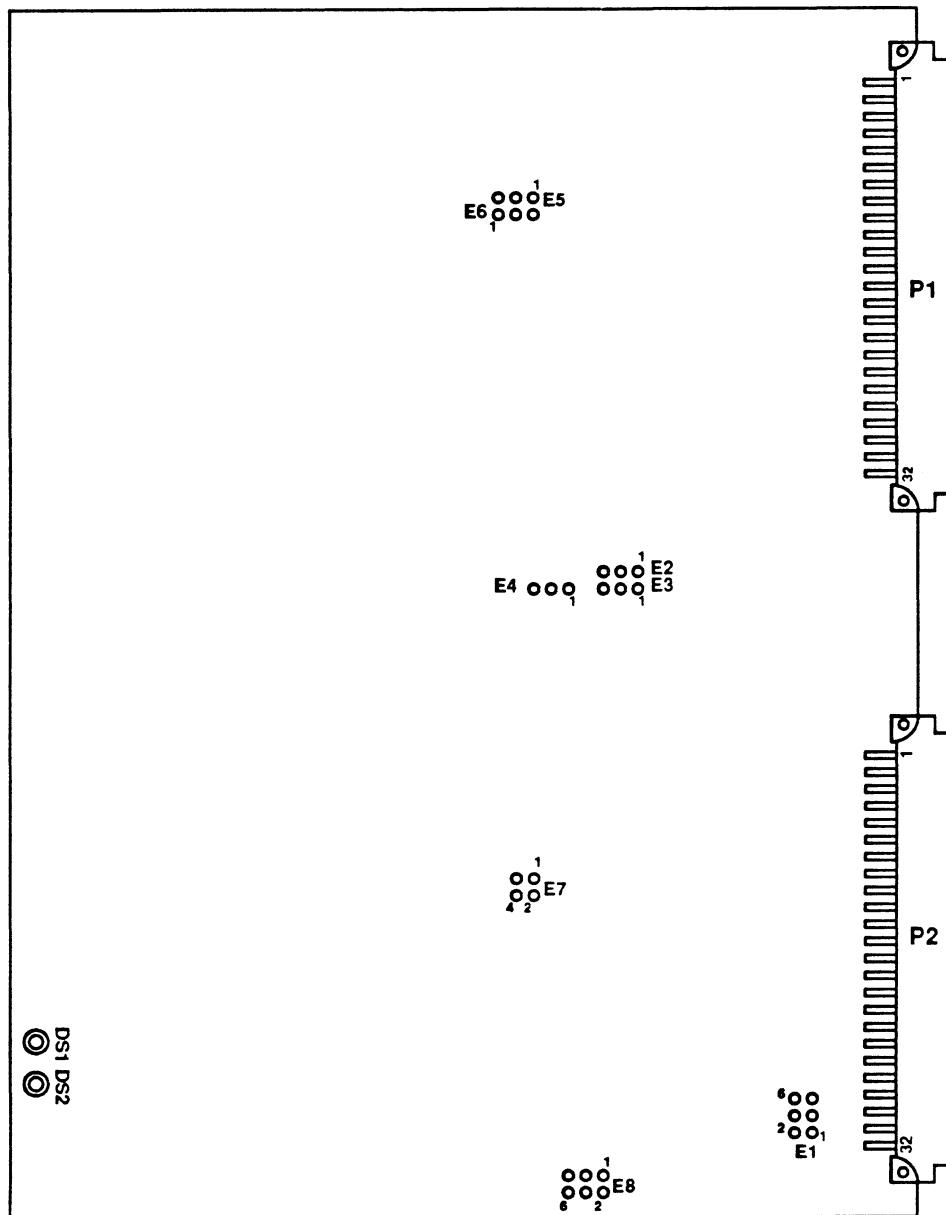

## 2.10 PVSB Configuration

As shown in Figure 2-8, there are eight jumper sets that configure the PVSB memory board. For quick reference, they and their functions are listed in Table 2-4.

Figure 2-8. PVSB Memory Board Jumper Positions

**Table 2-4.** Jumper Descriptions

| Jumper | Function                                                                                                                                                                                                       |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E1     | Connects the GA2-0 address lines from the PVSB to on board registers. Leave open in all ISI installation using the VME-68K30 designed for PVSB memory cards. <b>Interleaves memory banks A and C, B and D.</b> |

| E2-E3  | <b>Identifies whether one or more than one memory banks is installed on a board.</b>                                                                                                                           |

| E4     | <b>Sets RAS precharge and refresh cycle lengths.</b>                                                                                                                                                           |

| E5-E6  | <b>Set the available on-board RAM in 4 Mbyte increments.</b>                                                                                                                                                   |

| E7     | The I/O base address jumpers are used instead of the GA2-0 signal lines                                                                                                                                        |

| E8     | from the PVSB to set the board base address when the memory board is used with the VME-68K30.                                                                                                                  |

**2.10.1 E1: GA2-0 Input Enable**

Leave E1 unjumpered when using the VSB-8/16MB memory boards with the VME-68K30 processor, as shown in Table 2-5. Defaults are shown in **boldface**.

**Table 2-5.** E1: GA2-0 Input Enable

| Signal | Jumper        |

|--------|---------------|

| GA2    | <b>E1 out</b> |

| GA1    | <b>E1 out</b> |

| GA0    | <b>E1 out</b> |

**2.10.2 E2-E3: Bank Interleave**

Interleaving high-speed memory alternates memory bank access which allows memory access to one bank while the other is in a precharge refresh cycle. Each bank consists of 4 Mbytes of memory. Banks are installed to create boards of 4, 8 or 16 Mbytes capacity. Only the 8 and 16 Mbyte boards are interleaved. Since a 4 Mbyte board has only one bank of memory it can not be interleaved. The VME-68K30 runs interleaved memory at the same speed as a non-interleaved memory in current versions so interleaving does not improve access time. Set jumpers E2 and E3 according to the population of your VSB-8/16MB as shown in Table 2-6.

**Table 2-6.** E2-E3 Bank Interleaving

| E2  | E3  | Description                   |

|-----|-----|-------------------------------|

| 1-2 | 1-2 | 2 or 4 Banks - Interleave     |

| 1-2 | 2-3 | Not Valid                     |

| 2-3 | 1-2 | Not Valid                     |

| 2-3 | 2-3 | <b>1 Bank - No Interleave</b> |

### 2.10.3 E4: Number of Banks

The VSB-8/16MB will have one or more 4 Mbyte banks of memory. Set jumper E4 to identify whether there are one or more banks on board as shown in Table 2-7.

**Table 2-7. E4: Number of Banks**

| Number of Banks    | Jumper |     |

|--------------------|--------|-----|

| More than one bank | E4     | 1-2 |

| Only one bank      | E4     | 3-4 |

The RAM size jumpers (E-7) must correspond to the E4 setting when there are one or more than one banks installed.

### 2.10.4 E5-E6: Refresh Cycle Length

Table 2-8 shows jumper settings for E5 and E6 that match the refresh cycle length to the DRAMs used. 100  $\eta$ s DRAMs, used with a 25 MHz machine, and 120  $\eta$ s DRAMs are used with a 20 MHz machine. The refresh cycle is set by E-5 for memory banks B and D. Memory banks A and C are set by E-6. All boards should be set to a 100  $\eta$ s delay since slower delay times give unexpected results, even with the fastest DRAM available.

**Table 2-8. Refresh Cycle Length**

| Jumper | Pin | Delay        |

|--------|-----|--------------|

| E5     | 1-2 | 80 $\eta$ s  |

|        | 2-3 | 100 $\eta$ s |

| E6     | 1-2 | 80 $\eta$ s  |

|        | 2-3 | 100 $\eta$ s |

### 2.10.5 E7: RAM Size

Set E7 jumpers as shown in Table 2-9 to indicate the amount of on-board RAM available. The ISI processor board reads these jumpers out of the status register on each board, then determines how much total memory is available on the PVSB.

**Table 2-9. E7: RAM Size**

| E7  | E7  | Size | Total Memory |

|-----|-----|------|--------------|

| 1-2 | 3-4 |      |              |

| in  | in  | 0    | 4 Mbyte      |

| in  | out | 1    | 8 Mbyte      |

| out | out | 3    | 16 Mbyte     |

### 2.10.6 E8: Base Address on PVSB

Each card recognizes its address on the PVSB by the settings of base address jumpers E8 1-6. Address ranges are described in Table 2-10.

The lower 8 Mbytes of PVSB I/O space is used for board identification and configuration. Jumpers GA2-0 set the base address on a 64 Kbyte boundary. If a location does not respond during initialization, the processor assumes that the slot is empty or contains a board without slave functionality. The default is to have at least one memory board.

**Table 2-10.** Base Address on PVSB

| GA2 | GA1 | GA0 | PVSB Slot | Address Range for the VME-68K30 |         |                   |

|-----|-----|-----|-----------|---------------------------------|---------|-------------------|