# ISBC™ 464 PROM/ROM BOARD HARDWARE REFERENCE MANUAL

Order Number: 9800643-02

| REV. | REVISION HISTORY                                                                                                                                                                                           | PRINT<br>DATE |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| A    | Original Issue                                                                                                                                                                                             | 10/78         |

| 02   | Product revision: all switches converted to jumper configurations. Manual revisions: All switch references converted to equivalent jumper post numbering. New Service Assistance information in Chapter 4. | 10/81         |

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The Information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined as ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| BXP            | Insite             | iSBC            | Multibus      |

|----------------|--------------------|-----------------|---------------|

| CREDIT         | Intel              | iSBX            | Multimodule   |

| i              | int <sub>e</sub> l | Library Manager | Plug-A-Bubble |

| ICE            | Intelevision       | MCS             | PROMPT        |

| iCS            | Intellec           | Megachassis     | RMX/80        |

| <sup>i</sup> m | iOSP               | Micromainframe  | System 2000   |

| iMMX           | iRMX               | Micromap        | UPI           |

## PREFACE

This manual provides general information, installation instructions, principles of operation, and service information for the iSBC 464 PROM/ROM Memory Expansion Board. Additional information is available in the following publications:

| Manual                                                 | Number  |

|--------------------------------------------------------|---------|

| Intel iSBC™ 604/614 Cardcage Hardware Reference Manual | 9800708 |

| Intel Multibus Specification                           | 9800683 |

| Intel Component Data Catalog                           |         |

| Intel System Data Catalog                              |         |

| iSBC™ Application Manual                               |         |

|   |  | <br> | <br> |

|---|--|------|------|

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      | •    |

|   |  |      | £    |

|   |  |      | •    |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

| • |  |      |      |

|   |  |      | •    |

|   |  |      |      |

|   |  |      | •    |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      |      |

|   |  |      | _    |

|   |  |      |      |

|   |  |      |      |

# CONTENTS

|                                                                     | PAGE |

|---------------------------------------------------------------------|------|

| ov ADMID 1                                                          |      |

| CHAPTER 1 GENERAL INFORMATION                                       |      |

| Introduction                                                        | 1-1  |

| Description                                                         |      |

| Documentation Supplied                                              | 1-2  |

| Board Specifications                                                | 1-2  |

|                                                                     |      |

| CHAPTER 2                                                           |      |

| PREPARATION FOR USE                                                 |      |

| Introduction                                                        | 2-1  |

| Unpacking and Inspection                                            |      |

| Installation Considerations                                         |      |

| Power Requirements                                                  |      |

| Multibus Interface Requirements                                     |      |

| Option Block Configurations                                         |      |

| PROM/ROM Device Select Option Blocks                                | 2-9  |

| Mode Select Option Blocks                                           |      |

| Jumper Configurations                                               |      |

| Base Address Select Jumpers  Memory Order And PROM/ROM Installation |      |

| Page Select Jumpers                                                 |      |

| Memory Access Time Jumpers                                          |      |

| RAM Overlap Jumpers                                                 |      |

| Comprehensive Setup Procedure                                       |      |

| Board Installation                                                  | 2-21 |

|                                                                     |      |

| CHAPTER 3                                                           |      |

| PRINCIPLES OF OPERATION                                             |      |

| Introduction                                                        |      |

| Functional Description Memory Array And Addressing                  |      |

| Chip Select                                                         |      |

| Control Logic                                                       |      |

| Base Address Select Logic                                           | 3-7  |

| Page Select Logic                                                   |      |

| Memory Data Paths                                                   | 3-8  |

|                                                                     |      |

| CHAPTER 4                                                           |      |

| SERVICE INFORMATION                                                 |      |

| Introduction                                                        |      |

| Replacement Parts                                                   |      |

| Service Diagrams                                                    |      |

| pervice and webatt wastatance                                       | 4-5  |

# CONTENTS (continued)

# FIGURES

| 1-1.<br>2-1.<br>2-2.<br>2-3.<br>2-4.<br>2-5.<br>3-1.<br>3-2.<br>3-3.<br>3-4.<br>4-1.<br>4-2.   | iSBC 464 PROM/ROM Board.  Bus Exchange Timing | 1-1<br>2-8<br>2-10<br>2-11<br>2-12<br>2-13<br>3-2<br>3-4<br>3-5<br>3-8<br>4-4<br>4-5 |

|------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------|

|                                                                                                | TABLES                                        |                                                                                      |

| 1-1.<br>2-1.<br>2-2.<br>2-3.<br>2-4.<br>2-5.<br>2-6.<br>2-7.<br>2-8.<br>2-9.<br>2-10.<br>2-11. | Specifications                                | 1-3 2-2 2-4 2-5 2-6 2-7 2-9 2-14 2-15 2-17 2-18                                      |

| 2-11.<br>2-12.<br>3-1.<br>4-1.<br>4-2.                                                         | Board Access Time Selection                   | 2-10<br>2-19<br>3-5<br>4-1<br>4-2                                                    |

#### CHAPTER 1. GENERAL INFORMATION

### 1-1. INTRODUCTION

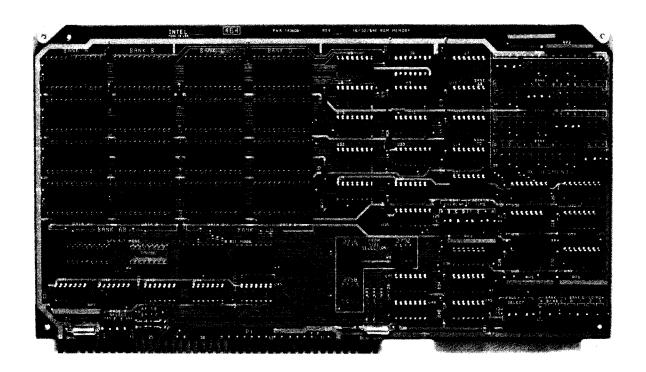

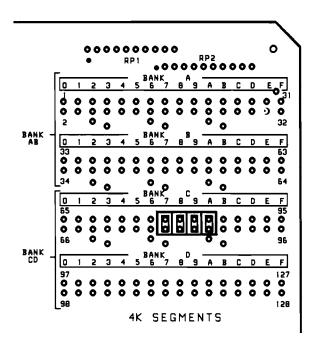

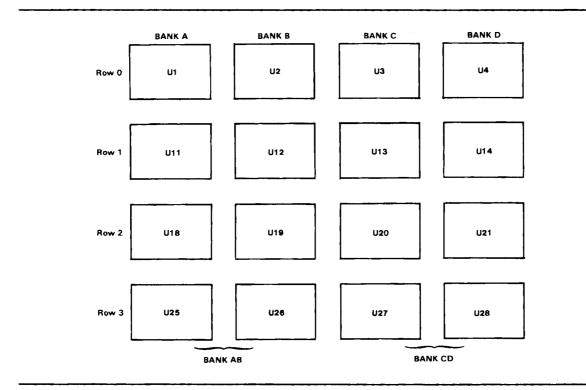

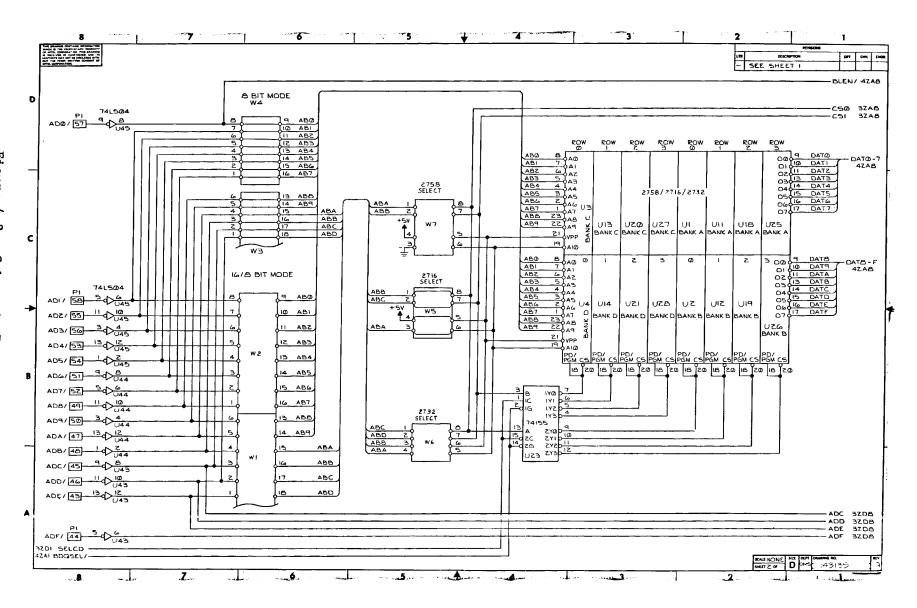

The iSBC 464 PROM/ROM Expansion Board is a member of Intel's complete line of iSBC memory and I/O expansion boards. The iSBC 464 board interfaces directly to any 8-bit or 16-bit iSBC Single Board Computer via the Multibus lines. Sixteen sockets provide up to 64K bytes of memory expansion (refer to Figure 1-1).

# 1-2. DESCRIPTION

The iSBC 464 board is designed to be plugged into a standard iSBC 604/614 Modular Backplane and Cardcage to interface with an Intel iSBC Single Board Computer, or with an Intel Intellec Microcomputer Development System.

Figure 1-1. iSBC 464 PROM/ROM Board

#### GENERAL INFORMATION

The iSBC 464 board memory capacity is determined by the size and quantity of PROM or ROM devices installed. The board may be operated in one of two modes, the 8-bit only mode or the 16/8-bit mode. The 16/8-bit mode allows 16-bit data to be accessed by both 16-bit and 8-bit processors, while the 8-bit mode generally provides more efficient memory usage in 8-bit only systems.

In addition to mode selection, the iSBC 464 board provides four other user selectable features, for optimum versatility: base address selection, page address assignment, RAM overlap indication, and access time selection. All of these features are implemented with push-on jumper connectors supplied with the board.

Base address selection refers to assigning a specific hexadecimal address range to each bank in the array. This address must reside on a 4K byte boundary. Page address selection permits assignment of the board memory to one or two of 16 possible 64K byte pages within a 1 megabyte address space. Each bank may then be assigned to one of the two pages, or divided between the two pages.

The RAM overlap feature is used to indicate whether or not a particular bank is overlapping system RAM (random access memory). The variable access time feature provides a means of setting the board response time, using current and future PROM/ROM devices.

All electrical connections are made through Multibus edge connector Pl. This connector (86 pins) plugs into the Multibus compatible iSBC 604/614 backplane, accommodating all power, address, data, and control lines. Connector P2 is not present on the iSBC 464 board.

### 1-3. DOCUMENTATION SUPPLIED

A schematic diagram is shipped with the iSBC 464 board. This diagram reflects the current revision level for the board you receive. Save the schematic diagram, by inserting it into the back of this manual. The diagram you receive with the board may be a newer version than the diagram presently in Chapter 4 of this manual.

# 1-4. BOARD SPECIFICATIONS

Board specifications are provided in Table 1-1.

### GENERAL INFORMATION

Table 1-1. Specifications

### MAXIMUM BOARD CAPACITY

|             | 8-Bit Mode | 16-Bit Mode |

|-------------|------------|-------------|

| 1K devices: | 16K bytes  | 8K words    |

| 2K devices: | 32K bytes  | 16K words   |

| 4K devices: | 64K bytes  | 32K words   |

#### BUS COMPATIBILITY

Interface: TTL compatible

Connector: 86-pin, doubled sided, P.C. edge connector with 3.96 mm

(0.156 inch) contact centers.

#### ADDRESS SELECTION

Base address on a 4K byte boundary for each bank except 4K PROMS in 16/18 bit mode (8K boundary).

#### PHYSICAL CHARACTERISTICS

30.48 cm (12 inches) Length: Width: 17.15 cm (6.75 inches)

Thickness: 1.27 cm (0.5 inch)

Weight: 294 grams (10.5 ounces) without PROM/ROMs

# POWER REQUIREMENTS

V<sub>cc</sub>: 5 volts dc +5%

1.1 Amps without PROM/ROMs

1.6 Amps with sixteen 2716 or 2758 type devices

I<sub>cc</sub>:

I<sub>cc</sub>:

I<sub>cc</sub>: 1.3 Amps with sixteen 2732 type devices 3.0 Amps with sixteen 2316E type devices

# HEAT DISSIPATION

| Icc  | Watts | gmcal/min | BTU/min | Device Type   |

|------|-------|-----------|---------|---------------|

|      |       |           |         |               |

| 1.10 | 5.5   | 78.3      | 0.317   | Without PROMs |

| 1.60 | 8     | 113.9     | 0.461   | 16 2716/2758  |

| 1.30 | 6.5   | 92.5      | 0.374   | 16 2732       |

| 3.00 | 15    | 213.5     | 0.864   | 16 2316E      |

| ļ.   |       |           |         |               |

### ENVIRONMENTAL REQUIREMENTS

0° to 55°C (32° to 131°F) Operating Temperature: Relative Humidity Limits: <90%, non-condensing

#### CHAPTER 2. PREPARATION FOR USE

# 2-1. INTRODUCTION

This chapter provides instructions for installing the iSBC 464 board into your system. This information includes unpacking information, power and cooling requirements, bus interface requirements, jumper configurations and a summary of setup instructions.

### 2-2. UNPACKING AND INSPECTION

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or waterstained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is not present when the carton is opened and the contents are damaged, keep the carton and packing material for the agent's inspection.

For repairs to a product damaged in shipment contact the Intel Product Service HOTLINE to obtain a return authorization number and further instructions (see section 4-4). A purchase order will be required to complete the repair. A copy of the purchase order should be submitted to the carrier with your claim.

### 2-3. INSTALLATION CONSIDERATIONS

The iSBC 464 board is designed for interface with an Intel iSBC Single Board Computer based system or an Intel Intellec Microcomputer Development System. Important installation and interfacing criteria are provided in the following sections.

#### 2-4. POWER REQUIREMENTS

The iSBC 464 board requires +5VDC. Current requirements are a function of the PROM/ROM device type and quantity installed on the board. Table 1-1 provides specific current requirements for several device types. For device types not listed in Table 1-1, refer to the manufacturer's specification sheet. Ensure that your system power supply has sufficient +5VDC current capacity to accommodate the additional load.

# 2-5. COOLING REQUIREMENTS

Adequate air circulation must be provided to prevent a temperature rise above  $55^{\circ}\text{C}$  ( $131^{\circ}\text{F}$ ). All Intel system enclosures provide adequate air circulation to hold temperature below the maximum. Board head dissipation is listed in Table 1-1.

# 2-6. MULTIBUS INTERFACE REQUIREMENTS

Board edge connector Pl provides the interface to the Multibus lines. Connector Pl pin assignments are listed in Table 2-1. Notice that all Multibus signals are not utilized by the iSBC 464 board. Signal descriptions for signals used by the board are provided in Table 2-2. Alternative mating connectors for Pl are listed in Table 2-3.

Table 2-1. Multibus™ Interface Connector Pl Pin Assignments

|            | (COMPONENT SIDE) PIN <sup>1,2</sup> MNEMONIC DESCRIPTION |             | PIN <sup>1</sup> ,2 |    | UIT SIDE)<br>C DESCRIPTION |                          |

|------------|----------------------------------------------------------|-------------|---------------------|----|----------------------------|--------------------------|

|            | 1                                                        | GND         | Signal GND          | 2  | GND                        | Signal GND               |

|            | 3                                                        | +5 <b>V</b> | +5Vdc               | 4  | +5V                        | +5Vdc                    |

| POWER      | 5                                                        | +5 <b>V</b> | +5 Vdc              | 6  | +5V                        | +5Vdc                    |

| SUPPLIES   | 7                                                        | +12V        | +12Vdc              | 8  | +12V                       | +12Vdc                   |

|            | 9                                                        | -5V         | -5Vdc               | 10 | -5V                        | -5Vdc                    |

|            | 11                                                       | GND         | Signal GND          | 12 | GND                        | Signal GND               |

|            | 13                                                       | BCLK/       | Bus Clock           | 14 | INIT/                      | Initialize               |

|            | 15                                                       | BPRN/       | Bus Priority In     | 16 | BPRO/                      | Bus Priority Out         |

| BUS        | 17                                                       | BUSY/       | Bus Busy            | 18 | BREQ/                      | Bus Request              |

| CONTROLS   | 19                                                       | MRDC/       | Mem Read Cmd        | 20 | MWTC/                      | Mem Write Cmd            |

| 55         | 21                                                       | IORC/       | I/O Read Cmd        | 22 | IOWC/                      | I/O Write Cmd            |

|            | 23                                                       | XACK/       | XFER Acknowledge    | 24 | INH1/                      | Inhibit 1<br>disable RAM |

|            | 25                                                       | LOCK/       | Dual Port Lock      | 26 | INH2/                      | Inhibit 2<br>disable ROM |

| BUS        | 27                                                       | BHEN/       | Byte High Enable    | 28 | AD10/                      |                          |

| CONTROLS   | 29                                                       | CBRQ/       | Common Bus Request  | 30 | AD11/                      | Address                  |

| AND        | 31                                                       | CCLK/       | Constant Clk        | 32 | AD12/                      | Bus                      |

| ADDRESS    | 33                                                       | INTA/       | Interrupt           |    |                            |                          |

|            |                                                          |             | Acknowledge         | 34 | AD1 3/                     |                          |

|            | 35                                                       | INT6/       | Parallel            | 36 | INT7/                      | Parallel                 |

|            | 37                                                       | INT4/       | Interrupt           | 38 | INT5/                      | Interrupt                |

| INTERRUPTS | 39                                                       | INT2/       | Requests            | 40 | INT3/                      | Requests                 |

|            | 41                                                       | INTO/       | <u></u>             | 42 | INT1/                      | <b>3</b>                 |

Table 2-1. Multibus™ Interface Connector Pl Pin Assignments (continued)

|                   | PIN <sup>1</sup> ,2                          | (COMPONENT SIDE) MNEMONIC DESCRIPTION                                |                                                   | PIN <sup>1</sup> ,2                          | (CIRCUIT S                                      | SIDE) DESCRIPTION                                 |

|-------------------|----------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------|-------------------------------------------------|---------------------------------------------------|

| ADDRESS           | 43<br>45<br>47<br>49<br>51<br>53<br>55       | ADRE/<br>ADRC/<br>ADRA/<br>ADR8/<br>ADR6/<br>ADR4/<br>ADR2/<br>ADR0/ | Address<br>Bus                                    | 44<br>46<br>48<br>50<br>52<br>54<br>56       | ADRF/ ADRD/ ADRB/ ADR9/ ADR7/ ADR5/ ADR3/ ADR1/ | Address<br>Bus                                    |

| DATA              | 59<br>61<br>63<br>65<br>67<br>69<br>71<br>73 | DATE/<br>DATC/<br>DATA/<br>DAT8/<br>DAT6/<br>DAT4/<br>DAT2/<br>DAT0/ | Data<br>Bus                                       | 60<br>62<br>64<br>66<br>68<br>70<br>72<br>74 | DATF/ DATD/ DATB/ DAT9/ DAT7/ DAT5/ DAT3/ DAT1/ | Data<br>Bus                                       |

| POWER<br>SUPPLIES | 75<br>77<br>79<br>81<br>83<br>85             | GND -12V +5V +5V GND                                                 | Singal GND Reserved -12Vdc +5Vdc +5Vdc Signal GND | 76<br>78<br>80<br>82<br>84<br>86             | GND<br>-12V<br>+5V<br>+5V<br>GND                | Signal GND Reserved -12Vdc +5Vdc +5Vdc Signal GND |

<sup>1.</sup> All odd numbered pins (1,3,5...85) are on component side of the board. Pin 1 is the left-most pin when viewed from the component side of the board with the extractors at the top. All unassigned pins are reserved. 2. Not all pins used by iSBC 464 board. See Table 2-2.

Table 2-2. iSBC™ 464 Signal Functions

| Signal        | Functional Description                                                                                                                                                                |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ADRO/-ADRF/   | Address. 16 bits used to address a specific word or byte in the iSBC 464 array.                                                                                                       |  |  |

| ADR10/-ADR13/ | Extended Address. Four additional address bits used for page selection.                                                                                                               |  |  |

| BHEN/         | Byte High Enable. Enables DAT8 - DATF (high order byte) in the 16/8 bit mode.                                                                                                         |  |  |

| CCLK/         | Constant Clock. 9.68 MHz signal used to clock the access time counter and th XACK/ flip-flop.                                                                                         |  |  |

| DATO/-DATF/   | Data. 16 bits of memory output data. Refer to paragraph 3-4 for bus definition.                                                                                                       |  |  |

| INH1/         | Inhibit RAM. Prevents overlapped RAM from responding to a Memory Read command.                                                                                                        |  |  |

| INH2/         | Inhibit ROM. Prevents the iSBC 464 from responding to the address on the Multibus.                                                                                                    |  |  |

| MRDC/         | Memory Read Command. Initiates the read cycle. Address must be present before command.                                                                                                |  |  |

| XACK/         | Transfer Acknowledge. Indicates to the computer board that the iSBC 464 has completed the specified memory read operation, and the data has been placed onto the Multibus data lines. |  |  |

Table 2-3. User Supplied Connectors

| Function                    | Pins  | Centers<br>(inches) | Connector<br>Type                                                       | Vendor P/N                                                                                                                  |

|-----------------------------|-------|---------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Multibus<br>Connector<br>Pl | 43/86 | 0.156               | Solder PCB  Wire Wrap (no ears)  Wire Wrap (with 0.128  Mounting holes) | Elfab BS1562043PBB Viking 2KH43/9AMK12  Edac 337-086-0540-201 Elfab BW1562D-43PBB  Edac 337-086-540-202 Elfab BW1562A-43PBB |

- Notes: 1. Connector heights are not guaranteed to conform to OEM equipment.

- 2. Wire wrap pin lengths are not guaranteed to conform to OEM equipment.

- 3. Connector number convention may not agree with board connector.

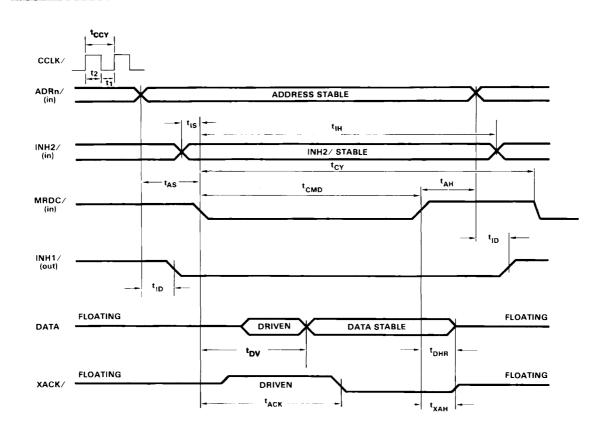

AC and DC characteristics of the iSBC 464 board are presented in Tables 2-4 and 2-5, respectively. The Multibus exchange timing for memory read operations is provided in Figure 2-1.

Table 2-4. AC Characteristics, iSBC™ 464 PROM/ROM Board

| Parameter          | Description                   | Minimum (nsec)                         | Maximum (nsec)                         | Comments                                                   |

|--------------------|-------------------------------|----------------------------------------|----------------------------------------|------------------------------------------------------------|

| t <sub>AH</sub>    | Address Hold<br>From Command  | 50                                     |                                        |                                                            |

| t <sub>AS</sub>    | Address Set-Up                | 30                                     |                                        |                                                            |

| 11.0               | To Command                    | 50                                     |                                        |                                                            |

| t <sub>DV</sub>    | Read Command To<br>Data Valid |                                        | t <sub>PROM</sub> +125                 | Where tpROM is tACC-57, tCE or tOE, whichever is greatest. |

| t <sub>ACK</sub> * | Command To XACK/              | (n-1)t <sub>CCY</sub> +55 <sup>†</sup> | (n+1)t <sub>CCY</sub> +25 <sup>†</sup> | Variable Access<br>Time RAM Over-<br>lap Jumper off.       |

| tccy               | CCLK/ Cycle                   | 100                                    |                                        |                                                            |

| t <sub>1</sub>     | CCLK/ Width                   | 35                                     |                                        | Time LOW                                                   |

| t <sub>2</sub>     | CCLK/ Width                   | 35                                     |                                        | Time HIGH                                                  |

| t <sub>CMD</sub>   | Read Command<br>Width         | t <sub>ACK</sub> MAX                   |                                        |                                                            |

| t <sub>CY</sub>    | Cycle Time                    | t <sub>CMD</sub> + 100                 |                                        | $t_{CY} = (t_{CMD} + t_{AH} + t_{AS})$                     |

| <sup>t</sup> DHR   | Data Hold From Command        | 23                                     | 67                                     |                                                            |

| t <sub>ID</sub>    | Address To<br>INH1/ Delay     |                                        | 63                                     |                                                            |

| t <sub>IH</sub>    | INH2/ Hold From<br>Command    | <sup>t</sup> CMD                       | t <sub>CMD</sub> + 50                  |                                                            |

| t <sub>IS</sub>    | INH2/ Set-Up To<br>Command    | -50                                    | -CHD                                   |                                                            |

| t <sub>XAH</sub>   | XACK/ Hold From<br>Command    | 50                                     | 57                                     |                                                            |

$<sup>\</sup>dagger$  n = the access time CODE (Decimal) with access time jumpers.

Maximum: based on all involved devices having maximum propagation and the

clock edge just preceded the instant the counter was enabled.

No response if addressed PROM is disabled or if the PROM inhibit (INH2/) is invoked.

2

<sup>\*</sup> Minimum: based on all involved devices having minimum propagation and clock edge being coincident with the counter enabled.

Table 2-5. DC Characteristics, iSBC™ 464 PROM/ROM Board

| Signals (Device) | Parameters                                                                                    | Min. | Max.        | Unit     | Test Conditions                                                                       |

|------------------|-----------------------------------------------------------------------------------------------|------|-------------|----------|---------------------------------------------------------------------------------------|

| ADRO/-ADRF/      | V <sub>IL</sub> -Input low voltage                                                            |      | 0.80        | v        |                                                                                       |

| MRDC/, CCLK/,    | V <sub>IH</sub> -Input high voltage                                                           | 2.0  |             | V        |                                                                                       |

| INH2/, BHEN/     | I <sub>IH</sub> -Input leakage<br>current                                                     |      | 20          | uA       | v <sub>CC</sub> = 5.25v                                                               |

|                  | I <sub>IL</sub> -Input load current                                                           |      | -0.5        | mA       | V <sub>CC</sub> = 5.25,<br>V <sub>IL</sub> = .4V                                      |

|                  | C <sub>L</sub> * - Capacitive load                                                            |      | 18          | pf       |                                                                                       |

| ADR10/-ADR13/    | V <sub>IL</sub> -Input low voltage<br>V <sub>IH</sub> -Input high voltage                     | 2.0  | 0.8         | V<br>V   |                                                                                       |

|                  | I <sub>IH</sub> -Input leakage<br>current                                                     |      | 80          | uA       | V <sub>CC</sub> = 5.25,<br>V <sub>IL</sub> = .4V                                      |

|                  | I <sub>IL</sub> -Input load current  C <sub>L</sub> * - Capacitive load                       |      | -1.7†<br>18 | mA<br>pf | V <sub>CC</sub> = 5.25,<br>V <sub>IL</sub> = .4V                                      |

| INH1/            | V <sub>OL</sub> -Low level output<br>voltage<br>V <sub>OH</sub> -High level output<br>voltage |      | 0.4         | v        | I <sub>OL</sub> = 20 mA<br>Open collector,<br>V <sub>CC</sub> = 4.5V,                 |

|                  | C <sub>L</sub> * - Capactive load                                                             |      | 18          | pf       | $I_{OH} = .25 \text{ mA}$                                                             |

| XACK/            | V <sub>OL</sub> -Low level output<br>voltage<br>V <sub>OH</sub> -High level output<br>voltage | 2.4  | 0.4         | v<br>v   | $V_{CC} = 4.5V,$ $I_{OL} = 32 \text{ MA}$ $V_{CC} = 4.5V,$ $I_{OH} = -5.2 \text{ mA}$ |

| DATO/-DATF/      | I <sub>LH</sub> -Input current at<br>high voltage<br>I <sub>LL</sub> -Input current at        |      | -80<br>80   | uA<br>uA | $V_{CC} = 5.25V,$ $V_{O} = 0.4V,$ $V_{CC} = 5.25V,$                                   |

|                  | low voltage CL* - Capacitive load                                                             |      | 30          | pf       | $V_0 = 2.4V$                                                                          |

NOTES: † Exceeds the Multibus spec of -0.8 mA. \* Estimate

Figure 2-1. Bus Exchange Timing

### 2-7. OPTION BLOCK CONFIGURATIONS

Instructions for configuring option block headers to select PROM/ROM device type and mode of operation are provided in the following two sections.

#### 2-8. PROM/ROM DEVICE SELECT OPTION BLOCKS

The iSBC 464 board is compatible with three different types of Intel PROM/ROM devices. These devices and their byte capacities are listed in Table 2-6. Three device select option blocks reside on the iSBC 464 board. Each option block corresponds to a particular device type. Table 2-6 indicates which option block pertains to which device type. The supplied 8-lead DIP header should be inserted into the desired option block, as indicated in the table. Only one device type may be selected at one time.

| Intel PROM/ROM | Option Block | Device Capacity | Maximum Board Capacity |

|----------------|--------------|-----------------|------------------------|

| 2758           | พ7           | 1024 x 8        | 16K Bytes              |

| 2716/2316      | พ5           | 2048 x 8        | 32K Bytes              |

| 2732           | พ6           | 4096 x 8        | 64K Bytes              |

Table 2-6. Device Select Option Blocks

### 2-9. MODE SELECT OPTION BLOCKS

The iSBC 464 board will operate in one of two modes: the 8-bit only mode or the 16/8-bit mode. The 16/8-bit mode allows 16-bit data words to be accessed by either 8 or 16-bit processors. The 16-bit system processor can read both the upper and lower byte in a single read cycle. However, an 8-bit system must use two read cycles to obtain both the upper and lower bytes. This is accomplished by transferring or "swapping" the upper data byte to the lower data byte path in two separate read cycles. Section 3-8 describes byte swapping in greater detail.

The board has four option blocks associated with mode selection. Option blocks W1 and W2 are used to select the 16/8-bit mode; and option blocks W3 and W4 are used to select the 8-bit only mode. Mode selection is accomplished by inserting the two supplied headers into the appropriate option blocks. Notice that one of the headers is an 18-lead DIP and therefore must reside in W1 or W3. The other header is a 16-lead DIP and must reside in W2 or W4.

### 2-10. JUMPER CONFIGURATIONS

The following sections provide instructions for configuring the base address, page address, RAM overlap, and access time jumpers.

#### 2-11. BASE ADDRESS SELECT JUMPERS

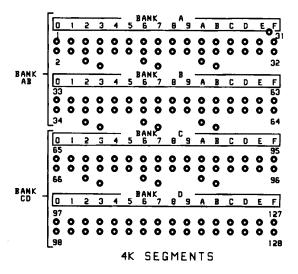

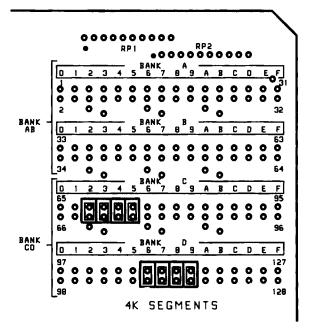

In both the 8-bit and the 16/8-bit modes, the base address of each bank must be specified by configuring one, two, or four jumper pairs in each bank jumper selection block (posts 1 through 128). In the 8-bit only mode, a base address for each bank may be selected. However, in the 16/8-bit mode, banks A and B are paired together to form bank AB, and banks C and D are paired together to form bank CD (see Figure 2-2). Notice that in the paired mode, banks A & C store the even data bytes and banks B & D store the odd data bytes.

In both modes the base address for each bank must be set to a 4K byte boundary, with one exception: when using 4K PROM devices in the 16/8-bit mode, only 8K byte boundaries are allowed. Table 2-7 illustrates this concept.

Figure 2-2. Base Address Select Jumpers

To select the desired base address for each bank in the 8-bit mode, refer to the 8-bit columns in Table 2-7. The table indicates which jumper pairs to enable by inserting a push-on jumper connector. The possible base address selections are shown in column one in the table. Each hexadecimal number in the second, third, or fourth columns of the table corresponds to a jumper pair segment on the board.

Similarly, to select the desired base address for each bank in the 16/8-bit mode, refer to the 16-bit columns in Table 2-7. Notice that a maximum of four jumper pairs may be selected in each bank. When 2732 devices are used in the 16/8-bit mode, select four contiguous segments in each bank.

To use Table 2-7, select the desired base address listed in the left column; then locate the PROM/ROM device type column at the top of the table. Each of these columns is subdivided into the 8-bit and the 16/8-bit modes. The jumper pairs to be inserted to obtain a particular base address are shown. Each sequence indicated must be repeated for each bank utilized. Two examples of the base address selection procedure are given below.

Example 1: In the 8-bit mode, if Intel 2716 PROM devices are used, and the base address of bank C is to be 7000, then segments 7 and 8 should be enabled by inserting push-on jumper connectors onto posts 79-80 (for segment 7) and 81-82 (for segment 8). All other segments in bank C should be disabled (no other jumper connectors installed). Figure 2-3 illustrates this example.

Figure 2-3. Example 1 8-bit Mode

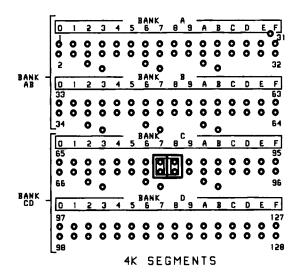

If the same address and device type are used, but the 16/8-bit mode is selected, segments 7, 8, 9 and A in bank pair CD must be enabled. This would be accomplished by installing push-on jumper connectors on posts 79-80 (for segment 7), 81-82 (for segment 8), 83-84 (for segment 9), and 85-86 (for segment A). Figure 2-4 illustrates this example.

Figure 2-4. Example 1 16-bit Mode

Example 2: Using Intel 2732 PROM devices in the 16/8-bit mode, a base address of 2000 is selected for bank pair CD. Table 2-7 indicates the following segments should be enabled: segments 2, 3, 4, and 5 in bank C; and segments 6, 7, 8, and 9 in bank D. Notice that the bank pair is treated as two separate banks with the lower segment values in the first bank and the higher segment values in the second bank. In this example the following jumper post pairs in bank C should be enabled by installing push-on jumpers: 69-70 (for segment 2), 71-72 (for segment 3), 73-74 (for segment 4), and 75-76 (for segment 5). In addition, the following jumper post pairs in bank D should be enabled by installing push-on jumpers: 109-110 (for segment 6), 111-112 (for segment 7), 113-114 (for segment 8), and 115-116 (for segment 9). Figure 2-5 illustrates this example.

Figure 2-5. Example 2 16-bit Mode

Table 2-7. Base Address Selection

| Hex Base<br>Address 2                                                                                        | 2758 (1K)                                                     |                                                                                                |                                                                                                | 5 (2K)                                                                                                                                                 | 2732 (4K)                                                                                                                                              |                                                                                                                                   |  |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                              | Segments On<br>8 Bit 16 Bit                                   |                                                                                                | Segment<br>8 Bit                                                                               | s On<br>16 Bit                                                                                                                                         | Segments On <sup>1</sup><br>8 Bit 16 Bit                                                                                                               |                                                                                                                                   |  |

| 0000<br>1000<br>2000<br>3000<br>4000<br>5000<br>6000<br>7000<br>8000<br>9000<br>A000<br>B000<br>C000<br>D000 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B<br>C | 0,1<br>1,2<br>2,3<br>3,4<br>4,5<br>5,6<br>6,7<br>7,8<br>8,9<br>9,A<br>A,B<br>B,C<br>C,D<br>D,E | 0,1<br>1,2<br>2,3<br>3,4<br>4,5<br>5,6<br>6,7<br>7,8<br>8,9<br>9,A<br>A,B<br>B,C<br>C,D<br>D,E | 0,1,2,3<br>1,2,3,4<br>2,3,4,5<br>3,4,5,6<br>4,5,6,7<br>5,6,7,8<br>6,7,8,9<br>7,8,9,A<br>8,9,A,B<br>9,A,B,C<br>A,B,C,D<br>B,C,D,E<br>C,D,E,F<br>D,E,F,O | 0,1,2,3<br>1,2,3,4<br>2,3,4,5<br>3,4,5,6<br>4,5,6,7<br>5,6,7,8<br>6,7,8,9<br>7,8,9,A<br>8,9,A,B<br>9,A,B,C<br>A,B,C,D<br>B,C,D,E<br>C,D,E,F<br>D,E,F,O | 0,1,2,3,4,5,6,7<br>2,3,4,5,6,7,8,9<br>4,5,6,7,8,9,A,B<br>6,7,8,9,A,B,C,D<br>8,9,A,B,C,D,E,F<br>A,B,C,D,E,F,O,1<br>C,D,E,F,O,1,2,3 |  |

| F000                                                                                                         | E<br>F                                                        | E,F<br>F,O                                                                                     | E,F<br>F,0                                                                                     | E,F,0,1<br>F,0,1,2                                                                                                                                     | E,F,0,1<br>F,0,1,2                                                                                                                                     | E,F,0,1,2,3,4,5                                                                                                                   |  |

### NOTES:

- 1. A maximum of four segments in each bank may be on. It is therefore necessary to use both banks to obtain the desired address.

- 2. Odd base addresses in the 16/8-bit mode, using 4K PROMs are not allowed.

## 2-12. MEMORY ORDER AND PROM/ROM INSTALLATION

Base address assignment will affect the low to high memory order within a bank. Four possible row orders exist for the iSBC 464 board. Row orders, from low to high, and their corresponding base addresses are compared in Tables 2-8 and 2-9.

Install PROM/ROM devices in each bank according to the row order specified in Tables 2-8 and 2-9 for the selected base address. Notice that in the 16/8-bit mode, banks A and C store the even bytes and banks B and D store the odd bytes.

Table 2-8. LOW to HIGH Memory Order, 8 Bit Mode

| Row Order             | 0-1-2-3         | 2-3-0-1    | 1-2-3-0 | 3-0-1-2 |

|-----------------------|-----------------|------------|---------|---------|

| Device Type 2758 (1K) | All 4K Segments | None       | None    | None    |

| 2716 (2K)             | All Even 4K     | All Odd 4K | None    | None    |

|                       | Segments        | Segments   | None    | None    |

| 2732 (4K)             | 0000            | 2000       | 1000    | 3000    |

|                       | 4000            | 6000       | 5000    | 7000    |

|                       | 8000            | A000       | 9000    | 8000    |

|                       | c000            | E000       | D000    | F000    |

Table 2-9. LOW To HIGH Memory Order, 16 Bit Mode

| Row Order             | 0-1-2-3                 | 2-3-0-1                | 1-2-3-0 | 3-0-1-2      |

|-----------------------|-------------------------|------------------------|---------|--------------|

| Device Type 2758 (1K) | All Even 4K<br>Segments | All Odd 4K<br>Segments | None    | None         |

| 2716 (2K)             | 0000                    | 2000                   | 1000    | 3000         |

|                       | 4000                    | 6000                   | 5000    | 7000         |

|                       | 8 000                   | A000                   | 9000    | вооо         |

|                       | C000                    | E000                   | D000    | <b>г</b> 000 |

| 2732 (4K)             | 0000                    | 4000                   | 2000    | 6000         |

|                       | 8000                    | C000                   | A000    | E000         |

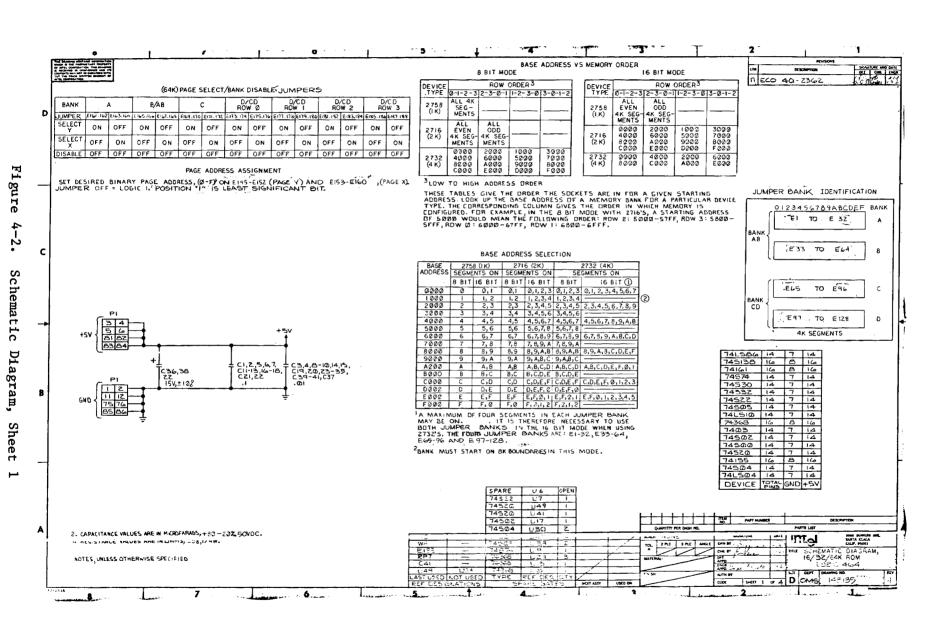

### 2-13. PAGE SELECT JUMPERS

If the iSBC 464 board is used in a system having 64K bytes of memory, or less, only address lines ADRO/ through ADRF/ are required. In larger systems, ADR10/ through ADR13/ are utilized to define one of 16 possible 64K byte segments or pages, within a 1 megabyte address space.

Each iSBC 464 board memory bank may reside in either of two 64K byte pages, labeled X and Y on the board. Any two pages of the 16 possible may be chosen and designated X and Y. The page select jumpers are used to assign a binary value to each of the two pages.

In the 8-bit mode, all four rows in banks A, B, and C must reside in one page or the other. Each row in bank D may reside in either page (that is, row 0 in page X, row 1 in page Y, all in X or all in Y, etc.). In the 16/8-bit mode, all rows in bank AB must reside in one page or the other, and each row in bank CD may reside in either page.

Jumper posts 145 through 160 are used to select the equivalent binary address for page X and Y. These jumpers, in conjunction with other circuitry will allow only a specific address on lines ADR10/ - ADR13/ to be read by the board. There are 16 possible values (0 through F) for each of the two pages. The selected value is programmed on the board by using push-on jumpers to indicate the binary equivalent of the desired hexadecimal page number. In this scheme, installing a push-on jumper programs the bit for a logic zero; not installing the push-on jumper programs the bit for a logic one.

The least significant bit of the four bit page value is shown on the board. An example will best illustrate the page address selection technique. Suppose you want your page Y to have a hexadecimal value of D. The binary equivalent for hexadecimal D is 1101 with the least significant bit on the right. Therefore, to program this binary value into the board using the jumper posts, you would not install a push—on jumper between posts 151-152 (bit 1), posts 147-148 (bit 4), or posts 145-146 (bit 8). However, you would install a push on jumper between posts 149-150 (bit 2).

The page X address is programmed the same way, using jumper posts 153 through 160 as indicated on the board. Remember that a jumper in place equals a logic 0 and no jumper equals a logic 1.

Jumper posts 161 through 188 are used to assign a particular bank or bank pair to either page X or Y. The method of assignment differs depending on whether the board is configured for 8-bit only or 16/8-bit operation. In addition, each row (socket) in bank D (in 8-bit operation) and bank pair CD (in 16-bit operation) may be assigned to page X or Y.

Each bank may be assigned to either page X or page Y. Table 2-10 summarizes the jumper configurations necessary to assign a bank or bank pair to the desired page. Notice that in the 16/8-bit mode banks A and B are paired to form bank AB. Select only these jumpers for bank AB when in the 16/8-bit mode. Likewise, only bank pair CD jumpers should be used for row selection inthe 16/8-bit mode. Any unused banks or unused rows in bank D/CD can be disconnected by leaving both the X and Y page jumpers out.

The board will not respond to deselected addresses. These addresses can then be used by the system for other memory.

Table 2-10. Page Select/Bank Disable Jumpers

| BANK                    |            | A          | Е          | AB         |            | С          | i          | /CD<br>OW 0 |            | CD<br>W 1  | D/0<br>RO  | CD<br>w 2  | D/(<br>ROI | CD<br>w 3  |

|-------------------------|------------|------------|------------|------------|------------|------------|------------|-------------|------------|------------|------------|------------|------------|------------|

| JUMPERS<br>FROM:<br>TO: | 161<br>162 | 163<br>164 | 165<br>166 | 167<br>168 | 169<br>170 | 171<br>172 | 173<br>174 | 175<br>176  | 177<br>178 | 179<br>180 | 181<br>182 | 183<br>184 |            | 187<br>188 |

| SELECT<br>Y             | ON         | OFF        | ON         | OFF        | ON         | OFF        | ON         | OFF         | ON         | OFF        | ON         | OFF        | ON         | OFF        |

| SELECT<br>X             | OFF        | ON         | OFF        | ON         | OFF        | ON         | OFF        | ON          | OFF        | ON         | OFF        | ON         | OFF        | ON         |

| DISABLE                 | OFF         | OFF        | OFF        | OFF        | OFF        | OFF        | OFF        |

#### NOTES:

Set desired binary page address, (0-F) on E145-E152 (Page Y) and E153-E160 (Page X).

Jumper OFF = Logic 1. Position "1" is least significant bit.

#### 2-14. MEMORY ACCESS TIME JUMPERS

Memory access time for the iSBC 464 board is defined as the interval between the Memory Read Command (MRDC/), and the Transaction Complete (XACK/) signal. The access time which is jumper selected should match the worst case access time of the devices installed on the board. Jumper posts 137 through 144 are used to program the board access time.

Table 2-11 provides the access time codes and the required jumper pairs to be inserted for various Intel devices. For other devices not listed in Table 2-11, refer to the manufacturer's specification sheet and Table 2-12.

In certain cases overall system timing may be enhanced by altering the jumper configurations from the values in the two tables. Refer to Section 2-15 for a description of these cases.

Table 2-11. Access Time Codes For Intel Parts

| Intel Part | t <sub>PROM</sub> (nsec) | Access Time Code(n) | Jumper Pairs In |

|------------|--------------------------|---------------------|-----------------|

|            |                          |                     |                 |

| 2758       | 450                      | 6                   | 2,4             |

| 2716       | 450                      | 6                   | 2,4             |

| 2716-1     | 350                      | 5                   | 1,4             |

| 2716-2     | 390                      | 6                   | 2,4             |

| 2716-5     | 490                      | 7                   | 1,2,4           |

| 2716-6     | 650                      | 8                   | 8               |

| 2732       | 450                      | 6                   | 2,4             |

| 2732-4     | 390                      | 6                   | 2,4             |

| 2732-6     | 550                      | 7                   | 1,2,4           |

| 2732A      | 250                      | 4                   | 4               |

| 2732A-2    | 200                      | 4                   | 4               |

| 2732A-3    | 300                      | 5                   | 1,4             |

| 2316E      | 393                      | 6                   | 2,4             |

$t_{\mbox{\footnotesize{PROM}}}$  equals the greatest of  $t_{\mbox{\footnotesize{OE}}},\ t_{\mbox{\footnotesize{CE}}}$  and  $t_{\mbox{\footnotesize{ACC}}}$  - 57

Table 2-12. Board Access Time Selection

| Access<br>Time Code n | · · · · · · · · · · · · · · · · · · ·                               |      | Maximum<br>Usable tpROM<br>(nanoseconds) |

|-----------------------|---------------------------------------------------------------------|------|------------------------------------------|

| 1                     | 1 2 1,2 4 1,4 2,4 1,2,4 8 1,8 2,8 1,2,8 4,8 1,4,8 2,4,8 1,4,8 2,4,8 | 55   | 80                                       |

| 2                     |                                                                     | 155  | 180                                      |

| 3                     |                                                                     | 255  | 280                                      |

| 4                     |                                                                     | 355  | 380                                      |

| 5                     |                                                                     | 455  | 480                                      |

| 6                     |                                                                     | 555  | 580                                      |

| 7                     |                                                                     | 655  | 680                                      |

| 8                     |                                                                     | 755  | 780                                      |

| 9                     |                                                                     | 855  | 880                                      |

| 10                    |                                                                     | 955  | 980                                      |

| 11                    |                                                                     | 1055 | 1080                                     |

| 12                    |                                                                     | 1155 | 1180                                     |

| 13                    |                                                                     | 1255 | 1280                                     |

| 14                    |                                                                     | 1355 | 1380                                     |

$t_{\mbox{\footnotesize{PROM}}}$  equals the greatest of  $t_{\mbox{\footnotesize{OE}}},\ t_{\mbox{\footnotesize{CE}}},$  and  $t_{\mbox{\footnotesize{ACC}}}$  - 57.

### 2-15. RAM OVERLAP JUMPERS

Jumper posts 129 - 136 are used to indicate a RAM overlap condition. This condition is true if a portion or all of the PROM/ROM in a particular bank overlaps into RAM space. Each of the jumper pairs corresponds to a bank as indicated on the board. Removing a jumper indicates a RAM overlap condition for that bank.

Removing the jumper extends the access time to a minimum of 1455 nanoseconds for that bank. In addition the INH1/ signal will remain true for 50 nanoseconds after XACK/ is true, resulting in a total extended minimum of 1505 nanoseconds when an overlap condition is indicated. The access time for the banks which do not have an overlap condition (jumpers in), will be the value set with the access time jumpers (Section 2-14).

In a RAM overlap condition, the maximum board access time of 1505 nanoseconds may not be required when used with certain RAM boards. If the RAM board can complete its refresh cycle in considerably less time than 1505 nanoseconds, the RAM overlap may not require activation.

In some cases, if the iSBC 464 board is frequently overlapping RAM, enhanced access time may be obtained by increasing the PROM/ROM access time (by jumper selection) to accommodate the RAM refresh time, provided this time is significantly below the 1505 nanosecond maximum time. Doing this will eliminate the need for indicating a RAM overlap condition. However, if the iSBC 464 board does not frequently overlap RAM, the PROM/ROM access time setting should remain as low as possible and the appropriate RAM overlap jumpers used.

### 2-16. COMPREHENSIVE SETUP PROCEDURE

The following procedure outlines the iSBC 464 board operational setup. Each step refers to a more detailed description in the text.

- a. Install device select header into one of the three option blocks (Section 2-8).

- b. Select 8-bit only mode, or the 16/8-bit mode, by installing two headers into the mode selection option blocks (Section 2-9).

- c. Select a base address for each bank or bank pair that will have PROM/ROM devices installed (Section 2-11).

- d. Install your PROM/ROM devices according to the memory order specified by the selected base address (Section 2-12).

- e. Set the page address for each page (Section 2-13).

- f. Assign each bank or bank pair to either page X or Y. Deselect unused banks or rows (Section 2-13).

- g. Set desired memory access time (Section 2-14).

- h. Indicate RAM overlap condition, if true (Section 2-15).

# 2-17. BOARD INSTALLATION

In an iSBC Single Board Computer based system, install the board in any slot that has not been wired for a dedicated function.

### CAUTION

Always turn off power before installing or removing the iSBC 464 board from its cardcage. Failure to take this precaution can result in damage to the board.

~ 1

•

### CHAPTER 3. PRINCIPLES OF OPERATION

### 3-1. INTRODUCTION

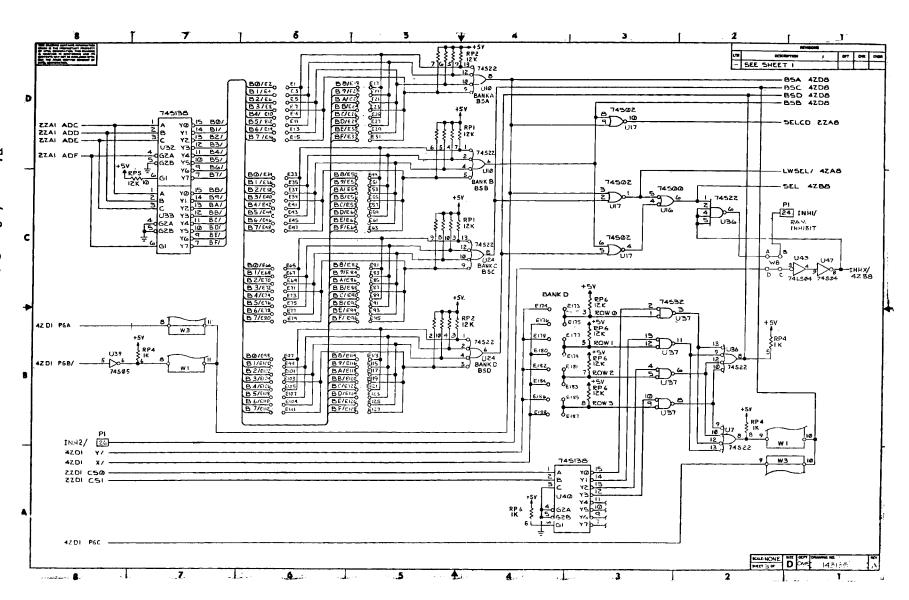

This chapter describes the iSBC 464 board principles of operation. Functional block diagrams and logic diagrams in Chapter 4 are referenced in this chapter. An overall functional description of the board is given in paragraph 3-2, while more detailed circuit operation of specific functional areas is given in subsequent paragraphs.

Both active—high (positive—true) and active—low (ground—true) signals appear on the schematics and drawings. To avoid confusion when referring to these signals, the following convention is used. The mnemonic for each active—low signal is terminated by a slash (e.g., SEL/). Such references indicate that the signal level is low when the condition is true (active). A mnemonic without a slash (e.g., ESB) refers to an active—high signal. These references indicate that the signal level is high when the condition is true (active).

# 3-2. FUNCTIONAL DESCRIPTION

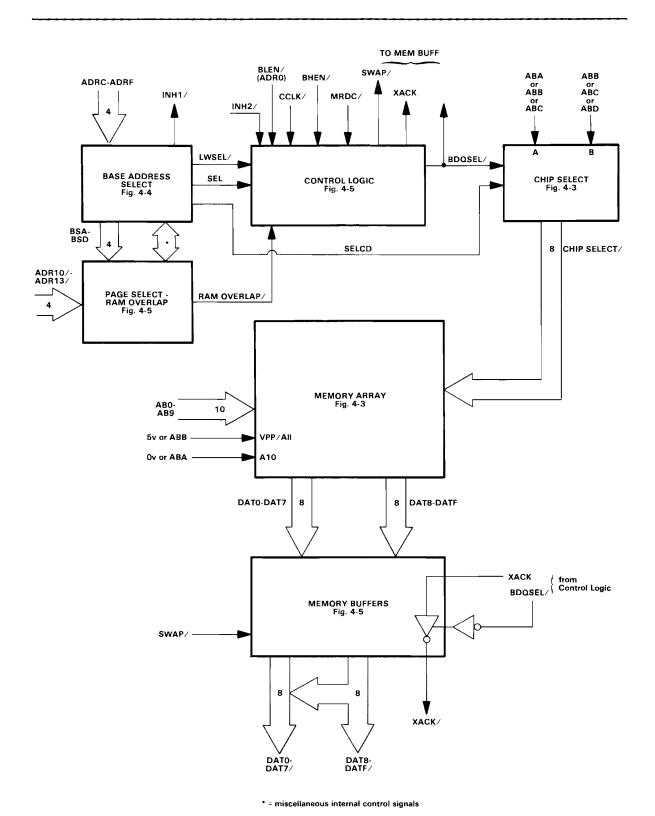

As shown in Figure 3-1. the iSBC 464 PROM/ROM board can be divided into six functional areas, for descriptive purposes:

- Memory array;

- Control logic;

- 3. Base address select;

- 4. PROM/ROM select logic;

- Page select logic;

- 6. Memory buffers.

The board outputs include 16 data lines and two control lines. Inputs include 20 address lines, three control lines, and one clock line.

All data from the iSBC 464 board is buffered before being placed on the Multibus. The buffers consist of line drivers and gating circuitry, activated by board control logic. When the memory space on the board is not addressed, the buffers are essentially disconnected from the data bus.

After the CPU has issued an address, and it has been stable for at least 50 nanoseconds, a Memory Read Command signal is issued (MRDC/). This command initiates the read cycle by enabling a low order device and a high order device, and by enabling the Access Time counter.

Figure 3-1. iSBC\*\* 464 Board Functional Block Diagram

#### PRINCIPLES OF OPERATION

#### NOTE

Access time as discussed here refers to the time between the Memory Read Command signal and the Transaction Complete signal.

The process of addressing a bank will drive the Inhibit RAM (INH1/) signal true. This signal is issued to the Multibus in order to inhibit all RAM in the system, preventing it from responding to the current address. If a PROM/ROM is selected which has its corresponding RAM Overlap jumper installed, an access time of 15 clock cycles is imposed. This allows any overlapped RAM to refresh before being inhibited. If the addressed memory is not overlapping RAM, the access time will be the value set with the access time jumpers. The signal INH1/ is true regardless of the value set (during a read cycle).

When the Access Time counter reaches its preselected or maximum count, the Transfer Acknowledge (XACK/) flip-flop is set and the XACK/ signal is gated onto the Multibus by BDQSEL/, which is true for the duration of MRDC/. In response to XACK/, the computer board removes MRDC/, and the address, thereby terminating the read operation.

To conserve power and minimize heat, all board memory chips are in a powered down standby state when not selected (except 2316E devices). When the board is accessed, two chips are always selected and thus active.

#### 3-3. MEMORY ARRAY AND ADDRESSING

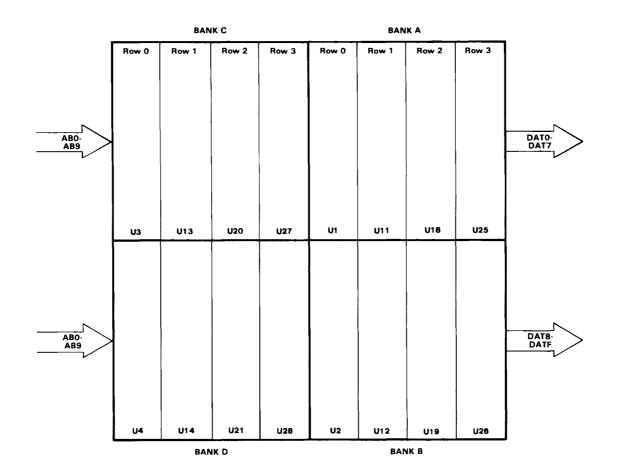

The iSBC 464 board memory is arranged into four banks, each of which is divided into four rows, as shown in Figure 3-2. During any given read cycle, a single row in two banks is selected. This selection is accomplished by the Chip Select circuitry, and is described in paragraph 3-4. The banks are arranged such that banks A and B are accessed together and banks C and D are accessed together. The physical and functional layouts of the array are compared in Figures 3-2 and 3-3.

In the 8 bit only mode, each bank is regarded as a separate entity, for data storage purposes. In the 16/8 bit mode, banks A and C store the even data bytes, while banks B and D store the odd data bytes.

The addressing structure will vary with device type and mode operation. In the 8 bit mode, address lines ADRO/ through ADRD/ are used directly by the array for byte location and chip selection purposes. In the 16/8 bit mode, the address vector is shifted one bit, with ADRO/ becoming the odd/even byte indicator (signal BLEN/). All other incoming address lines are also shfited, i.e., ADR1/ becomes ABO and ADRE/ becomes ABD.

Figure 3-2. Memory Array Functional Layout

Figure 3-3. Memory Array Physical Layout

With all three device types, ABO through AB9 are used directly by the array. However, ABA through ABD functions differ, according to device capacity. Table 3-1 outlines these differences.

Table 3-1. Input Function Reference

| Address<br>Bus |      | Device |      |

|----------------|------|--------|------|

| Inputs*        | 1K   | 2K     | 4K   |

| АВА            | C.S. | U10    | U10  |

| АВВ            | C.S. | C.S.   | VPP  |

| АВС            |      | C.S.   | C.S. |

| A B D          |      |        | C.S. |

| +5 Volts       | VPP  | VPP    |      |

| Ground         | U10  |        |      |

C.S. = Chip Select, Pin 20

U10 = Pin 19

VPP = Pin 21

<sup>\*</sup> Internal Bus; not to be confused with Multibus.

### PRINCIPLES OF OPERATION

### 3-4. CHIP SELECT

In addition to using ABA through ABD, the chip selection circuitry uses two other internal signals during the read operation. The signal SELCD is generated by the base address decoding logic and is true if banks C or D have been addressed. Conversely, it will be false if banks A or B are addressed. Hence, the signal will select either half of the array. Address bus lines ABA-ABD will then select one of the four rows within that half of the array.

The other signal used by the chip select circuitry, BDQSEL/, in its true state enables the input to the circuitry and in its false state disables the inputs. Essentially, it allows or does not allow a read operation to occur. The BDQSEL/ signal is a function of MRDC/ and the address. It will be true when MRDC/ is true, and the board is selected.

#### 3-5. CONTROL LOGIC

Three input control signals are used by the iSBC 464 board: Memory Read Command (MRDC/), Inhibit ROM (INH2/), and Byte High Enable (BHEN/). A fourth signal, Constant Clock (CCLK/), provides timing for the board. All signals are issued by the computer board, via the Multibus lines.

The INH2/ signal is used to disable the entire board during a read cycle in which the system controller is accessing RAM or I/O which shares the same address space as the iSBC 464 board. When INH2/ is true, the Access Time counter (circuit U35, Figure 4-2) and the Transfer Acknowledge flip-flop remain cleared and INH1/ remains inactive. This action allows overlapped memory or I/O to respond to the address on the Multibus lines.

The MRDC/ signal indicates that a valid address is present on the Multibus and that the contents of that location are to be read and placed on the system data bus.

A 9.68 MHz constant clock signal is used for board timing purposes. This signal clocks the Access Timer and the Transfer Acknowledge flip-flop.

The BHEN/ signal is used only in the 16/8 bit mode. When true, it enables both the high order (odd) and the low order (even) bytes from the memory buffers onto the Multibus. The signal must be false to enable the swap byte operation (refer to paragraph 3-8 for a discussion of this operation).

The MRDC/ gate (U46-8, Figure 4-2) performs three basic functions: it generates BDQSEL/, qualifies the memory buffer gating circuitry, and clears the Access Time Counter and the XACK flip-flop.

The signal BDQSEL/ has two basic functions: when true, it gates the XACK signal onto the Multibus lines; it also is used to enable the Chip Select circuitry (refer to paragraph 3-4).

### PRINCIPLES OF OPERATION

The inverted output of the MRDC/ gate will qualify the two memory buffer gate drivers (U16-8, U16-11, Figure 4-2). Data in the buffers will be gated out by one of these drivers. One of the drivers is enabled during any given read cycle. This operation is discussed in paragraph 3-8.

The Access Time Counter must be enabled at the beginning of every read cycle. The counter is used to generate XACK/. This signal indicates to the computer board that the data is valid. The counter also allows overlapped RAM to complete any referesh operation before being inhibited by the iSBC 464 board (see paragraph 2-15). The output of the counter sets the XACK flip-flop on the positive edge of the clock pulse. The XACK/ signal is discussed in paragraph 3-2.

### 3-6. BASE ADDRESS SELECT LOGIC

This logic and associated jumpers are used to assign a specific base address to a particular bank. This address must lie on a hexadecimal 4K byte boundary.

Base address assignment is accomplished by decoding address bits ADRC through ADRF into 16 lines, representing the 16 4K segments of memory, and subsequently enabling the desired combination of segments into a group of selection gates (see Figure 4-2). The outputs of this logic will select either the C and D half of the array (SELCD true) or the A and B half (SELCD false).

In the 16/8 bit mode, banks A and B are paired together and banks C and D are paired. This forms two 16 bit banks, with the even bytes residing in banks A and C and the odd bytes residing in banks B and D. In this mode the memory is word or byte addressable.

# 3-7. PAGE SELECT LOGIC

This logic provides for assigning board memory to one or two of the 16 possible 64K byte page values. The two selected pages are designated X and Y, with jumper pairs provided to preset the binary value of each page. The logic is arranged such that banks A, B, and C must reside totally in one page or the other, and each row in bank D or C/D may reside in one of the two pages.

Page addressing from the system controller is accomplished with the ADR10/ through ADR13/ address lines. The desired page X and Y values are set with jumpers.

#### PRINCIPLES OF OPERATION

## 3-8. MEMORY DATA PATHS

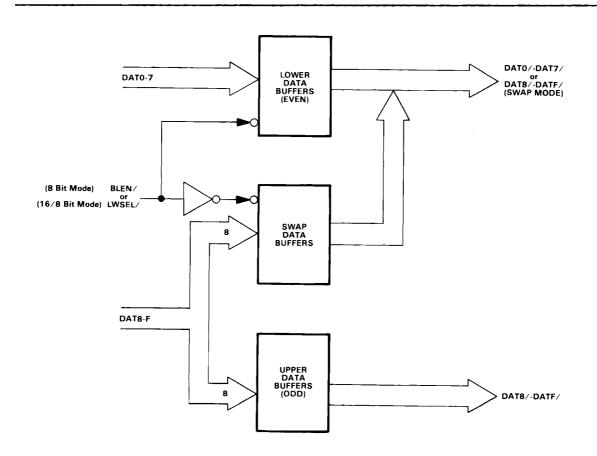

In the 16/8 bit mode, even data bytes from the array will be transferred to the memory buffers on the low order data bus, and the odd bytes will be transferred on the high order data bus. In the 8 bit only mode, data bytes from banks A and C will be transferred to the low order bus and data bytes from banks B and D will be transferred to the high order bus. When gated out onto the Multibus, all data is inverted.

There are two methods of gating the buffered data onto the Multibus. As shown in Figure 3-4, it is possible to transfer the odd data bytes onto the low order data output lines. This transfer is known as byte swap. In the 8-bit only mode the swap occurs when LWSEL/ is false. In the 16/8 bit mode it occurs when ADRO (BLEN) is a 1. In either mode, the Multibus signal BHEN/ must be false to enable the swap.

The second method of gating buffered data onto the Multibus simultaneously enables the DATO-DAT7 bus onto the low order output lines, and the DAT8-DATF bus onto the high order output lines. This 16-bit output is enabled when ADRO (BLEN) is a 0. This second method of gating the data onto the Multibus is also enabled when BHEN/ is true, regardless of the value of ADRO/ or LWSEL/.

Figure 3-4. Byte Swap Block Diagram

## CHAPTER 4. SERVICE INFORMATION

# 4-1. INTRODUCTION

This chapter provides a list of replacement parts, logic diagrams, and repair assistance information pertaining to the iSBC 464 Memory Expansion Board.

# 4-2. REPLACEMENT PARTS

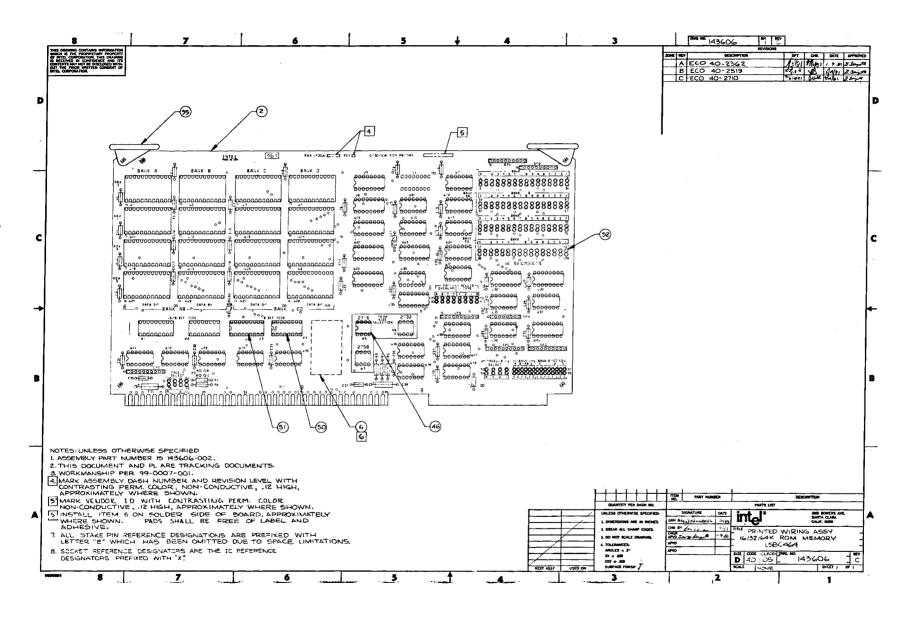

Table 4-1 provides a list of replacement parts for the iSBC 464 board. The part location, description, part number, manufacturer, and quantity of parts are given in the table. Table 4-2 identifies and lists the addresses of the manufacturers referenced in Table 4-1.

Table 4-1. Replacement Parts List

| Reference<br>Designation                                                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                    | Mfr. Part No.                                                                                            | Mfr. Code                                | Qty.                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------------------------|

| U5,8,15,22,29<br>U7,10,24,36<br>U9<br>U16<br>U17<br>U23<br>U30,47<br>U31<br>U32,33,40<br>U35<br>U37<br>U38<br>U39<br>U41,49<br>U42,48<br>U43,44,45<br>U46 | IC Tri-State Hex Buffer IC Nand Gate IC Dual D Type Flip-Flop IC Nand Gate IC Nor Gate IC Decoder IC Hex Inverter IC Nand Gate IC Decoder IC Synchronous Counter IC Or Gate IC Nand Gate IC Nand Gate IC Hex Inverter IC Nand Gate IC Hex Inverter IC Nand Gate IC Hex Inverter IC Nand Gate IC Exclusive OR Gate IC Hex Inverter IC Nand Gate | 74368 74S22 74S74 74S00 74S02 74155 74S04 74S30 74S138 74161 74S32 7403 74S05 74S20 74LS86 74LS04 74LS10 | TI T | 5<br>4<br>1<br>1<br>2<br>1<br>3<br>1<br>1<br>2<br>2<br>2<br>3 |

| C1,2,5,6,7,11,<br>12,13,16,17,<br>18,21,22<br>C3,4,8,9,10,<br>14,15,19,20,23-<br>35,37,39,40,41<br>C38,36                                                 | Capacitor, ceramic, 0.1 uf 50v  Capacitor, ceramic, 0.01 uf 50v  Capacitor, tantalum, 22 uf 15v                                                                                                                                                                                                                                                | OBD<br>OBD                                                                                               | CML<br>CML                               | 13<br>26<br>2                                                 |

#### SERVICE INFORMATION

Table 4-1. Replacement Parts List (continued)

| Reference<br>Designation                                                             | Description                                                                                                                                                                                                                                                          | Mfr.<br>Part No.                                                                          | Mfr. Code                                                                       | Qty.                                            |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------|

| R1-5<br>RP1,2,3,5,6,7<br>RP4<br>W1,3<br>W2,4<br>W5/6/7<br>U1-4,11-14,<br>18-21,25-28 | Resistor, 56k ohm, 0.25w, 5% Resistor Pack, 10 pin, 12k ohm Resistor Pack, 8 pin, 1k ohm  Socket, 18 pin DIP Socket, 16 pin DIP Socket, 8 pin DIP Socket, PROM/ROM Device, 24 pin Header (jumper plug), 8 pin DIP Header, 16 pin DIP Header, 18 pin DIP Card Ejector | OBD<br>101R12K<br>7641R1K<br>OBD<br>OBD<br>OBD<br>OBD<br>OBD<br>OBD<br>OBD<br>OBD<br>S203 | CML<br>CTB<br>BK<br>CML<br>CML<br>CML<br>CML<br>CML<br>CML<br>CML<br>CML<br>SCA | 5<br>6<br>1<br>2<br>2<br>1<br>16<br>1<br>1<br>2 |

Table 4-2. Manufacturer's Codes

| Code                          | Manufacturer                                                                                             | Address                                                                    |

|-------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| BK<br>CML<br>CTB<br>SCA<br>TI | Beckman Co.,<br>Any commerical source<br>CTS of Berne, Indian<br>Scanbe, Inc.<br>Texas Instruments, Inc. | Fullerton, CA OBD = Order by description Berne, IN El Monte, CA Dallas, TX |

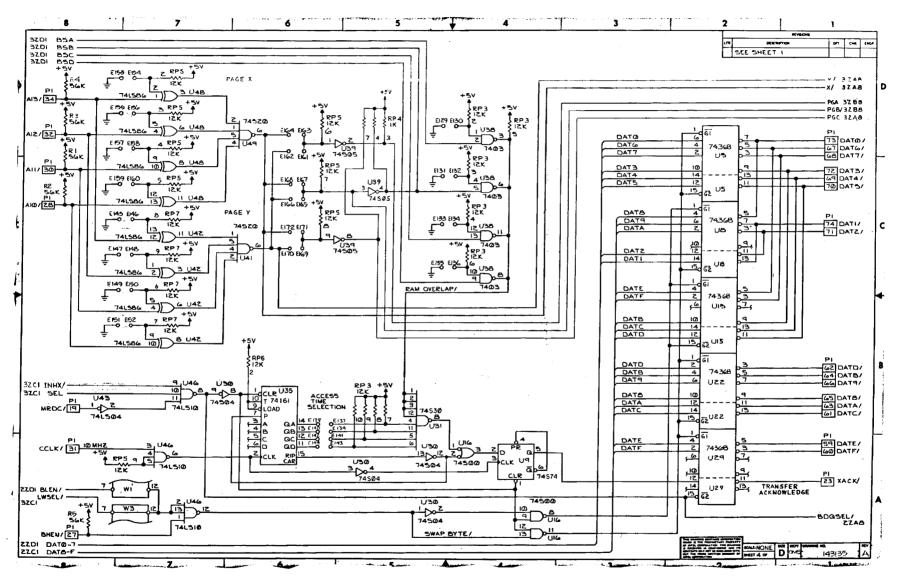

# 4-3. SERVICE DIAGRAMS

The iSBC 464 board parts location drawing and logic diagrams are provided in Figures 4-1 and 4-2. Signal mnemonics ending with slashes (e.g., PGB/) indicate active low operation. Conversely, mnemonics without slashes (e.g., SEL) indicate active high operation.

The schematic diagrams are current when the manual is printed. However, minor revisions to the diagrams may occur between manual printings. Therefore, Intel provides photocopies of the current schematic diagrams with the board, when it is shipped from the factory. These diagrams should be inserted into this manual for future reference. In most instances, the diagrams shipped with the board will be identical to those printed in the manual.

### SERVICE INFORMATION

# 4-4. SERVICE AND REPAIR ASSISTANCE

United States Customers can obtain service and repair assistance by contacting the Intel Product Service Hotline in Phoenix, Arizona. Customers outside the United States should contact their sales source (Intel Sales Office or Authorized Distributor) for service information and repair assistance.

Before calling the Product Service Hotline, you should have the following information available:

- a. Date you received the product.

- b. Complete part number of the product (including dash number). This number is usually silk-screened onto the board.

- c. Serial number of product. This number is stamped on the board.

- d. Shipping & billing addresses.

- e. If your Intel product warranty has expired, you must provide a purchase order number for billing purposes.

- f. If you have an extended warranty agreement, be sure to advise the Hotline personnel of this agreement.

Use the following numbers for contacting the Intel Product Service Hotline:

TELEPHONE

All U.S. locations, except Alaska, Arizona, & Hawaii:

(800) 528 - 0595