File No. S360-01 Form A27-2719-0

# Systems Reference Library

# IBM System/360 Model 67

# **Functional Characteristics**

This publication contains detailed information on the organization, characteristics, features, and functions unique to the IBM System/360 Model 67 Time Sharing System. Major areas described include time-sharing philosophy, system structure, new units, generalized information flow, standard and special features, instruction timings, and the system control panel.

Descriptions of specific input/output devices used with the Model 67 appear in separate publications. See the <u>IBM System/360 Bibliography</u>, Form A22-6822 for a listing and a brief description of these publications.

The material in this publication is presented with the assumption that the reader has knowledge of System/360 as defined in the <u>IBM System/360 Principles of Operation</u>, Form A22-6821 and the <u>IBM System/360 System Summary</u>, Form A22-6810. The <u>IBM System/360 Model 67 Configurator</u>, Form A27-2713 also may be of interest to the reader.

### First Edition

Specifications contained herein are subject to change from time to time. Any such change will be reported in subsequent revisions or Technical Newsletters.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form is provided at the back of this publication for reader's comments. If the form has been removed, comments may be addressed to IBM Corporation, Product Publications, Department 528, Kingston, New York 12401.

© International Business Machines Corporation 1967

### CONTENTS

| SYSTEM DESCRIPTION                          |

|---------------------------------------------|

| Program Characteristics 6                   |

| Re-entrant Code                             |

| Data Set Management                         |

| User Commands                               |

| Paging                                      |

| Segmentation                                |

| Equipment Characteristics                   |

| Dynamic Address Translation                 |

| Extended PSW Mode                           |

| High Resolution Interval Timer              |

| Storage Protection Extension                |

| Partitioning                                |

| Floating Addressing                         |

|                                             |

|                                             |

| SYSTEM COMPONENTS                           |

| IBM 2067 Processing Unit                    |

| Processor Storage Addressing                |

| Floating Addressing                         |

| Dynamic Address Translation                 |

| Timing         1         13                 |

| Channel Addressing                          |

| Instruction Fetching and Execution          |

|                                             |

|                                             |

|                                             |

|                                             |

| Interruption Times                          |

| Modified Instructions                       |

| New Instructions                            |

| Arithmetic and Logical Functions            |

| Local Store                                 |

| IBM 2846 Channel Controller                 |

| Storage Selection Element                   |

| Processor Interface Element                 |

| Channel Interruption                        |

| Error Detection                             |

| IBM 2365 Processor Storage                  |

| Priority                                    |

| Access Time                                 |

| Storage Protection                          |

| Partitioning                                |

| IBM 2167 Configuration Unit                 |

| Partitioning Switches                       |

| Control Register Bit Assignment for Sensing |

| SYSTEM CONFIGURATION CHARACTERISTICS                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Configurations                                                                                                                                   |

| System Data Flow                                                                                                                                        |

|                                                                                                                                                         |

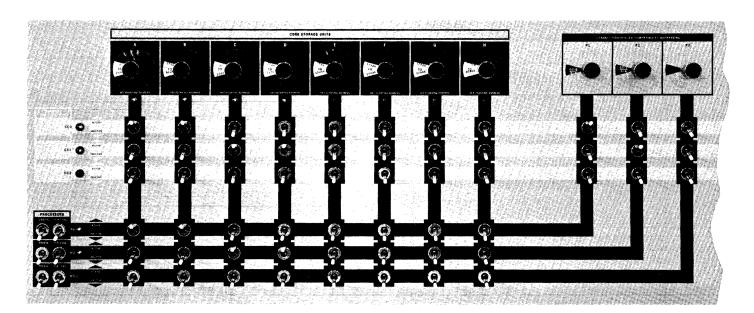

| SYSTEM CONTROL PANEL                                                                                                                                    |

| Operator Intervention Controls                                                                                                                          |

| Start Pushbutton                                                                                                                                        |

| Stop Pushbutton                                                                                                                                         |

| Rate Switch                                                                                                                                             |

| System Reset Pushbutton                                                                                                                                 |

| Check Reset Pushbutton                                                                                                                                  |

| Storage Select Switch (Section F) 40                                                                                                                    |

| Address Switches (Section E)                                                                                                                            |

| Data Switches (Section E) $\ldots$ $\ldots$ $\ldots$ $\ldots$ 40                                                                                        |

| Store Pushbutton $\ldots \ldots \ldots$ |

| Display Pushbutton                                                                                                                                      |

| Address Compare Switch                                                                                                                                  |

| PSW Restart Pushbutton                                                                                                                                  |

| Set IC Pushbutton (Instruction Counter)                                                                                                                 |

| CPU Check Switch                                                                                                                                        |

|                                                                                                                                                         |

| Log Out Pushbutton       42         Stop On Storage Check Switch       42                                                                               |

|                                                                                                                                                         |

| <b>3 1 1 1 1 1 1 1 1 1 1</b>                                                                                                                            |

| Roller Indicators                                                                                                                                       |

| Customer Engineering Control                                                                                                                            |

| Key Switch and Meters                                                                                                                                   |

| INSTRUCTION TIMES                                                                                                                                       |

| Introduction                                                                                                                                            |

| Timing Considerations                                                                                                                                   |

| Timing Assumptions                                                                                                                                      |

| Legends                                                                                                                                                 |

| Legends for Instructions with Multiple Timing Formulas 44                                                                                               |

| Legends for Instructions with Single Timing Formulas 44                                                                                                 |

| Average Instruction Times                                                                                                                               |

| Detailed Instruction Times (Variable Field Length Instructions). 54                                                                                     |

| Timing Formulas for VFL Instructions (Model 67-1) 54                                                                                                    |

| Timing Formulas for VFL Instructions (Model 67-2) 55                                                                                                    |

| I ming formatias for VFL instructions (Model 07-2)                                                                                                      |

| APPENDIX A. SUMMARY OF SYSTEM CONTROL PANEL                                                                                                             |

|                                                                                                                                                         |

| CONTROLS AND INDICATORS                                                                                                                                 |

|                                                                                                                                                         |

| GLOSSARY                                                                                                                                                |

| BIDEI                                                                                                                                                   |

| INDEX                                                                                                                                                   |

## ILLUSTRATIONS

### Figures

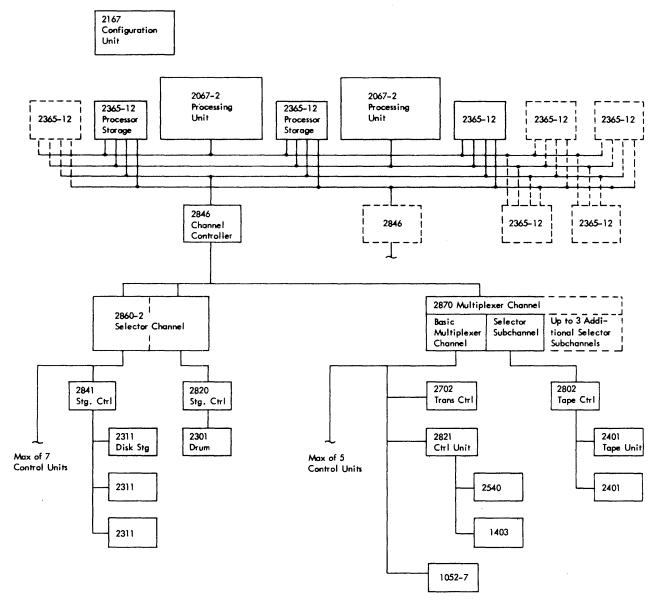

| System/36  | 0 Model 67-2 Duplex Configuration                     | 4 |

|------------|-------------------------------------------------------|---|

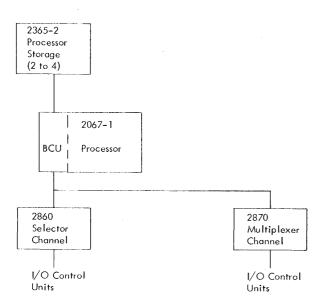

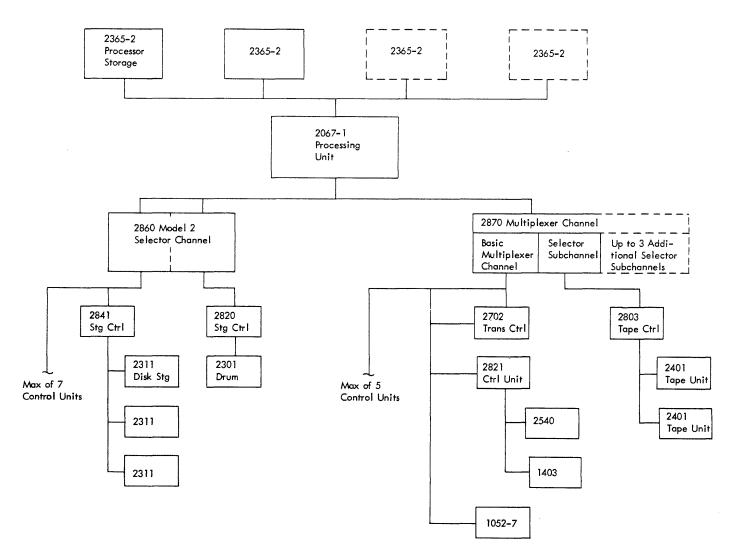

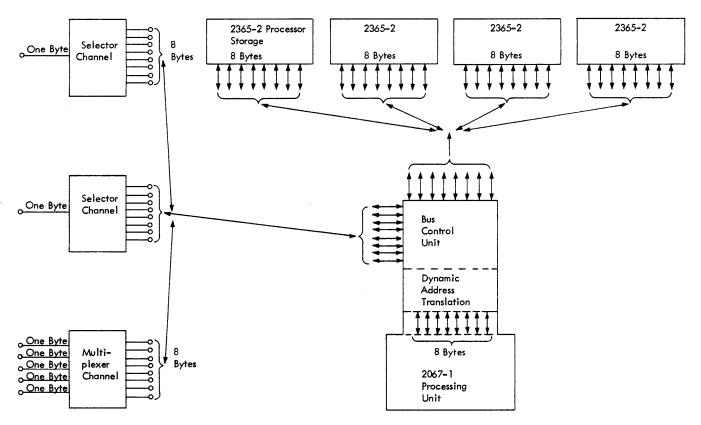

| Figure 1.  | Model 67-1 Configuration                              | 5 |

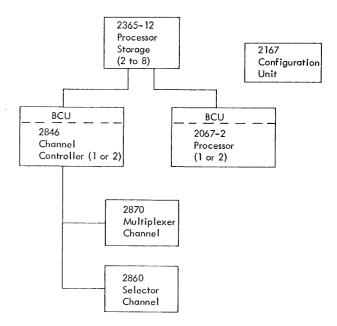

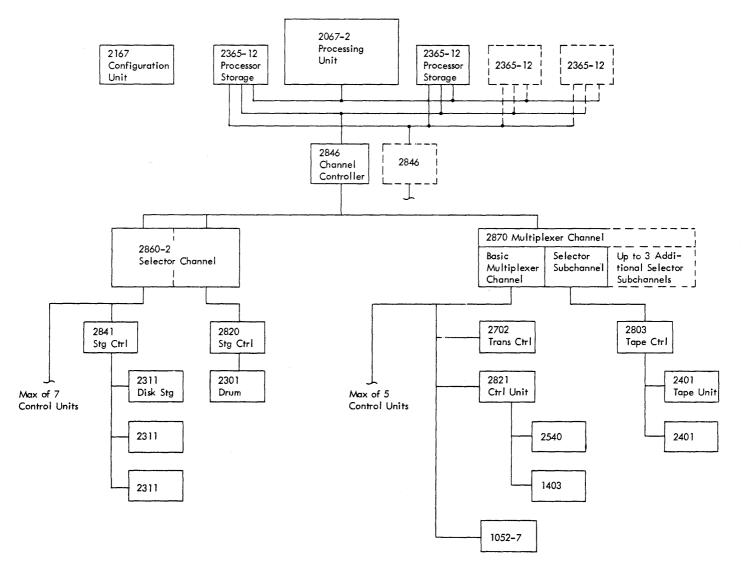

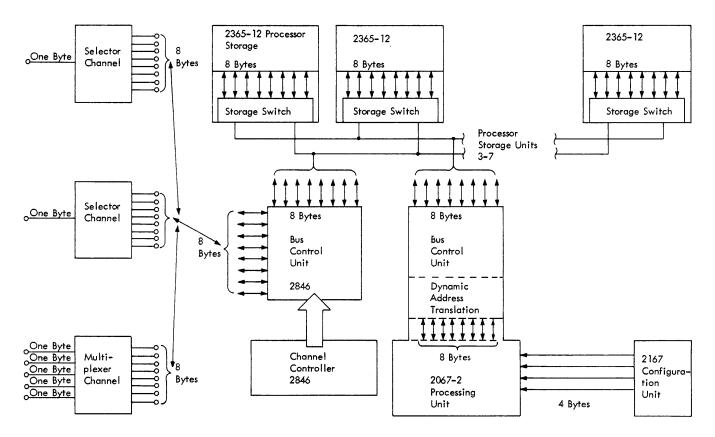

| Figure 2.  | Model 67-2 Configuration                              | 5 |

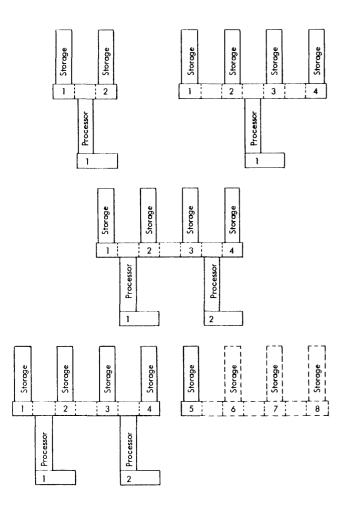

| Figure 3.  | Model 67 Outline Configurations                       | б |

| Figure 4.  | Address Interval Assignment                           | L |

| Figure 5.  | Data Flow for Dynamic Address Translation (24-Bit).   | 2 |

| Figure 6.  | Data Flow for Dynamic Address Translation (32-Bit). 1 | 4 |

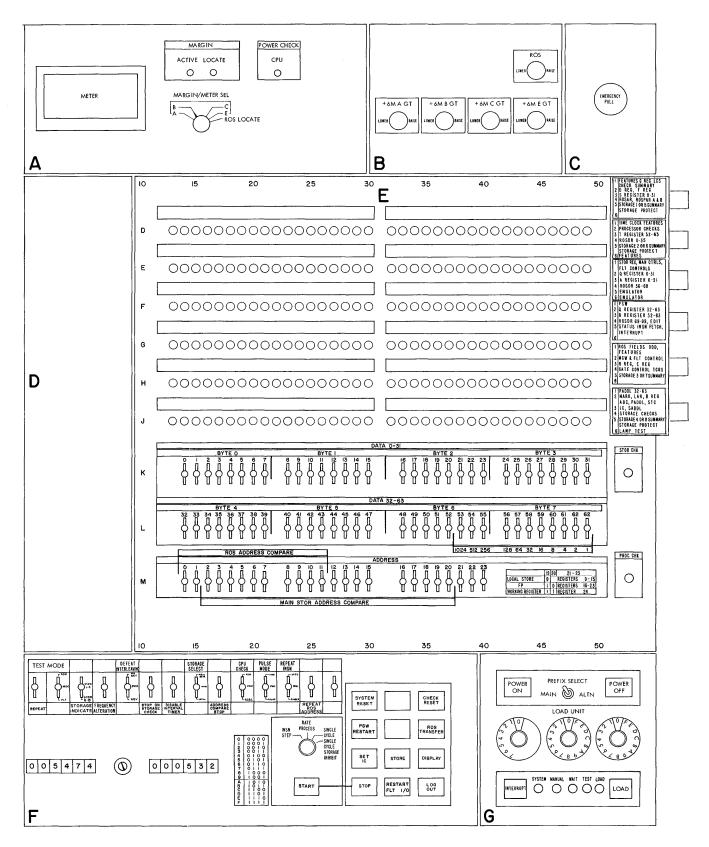

| Figure 7.  | Configuration Unit Control Panel                      | 0 |

| Figure 8.  | Model 67-1 Minimum Configuration                      | 4 |

| Figure 9.  | Model 67-2 Half-Duplex System, Minimum                |   |

| Configurat | tion                                                  | 5 |

# Configuration. 36 Figure 11. Model 67-1 Data Flow Diagram. 37 Figure 12. Model 67-2 Data Flow Diagram. 37 Figure 13. System Control Panel 39 Tables 39 Table 1. Format of Registers and Entries. 11 Table 2. Bit Alignment of Address Arithmetic 13 Table 3. Associative Register Format 13 Table 4. Control Registers. 16 Table 5. Control Register Bit Assignments 31

Figure 10. Model 67-2 Duplex System, Minimum

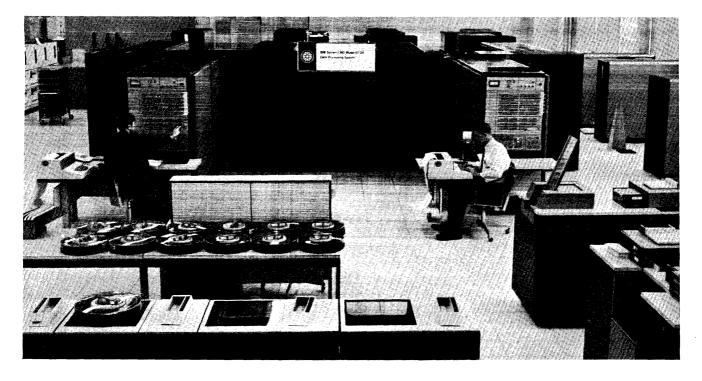

System/360 Model 67-2 Duplex Configuration

IBM System/360 is a versatile, all-purpose family of data processing equipment that can accommodate the wide range of applications which may be encountered in a diversified computing activity. The system is unique in its capability to grow easily with the needs for increased computational capabilities. If particular input/output (I/O) equipment is outgrown, more and/or faster I/O equipment can be added. Also, processor storage capacity can be increased easily. The important point, however, is that any or all of this growth can be accomplished without changes, either in system programming or in problem programming.

The basic architecture of System/360 makes it ideally suited to operate in a multiprogramming and multiprocessing environment, Model 67 extends this basic architecture to provide the additional capabilities of a time-sharing system.

Four new units are introduced by the Model 67:

- 1. The IBM 2067 Processing Unit Models 1 and 2,

- 2. The IBM 2365 Processor Storage Model 12

- 3. The IBM 2846 Channel Controller, and

- 4. The IBM 2167 Configuration Unit.

These new units, together with the IBM 2365 Processor Storage Model 2, 2860 Selector Channel, 2870 Multiplexer Channel, and the wide range of IBM System/360 control units and devices are the building blocks for Model 67 configurations.

There are two models of the Model 67, termed 67-1 and 67-2. The Model 67-1 is a single-processor (simplex) system which uses the 2067-1 (Figure 1),

Figure 1. Model 67-1 Configuration

while the Model 67-2 describes systems using the 2067-2 both in half-duplex (one processor) and in duplex (two processor) configurations (Figure 2). The Model 67-1 cannot be converted to a Model 67-2 in the field.

The outline configurations of the Model 67 produced by the various combinations of a 2365 Processor Storage and 2067 central processing units (CPU's) shown in Figure 3 are only a few of the combinations possible.

The system control panel is located at one end of the 2067. An IBM 1052 Printer-Keyboard can be placed adjacent to the 2067 Processing Unit reading board.

Standard features for any System/360 Model 67 include:

Universal Instruction Set

High-Resolution Interval Timer

7-Bit Storage Protection

24-Bit Dynamic Address Translation

Optional features for System/360 Model 67 include: Extended Dynamic Address Translation

709/7040/7044/7090/7094/7094II Compatibility 1052 Adapter

Floating Storage Addressing (2067-1 only)

Direct Control (2067-1 only)

Extended Direct Control (2067-2 only)

Partitioning Sensing (2067-2 only)

- Additional 2846 Attachment (2067-2 only)

- Additional Addressing (2067-2 only)

Figure 2. Model 67-2 Configuration

System Description

Figure 3. Model 67 Outline Configurations

A variety of control units and I/O devices are available for use with the Model 67. Descriptions of specific I/O devices appear in separate publications. Configurators for the I/O devices and systems components are also available. See <u>IBM System/360 Bibliography</u>, Form A22-6822.

Model 67 is a general-purpose computing system which provides the user of an I/O device, called a "terminal", with the use of the system at times and places of his choosing.

A general-purpose computing system is one which will accommodate a variety of problems, expressed in several languages (including the language of the computer itself), and introduced from different sources. Model 67 provides:

• On-Line Capability -- The Model 67 couples users of computation facilities more closely to computer systems. This close user-system contact does not require physical proximity of the terminals; communication lines, dial connections, or similar apparatus of communications technology can be used in the system to convey computational power over any distance. The online capability makes possible the functions of console type debugging techniques, conversational mode of operation, and the immediate utilization of many short duration "shots" on the facility without significant delay. To enhance this on-line capability, the system employs large-capacity, direct-access storage devices to provide access both to the data bases and to programs of interest to the users.

- Multiple-Access Capability -- Many users share the total system facility concurrently. One reason for providing multiple access in on-line systems is that, typically, one user does not continually require the total system facility. Without the multiple-access capability, a brief pause by a user would idle the entire system. With the multiple-access capability, pauses serve other uses. Since the cost of doing this is small compared to the facility time recovered, it is profitable, therefore, to have the capability of serving many users simultaneously.

- Multiprocessor Capability -- For multiprocessor configurations, parallel operation is the normal mode of the system. During parallel processor operations, two CPU's can execute the same monitor simultaneously, independently executing programs, accessing storage, and controlling input/output. Since the monitor program is not changed by execution, simultaneous usage presents no problems.

- Time-Slicing Capability -- Many different tasks are interleaved by using a timing mechanism to signal the end of the time interval given to one task and to permit the transfer of a CPU to another task. Each user receives a slice of computer time periodically, and within a short cycle of time all users are responded to in some sense.

Time sharing is characterized by the time-slicing capability. Time slicing, in conjunction with the supervisor program scheduling and dispatching routines, enhances the Model 67s ability to operate as a conventional batch processing system and as a conversational mode processor.

### PROGRAM CHARACTERISTICS

Several highlights of Time Sharing System/360 (TSS/360) are described in the following paragraphs; TSS/360 is described in greater detail in the <u>IBM</u> <u>System/360 Time Sharing System Concepts and Facilities</u>, Form C28-2003.

### Re-entrant Code

Much of the coding in the time-sharing system is reentrant. Since a re-entrant program is not modified in any way by execution, it can be shared by several other programs that can be executed by one or more processors. All parameters, data locations, and working storage spaces are passed to the re-entrant program. The integrity of each user's data is maintained regardless of the number of users who have entered the program.

Re-entrant coding of programs enhances system efficiency because only one copy of a multiple-usage program or subroutine need be present in processor storage.

### Data Set Management

To the user, the computing system can be a file space as well as a computing device. The user need not keep programs (problem statements) or data files at his location. These can be introduced into the system, left in, and recalled and manipulated at will.

To maintain large sets of files with complete safety and security, the system contains a catalog of all data files within its storage devices, and provides many modes of protection for these files. A user can specify that his files be accessible only to himself, or be accessable only to specific individuals other than himself. Various modes of access can be specified, for read-only purposes and for both reading and writing.

### User Commands

A terminal user can request the system to take certain actions in his behalf. Each action that he can specify is a command which, in the case of a typewriter-like terminal, is a one-line message. Commands are always acted upon by the Command-Language Interpreter, which receives the incoming message, scans it to determine the nature of the action requested, and fetches from the system files the command program that will carry out the action.

The command system (the set of actions that the Command-Language Interpreter can recognize) provides the capability for a program to be:

- 1. Entered from the terminal, line by line with immediate diagnostic feedback from the system after each line.

- 2. Cataloged, stored permanently in the system for later manipulation, and then made part of the user's prestored library.

- 3. Compiled or assembled.

- 4. Executed.

The user appears to the system as an active terminal that is presenting a series of tasks to be performed. As long as these tasks are system commands, the system fetches its own programs and executes them on behalf of the user. System commands are similar to user programs in that they are time shared and multiprogrammed during execution. When the user initiates execution of his own program, he retains complete control over it. Thus the command system also allows a program to be:

- Stopped

- Modified or displayed (for debugging purposes)

- Restarted

- Terminated.

Beyond the basic capabilities of entering, executing, and controlling programs from terminals, the command system provides for system accounting and file maintenance.

### System Accounting

A user must LOGON at a terminal before any other action can be taken, and LOGOFF when his terminal operations are complete. These commands identify the user to the system and initiate time charges to the user for services rendered. If, in succeeding commands, he requests access to files, his identity will be matched against file-protection and security data, to insure file integrity and to prohibit unauthorized access to files.

### File Maintenance

A user can request that his files be moved from one storage unit to another or be removed from the system. He can also modify them, combine them, or change their protection status. Commands can be initiated from terminals, as previously described, or they can in most cases be embedded in programs as the equivalent of subroutine calls. Commands can also be included as "control card" functions to specify the type of processing to be applied to batch jobs entering the system.

The command system allows the user to direct the system in its manipulation of files and in the solution to problems. More than this, however, it is the universal interface between the system and the outside world. From the machine-room console, for example, installation personnel control recovery functions of the system, using special commands reserved only for their use. Batch jobs entering the system from peripheral equipment or tape drives are controlled by the command system.

### Paging

Every program using the system is treated as a sequence of 4096-byte units called "pages". By dividing programs up into pages, processor storage can be allocated in page (4096-byte) increments. Program pages, therefore, can be located randomly throughout core storage and swapped in and out of processor storage as pages are needed, commensurate with available space. Random location of pages for a given program necessitates the construction of tables (page tables) that reflect the processor storage location of the pages. The swapping of pages between auxiliary storage and processor storage is defined as "page turning". If a page of instructions refers to a program location not currently in processor storage, the system will stop operating the program temporarily, make arrangements to fetch the page from auxiliary storage (the disk and drum storage space reserved specifically for paging), and perform other operations in the interim.

Page turning has the following advantages:

- 1. The entire program need not be in core storage to operate. Parts of many programs can be present, and several may be ready for processing. Thus, the system has many opportunities to do useful work while a page is being swapped.

- 2. Program "swap time" is reduced as an overhead factor since only active pages of a program require movement between core storage and auxiliary storage.

- 3. Although written and executed as a classical set of contiguous instructions and working space, a program can exist in the machine as scattered active pages.

The programmer's concept of the program being executed is of a "virtual storage" rather than of an actual processor storage situation.

The user's virtual storage is the contiguous address space that would be needed to store the user's program. This virtual storage is not limited by actual processor storage size but is limited only by the available auxiliary (disk and drum) space. Theoretically, the programmer has 16 million bytes (24-bit addressing) or up to 4 billion bytes (optional 32-bit addressing) of virtual storage at his disposal.

### Segmentation

System/360 24-bit addressing enables a 4096-page virtual storage. Virtual storage has been divided into 16 segments containing 256 pages each. A segment table with only 16 entries accounts for all virtual storage. When a page of the user's program is moved from virtual storage to processor storage, the location of the page is recorded in a page table. The entries in

the page table are sequential by virtual address. The location of the page table is recorded in the segment table.

Since each segment contains 256 pages, the page table cannot contain more than 256 entries. If the program occupies more than one segment of virtual storage, a page table is established for each segment as its pages are moved to processor storage. Many segments can be used to organize a user program in virtual storage. Large working areas can be assigned virtual storage space. However, only an actual reference to a segment will result in the generation of a page table for that segment. This avoids reserving large areas in page tables for pages not currently in use.

### EQUIPMENT CHARACTERISTICS

### Dynamic Address Translation

Dynamic address translation is the process of converting virtual addresses into actual processor storage addresses during instruction execution. A bit in the program status word (PSW) determines if translation is active or inactive. The translation feature is implemented in hardware in the processor. All processor storage addresses that originate from the processor, except for hardware generated addresses (PSW, etc.), are subject to translation. Storage addresses originating from the channels are not subject to translation. The basic feature provides for 24-bit addresses, whereas an optional feature provides translation for either 24-bit or 32-bit addresses.

Prefixing as described in the <u>IBM System/360</u> <u>Principles of Operation</u> manual is applied to each address after translation; i.e., if the translated address is in the range 0-4095, the address may be further modified under control of prefixing. Prefixing can be deactivated by a manual switch.

Programming Note: Primary and alternate prefix areas must not be assigned within the first 72K bytes of physical storage.

### Extended PSW Mode

The Model 67 can operate under control of Operating System/360 (OS/360, standard PSW mode) or under control of TSS/360 (extended PSW mode). Up to fourteen channels can be attached in duplex configurations of the Model 67. Since this extended I/O capability requires additional interrupt masking capability, additional control registers have been implemented in the processor; TSS/360 utilizes this additional capability by operating the Model 67 in the extended PSW mode. In addition, the PSW is redefined when the Model 67 is operating in extended PSW mode.

### High Resolution Interval Timer

An interval timer with a high degree of resolution has been implemented in the processor. This timer supports the time slicing technique, and is used with the TSS/360 dispatching and scheduling routines to signal the end of the time interval allotted to a given task. The operation of this timer is fully compatible with the timer operation described in the <u>IBM System/360</u> <u>Principles of Operation manual</u>.

### Storage Protection Extension

Additional capability has been implemented in the storage protection circuitry. The extended field of the storage protection key allows TSS/360 to evaluate the utilization of storage. If a reference is made to any location within a given block of storage, that fact is recorded in the protection key for that block. If the reference is a store operation, that fact is also recorded in the protection key. This recording is always active and is independent of the CPU state of the instruction or command being executed or of the manner in which the address is generated. The recorded information is accessable to the standard 'insert storage key' instruction. The increased field size affects only the set storage key and 'insert storage key' instructions; the size of the PSW and channel address word (CAW) protection key fields are unchanged.

### Partitioning

Partitioning is the division of a duplex configuration into two isolated subsystems. Partitioned units are made unavailable to part of the system for programmed control. This facility is implemented in units that have more than one interface to a processorcontrolled subsystem. Each interface is equipped with a manual switch. This switch, together with a configuration-control bit in the processor and the "wait" state of the processor, control the partitioned status of all units in the system. Each processor can sense the status of all partitioning switches, regardless of the partitioned status of the processor.

### Floating Addressing

### Processor Storage

In a duplex configuration, the total bank of high speed processor storage is composed of several individual shared storage units. Each storage unit contains an increment of the total storage capacity in consecutive, unique addresses. In a time shared system, this bank of storage is exposed to partitioning into several parts for use by independent subsystems. Thus, each unit can be reassigned any one of the address intervals possible in the given system. For example, configurations of four storage units providing a total of 1024K bytes of processor storage could be addressed as follows:

| C (;                          | Address Interval |           |           |            |  |  |

|-------------------------------|------------------|-----------|-----------|------------|--|--|

| Configuration                 | Unit A           | Unit B    | Unit C    | Unit D     |  |  |

| Unpartitioned                 | 000-256K         | 256K-512K | 512K-768K | 768K-1024K |  |  |

| Partitioned                   | 000-256K         | 256K-512K | 000-256K  | 256K-512K  |  |  |

| Unit A Out for<br>Maintenance |                  | 000-256K  | 256K-512K | 512K-768K  |  |  |

Many different arrangements are possible, especially with a system that has as many as eight processor storage units. A single unit can be shared by two subsystems, or more than one unit can be shared by two subsystems. The example shows that more than one unit can contain the same address interval. Partitioning controls prevent a single address from acessing two units that contain the same address interval. In a single-processor configuration, the floating addressing capability is invoked when address reassignment is needed because a processor storage unit has failed.

### Channel

In a duplex system, channels are controlled and attached to the system via a Channel Controller (see Figure 2). Channel addressing is defined by the Channel Controller to which a given channel is attached; for example, channels 0-6 are attached to Channel Controller 0, channels 8-14 are attached to Channel Controller 1. This kind of channel addressing is possible with TSS/360 if the CPU is in extended PSW mode operation. Channels are addressed as 0-6 when the system is operating in standard PSW mode (OS/360).

Floating channel addressing permits addresses 0-6 to be assigned to either Channel Controller; for example, a partitioned system that contains Channel Controller 1 (channel addresses 8-14) can be assigned channel addresses 0-6. Therefore, OS/360 can be run on either subsystem, and TSS/360, OS/360, or a maintenance function can occupy the remaining subsystem.

### SYSTEM COMPONENTS

Four new units are introduced by the Model 67.

- 1. IBM 2067 Processing Unit

- 2. IBM 2846 Channel Controller

- 3. IBM 2167 Configuration Unit

- 4. IBM 2365 Processor Storage Model 12

The following paragraphs contain a detailed description of these units.

### IBM 2067 PROCESSING UNIT

The IBM 2067 Processing Unit is available in two models. The 2067-1 is used for single processor configurations only. It is characterized by direct attachment of up to seven channels, storage control both for the processor and for channels, and a direct control feature capable of controlling and/or synchronizing special external devices. The 2067-2, designed for use in duplex configurations, is characterized by addressing capability for 14 I/O channels, attachment of a maximum of two Channel Controller units. processor storage control, and an extended direct control feature capable of communicating control information between two 2067-2s. When a 2067-1 is used. the configuration is called a Model 67-1 system: when two or more 2067 Model 2s are used, the configuration is called a Model 67-2 system. These systems are shown in Figures 1 and 2.

The 2067 contains the facilities for (1) addressing processor storage, (2) instruction decoding and execution, and (3) performing arithmetic and logical functions. Except where otherwise noted, the following descriptions apply to both models of the 2067 and to 24-bit addressing.

### Processor Storage Addressing

The Bus Control Unit (BCU) located in the CPU controls processor storage addressing. Addresses are communicated to processor storage via a storage address bus (a multiplex bus since it is connected from the BCU to each Processor Storage Unit in a chain-like fashion). The BCU sends a select storage signal to each Processor Storage Unit; this signal requests a storage cycle and identifies the storage unit which is to sample the address bus.

One difference between the 2067-1 and the 2067-2

is the functions performed by the BCU. In the 2067-1, the BCU provides access to processor storage both for processor references and for channel requests. The 2067-2 BCU accesses processor storage for the CPU only. In configurations using a 2067-2, channel requests are communicated to processor storage via the Channel Controller.

When handling CPU storage requests, the BCU stops the CPU clock when the channel has taken priority, when the referenced Processor Storage Unit is busy, or when the data required on a fetch cycle has not arrived in the time expected by the CPU.

### Floating Addressing

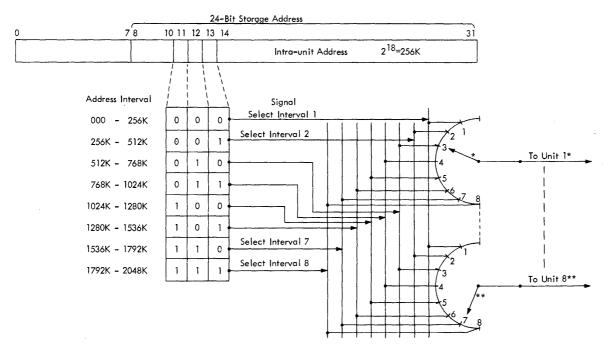

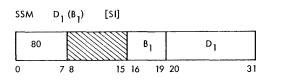

Floating storage addressing switches distribute select signals to the appropriate Processor Storage Unit. One eight position switch is associated with each Processor Storage Unit. These positions correspond to the address intervals possible in any system. A 3-bit field from the actual address is decoded into one of the eight possible selection signals (Figure 4). The unit associated with the switch that is selecting the interval will (1) receive the request for a storage cycle and (2) sample the address from the address bus when the request is honored. This decoding and selection is accomplished in the BCU of the CPU and Channel Controller.

### Dynamic Address Translation

Another factor affecting the addressing of processor storage is dynamic address translation, which records the relationship between the virtual address and the physical storage address used. This record is important to the segmentation and paging techniques previously described. The processor storage location of each user's page is recorded sequentially in a page table by virtual storage address. The page table's starting address is recorded in the user's segment table (Table 1) which is loaded in processor storage. Each time the user is given control of the processor, the starting address of the segment table is loaded into control register 0 (the segment table register) by the control program.

\* Storage unit 1 will be selected by addresses between 562K and 768K.

\*\* Storage unit 8 will be selected by addresses between 1563K and 1792K.

Figure 4. Address Interval Assignment

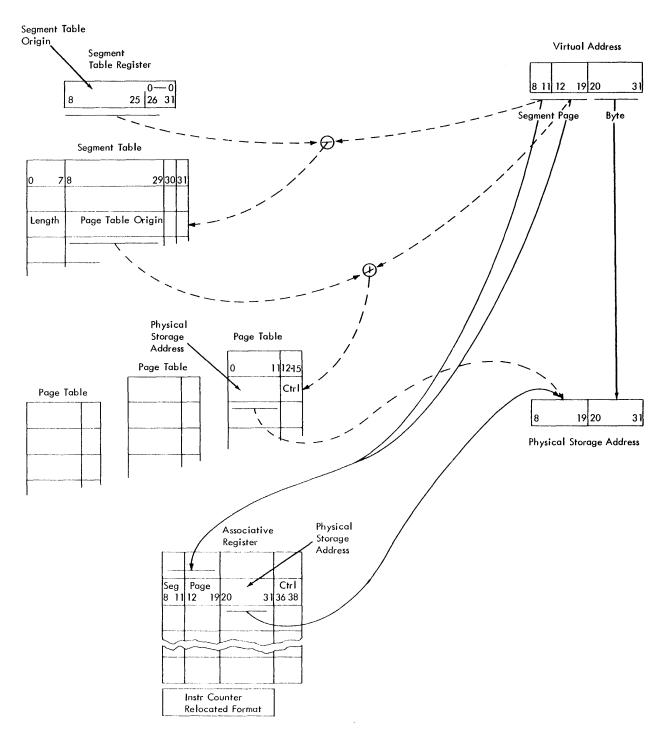

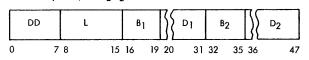

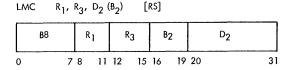

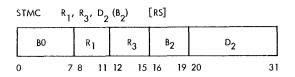

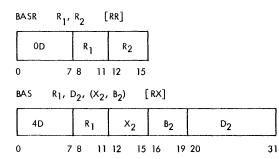

The virtual address operand is formed from the base address, index, and/or displacement as determined by the instruction format. The resulting virtual operand address has three parts:

|   |    | Segment<br>Address | Page<br>Addres | s  |    | Byte<br>Address |    |

|---|----|--------------------|----------------|----|----|-----------------|----|

| 0 | 78 | 11                 | 12             | 19 | 20 |                 | 31 |

Each part of this virtual address is used to retrieve the physical address of the operand (Figure 5).

The physical address of the operand consists of a byte address (12 low-order bits) and a page address (12 high-order bits). Bits 20-31 of the virtual address provide the byte address and bits 0-11 of a page table entry are the source of the page address. The segment address and page addresses in the virtual address are used to locate the appropriate page table entry.

The segment table register (control register 0) contains the address, in processor storage, of the segment table. The segment table contains one entry for each segment (this entry is the address of the page table for that segment). The segment address (from the virtual address) is added to the segment table origin to locate the page table origin for that segment.

### Table 1. Format of Registers and Entries

1.

2.

З.

| Bits   | Meaning                        | Remarks                                                                                          |  |  |  |  |

|--------|--------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| Segme  | Segment Table Register Format: |                                                                                                  |  |  |  |  |

| 0-7    | Segment Table Length*          | Indicates the number of 16–entry<br>groups in the segment table .<br>All zero = One group .      |  |  |  |  |

| 8-31   | Segment Table Origin           | Since the segment table origin is<br>located on a 64-byte boundary,<br>bits 26-31 must be zero . |  |  |  |  |

| Segme  | nt Table Entry Format:         |                                                                                                  |  |  |  |  |

| 0-7    | Page Table Length              | Indicates the number of entries in<br>the page table.<br>All zero = One entry.                   |  |  |  |  |

| 8-30   | Page Table Origin              | The page table origin is located on a 2-byte boundary.                                           |  |  |  |  |

| 31     | Page Table Availability        | 1 = Segment translation exception<br>(program interrupt code 16).                                |  |  |  |  |

| Page 1 | Table Entry (Halfword):        |                                                                                                  |  |  |  |  |

| 0-11   | Physical Block Address         | Starting addresses of page.                                                                      |  |  |  |  |

| 12     | Page Availability              | 1 = Page translation exception<br>(program interrupt code 17).                                   |  |  |  |  |

| 13-15  | Control Bits, Reserved         | Must be 000 or specification exception.                                                          |  |  |  |  |

|        |                                |                                                                                                  |  |  |  |  |

\* Used only with CPU's that contain the 32-bit addressing feature.

Figure 5. Data Flow for Dynamic Address Translation (24-Bit)

Then, the page address (from the virtual address) is added to the page table origin. This locates the physical starting address of the page in processor storage. (The page table contains a maximum of one entry for each page in the segment.) The byte address from the virtual address is then combined with the page starting address to form the physical operand address (Table 2).

To avoid repeating this translation process for every memory reference by a user program, the page table entry (page starting address, bits 8-19) is recorded with, and identified by, its virtual address

### Table 2. Bit Alignment of Address Arithmetic

### 1. Segment Table Entry Address

| Bits<br>(24–Bit Mode) | Meaning                     | Remarks                                             |

|-----------------------|-----------------------------|-----------------------------------------------------|

| 8-31                  | Table Origin                | Bits 26-31 are considered zero.                     |

| 8-11                  | Added to Logical<br>Address | Aligned with 26–29 of segment table origin.         |

| 8-31                  | Yields Sum                  | Segment table entry address<br>(30–31 always zero). |

| Bits<br>32-Bit Mode)  | Meaning                     | Remarks                                             |

| 8-31                  | Table Origin                | 26-31 are considered zero.                          |

| 0-11                  | Added to Logical<br>Address | Aligned with 18–29 of segment<br>table origin.      |

| 8-31                  | Yields Sum                  | Segment table entry address<br>(30–31 always zero). |

2. Page Table Entry Address - Either 24- or 32-Bit Mode

| Bits  | Meaning                     | Remarks                                          |

|-------|-----------------------------|--------------------------------------------------|

| 8-31  | Page Table Origin           | 31 is considered zero.                           |

| 12-19 | Added to Logical<br>Address | Aligned with 23–30 of page<br>table origin.      |

| 8-31  | Yields Sum                  | Page table entry address (31 is<br>always zero). |

3. Physical Address Result

|   | Bits  | Meaning          | Remarks                       |

|---|-------|------------------|-------------------------------|

|   | 0-11  | Page Table Entry | The high-order portion.       |

| • | 20-31 | Logical Address  | The low-order portion.        |

|   | 8-31  | Physical Address | Both portions taken together. |

(segment and page address, bits 8-19) in an associative storage register. If a subsequent reference is within that virtual page, the virtual address accesses the associative register. The page starting address stored in the register is affixed to the byte address and forwarded to the BCU.

Eight associative storage registers are in the associative array; each stores an individual page address (Table 3). Bits 36 and 37 of each register reflect the validity and the usage of that entry, respectively. Both bits are set to 1 when the register is loaded, and both are reset to 0 when the segment table register (control register 0) contents are changed. If, within a user's time slice, eight separate pages are referenced (i.e., all associative registers have been loaded and each bit 37 is a 1), all bit 37s are reset to 0. Subsequent references to a register will cause bit 37 for that register to be set. During subsequent translations, the result will be loaded into the lowest-numbered register that has a

### Table 3. Associative Register Format

### 24-Bit Addressing:

| Bits          | Content                                    | Remarks                                                                                                      |

|---------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 8-19          | Virtual Address                            |                                                                                                              |

| 20-31         | Physical Address                           | The page address from a previous<br>translation which corresponds to<br>the virtual address in bits<br>8–19. |

| 32-35         | Unassigned*                                |                                                                                                              |

| 36            | Register Valid                             | Set to 1 upon loading the register.                                                                          |

| 37            | Recent Usage –<br>"Load"                   | Set to 1 upon loading the register and upon any use thereafter.                                              |

| 38            | Disable                                    | Set with special diagnose codes<br>8–15.                                                                     |

| 32-Bit Addres | sing: Same as above ex<br>is in bits 0–19. | cept for virtual address, which                                                                              |

\* For expansion; not physically implemented.

0 in a bit 37. Bit 37 is set to a 1 as a result of this load. With this technique, the associative array always contains the most recent and/or most frequently used page addresses.

Since instructions frequently occur in sequence, an "IC register" is implemented to hold and provide the translated page address for use in serial instruction sequences; this avoids repeated accesses of the page address from the associative array.

Dynamic address translation applies only when the CPU is operating in extended PSW mode. Bit 5 of the extended PSW controls whether translation is active (bit 5=1) or inactive. When translation is active, all program-generated processor storage addresses originating from the CPU are subject to translation; hardware-generated addresses (e.g., from timer, new PSW fetch, old PSW store, etc.) and storage addresses originating from the channels are not subject to translation.

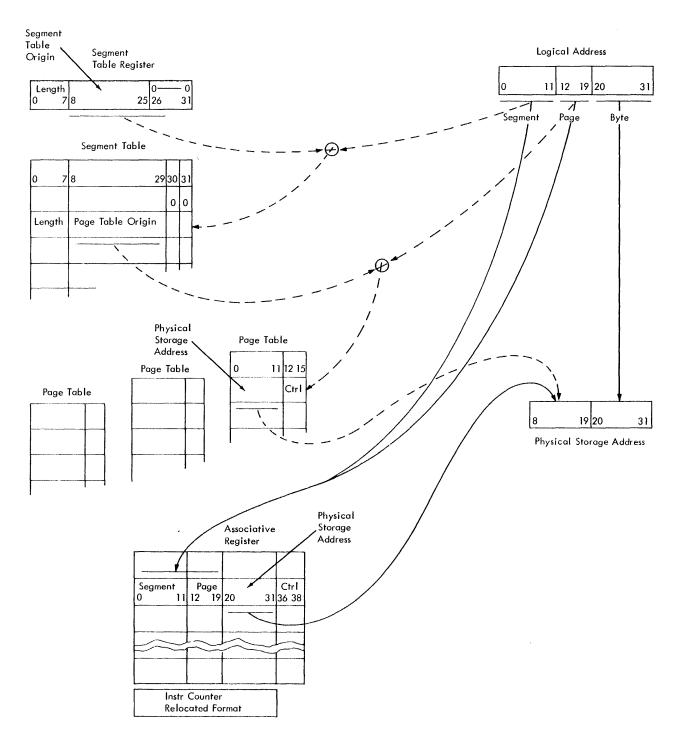

Prefixing is applied to the address after translation. If the translated address is in the range of 0-4095, further address modification under control of prefixing might occur. A switch on the 2167 control panel can be used to manually deactivate prefixing. The basic prefixing feature provides translation for 24-bit addresses, whereas an optional feature provides translation for either 24-bit or 32-bit addresses (Figure 6). Bit 4 of the extended PSW indicates whether 24-bit or 32-bit address computation arithmetic should apply.

### Timing

Instruction execution timing in the 2067 is affected by the dynamic address translation process as follows.

Figure 6. Data Flow for Dynamic Address Translation (32-Bit)

When dynamic address translation is active and the translated address is in the associative array, no table references are required. The necessary physical address is made available in 150 nsec, thus adding 150 nsec to each storage reference for an operand. Consecutive instructions addressed sequentially incur the additional 150 nsec on the first array reference only. Succeeding instructions in the sequence use the translated address from the instruction counter register which adds no additional time to the operand reference.

Instructions which are located in a different page,

or which are in the same page block but are reached by branching require either the 150 nsec as above, or the longer lookup time as described in the following paragraph.

When address translation is active and the physical address is not in the associative array, translation is obtained through two storage references. Thus, the approximate time required is: (1) two storage references, one each for segment table and page table entries, plus (2) the storage reference for data, plus (3) 750 nsec. The exact time depends on the other CPU or Channel Controllers requiring access to the same storage unit during the translation operation.

### **Channel Addressing**

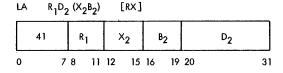

The 2067-1 can attach up to six selector channels and one multiplexer channel. Channel and device addressing is performed as described in the <u>IBM System/360</u> <u>Principles of Operation</u> manual. There is very little difference in channel address handling when the 2067-1 is operating in standard PSW mode or in extended PSW mode.

The 2067-2 can attach two Channel Controllers, each of which can attach up to seven channels. Channel addressing is preceded by selection of a Channel Controller. The channel address field of the effective address formed by an I/O instruction is expanded to provide for Channel Controller addressing. In the extended PSW mode of operation, bits 16-20 of the effective address are decoded to select one Channel Controller. Addresses 00100 through 11111 are decoded as invalid channel addresses. Instructions that specify these addresses are terminated without selection of a 2846, and condition code 3 is set into the PSW.

When the 2067 is operating in standard PSW mode, the channel controller compatibility addressing switch controls selection of a Channel Controller. The setting of this switch determines the Channel Controller to which the start I/O signal, I/O interrupt mask bits, channel and device addresses, etc. will be distributed. Since either Channel Controller can be selected for use by the CPU that is operating in standard PSW mode, I/O instructions in programs that operate in standard PSW mode must address Channel Controller 0 (i.e., bits 16-20 of the channel address field must be 0s).

When the system is in the standard PSW mode, the storage protection key is sent to the Channel Controller specified by the channel controller compatibility addressing switch.

### Instruction Fetching and Execution

The PSW controls instruction sequencing and holds and indicates the status of the system relative to the program currently being executed. When operating in the standard PSW mode, the PSW format is identical to the format described in the <u>IBM System/360</u> <u>Principles of Operation</u> manual. The PSW format is redefined as follows when operating in the extended PSW mode:

| Spare            | Bit I I     | /O Ext.<br>Mask Mask   | Protec.<br>Key   | AMWP   | ILC   | cc    | Prog .<br>Mask | Spare   |

|------------------|-------------|------------------------|------------------|--------|-------|-------|----------------|---------|

| 0 3              | 4 5         | 6 7                    | 8 11             | 12 15  | 16 17 | 18 19 | 20 23          | 24 31   |

| $\left( \right)$ |             | Instructi              | on Addre         | \$5    |       |       |                |         |

| 32               |             |                        |                  |        |       |       |                | ]<br>63 |

| Bit              | Meaning     |                        |                  |        |       |       |                |         |

| 0-3              | Spare (must | t be 0 s)              |                  |        |       |       |                |         |

| 4                | 24-32 Bit A | Address Mod            | de               |        |       |       |                |         |

| 5                | Translation | Control                |                  |        |       |       |                |         |

| 6                | I/O Mask (  | (Summary)              |                  |        |       |       |                |         |

| 7                | External M  | ask (Summa             | ıry)             |        |       |       |                |         |

| 8-11             | Protection  | Key                    |                  |        |       |       |                |         |

| 12               | ASCII-8 M   | ASCII-8 Mode (A)       |                  |        |       |       |                |         |

| 13               | Machine C   | Machine Check Mask (M) |                  |        |       |       |                |         |

| 14               | Wait State  | Wait State (W)         |                  |        |       |       |                |         |

| 15               | Problem Sto | Problem State (P)      |                  |        |       |       |                |         |

| 16-17            | Instruction | Length Coo             | le (ILC)         |        |       |       |                |         |

| 18-19            | Condition ( | Code (CC)              |                  |        |       |       |                |         |

| 20-23            | Program Mo  | isk:                   |                  |        |       |       |                |         |

|                  | 20          | Fixed Point            | Overflo          | w Mask |       |       |                |         |

|                  | 21          | Decimal O              | verflow <i>I</i> | Mask   |       |       |                |         |

|                  | 22          | Exponent U             | Inderflow        | Mask   |       |       |                |         |

|                  | 23          | Significanc            | e Mask           |        |       |       |                |         |

| 24-31            | Spare       |                        |                  |        |       |       |                |         |

| 32-63            | Instruction | Address                |                  |        |       |       |                |         |

The content of several PSW fields is further specified, as follows. Unless bits 0-3 are 0s, a specification exception is generated. When the 32bit addressing option is not installed, bit 4 must be 0. Specification exceptions are generated if this format is violated. These specification exceptions are recognized either during the execution of the instruction that follows the loading of the PSW, or following the 'set system mask' instruction.

### Fetching

Instruction fetching by the CPU (1) retrieves machine instructions from the storage units, and (2) performs the operations common to many instructions. More specifically, the instruction fetching process insures a correct value in the instruction counter, fetches instructions from storage, determines the format (RR, RX, RS, SI, and SS) of the fetched instructions, and loads the appropriate registers with operands and data fields. Then control is transferred to the execution phase, in which specific machine instructions are decoded and executed.

Each instruction fetch retrieves one doubleword from storage. Since instructions vary from one to three halfwords in length, as few as  $1 \frac{1}{3}$  instructions (SS format) or as many as four complete instructions (RR format) can be retrieved from the processor storage unit during one fetch operation. The instruction counter is incremented by 8 each fetch operation.

Operands specified by RR format instructions are placed directly into the desired data flow registers during the instruction fetch operation. Operands specified by RX, RS, SI, and SS format instructions require effective address generation; when the effective address is calculated, control is passed to the operations necessary to complete execution of the instruction.

### Execution

Instruction execution is a series of functional operations performed in a specific sequence. These operations are determined by the operation code of the instruction to be executed and by certain other environmental conditions; frequently, the relative importance of these environmental conditions is a function of the type of instruction currently controlling the CPU. Read-only storage (ROS), a fundamental device within the 2067, controls instruction execution. Each ROS address contains predetermined information that is used as required during instruction execution to control data flow. The program does not address ROS; instead, ROS operations are directed by conditions established by specific instructions and/or by their execution. Information in ROS is indestructible, and can be modified only by physically changing the ROS element.

### Interruptions

Since the Model 67 has extended I/O capability with respect to the standard System/360, it has expanded control over I/O interruptions. This control is accomplished by using additional control registers in the 2067. Both logic registers and switch registers

(partitioning switches) are used as control registers (Table 4).

### Table 4. Control Registers

| Register | Bit Position Assignments                                 |                                                                      |  |  |  |  |

|----------|----------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|

| 0        | Segment Table Register (for Dynamic Address Translation) |                                                                      |  |  |  |  |

| 1        | Unassigned*                                              |                                                                      |  |  |  |  |

| 2        | Translation Exc                                          | Translation Exception Address Register                               |  |  |  |  |

| 3        | Unassigned*                                              |                                                                      |  |  |  |  |

| 4        | Extended Mask                                            | Registers for I/O Channel Masks                                      |  |  |  |  |

| 5        | Unassigned*                                              |                                                                      |  |  |  |  |

| 6        | Bits 0, 1:                                               | Machine Check Mask Extensions for<br>Channel Controllers             |  |  |  |  |

|          | Bits 2, 3:                                               | Reserved                                                             |  |  |  |  |

|          | Bits 4-7:                                                | Unassigned*                                                          |  |  |  |  |

|          | Bit 8:                                                   | Extended Control Mode                                                |  |  |  |  |

|          | Bit 9:                                                   | Configuration Control Bit; defines when partitioning can take place. |  |  |  |  |

|          | Bits 10-23:                                              | Unassigned*                                                          |  |  |  |  |

|          | Bits 24-31:                                              | External interruption masking as follows:                            |  |  |  |  |

|          | Bit Position                                             | Interruption Source                                                  |  |  |  |  |

|          | 24                                                       | Timer                                                                |  |  |  |  |

|          | 25                                                       | Interrupt Key                                                        |  |  |  |  |

|          | 26                                                       | Malfunction Alert - CPU 1 (Ext. Sig. 2)                              |  |  |  |  |

|          | 27                                                       | Malfunction Alert - CPU 2 (Ext. Sig. 3)                              |  |  |  |  |

|          | 28                                                       | Reserved (Ext. Sig. 4)                                               |  |  |  |  |

|          | 29                                                       | Reserved (Ext. Sig. 5)                                               |  |  |  |  |

|          | 30                                                       | External Interrupt - CPU 1, 2 (Ext. Sig. 6)                          |  |  |  |  |

|          | 31                                                       | Reserved (Ext. Sig. 7)                                               |  |  |  |  |

| 7        | Unassigned                                               |                                                                      |  |  |  |  |

| 8-14     | Partitioning Se                                          | ensing Registers. See 2167 description for                           |  |  |  |  |

8-14 register layout.

### 15 Unassigned\*

\* For expansion; not physically implemented.

The CPU distributes one machine check mask bit to each Channel Controller. Control register 6 (external machine check mask register) bits 0 and 1 are used for this function. Distribution of these mask bits is not affected by the PSW mode of operation and is independent of the channel controller compatibility addressing switch; PSW bit 13 is a summary mask for all machine check interrupts. The following situations are possible:

| PSW    | Contro                 |    |                                                                                                                                |

|--------|------------------------|----|--------------------------------------------------------------------------------------------------------------------------------|

| Bit 13 | Regist<br><u>Bit 0</u> |    | Remarks                                                                                                                        |

| 0      | х                      | х  | Regardless of the status of<br>bits 0 and 1 of control regis-<br>ter 6, all machine checks<br>are masked off by PSW bit<br>13. |

| 1      | 0                      | 0  | Only CPU machine checks will be recognized.                                                                                    |

| 1      | 0                      | 1  | CPU and Channel Controller<br>1 machine checks will be<br>recognized.                                                          |

| 1      | 1                      | 0  | CPU and Channel Controller<br>0 machine checks will be<br>recognized.                                                          |

| 1      | 1*                     | 1* | All machine checks will be recognized.                                                                                         |

\*These bits are set to 1 by system reset. Program systems, other than TSS/360, that do not contain instructions for modifying control register 6 must use PSW bit 13 for control over machine check interruptions.

Control register 6 also contains external interrupt mask bits. This field is added to control register 6 by the extended direct control feature. Bits 24 through 31 of control register 6 are always active as mask bits and are not affected by mode changes of the PSW. They are all set to 1 by system reset, power on reset, initial program load, IPL and external start. Bit 7 of either PSW is a summary mask for external interrupts; it must be a 1 for any external interrupts to be recognized.

The Model 67 is compatible with the interrupt capabilities described in the <u>IBM System/360 Principles of Operation</u> manual. In addition, the following program- and machine-check interruptions are recognized.

### **Program Interruptions**

<u>Specification Exception</u>: A specification exception (interruption code 6) also is recognized:

1. When bit 4 of the extended PSW is a 1 when

the 32-bit addressing option is not installed.

- 2. When bits 0-3 of the extended mode PSW are not 0s, or

- 3. When bits 13-15 of the page table entry accessed during an address translation are not 0s.

Specification exceptions relating to the extended PSW are recognized during execution of the instruction that follows the loading of the PSW or follows the 'set system mask' instruction. For the situation listed as item 3 above, the operation is suppressed. The instruction length code is 1, 2, or 3.

- Data Exception: Data exception (interruption code 7) is also generated if bits 26-31 of the segment table register (control register 0) are not 0s. It is recognized following execution of the instruction that loads the segment table register. When data exception is recognized, the resulting interrupt request is handled as described in the IBM System/360 Principles of Operation manual. The operation is terminated, and the instruction length code is 2.

- <u>New Exceptions:</u> Because of dynamic address translation, two entries are added to the list of program interruptions:

| Int | erruptic | on Code   |                               |

|-----|----------|-----------|-------------------------------|

| Dec | Hex      | Binary    | Program Interruption<br>Cause |

| 16  | 10       | 0001 0000 | Segment Translation           |

| 17  | 11       | 0001 0001 | Page Translation              |

A segment-translation exception is recognized:

- 1. When 32-bit addressing (bits 0-7 of the segment table register indicate the segment table length) and the quantity in bits 0-7 of the logical address is greater than the segment table length, or

- 2. When the segment table entry is accessed and bit 31 is a 1. (Bit 31 indicates the availability of a page table for that segment, and is 0 when a page table has been established for that segment.)

A page-translation exception is recognized:

- When the quantity in bits 12-19 of the logical address is greater than the page table length. (The quantity in bits 0-7 of the segment table entry is the page table length.)

- 2. When the page table entry is accessed and bit 12 is a 1. (Bit 12 of the page table entry, the availability bit, is 0 when the page represented by that entry is in the core address identified by the entry.)

Whenever a segment- or page-translation exception is recognized, the instruction is suppressed and storage is not modified. The virtual address that was to be translated is recorded in the translation exception address register (control register 2) and, if in 24-bit addressing mode, bits 0-7 are made 0s. The instruction length code for both exceptions may be 1, 2, or 3.

### Machine Check Interruption

In addition to the machine check capability described in the <u>IBM System/360 Principles of Operation</u> manual, the 2067 performs machine checking on the dynamic address translation unit. Additional information about the machine check interruption is stored in the first byte (bits 0-7) of the translation exception address register (control register 2). Bits 50-54 in the maintenance control word indicate to the monitor whether a dynamic address translation unit machine check has caused the interruption; if it has, a 1-bit in the translation exception address register will indicate one of the following conditions:

### Bit Condition

- 0 More than one associative register contains identical information, or one of the comparing circuits is at fault.

- 1 A successful compare is achieved with a virtual address that is higher than the addresses in the segment table.

- 2 The virtual address portion of the translated address just stored in the associative array

does not compare with the virtual address that should have been stored.

- 3 A reset of the load-valid bits in the associative array was unsuccessful.

- 4 Parity of the adder sum is inconsistent with the predicted parity.

- 5 Parity of the virtual address was incorrect when received by the associative array.

- 6 Parity of the data word from storage was incorrect when received by dynamic address translation circuitry.

- 7 Parity of instruction bits 8-15 was incorrect when received by dynamic address translation circuitry.

When a machine check interruption is recognized, execution of the instruction is terminated and the interrupt request is handled as described in the IBM System/360 Principles of Operation manual except as follows. When a machine check interrupt is caused by an external machine check (I/O machine check), the CPU (1) completes execution of the current instruction, (2) does not initiate an internal diagnostic procedure, and (3) does not perform a diagnostic scan out into the storage area beginning at location 128. For both machine check and external machine check, the CPU stores the old PSW in location 48 and loads the new machine check PSW from location 112. Bit 17 of the old machine check PSW identifies the CPU mode of operation at the time of interruption. Bit 17 is stored as a 1 when the CPU is in extended PSW mode and as a 0 in standard PSW mode. The highorder bit of the interrupt code (bit 16 of old machine check PSW if the CPU is in standard PSW mode) indicates whether the machine check is an external machine check. This high-order bit is a 1 for external machine checks and a 0 for CPU machine checks.

### Interrupt Codes

In extended PSW mode, when the PSW is stored as the old PSW, the 16-bit interruption code is stored as a halfword in storage as follows:

| Interruption Type | Permanent Storage Address |         |  |  |

|-------------------|---------------------------|---------|--|--|

|                   | Decimal                   | Hex     |  |  |

| External          | 14-15                     | E-F     |  |  |

| SVC               | 16-17                     | 10-11   |  |  |

| Program           | 18-19                     | 12 - 13 |  |  |

| Machine check     | 20-21                     | 14 - 15 |  |  |

| I/O               | 22-23                     | 16 - 17 |  |  |

These bytes are not loaded when loading a PSW.

### Extended Direct Control

The extended direct control feature enables direct communication of control information between two CPU's. Each CPU in a duplex system must be equipped with this feature. Extended direct control is a modification of the multisystem operation and the direct control feature described in the IBM System/ 360 Principles of Operation manual. Two major modifications have been implemented by this feature. The 'read direct' instruction has been made an invalid instruction and the 'direct-out' lines are terminated within the CPU. Since the duplex configuration of the Model 67 is a shared storage system, there is no need to transfer a data byte over the 'direct-out' lines to the other CPU. Another CPU's attention can be directed to an area of shared storage via the external interruption signal lines.

The extended direct control feature uses the 'write direct' instruction and six external interruption lines:

| Interrupt<br><u>Line</u> | <u>CPU 1</u>                              | CPU 2                                  |

|--------------------------|-------------------------------------------|----------------------------------------|

| 2                        | Not used                                  | Machine check out<br>signal from CPU 1 |

| 3                        | Machine check<br>out signal from<br>CPU 2 | Not used                               |

| 4,5                      | Reserved for future                       | euse                                   |

| 6                        | Timing signal<br>from CPU 1 or<br>CPU 2   | Timing signal from<br>CPU 1 or CPU 2   |

| 7                        | Not used                                  | Not used                               |

Line numbers correspond to external signal designations used with the interruption codes listed in the <u>IBM System/360 Principles of Operation</u> manual. Interrupt codes and mask bits for these lines are as follows:

|      | Control Register 6<br>External Interrupt |                   |

|------|------------------------------------------|-------------------|

| Line | Mask Bit                                 | Interruption Code |

| 2    | 26                                       | 00000000 nnlnnnn  |

| 3    | 27                                       | 00000000 nnnlnnnn |

| 6    | 30                                       | 00000000 nnnnnnln |

WRITE DIRECT is used in the Model 67 to generate the timing signal external interrupt request (line 6) and the external start signals. The I<sub>2</sub> field of the instruction is divided into two fields by function. Bits 8 - 11 are assigned to the external interrupt function, and bits 12 - 15 are assigned to the external start function. Bit 8 is assigned to CPU 1 and bit 9 is assigned to CPU 2. Regardless of which CPU executed the 'write direct' instruction, a 1 in bit 9 of the I<sub>2</sub> field will generate external interrupt signal on line 6 of CPU 2. A CPU can interrupt itself.

Bit 12 of the  $I_2$  field is assigned to start CPU 1 and bit 13 is assigned to start CPU 2. Since there is a main 'external start' line and an alternate 'external start' line for each CPU, bit 7 (low-order bit) of the data byte addressed by the 'write direct' instruction is used with the  $I_2$  bit(s) to generate the appropriate external start signal. For example, if bit 12 (of the I field) is a 1 and bit 7 (of the data byte) is a 0, a signal is generated on the main 'external start' line of CPU 1. When bit 12 is a 1 and bit 7 is a 1, a signal is generated on the alternate 'external start' line of CPU 1. Note that CPU 1 is started regardless of which CPU executed the instruction. "Main" and "alternate" correspond to the main and alternate prefix values prewired in each CPU. More than CPU can be signaled by one 'write direct' instruction. The external start signal pre-empts current operations in the receiving CPU. The current operation is terminated, the current PSW is replaced by the contents of the new PSW at byte address 0000 (defined as the new external start PSW), and the current PSW is lost. Selection of the prefix value is a function of the line (main or alternate) on which the signal was received. A system reset of all control latches occurs in the receiving CPU, but the reset is not propagated to the I/O components. Therefore, the programmer must insure, by suitable programming constraints, that the receiving CPU is not executing an I/O instruction and is not accepting an I/O interrupt. If either of these conditions occurs simultaneously with receipt of the external start signal, the results are generally unpredictable and the I/O channel and/or channel

control unit may hang up.

The external start sequence is completed after 50 us. Results are unpredictable for successive external starts issued to one CPU more frequently than one every 150 us.

Extended direct control can be partitioned by switches on the Configuration Unit. One switch per CPU can be set to remove the CPU from the external direct control interface. When the CPU is partitioned off, machine checkout and timing signals are not generated, and external start and external interrupt-in signals are ignored (do not remain pending). When partitioned, a CPU cannot external start itself and cannot interrupt itself, although manual IPL (load) and the interrupt pushbutton are still effective.

### High Resolution Interval Timer

An interval timer with a high degree of resolution is used in the 2067. Operation of this timer is fully compatible with that described in the <u>IBM System/360</u> <u>Principles of Operation manual.</u>

The high resolution timer provides approximately 13-microsecond resolution. This is accomplished with an 8-bit hardware register which contains the low-order byte of the timer. Each time the loworder byte counts to zero, the timer value at locations 80-82 is decremented at the end of the instruction currently being executed.

An operand fetch from location 80 will retrieve the three high-order bytes from location 80 plus the low-order byte from the hardware register. If the low-order byte has stepped through zero during the instruction prior to a fetch from location 80, zeros are inserted into the low-order byte instead of the contents of the hardware register. Any instruction that stores into location 80 also stores the low-order byte into the hardware register as well as a full word into location 80. If the timer value at location 80 changes from positive to negative, an external interruption is requested.

Programming Note: If the emulator feature is installed and if the system is in emulator mode, a machine check is not indicated by the machine time-out feature, and the machine-check interruption is lost.

### Interruption Times

Interruption times vary for the class of interruption and for the type of instruction being executed at the time of the interruption.

### **External Interruption**

External interruption time is 3.15 microseconds; it extends from the time the external interruption is discovered and honored to the time the next instruction is started.

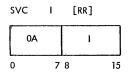

### Supervisor Call Interruption

Supervisor call interruption time is 3.95 microseconds (including supervisor call instruction time); it extends from the time the external interruption is discovered and honored to the time the next instruction is started.

### **Program Interruption**