**IBM** Customer Engineering

# 1620

Data Processing System

MACHINE SERIA

## 1620 SERVICE INDEX

## INTRODUCTION

The 1620 Service Index is designed to guide Customer Engineers toward a logical and rapid solution to system failures. It is intended that function charts, logics, reference manuals, etc. be used in connection with the Service Index.

Each section of the Service Index is indexed separately and includes individual page and figure numbering to permit rapid access to the specific information needed by the Customer Engineer.

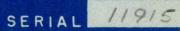

1622 - Page 3-16

1624 - Page 3-15

See General Trouble Shooting Section - Page 2-2 See Fortran Section - Page 7-2

# GENERAL TROUBLE-SHOOTING

## INFORMATION

## CHECK LIST

- I. General Information

- A. On what operation does the machine fail?

- 1. DFT

- 2. Customer work (Fortran, etc.)

- 3. Op code of failure

- B. What is the frequency of error?

- 1. Time of day

- 2. Environment (temperature, etc.)

- 3. Does customer power fluctuate at certain time of day? (welder, heavy machinery, etc.)

- **11.** General Check List

- A. Have you checked for loose or bent connectors?

- 1. 32 pin connectors (x, y, etc.)

- 2. Edge connectors.

- 3. Laminar buss (pins and terminals)

- 4. TB connectors (power supply, power sequence, etc.)

- B. Have you checked for grounds?

- 1. DC isolated ground

- 2. AC isolated ground

- 3. Ground straps (check contact from the gate to the frame)

- C. Have you checked the Power Supplies?

- 1. Voltage levels

- 2. Ripple

- D. Have you checked Muffin fans?

- 1. Power supply fans

- 2. Gate fans

- E. Does the machine fail on margins?

- 1. Normal margins ± 15%

- 2. ±30% margins

- \*3. Heat

- \*4. Cold

\*Steps 3 and 4 are last ditch efforts and should be used only after all other procedures fail (See Note 1).

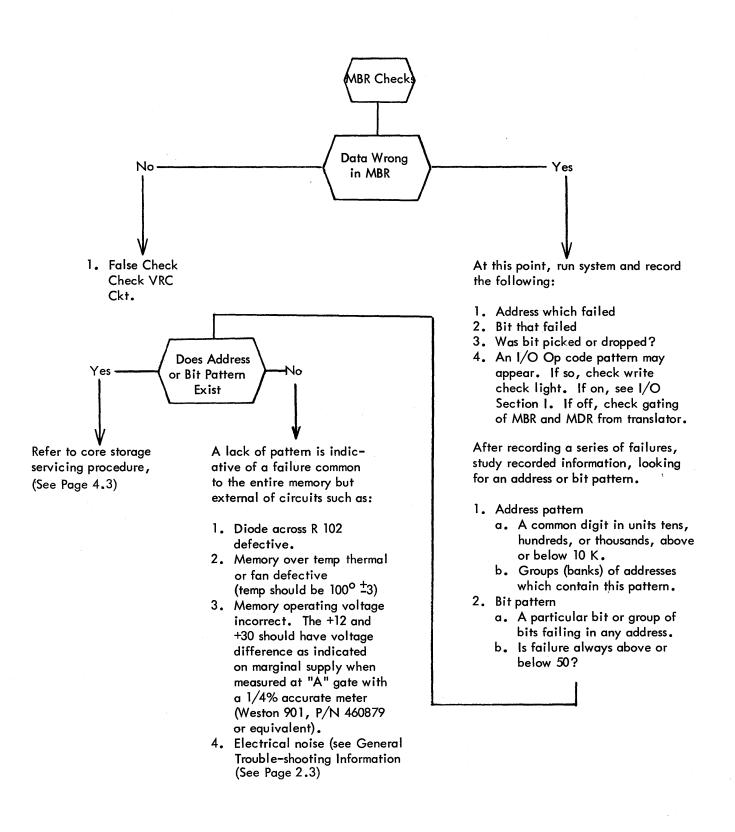

**III.**Core Storage Check List

- A. Have you checked the difference voltage using 1/4% accurate meter?

- B. What lights are on?

- C. What is the pattern of the failure?

- 1. Greater or less than 50; odd or even, etc.

- 2. Picking or dropping bits

- 3. What bits are affected?

- D. Is the trouble in MBR rather than memory? E. Memory Temperature  $100^{\circ} \pm 3^{\circ}$  (Muffin Fan)

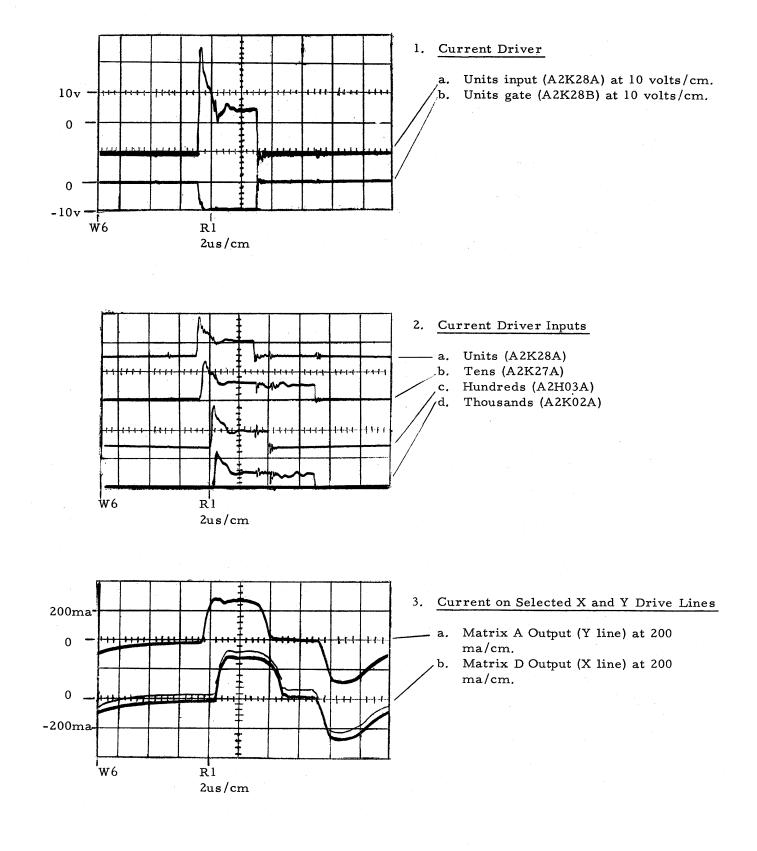

- F. Have you scoped (using current probe)?

- 1. x, y drive lines

- 2. z (inhibit) drive lines

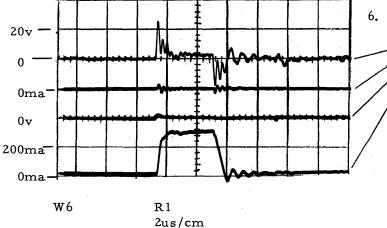

- 3. Decode Output

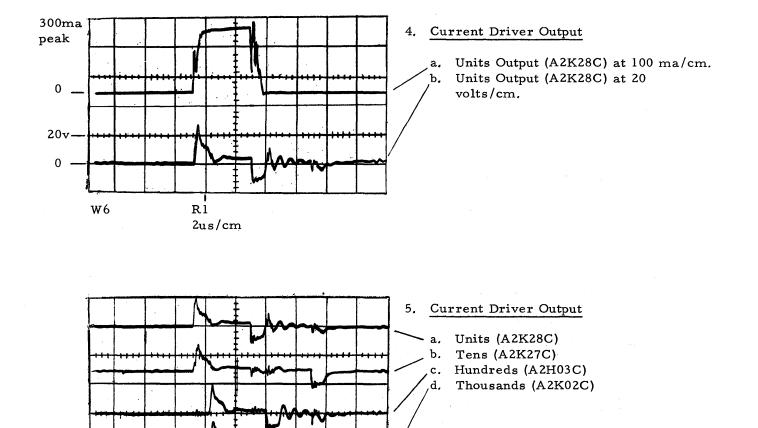

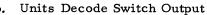

- 4. Current driver outputs

- 5. All lines to the inductors

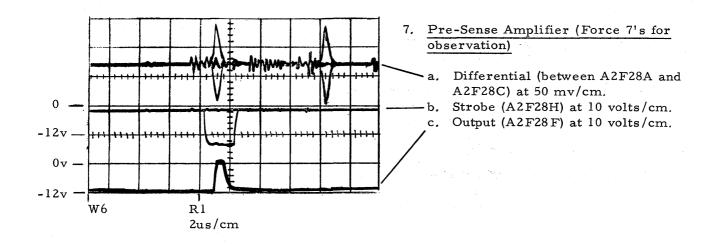

- G. Have you scoped the sense lines (using a 535 or equivalent scope and a type "D" High Gain Differential Pre-amp plug in unit)?

- H. Have you checked the physical wiring of the indicators?

- Have you followed scope procedures in 1620 1. CE Reference Manual?

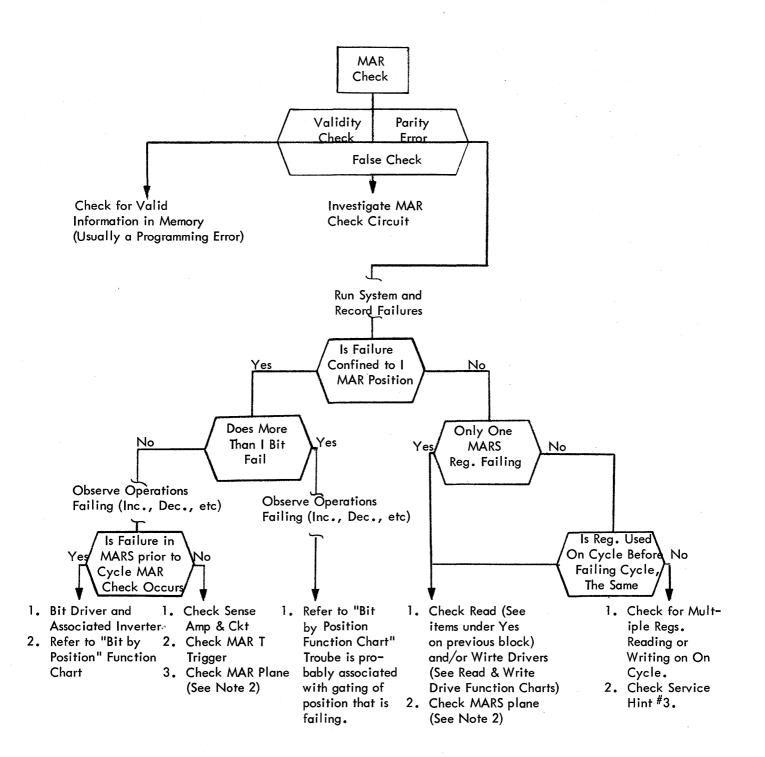

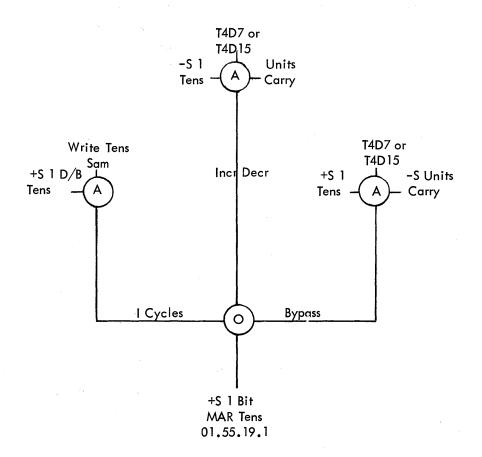

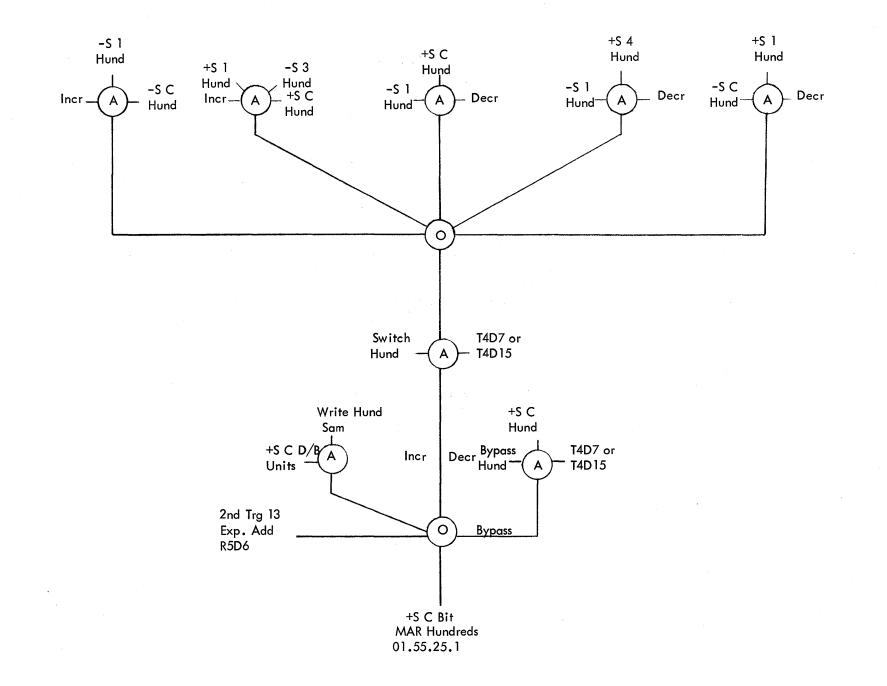

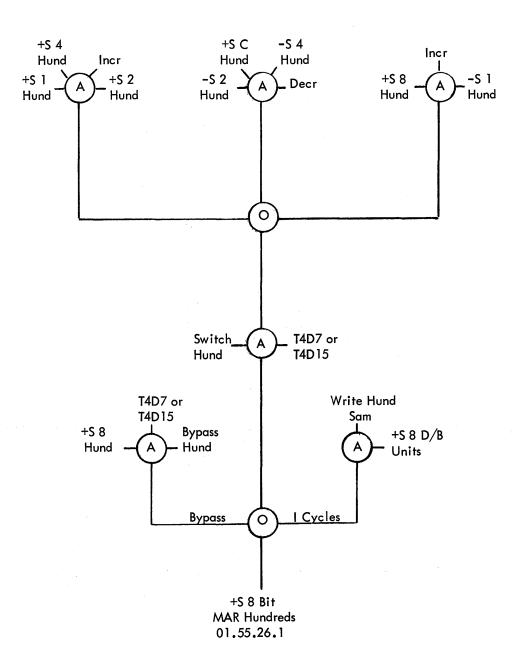

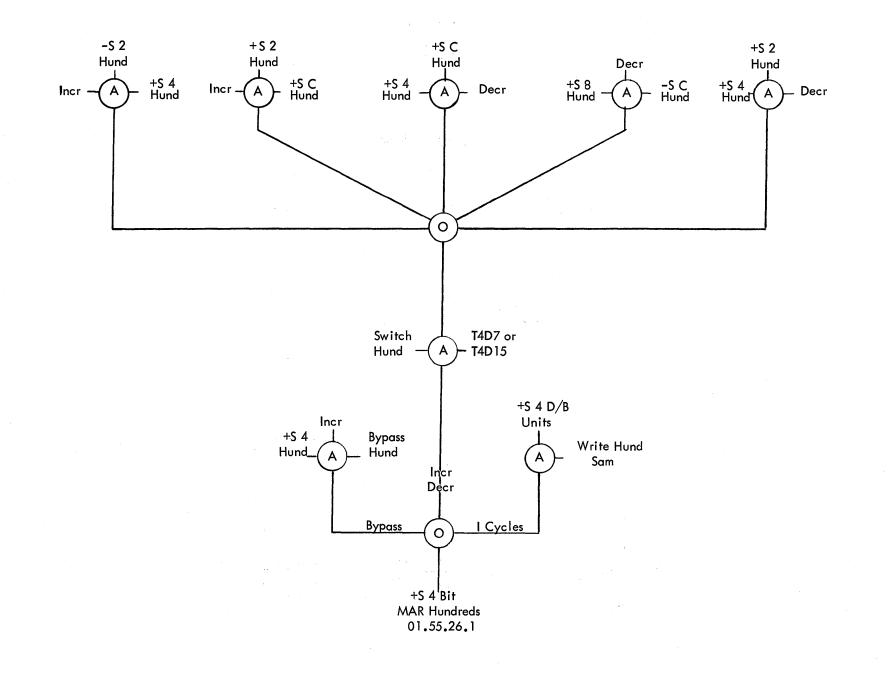

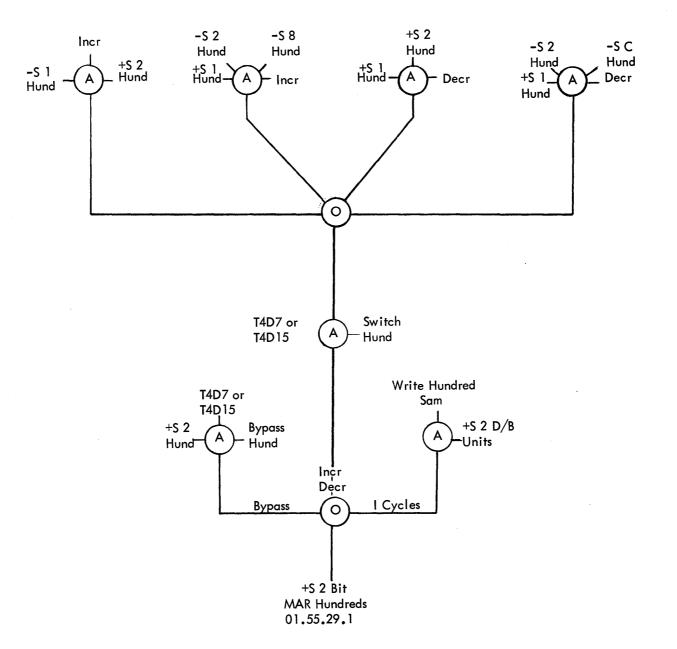

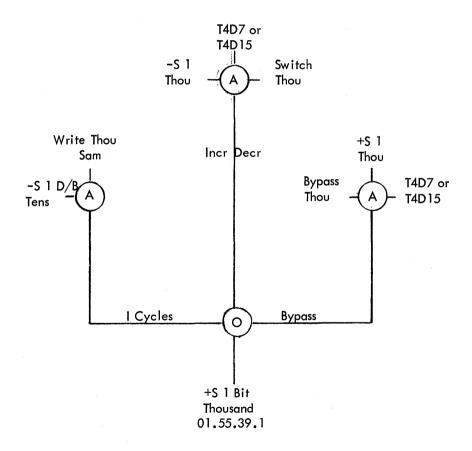

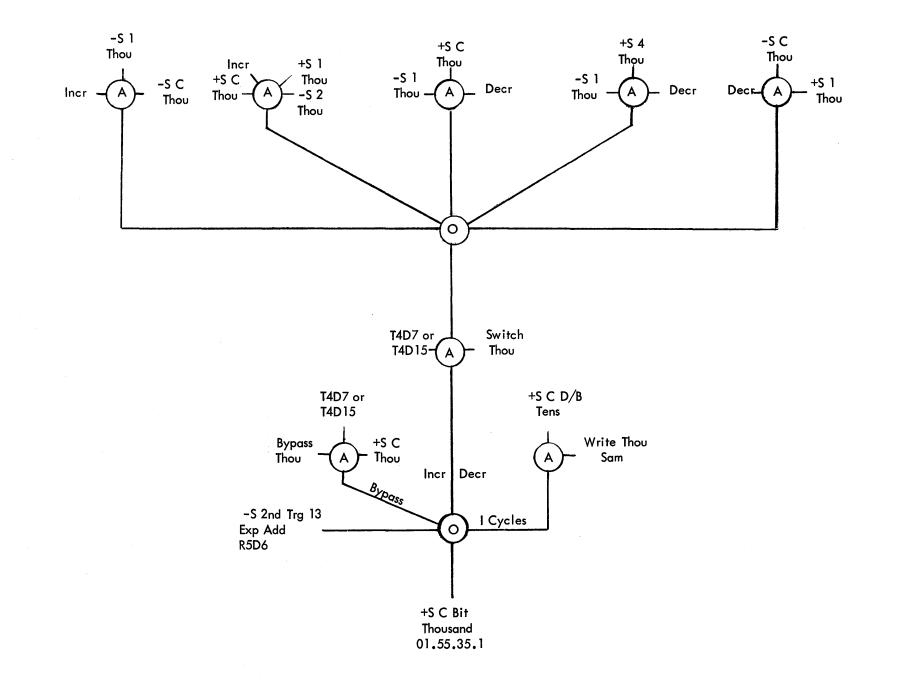

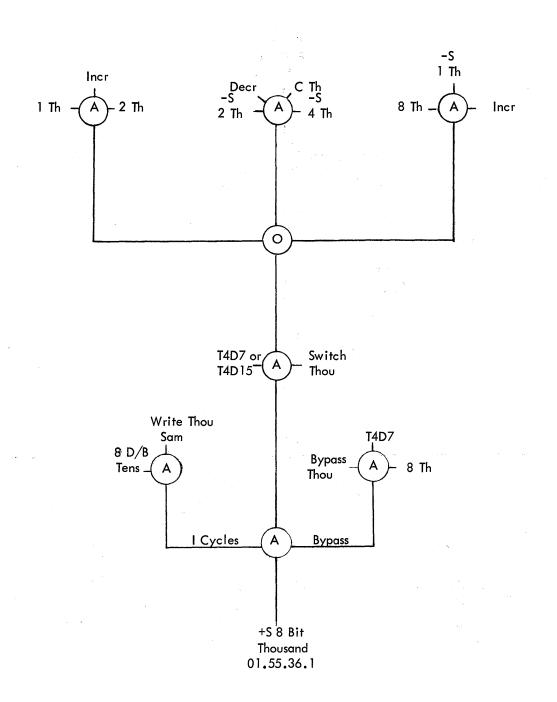

- IV. MAR Check List

- A. What console lights are on?

- 1. Op code of failure

- 2. Previous Op code

- 3. "E" or "I" cycle trigger of failure

- 4. Which register failed

- 5. Failure to read, or write

- 6. Is the trouble in MAR triggers

- 7. Is the trouble in Inc. Dec. switch

- 8. Is the trouble in Multiply Register or T/C Circuits.

- B. Have you scoped (using a current probe)?

- 1. Read drivers to all registers

- 2. Sense lines

- 3. Write drivers to all registers

- 4. Bit drivers

Note 1: If errors do not become more frequent with marginal check part (1 or 2), block the fans and let the gates heat up.

If part 3 does not solve the problem, obtain about 50lbs. of dry ice, remove the filters from the gate, place the dry ice on the floor, then construct a skirt out of paper and cause all the air to be drawn from around the dry ice.

Note 2: Observe the function of the "E" or "I" cycle trigger to determine the register affected. Under some triggers, more than one register is affected. Be critical of the timing of the pulses on these lines. If the failure occurs while writing, it will be detected at the time it is read out. In order to determine the cause, scoping must be done at the time of writing. Some intermediate checks can be performed by use of the MAR Display Switch, by stopping at different trigger times and displaying the register in question. Check to be sure that only the registers called for by a trigger are being operated on.

#### TRANSIENT POWER LINE NOISE

The only pattern that can be associated with noise is its lack of a pattern. If transient noise is suspected, the Physical Planning Department should be alerted to the situation. Listed below are some common symptoms noted in the field:

- 1) Highly intermittent failures

- 2) Failure defies any analysis by pattern

- Failures occur mostly during the day (commonly related to the start or end of a work day when large numbers of equipment are being turned On or Off).

- 4) Week end performance relatively trouble free. Areas in the 1620 system most noise sensitive:

- 1) 1622 units tens ring

- 2) Binary triggers

- 3) Drift latches

Methods of determine noise:

1) Scope

- a. Suspected line

- b. "J" pins SMS Panels containing failures

- c. AC input lines at contactors

- Indicator A drift latch may be wired into circuit and gated to indicate a transient pulse. One of the test lamps (T1 or T2) on 1620 console could reflect status of this latch.

- New Input Run in temporary cable from building service to 1620. This will give the CE a power line free of building transients.

Methods of aggravating noise problems:

- Determine other equipment on the 1620 line. Run a program while throwing On/Off switchs on this equipment, i.e., air-conditioning units, heaters, other DP equipment, etc.

- 2) Separate AC and DC isolated ground from machine frame.

Areas to investigate if noise problems are encountered or suspected:

- 1) Is system on separate power line?

- 2) Does system have a good ground return to power source (in most cases conduit ground is not satisfactory)?

# INPUT - OUTPUT

|                          | Page |

|--------------------------|------|

| Typewriter               |      |

| Read Checks              | 3.2  |

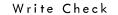

| Write Checks             | 3.4  |

| Known Trouble Tips       | 3.5  |

| Service Checks           | 3.9  |

| 1621-1624                |      |

| Read Checks              | 3.10 |

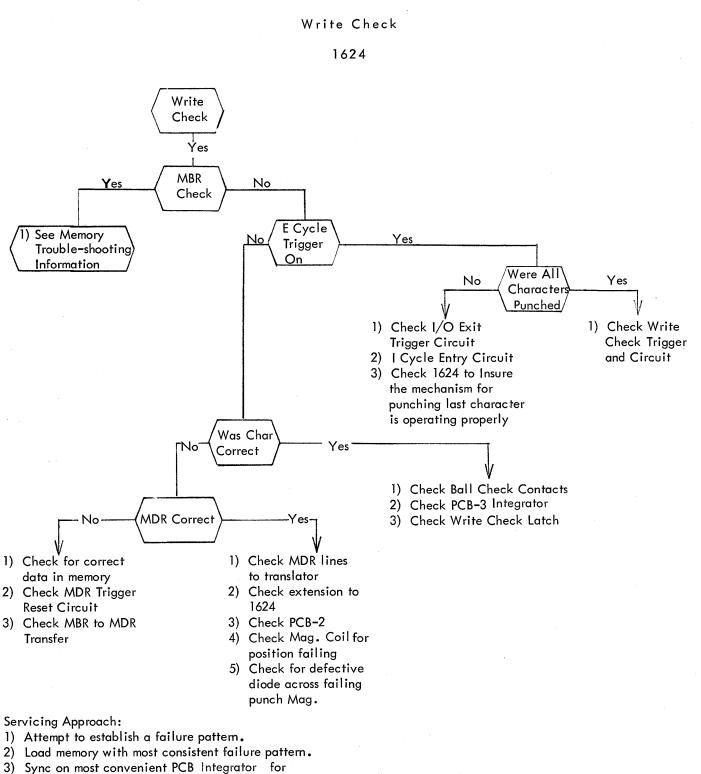

| Write Checks             | 3.15 |

| 1622                     |      |

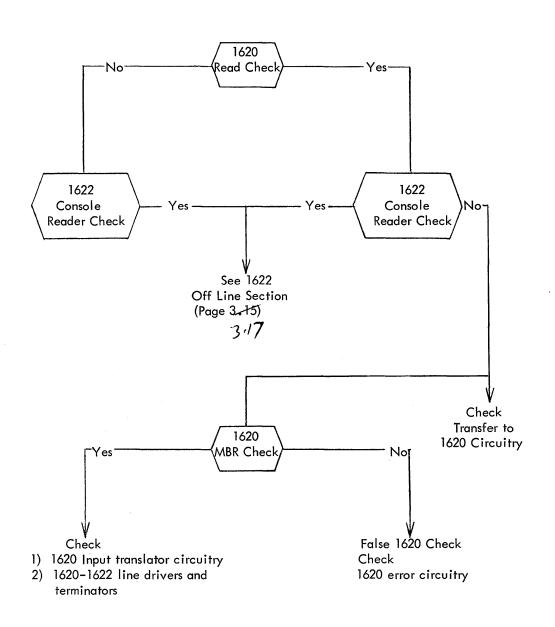

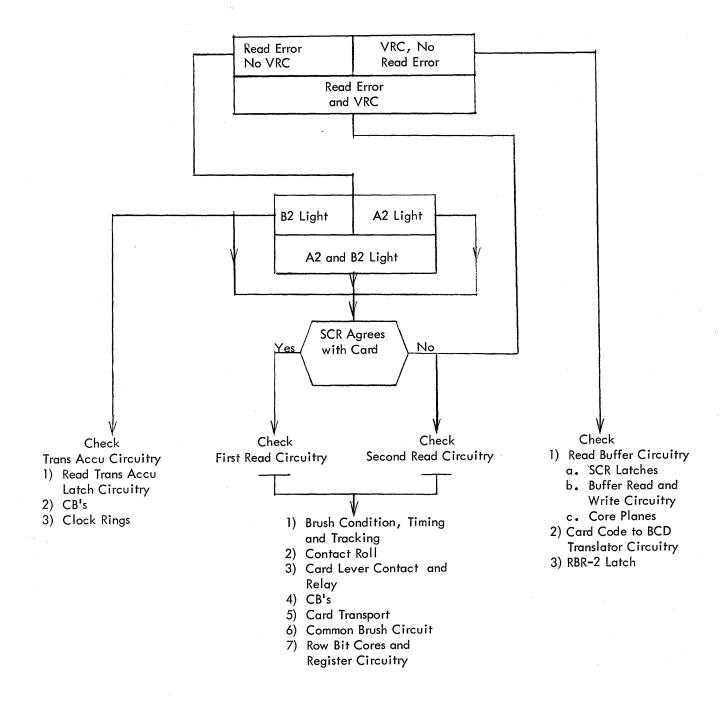

| Read Checks              | 3.16 |

| Reader Checks (off line) | 3.17 |

| Reader Checks (off line)       | 3.17 |

|--------------------------------|------|

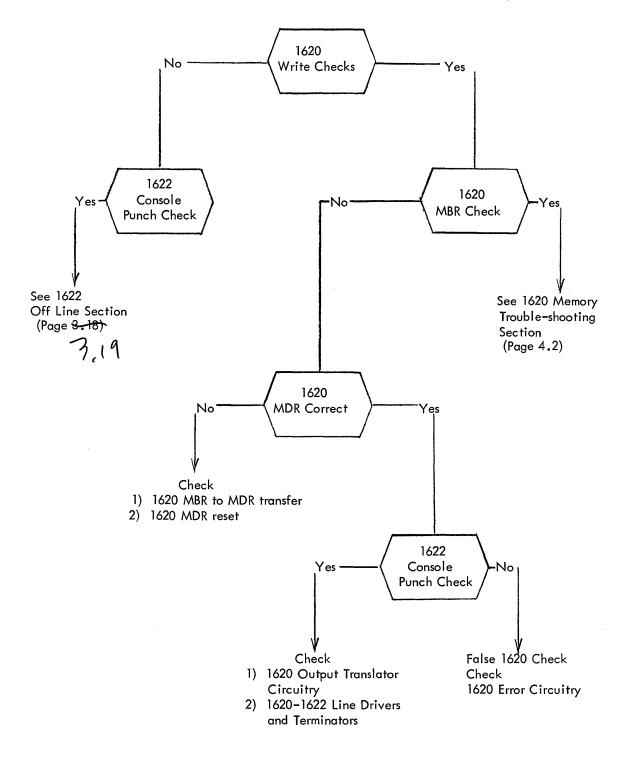

| Write Checks                   | 3.18 |

| Punch Checks (off line)        | 3.19 |

| Known Trouble Tips             | 3.20 |

| Service Hints                  | 3.22 |

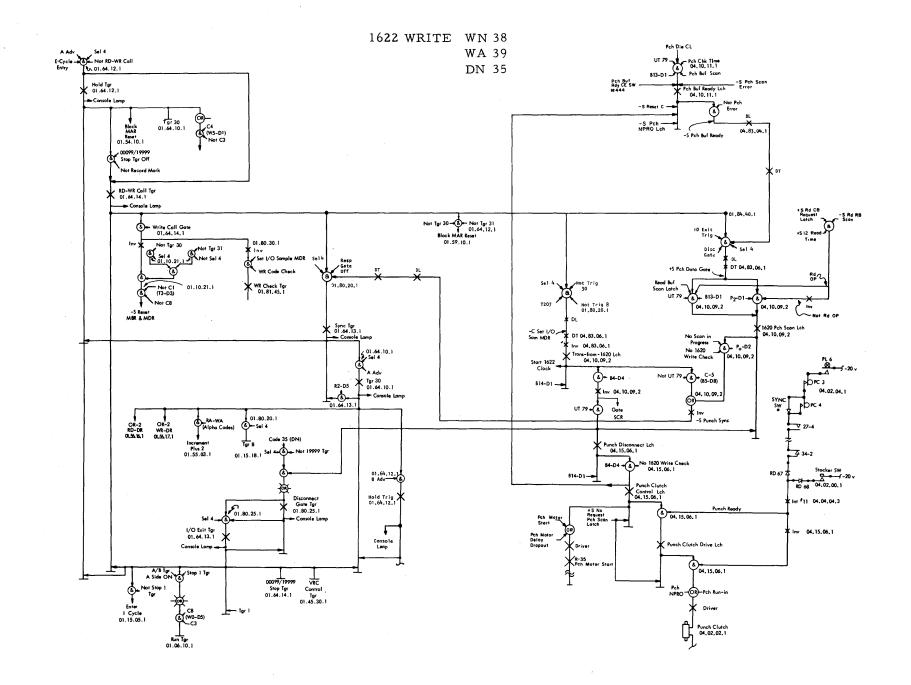

| 1620-1622 Data Transfer Charts | 3.31 |

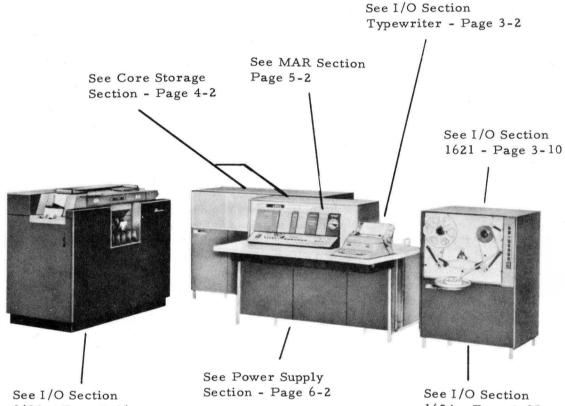

## Read Checks

## Typewriter

## **Scoping Methods**

- The input translator may be scoped by blocking a typebar in its fully raised position with the typewriter on-off switch in the off position. At this time, the input translator is conditioned to accept the bit(s) corresponding to the typebar raised.

- 2) The transfer to MDR, and from MDR to MBR, may be scoped by blocking a bit relay or group of relays transferred and locking the system in a trigger 30 operation. To lock in a trigger 30 operation, block the "B" advance pulse which turns on the hold trigger.

## Probable Cause

MAR incrementing when flag key is depressed or extra digits being set in memory (i.e., having 1223 set in memory after keying in 123.)

Trouble

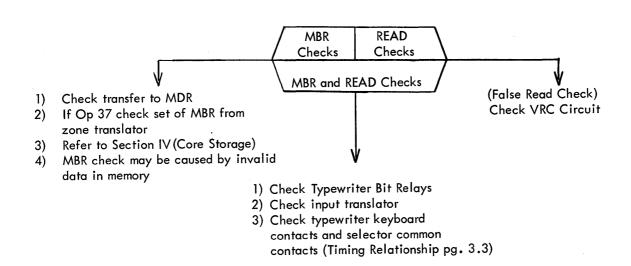

- 1) a. Check for a broken spring on the left end of the ribbon lift bail.

- b. Selector Common Contacts and Typewriter Magnet Armature contacts maladjusted. The following relationship should exist:

- 2) a. Skipped I/O Instructionsb. Multiple I Cycle Triggers

- 2) a. Check carriage return contact to insure that the N/O contact has a minimum of .010 rise from its support strap during entire length of carriage return.

c. E and I Cycle

b. Check tab interlock contact to insure that the N/O strap has .020 "To .030" contact rise.

Servicing Approach:

- 1) Attempt to establish a failure pattern

- 2) Load memory with most consistent failure pattern

- 3) Sync on CR 5 for typewriter translator failures

- 4) Sync on Trigger 30, sync trigger, etc., for troubles during set of MDR.

#### KNOWN TROUBLE TIPS Typewriter

#### Broken Typebars

Improper setting of Impression Control and/or Multiple Copy Control can contribute to excessive typebar breakage. Operators should be advised of the following procedures for setting the above controls.

Impression Indicator. The lever under this window can be positioned in setting from 0 to 10 to determine the force with which the typebars strike the paper. The higher the indicator setting, the harder the typebars strike. To test for the correct setting, move the indicator up until the comma and period print distinctly but not heavily. Use a higher setting for multiple copies, but be sure that the multiple copy lever is also correctly set before finally adjusting the impression.

<u>Multiple Copy Control</u>. This lever moves the platen backward to compensate for the greater thickness of additional copies. As a general rule, the lever should be set at "A" for one to three copies and moved back one position for each additional three to five copies. Heavy print at the top of characters shows that the platen is too far back; heavy print at the bottom of characters shows that the platen is too far forward. The shilling mark (/) is a good character to use in checking multiple copy settings.

## IMPRESSION AND TYPE ALIGNMENT

#### VERY WEAK OR NO IMFRESSION

Multiple copy lever in wrong position. Ribbon color control button in stencil position. Wrong platen for thickness of form. Platen too soft. Improper power roll speed. Bind in power roll and drive mechanism. Ribbon failing to feed properly. Oil on ribbon. Ring and cylinder out of adjustment. Dirty or glazed power roll. Power roll may need to be replaced. Cam Serration worn at the knockout position. Replace cam. Loose rubber on power roll.

Improper cam clearance.

Dirt in segment or on typebars in the slots. Impression indicator set too low.

Universal bar or escapement choking off typebar action.

Impression control screws set too light.

Type impression may be set too light to avoid cutting the paper. Polish the type faces.

#### INTERMITTENT LIGHT IMPRESSION

Dirt in segment. Finger prints or grease on paper. Cam serrations worn at the knockout position. Replace cam. Bind in type bar linkage or type guide. Misadjustment of type bar. Worn type bar or universal bar. Loose carriage. Eccentric power roll due to loose rubber. Dirty or glazed power roll. Power roll may need to be replaced.

CHARACTER FAILS TO PRINT Letter cam pivot worn. Armature off push rod. Bail armature stop too far forward. Weak magnet. Low voltage shot to mag. - (less than 42 volts) Typebar misaligned. Power roll worn.

DIFFERENT HEIGHT ON END TYPEBAR Type bar guide may be leaning to right or left.

## OVERPRINTING AND UNDERPRINTING

Check for light top or bottom. Check motion. Improper platen. Cushion of paper too deep in the form. Check multiple copy lever. Check ring and cylinder adjustment.

## TYPE CUTTING

Check power roll speed. Impression indicator set too high. Platen too hard. Check ring and cylinder adjustment. Type may need polishing. Impression control screws may require adjustment. Some papers are brittle and cut too easily. Such paper may be reinforced by using a sheet of tough tissue behind the original.

#### PILING

Insufficient carriage tension. Improper universal bar adjustment. Dirt in segment. Dirt on power roll. Escapement tripping too late or too early. Dirt in carriage ways and rails. Worn typebar. Broken or worn universal bar. It is possible for an operator to pile the type by uneven rhythm or by striking two or more keys nearly simultaneously. Strict adherence to adjustment procedures will minimize this occurrence.

## PAPER WRINKLING

Swollen platen and feed rolls. Uneven feed roll pressure. Bent deflectors. Check all paper feed pointers. Partial feed roll contact.

## CARRIAGE RETURN

## FAILS TO OPERATE

Faulty cam link adjustment Bind in cam. Back space pawl may be binding the interlock which will cause carriage return failure.

#### INCOMPLETE RETURN

Faulty cam adjustment.

Escapement pawl pulled too far out of the rack. Tip of the clutch knockout lever adjusted too high. Clutch lever bracket adjusted too loosely.

Nut on compression spring under machine should be tightened.

Lack of tension of the latch spring. Improper cam link adjustment. Improper latch adjustment.

#### CARRIAGE LOCKS

Latch link adjustment allows too deep a latch engagement.

Excessive latch spring tension. Weak motor.

Bind in power roll and drive mechanism. Tip of clutch knockout lever too low.

Clutch knockout lever link adjusted so knockout lever is too low.

Margin rack adjustment allows too much overbank. Clutch lever bracket adjusted too tightly. Adjusting nut on compression spring adjusted too tightly. Clutch operating arm too close. Carriage return tape off pulley. Truck roller or star wheel binds. Upper line lock Bellcrank spring.

UNEVEN MARGIN Margin rack out of adjustment.

Broken tab lever assembly or margin stop. Excapement pawl sticking or binding. Weak pawl spring. Air cylinder port closed too much. Carriage return contacts maladjusted or bouncing. Too strong carriage return - especially on long carriage machines.

## MOTOR

FAILS TO START OR RUN Faulty condenser. Check by turning motor by hand. Faulty motor. Broken switch. Switch link improperly adjusted. Frozen bearing. Belts too tight.

#### NOISE

TOP COVER VIBRATES Open cover and spread sides slightly.

REAR COVER VIBRATES Reposition rear cover.

CARRIAGE END COVERS VIBRATE Reform spring clips.

PAPER TABLE VIBRATES Reset positioning collars.

NOISY PAPER BAIL Check for broken paper bail spring. Reposition bail rolls on shaft.

NOISY DRIVE Check motor and pulley lubrication. Align pulleys. Replace worn belts. Adjust belts. Check power roll adjustment.

NOISY TYPING Typebar hitting front scale. Type rest pad worn. Platen too hard.

3.6

## NOISY SHIFT

Broken shift stop bracket. Broken segment guide. Cracked bumper on shift pusher. Shift stop screw rubbing on bracket.

## NOISY SPACE BAR

Improper stop bracket adjustment. Space bar mechanism hitting case. Improper pawl release lever adjustment allowing escapement pawls to drag.

## NOISY CARRIAGE RETURN

Improper adjustment of the eccentric on the pawl release lever allowing the pawls to drag. Clutch adjusted to return the carriage too hard.

#### SHIFT

INCOMPLETE SHIFT Pusher too high or too low. Binds in basket or shift mechanism. Excessive or uneven pin clearance. Broken hairpin spring. Keybutton binding.

## FAILS TO SHIFT

Check cam adjustment. Improper pin clearance. Pusher too high or too low. Improper cam link adjustment. Lack of lubrication. Cam may be binding. Shift equalizing rod out of place or warped. Excessive pin to pusher clearance. Bind in plunger or maladjusted. Cam trip lever maladjusted. Auxiliary hairpin spring off.

## MOTION FAULTY

Improper adjustment or adjusting nuts. Adjusting lock nuts.

Left and right-hand shift motion adjustments not made equal. Test with strips of paper between the stop washers and the brackets in each position of the basket.

Lock nut on stop bracket adjusting screw loose. Broken stop bracket (basket should rest evenly on

both brackets to prevent breakage). Broken segment guide.

## LIGHT TOP OR BOTTOM

Adjust shift stop bracket screws. Wrong platen for thickness of form. Copy control lever set at improper position. Check platen guide yokes for loose platen.

## SLOW OR BOUNCING SHIFT

Improper cam adjustment. Improper pin clearance. Improper pusher adjustment. Broken pusher buffer. See that operator is not "beating the shift". Power roll glazed. Cam bind. Worn cam.

## TABULATION

FAILS TO OPERATE OR TABULATES ONLY A FEW SPACES Improper cam adjustment. Fractured cam or link. Improper key lever link adjustment. Tab lever not being pulled far enough to latch. Linkage too long. Improper latch adjustment. Improper latch stop adjustment. Tab lever binding on margin rack. Bind in tab lever fulcrum. Improper tab rack adjustment which may cause tab lever to strike tab stop. Tab lever stop on rear rail set too far forward. Friction governor adjustment may be faulty, causing a bind. Weak tab lever spring may prevent tab lever from restoring properly. Back space pawl may be binding the back space interlock which will cause tab failure. Lack of lubrication. Excessive cam clearance. Tab latch keeper to far rear. Trip link maladjusted. Plunger maladjusted or binding. Maladjusted interlock contacts. TABULATES SHORT Tab rebound check lever has excessive clearance with tab stop. Worn tab stop. Tab lever moving too far into the tab rack. Tab lever binding on the margin rack. Bind in the tab lever. Improper latch stop adjustment, allowing excessive clearance between tab lever and tab rack. Friction governor too tight. Insufficient carriage tension.

Tab stop not completely set.

See that the operator is not beating the tabular operation. This would appear as tabulating short

by less than a full space.

Rebound check lever may be too low and passing under the tab stop or may have excessive clearance with the tab stop. Bouncing or maladjusted contacts. Bind in carriage.

#### TABULATES EXTRA SPACES

Tab lever not getting sufficient bite on the tab stop. Friction governor too loose. Excessive carriage tension. Tab stop improperly set.

#### CARRIAGE LOCKING

Tab rebound check lever holding tab stop too tightly. Improper latch adjustment not allowing tab lever to unlatch.

Friction governor too tight not allowing the tab lever to knock off.

Rebound check lever too high, catching and holding the tab lever out.

## BACK SPACE

FAILS TO OPERATE

Bind in cam.

Improper cam adjustment.

Bind in linkage.

Broken, bent or improperly adjusted guide lug.

Fractured cam or links.

Broken escapement spring or corner bell crank spring. Final stop adjusted too close.

Adjust height of back space pawl.

Interlock binding or interfering with back space

pawl.

Binding keybutton.

Glazed power roll.

## BACKS TWO SPACES

Cam repeats. Excessive play in linkage. Improper final stop adjustment. Improper guide lug adjustment.

INTERMITTENT FAILURE

Lack of lubrication on back space pawl. Improper cam adjustment. Fractured cam. Excessive play in linkage. Improper final stop adjustment. Improper guide lug adjustment. Adjust height of back space pawl.

#### SPACE BAR

FAILS TO OPERATE

Check cam adjustment. Bind in cam.

Space bar binding on cover.

Improper stop bracket adjustment.

Improper cam link adjustment. Spring on escapement lever plate loose or stretched.

Bind or maladjusted plunger - (critical). Plunger must be lined up directly over the hole in the top of the solenoid to eliminate possible binds.

Plunger bottoming in solenoid.

#### REPEATING

Faulty cam (do not confuse with need for stop bracket or cam link adjustment).Stop bracket adjustment too low.Improper cam link adjustment.Operator may be operating the space bar twice.

#### ERROR TYPEOUT - CHECK LITES

Selector Contacts maladjusted. Ribbon lift operating link shorting contacts. Worn letter cam pivot. Loose contact wires or short between pins. Binding typebar. Broken keyboard contacts.

#### SERVICE CHECKS

- A. MOTOR AND DRIVE

- 1. Coasts freely when power is turned off.

- 2. Belts and pulleys are aligned correctly.

- 3. 1/4" belt deflection.

- 4. Power roll end play is correct (.002" .010")

#### B. CARRIAGE

- 1. Freedom of movement No play

- 2. No loose parts particularly margin and tab rack.

- 3. Carriage tension and carriage return tape.

- 4. Platen turns freely when not detented.

- 5. Pin wheels do not bind.

## C. TYPEBARS

- Use type alignment sample (B-1 Ref. Manual, Page 5)

- 2. No binds or loose type slugs.

#### D. ESCAPEMENT

- 1. Fast, unhesitating action over the full length of the carriage (space across several times).

- 2. All typebars trip the escapement pawl as they enter the type guide.

#### E. CARRIAGE RETURN

- 1. Positive return from any carriage position with line space lever at three (3).

- 2. Impact is cushioned before striking left margin.

- 3. No excessive whip of the carriage return tape on successive carriage returns.

- 4. Carriage return clutch plate to operating arm clearance (.005" .015").

## F. BACKSPACE

- 1. Backspace complete length of carriage.

- 2. Carriage does not lock up when backspace and carriage return key are depressed simultaneously.

#### G. TAB

- 1. Tab check lever two (2) spaces to the right of the tab stop on long and short tabulations.

- 2. Tab speed about the same as carriage return speed.

## H. RIBBON MECHANISM

- 1. Reverses easily on both sides.

- 2. Feed pawls feed two (2) full teeth on ribbon spools.

- 3. Ribbon lift guide is not binding.

- 4. All characters strike the ribbon in both upper and lower position of the color control lever.

## I. SHIFT

- 1. Equal distance (1/16") between pusher and upper and lower pins on the shift actuating plate.

- 2. Shift lock holds the basket securely (up and down).

- 3. All characters have even impression (top and bottom) in either shift position.

#### J. SOLENOIDS

- 1. Remove and clean space, tab, C.R. solenoid plungers.

- 2. With plungers bottom, key lever should be 1/32" from the bottom of the slot with cam just tripped.

- 3. Plunger spring hooks are centered in key lever slots.

- 4. With power off, cam release lever of a tripped functional cam should rest midway on the cam log.

## K. MAGNET UNIT

- 1. Armatures and push rods do not stick or bind.

- 2. All amatures result in a smooth typing speed.

- 3. Armature to stop bail clearance (.070")

- Cam to power roll clearance (light drag on two IBM cards).

#### L. INTERLOCK CONTACTS

1. Contacts are clean and remain closed for the full duration of the operation.

## Read Checks

## 1621

1) Check transfer to MDR

- 2) If Op 37 check set of MBR from zone translator

- 3) Check sync lamp timing and duration (Note 2) (Page 3.11)

- 4) Refer to Section IV (Core Storage) (Page 4.2)

- Check Photo Diode outputs (Note 1)

- 2) Check Sync Lamp Timing and Duration (Note 2) (Page 3.11)

- 3) Check Voltage Taps on 1621 power transformer to insure they conform to the tap settings on the 1620 transformers (208V or 230VAC)

- Check Read Window to insure that it is free of dust and that the window mask is clear of photo diode light path.

#### Scoping Procedures

#### Notes:

- Read Photo Diode Adjustment Procedure Before the following diode adjustments are made, clean the read head area to remove all dust from the read window. Make certain that the +12 and -12v power supplies are adjusted to the nominal values given on the 1620 voltage specification chart.

- 1) Center diode potentiometers 1 through 8.

- 2) Set read lamp potentiometer for minimum intensity.

- Record diode output with no tape in machine. Scope channels 1 through 8 at A4A04B, D, H.

G, and A4A05B, D, H, G on 02.83.50.1.

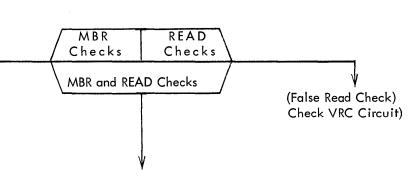

Select a diode that has an output that is near to the average output of all diodes and use it as a reference or base for Steps 5 and 6. For example, see Figure 1.

| Channel | Scope Point | Voltage Reading |

|---------|-------------|-----------------|

| 1       | A4A04 B     | -10.0v          |

| 2       | A4A04 D     | - 8.0v*         |

| 3       | A4A04 H     | - 9.2v          |

| 4       | A4A04 G     | - 6.4v          |

| 5       | A4A05 B     | -11.3v          |

| 6       | A4A05 D     | - 2.2v**        |

| 7       | A4A05 H     | - 9.8v          |

| 8       | A4A05 G     | -10.4v          |

|         |             | -67.3           |

# 8.4v Ave 8 67.3

\*Use this diode as the reference diode because it is closest to the calculated average.

\*\* This diode may need to be rotated, the mask may be dirty or out of adjustment, the gasket may be out of place or the diode may need to be replaced if it cannot be brought to specified levels.

- 5) With no tape in the machine, scope the reference diode selected in Step 4 and adjust the read lamp potentiometer until the diode output is -10v. Ideally, the potential on the read lamp should not exceed 11v.

- Scope the remaining diodes and adjust the individual read diode sensitivity potentiometers for a -10.0v output at each diode. This is a starting point for the following adjustments:

If -10v cannot be obtained, it may be necessary to change the read lamp potentiometer adjustment, keeping in mind the ideal potential for the lamp. If the read lamp potentiometer is re-adjusted, the diode outputs should be re-checked and the diode potentiometers re-adjusted if necessary.

- 7) (a) Punch up a length of tape with 1, 2, 4, 8, C, O, X, EL, etc., in consecutive positions. This can be done by inserting a read alphameric instruction with the typewriter designated as the input device (37 00501 00100). RELEASE and START. Depress the shift key and type 1, 2, 4, 8, spare bar, O, -, +. Now set up a program loop to write alphamerically on the punch (39 00500 00200 49 00000 00000). RELEASE and START. The paper tape punch should now be punching the desired pattern. Form the punched tape into a loop and place on the read head. A good splice can be made by cutting the tape on an angle, about 45°; holding the ends of the tape, with Channel 1 toward you, overlap tape end in LEFT hand OVER tape end in RIGHT hand by 1/16" to 1/8". Glue in this position, with feed holes aligned, using a quick setting glue such as IBM tape mucilage, Part #221020.

- (b) Set 1621 switch for strip mode.

- (c) Depress NON-PROCESS RUNOUT. The loop should now be running over the read head.

- (d) Measure the peak-to-peak voltage swing at the points given in Step 3. The diode swing is a result of the change in light when reading through tape (positive level) to a light through a code hole (negative level) and is a function of diode sensitivity and tape transparency. The diode potentiometers will adjust the plus and minus levels up or down simultaneously.

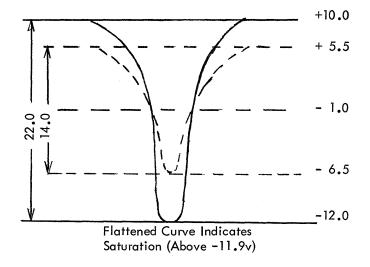

- The peak-to-peak voltage swing must be at least 14.0 volts. If a diode fails to meet the minimum 14.0 volts swing with the power supplies at their nominal values, and rotation of the diode does not increase the sensitivity thereby increasing the swing, replace the diode.

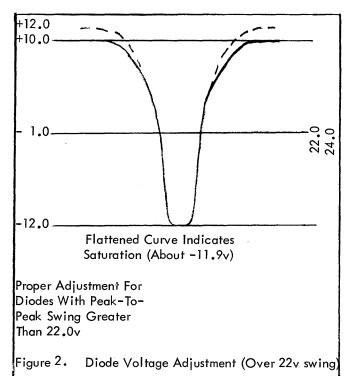

- (2) For diodes with peak-to-peak voltages between 14.0 volts and 22.0 volts, center the voltage swing about -1.0 volt reference with the diode potentiometer. For example, a diode with a minimum swing of 14.0 volts would be set to +6v and -8.0v. See Figure 1.

Proper Adjustment For Diodes With Peak-To-Peak Swing From 14.0v To 22.0v

Figure <sup>1</sup>. Diode Voltage Adjustment (14 to 22v swing)

3.11

- (3) For diodes with peak-to-peak voltages greater than 22.0 volts, set the negative peak to -12.0 volts (just in saturation). The positive peak will be between +10.0 and +12.0v. See Figure 2.

- (e) Measure the +S amplifier outputs at 4A07G, K, C, L, and 4A08G, K, C, and 4A09C. The + signals must be at least 2.0 milliseconds in duration.

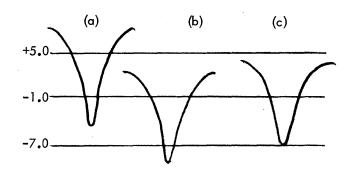

- (f) Changes in voltage, temperature, and dust on the read window will cause the voltage level to move up or down from their initial values. An average cyclic shift of 1 volt is to be expected. Readjust any diode as per 7) (d) when the power supplies are adjusted to their nominal setting and any one of the following conditions exist. See Figure 3.

- (a) The positive level is more negative than +5.0 volts.

- (b) The negative level is more positive than 7.0 volts.

- (c) The +S amplifier signals at points listed in 7) (e) are less than 2.0 milliseconds in duration.

Figure 3. Effect of Change in Voltage, Temperature, and Dust on Read Window

Re-adjust per Step 7 if any of the above conditions exist. (c) Indicates a diode with less than the minimum 14.0v swing.

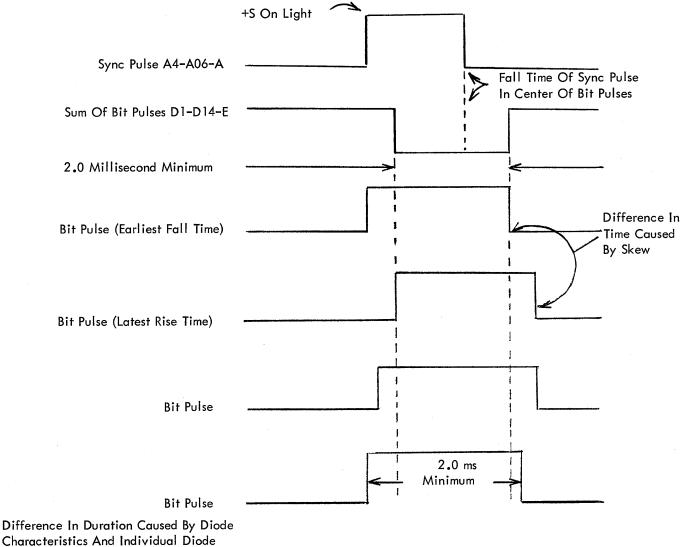

- 2. <u>Timing Disk Lamp and Photo Diode</u> The timing disk lamp must be adjusted so that both of the following conditions are met:

- The negative peak of the diode measured at A4A06C must be set to -12 volts (just in saturation).

- The trailing edge of the sync pulse must be in the center of the code pulse within .5m sec for all channels.

Whenever the lamp assembly is shifted to obtain the correct timing, a change in diode output will be noted because this adjustment also affects vertical/horizontal positioning of the light source relative to the diode. More or less light reaching the diode alters the sync diode output which in turn causes a wider or narrower sync pulse. Since timing is arrived at using the trailing edge of the sync pulse, the diode output and timing adjustments are interacting. To satisfy conditions 1 and 2 as previously stated, the combined adjustments of the sync lamp potentiometer, lamp, socket, timing disk diode potentiometer, and/or the complete lamp block assembly may be required.

#### **ADJUSTMENT**

The "anded" output of tape Channels 1, 2, 3, 6 and 7 can be used to check the sync pulse timing as follows:

Punch up a length of tape with G, EL, G, EL, etc., in consecutive positions. This can be done by inserting a read alphameric instruction with the typewriter designated as the input device. INSERT. Type 37 00501 00100, 39 00501 00200, 49 00012. RELEASE START. Type G, <sup>‡</sup>. RELEASE. START. The paper tape punch should now be punching the desired pattern. Form the punched tape into a loop and place on the read head.

- 2. Tie D1D14F and D1D14G to ground (system diagram 01.80.30.1). The eight input AND will now be satisfied when reading a "G" character. (Tape channels 1, 2, 3, 6, and 7; and channels 4 and 5 tied to ground). The tape pattern with alternate "G" and "EL" punches is used to obtain a data signal every other character.

- 3. Set up a program loop to read tape as follows: INSERT; Type 37 00501 00300, 49 00000. RELEASE; START; The reader should now be running the loop of tape.

- 4. Set scope trigger mode to external minus.

- 5. Sync scope on "anded" output at D1D14E on 01.80.30.1.

- 6. Scope D1D14E and place the center of the -S waveform in the center of the scope face. The -S "anded" output must be at least 2 milliseconds in duration. Failure to meet this requirement indicates an improperly aligned read mask.

- 7. A time/div. setting of approximately 500 sec/div. will spread the -S output waveform across the scope face.

- 8. Scope the sync diode output at A4A06C on 02.83.50.1.

- (a) Set the timing lamp potentiometer for 10v across the lamp.

- (b) Adjust the timing disk diode potentiometer for a negative peak of -10v on the timing signal (adjust the timing lamp if the potentiometer limit is reached).

- (c) Loosen the two lamp assembly holding screws and adjust the assembly for a maximum negative peak. Make sure that the top of the timing lamp is not touching the drive shaft.

- (d) Re-adjust the timing disk diode potentiometer to set the negative peak to -12v on the timing signal (just in saturation).

- 9. Scope the type sync output pulse at A4A06A and adjust the lamp assembly so that the fall of the sync pulse (+S to -S) occurs in the center of the "anded" output waveform within 0.5 milliseconds (Center of scope face due to Step 6). Scope A4A06A and A4A06C alternately to maintain the negative peak of the diode at -12v while positioning the sync. The negative peak may be re-adjusted to -12 with the timing diode potentiometer to facilitate this adjustment. See Figure 4.

Potentiometer Adjustment

- Sync on most convenient PCB Integrator fo translator problem.

- 4) Sync on Trigger 30, sync trigger, etc., for troubles during set of MDR.

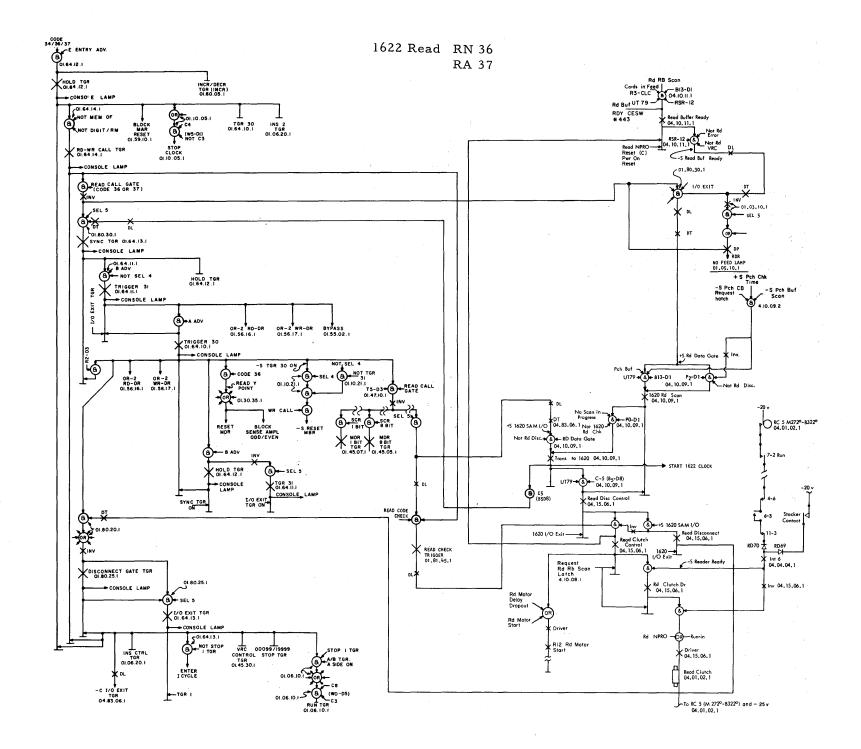

Read Checks Card Reader - Punch

à,

# 1622 Off Line Section

## Reader Checks

## Write Checks

## Card Reader - Punch

## 1622 Off Line Section

## Punch Checks

## KNOWN TROUBLE TIPS Card Reader Punch

FEED TROUBLE

- 1. Check feed knives for alignment and travel, and feed rolls for adequate pressure.

- 2. The failure of the last few cards to feed can result from too wide an angle between the card weight and the card weight spring. This can be corrected by using an older card weight or by forming the springs. Tension of the hopper contact will accentuate this condition.

- Card dust and shavings in the feed or dirt on the feed rolls can result in read-in errors. Operations which require overpunching result in fine card shavings which may not follow the chip chute and can float around in the transport and relay areas.

- 4. Care should be exercised in replacing the chip chute. It can be inserted backward covering the chute opening and causing chips to pile up inside the machine.

- 5. A loose feed roll drive belt can cause read-in errors. If the belt is too loose, it can jump a tooth on the first feed roll drive gear and cause the card to read one digit low for the card cycle. The trouble will be intermittent, for on the next card cycle it will be back in time. Loose belts can also cause CB timing variation and results in read-in errors.

- 6. The contact rolls setscrews should be checked to ensure that the roll is being positively driven. A dragging contact roll can cause read-in errors as well as jamming problems.

- 7. Pressure shoes should be checked for sufficient tension and even drag. The shoe surfaces tend to become polished. This trouble can be corrected by increasing the spring tension or roughening the surface of the shoes. Lack of, or uneven, tension can cause off-punching as well as jamming.

- 8. If jamming is experienced at the forward aligners, the edge of the aligners should be examined. If the surfaces are not smooth, they should be honed.

- If the die retracting pin spring tension is insufficient, it is possible for the pin to bounce in the card line. This will show as a nick on the card edge and again result in off-punching as well as jamming.

Lubriplate (IBM #70), P/N 435682 has been helpful in reducing belt and pulley wear.

## **BRUSH TROUBLE**

- 1. Check the reading brushes for correct timing and tracking.

- 2. Brushes should be centered over the contact roll to facilitate straight feeding of the card and prevent it from being forced up or down into the card guides. Bent brushes can catch the card edge or holes in the card. Care in removing and replacing the brush blocks in the machine will reduce the bent brush problem.

- 3. Intermittent read failures can occur if brushes rub the brush separator. Over-all centering of brushes in the brush separator slots is accomplished by shifting the brush separator. Individual brushes which are misaligned must be individually aligned for proper centering within the separator slots. This should result in the brushes tracking through the center of the hole. Any brush separators which do not permit uniform tracking at the extreme ends of the card should be replaced.

- 4. Read-in troubles can result from brush blocks which have not been locked in place. Always check the brush blocks on a read-in trouble call.

- A loose feed roll common brush or a lack of a common brush tension can result in read-in errors.

- 6. Also check for:

a. Loose, cracked or broken Quick Disconnect blocks.

- Loose individual terminals from brush cable or between Quick Disconnect and brush blocks.

- c. Examine and flex brush cables to check for open or shorted wires.

- Carefully examine the brushes for bent, broken (electrical shorts) or short (brush) strands. A short strand can be a real trouble-maker and is difficult to see.

## PUNCH TROUBLE

- Off-punching cards by one digit can be caused by a loose picker knife drive belt. This can happen when the clutch latches and the belt jumps one tooth on first feed roll drive pulley.

- 2. If cards are nicked on the leading edge by the punches, check the timing of the first stepped roll.

- 3. If vertical registration varies slightly, check pressure shoe springs for tension. Check that pressure shoes have not become polished where they contact the card.

- 4. Varying vertical registration can be caused by an intermittent roll closing too soon and moving the card slightly at end of the previous Geneva cycle.

- 5. Variable registration 12 through 9 may be caused by insufficient intermittent roll tension. Tension trouble can be caused by the cam follower hitting the low dwell of its operating cam or by a weak spring.

- 6. Variable registration 12 through 9 may be caused by polished intermittent rolls or worn Geneva gears.

- 7. If vertical registration is off for the entire card, check Geneva gears for proper mesh and for loose pins.

- 8. If the punch unit cuts long holes or is tearing holes, check the punch unit timing.

- Partial punching or double punching can be caused by too little armature-to-core clearance. Partial punching can also be caused by too much armatureto-core clearance.

- 10.Insufficient wink between the Geneva Drive Gears and the intermittent roll drive gears can result in rapid gear wear and breakage of the intermittent roll shaft. Wink must be checked around the circumference of the gears. There must be a minimum perceptible wink and a maximum of .003" wink. If an intermittent roll shaft breaks, the gear wear in the Geneva is usually found to be sufficient to require the replacement of the Geneva drive housing also.

- 11.Card jamming can be caused by loose punch bail tongue screws (apply Glyptol to threads).

#### STACKER TROUBLE

- Jamming in the stacker area can result from improperly adjusted chute blades, loose screws on the magnet assembly, or oil between the chute blades.

- 2. The stacker plate can bind owing to warpage of the plastic, which can cause jamming in the stacker pocket. This trouble can be eliminated by grinding, filing, or sanding the top edge of the plate that goes into the slides.

- 3. If cards are turned end for end, check for verify notch catching.

#### GENERAL

Cables should be inspected occasionally for rubbing against the frame or gates. Where rubbing is experienced, retaping and repositioning, if possible, are suggested.

## SERVICE HINTS

#### Card Reader Punch

Trouble-shooting Methods

Removing the error relay driver A2C07 effectively cripples the error stop circuits.

Grounding either the read buffer ready latch or the punch buffer ready latch permits continual transfer of data between the buffer and the 1620, while the 1622. is stopped. This permits scoping the data transfer circuits without cards in the 1622.

#### Reader Scan Ring - RSR

Reader scan ring trouble will usually show up as dropped or extra bits in the SCR. To check:

- 1) Turn on the read row bit scan latch by grounding A2C10 F (04.10.08.1). The RSR should now be running.

- Scope timings and levels using marginal voltages as needed.

## Row Bit (RB-2)

If the RB-2 read sense amplifier is failing, the SCR will contain all "C" bits after reading in a card containing miscellaneous punches.

If a single position of RB-2 fails when displayed in the SCR, the SCR will contain "C" bits regardless of data in the associated card column. Also, a read check will occur (B2 light on) for any column containing as odd numbers of holes. To check:

- Run a test deck with ripple pattern if it appears that there is no output from the RB-2 sense amplifier.

- 2) If it is a single column failure, run a test deck with a punch in the failing column.

- 3) Scope sense amplifier output at A1 B05 AF (04.30.02.1) using internal sync.

- a. If there is no output using the ripple deck, the trouble could be the common brush, common brush transistor, display switch contacts, CLC and CLC relay points, or the sense amplifier.

- b. If there is no output for a single position, the trouble could be the individual reading brush and circuit, read brush resistor, or connector.

c. Incorrect CB timing will give reading failures. Note: The same testing procedure is used for RB-2 punch sense amplifier. Items a. and b. apply to the punch side also. Scope at A1 B04 AF (04.30.02.1).

## Row Bit Register 2 (RBR-2)

This single latch is turned on by the output of either the read or punch RB-2 sense amplifier. To check:

- 1) Run same test decks as when checking RB-2.

- Scope RBR-2 (on side) output at A1 B18 B (04.25.03.1).

#### Single Character Register (SCR)

Failures of the RSR, inhibit drivers, SCR latches, RB-2 and RBR-2 will show up in the SCR. If a check of the RSR, RB-2 and RBR-2 shows that they are functioning properly, a further check of the SCR and associated circuits is indicated.

SCR failure indications:

- Groups of ten dropped (SCR blank), for example: 0 through 9, 10 through 19, 20 through 29, etc., indicates a failure in the selection (decode) switches in the tens part of UTR.

- - a. Turn on RBR-2 latch by grounding A1 B18 P (04.25.03.1).

- b. Turn on the read select key and single cycle to the failing position.

- c. Turn on the not units advance key to prevent UTR from stepping.

- d. Depress the start key.

The failing position should be reading and writing in the read buffer. Scope read and write decode switches, A1 D05 F and H (04.30.06.1). The voltage probe can be used to determine that a decode switch is selected. However, the current probe must be used to check that the decode switch and current source circuit is functioning properly.

- Pattern of all 1 bits or all 4 bits, etc., dropped, indicates a possible failure of an inhibit driver or one of the SCR latches. To check:

- a. Read in one card which contains punches associated with the failing bit.

- b. Turn on read select switch.

- c. Depress CE start key. The clock and UTR should now be running and circulating the character through the 80 positions of the read buffer and associated circuitry.

- d. Sync on BO.

- Check levels and timings of the sense amplifier strobe, sense amplifier output, read/write current or voltage, inhibit lines, and SCR latches.

- f. Vary marginal voltage as needed.

- 4) For particular character dropping or picking up bits (6 (4-2) drops the 2 or 6 (4-2) comes out as 4-2-8):

- a. Check RSR as given previously.

- b. The failure could be in the card-code-to-BCD translator.

## Card-Code-to-BCD Translator

Failures in the translator will show as dropped or extra bits in the SCR. As an example, dropping or picking up of bits for a six is used here. To check:

- Turn on read row bit scan latch by grounding A2 C10 F (04.10.08.1).

- Turn on RSR-6 latch by grounding A2 E16 F on 04.35.14.1.

- Turn on RBR-2 latch by grounding A1 B18 P (04.25.03.1).

- 4) Turn on read select switch.

- 5) Depress start key on CE panel. The output of RBR-2 is now being translated as a six and is continuously circulating through the read buffer and associated circuitry.

- Use scope to check circuits (Sync on B0 at A2 E05 A (04.15.01.1). Vary marginal voltages as needed.

Read Trans Accu (Pre "J" Suffix Machines Only)

- To check operation of the read trans accu scan latch:

- 1) Place a deck of blank cards in the hopper.

- 2) Turn on line-off line switch to off line position.

- Set up scope to observe the read trans accu scan latch. The latch will be turned on once and then off.

- 4) Depress CE start key to cause a three card run-in. Observe scope.

If the read trans accurscan latch fails to turn on, check circuits back to and including the CB's.

If the read trans accu scan latch turns on, the following procedure can be used to set up a continuous loop for transferring A1 to A2 and B1 to B2.

- Set all A1 and B1 cores to the one state by initiating a three card run-in using a ripple deck.

- Turn on the read trans accu scan latch by grounding A2 D13 F (04.10.08.1). With the read trans accu scan latch turned on, the clock and UTR will start. The one status of the A1 and B1 cores will transfer to A2 and B2 on the first UTR cycle.

- Remove the ground from the read row bit scan latch and single cycle 00 through 79 observing that the A1, B1, A2 and B2 lights are on for each core position.

For a further check of A1, A2, B1, and B2 circuits, see procedure given under Reader-Punch Check Circuits.

## 1622 to 1620 Transfer (Read) Operations

## Continuous Transfer Loop

The following procedure can be used to facilitate locking the 1620–1622 in a continuous transfer to 1620 operation.

- Insert the following program: 00000 36 01000 00500 00012 46 00000 00600 00024 49 00000

- 2) Turn read check error switch to the program position.

- Place a card with the desired information, as well as an 11-12 punch combination in any column other than column 80, in the read feed. Run in card under control of the above program.

This procedure will force a 1620 read check which will prevent a read clutch cycle and also prevent resetting the buffer ready latch. Continuous transfers to 1620 will take place with a read check occurring on each. However, the 46 code will interrogate and reset check indicator allowing subsequent transfers to proceed.

Control lines and data lines can be scoped dynamically while this program is running.

#### Alternate Procedure for Continuous Transfer Loop

This procedure does not force a read check. Therefore, if for some reason the forced read check is undesirable, this alternate procedure should be used.

- Turn on the read buffer ready latch by grounding A2 C05 K (04.10.11.1)\*

- 2) Insert: 00000 36 xxxxx 00500 RN 00012 34 00000 00101 K-Space 00024 49 00000 00000 B

- 3) Depress release key then start key. The data and control lines may now be scoped as desired.

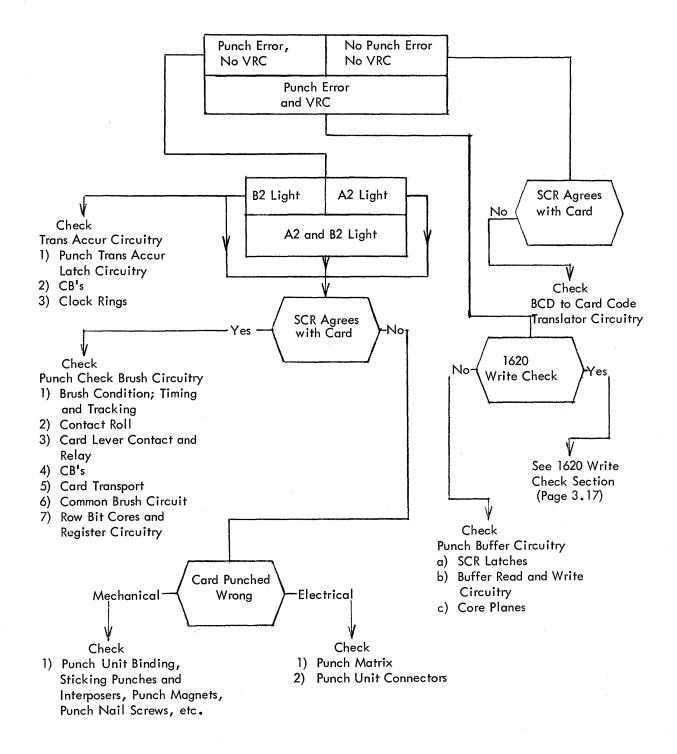

PUNCH SERVICING PROCEDURES, CHECKS AND HINTS

## Punch VRC Immediate Stop

The units tens ring can be stopped when a punch VRC occurs by connecting jumpers as follows: from A2 C15 E (Logic 04.10.07.1) to an unused inverter circuit to A2 C04 C (Logic 04.10.10.1). The units tens ring will stop immediately because the units advance will be blocked. The card will be laced in the specific column in which the VRC occurred and for the remainder of the card. The punch buffer will not be reset. After removal of the jumpers, it will be possible to interrogate it for the cause of the VRC. The stop key must be depressed before removal of the jumpers to prevent reloading the buffer.

\*or read buffer ready switch if machine so equipped.

#### Punch Scan Ring (PSR)

Punch scan ring failures are shown by incorrectly punched cards such as double punching or missed punches in an entire row. Punch check errors will also occur.

To check the PSR, turn on the punch scan latch by grounding A2 D16 F (04.10.08.2). When the punch scan latch is on, the UTR and the PSR start. Scope the PSR circuits for levels and timings. Vary marginal voltage as needed.

#### BCD-to-Card-Code Translator

Failures in the BCD-to-card-code translator show up as incorrectly punched cards. To check:

- 1) Load the punch buffer from the 1620 (write code operation) using data corresponding to the failure.

- 2) Follow checking setup procedure given under PSR.

- Scope the BCD-to-card-code translator for timings and levels, varying the marginal voltage as needed.

Note: Failing punch magnet circuitry and punch mechanics will also appear as incorrectly punched cards.

1620 to 1622 Transfer (Write) Operation

## Continuous Transfer Loop

The following procedure can be used to facilitate locking the 1620–1622 in a continuous transfer to 1622 operation.

- Turn on the punch buffer ready latch by grounding A2 D26 H (04.10.11.1)\*

- Insert the following program: 00000 38 xxxxx 00400 WN 00012 34 00000 00101 K-Space 00024 49 00000 00000 B

- 3) Depress release key then start key. The data and control lines may now be scoped as desired.

## READER-PUNCH CHECK CIRCUITS

Checking A1, B1, A1-CBCR, B1-CBCR, OR and Exclusive OR

The objective of this procedure is to test:

- 1) A1-CBCR and B1-CBCR.

- 2) The OR associated with A1-CBCR.

- 3) The exclusive OR (XO) associated with B1-CBCR.

- 4) The inhibit drivers for A1 and B1 core planes.

- 5) The read drivers, write drivers, and sense amplifiers associated with A1 and B1 core planes.

## Procedure

- Operate NPRO key to clear all check planes (reset cores to "0").

- Turn on RBR-1 latch by grounding A1 B18 F (04.25.03.1).

- \*or punch buffer ready switch if machine so equipped.

- a. For single cycle operations:

- (1) Turn on single cycle switch.

- (2) Turn on read select switch.

- (3) Using CE start key, single cycle 00 79 five times. The A1 and B1 lights should show the following pattern:

First time through A1 and B1 are blank Reading out cleared cores ("0") and writing back 1's from RBR-1 through OR (A1) and through XO (B1).

Second time through A1 and B1 are on for each position

Reading out 1's set on first time through. Writing into A1 plane from A1 OR RBR-1. Inhibiting writing into B1 plane because both RBR-1 and B1 are on and the XO inhibits the write back.

Third time through A1 is on for all 80 positions -B1 is blank

Reading out A1 cores which were set on second time through. B1 blank because B1 cores were inhibited from writing on second time through. Write back into A1 cores from A1 or RBR-1.

Write back into B1 from RBR-1 through XO. Fifth time through Same as third time. Note: That after the first time through (all blank), the second, fourth, sixth, etc., times through will always be alike.

- b. For electronic speed operation:

- (1) Turn off single cycle switch.

- (2) Depress CE start key and allow rings to run for a few seconds.

- (3) Depress CE stop key. The A1 and B1 configuration should be like either an even (second, fourth, etc.) time through, or an odd (third, fifth, etc.) time through.

- (4) Turn on single cycle switch.

- (5) Using CE start key, single cycle 00 through 79 twice to observe that the A1 and B1 lights conform to the odd or even configuration. If A1 or B1 do not conform, run the machine at electronic speed and scope the circuits while checking timings and levels. Vary the marginal voltage as needed.

Checking A2, B2, A2-CBCR, B2-CBCR, Comparing AND, and Exclusive OR

- The objective of this procedure is to test:

- 1) A2-CBCR and B2-CBCR.

- 2) The comparing and associated with A2-CBCR.

- 3) The exclusive OR (XO) associated with B2-CBCR.

- The inhibit drivers, read drivers, write drives and sense amplifiers associated with the A2 and B2 core planes.

#### Procedure

- Operate NPRO to clear all check planes (reset cores to "0").

- 2) Turn on read select switch.

- Turn on A2-CBCR latch by grounding A1 B20 F (04.25.03.1). The output of A2-CBCR is used to set all cores in A2 to the one status.

- Turn on B2-CBCR latch by grounding A1 B20 P (04.25.03.1). The output of B2-CBCR is used to set all cores in B2 to the one status.

- 5) Using CE start key, run the machine for a few seconds.

- 6) Depress CE stop key. The cores in the A2 and B2 planes should be all set to the one status.

- 7) Remove ground wires from A2 and B2-CBCR's.

- 8) Using CE start key, run machine for a few seconds. The A2 cores are being read out to A2-CBCR. With A2-CBCR on and RBR-2 off, the comparing AND is satisfied and at write time the A2 cores will be set to the one status. The B2 cores are being read out to B2-CBCR. With B2-CBCR on and RBR-2 off, the XO causes a one to be written back into the B2 cores.

Single cycle through all 80 buffer positions and check that the A2 and B2 lights come on for every position. If the check is satisfactory, the A2 and B2 sense amplifiers, read drivers, write drivers, comparing AND and exclusive OR circuits are working properly for a no compare condition. Vary marginal voltage as needed.

To check the comparing AND and the exclusive OR for a compare conditions and to check the inhibit drivers, the RBR-2 latch must be turned on. With RBR-2 on:

- The comparing AND will not be satisfied and the one status of the A2 cores read out to A2-CBCR will be inhibited from writing back into the A2 plane.

- The XO circuit will have like inputs to both sides on one cycle (B2 core reads out to turn on B2-CBCR) and will therefore inhibit writing back into the B2 plane.

On the next cycle B2-CBCR will not be turned on (no cores in the one status in B2 plane) while RBR-2 is still on. The XO circuit has unlike inputs and ones will be written back into B2 plane. To check:

- 1) Turn on RBR-2 by grounding A1 B18 P (04.25.03.1).

- 2) Turn on single cycle switch.

- 3) Turn on read select switch.

4) Using CE start key, single cycle 00 through 79. First cycle through A2 and B2 on Second cycle through A2 off and B2 off Third cycle through A2 off and B2 on Fourth cycle through Same as second Fifth cycle through Same as third

This test can be made at electronic speeds. If failures develop, scope the associated circuitry for levels and timings. Vary the marginal voltage as needed.

## INTERLEAVE OPERATION

Reader or punch checks may occur with interleave troubles.

Indications of Interleave Problems

- The 80th character transferred to the 1620 is missing or incorrect. This could occur if the punch trans accu scan latch is turned on while the read disconnect latch is on. The extender A1 E09 (04.10.08.2) to the AND A2 D20 is for the purpose of preventing this condition. This applies to pre "J" suffix 1622's only.

- Incorrect or missing punching and reading could occur in the punch operation latch A2 A16 (04.10.09.2) fails to turn on during a punch operation and a read operation is initiated by the 1620.

- 3) If an attempt is made to select the read and punch buffer simultaneously, nothing will be punched and nothing will be loaded into the read buffer. (Units read and write "X" drivers are inoperative). A VRC check will result because nothing will be placed in the SCR. Operating the CE read and punch select switches at the same time will cause the condition just described.

- 4) If data being loaded into the read buffer is simultaneously punched in a card and this data is not in the punch buffer, the "+S Punch buffer scan" to A2 B08 H (04.35.01.1) is probably floating (open).

Interleave Trouble Diagnosis Run read and punch "off line" simultaneously.

If interleave failures do not occur, the failing interlock is associated with either transfer from or transfer to the 1620. If failures do occur, they eliminate the previously mentioned interlocks.

If the failures occur fairly frequently (every 5 or 6 cards), the failing interlock is probably the read row bit scan and punch buffer scan.

Failures between row bit scan and punch trans accu or between punch buffer scan and read trans accu occur every 40 to 50 cards.

Failures seldom occur between read trans accu and punch trans accu or between stacking latches.

#### Checking Interleave Operations

Jumper wires may be used to force interleave between any two of the scan latches. For example, an interleave between read row bit scan and punch buffer scan can be forced as follows:

- 1) Put the punch stacking latch (A2 D16) on an extender and remove the lead from pin L.

- Jumper from the read stacking latch turn-off output (A2 C10 Q on 04.10.08.1) to the punch stacking latch turn-on input which is now on the extender (A2 D16 L on 04.10.08.2).

- 3) Jumper from the punch stacking latch turn-off input (A2 D16 Q on 04.10.08.2) to the read stacking latch turn-on input. (A2 C10 L on 04.10.08.1).

Pin L is not in use so an extender is not needed.

- 4) Depress the reader or punch start keys to start the operation.

Once started, the read row bit scan and punch buffer scan should alternate but never overlap. If a failure occurs, alternation may stop. If it stops, run one feed and scope the interlocks involved.

Jumper wires may be used to force interleave between other latches. (This applied to pre "J" suffix 1622's only).

| 1) | Read Stacking Late                | :h    | Punch Trans Accu Stacking<br>Latch           |

|----|-----------------------------------|-------|----------------------------------------------|

|    | Jumper A2 C10 Q<br>A2 D19 Q       | to A2 | 2 D19 L and A2 C10 L to                      |

| 2) | Read Trans Accu<br>Stacking Latch |       | Punch Stacking Latch                         |

|    | Jumper A2 D13 Q                   | to    | A2 D16 L (lead removed on<br>extender pin L) |

|    | and A2 D13 L                      | to    | A2 D16 Q                                     |

| 3) | Read Trans Accu                   |       | Punch Trans Accu Stacking                    |

|    | Stacking Latch                    |       | Latch                                        |

|    | Jumper A2 D13 Q                   | to    | A2 D19 L                                     |

|    | and A2 D13 L                      | to    | A2 D19 Q                                     |

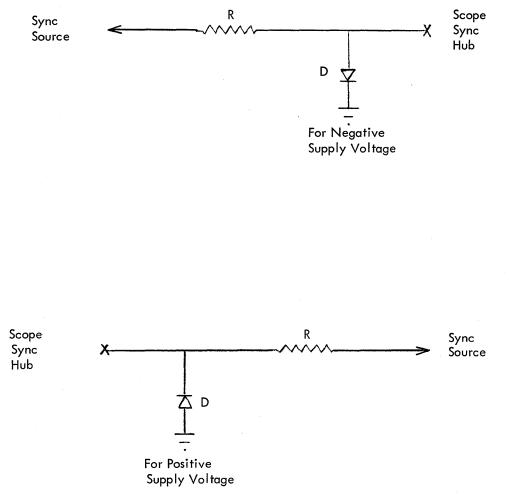

#### **Miscellaneous Service Hints**

When a line containing an inductive spike must be used as a scope sync, i.e., relays, magnets, etc. a resistor and rectifier may be used as shown to remove the spike at the scope sync hub (this does not remove the spike in the machine). (See Page 3.36)

## OFF LINE SERVICING

Punch buffer or read buffer can be loaded artifically by forcing bits from the single character register and the CE switches in back of the machine.

- Ground "P" or "F" pin of desired SCR latch or latches (see logic pages 04.25.01.1 and 04.25.02.1)

- 2) Transfer Read Select or Punch Select Switch.

- 3) Depress start key. (Single cycle switch may be transferred for advancing one position at a time).

May be 10K to 50K

R

D

May be any diode or small selenium rectifier that has a voltage rating greater than the supply voltage. Single Cycle 1622 Read Operation

- Jumper A2 B23 H to A2 E26 F and A2 A11 B to A2 E26 A (or any other unused inverter) - Allows CE clock start.

- 2) Remove SMS card at A2 C07 Prevents error stop of machine.

- 3) Remove SMS card at A2 B23 Prevents automatic clock start.

- 4) Remove PM Relay #3 Opens #2 read CLC circuit.

- 5) Transfer the following switches:

- a. Override switch

- b. Off line switch

- c. Single cycle switch

- d. Read select switch

- 6) Run any card with all 80 columns punched through read feed (any punches) Loads RB-1 cores.

- Single cycle the UT ring for RB-1 to A1B1 transfer -RB-1 light should be on for all positions.

- Again single cycle the UT ring to check RB-1 to A1B1 transfer - RB-1 light should be out and A1B1 lights should be on for all positions.

- 9) Ground A2 D13 F Collector Pullover Read Trans Accu Latch.

- 10) Single Cycle the UT ring for A1B1 to A2B2 transfer-A1B1 and A2B2 lights should be on for all positions.

- Replace PM Relay #3 and remove PM Relay #2 -Opens #1 read CLC circuit.

- 12) Run any card with all 80 columns punched through the read feed. (Any punches) - Loads RB-2 cores.

If display of other than a 12 punch (CAB bits) is desired, follow Steps 13 and 14.

- Remove the SMS card at A2 D13 (Read Trans Accu Latch) - Prevents continuous reset of Reader Scan Ring Latches.

- 14) Advance Reader Scan Ring as follows: Ground A2 E18 A (RSRB advances) Ground A2 E17 A (RSRA advances)

Repeat alternately to advance ring 9-8-7-6-5-4-3-2-1

Then Ground A2 E21 F (RSRB advance P) Ground A2 E22 E (RSRA advance P)

Repeat alternately to advance ring 0-11.

- Single cycle the UT ring for RB-2 to A2B2 and buffer transfer - A1B1 lights out and A2B2 lights on.

- 16) Again single cycle the UT ring to check RB-2 to A2B2 and buffer transfer - A2B2 lights out, single character register displays bit structure of character, Reader Scan Ring was set for

17) Repeat 16 - Bufferwrong - inhibit trouble.

Single Cycle 1622 Punch Operation

- Load 1622 Punch Buffer with all positions having the bit structure (same character) as follows:

a. Insert 36 00100 00100

- b. Rel Start, type in 80 characters (same character)

- c. Insert, type in 38 00100 00100 49 00000

- d. Run blank cards in and punch several cards

- e. Stop machine

- 2) Jumper A2 B23 H to A2 E26 F and A2 A11 B to A2 E26 A or any other unused inverter (Allows clock start)

- 3) Remove SMS card at A2 C07

- 4) Remove SMS card at A2 B23

- 5) Remove Relay 32

- 6) Transfer the following switches:

- a. Override switch

- b. Off line switch

- c. Single cycle switch

- d. Punch select switch

- 7) Reset A1B1 and A2B2 as follows:

- a. Ground A1 B23 G

- b. Step through UTR

- c. Ground A1 B23 K

- d. Step through UTR

- 8) Turn on Punch Scan Latch Ground A2 D16 F

- Advance Punch Scan Ring to character position before the one equal to the digit stored in Punch Buffer.

- Remove the SMS card at A2 D19 Punch Trans Accu Latch - Prevents continuous reset of Punch Scan Ring.

- Advance Punch Scan Ring as follows: Ground A2 F16 A (PSRB advance) Ground A2 F15 A (PSRA advance)

Repeat alternately to advance ring 12–11–0–1–2– 3–4–5–6 then Ground A2 F22 P (PSRB advance P) A2 F23 E (PSRA advance P) Transfer to and from 1620 can be accomplished by

turning on CE MAR stop bypass switch. SCE key can be used to single cycle these transfers when a Read or Write Op code is addressed in the 1620.

- Single cycle UT ring for Buffer to A1B1 transfer -RB-1 should be on for all positions.

- Again single cycle UTR ring to check buffer to A1B1 transfer - RB-1 light should be out and A1B1 light on for all positions.

- 14) Replace A2 D19 SMS card in socket.

- 15) Ground A2 D19 F collector pullover punch Trans Accu Latch.

- Single cycle UT ring for A1B1 to A2B2 transfer A1B1 and A2B2 lights should be on for all positions.

- 17) Replace Relay 32.

- Run any card with all 80 columns punched through the punch feed (any punches).

- Single cycle UT ring for RB-2 to A2B2 transfer (RB-2, A1B1 and A2B2 lights should be on for all positions).

- 20) Again single cycle UT ring to check RB-2 to A2B2 transfer (RB-2 and A2B2 lights should be off and A1B1 lights should be on for all positions).

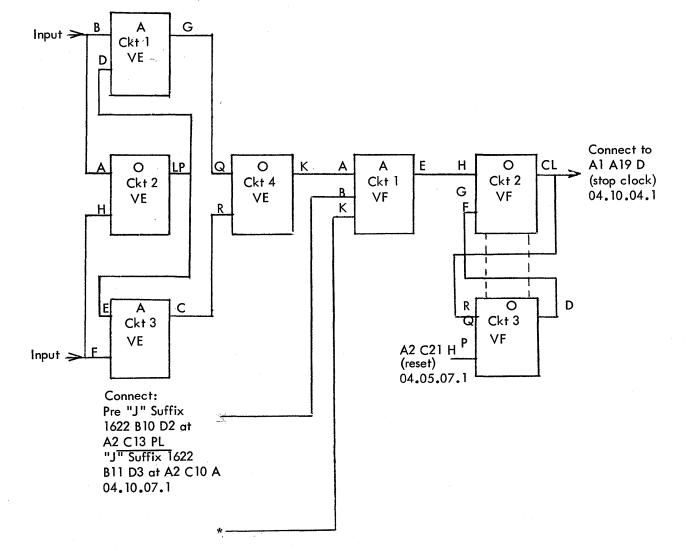

#### Stop on Error - IBM 1622

For highly intermittent trouble experienced in comparing circuits on the 1622, the following circuit can be wired temporarily. It will stop the clock in the UT ring position and scan ring position in which the failure occurred.

To check read trouble, it is necessary to gang punch a deck of cards from one given card (preferably an error card) having random punching in it. Trans Accu operation (Test 3) can only be checked with cards having a single punch per column.

To check punch trouble, it is only necessary to punch repetitively from a given area of memory having information similar to that described in the previous paragraph. (See Page 3.39)

# CHARTS

Pages 5.40 through 3.43 are improved timing and function charts for 1620-1622 transfer operation.

Test 1 - To check row bit registers, row bit cores, brushes, etc., run in cards, connect inputs indicated in drawing to RBR-1 at A1 B18 F and RBR-2 at A1 B18 P on 04.25.03.1 and either read or punch cards as described above. Machine will stop on error with only one RBR light on.

Test 2 - To check CBCR circuitry, run in cards, connect inputs indicated in drawing to CBCR-A1 at A1 B19D and CBCR-A2 (04.25.03.1). \*Connect Pin "K" of VF circuit 1 in drawing to appropriate (read or punch) +S Trans Accu on 04.10.08.1 or 2. Machine will stop on error with only one CBCR-A light on.

Test 3 - To check Trans Accu circuitry, run in cards, connect inputs indicated in drawing to CBCR-A2 at A1 B20 D and CBCR-B2 at A1 B20 C (04.25.03.1). \*Connect Pin "K" of VF circuit 1 in drawing to appropriate -S Trans Accu on 04.10.08.1 or 2. Machine will stop on error with only one CBCR #2 light on.

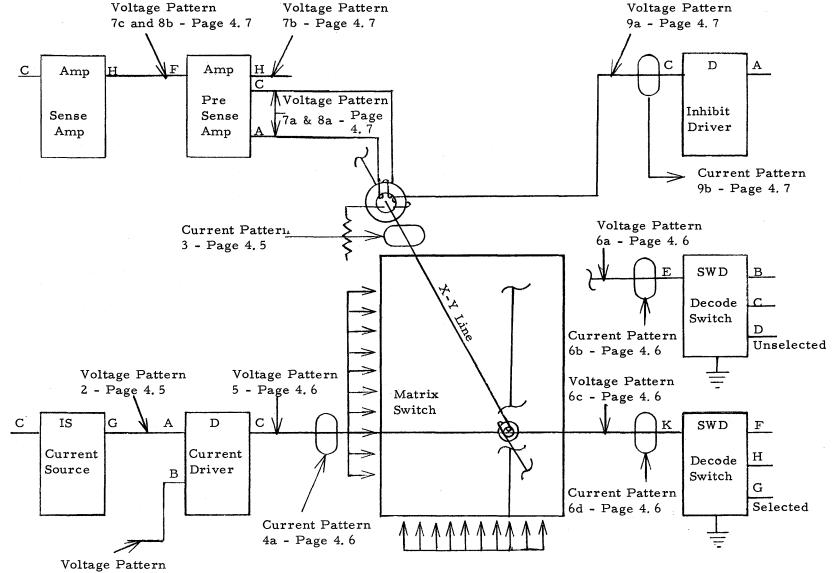

## CORE STORAGE

|                          | Page |

|--------------------------|------|

| MBR Checks               | 4.2  |

| Service Procedure        | 4.3  |

| Scope Chart and Patterns | 4.4  |

| CORE STORAGE SERVICING PROCEDURE                                                                                                                                                                                                                                                     | current which would cause the shorted line to carry                                                                         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Because of the size of core storage wires and terminals                                                                                                                                                                                                                              | less current than is necessary for proper operation.                                                                        |  |

| a strong light and magnifying glass is desirable when                                                                                                                                                                                                                                | Therefore, with this type of failure, unpredictable                                                                         |  |

| broken wires and shorts are suspected.                                                                                                                                                                                                                                               | results can occur:                                                                                                          |  |

| In diagnosing memory problems, it should be kept in mind that a short in core storage will cause a split in                                                                                                                                                                          |                                                                                                                             |  |

| Problem                                                                                                                                                                                                                                                                              | Possible Cause                                                                                                              |  |

| 1. No read or write in any position of memory                                                                                                                                                                                                                                        | Bias winding, current source, or current driver.                                                                            |  |

| <ol> <li>Missing bits in either all even addresses (or odd)</li></ol>                                                                                                                                                                                                                | Open sense winding or weak presense amplifier.                                                                              |  |

| in all addresses either <50 or>50.                                                                                                                                                                                                                                                   | Shorted inhibit drives.                                                                                                     |  |

| <ol> <li>Extra bits in either all even addresses (or odd) in</li></ol>                                                                                                                                                                                                               | Open inhibit winding or weak inhibit driver.                                                                                |  |

| all addresses either <50 or >50.                                                                                                                                                                                                                                                     | Shorted sense amp.                                                                                                          |  |

| <ol> <li>Dropping all bits in banks of 10 addresses, i.e.,<br/>X09XX, X19XX to X99XX.</li> </ol>                                                                                                                                                                                     | Decode switch or associated wire in matrix switch.<br>(An open decode switch can cause damage to other<br>decode switches). |  |

| <ul> <li>5. Dropping all bits in addresses as patterned below:</li> <li>(a) 200 addresses</li> <li>(b) Common digits in either units, tens and ten<br/>K or hundreds and thousands, i.e., 000XX to<br/>099XX and 100XX to 199XX or 0XX00 to<br/>0XX99 and 1XX00 to 1XX99.</li> </ul> | Open X or Y line.                                                                                                           |  |

6. With conditions in Step 5 but in banks of 10. Open inductor.

| Operation              | Switch #3   | Switch #4   | Switch #5   | Switch #6   |

|------------------------|-------------|-------------|-------------|-------------|

| Force all bits         | Normal      | Normal      | Transferred | Transferred |

| Blank Memory           | Transferred | Transferred | Normal      | Normal      |

| Force Flag 8's<br>(88) | Normal      | Transferred | Transferred | Normal      |

| Force 7's (77)         | Transferred | Normal      | Normal      | Transferred |

1b - Page 4.5

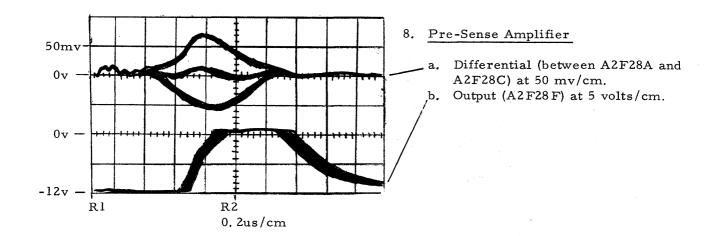

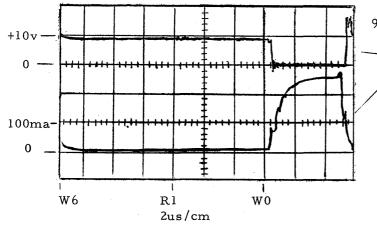

TYPICAL CORE STORAGE CIRCUITRY

a. Unselected (A2H25E) at 20 volts/cm.

- b. Unselected (A2H25E) at 200 ma/cm.

- c. Selected (A2H25E) at 20 volts/cm.

- d. Selected (A2H25E) at 200 ma/cm.

R1

2us/cm

**W**6

- 9. Inhibit Driver

- a. Output (A2E08C) at 10 volts/cm.

- b. Output (A2E08C) at 100 ma/cm.

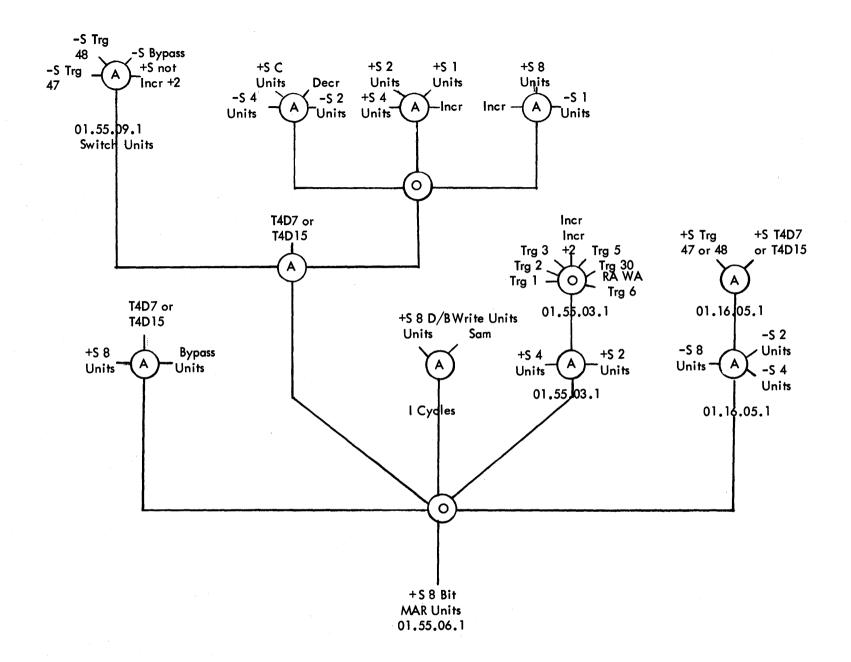

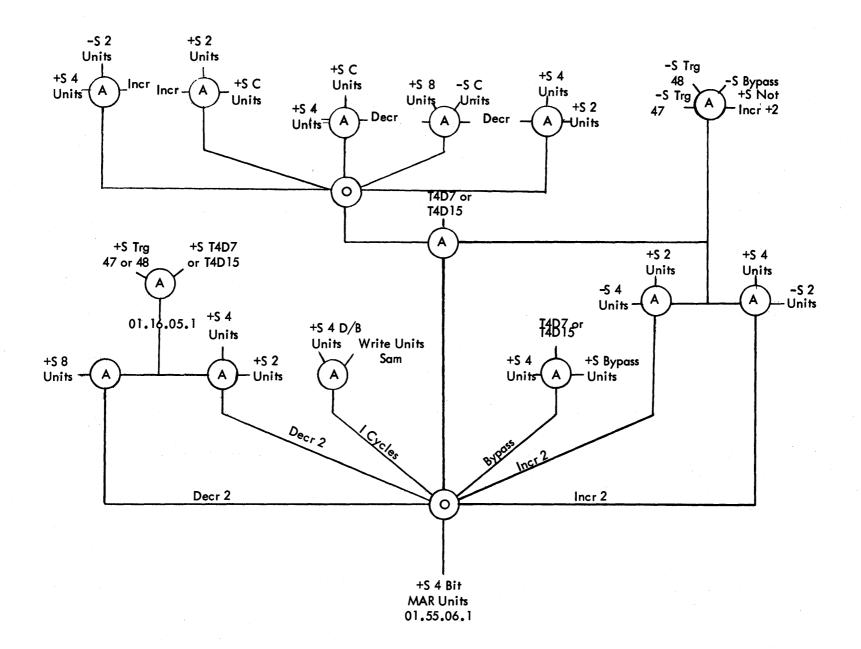

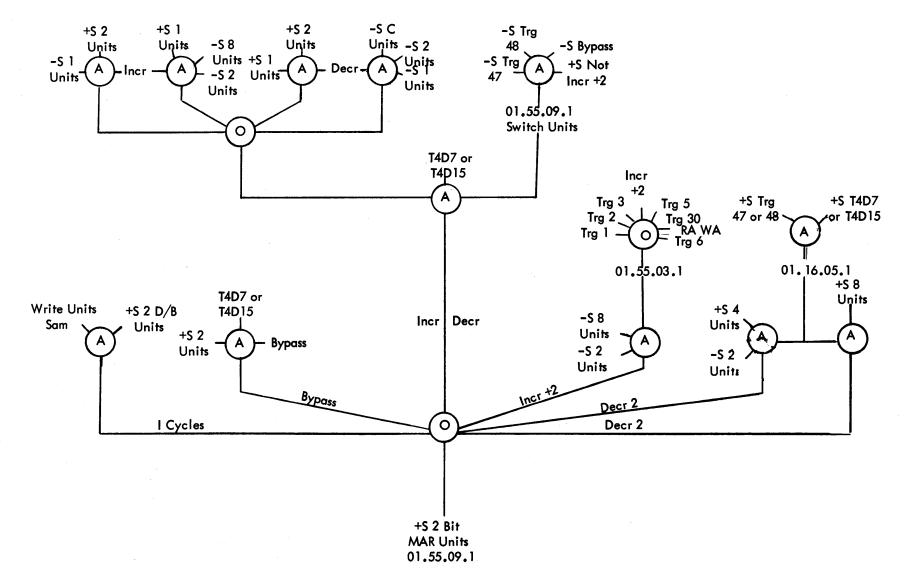

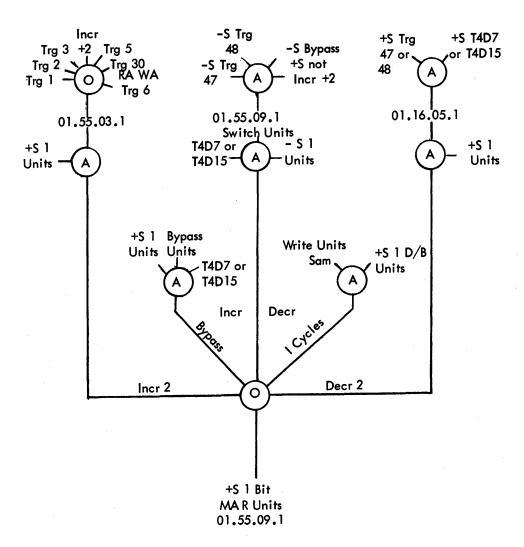

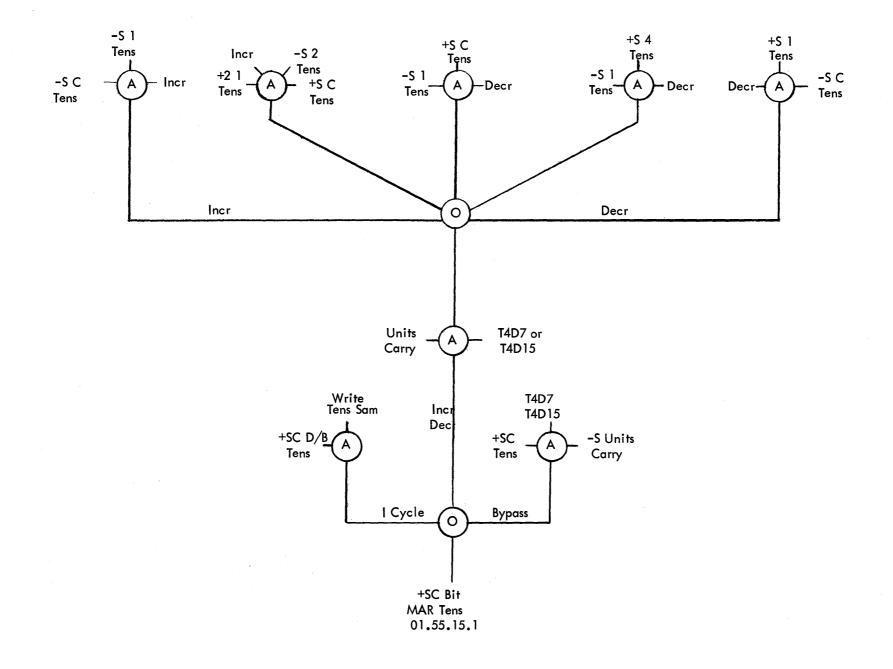

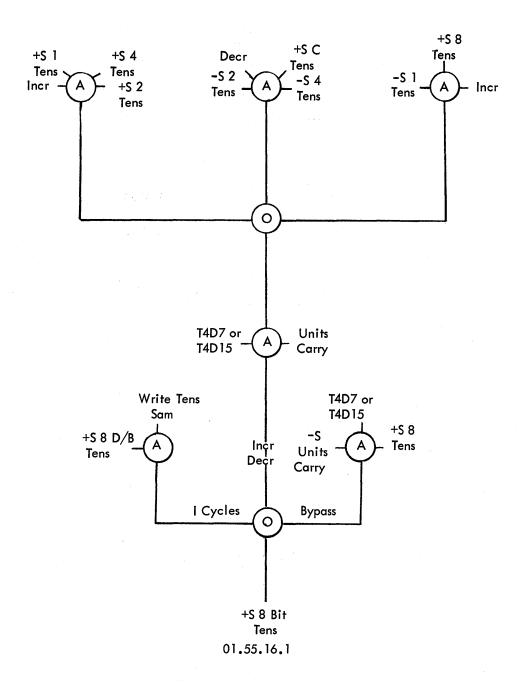

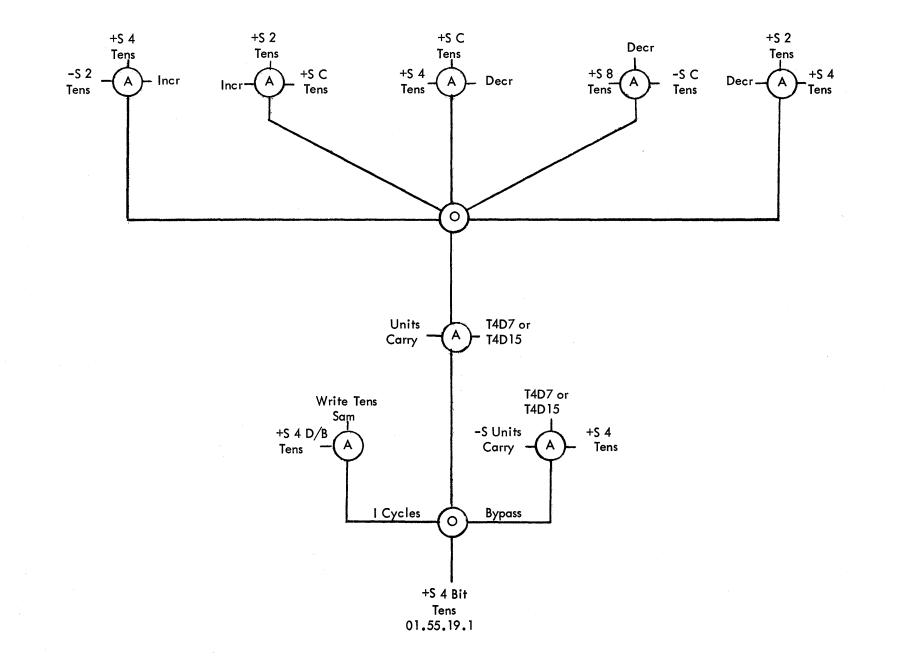

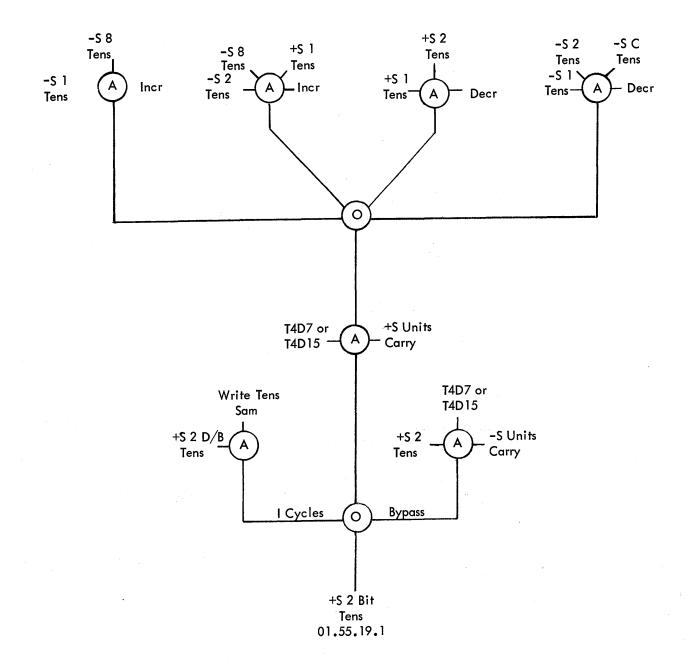

## MAR

|                     | Page |

|---------------------|------|

| MAR Checks          | 5.2  |

| Service Hints       | 5.3  |

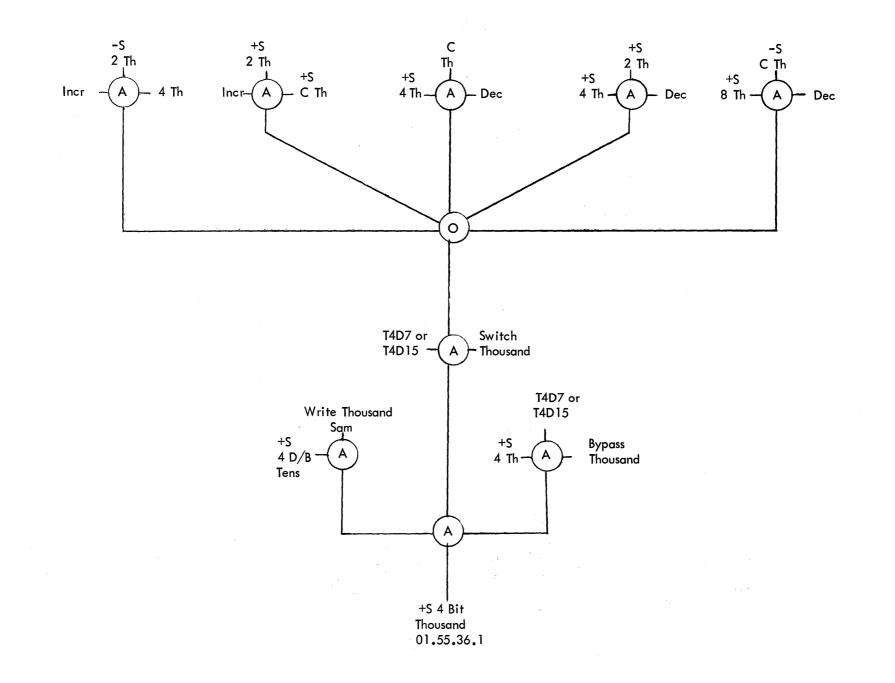

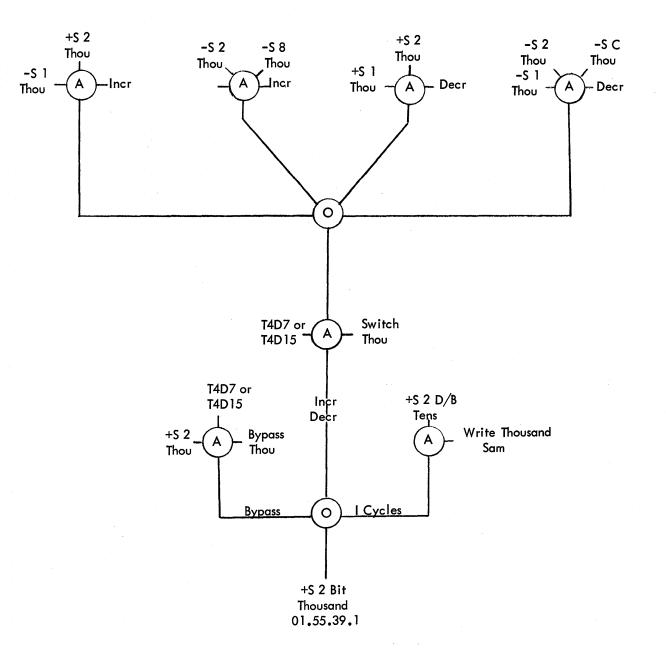

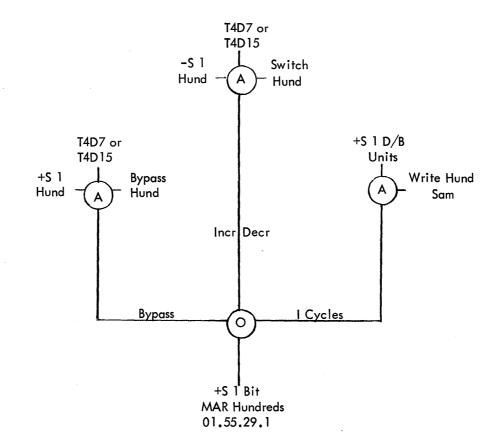

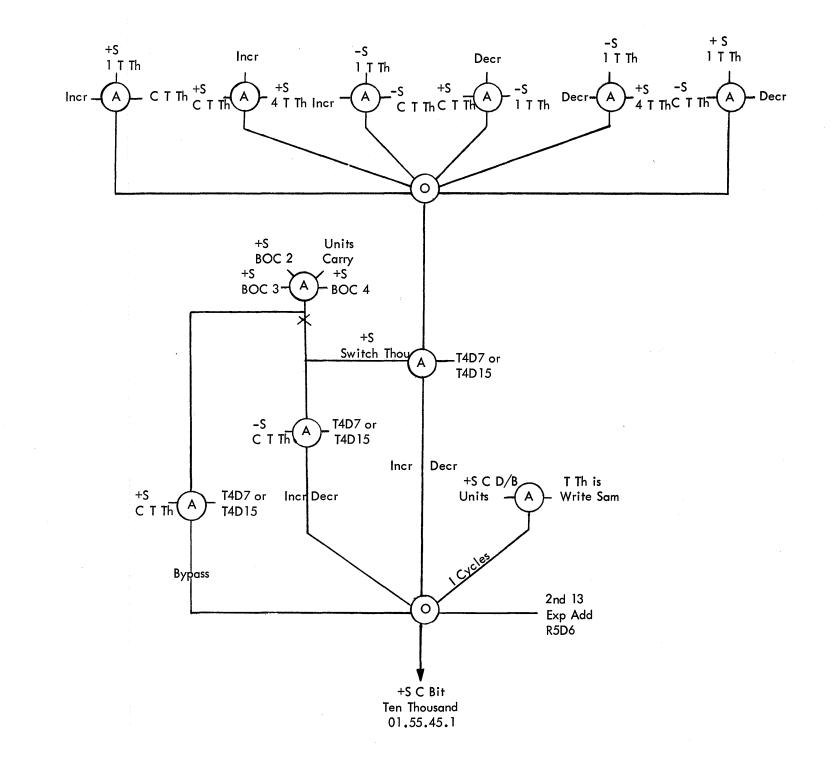

| MAR Function Charts | 5.4  |

These are drawn from F suffix logics but are satisfactory for general use on any suffix 1620.

Page 5 of the 1620 CE Reference Manual Supplement, Form #227-5620-1.

#### MAR CHECK SERVICE HINTS

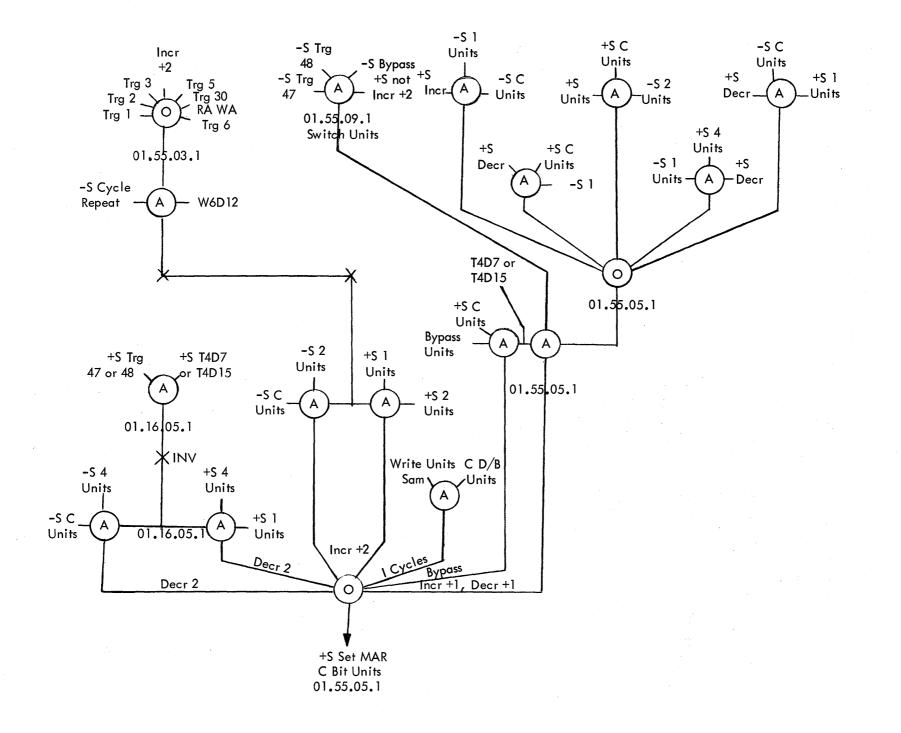

- When a MAR check occurs which cannot be analyzed to one or two SMS cards by using the Function Charts on pages 5.4 through 5.27. A scoping loop must be developed. The best scoping loop is a short program to determine what program would most effectively record several failures and develop a one or two instruction loop that duplicates your most common failure. Example: A failure which occurs when decrementing from 00000 to 19999 (20 K system) may be scoped on Dec (-1) loop "a".

- a. Dec (-1) Loop 25 00000 00000 (P & Q field 49 00000 may be altered to check any failing address)

The following events take place on this program:

- Op 25 1. | cycles -Inc +2 00000 to 00011

- 2. "E" cycle entry Turn Off Inc/Dec trigger (Dec)

- Trg. 26 Read & Write OR-1 Dec (00000 to 19999)

- 4. Trg. 27 Read & Write OR–2 Dec (00000 to 19999) Enter I Cycles

- Op 49 5. I cycles Inc +2 00011 to 00023

- "E" cycle entry Change status of 1nc/Dec trigger

- 7. Trg. 18 Read OR-2, Write IR-1 Bypassed branch back to Op 25.

To scope a decrement problem, sync scope on Trg. 26 or Trg. 27.

Note - During this loop, the failure will not appear in MAR, therefore you will not branch to an incorrect location.

- b. Inc (+1) Loop Set record mark at failing address 00000 31 xxxxx xxxxx 1. P & Q field rep 00012 49 00004 failing address.

Operation will be same as in Dec (-1) Loop inserted at any location.

- c. Inc (+2) Loop 00000 49 00000 I cycle will give you the best loop for Inc +2 problems.

- d. Dec (-2) Loop 26 00011 00006 48 The primary purpose of this program is to lock up in I cycles while exercising Dec -2 on Trgs. 47 and 48. If a failure occurs, the machine will halt.

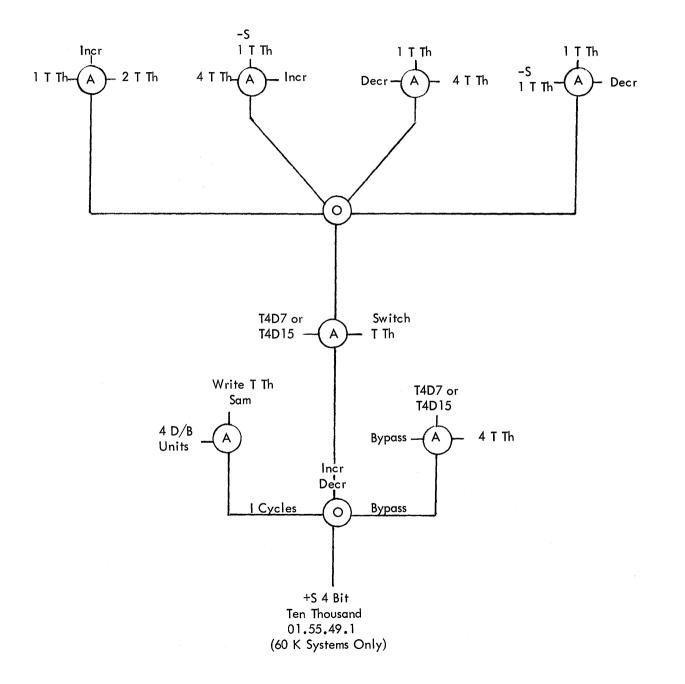

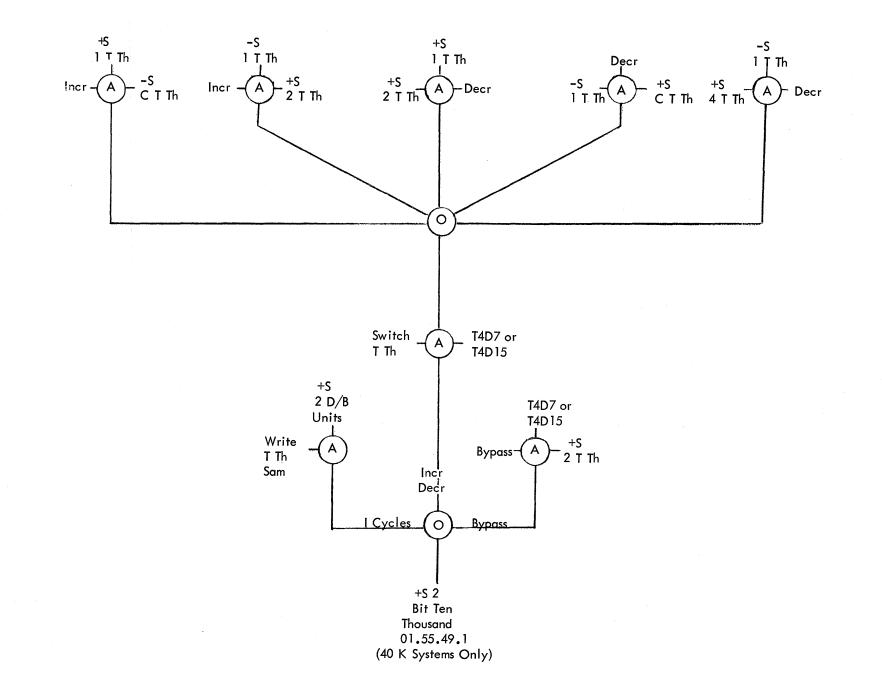

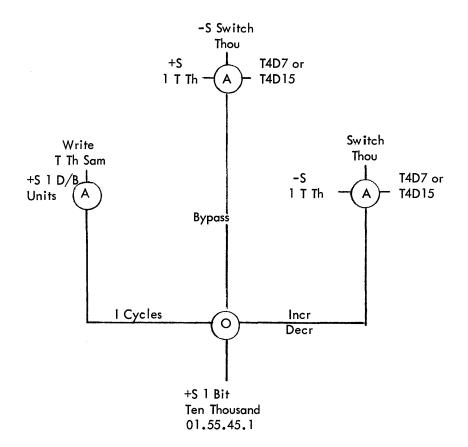

- On 1620 serial 10701 and higher, the rotary MAR selector switch can be used in connection with switches 7 and 8 to excercise the MAR, MARS, Incr-Decr circuits, MAR Read and Write drivers, etc. for any specific MAR register. See item 2.3.1

# POWER SUPPLY

|                 | Page |

|-----------------|------|

| Service Hints   | 6.2  |

| Condensed Logic | 6.3  |

#### SERVICE HINTS

# Power Supplies

If one or more circuit breakers trip to the Off position when power is applied, check their outputs for shorts to other voltage levels, as well as to ground.

Note: A good ohmmeter than can peg to zero resistance on the R x 1 scale must be used, because of the very low total resistance of the circuits. Look for dead shorts. The minimum resistance to be expected can be found by dividing the supply voltage by the maximum output current.

If trouble is in an individual power supply, some of the following points may be useful:

- On the logic diagrams, those parts enclosed within dotted or broken lines are located on the SMS cards or in the overvoltage device.

- 2) Series power supply transistors are those other than the ones on the power supply SMS cards.

- With the power supply removed, you can wire 110 VAC into TB1 pins 1 and 2. Output may not reach full value, but should be close and adjustable (remove overvoltage device or overvoltage SMS card).

- Visually inspect the unit for crimped wires or cable chafing, (unit may work in opened position, but not in closed).

- 5) If the voltage is too high and cannot be varied by the adjusting control, check for shorted series power supply transistors (located on the large power supply heat sink), or for a bad power supply SMS card.

- 6) If the output voltage is high and CB1 did not trip, replace the overvoltage protective device or overvoltage SMS card (if supply is so equipped).

- 7) An open diode in the rectifier circuit shows up as low voltage under load. This can be detected by feeling the diodes: they are quite warm when operating normally. If one is cold, it is probably open.

- 8) A shorted diode in the rectifier circuit will probably trip the circuit breaker in the primary of the input transformer. It may also trip the overcurrent CB due to overvoltage spikes on the output. With the overvoltage device removed, the spikes can be scoped at the output terminals.

- Shorted or open series power supply transistors can be detected by scoping or by checking the resistors in the emitter circuit for heat.

- Check voltages after the machine has been On for 15 minutes. Voltage may drift slightly between cold and warm states.

- Do not ground the meter or scope to the heat sink. Instead, ground to the holding screws at the corners of the unit.

- 12) If the system powers down immediately after a power up and the voltages of the various power supplies are correct, remove the overvoltage device from the power supplies one at a time and repeat the power up sequence. If power up is successful, the overvoltage device is faulty for that power supply.

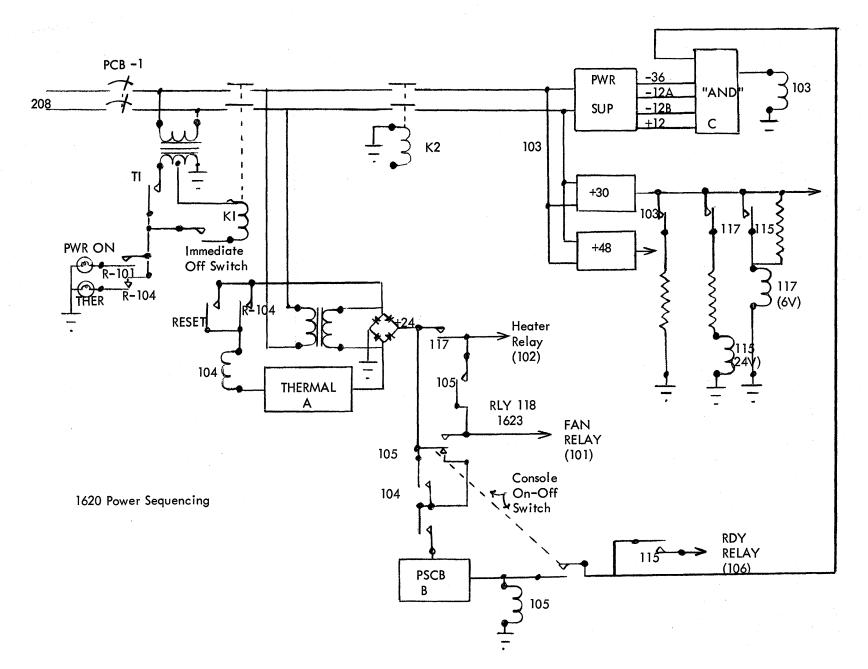

- 13) The charts on page 6.3 and 6.4 may be helpful in determining causes of power supply failures.

6.3

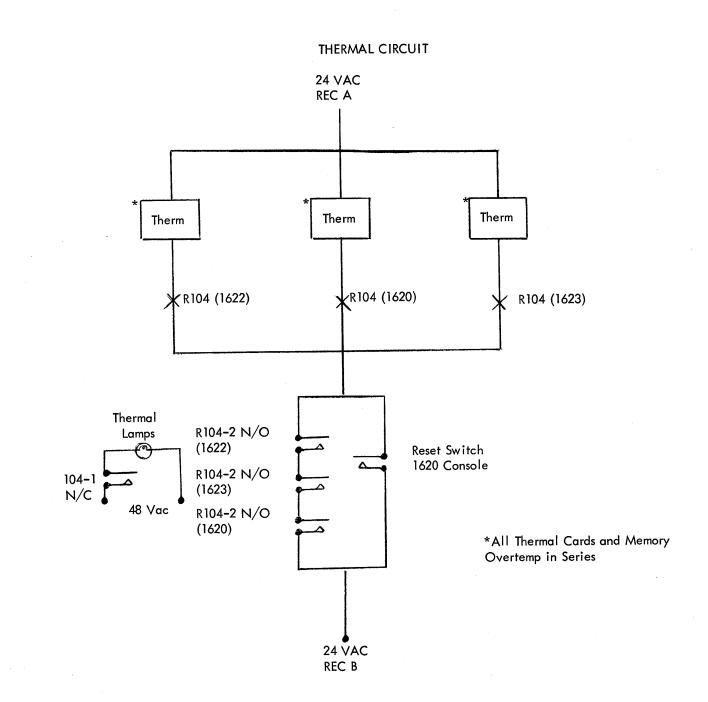

To detect which machine is causing thermal condition, hold down reset on 1620 and note which thermal lamp does not go out.

# FORTRAN

|                  |  | Page |

|------------------|--|------|

| Original Fortran |  | 7.2  |

| Format Fortran   |  | 7.6  |

#### FORTRAN DIAGNOSTIC PROCEDURE

# SECTION I

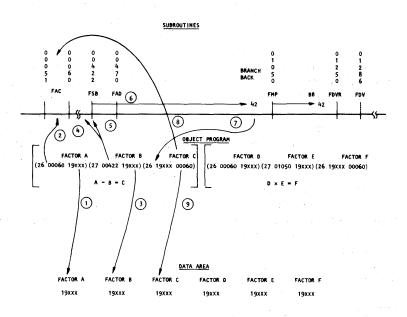

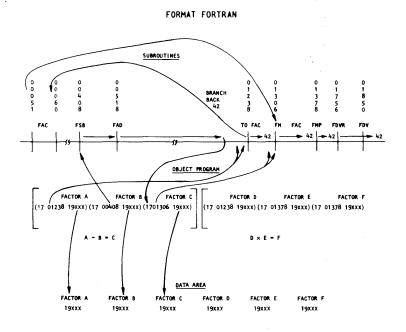

# Description

Fortran subroutines consist of a series of fixed programs in machine language which perform specific floating and fixed point arithmetic operations, such as; add, subtract, multiply, divide, logarithms, square root, trigometric functions, etc.