## HARDWARE BULLETIN

# **SERIES 200**

# TYPES 281-1E, 285-1E COMMUNICATION UNITS

SUBJECT:

Equipment Specifications for the Type 281-1E Communication Control and the Type 285-1E Communication Adapter Unit (for use with the IBM 1050 Remote Terminals and the Model 103A DATA-PHONE Data Sets).

SPECIAL INSTRUCTIONS:

This bulletin supersedes the Customer Information Bulletion 200-34 dated November 2, 1964. It will, in turn, be superseded by more detailed programming and operating procedures in forthcoming publications. The reference used in this text is the bulletin entitled <u>Equipment Specification for</u> the Type 286-1, -2 and -3 Multi-Channel <u>Communication Controls</u>, File No. 112. 0005.1100.00.03.

DATE: October 27, 1965

۰.

FILE NO. 112.0005.1100.0-061

31065 Printed in U.S.A.

## Copyright 1965

Questions and comments regarding this manual should be addressed to:

Honeywell Electronic Data Processing Information Services 60 Walnut Street Wellesley Hills, Massachusetts 02181

#### EQUIPMENT SPECIFICATIONS FOR THE TYPE 281-1E COMMUNICATION CONTROL AND THE TYPE 285-1E COMMUNICATION ADAPTER UNIT

#### I. GENERAL DESCRIPTION

The Honeywell Type 281-1E Communication Control and Type 285-1E Communication Adapter Unit provide the interconnection of a Series 200 central processor with IBM 1050 Remote Terminals by means of Bell 103A DATA-PHONE datasets on switched, voice-grade telephone lines or on TWX CE (TWX Customer Equipment) switched narrow-band lines. (Appendix I of this bulletin designates possible Honeywell/IBM 1050 operation via other common carrier facilities.)

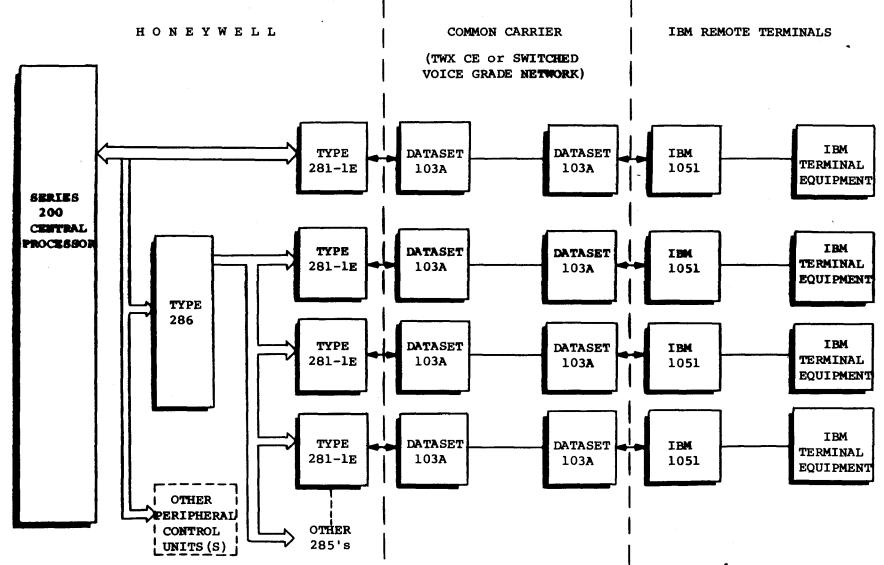

As illustrated in Figure 1, page 2, the Type 281-1E Communication Control is used to connect one voice-grade telephone line or TWX CE line to the Series 200 central processor, while the Type 285-1E Communication Adapter Unit is used in conjunction with a Type 286 Multi-Channel Communication Control to connect one voice-grade telephone line or one TWX Prime line when a maximum of 63 communication lines are to be connected to a central processor.

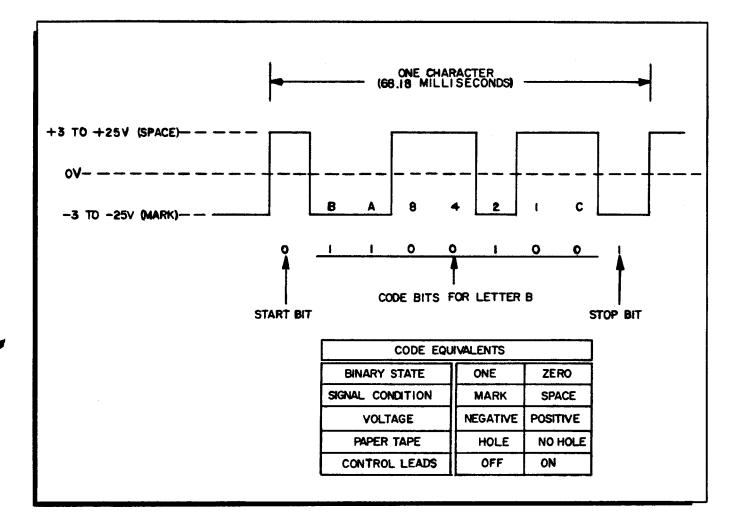

The communication line is characterized by start-stop, synchronous, serial transmission of seven-level (six-bit plus an odd-parity check bit) code in two-way, non-simultaneous, half-duplex mode.

One character comprises seven code bits plus stop and start bits. The duration of the complete character is 68.18 milliseconds, and the maximum line speed is 14.8 characters per second, or 134.98 baud (the baud rate being the reciprocal of the information bit duration expressed in seconds).

Equipment at the remote stations consists of an IBM 1051 Data Communication Control Unit in combination with one or more of the following IBM devices:

> 1052 Printer Keyboard (Selectric Model) 1053 Printer 1054 Paper Tape Reader which will reverse and read for error correction 1055 Paper Tape Punch 1056 Card Reader which will reread a card for error correction 1057 Card Punch 1058 Printing Card Punch

The standard Series 200 logic drawer contains one Type 281-1E Communication Control or eight Type 285-1E Communication Adapter Units.

Figure 1. Applications of Types 281-1E and 285-1E

**Lines in the second second**

N

#### II. INTERFACE WITH THE SERIES 200 CENTRAL PROCESSOR OR THE TYPE 286 MULTI-CHANNEL COMMUNICATION CONTROL

#### A. The Type 281-1E/Central Processor Interface

Standard peripheral interface logic for non-simultaneous input and output connects the Type 281-1E to the Series 200 standard peripheral bus.

#### B. The Types 285-1E/286 Interface

This interface is demonstrated below:

2 DATA LINES

•

۸

| 286>285               | Information out (serial by bit)                                   |

|-----------------------|-------------------------------------------------------------------|

| 286-285               | Information in (serial by bit)                                    |

| 6 ADDRESS LINES       |                                                                   |

| 286 285               | Select a particular Type 285                                      |

| 2 REQUEST LINES       |                                                                   |

| 286-285               | Type 285 requests a bit from Type 286                             |

| 286285                | Type 285 requests Type 286 to take a bit                          |

| 2 TIMING LINES        |                                                                   |

| 286>285               | Bit ready on Data-Out line                                        |

| 286>285               | Bit received on Data-In line                                      |

| 1 RESET LINE          |                                                                   |

| CP 286 285            | Reset by depressing INITIALIZE on central processor control panel |

| 1 SPECIAL STROBE LINE |                                                                   |

| 286> 285              | Control information to the Type 285                               |

All signals are at the voltage level of ground or +5 vdc, nominal.

#### III. INTERFACE WITH THE COMMON CARRIER

### A. <u>General</u>

The common carrier line termination is a Bell 103A DATA-PHONE dataset.

#### B. Interface Signals

The voltage-level signals of these communication controls are converted by the dataset into audio-frequency signals for transmission on the line.

The interface signals between the dataset and the communication controls are listed in Table I, below.

#### Table I. Interface with BELL 103A DATA-PHONE Dataset

| PIN<br>NUMBER | BELL<br>DESIGNATOR | DESCRIPTION                  | SIGNAL<br>SOURCE |

|---------------|--------------------|------------------------------|------------------|

| 1             | AA                 | Frame Ground                 |                  |

| 2             | BA                 | Transmitted Data             | 281-1E or 285-1E |

| 3             | BB                 | Received Data                | Dataset          |

| 5             | СВ                 | Clear To Send                | Dataset          |

| 6             | CC                 | Data Set Ready               | Dataset          |

| 7             | AB                 | Signal Ground                |                  |

| 8             | CF                 | Carrier Detector             | Dataset          |

| 20            | CD                 | Data Terminal Ready          | 281-1E or 285-1E |

| 4             |                    | Reserved for Tel.<br>Co. use |                  |

| 10            |                    | Reserved for Tel.<br>Co. use |                  |

| 22            |                    | Reserved for Tel.<br>Co. use |                  |

#### Figure 2. Data Signal at Control Unit/Dataset Interface

More detailed information on the 103A DATA-PHONE dataset interface may be found in the <u>AT&T</u> Data and Teletype Planning Engineer "Blue Book".

#### IV. REMOTE STATION EQUIPMENT AND CODE CHARACTERISTICS

#### A. <u>Remote Station Equipment</u>

An IBM remote terminal system consists of an IBM 1051 Control Unit and one or more of the other IBM devices listed below.

#### 1. The 1051 Control Unit

This unit is the center for all data flow. It contains data channels, control circuit code translator and power supply for the entire system. The unit transmits at the maximum rate of 14.8 characters per second (Section I, fourth paragraph).

#### 2. The 1052 Printer Keyboard

The 1052 Printer Keyboard is a modified IBM 26 Keyboard housed in the same cover as the printing mechanism of the IBM Selectric ("golf ball") Typewriter. It is connected by means of data channels in the control unit.

#### 3. The 1053 Printer

This is the printing mechanism from the IBM Selectric Typewriter.

#### 4. The 1054 Paper Tape Reader

The unit reads system code from either one-inch, eight-track paper tape or eight-track edge-punched documents. It can backspace over a record, then reread it.

#### 5. The 1055 Paper Tape Punch

This unit punches into one-inch, eight-track paper tapes or edge-punched documents.

#### 6. The 1056 Card Reader

The IBM 1056 Reader reads cards serially, translating the card code into system code. Cards are fed into the unit singly or - by means of a special feature - in packs of 300 cards each (maximum).

#### 7. The 1057/1058 Card Punch

This unit is an IBM 534 Card Punch or an IBM 536 Printing Card Punch with a translator which converts system code to card code. NOTE :

An annotated bibliography of "References **for** IBM 1050 System Available at Honeywell EDP Engineering" forms Appendix II of this bulletin.

B. Code and Message Characteristics

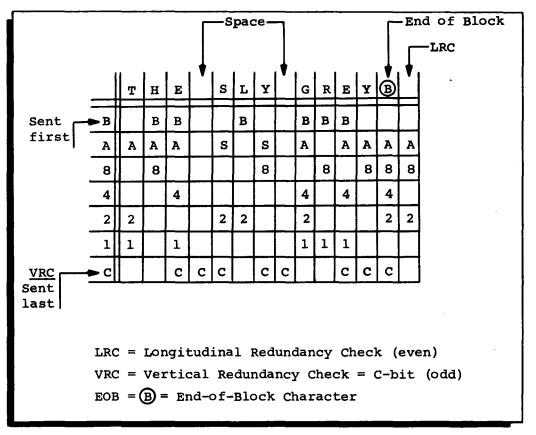

Messages are transmitted in variable-length blocks in the IBM six-bit BCD code plus a seventh - C - bit which provides a parity check on each character. Figure 3, below, illustrates a sample message. Table II, page 8, gives the appropriate IBM code.

#### Figure 3. IBM 1050 Block Transmission

Each message block is terminated by an end-of-block (EOB) character followed by a longitudinal redundancy check (LRC) character. This LRC character is formed by seven half-adders which count all transmitted or received code bits, including vertical redundancy check (VRC) C-bits and the bits of the EOB character. Because the C-bit is counted, the LRC character may have either odd or even parity. Over-all longitudinal parity of a block including the LRC character is even.

## Table II. IBM 1050 System Code

.

| CHARACTERS    |            | ODD PARITY<br>BCD CODE |     |            |          |            |     |

|---------------|------------|------------------------|-----|------------|----------|------------|-----|

|               | <b>_</b>   | ]                      | BCI | <u>p (</u> | 30       | )E         |     |

| NCRMAL SHIFT  | 8          | 4                      | 2   | 1          | в        |            | с   |

| 1             |            |                        | L   | 1          |          |            |     |

| 2             | _          |                        | 2   | _          |          |            |     |

| 3             |            |                        | 2   | 1          |          |            | С   |

| 4             |            | 4                      |     |            |          |            |     |

| 5             |            | 4                      |     | 1          |          |            | C   |

| 6             |            | 4                      | 2   |            |          |            | С   |

| 7             |            | 4                      | 2   | 1          |          |            |     |

| 8             | 8          |                        |     |            |          | _          | _   |

| 9             | 8          |                        |     | 1          |          |            | С   |

| 0             | 8          | _                      | 2   |            |          |            | C   |

| <u>A</u>      |            |                        |     | 1          | В        | A          |     |

| B             |            |                        | 2   |            | В        | A          |     |

| C             |            |                        | 2   | 1          | B        | A          | C   |

| D             |            | 4                      |     |            | В        | A          |     |

| É             |            | 4                      |     | 1          | B        | A          | С   |

| F             |            | 4                      | 2   |            | ₿        | A          | C   |

| G             |            | 4                      | 2   | 1          | B        | A          |     |

| H             | 8          |                        |     |            | В        | A          |     |

| I             | 8          |                        |     | 1          | В        | A          | C   |

| J             |            |                        |     | 1          | В        |            | C   |

| K             |            |                        | 2   |            | B        |            | Ċ   |

| L             |            |                        | 2   | 1          | В        |            |     |

| M             |            | 4                      | Ĩ   | ŕ          | B        |            | C   |

| N             |            | Ā                      | -   | 1          | B        |            | Ť   |

| 0             | 1.         |                        | 2   | ÷          | В        |            |     |

| P             |            | 4                      | 2   | 1          | В        |            | С   |

| Q             | 8          | 7                      | ĩ   | ÷          | B        |            | Č   |

| R             | 8          | Η                      | Н   | T          | B        |            | ۴   |

| S             | ╉          | М                      | 2   | H          | -        | Ā          | C   |

| Ť             |            |                        | 2   | 1          |          | Â          | ۲   |

| Ū             | +-         | 4                      | ĥ   | <u> </u>   | Η        | Â          | c   |

| V             |            | 4                      |     | 1          |          | Â          | ř   |

| W             |            | 4                      | 2   | <u> </u>   |          | Â          | ┢── |

| X             |            | 44                     | 2   | 1          |          | Â          | C   |

| <u>х</u><br>Ү | 8          | *                      | ř.  | H          |          | A          | č   |

| <u>z</u>      | 8          |                        |     | 1          |          | Ā          | ۲   |

| <u> </u>      |            | H                      | 2   |            | R        | A A        |     |

| \$            |            |                        | d N | 1          | B        | <b>.</b>   | C   |

|               | 8<br>8     | $\vdash$               | 2   | 1          | 4        | ٨          | C   |

| į.            | <b>⊢</b> ° | $\vdash$               | ŕ   | $\vdash$   | $\vdash$ | A          | ٣   |

|               |            |                        | -   | 1          |          | Å.         | C   |

| <u> </u>      | 8          | Η                      | 2   | 1          |          | <b>Å</b> . | ۲   |

| #&            | -l°        | $\vdash$               | 2   | $\vdash$   | -        | -          |     |

| <u> </u>      |            | Н                      |     | Н          | B        | A          | C   |

|               |            |                        |     |            | В        |            |     |

|            |                        |   |   |   |   |   | -   |

|------------|------------------------|---|---|---|---|---|-----|

| FUNCTIONS  | ODD PARITY<br>BCD CODE |   |   |   |   |   | Y · |

|            | 8                      | 4 | 2 | 1 | В | A | C   |

| BKSP       | 8                      | 4 | 2 |   | B |   | C   |

| EOT        | 8                      | 4 | 2 | 1 |   |   | C   |

| DELETE     | 8                      | 4 | 2 | 1 | В | A | C   |

| DOWN-SHIFT | 8                      | 4 | 2 |   | В | A |     |

| CR AND LF  | 8                      | 4 |   | 1 | B |   | C   |

| PREFIX     | 8                      | 4 | 2 | 1 |   | A |     |

| IDLE       | 8                      | 4 | 2 | 1 | B |   |     |

| RDR STOP   | 8                      | 4 |   | 1 |   |   |     |

| SPACE      |                        |   |   |   |   |   | C   |

| EOB        | 8                      | 4 | 2 |   | Γ | A | C   |

| UP-SHIFT   | 8                      | 4 | 2 |   |   |   |     |

| LF         | 8                      | 4 |   | 1 |   | A | C   |

| TAB        | 8                      | 4 |   | 1 | В | A |     |

| RESTORE    | 8                      | 4 |   |   | В |   |     |

| BYPASS     | 8                      | 4 |   |   | Γ | A |     |

| EQA        | 8                      |   | 2 | 1 | Γ | Γ |     |

#### V. OPERATIONAL CONTROLS

The Bell 103A DATA-PHONE dataset provides the operational controls for these communication systems.

#### A. Voice-Grade Line System

Calls are initiated by dialing the remote station with the dataset. Voice communication is thus established and the DATA push-button switches at each station are depressed so that data transfer is initiated.

#### B. TWX Prime System

Here calls are placed and data transfer is initiated by means of the dataset as in the voice-grade line system, but without establishment of voice communication.

#### VI. PROGRAMMING INFORMATION

#### A. <u>General</u>

The Type 281-1E handles data on either a single-character or message-block basis, whereas the Type 285-1E transmits via a Type 286 Multi-Channel Communication Control only in the single-character method. These factors - together with others mentioned in the following paragraphs of this section - cause some basic programming differences between the two systems.

#### B. Type 281-1E Programming

Its block transmission capabilities allow the Type 281-1E to handle more data with less manipulation and fewer program interruptions than single-character operation. Thus, block transmission is essential with very high-speed lines. Also, it is convenient with low-speed lines when communications share computer time with other processing.

Whichever the method of Type 281-1E transmission - single-character or message-block - only a record mark in the main memory data storage area terminates data transfer and releases the read/write channel involved.

#### NOTE

In the following discussion of the Type 281-1E, we assume the system includes the Program Interrupt capability (standard on all Series 200 central processors except Type 201). However, actual operation of this communications control

#### NOTE (Cont)

unit does not require such system capability; the Type 281-1E may be tested frequently by the program to ensure that a character is moved to or from its shift register during stop-bit time.

#### 1. <u>Initial Start</u>

The Type 281-1E is activated by depressing INITIALIZE on the central processor control panel during application of power to the system.

#### 2. <u>Receive</u>

Reception of the first character's start bit from the line switches this communication control to "busy". The first full character received by the 281-1E causes a program interrupt if the interrupt has been allowed by execution of the "Set Allow" Peripheral Control and Branch (PCB) instruction. The Allow switch remains set until specifically reset by the program or by activation of the INITIALIZE button.

In response to this interrupt, the program must issue a Peripheral Data Transfer (PDT) instruction to bring that character and succeeding ones into the assigned main memory area. Reception continues until a record mark is encountered in memory, then the read/write channel is released. If no more characters are received during the half-character period after the record mark is encountered, the 281-1E reverts to "not busy", and an interrupt requesting output occurs when Allow is set. This latter interrupt may be used to indicate the end of a received message. Thus, if characters are being received at the less than two-thirds of a line rate, two interrupts per character may occur.

When a received message occupies less than the assigned memory area, the record mark terminating data transfer is not encountered. In this case, a timer in the Type 281-1E is activated and - after 30 seconds - the assigned read/write channel is released, the Device Error switch is set, the control reverts to Not Busy. An interrupt requesting output now occurs if Allow is set.

#### 3. Transmit

Starting from the "initialized" condition, where no interrupts are allowed, an "Allow Interrupt" PCB instruction is given, followed by a PDT instruction to begin transmission of data from the central processor. Data is transferred from the assigned memory location until a record mark is encountered; then the read/write channel is released. Here, an interrupt occurs after the last character goes onto the line. A second PDT instruction is now given to continue data transmission or - if transmission is complete - a "Reset Interrupt" PCB instruction is sent to acknowledge receipt of the last interrupt and to indicate that no more data will be sent. An interrupt next occurs if data is received, or a "Reset Allow" PCB instruction can be given to prevent any interrupt from the Type 281-1E.

#### C. Line-Disconnect Capability

The three line-disconnect capabilities - any one of which may be supplied for the Type 281-1E or 285-1E - are described below:

- 1. No automatic line disconnect; manual disconnect only.

- 2. Automatic line disconnect only by program:

- a. <u>Type 281-1E</u>

Here line disconnect is accomplished by a PDT instruction having a control character C3 of octal 01. This instruction causes the communications control to send the single character specified by the A address, then to send a disconnect signal to the data set. When the disconnect signal has been sent, the control unit is disabled for five seconds.

b. <u>Type 285-1E</u>

Line disconnect is accomplished in the Type 285-lE by the "Special Strobe" PDT instruction. This causes the 285-lE to send a disconnect signal to the dataset. When the disconnect signal is sent, the 285-lE is disables for five seconds.

- 3. Automatic disconnect by means of the no-operation timer or program.

- a. <u>Type 281-1E</u>

During reception, with an input instruction stored in the Type 281-1E, a period of inactivity on the line of approximately thirty seconds causes release of the assigned read/write channel. Approximately thirty seconds after this release - if there is still no activity on the line the 281-1E sends a disconnect signal to the dataset and is itself disabled for five seconds.

When no input instruction is stored in the Type 281-1E, a 30-second period of inactivity causes the line to disconnect and the 281-1E is disabled for five seconds.

Line disconnect by program is accomplished as described in Section VI,C,2.

#### b. Type 285-1E

Because there is no instruction storage available in this unit, one 30-second period of inactivity on the line during transmission or reception, causes disconnection of the dataset and a five-second disablement of the 285-1E.

Line disconnect by program is accomplished as described in Section VI,C,2.

#### D. Peripheral Control and Branch (PCB) Instructions

1. General Format

| OP CODE | A ADDRESS | CONTROL CHARACTERS |                                                                                           |                       |  |  |  |

|---------|-----------|--------------------|-------------------------------------------------------------------------------------------|-----------------------|--|--|--|

|         |           | Cl                 | C2                                                                                        | C3                    |  |  |  |

| PCB     | A         | 6.54321<br>RWC     | $\begin{array}{c} 6 \\ \underline{5 \ 4 \ 3 \ 2 \ 1} \\ \hline \\ Peripheral \end{array}$ | <u>654321</u>         |  |  |  |

|         | Int       |                    | Address<br>ection<br>icator                                                               | Control<br>Parameters |  |  |  |

| A Address -                | This is the memory location to<br>which the program branches (in a<br>branching PCB instruction) if the<br>condition tested by the PCB instruc-<br>tion is true.                                                                                                                   |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interlock Bit -            | The interlock bit is immaterial.                                                                                                                                                                                                                                                   |

| Read/Write Channel (RWC) - | This selects the read/write channel<br>between main memory and the peri-<br>pheral device. Cl contains the num-<br>ber of the RWC being tested for<br>availability and must be set to zero<br>if no RWC is to be tested.<br>RWC1 = 01001 RWC3 = 01011<br>RWC2 = 01010 RWC1'= 01101 |

| Direction Indicator Bit -  | This bit is immaterial.                                                                                                                                                                                                                                                            |

| Peripheral Address -<br>(  | This is the logical address of the communication control on the peri-<br>pheral bus.                                                                                                                                                                                               |

Control Parameters (C3) - The C3 character of the PCB instruction specifies questions and control for the Type 281-1E. Additional control characters may be used if required. See Table III, page 15, for the description and coding of C3.

#### E. Peripheral Data Transfer (PDT) Instructions

1. General Format

| OP CODE | A ADDRESS | CONTROL CHARACTERS |                                      |               |  |  |

|---------|-----------|--------------------|--------------------------------------|---------------|--|--|

|         |           | Cl                 | C2                                   | С3            |  |  |

| PCB     | λ         | 6 5 4 3 2 1<br>RWC | 6 5 4 3 2 1<br>Peripheral<br>Address | <u>654321</u> |  |  |

|         | In        | terlock Dir        | ection                               | Control       |  |  |

|         |           | 0 =                | icator<br>Transmit<br>Receive        | Parameters    |  |  |

| A Address -                | This contains the address of the<br>main memory location to or from<br>which data is transferred by the<br>Type 281-1E. For Type 285-1E PDT<br>instruction programming, see the<br>reference bulletin Type 286-1, -2<br>and -3, Section VI,E. |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interlock Bit -            | If the interlock bit is a one,<br>memory access is not granted to<br>RWCl'. If this bit is a zero,<br>memory access is granted to RWCl'.                                                                                                      |

| Read/Write Channel (RWC) - | This selects the read/write channel between main memory and the peripheral device.                                                                                                                                                            |

|                            | RWC1 = 01001RWC3 = 01011RWC2 = 01010RWC1'= 01101                                                                                                                                                                                              |

| Direction Indicator -      | This indicator shows the direction of data transfer.                                                                                                                                                                                          |

| ،<br>13                    | <pre>1 = Move data from the Type 281-1E to memory location A, A+1, A+n, until a record mark is encountered.</pre>                                                                                                                             |

|                      | <pre>0 = Move data from memory locations A, A+1,A+n, to the Type 281-1E until a record mark is encountered.</pre> |

|----------------------|-------------------------------------------------------------------------------------------------------------------|

| Peripheral Address - | This is the logical address of the communication control on the peri-<br>pheral bus.                              |

| Parameters (C3) -    | See Table IV, below, for description<br>and coding of C3 for the Type 281-1E.                                     |

| Table I | v. | PDT | Control | Characte | r C3 |

|---------|----|-----|---------|----------|------|

|         |    |     |         |          |      |

| C3 (Octal) | Description                                                                                                                                                                                   |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50         | Present character being transferred<br>to the control unit has even parity.<br>This character is used when required<br>for the LRC character. See Section<br>VI,I, re: the LRC character.     |

| 01         | Causes the control unit to send the<br>single character specified by the<br>A Address, then send the disconnect<br>signal to the dataset. See Section<br>VI,C, re: the disconnect capability. |

Note 1. For the description on Type 285-1E programming, see the reference bulletin Type 286-1, -2 and -3, Section VI,E.

#### F. Record Marks and Character Location in Main Memory

1. Record Marks Required

#### a. The Type 281-1E Single-Character Method

When transmitting data by the single-character method, a record mark is placed in memory location A+1 to terminate a character. During data reception, a record mark in location A indicates character termination. At the termination of either reception or transmission, the RWC current location counter contains the address of A+1.

| Table | III. | PCB | Instructions | for | the | Type | 281 <b>-1</b> E |

|-------|------|-----|--------------|-----|-----|------|-----------------|

|       |      |     |              |     |     |      |                 |

|    | PCB             | Description                                                                                    | C3 (Octal) |

|----|-----------------|------------------------------------------------------------------------------------------------|------------|

| No | n-Branching     |                                                                                                |            |

| 1  | Set Allow       | Allows the Type 281-1E to interrupt the central processor.                                     | 71         |

| 2  | Reset Allow     | Prevents interrupts.                                                                           | 70         |

| 3  | Reset Interrupt | Resets present interrupt by resetting<br>Interrupt. Allows RNM instruction to<br>be effective. | 74         |

|    | Branching       |                                                                                                |            |

| 4  | Interrupt       | Are Allow and Interrupt both set? If yes, branch to A.                                         | 75         |

| 5  | Busy            | Is the Type 281-1E busy?<br>If yes, branch to A.                                               | lø         |

| 6  | Parity          | Did any character have even parity?<br>If yes, branch to A.                                    | 4ø         |

| 7  | Device Error    | Has an error other than parity occurred?<br>If yes, branch to A.                               | 5Ø         |

| 8  | Output Request  | Is the Type 281-1E requesting data for<br>transmission onto the line? If yes,<br>branch to A.  | 6Ø         |

| 9  | Input Request   | Is the Type 281-lE requesting that the<br>CP take received data? If yes, branch<br>to A.       | 61         |

Note 1. PCB instructions numbered 1, 2, 3, and 4 exist on the Type 201 Central Processor only if the latter has Program Interrupt capability. They are standard on all other Series 200 processors.

Note 2. For Type 285-1E PCB instructions, see the reference bulletin, Type 286-1, -2 and -3, Section VI,D.

#### b. Type 281-1E Block Method

During block-method transmission, a record mark is placed in memory location A+n (n being the number of characters in a block) to terminate the transmission of a group of characters. Upon reception of data in the block mode, the record mark is placed in memory location A+(n-1) to terminate the message and release the read/write channel. At termination of either data transmission or reception, the RWC current location counter contains the address of A+n.

#### c. Type 285-1E

No record marks are required in transmission or reception of data in the case of this unit.

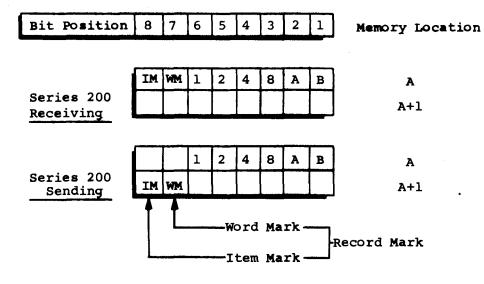

#### 2. Character in Main Memory (Type 281-1E, Single-Character Mode)

#### NOTE

When the central processor is receiving, the C-bit (parity) is checked in the Type 281-1E and does not pass into main memory. When the central processor is sending, the C-bit is supplied by the Type 281-1E.

For Type 285-1E main memory character programming, see the reference bulletin, <u>Type 286-1, -2 and -3</u>, Section VI.

## G. IBM 1050 Code in Series 200 Main Memory

Codes transmitted from IBM 1050 terminals or to them are shown Table V, below, as they appear in the Series 200 main memory. This table provides the basis for the Move and Translate (MAT) table.

|  | Table V. | Codes Fi | rom or | to | <b>IBM</b> 1050 | Terminals a | as | Placed | in | Series | 200 | Memory |

|--|----------|----------|--------|----|-----------------|-------------|----|--------|----|--------|-----|--------|

|--|----------|----------|--------|----|-----------------|-------------|----|--------|----|--------|-----|--------|

|                                      | IBM<br>HONEYWELL                                                                                                                                                                 | 1248AB<br>654321                                     |                                                                                                                                                                                 | IBM<br>HONEYWELL                                                                                                                             | 1248 <b>AB</b><br>654321                             |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| CHARACTER                            | OCTAL                                                                                                                                                                            | BINARY                                               | CHARACTER                                                                                                                                                                       | OCTAL                                                                                                                                        | BINARY                                               |

| 123456789ØABCDEFGHHJKLMNOPQRSTUVWXYZ | 40<br>20<br>60<br>10<br>50<br>30<br>70<br>44<br>24<br>33<br>63<br>13<br>53<br>73<br>77<br>41<br>21<br>11<br>51<br>71<br>55<br>52<br>62<br>12<br>52<br>62<br>12<br>52<br>72<br>64 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | ¢<br>¢<br>¢<br>¢<br>¢<br>ksp<br>ECT<br>DELETE<br>DOWN-<br>SHIFT<br>CR AND LF<br>PREFIX<br>IDLE<br>RDR STOP<br>SPACE<br>EOB<br>UP-SHIFT<br>LF<br>TAB<br>RESTORE<br>BYPASS<br>EOA | 67<br>65<br>66<br>02<br>42<br>64<br>03<br>01<br>35<br>74<br>77<br>37<br>55<br>76<br>75<br>54<br>00<br>36<br>34<br>56<br>57<br>15<br>16<br>64 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

The octal conversion of IBM 1050 characters is given in Table VI, below.

| SERIES 200<br>Octal | IBM<br>1050 | SERIES 200<br>Octal | IBM<br>1050 | SERIES 200<br>Octal | <b>IBM</b><br>1050 |

|---------------------|-------------|---------------------|-------------|---------------------|--------------------|

| 00                  | SPACE       | 30                  | 6           | 60                  | 3                  |

| 01                  | -           | 31                  | 0           | 61                  | L                  |

| 02                  | <b>@</b>    | 32                  | W           | 62                  | т                  |

| 03                  | &           | 33                  | F           | 63                  | С                  |

| 04                  | 8           | 34                  | UP-SHIFT    | 64 =                | # also EOA         |

| 05                  | Q           | 35                  | BSKP        | 65                  | \$                 |

| 06                  | Y           | 36                  | EOB         | 66                  | ,                  |

| 07                  | н           | 37                  | DOWN-SHIFT  | 67                  | •                  |

| 10                  | 4           | 40                  | 1           | 70                  | 7                  |

| 11                  | M           | 41                  | J           | 71                  | Р                  |

| 12                  | υ           | 42                  | 1           | 72                  | х                  |

| 13                  | D           | 43                  | A           | 73                  | G                  |

| 14                  | not used    | 44                  | 9           | 74                  | EOT                |

| 15                  | RESTORE     | 45                  | R           | 75                  | IDLE               |

| 16                  | BYPASS      | 46                  | Z           | 76                  | PREFIX             |

| 17                  | not used    | 47                  | I           | 77                  | DELETE             |

| 20                  | 2           | 50                  | 5           |                     |                    |

| 21                  | к           | 51                  | N           | I                   |                    |

| 22                  | S           | 52                  | v           |                     | x                  |

| 23                  | В           | 53                  | Е           |                     |                    |

| 24                  | ø           | 54                  | RDR STOP    |                     |                    |

| 25                  | not used    | 55                  | CR and LF   |                     |                    |

| 26                  | not used    | 56                  | LF          |                     |                    |

| 27                  | not used    | 57                  | TAB         |                     | •                  |

Table VI. Octal Conversion of IBM 1050 Characters

#### H. General Program Timing Considerations

The program must empty the Type 281-1E data buffer during the stop-bit time interval of 8.9 milliseconds. The program has a character time interval (68.18 milliseconds) to empty the data buffer of the Type 286 communication control associated with a Type 285-1E. If received data is not taken from the buffer of the Type 281-1E or Type 286 in the time specified, data is lost. In this event, the Type 281-1E Error switch is set or an error indication is stored in the Type 286.

In the case of the Type 286/Type 285-1E, if a character is not sent by the central processor during the specified time, the last character transmitted is again sent by the Type 286, unless the program has issued a "Transmit Last Character" PDT instruction. For further details on Type 286/285-1E programming, see the reference bulletin, Type 286-1, -2 and -3, Section VI.

#### I. The LRC Character in the Type 281-1E

Transmitted and received LRC characters are the half-add sum of the data and parity bits of the message. The six data bits of the LRC character are supplied and checked by the program.

#### 1. Transmission of the LRC Character

In transmission of the LRC character, the half-add sum of of the data bits is transferred to the Type 281-1E by means of a PDT instruction. If the message contains an odd number of characters, it requires no C3 control character. The message is transmitted with odd parity, which is correct. However, if the message contains an even number of characters, resulting in an even-parity LRC character, the PDT instruction to transmit the LRC character must have a C3 control character of octal 50.

#### 2. <u>Reception of the LRC Character</u>

The LRC character is received as is any other data character, except that its parity may be odd or even, as described in Section VI,I,l, above. When the received message has an even number of characters but the parity error test shows odd parity, the received LRC character is in error. If the test for parity is satisfactory, the C-bit of the LRC character is correct, but the other six bits must be checked by the program.

#### J. Line Control Function of the IBM 1050 System

Line control is used by a central facility to control operation of a communication line servicing several stations. It is not required when only two stations are on a line; in this configuration, either station can initiate transmission. A Line Control switch within the cover at the rear of the IBM 1050 Control Unit regulates the function.

#### 1. Operation With Line Control

The central facility puts all stations in the control mode by transmitting an End-of-Transmission (EOT) character identifying the next character as an address. The address character conditions the selected terminal or terminals to receive the component-selection character. After the component-selection character is transmitted, the selected terminal responds with a positive answer if it is ready to receive a message, or with an End-of-Address (EOA) character if it is ready to transmit a message. A negative answer indicates that the terminal is not ready. No answer indicates the power is off at the addressed terminal. If the addressed terminal is ready to receive a message, the the central facility precedes its message with an EOA character.

The EOA character terminates the control mode for all stations and places the selected station in the data mode.

The EOA character is not included in the LRC character.

#### 2. Operation Without Line Control

Without line control, either station initiates transmission by preceding a message with its prefix character, plus a component-recognition character. Both keyboard and reader are automatically recognized when an IBM 1050 terminal is reset.

The prefix and the component-recognition characters are included in the LRC character.

#### K. <u>Series 200/Type 281-1E Interface Signals</u>

#### 1. Single-Character Transmission

The following paragraphs describe interface signals between the Type 281-1E and its Series 200 central processor for single-character transmissions.

a. Device Busy

The busy signal, when active, indicates to the program that a PDT instruction can not be be accepted by the control unit.

Busy is active whenever the read/write channel associated with a PDT instruction addressed to the control unit is busy, or the control unit is transmitting data to the line or receiving data from it.

#### b. <u>Interrupt</u>

' The interrupt signal indicates to the program that the control unit is requesting service.

The Interrupt is set in response to the first "Set Allow" PCB instruction if the control unit is initialized. The

state of the output frame demand (OFD) or input frame demand (IFD) switch can not be guaranteed: either Input or Output Frame Demand can be present. If the IFD is present, a "Receive" PDT instruction is executed; if OFD is present, then the control unit is ready to accept a "Transmit" PDT instruction. Thereafter, the interrupt occurs whenever an OFD or IFD again becomes active.

The interrupt signal from the control unit is reset by one of the following: a PDT instruction to the control unit, a "Turn Off Interrupt" PCB instruction to the control unit, or initialization of the system.

c. Input Frame Demand (IFD) (Tested by a PCB instruction with C3 octal 61)

Input Frame Demand indicates to the program that a "Receive" PDT instruction is being requested by the control unit and must be issued to ensure proper operation.

The IFD signal becomes active when the control unit has assembled a character from the line and is ready to transfer it to the computer.

IFD is reset by the next PDT instruction to the control unit. If no PDT instruction is executed, the IFD signal is not reset.

d. Output Frame Demand (OFD) (Tested by a PCB instruction with C3 octal 60)

Output Frame Demand indicates to the program that the control unit is capable of accepting a "Transmit" PDT instruction.

The OFD signal is present when the control unit is not actively transmitting or receiving data or IFD is not active.

The OFD signal becomes active in the Transmit mode when the control unit is ready to transmit the next character. When receiving, OFD becomes active after one-half character time of inactivity on the line, provided that a PDT instruction has been executed to reset the IFD signal.

Output Frame Demand is reset by either a "Transmit" or a "Receive" PDT instruction or when the control unit senses a character on the line. e. <u>Timing Error</u> (Tested by a PCB instruction with C3 octal 50)

This signal indicates that a data character has been lost in the control unit.

In the Receive mode, the timing error is set if a "Receive" PDT instruction is not issued in response to the IFD signal before the beginning of the next character is sensed on the line.

The timing error is reset by the next PDT instruction to the control unit.

f. Parity Even (Tested by a PCB instruction with C3 octal 40)

The parity even signal is associated with Receive mode only.

This signal is set if a character is sensed with even parity at the end of the character assembly time (when the IFD becomes active).

The signal is reset by the next PDT instruction to the control unit.

g. Turn Off Interrupt (Via a PCB instruction with C3 octal 74)

The "Turn Off Interrupt" PCB instruction allows the Resume Normal Mode (RNM) instruction to be effective without executing a PDT instruction to the control unit.

h. <u>Reset Allow</u> (Via a PCB instruction with C3 octal)

The "Reset Allow" PCB instruction prevents all future interrupts from the control unit. The present interrupt is not reset by this PCB instruction. Turn Off Interrupt or a PDT instruction is required before an RNM instruction is effective.

#### 2. Single-Character Timing Considerations

#### a. <u>Set Allow</u>

The timing of the interrupt in response to the "Set Allow" PCB instruction is not predictable and should not be relied on for timing purposes.

b. <u>Received Data</u>

The data in response to a "Receive" PDT instruction is not guaranteed to be in main memory until 11 memory cycles after the end of the extraction of the instruction.

#### c. Transmitted Data

Data in main memory being transferred by a "Transmit" PDT instruction can not be changed until 14 main memory cycles are completed after the end of the extraction of the instruction.

#### NOTE

The read/write channel is busy until all data is transferred. The control unit is busy two main memory cycles longer than the read/write channel.

#### 3. <u>Message or Block Transmission</u>

The following paragraphs describe the interface signals for message or block transmission between the Type 281-1E Communication Control and its Series 200 central processor.

#### a. Input Frame Demand (IFD)

The IFD signal becomes active when the control unit has assembled the first character of the message or block from the line and is ready to transfer it to the central processor.

The IFD signal is reset by the next PDT instruction and is not made active again by a character on the line until after the assigned read/write channel is released. This release may occur because of a record mark sensed in memory or because of a line inactivity time-out extending over approximately 30 seconds.

#### b. Output Frame Demand (OFD)

The OFD signal becomes active during transmission when the control unit is ready to transmit the next message or block.

When receiving, the OFD becomes active after one-halfcharacter time of inactivity on the line, provided that the read/write channel has been released. If the read/ write channel has not been released, an inactivity period of approximately 30 seconds is required before the release is effective; at this time, OFD becomes active.

#### c. <u>Timing Error</u>

When receiving, the timing error is also set if the read/write channel is released by the control unit after the 30-second inactivity time out.

#### L. The Type 285-1E/Type 286 "Special Strobe" PDT Instruction

The "Special Strobe" PDT instruction can be used by the program with a line in the Receive mode, causing the control unit to send a disconnect signal to the dataset. (For Type 285-1E programming, see the reference bulletin Type 286-1, -2 and -3, Section VI.)

#### VII. OPTIONAL FEATURES

#### A. Parity Check

Though odd parity checking and generation is standard in the Type 281-1E, no parity checking or generation is performed by the standard Type 285-1E. The odd parity check in the Type 285-1E/Type 286/IBM 1050 application is accomplished by installation of Feature 086 in the Type 286 communication control, in conjunction with programming (see the reference bulletin, Type 286-1, -2 and -3, Section VI,I).

#### B. Long Check

#### 1. <u>The Type 281-1E</u>

Longitudinal check in the Type 281-1E/IBM 1050 application is accomplished by programming (Section VI,I).

#### 2. <u>The Type 285-1E</u>

Longitudinal checking in the Type 285-1E/Type 286/IBM 1050 application is accomplished by installation of Long Check Feature 087 in the Type 286 Communication Control or by programming (see the reference bulletin, <u>Type 286-1, -2 and -3</u>, Section VI,H).

#### APPENDIX I

#### HONEYWELL/IBM 1050 APPLICATIONS

| LINE                                                       | TERMINATION     | HONEYWELL CONTROL UNIT |

|------------------------------------------------------------|-----------------|------------------------|

| Voice-grade telephone                                      | 103A Data Set   | Type 281-1E or 285-1E  |

| Narrow-band line (i.e., TWX CE)                            | 103A Data Set   | Type 281-1E or 285-1E  |

| Voice-grade telephone, private line                        | 103F Data Set   | Type 281-1J or 285-1J  |

| Narrow-band line, private line<br>(Bell-proposed 150-Baud) | EIA Termination | Type 281-1J or 285-1J  |

| Narrow-band                                                | WU Type 11725   | Type 281-1K or 285-1K  |

1

(WU 180 Baud)

#### NOTE

The following two categories of IBM 1050 applications are in use but will not be connected to Honeywell systems.

- A Teletype-grade private line WU or Bell 75-baud service which is slower than the IBM 1050 capability.

- Customer-owned lines using IBMprovided Model at both the computer and IBM 1050 stations.

**A-1**

#### APPENDIX II

#### REFERENCES FOR IBM 1050 SYSTEM AVAILABLE

#### <u>AT</u>

#### HONEYWELL EDP ENGINEERING

1. <u>IBM Systems Reference Library</u> <u>IBM 1050 Data Communications System</u>

> Introduction, Operating Features, Controls and Indicator lights, Special Features. (28 pages, 18 illustrations)

2. Original Equipment Manufacturer Information IBM 1050 Data Communications System

> General Description for OEM use, covers changes as of July 1963. (27 pages, 17 figures)

3. IBM Customer Engineering Maintenance Manual 1050 Data Communications System

> General, Unpacking Instructions, Data Sets used, Cabling, Model 1 Home and Line Loop, Model II Line Only Data Channels, Switches, Control Keys, Codes, Correction Features, Line Control, Telegraph Grade Line Use, Customer and CE Aids, Diagnostic Tests, 1051 Latch and Trigger Descriptions. (124 pages, 20 illustrations)

4. <u>IBM Customer Engineer Manual Of Instructions</u> <u>I/O Printer (Modified IBM Selectric)</u>

> Printing, Character Selection, Operation-Control Mechanisms, Margin and Paper Control. (77 pages, 155 illustrations)

5. <u>IBM Customer Engineering Reference Manual</u> <u>IBM Selectric Universal I/O Keyboard Printer</u>

| а. | Adjustments | 44 pages | 224 illustrations             |

|----|-------------|----------|-------------------------------|

| b. | Removal     | 18 pages | 61 illustrations              |

| c. | Lubrication | 11 pages | 13 illustrations              |

|    |             |          | (73 pages, 298 illustrations) |

6. IBM Customer Engineering Instructions - Maintenance 1052 Keyboard Printer, 1053 Printer

> Introduction, Printing Controls and Indicator Lights, Adjustments. (34 pages, 50 illustrations)

#### 7. IBM Customer Engineering Instructions - References

1057 Card Punch, 1058 Printing Card Punch Introduction, Punch, Printing and Non-Printing, EDB and LRC Operations, Interlock, Patch Panel. (22 pages, 13 illustrations)

8. <u>IBM Customer Engineering Manual of Instruction</u> <u>1056 Card Reader</u>

> Functional Units, Reader Operation, Wiring Diagrams. (21 pages, 16 illustrations)

• •

۰. ۲

. .

| HONEYWELL | EDP  | TECHNICAL | . PUBLICATIONS |

|-----------|------|-----------|----------------|

| US        | ERS' | REMARKS   | FORM           |

TITLE: Types 281-1E, 285-1E Communication Units DATED: October 27, 1965 FILE NO: 112.0005.1100.0-061

ERRORS NOTED:

**Cut Along Line**

SUGGESTIONS FOR IMPROVEMENT:

ţ

Fold

.

Fold

Cut Ing Line

## BUSINESS REPLY MAIL

No postage stamp necessary if mailed in the United States POSTAGE WILL BE PAID BY

HONEYWELL ELECTRONIC DATA PROCESSING DIVISION

60 WALNUT STREET WELLESLEY HILLS, MASS. 02181

f

ATT'N: PUBLICATIONS AND WRITING SERVICES DEPARTMENT