DASH-CADAT Plus LOGIC SIMULATION, TIMING ANALYSIS AND TESTING, RIGHT AT YOUR PC.

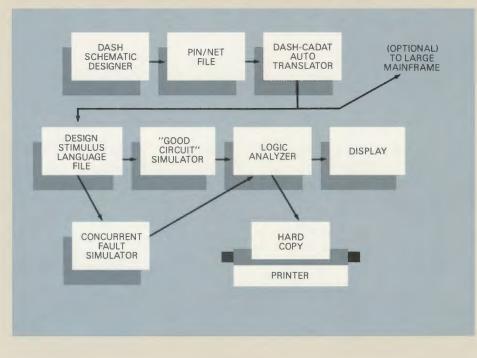

FutureNet<sup>®</sup> puts mainframe power on your desktop with logic simulation, timing verification and fault simulation software for the IBM<sup>®</sup> PC AT. With a logic analyzer waveform display and a new menu system, DASH<sup>™</sup>-CADAT Plus makes complex simulation easy. It not only speeds circuit development, it also helps you debug your designs and develop complete programs for 100% testability.

From a library of more than 100 primitives, DASH-CADAT Plus simulates application specific integrated circuit (ASIC) designs or printed circuit boards (PCBs). The optional CATS<sup>™</sup> hardware modeler accurately models LSI/VLSI components, so you can simulate both board operation and timing behavior.

DASH-CADAT Plus has much greater capacity and speed than other desktop logic simulators. With a 32-bit co-processor and up to 4 megabytes of memory, it can handle designs up to 30,000 gates with speed and computational power rivaling a mainframe, for a fraction of the cost.

## LOGIC SIMULATION IDENTIFIES ERRORS BEFORE PROTOTYPES ARE BUILT. Debug

your design using DASH-CADAT Plus as a software "breadboard". Logic simulation helps you identify and correct errors in your design before you go to the time and expense of building prototypes. This

not only speeds the process but lets you improve the quality of your design because it's easy to make circuit changes and see the results.

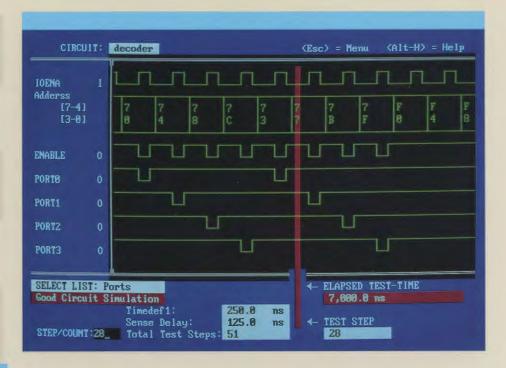

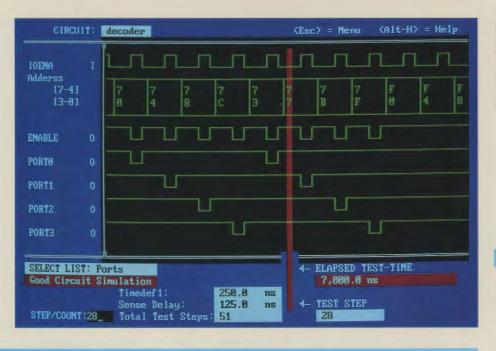

FAMILIAR LOGIC ANALYZER GRAPHICS FOR EASIER CIRCUIT ANALYSIS. We've wrapped our UNIX™-based DASH-CADAT Plus in a color graphics MS-DOS® shell so the display of simulation waveforms looks like a logic analyzer's. View simulated activity on any node in the circuit, at any point in time, down to 0.1 nanosecond resolution.

**THE EASIEST WAY TO ANALYZE TIMING.** Even when a design is logically correct, the timing may not be correct. Use the power of DASH-CADAT Plus to catch and correct these timing problems, even high-speed errors which are difficult to find with a prototype and a logic analyzer. The fan-

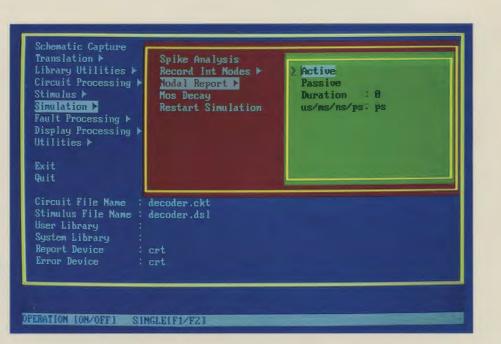

The menu hierarchy leads you step-by-step, presenting all your choices at every level.

out loading analysis accurately simulates the timing effects of pin loading and layout in ASICs.

## SAVE TIME BY SIMULATING ONLY WHAT YOU NEED.

You can set the level of simulation to focus on the information you need, whether you work top down or bottom up. You can begin simulation at the transistor level and move to the module, subsystem and product function levels. Or, reverse the process and work top down.

# FAULT SIMULATION HELPS YOU CREATE

**TESTABLE DESIGNS.** DASH-CADAT Plus gives you the tools to quickly develop an exhaustive test program that checks your entire circuit under every possible condition. When the highest possible portion of the circuit can be tested, you'll have total confidence in your design implementation.

DASH-CADAT Plus is integrated with a true concurrent functional fault simulator, DASH-FAULTSIM. The concurrent technique greatly speeds the fault simulation process and actually gains efficiency as circuit sizes increase, providing support for tomorrow's technologies.

WRITE COMPREHENSIVE TEST SETS MORE QUICKLY WITH OUR HIGH-LEVEL LANGUAGE. Our structured stimulus language makes it easy to write, change and maintain large sets of test vectors. Write your test programs in plain English. You won't be faced with endless columns of 1s and 0s.

FAULT GRADING: DESIGN TOWARDS 100% TESTA-BILITY. DASH-FAULTSIM can help you determine how thoroughly your set of vectors exercises the circuit. It can also help you alter an untestable design.

# IT'S EASY TO TAKE ADVAN-TAGE OF DASH-CADAT PLUS POWER.

## LOGIC SIMULATION BUILDS CONFIDENCE

**INTO YOUR DESIGN.** Build your design in functional segments, defining functions of less and less complexity until you reach the primitive level of logic. DASH-CADAT Plus supports you at every level. The behavioral modeling language gives you a way to represent major blocks in the circuit. The extensive primitive element library supports more than 90 classes of logic devices for the logical design stage. Finally, 20 different transistor models are provided to accurately represent the circuit at its most basic level.

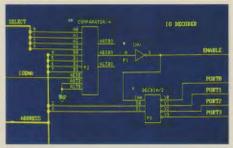

Designs created with the DASH Schematic Designer system are automatically converted to a CADAT<sup>™</sup> circuit description file using the pin list provided by DASH. This schematic depicts a simple Address Decoder of a peripheral device.

#### MENUS AND ON-LINE HELP FOR EASY ACCESS.

DASH-CADAT Plus integrates all simulation options into one familiar menu. An on-line set of help menus explains the effects of each option in detail. This MS-DOS shell insulates you from the complexities of UNIX, while letting you take advantage of its power.

#### FUNCTIONAL SPECIFICATION: DEFINING YOUR

**DESIGN.** Begin simulation by describing your target circuit specifications in our

By looking at the address bus lines on the waveform display, you can easily see whether the circuit is enabling the correct ports given the inputs. Select the sequence of the displayed signals and how you want them grouped.

comprehensive test program to ensure your design can be built and tested. Using the same circuit and stimulus files as DASH-CADAT Plus, DASH-FAULT-SIM automatically generates files containing all the information needed for fault simulation.

FULL CONCURRENT FAULT SIMULATION. DASH-FAULTSIM uses a mathematical, "stuck at 0/stuck at 1", fault model to determine how well your test program detects all possible faults in the circuit. It identifies the percentage of errors you can detect with your test program and identifies areas not covered.

The full concurrent functional simulation technique is the fastest fault simulation technique available today. It follows the chain reaction through the circuit caused by a particular fault. It runs faster because it narrows the area of analysis to just that portion of the circuit directly affected by each fault.

For large simulations, you may want to judge test program quality on a 5% sample, rather than the full run. DASH-FAULTSIM includes a statistical sampling feature that lets you grade a random cross section of possible faults. This gives you a quick feel for test program quality, highlighting areas of the test program that need improvement. When you get adequate coverage with the small sample, you can confidently run full fault simulation.

WRITING TEST VECTORS. DASH-CADAT Plus provides a high-level language with enough versatility to define simple or complex stimulus quickly and painlessly. When exercising a multiplier circuit, for example, you can define a stimulus macro that supplies the basic clocking and control sequence, accepting the numbers to be multiplied as arguments. Developing a comprehensive test program is as simple as calling the macro several times with different arguments.

high-level stimulus language. Specify the desired operating speed and the input/ output behavior of the new design before any logic circuitry is built. This becomes the basis of comparison as you refine your design, and ensures the final circuit will function as you originally intended. LOGIC VERIFICATION: DOES THE CIRCUIT BEHAVE **CORRECTLY?** As you implement individual blocks of the design, DASH-CADAT Plus presents results using familiar waveforms, so you can easily compare logic behavior to the original functional specifications. CADAT's true 21-state modeling, along with many MOS-related features, ensure accurate MOS and VLSI simulations.

min/max timing simulator allows you to account for differences in timing between devices. Use it to determine where your choice of components could be improved, or a potential timing problem exists. Find race and hazard conditions that may render a design unproducible. With all of this work done in software, you can build just one prototype after you're convinced the circuit functions the

TIMING ANALYSIS. DASH-CADAT Plus'

### **FAULT SIMULATION HELPS YOU BUILD**

way you intended.

**TESTABLE CIRCUITS.** Once your logic design has been verified with DASH-CADAT Plus, you'll want to develop a

FIVE ESSENTIAL FAULT REPORTS. During analysis, DASH-FAULTSIM identifies all failure modes: the universe of errors in the circuitry. It then generates a variety of reports to help you improve the test program.

1. COMPLETE FAULT LIST.

Lists each fault indicating its status.

**2. UNDETECTED FAULT LIST.** Lists only the undetected faults.

#### 3. STEP-BY-STEP LIST.

Sorts simulation results step-bystep to provide a fault detection histogram.

## 4. FAULT DICTIONARY.

Lists the "tell tale" signatures each fault produces at the circuit's primary outputs.

### **5. STATISTICAL FAULT TRACE LIST.**

The chain reaction of events caused by each fault. Use this important feature to identify hot spots, where the density of fault effects is high.

**SUPPORT AFTER THE SALE.** FutureNet not only gives you more performance for your dollar; we back it up with complete service after the sale. Our extensive 90-day warranty goes beyond a standard guarantee and covers:

- any defects in hardware workmanship or materials

- free telephone applications engineering support

- free software updates released during the warranty period.

## **FUTURENET'S FAMILY OF MAINFRAME PERFORMANCE CAE TOOLS FOR YOUR PC.**

DASH-CADAT Plus is just one of a complete family of tools giving you the CAE performance you need at a price you can afford. From DASH Schematic Designer to DASH-PCB, FutureNet software lets vou take even the most complex designs through schematic capture, simulation and printed circuit board layout, faster and easier. And right at your PC. Call us today and we'll help you get started.

Distributed by Hamilton/Avnet.

Authorized IBM Value-Added Dealer

Dista I/O Corporation 105/25 Willows Road N. E., PO, Box 97046, Redmond, WA 98073-9746, U.S. A. (206) 881-6444/Telex 15-2167 FutureNet 3310 Topanga Caryon Boulevard, Chatsworth, CA 91311-7528 (818) 700-0691/Telex 310-494-2691 Data I/O Canade 6725 Ariport Road, Suite 302, Mississauga, Onation L4V 155 (1416) 678-0761 Data I/O Canade 6725 Ariport Road, Suite 302, Mississauga, Onation L4V 155 (1416) 678-0761 Data I/O Carpande 7275 Ariport Road, Suite 302, Mississauga, Onation L4V 155 (1416) 678-0761 Data I/O Carpan Sumitomoseimei Highashishinbashi Bidg, 8F, 2-77, Highashi-Shinbashi, Minato-ku, Tokyo 105, Japan (03) 432-6991/Telex 2522685 DATAIO J Data I/O Japan Sumitomoseimei Highashishinbashi Bidg, 8F, 2-77, Highashi-Shinbashi, Minato-ku, Tokyo 105, Japan (03) 432-6991/Telex 2522685 DATAIO J

FutureNet is a registered trademark of FutureNet, a Data I/O Company. Induced is a registered trademark of International Business Machines Corporation.

IBM is a registered trademark of International Business Machines Corporation.

MS-DOS is a registered trademark of Microsoft Corporation.

IMDASH is a trademark of FutureNet, a Data I/O Company.

IMCATS and CADAT are trademarks of HHB Softron, Inc.

IMUNIX is a trademark of AT&T Technologies.

1136D/25K/686