## OCTAPORT I/O CARD

## INSTALLATION PROCEDURE

Applicable to installation of P/N: 801957 (8-Ports & clocks)

801976 (4-Ports & clocks)

801995 (8-Ports & no clocks)

802014 (4-Ports & no clocks)

## Address Select

System I/O Card Card Address Interrupt Jumper A7 A6 A5 A4

1st I/O card in system (801957 or

801976) BO

C1

OUT IN OUT OUT (A6 in foil on card)

2nd I/O card in system (801995 or

system (801995 or 802014)

CO C2 OUT OUT IN IN

## REFER TO PAGE 3 FOR 2ND I/O CARD CONVERSION, INSTALLATION PROCEDURE ADDENDUM

## 1-Port or 8-Port

4-Port versions 801976 or 802014 have jumpers at P4, P5, P6, and P7, also that 8-Port version 801957 or 801995 don't have these jumpers.

#### <u>Baud</u> <u>Rate</u>

The baud rate is set at manufacture at 9600 and is changed by cut and jumper. To change a baud rate, locate the hex pad corresponding to the number of the port in question (just above B10 through B13). Cut the trace just above the hex pad. Jumper the hex pad to the desired baud rate (either side of A7).

## 50 - 60HZ

In a 50HZ AC power system cut 50HZ trace between A2-A3. In a 60HZ system insure that the two 50HZ hex pads are connected.

## Card Placement

The Octaport card may be placed into any S100 bus card slot.

400512 Rev C 23 Feb 1982

# Octaport I/O Interface Card P/N 802337 - Octaport I/O Interface Cable Assembly P/N 804551

Connection from the Octaport card to the outside world is via one or more Interface Cards or Interface Cable Assemblies or a mixture of the two. Each will interface 4 ports, the Interface Card requiring 4 rear panel holes. The choice of Interface Card, Interface Cable Assembly, or mixture depends on the rear panel version level (number of holes available) and the number of ports being installed.

Both interfaces correct via a 20 pin ribbon cable to the Octaport Card. The first Ribbon Cable is plugged into J1 and the second into J2.

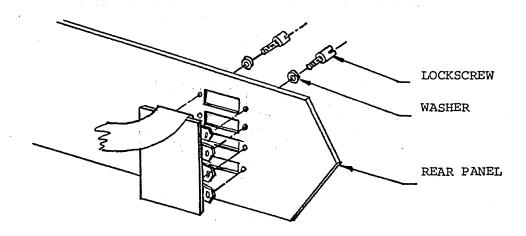

The Interface Card is installed through the rear panel and held in place with 8 speednuts and 8 lock screws. Install lockwasher over threaded portion of lockscrew before installing lockscrews. Nuts in package may be discarded.

## Octaport System Integration

System software for the Octaport card is self generating by answering the questions posed by the program DYNASYS.

#### ADDENDUM TO

## OCTAPORT I/O CARD

## INSTALLATION PROCEDURE

#### PURPOSE

The purpose of this addendum is to modify the Octaport I/O Card Installation procedure for installing the second card in a system. The second card does not require clocks or interrupt control logic. Since these cards are now being manufactured without IC sockets, it has not been clear how to disable the clocks and interrupt control.

#### ADDENDUM

#### ADD:

When installing the second Octaport in a system disable the clock and interrupt control logic by:

List per items 1 thru 8

- 1. Make these changes to Octaport (801957) or Quadraport (801976)

- 2. Cut (solder side) interrupt Jumper Cl.

- 3. Jumper (either side) interrupt Jumper C2.

- 4. Cut (component side) address Jumper A6

- 5. Jumper (either side) address Jumpers A4 and A5.

- 6. Cut trace (solder side) at IC Cl Pl.

- 7. Jumper (solder side) Cl Pl to Cl Pl6.

- 8. Cut trace running between C2 P3 and C2 P4 (component side).

400512

Rev C

sht. 3

SCHEMATIC

OCTAPORT INTERFACE ASSEMBLY

|                 |               | SIGNAL    | 20 PIN RIBBON   |

|-----------------|---------------|-----------|-----------------|

| PORT #/POSITION | PIN #         | NAME      | CONNECTOR PIN # |

| PORT 0 OR 4/    | 1             | *SFTY GND | -               |

| -               | 2             | RXD       | 1               |

| TOP CONNECTOR   | 3             | TXD       | 6               |

|                 | 4             | RTS 1     | 7               |

|                 | 5             | CTS 1     | <b>3</b>        |

|                 | 7             | GND       | 9, 10, 19, 20   |

| PORT 1 OR 5/    | 1             | *SFTY GND |                 |

| 2ND FROM        | 2             | RXD       | 2               |

| TOP CONNECTOR   | 3             | TXD       | 5<br>8          |

|                 | 4             | RTS'      | 8               |

|                 | 5             | CTS '     | 4               |

|                 | 7             | GND       | 9, 10, 19, 20   |

| PORT 2 OR 6/    | 1             | *SFTY GND | -               |

| 3RD FROM        | 2             | RXD       | 15              |

| TOP CONNECTOR   | 3             | TXD       | 18              |

|                 | <u>4</u><br>5 | RTS *     | 17              |

|                 | 5             | CTS 1     | 16              |

|                 | 7             | GND       | 9, 10, 19, 20   |

| PORT 3 OR 7/    | 1             | *SFTY GND |                 |

| BOTTOM          | 2             | RXD       | 12              |

| CONNECTOR       | 3             | TXD       | 13              |

|                 | 4             | RTS *     | 14              |

|                 | 5             | CTS '     | 11              |

|                 | 7             | GND       | 9, 10, 19, 20   |

<sup>\*</sup> Safety ground is an external connection to PC card.

## PRODUCT DESCRIPTION (Preliminary)

4/2/80 REV

## OCTAPORT CARD

The Octaport Card is an eight port serial Input-Output card with interrupt control and timers. The Octaport provides the I/O and control required in a multi-user system or whenever many serial RS232 level I/O channels are required.

#### DESCRIPTION

## I/O PORT

Mode:

Full duplex synchronous or asynchronous.

Levels:

(Data & Control): RS232.

Control:

2 each; 1 input and 1 output.

Baud Rate:

110 thru 9600 standard, 19,200 baud optional; jumper selectable.

Interrupt:

V13, V14, or V15 for any data available.

#### TIMERS

Number:

2

Interval:

1-sec and 1/60-sec.

Source:

S100 bus pin 55 RTC.

Indication:

Board status bit for each timer and V16 for either.

## BOARD STATUS

Ports:

2 each.

Function:

1 port to indicate data available for each I/O port.

1 port to indicate status of timers and reset timers.

## INTERRUPT CONTROLLER

Dedicated:\*

I/O receive data available dedicated to V13, V14, or

V15; jumper selectable. V16 dedicated to timers.

General:

V10, V11, V12, and V17 are generated in response to

appropriate S100 bus signal.

<sup>\*</sup>Dedicated interrupts may be jumpered to corresponding S100 pins if desired.

Product Description (Preliminary)

Octaport Card

## INTERFACE CARD P/N 802337

Interface is via an Interface Card containing four DB25 connectors connected to the Octaport through a 20-pin ribbon cable (two are required for eight ports).

## CARD CONFIGURATIONS

| P/N    | DESCRIPTION                                                                                                   | INSTALL FOR                                                                               |

|--------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 801957 | Octaport Card with eight I/O Ports, Timers, Status Ports, Interrupt Controller and two each Interface Cards.  | I/O expansion beyond the CPU I/O ports; includes Interrupt Controller and Timers.         |

| 801976 | Octaport Card with four I/O Ports, Timers, Status Ports, Interrupt Controller and One Interface Card.         | I/O expansion beyond the CPU I/O ports; includes Interrupt Controller and Timers.         |

| 801995 | Octaport Card with eight I/O<br>Ports and Data Available Status<br>Port only and two each Interface<br>Cards. | I/O expansion beyond one or<br>more Octaport Cards; no<br>Interrupt Controller or Timers. |

| 802014 | Octaport Card with four I/O Ports and Data Available Status Port only and one Interface Card.                 | I/O expansion beyond one or<br>more Octaport Cards; no<br>Interrupt Controller or Timers. |

#### ADDRESSING

The Octaport Card occupies an address space of 16 conventional ports, yet 18 ports are required to implement the desired functions. The extra ports are obtained by taking advantage of the Z80 I/O instructions which control the upper eight addresses during input-output.

For instance, LD A,2 IN OBOH

will input from port BO (low order address of BO) with O2 on the high order address lines.

The Octaport decodes address bits A8 and A9 as well as A7 thru A0. A0, 1 or 2 on the high order address bits is recognized as follows:

| Address Bits A9-A8 | Function                            |  |  |

|--------------------|-------------------------------------|--|--|

| 0                  | USART Data-Control                  |  |  |

| 1                  | USART Receive Data Available Status |  |  |

| 2                  | Timers Status and Reset             |  |  |

Product Description (Preliminary)

Octaport Card

The card, as manufactured, has a base address of BOH. This can be cut and jumper changed to any of OOH, 10H, 20H, throu FOH as desired. The Dynabyte master plan calls for the first card in a system to be based at BOH; the second at COH.

The table that follows displays the address space occupied by an Octaport based at BOH. The table may be extended to any base by substituting the desired base for B.

| Address                     |                                               |

|-----------------------------|-----------------------------------------------|

| <u>High Order-Low Order</u> | Description                                   |

|                             | TWO DOWN DOWN DAME                            |

| 0-во                        | IN/OUTPUT PORT O USART DATA                   |

| O-B1                        | IN/OUTPUT PORT O STATUS/COMMAND               |

| 0-В2                        | IN/OUTPUT PORT 1 USART DATA                   |

| 0-в3                        | IN/OUTPUT PORT 1 STATUS/COMMAND               |

| 0 <b>-</b> B4               | IN/OUTPUT PORT 2 USART DATA                   |

| 0 <b>-</b> B5               | IN/OUTPUT PORT 2 STATUS/COMMAND               |

| 0 <b>–</b> B6               | IN/OUTPUT PORT 3 USART DATA                   |

| O-B7                        | IN/OUTPUT PORT 3 STATUS/COMMAND               |

| 0 <b>–</b> B8               | IN/OUTPUT PORT 4 USART DATA                   |

| O-B9                        | IN/OUTPUT PORT 4 STATUS/COMMAND               |

| <b>O-BA</b>                 | IN/OUTPUT PORT 5 USART DATA                   |

| О-ВВ                        | IN/OUTPUT PORT 5 STATUS/COMMAND               |

| O-BC                        | IN/OUTPUT PORT 6 USART DATA                   |

| O-BD                        | IN/OUTPUT PORT 6 STATUS/COMMAND               |

| O-BE                        | IN/OUTPUT PORT 7 USART DATA                   |

| O-BF                        | IN/OUTPUT PORT 7 STATUS/COMMAND               |

| 1-Bx                        | INPUT - Receive Data Available Status         |

|                             | Bit n $(n=0-7) = 1$ for Port n data available |

|                             | OUTPUT - Not defined.                         |

|                             | Outrot - Not delined.                         |

| 2-Bx                        | INPUT - Bit 7: 1/60 sec timer ready.          |

|                             | (Active High) Bit 6: 1 sec timer ready.       |

|                             | Bit 5-0: Not defined                          |

## NOTE: (1) x = any hex digit.

- (2) USART is Intel 8251. (See Intel Manual for Status and Command description.)

- \*(3) Timers run continuously; only ready bits are set and reset.

Product Description (Preliminary)

Octaport Card

## INTERRUPTS

The following Interrupts have been defined in a multi-user MP/M environment.

| Function     | Interrupt | Call Address | S100 Bus Pin |

|--------------|-----------|--------------|--------------|

| System       | RST 0     | ОН           | 4            |

| *Hard Disk   | RST 1     | 8н           | 5            |

| *Floppy Disk | RST 2     | 10H          | 6            |

| I/O Card 1   | RST 3     | 18Н          | 7            |

| I/0 Card 2   | RST 4     | 20H          | <b>8</b>     |

| **           | RST 5     | 28Н          | 9            |

| Clocks       | RST 6     | 30н          | 10           |

| System       | RST 7     | 38н          | 11           |

<sup>\*</sup> Hard and Floppy Disk interrupts may be combined on RST2 for some systems with RST1 reserved for special applications.

<sup>\*\*</sup> RST5 is not defined but reserved.