### DIGITAL SYSTEMS

### FLOPPY DISK SYSTEM REFERENCE MATERIAL

List of Attachments FDC-1 Interface Manual Shugart Disk Drive Manual ALTAIR-Compatible Bus Interface 8080 Software Information Warranty Information

DIGITAL SYSTEMS is currently marketing only the FDC-1 floppy disk controller board and Shugart disk drives. We are providing documentation on the interface we have used to interface the FDC-1 to an Altair compatible machine. We have used the resulting system to run CP/M, a sophisticated disk operating system.

While the bus interface to the FDC-1 is a relatively simple cicuit, the total disk system is complex. Debugging a hand wired system may be beyond the capabilities of an inexperienced TTL designer.

DIGITAL SYSTEMS will produce a completely assembled and tested interface to the FDC-1 if there is sufficient demand. We estimate the cost of the board to be \$30 with availability October 1. Let us know if you would be interested in this board as we believe this would be the best way for most users to bring up a disk system.

DIGITAL SYSTEMS MODEL FDC-I FLOPPY DISK CONTROLLER INTERFACE MANUAL

)

DIGITAL SYSTEMS 754 Carmel Ave Livermore, California 94550

(415) 443-4078

This manual is PROPRIETARY INFORMATION of DIGITAL SYSTEMS and is not to be used or distributed without the express permission of DIGITAL SYSTEMS.

Copyright C 1976 DIGITAL SYSTEMS

DIGITAL SYSTEMS FDC-I Interface Manual

Ale and the second loops and the second loops and the second loop of the second and the second loop of the second

a boliga esta a la seconda en la seconda La seconda en la seconda en

### · 我们的问题。 "我们们我

·

.

다. (1999년 - 1997년 1997년 - 국가 (1997년 - 1997년 - 1998년 - 1999년 - 1997년 - 1997년 - 1997년 - 1997년 - 1997년 - 1997년 - 1998년 - 1997년 - 1997년

and the second second

#### INTRODUCTION

This manual provides the information needed to utilize the DIGITAL SYSTEMS Model FDC-1 floppy disk controller within a data system. It is intended as a reference for technical personnel engaged is the specification, design, and implementation of a digital system with flexible disk drive storage devices. Both hardware and software requirements for integrating the FDC-1 with memories, processors, disk drives, and system wide controlling devices are described.

Details of the interior of the FDC-I do not appear here; these are found in the FDC-I Technical Description manual. Aspects of the controller detailed here include specification and timing for all exterior interface signals, physical layout, power requirements, and required command sequences generally supplied under program control from a host processor system to the disk controller.

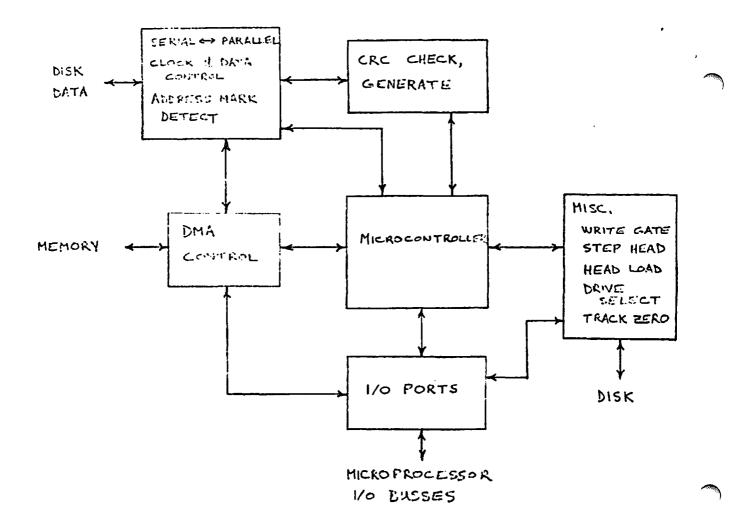

A block diagram of the FDC appears in Figure 1.

The FDC-I is a flexible disk drive controller for up to four selectable drives. The FDC-I uses a high speed microprocessor based design providing reliable and flexible functions implemented in read-only memory logic. Features of the FDC-I include drive write protect, automatic CRC generation and check, full IBM 3740 compatible soft sector formatting, automatic track seek verify, and head retraction after eight idle disk rotations to assure long diskette life. An automatic bootstrap load from Track Ø, Sector I can be done at system initialization without system processor intervention.

The FDC-I is fully TTL implemented and compatible. An adaptible, simple interface to mini and microprocessor systems is provided with 8 bit parallel input and output busses for control information. A DMA interface moves data directly in or out of memory once a transfer is initiated.

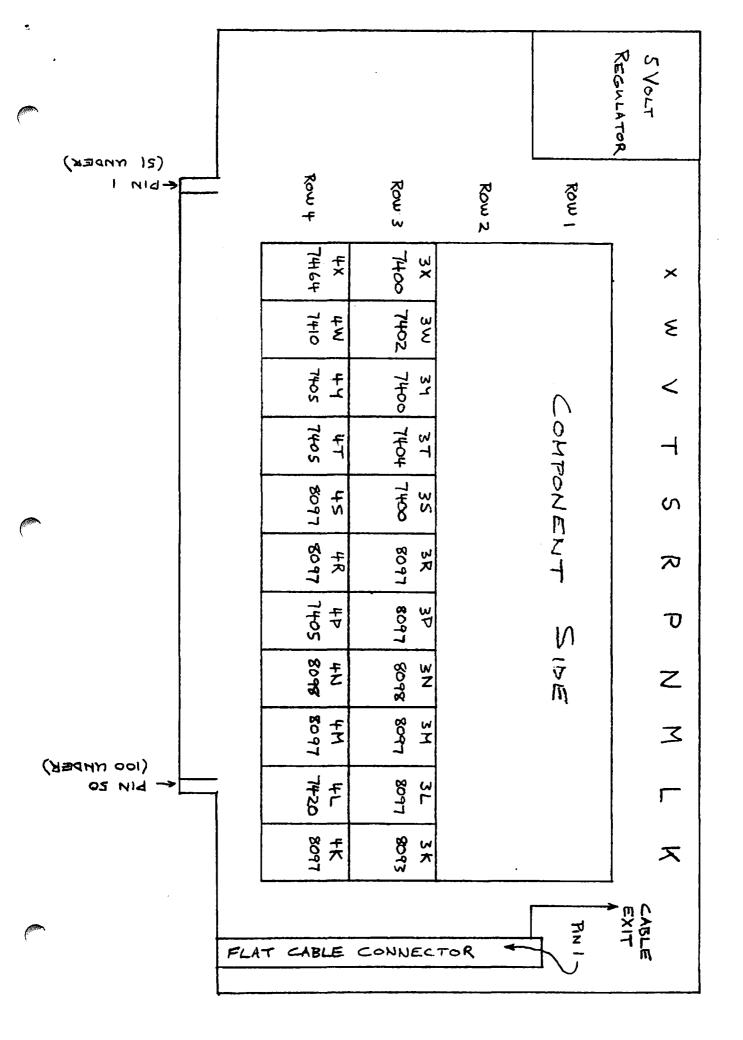

Packaging is on a single  $|0" \times |2"$  PC board with system interface via standard edge connectors and flat cable to the flexible disk drives.

Figure I. FDC-I Block Diagram.

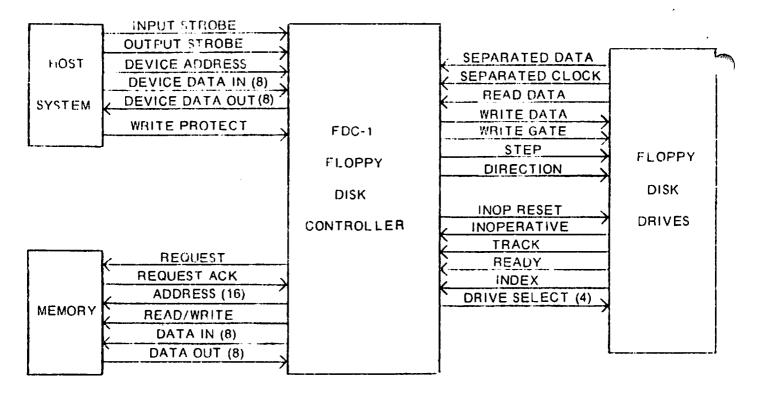

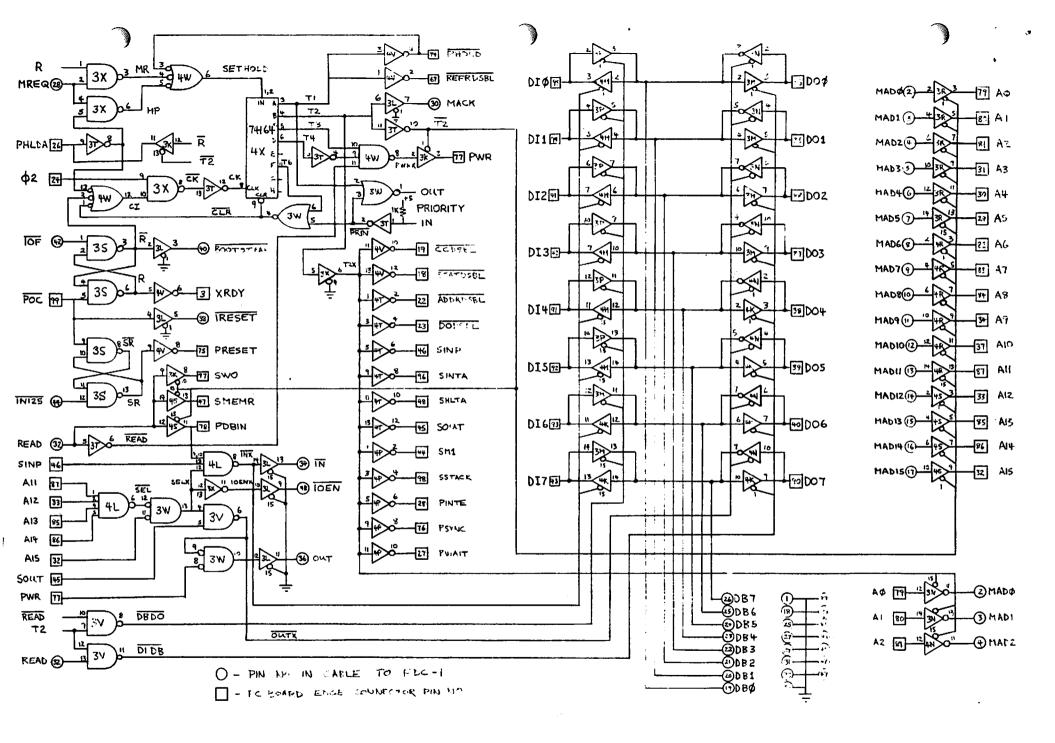

HARDWARE INTERFACE TO THE FDC-I

A diagram of the FDC external signals appears in Figure 2. The signals can be divided into three distinct interfaces; the device, direct memory interface (DMA), and disk interfaces. The device interface implements command and status information between host system control hardware (i.e. processor and processor support logic) and the FDC. The DMA interface exchanges data with up to 64 Kbytes of random access memory. The disk interface connects the FDC to a chain of flexible disk drives handling IBM format compatible diskette media. Initialization and power supply lines complete the FDC requirements.

A detailed description for each interface follows. Reference is made to the appendices containing backplane signal pinouts (JI and J2), connector pinouts for the disk interface (J3), and the following table summarizing the mnemonic name, active state, and description fc all interface signals. SYSTEM BUSSES

Following is a summary of the busses and controls for the FDC, their names, active state, and description. All busses except MAD are 8 bits wide, bit 7 is the most significant bit, bit 0 the LSB. Index x varies from 0 to 7 unless otherwise noted.

| Name        | Active | Description                                                                   |

|-------------|--------|-------------------------------------------------------------------------------|

| DINX        | hi     | device input bus<br>data to host via backplane                                |

| -DOUTx      | low    | device output bus<br>data from host via backplane                             |

| MDINX       | hi     | memory data in<br>data to memory via backplane                                |

| MDOUTX      | hi     | memory data out<br>data from memory via backplane                             |

| -DEVx       | low    | device address to devices                                                     |

| MADx        | hi     | x ranges from Ø to 15<br>16 bit memory address bus<br>to memory via backplane |

| REQ         | hi     | single line raised by FDC<br>to request a memory cycle                        |

| АСК         | hi     | single line raised by<br>host memory system to grant<br>a memory cycle        |

| -WRITE      | low    | lowered after cycle is granted<br>if FDC wishes to write to memory            |

| <b>-</b> IN | low    | input device strobe                                                           |

| OUT         | high   | output device strobe                                                          |

| -IRESET     | low    | system restart signal                                                         |

| -IOF        | low    | I/O finished by FDC                                                           |

| -BOOTSTRAP  | low    | forces FDC to execute bootstap<br>and return -IOF                             |

| DZPROT      | high   | inhibit writing on disk Ø                                                     |

All bus levels are TTL standard, with low level signals below 0.4 VDC and high level signals above 2.5 VDC. All signals listed above except REQ and the last six signals in the table are implemented as high impedance (TRI-STATE) drivers which may be shared by other host system devices using appropriate strobing.

Figure 2. FDC-I External Signals.

DEVICE INTERFACE

Interaction between the host processor or controlling hardware and the FDC is implemented by the device interface. The controller is idle until an eight bit address appears on the device address bus (-DEVi) and one of two strobes (OUT or -IN) appears simultaneously with the device address. Strobes cause decoding logic to sense the state of the -DEVi bus and, if it is presenting one of the set of addresses given below with the appropriate strobe, a set of actions occurs. With a device address and an OUT strobe, data bits present on the device output bus (-DOUTi) will affect the FDC as indicated below. Device addresses decoded with -IN will cause the FDC to drive status bits onto the device input bus (DINi) for use by the host system. All signals must be stable at their active level for a minimum of 200 nanoseconds.

Note the locations of the device address bus (-DEVi), device input bus (DINi), device output bus (-DOUTi), and strobes OUT and -IN on the table in Appendix I.

Device 127D (177Q, 7F hex) is the status input device when strobed by -IN and the command output device when strobed by OUT. The status device delivers eight bits of disk system status to the device input bus bits 0 through 7. These bits will be stable 100 nanoseconds after the device address is available and remain stable for as long as the address and strobe are stable.

The status bits are:

- Bit 0: file inoperative an error signal from the disk indicating invalid writing sequencing

- I: step ready indicates IØ milliseconds elapsed since the last step command was executed and the disk is able to execute further commands

- 2: track zero indicates that the read/write head on the selected disk is positioned at the outermost track

- 3: I/O finish indicates that the FDC has completed processing (or aborted because of an error condition) the previous read or write command

- 4: track error indicates the byte read from memory at the initial DMA address did not match the track byte of an ID field actually read from the disk. The current command is aborted.

- 5: ID CRC error a CRC error was encountered in the ID field of the requested track/sector. Kead commands will complete but Write commands are aborted.

- 6: Data CRC error indicates a CRC error in the data fields during a Read command

- 7: Head Unloaded indicates at least eight revolutions of the disk have occurred since the last Read or Write command, and the hardware has unloaded the head of the selected disk. If a software error results in a request for a sector number greater than 26D, this bit and a zero bit 3 (I/O never finishes) will indicate the error as the FDC will search forever for the requested illegal sector.

When device address [27D appears with the OUT strobe, the bits on the device output bus (-DOUTi) are interpreted by the FDC as command bits. The command register in the FDC is loaded using OUT as a strobe to the register.

The command bits are:

- Bit 0: file inoperative reset required response to the file inoperative status bit

- I: step commands the selected drive to move in the direction selected by bit 2.

- 2: direction directs the disk drive to step towards Track 77 (innermost) when active (-DOUT2 low) and towards Track 00 when inactive (-DOUT2 high).

- 3: enable enables loading of drive select bits 4 and 5

- 4: drive select low order of two decoded select bits

- 5: drive select high order of two decoded select bits. Bits 4 and 5 are latched and decoded to select one of four drives as the recipient of all commands directed to the FDC system. If bit 3 (enable) is inactive, bits 4 and 5 are ignored in a command word and the previously selected drive is used.

- 6: Read initiate reading. The address of the memory buffer has been preloaded into the FDC memory address register (see below) and the host system has positioned the selected disk at the desired track. The Read command causes the first byte of the buffer to be fetched and compared to the track ID read from the drive. A mismatch causes a Track error. The second byte of the buffer is fetched and specifies a Sector number and the FDC reads sector ID fields until a match occurs. The third buffer byte is loaded by the FDC with the address mark for the data field read, then 128 bytes are transferred from the drive to memory.

- 7: Write initiates a write operation. Track and sector are identified as for a Read and a Track error aborts the operation. After positioning, using track and sector bytes from the memory buffer, the third byte is written as the address mark for the data field and the next 128 bytes transferred from memory to the drive.

Note that all bits, except disk select bits, are reset on the FDC at the completion or abort of a Read or Write command. All bits are cleared when the controller is reset (-IRESET, below).

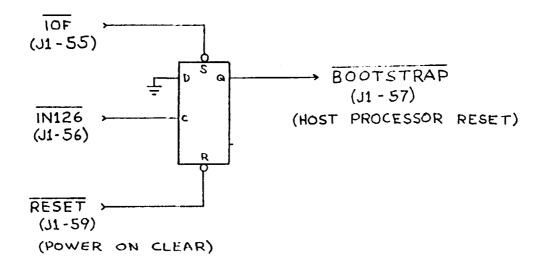

Device address 126D (176Q, 7E hex) is decoded and made available to the host system on JI-56 as signal -IN126 whenever it is issued with the -IN strobe. It is suggested that the host system use the signal as a software issued restart command by implementing the logic equivalent of Figure 3. A further explanation of Figure 3 appears in the section on initializing the FDC below.

The DNA interface communicates directly with any compatible random access memory once a Read or Write command is initiated by the host system. This interface uses the DMA address register loaded by OUT devices 126D and 125D as a starting address and always employs 131 sequential bytes of memory for a disk transfer. When the FDC is ready to access memory for any single byte transfer, signal REQ (J2-55) is raised. Nothing occurs until signal ACK (J2-56) appears true, raised by the host memory system when a memory cycle is granted to the FDC. ACK should be raised within (30 - memory cycle time) microseconds of the leading edge of REQ in order to service the FDC in time. ACK must remain true during the entire memory cycle.

When ACK appears high at the FDC, REQ is lowered and the DMA address register is gated to the memory address bus MADi, and signal -WRITE is lowered if a memory write (disk read) is requested. Address lines are stable within 100 nanoseconds of the leading edge of ACK. If -WRITE remains high, a memory read (disk write) is in progress. For memory read, the host memory must gate the contents of the memory byte addressed by MADi onto the memory data out bus MDOUTi (8 bits). When the data is stable, signal ACK must be lowered. The trailing edge of ACK is used by the FDC to latch the data byte. Busses are then released by the FDC within 50 nanoseconds of the trailing edge of ACK.

If a memory write is requested, the memory address is also gated to the MADi bus when ACK appears. In addition, -WRITE is lowered and data to be written in memory is placed on the memory data input bus MDINi (8 bits). Once the host memory has captured the data and address, ACK should be lowered and the busses will be released.

The FDC requests 131 sequential bytes of data for each transfer. The first three bytes are disk address information: track number, sector number, and data address mark. The remaining 128 bytes are data. The FDC automatically increments the DMA address appropriately, formats data, and generates or checks CRC characters.

In summary, the FDC directly accesses up to 64 Kbytes of random access memory using a simple asynchronous handshaking protocol. Memory address, READ/WRITE, input data, and output data are used after a request is made and acknowledged indicating that a memory cycle is granted to the FDC. Memory buffers of 131 bytes are required for each transfer.

### DISK INTERFACE

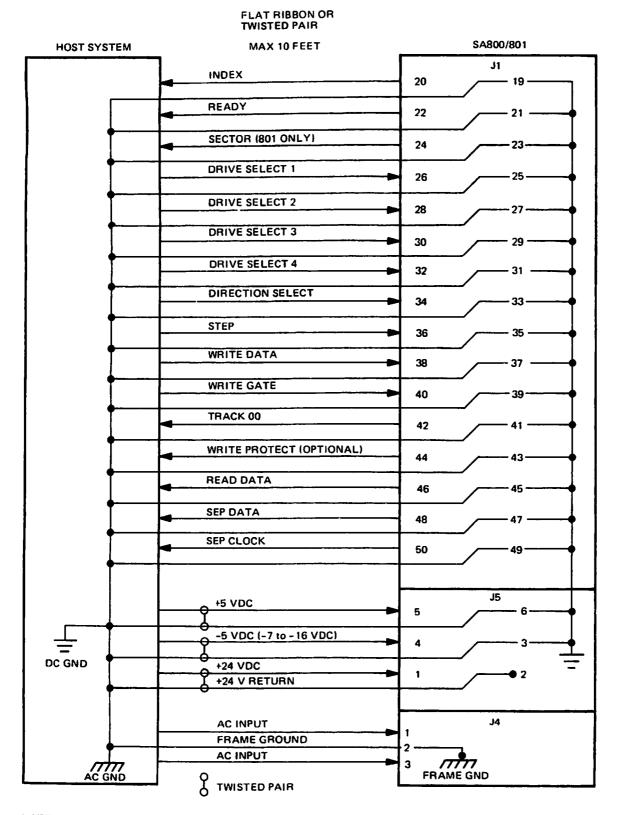

The disk interface is a set of signals on a separate 50 pin connector (J3) providing control and data paths to one to four drives.

A description of each available signal appears below. All are active low TTL level signals. An asterisk (\*) next to the signal name indicates signals from the drive to the controller. A plus (+) indicates an optional signal not vital to the FDC operation. Refer to Appendix I for pinout of connector J3. Device address 126D when strobed by the OUT signal loads the contents of the -DOUTi data bus into the most significant byte of the DMA address register. Data on the -DOUTi bus should be stable when the OUT strobe is issued.

Device address 125D (1750, 7D hex) when strobed by the OUT signal loads the contents of the -DOUTi data bus into the least significant byte of the DMA address register.

In summary, the device interface provides address bits to activate the FDC, uses strobes -IN and OUT to synchronize the actions of the controller with a host system, and has data paths for status and control information. These paths are used by the FDC as follows:

| STROBE | ADDRESS | HOST DATA IN | HOST DATA OUT        |

|--------|---------|--------------|----------------------|

| OUT    | 27D     | none         | command word         |

| OUT    | 26D     | none         | MSByte DMA address   |

| OUT    | 25D     | none         | LSByte DMA address   |

| -IN    | 27D     | status       | none                 |

| -IN    | 26D     | none         | none (J -56: -IN 26) |

Ŀ

|   | •  | Name       | Description                                                                                                                                                                                       |

|---|----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ē | *+ | -FILEINOP  | disk file inoperative - an error<br>condition from the drive detecting<br>illegal signal conditions during write                                                                                  |

|   | +  | -FIR       | file inoperative reset - response to the<br>FILEINOP condition from the host system<br>via the command byte                                                                                       |

|   | *  | -INDEX     | index pulse indicating rotating diskette<br>is at the beginning of a track                                                                                                                        |

|   | *  | -READY     | ready level indicating drive is in an operable condition(door closed, diskette up to speed, etc.)                                                                                                 |

|   |    | -DSØ       | disk select 0 - disk select lines are<br>wired one line per drive                                                                                                                                 |

|   |    | -DS I      | disk select                                                                                                                                                                                       |

|   |    | -DS2       | disk select 2                                                                                                                                                                                     |

|   |    | -DS3       | disk select 3                                                                                                                                                                                     |

| ( |    | -DIR       | direction - indicates direction head should move<br>in response to a -STEP pulse. A low (active)<br>on -DIR indicates stepping toward diskette<br>center, a high towards diskette edge (Track Ø). |

|   |    | -STEP      | step - 10 microsecond pulse to drive when<br>a head step in the indicated direction is<br>required                                                                                                |

|   |    | -WRITEDATA | interleaved clock and data pulses to be<br>written onto diskette                                                                                                                                  |

|   |    | -WG        | write gate - signal windowing WRITEDATA to<br>enable drive for writing                                                                                                                            |

|   | *  | -TRKZRO    | track zero – active when drive detects<br>head positioned at track 00                                                                                                                             |

|   | *+ | -READATA   | interleaved data and clock pulses from<br>drive                                                                                                                                                   |

|   | *  | -SD        | separated data pulses from drive                                                                                                                                                                  |

|   | *  | -SC        | separated clock pulses from drive                                                                                                                                                                 |

|   |    |            |                                                                                                                                                                                                   |

The FDC requires that the drive electronics provide clock pulses on the -SC line and data pulses without clocks on the -SD line. -READATA is unused. The -STEP pulse may be longer than 10 microseconds.

$( \$

#### INITIALIZATION

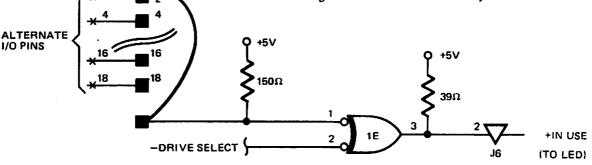

The sample circuitry in Figure 3 illustrates the initialization / requirements for the FDC. System wide reset circuitry should place a TTL low signal (-IRESET) on JI-55 to the and preset signal FDÇ BOOTSTRAP. Active low -BOOTSTRAP must be available to the FDC on JI-57. When the FDC completes its bootstrap procedure of reading track zero, sector one into DMA addresses 00-7F hex, it will issue 50 nanosecond pulse -IOF . In fact, -IOF is issued at the completion of every disk input or output operation. -IOF is used to clear the BOOTSTRAP latch which in turn may be used to signal the host system to begin execution of the bootstrap program now in low memory. BOOTSTRAP may be invoked under program control by issuing an -IN strobe with device address 126D. Signal -IN126 will appear on J1-56 and set BOOTSTRAP on its trailing edge.

#### POWER SYSTEM

+5 volts DC should be wired to pins 1,2,3, and 4 of both connectors JI and J2. 2.5 amps may be drawn by the FDC. Pins 83, 84, 85, and 86 of both connectors should be grounded. All odd numbered pins on connector J3 are grounded.

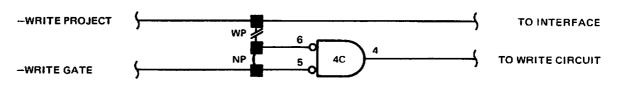

### WRITE PROTECT

The FDC provides write protection for the disk drive selected by signal -DSØ or all drives(jumper selectable). In order to allow writing, the DZPROT signal on JI-9 must be grounded (TTL "0") by the host system.

#### Figure 3. Initialization Circuitry.

SOFTWARE

The following system software control by the host CPU is required when using the FDC-1:

- I. Software must step the head to the desired track (using STEP and DIRECTION bits of the command byte) before reading or writing.

- 2. The initial DMA address must be loaded (2 bytes) prior to issuing a READ or WRITE command.

- 3. The three bytes in memory starting at the DMA address must be set to the desired track, sector, and address mark (for write).

- 4. A simple retry scheme should be implemented to attempt recovery from disk errors. (For track error, seek track Ø and then desired track before retry).

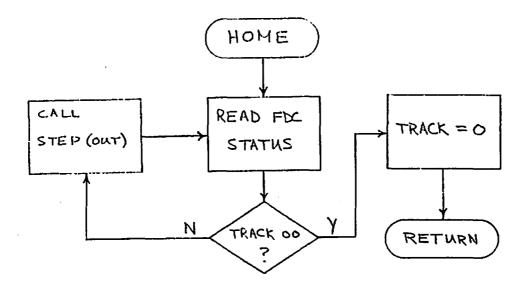

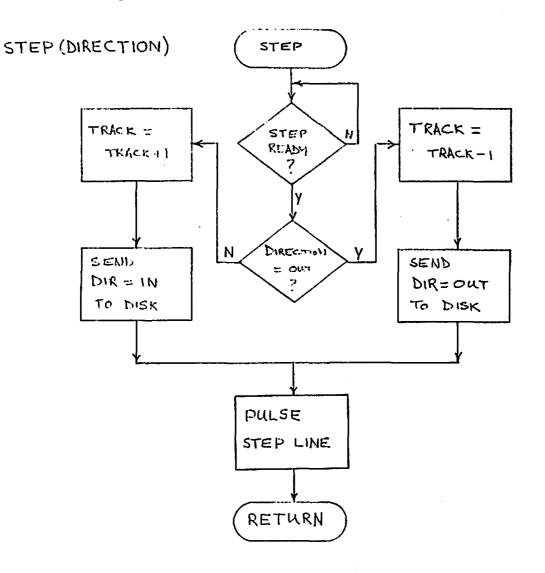

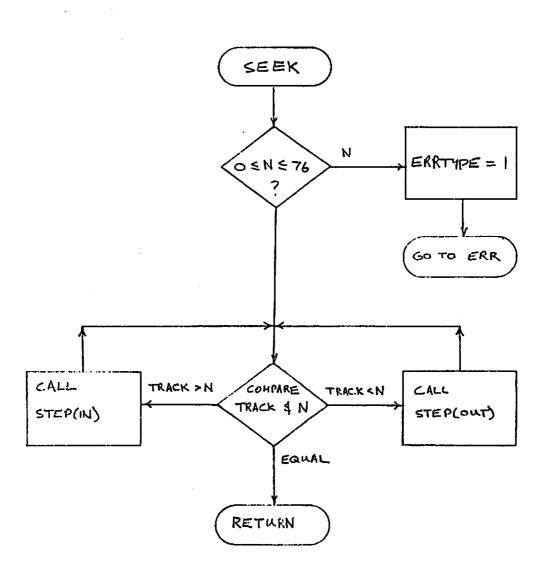

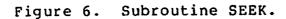

Figures 4 to 7 contain flowcharts for the following routines:

| HOME  | - | seek track zero          |

|-------|---|--------------------------|

| STEP  | - | step one track in or out |

| SEEK  | - | seek any valid track     |

| READ  | - | read one sector          |

| WRITE | - | write one sector         |

Assembly language code for the above routines is available for the 8080. Also available is a complete Disk Operating System for the 8080.

Figure 4. Subroutine HOME.

Subroutine STEP. Figure 5.

SEEK (N, ERR)

. . . . . . . . .

READ or WRITE (TRK, SECT, BUF, ERR)

Figure 7. Subroutines READ and WRITE.

Figure 7a. Subroutines READ and WRITE (cont).

•

#### JI TOP EDGE CONNECTOR

| <pre>1 +5 VDC<br/>3 +5 VDC<br/>5<br/>7<br/>9<br/>11<br/>13<br/>15<br/>17 GROUND<br/>19<br/>21 -DEV0 (device address bus)<br/>23 -DEV2<br/>25 -DEV4<br/>27 -DEV6<br/>29 -DOUTØ (data out buss)<br/>31 -DOUT2<br/>33 -DOUT4</pre> | 2 +5 VDC<br>4 +5 VDC<br>6<br>8<br>10<br>12<br>14<br>16<br>18 GROUND<br>20<br>22 -DEVI<br>24 -DEV3<br>26 -DEV5<br>28 -DEV7<br>30 -DOUTI<br>32 -DOUT3<br>34 -DOUT5 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35 -DOUT6<br>37 DINØ (data in buss)                                                                                                                                                                                             | 36 -DOUT7<br>38 DIN1                                                                                                                                             |

| 39 DIN2                                                                                                                                                                                                                         | 40 DIN3                                                                                                                                                          |

| 4  DIN4                                                                                                                                                                                                                         | 42 DIN5                                                                                                                                                          |

| 43 DIN6                                                                                                                                                                                                                         | 44 DIN7                                                                                                                                                          |

| 45 -IN (in strobe)                                                                                                                                                                                                              | 46 OUT (out strobe)                                                                                                                                              |

| 47                                                                                                                                                                                                                              | 48                                                                                                                                                               |

| 49                                                                                                                                                                                                                              | 50                                                                                                                                                               |

| 51                                                                                                                                                                                                                              | 52                                                                                                                                                               |

| 53                                                                                                                                                                                                                              | 54                                                                                                                                                               |

| 55 -IRESET (initial reset)                                                                                                                                                                                                      | 56 -IN126                                                                                                                                                        |

| 57 -BOOTSTRAP                                                                                                                                                                                                                   | 58                                                                                                                                                               |

| 59 -IOF                                                                                                                                                                                                                         | 60<br>62                                                                                                                                                         |

| 61                                                                                                                                                                                                                              | 64                                                                                                                                                               |

| 63<br>65                                                                                                                                                                                                                        | 66                                                                                                                                                               |

| 67                                                                                                                                                                                                                              | 69                                                                                                                                                               |

| 69                                                                                                                                                                                                                              | 70                                                                                                                                                               |

| 71                                                                                                                                                                                                                              | 72                                                                                                                                                               |

| 73                                                                                                                                                                                                                              | 74                                                                                                                                                               |

| 75                                                                                                                                                                                                                              | 76                                                                                                                                                               |

| 77                                                                                                                                                                                                                              | 78                                                                                                                                                               |

| 79                                                                                                                                                                                                                              | 80                                                                                                                                                               |

| 81                                                                                                                                                                                                                              | 82                                                                                                                                                               |

| 83 GROUND                                                                                                                                                                                                                       | 84 GROUND                                                                                                                                                        |

| 85 GROUND                                                                                                                                                                                                                       | 86 GROUND                                                                                                                                                        |

|                                                                                                                                                                                                                                 |                                                                                                                                                                  |

| , <b>9</b>                               |                        |

|------------------------------------------|------------------------|

| • 1 + 5 VDC                              | 2 + 5 VDC<br>4 + 5 VDC |

| 3 + 5 VDC<br>5                           | 4 + J VDC<br>6         |

| 7                                        | 8                      |

| 9                                        | 10                     |

|                                          | 2<br>  4               |

| 3<br>  5                                 | 14                     |

| 17                                       | 18                     |

| 19                                       | 20                     |

| 21 MDINØ (memory data in)                | 22 MDINI               |

| 23 MDIN2                                 | 24 MDIN3<br>26 MDIN5   |

| 25 MDIN4<br>27 MDIN6                     | 26 MDIN5<br>28 MDIN7   |

| 29 MADØ (memory address buss)            | 30 MADI                |

| 31 MAD2                                  | 32 MAD3                |

| 33 MAD4                                  | 34 MAD5                |

| 35 MAD6                                  | 36 MAD7<br>38 MAD9     |

| 37 MAD8<br>39 MAD10                      | 40 MADII               |

| 41 MADI2                                 | 42 MAD13               |

| 43 MADI4                                 | 44 MADI5               |

| 45                                       | 46                     |

| 47 MDOUTØ (memory data out)<br>49 MDOUT2 | 48 MDOUTI<br>50 MDOUT3 |

| 5 MDOUT4                                 | 52 MDOUT5              |

| 53 MDOUT6                                | 54 MDOUT7              |

| 55 REQ                                   | 56 ACK                 |

| 57                                       | 58                     |

| 59<br>6 I                                | 60<br>62               |

| 63 -WRITE (read)                         | 64                     |

| 65                                       | 66                     |

| 67 GROUND                                | 68 GROUND              |

| 69                                       | 70<br>72               |

| 71<br>73                                 | 74                     |

| 75                                       | 76                     |

| 77                                       | 78                     |

| 79                                       | 80                     |

| 81                                       | 82<br>84 CDOUND        |

| 83 GROUND<br>85 GROUND                   | 84 GROUND<br>86 GROUND |

| 0 GUUND                                  | OO GROUND              |

The controller uses a 50 connector cable for communication with the disk drives. This cable is designated J3 in the system. Pinout for the cable is:

| PIN     | SIGNAL NAME                       |

|---------|-----------------------------------|

| 2 4     |                                   |

| 4       |                                   |

| 6<br>8  |                                   |

| 8<br>10 |                                   |

| 12      |                                   |

| 4       |                                   |

| 16      | -FILEINOP (disk file inoperative) |

| 18      | -FIR (file inoperative reset)     |

| 20      | -INDEX                            |

| 22      | -READY                            |

| 24      |                                   |

| 26      | -DSØ (disk select 0)              |

| 28      | -DS I                             |

| 30      | -DS2                              |

| 32      | -DS3                              |

| 34      | -DIR (direction select)           |

| 36      | -STEP                             |

| 38      | -WRITEDATA                        |

| 40      | -WG (write gate)                  |

| 42      | -TRKZRØ (track Ø)                 |

| 44      |                                   |

| 46      | -READATA                          |

| 48      | -SD (separated data)              |

| 50      | -SC (separated clock)             |

ALL ODD PINS: GROUND

# SA800/801 Diskette Storage Drive

Original Equipment Manufacturers Manual

э,

• •

## TABLE OF CONTENTS

•

٠

٠

| 1.0 | Introdu | ction                                |

|-----|---------|--------------------------------------|

|     | 1.1     | General Description                  |

|     | 1.2     | Specification Summary                |

|     | 1.2.1   | Performance Specifications           |

|     | 1.2.2   | Functional Specifications            |

|     | 1.2.3   | Physical Specifications              |

|     | 1.2.4   | Reliability Specifications           |

| 2.0 | Functio | nal Characteristics 5                |

|     | 2.1     | General Operation 5                  |

|     | 2.2     | Read/Write and Control Electronics 6 |

|     | 2.3     | Drive Mechanism 6                    |

|     | 2.4     | Positioning Mechanism 6              |

|     | 2.5     | Read/Write Head 6                    |

|     | 2.6     | Recording Format 6                   |

| 3.0 | Functio | nal Operations                       |

|     | 3.1     | Power Sequencing                     |

|     | 3.2     | Drive Selection                      |

|     | 3.3     | Track Accessing                      |

|     | 3.3.1   | Step Out                             |

|     | 3.3.2   | Step In                              |

|     | 3.4     | Read Operation                       |

|     | 3.5     | Write Operation                      |

|     | 3.6     | Sequence of Events                   |

## TABLE OF CONTENTS Cont.

| 4.0 | Electrical | Interface                  |  |

|-----|------------|----------------------------|--|

|     | 4.1        | Signal Interface           |  |

|     | 4.1.1      | Input Lines                |  |

|     | 4.1.1.1    | Input Line Termination     |  |

|     | 4.1.1.2    | Drive Select 1 - 4         |  |

|     | 4.1.1.3    | Direction Select           |  |

|     | 4.1.1.4    | Step                       |  |

|     | 4.1.1.5    | Write Gate                 |  |

|     | 4.1.1.6    | Write Data                 |  |

|     | 4.1.1.7    | Head Load (Optional Input) |  |

|     | 4.1.1.8    | In Use (Optional Input)    |  |

|     | 4.1.2      | Output Lines               |  |

|     | 4.1.2.1    | Track Zero                 |  |

|     | 4.1.2.2    | Index                      |  |

|     | 4.1.2.3    | Sector (SA801 Only)        |  |

|     | 4.1.2.4    | Ready                      |  |

|     | 4.1.2.5    | Read Data                  |  |

|     | 4.1.2.6    | Sep Data                   |  |

|     | 4.1.2.7    | Sep Data                   |  |

|     | 4.1.2.8    | Write Protect (Optional)   |  |

|     | 4.1.3      | Alternate I/O Pins         |  |

|     | 4.2        | Power Interface            |  |

|     | 4.2.1      | AC Power                   |  |

|     | 4.2.2      | DC Power                   |  |

## TABLE OF CONTENTS Cont.

٠

.

| 5.0 | Physical  | Interface                                                      |

|-----|-----------|----------------------------------------------------------------|

|     | 5.1       | J1/P1 Connector                                                |

|     | 5.2       | J5/P5 Connector                                                |

|     | 5.3       | J4/P4 Connector                                                |

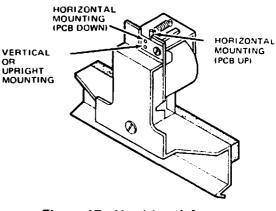

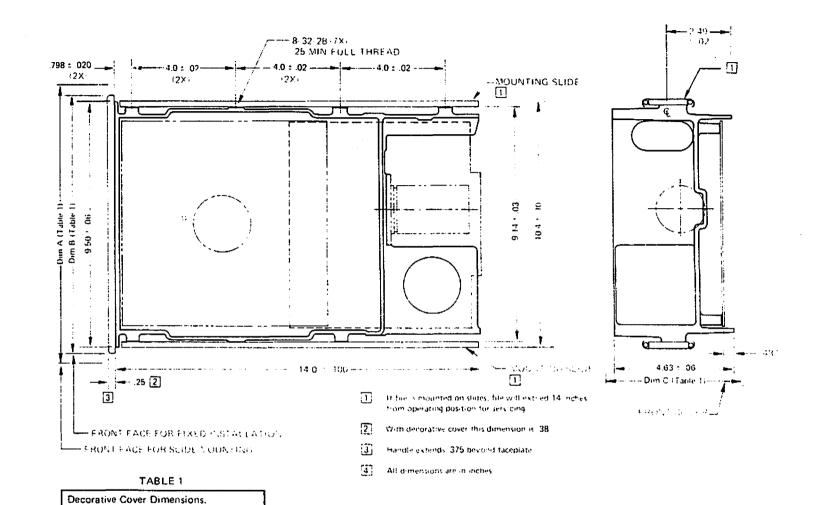

| 6.0 | Drive Phy | vsical Specifications                                          |

|     | 6.1       | Drive Dimensions                                               |

|     | 6.2       | Mounting Recommendations                                       |

|     | 6.2.1     | Vertical Mounting                                              |

|     | 6.2.2     | Horizontal Mounting                                            |

|     | 6.2.3     | Upright Mounting                                               |

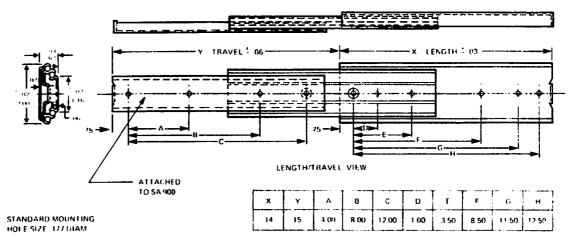

|     | 6.3       | Chassis Slide                                                  |

|     | 6.4       | Decorative Face Plate                                          |

| 7.0 | Customer  | Installable Options                                            |

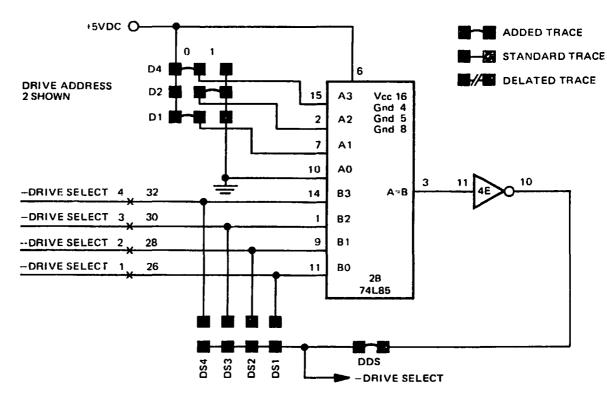

|     | 7.1       | Drive Select - One to Eight Drives                             |

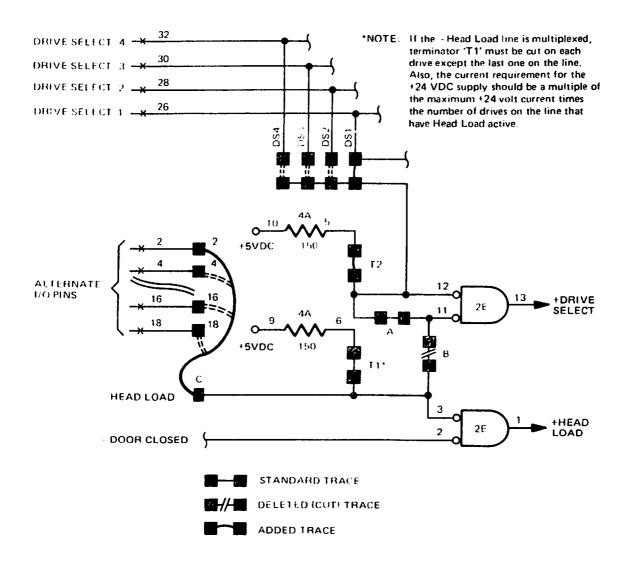

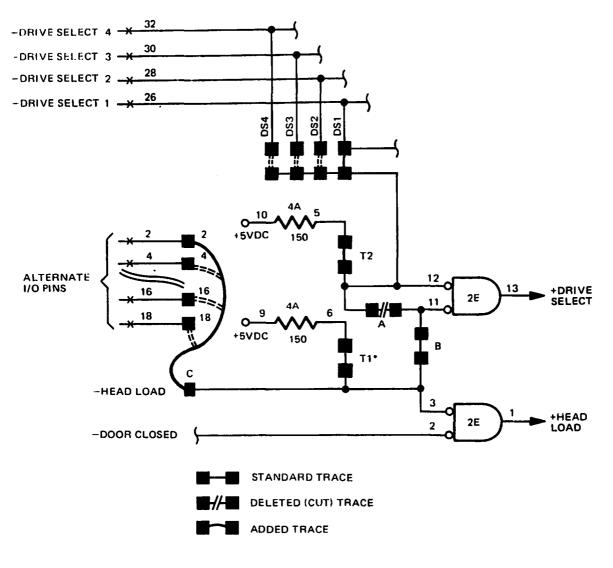

|     | 7.2       | Select Drive Without Loading Head<br>or Enabling Stepper Motor |

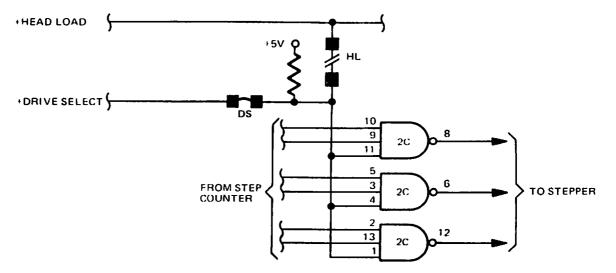

|     | 7.3       | Select Drive and Enable Stepper<br>Without Loading Head        |

|     | 7.4       | Load Head Without Selecting Drive<br>or Enabling Stepper       |

|     | 7.5       | Radial Ready                                                   |

|     | 7.6       | Radial Index/Sector                                            |

|     | 7.7       | Eight, 16, or 32 Sectors                                       |

|     | 7.8       | In Use Optional Input (Activity LED)                           |

|     | 7.9       | Write Protect Optional Use                                     |

## TABLE OF CONTENTS Cont.

| 8.0 | Operatio | n Procedures                  | • | • | • | • | • | · | • | • | • | 35 |

|-----|----------|-------------------------------|---|---|---|---|---|---|---|---|---|----|

|     | 8.1      | Diskette Loading and Handling | • | • | • | • | • | • | - | • | • | 35 |

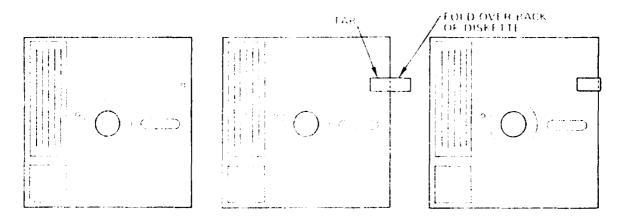

|     | 8.2      | SA101 Write Protect           | • | • | • | • | • | • | • | • | • | 36 |

|     | 8.3      | SA 100 Write Protect          | • | • | • | • | • | • | • | • | • | 36 |

| 9.0 | Error De | tection and Correction        | • | • |   | • | • | • | • | • | • | 37 |

|     | 9.1      | Write Error                   | • | • | • | • | • | • | • | • | • | 37 |

|     | 9.2      | Read Error                    | • | • | • | • | • |   |   |   | • | 37 |

## LIST OF ILLUSTRATIONS

| 1.  | SA800/801 Diskette Storage Drive             |

|-----|----------------------------------------------|

| 2.  | SA800/801 Functional Diagram 5               |

| 3.  | Track Access Timing                          |

| 4.  | Read Initiate Timing                         |

| 5.  | Read Signal Timing                           |

| 6.  | Write Initiate Timing                        |

| 7.  | Write Data Timing                            |

| 8.  | General Control and Data Timing Requirements |

| 9.  | Interface Connections                        |

| 10. | Interface Signal Driver/Receiver             |

| 11. | Index Timing                                 |

| 12. | Sector Timing                                |

## LIST OF ILLUSTRATIONS Cont.

•

(Inter

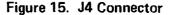

| 13.         | J1 Connector Dimensions                                          |

|-------------|------------------------------------------------------------------|

| 14.         | J5 Connector                                                     |

| 15.         | J4 Connector                                                     |

| 16.         | Interface Connectors – Physical Location Diagram 20              |

| 17.         | Head Load Actuator – Mounting Prerequisites                      |

| 18.         | SA800/801 Diskette Storage Drive Dimensions                      |

| 19.         | Slide Mounting Dimensions                                        |

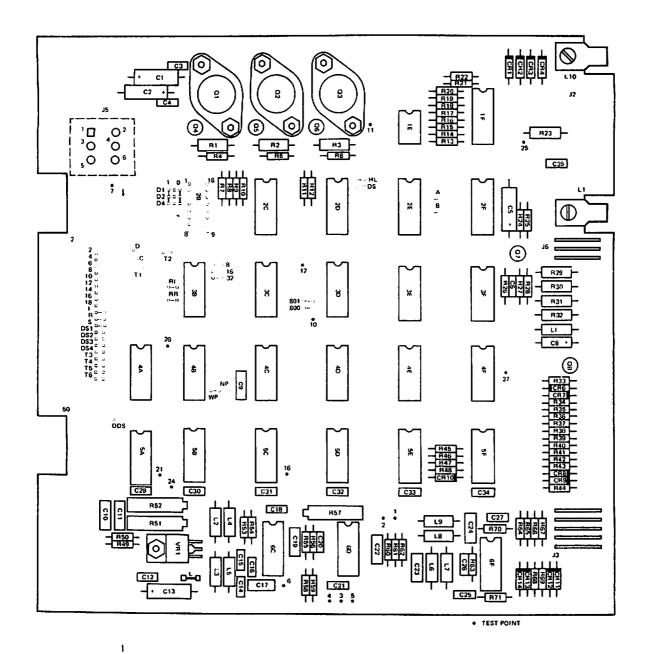

| 20.         | SA800/801 PCB Component Locations                                |

| 21.         | Drive Select Circuitry                                           |

| 22.         | Select Drive Without Loading Head Circuit                        |

| 23.         | Stepper Motor Enable Circuit                                     |

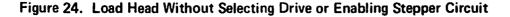

| 24.         | Load Head Without Selecting Drive<br>or Enabling Stepper Circuit |

| 25.         | Radial Ready Circuit                                             |

| 26.         | Radial Index/Sector Circuit                                      |

| 27.         | Sector Timing Relationships                                      |

| <b>2</b> 8. | Sector Divide Circuit                                            |

| 29.         | In Use/Activity LED Circuit                                      |

| 30.         | Write Protect Circuit                                            |

| 31.         | Loading SA800/801                                                |

| 32.         | Diskette Write Protected                                         |

| 33.         | Write Protect Hole Specifications.                               |

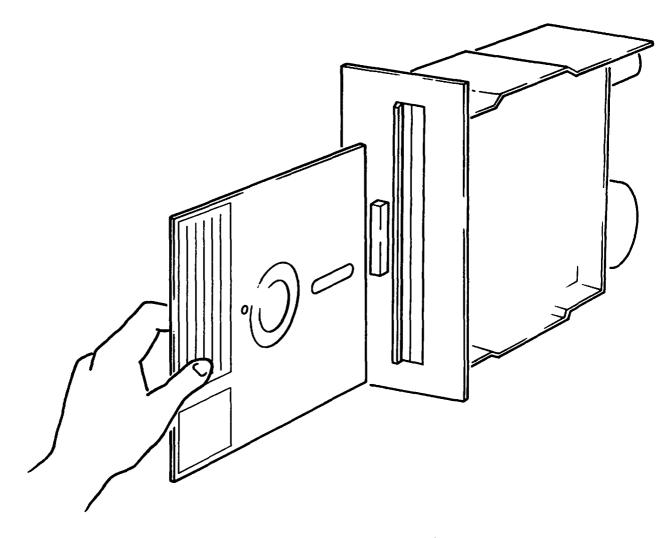

Figure 1. SA800/801 Diskette Storage Drive

#### **1.0 INTRODUCTION**

#### 1.1 General Description

The SA800/801 are enhanced versions of the successful SA900/901 Diskette Storage Drive. The SA800/801 provides the customer with a mature and reliable product, manufactured to the same high standard of excellence as the 900/901, bi-with additional features.

The SA800 Diskette Storage Drive can read and write diskettes for interchange with other SA800's, the SA900, IBM 3741, 3742 or 3540 and with the new IBM System 32.

The SA801 provides the same features as the SA800 with additional flexibility for those requirements which preclude IBM compatibility.

The SA800/801 Diskette Storage Drives have as standard features: a patented diskette clamping/ registration design which eliminates the possibility of damage to the diskette due to misregistration and guarantees over 30,000 interchanges with each diskette; single and double density capability on the same drive for the same price; a proprietary ceramic R/W head designed and manufactured by Shugart Associates to provide media life exceeding 3.5 million passes/track and head life exceeding 15,000 hours; an activity light which indicates drive in use; and ribbon cable or twisted pair connector for ease of packaging. All of these features and more are available with the SA800/801.

SA800/801 Diskette Storage Drives provide the system designer solutions to his applications requirements with greater performance and reliability than cassette or cartridge drives, and lower cost with increased function over card I/O and reel-to-reel tape drives.

Applications for the SA800/801 Diskette Storage Drive are key entry systems, point of sale recording systems, batch terminal data storage, microprogram load and error logging, minicomputer program and auxiliary data storage, word processing systems and data storage for small business systems.

The SA100 Diskette, IBM Diskette or equivalent, can be read and written interchangeably between any SA800 and IBM 3741/42, 3747 and 3540. The SA101 Diskette can be read or written interchangeably on any SA801.

### 1.2 Specification Summary

### 1.2.1 Performance Specifications

| Capacity          | Single Density   | Double Density   |

|-------------------|------------------|------------------|

| Unformatted       |                  |                  |

| Per Disk          | 3.2 megabits     | 6.4 megabits     |

| Per Track         | 41.7 kilobits    | 83.4 kilobits    |

| 1BM Format        |                  |                  |

| Per Disk          | 2.0 megabits     | n/a              |

| Per Track         | 26.6 kilobits    | n/a              |

| Transfer Rate     | 250 kilobits/sec | 500 kilobits/sec |

| Latency (average) | 83 ms            | 83 ms            |

| Access Time       |                  |                  |

| Track to Track    | 10 ms            | 10 ms            |

| Average           | 260 ms           | 260 ms           |

| Settling Time     | 8 ms             | 8 ms             |

| Head Load Time    | 35 ms            | 35 ms            |

### 1.2.2 Functional Specifications

| Single Density     | Double Density                                                                                   |

|--------------------|--------------------------------------------------------------------------------------------------|

| 360 rpm            | 360 rpm                                                                                          |

|                    |                                                                                                  |

| 3200 bpi           | 6400 bpi                                                                                         |

| 6400 fci           | 6400 fci                                                                                         |

| 48 tpi             | 48 tpi                                                                                           |

| 77                 | 77                                                                                               |

|                    |                                                                                                  |

| 0                  | 0                                                                                                |

| 32/16/8            | 32/16/8                                                                                          |

| 1                  | 1                                                                                                |

| FM                 | м <sup>2</sup> FM                                                                                |

|                    |                                                                                                  |

| SA100/IBM Diskette | SA100/IBM Diskette                                                                               |

| SA101              | SA101                                                                                            |

|                    | 360 rpm<br>3200 bpi<br>6400 fci<br>48 tpi<br>77<br>0<br>32/16/8<br>1<br>FM<br>SA100/IBM Diskette |

### 1.2.3 Physical Specifications

| Environmental Limits                             |                              |  |  |  |

|--------------------------------------------------|------------------------------|--|--|--|

| Ambient Temperature                              | = 50°F to 100°F              |  |  |  |

| Relative Humidity                                | = 20% to 80%                 |  |  |  |

| Maximum Wet Bulb                                 | = 78°F                       |  |  |  |

| AC Power Requirements                            |                              |  |  |  |

| 50/60 Hz ± 0.5 Hz                                |                              |  |  |  |

| 100/115 VAC Installations                        | = 90 to 127 V @ .4A typical  |  |  |  |

| 200/230 VAC Installations                        | = 180 to 253 V @ .2A typical |  |  |  |

| DC Voltage Requirements                          |                              |  |  |  |

| +24 VDC ± 5% 1.3A typical                        |                              |  |  |  |

| + 5 VDC ± 5% 0.8A typical                        |                              |  |  |  |

| - 5 VDC ± 5% .05A typical (option -7 to -16 VDC) |                              |  |  |  |

| Mechanical Dimensions                            |                              |  |  |  |

| Width = $45/8$ in.                               |                              |  |  |  |

| Height = $9 \frac{1}{2}$ in.                     |                              |  |  |  |

| Depth = $14  1/4  in$ .                          |                              |  |  |  |

| Weight = $13.0$ lbs.                             |                              |  |  |  |

| Heat Dissipation = 245 BTU/hr. typical           |                              |  |  |  |

|                                                  |                              |  |  |  |

### 1.2.4 Reliability Specifications

MTBF:

PM:

MTTR:

Component Life: Error Rates:

Soft Read Errors:

Hard Read Errors:

Seek Errors:

Media Life: Passes per Track Insertions: 5000 POH under heavy usage 8000 POH under typical usage.

Every 5000 POH under heavy usage.Every 15,000 POH under typical usage.30 minutes.

15,000 POH.

1 per  $10^9$  bits read. 1 per  $10^{12}$  bits read. 1 per  $10^6$  seeks.

3.5 x 10<sup>6</sup> 30,000+

.

•

• •

. .

.

.

# 2.0 FUNCTIONAL CHARACTERISTICS

# 2.1 General Operation

The SA800/801 Diskette Storage Drive consists of read/write and control electronics, drive mechanism, read/write head, track positioning mechanism, and the removable diskette. These components perform the following functions:

> Interpret and generate control signals. Move read/write head to the selected track. Read and write data.

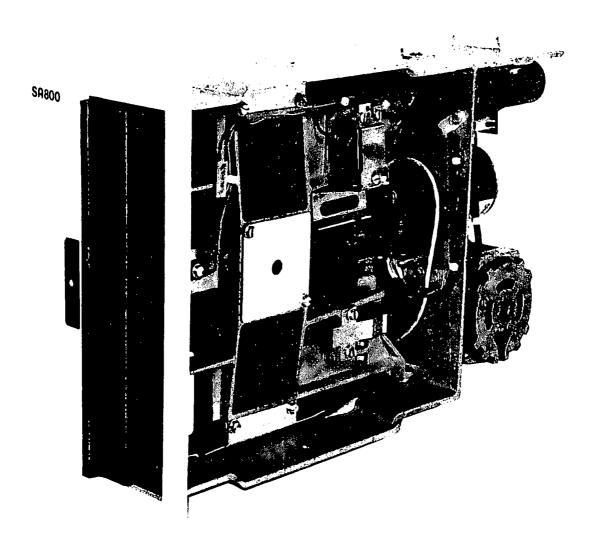

The relationship and interface signals for the internal functions of the SA800/801 are shown in Figure 2.

The Head Positioning Actuator positions the read/ write head to the desired track on the diskette. The Head Load Actuator loads the diskette against the read/write head and data may then be recorded or read from the diskette.

Figure 2. SA800/801 Functional Diagram

# 2.2 Read/Write and Control Electronics

The electronics are packaged on one PCB. The PCB contains:

- 1. Index Detector Circuits (Sector/Index for 801)

- 2. Head Position Actuator Driver

- 3. Head Load Actuator Driver

- 4. Read/Write Amplifier and Transition Detector

- 5. Data/Clock Separation Circuits

- 6. Write Protect

- 7. Drive Ready Detector Circuit

- 8. Drive Select Circuits

# 2.3 Drive Mechanism

The Diskette drive motor rotates the spindle at 360 rpm through a belt-drive system. 50 or 60 Hz power is accommodated by changing the drive pulley and belt. A registration hub, centered on the face of the spindle, positions the Diskette. A clamp that moves in conjunction with the cartridge guide fixes the Diskette to the registration hub.

# 2.4 Positioning Mechanism

An electrical stepping motor (Head Position Actuator) and lead screw positions the read/write head. The stepping motor rotates the lead screw clockwise or counterclockwise in 15° increments. A 15° rotation of the lead screw moves the read/ write head one track position. The using system increments the stepping motor to the desired track.

# 2.5 Read/Write Head

The SA800/801 head is a single element ceramic read/write head with straddle erase elements to provide erased areas between data tracks. Thus normal interchange tolerances between media and drives will not degrade the signal to noise ratio and insures Diskette interchangeability.

The read/write head is mounted on a carriage which is located on the Head Position Actuator lead screw. The Diskette is held in a plane perpendicular to the read/write head by a platen located on the base casting. This precise registration assures perfect compliance with the read/write head. The Diskette is loaded against the head with a load pad actuated by the head load solenoid.

The read/write head is in direct contact with the Diskette. The head surface has been designed to obtain maximum signal transfer to and from the magnetic surface of the Diskette with minimum head/Diskette wear.

# 2.6 Recording Format

The format of the data recorded on the disk is totally a function of the host system, and can be designed around the users application to best take advantage of the total available bits that can be written on any one track.

For a detailed discussion of various recording formats, the systems designer should read one of the following:

- 1. IBM Compatibility Manual Publication number SA0006-5

- 2. Shugart Associates Double Density Design Guide Publication number SA0008-0

- 3. SA801/901 Track Formats Publication number SA0010-0

#### 3.0 FUNCTIONAL OPERATIONS

# 3.1 Power Sequencing

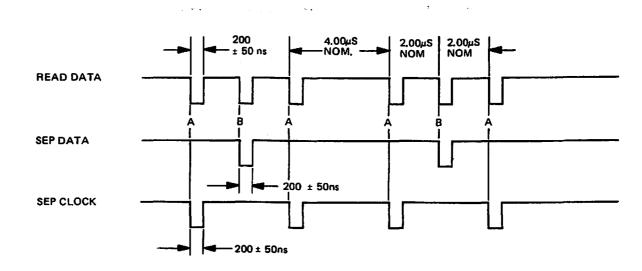

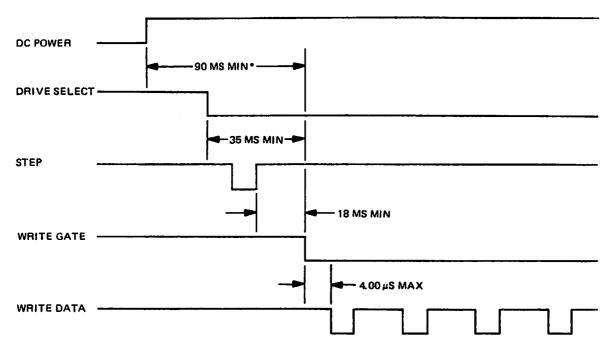

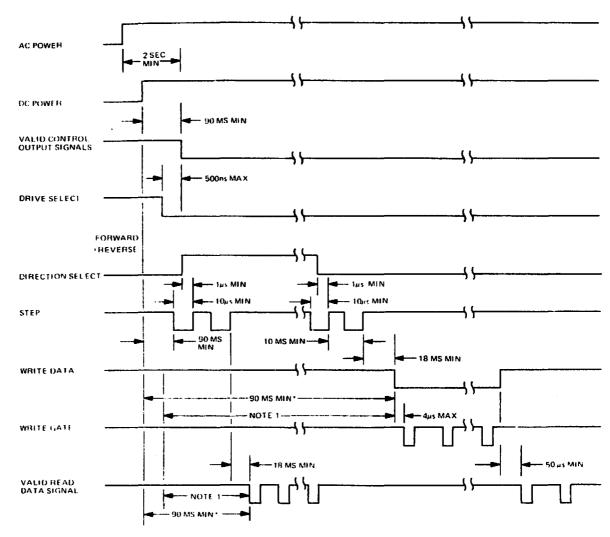

Applying AC and DC power to the SA800/801 can be done in any sequence, however, once AC power has been applied, a 2 second delay must be introduced before any Read or Write operation is attempted. This delay is for stabilization of the Diskette rotational speed. Also, after application of DC power, a 90 millisecond delay must be introduced before a Read, Write, or Seek operation or before the control output signals are valid. After powering on, initial position of the R/W head with respect to data tracks is indeterminant. In order to assure proper positioning of the R/W head prior to any read/write operation after powering on, a Step Out operation should be performed until the Track 00 indicator becomes active.

#### 3.2 Drive Selection

Drive selection occurs when a drive's Drive Select line is activated. Only the drive with this line active will respond to input lines or gate output lines. Under normal operation, the Drive Select line will load the R/W head, apply power to the stepper motor, enable the input lines and activate the output lines. Optional modes of operation are available to the user by cutting or connecting traces. Reference section 7 for these user installable features.

# 3.3 Track Accessing

Seeking the R/W head from one track to another is accomplished by:

- a. Activating Drive Select line.

- b. Selecting desired direction utilizing Direction Select line.

- c. Write Gate being inactive.

- d. Pulsing the Step line.

Multiple track accessing is accomplished by repeated pulsing of the Step line until the desired track has been reached. Each pulse on the Step line will cause the R/W head to move one track either in or out depending on the Direction Select line. Head movement is initiated on the trailing edge of the Step Pulse.

#### 3.3.1 Step Out

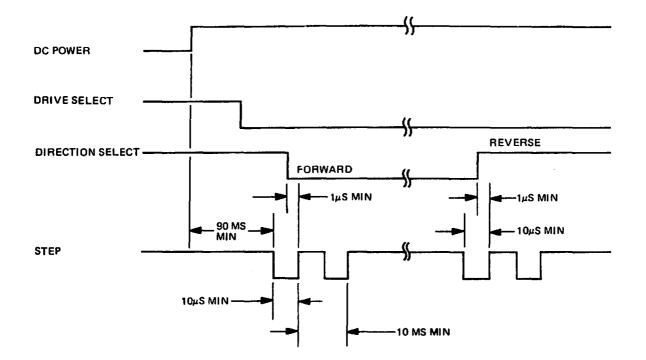

With the Direction Select line at a plus logic level (2.5V to 5.25V) a pulse on the Step line will cause the R/W head to move one track away from the center of the disk. The pulse(s) applied to the Step line and the Direction Select line must have the timing characteristics shown in Figure 3.

\* 2 SECONDS IF AC AND DC POWER ARE APPLIED AT SAME TIME

Figure 4. Read Initiate Timing

# 3.3.2 Step In

With the Direction Select line at a minus logic level (0V to .4V), a pulse on the Step line will cause the R/W head to move one track closer to the center of the disk. The pulse(s) applied to the Step line must have the timing characteristics shown in Figure 3.

# 3.4 Read Operation

Reading data from the SA800/801 Diskette Storage drive is accomplished by:

- a. Activating Drive Select line.

- b. Write Gate being inactive.

The timing relationships required to initiate a read sequence are shown in Figure 4. These timing specifications are required in order to guarantee that the R/W head position has stabilized prior to reading.

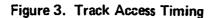

The timing of the read signals, Read Data, Separated Data, and Separated Clock are shown in Figure 5.

# 3.5 Write Operation

Writing data to the SA800/801 is accomplished by:

- a. Activating the Drive Select line.

- b. Activating the Write Gate line.

- c. Pulsing the Write Data line with the data to be written.

The timing relationships required to initiate a write data sequence are shown in Figure 6. These timing specifications are required in order to guarantee that the R/W head position has stabilized prior to writing.

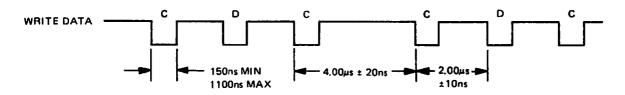

The timing specifications for the Write Data pulses are shown in Figure 7.

# 3.6 Sequence of Events

The timing diagram shown in Figure 8 shows the necessary sequence of events with associated timing restrictions for proper operation.

A = LEADING EDGE OF BIT MAYBE ± 400 ns FROM ITS NOMINAL POSITION. B = LEADING EDGE OF BIT MAYBE ± 200 ns FROM ITS NOMINAL POSITION.

Figure 5. Read Signal Timing

\* 2 SECONDS IF AC AND DC POWER ARE APPLIED AT SAME TIME.

Figure 6. Write Initiate Timing

Figure 7. Write Data Timing

\* 2 SECONDS IF AC AND DC POWER ARE APPLIED AT SAME TIME

NOTE 1. 35ms minimum delay must be introduced after Drive Select to allow for proper head load setting. If stepper power is to be applied independent of Head Load, there as 8ms minimum delay must be introduced to allow for stepper settling. See section 7 on optional customer installable features.

# Figure 8. General Control and Data Timing Requirements

•

a serve Barn Construction and the body of expression Goldstore

# 4.0 ELECTRICAL INTERFACE

The interface of the SA800/801 Diskette drive can be divided into two categories:

- 1. Signal

- 2. Power

The following sections provide the electrical definition for each line.

Reference Figure 9 for all interface connections.

#### 4.1 Signal Interface

The signal interface consists of two categories:

- I. Control

- 2. Data transfer

All lines in the signal interface are digital in nature and either provide signals to the drive (input), or provide signals to the host (output), via interface connector P1/J1.

# 4.1.1 Input Lines

There are ten (10) signal input lines, eight (8) are standard and two (2) are user installable options (reference section 7).

The input signals are of two types, those intended to be multiplexed in a multiple drive system and those which will perform the multiplexing. The input signals to be multiplexed are:

- 1. Direction Select

- 2. Step

- 3. Write Data

- 4. Write Gate

The input signals which are intended to do the multiplexing are:

- 1. Drive Select 1

- 2. Drive Select 2

- 3. Drive Select 3

- 4. Drive Select 4

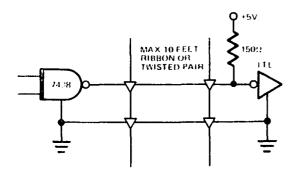

The input lines have the following electrical specifications. Reference Figure 10 for the recommended circuit.

True = Logical zero = Vin ±0.0V to +0.4V (a' lin = 40 ma (max) False = Logical one = Vin +2.5V to +5.25V (a' lin = 0 ma (open) Input Impedence = 150 ohms

NOTE: Not shown are the nine Alternate I/O connections. The connections for these lines are on pins 2, 4, 6, 8, 10, 12, 14, 16, and 18. Signal return for these lines are on pins 1, 3, 5, 7, 9, 11, 13, 15, 17, and 19 respectively. Reference section 7 for uses of these lines.

# Figure 9. Interface Connections

#### 4.1.1.1 Input Line Termination

The SA800/801 has been provided with the capability of terminating the four input lines, which are meant to be multiplexed, by jumpering traces. The four lines and their respective jumpering traces are:

- 3. Write Data ..... Trace "T5"

In order for the drive to function properly, the last drive on the interface must have these four lines terminated. Termination of these four lines can be accomplished by either of two methods.

- 1. Install jumpers (on the last drive) across the posts provided on the PCB. The jumpers may be installed by soldering, wire wrapping, or by use of a shorting plug Shugart P/N 15648 or AMP P/N 530153-2. The shorting plugs are not supplied with each drive unless it is specified on the order.

- External termination may be used provided the terminator is beyond the last drive. Each of the four lines should be terminated by using a 150 ohm, ¼ watt resistor, pulled up to +5 VDC.

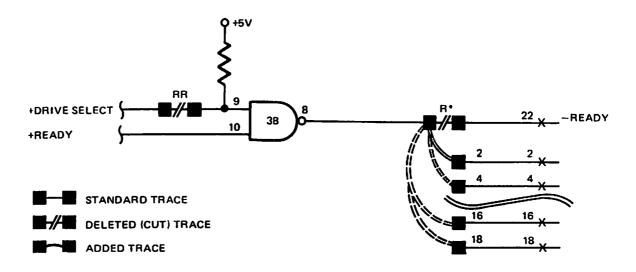

#### 4.1.1.2 Drive Select 1 - 4

Drive Select when activated to a logical zero level, activates the multiplexed I/O lines and loads the R/W head. In this mode of operation only the drive with this line active will respond to the input lines and gate the output lines.

Four separate input lines, Drive Select 1, Drive Select 2, Drive Select 3, and Drive Select 4, are provided so that up to four drives may be multiplexed together in a system and have separate Drive Select lines. Traces 'DS1', 'DS2', 'DS3', and 'DS4' have been provided to select which Drive Select line will activate the interface signals for a unique drive. As shipped from the factory, a shorting plug is installed on 'DS1'. To select another Drive Select line, this plug should be moved to the appropriate 'DS' pin. For additional methods of selecting drives, see section 7.1.

#### 4.1.1.3 Direction Select

This interface line is a control signal which defines direction of motion the R/W head will take when the Step line is pulsed. An open circuit or logical one defines the direction as "out" and if a pulse is applied to the Step line the R/W head will move away from the center of the disk. Conversely, if this input is shorted to ground or a logical zero level, the direction of motion is defined as "in" and if a pulse is applied to the step line, the R/W head will move towards the center of the disk.

# 4.1.1.4 Step

This interface line is a control signal which causes the R/W head to move with the direction of motion as defined by the Direction Select line.

The access motion is initiated on each logical zero to logical one transition, or the trailing edge of the signal pulse. Any change in the Direction Select line must be made at least  $1\mu$ s before the trailing edge of the Step pulse. Refer to Figure 3 for these timings.

# 4.1.1.5 Write Gate

The active state of this signal, or logical zero, enables Write Data to be written on the diskette. The inactive state, or logical one, enables the read data logic (Separated Data, Separated Clock, and Read Data) and stepper logic. Refer to Figure 6 for timings.

# 4.1.1.6 Write Data

This interface line provides the data to be written on the diskette. Each transition from a logical one level to a logical zero level, will cause the current through the R/W head to be reversed thereby writing a data bit. This line is enabled by Write Gate being active. Refer to Figure 7 for timings.

# 4.1.1.7 Head Load (Optional input trace 'C')

This customer installable option, when activated to a logical zero level and the diskette access door is closed, will load the R/W head load pad against the diskette. Refer to section 7 for uses and method of installation.

# 4.1.1.8 In Use (Optional input trace 'D')

This customer installable option, when activated to a logical zero level will turn on the Activity LED in the door push button. This signal is an "OR" function with Drive Select. Refer to section 7.8 for uses and method of installation.

# 4.1.2 Output Lines

There are seven (7) output lines from the SA800 and eight (8) from the SA801. There also is one (1) optional output line from the SA800/801.

The output signals are driven with an open collector output stage capable of sinking a maximum of 40 ma at a logical zero level or true state with a maximum voltage of 0.4V measured at the driver. When the line driver is in a logical one or false state the driver is off and the collector current is a maximum of 250 microamperes.

Refer to Figure 10 for the recommended circuit.

Figure 10. Interface Signal Driver/Receiver

### 4.1.2.1 Track 00

The active state of this signal, or a logical zero indicates when the drives R/W head is positioned at track zero (the outer most track) and the access circuitry is driving current through phase one of the stepper motor. This signal is at a logical one level, or false state, when the selected drives R/W head is not at track 00.

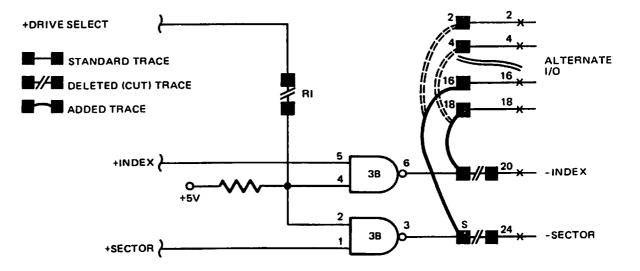

## 4.1.2.2 Index

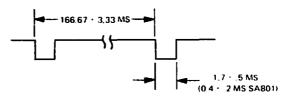

This interface signal is provided by the drive once each revolution of the diskette (166.67ms) to indicate the beginning of the track. Normally this signal is a logical one and makes the transition to the logical zero level for a period of 1.7ms (0.4ms on SA801) once each revolution. The timing for this signal is shown in Figure 11.

To correctly detect Index at the control unit, Index should be false at Drive Select time, that is, the CU should see the transition from false to true after the drive has been selected.

For additional methods of detecting Index, refer to section 7.6.

# Figure 11. Index Timing

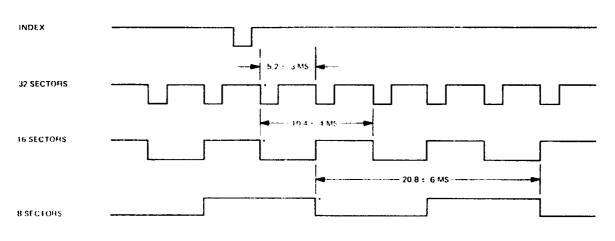

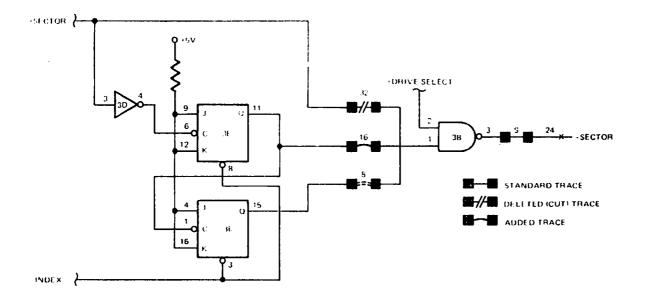

#### 4.1.2.3 Sector (SA801 only)

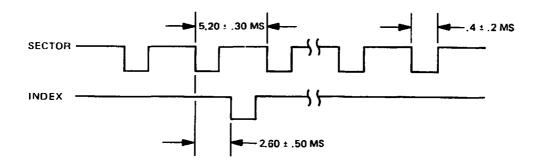

This interface signal is provided by the drive 32 times each revolution. Normally, this signal is a logical one and makes the transition to a logical zero for a period of 0.4ms each time a sector hole on the Diskette is detected. Figure 12 shows the timing of this signal and its relationship to the Index pulse.

For additional methods of detecting Sector refer to section 7.7.

Figure 12. Sector Timing

# 4.1.2.4 Ready

This interface signal indicates that two (2) index holes have been sensed after properly inserting a diskette and closing the door, or that two index holes have been sensed following the application of +5V power to the drive.

For additional methods of using the Ready line, refer to section 7.5.

# 4,1.2.5 Read Data

This interface line provides the "raw data" (clock and data together) as detected by the drive electronics. Normally, this signal is a logical one level and becomes a logical zero level for the active state. Reference Figure 5 for the timing and bit shift tolerance within normal media variations.

#### 4.1.2.6 Sep Data

This interface line furnishes the data bits as separated from the "raw data" by use of the internal data separator. Normally, this signal is a logical one level and becomes a logical zero level for the active state. Reference Figure 5 for the timing. This line is available on the SA800/801 Model 1 only.

#### 4.1.2.7 Sep Clock

This interface line furnishes the clock bits as separated from the "raw data" by use of the internal data separator. Normally, this signal is a logical one level and becomes a logical zero level for the active state. Reference Figure 5 for the timing. This line is available on the SA800/801 Model 1 only.

# 4.1.2.8 Write Protect (Optional)

This interface signal is provided by the drive to give the user an indication when a Write Protected Diskette is installed. The signal is logical zero level when it is protected. Under normal operation, the drive will inhibit writing with a protected diskotte installed in addition to notifying the interface.

For other methods of using Write Protect, refer to section 7.9.

# 4.1.3 Alternate I/O Pins

These interface pins have been provided for use with customer installable options. Refer to section 7 for methods of use.

# 4.2 Power Interface

The SA800/801 Diskette Storage Drive requires both AC and DC power for operation. The AC power is used for the spindle drive motor and the DC power is used for the electronics and the stepper motor.

# 4.2.1 AC Power

The AC power to the drive is via the connector P4/J4 located to the rear of the drive and below the AC motor capacitor. The P4/J4 pin designations are outlined below for standard as well as optional AC power.

| P4<br>PIN         | 60 Hz                                   |                                           | 50 Hz                                   |                                           |  |

|-------------------|-----------------------------------------|-------------------------------------------|-----------------------------------------|-------------------------------------------|--|

|                   | 110 V (Standard)                        | 208/230 V                                 | 110 V                                   | 220 V                                     |  |

| 1<br>2<br>3       | 90-127 VAC<br>Frame Gnd<br>90-127 V Rtn | 180-253 VAC<br>Frame Gnd<br>180-253 V Rtn | 90-127 VAC<br>Frame Gnd<br>90-127 V Rtn | 180-253 VAC<br>Frame Gnd<br>180-253 V Rtn |  |

| MAX<br>CURRENT    | 0.5 Amps                                | 0.4 Amps                                  | 0.6 Amps                                | 0.4 Amps                                  |  |

| FREQ<br>TOLERANCE | ±0.5 Hz                                 |                                           | ±0.5 Hz                                 |                                           |  |

# 4.2.2 DC Power

DC power to the drive is via connector P5/J5 located on non-component side of PCB near the P4 connector. The three DC voltages and their specifications along with their P5/J5 pin designators, are outlined below.

| P5<br>PIN | DC VOLTAGE                                    | TOLERANCE | CURRENT                  | MAX<br>RIPPLE (p to p) |

|-----------|-----------------------------------------------|-----------|--------------------------|------------------------|

| l         | +24 VDC                                       | ±1.2 VDC  | 1.7 A Max**<br>1.3 A Typ | 100 mv                 |

| 2         | +24 V Return*                                 |           |                          |                        |

| 3         | - 5 V Return                                  |           |                          |                        |

| 4         | - 5 VDC                                       | ±0.25 VDC | 0.07 A Max<br>0.05 A Typ | 50 mv                  |

|           | Optional<br>- 7 to -16 VDC<br>(Cut Trace 'L') | NA        | 0.10 A Max<br>0.07 A Typ | NA                     |

| 5         | + 5 VDC                                       | ±0.25 VDC | 1.0 A Max<br>0.8 A Typ   | 50 mv                  |

| 6         | + 5 V Return                                  |           |                          |                        |

- \*The +24 VDC power requires a separate ground return line. Also, the +24V Return, other Ground Return lines, and Frame Ground must be connected together at the main power supply.

- \*\*If either customer installable option described in sections 7.2 and 7.4 are used, the current requirement for the +24 VDC is a multiple of the maximum +24V current times the number of drives on the line.

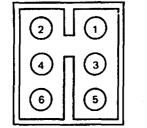

# 5.0 PHYSICAL INTERFACE

The electrical interface between the SA800/801 and the host system is via three connectors. The first connector, J1, provides the signal interface; the second connector, J5, provides the DC power; and the third connector, J4, provides the AC power and frame ground.

This section describes the physical connectors used on the drive and the recommended connectors to be used with them. Refer to Figure 16 for connector locations.

# 5.1 J1/P1 Connector

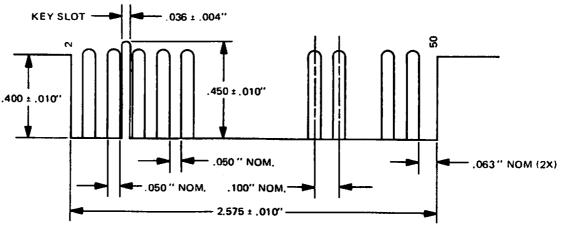

Connection to J1 is through a 50 pin PCB edge card connector. The dimensions for this connector are shown in Figure 13. The pins are numbered 1 through 50 with the even numbered pins on the component side of the PCB and the odd numbered pins on the non-component side. Pin 2 is located on the end of the PCB connector closest to the AC motor capacitor and is labeled 2. A key slot is provided between pins 4 and 6 for optional connector keying.

The recommended connectors for P1 are tabulated below.

| TYPE OF CABLE                          | MANUFACTURER    | CONNECTOR P/N | CONTACT P/N                           |

|----------------------------------------|-----------------|---------------|---------------------------------------|

| Twisted Pair, #26<br>(crimp or solder) | АМР             | 1-583717-1    | 583616-5 (crimp)<br>583854-3 (solder) |

| Twisted Pair #26<br>(solder term.)     | VIKING          | 3VH25/1JN-5   | NA                                    |

| Flat Cable                             | 3M "Scotchflex" | 3415-0001     | NA                                    |

BOARD THICKNESS .062 ± .007 "

Figure 13. J1 Connector Dimensions

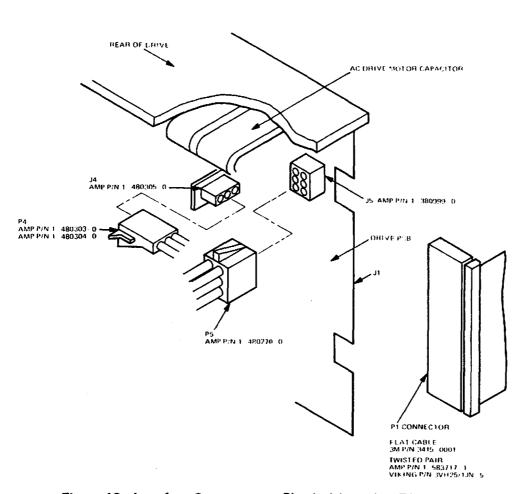

# 5.2 J5/P5 Connector

The DC power connector, J5, is mounted on the non-component side of the PCB and is located below the AC motor capacitor. J5 is a 6 pin AMP Mate-N-Lok connector P/N 1-380999-0. The recommended mating connector (P5) is AMP P/N 1-480270-0 utilizing AMP pins P/N 60619-1. J5 pins are labeled on the component side of the PCB with pin 5 located nearest J1/P1. Figure 14 illustrates J5 connector as seen on the drive PCB from non-component side.

### 5.3 J4/P4 Connector