# **RUX50** Controller

### **Technical Manual**

digital

.

EK-RUX50-TM-001

## **RUX50** Controller

**Technical Manual**

Prepared by Educational Services of Digital Equipment Corporation First Edition, October 1984

Copyright © 1984 by Digital Equipment Corporation. All Rights Reserved.

Printed in U.S.A.

The reproduction of this material, in part or whole, is strictly prohibited. For copy information, contact the Educational Services Department, Digital Equipment Corporation, Maynard, Massachusetts Ø1754.

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

IBM is a trademark of International Business Machines Corporation.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts.

| digital      | DIGITAL      | RSTS           |

|--------------|--------------|----------------|

| DECmate      | MASSBUS      | RSX            |

| DECnet       | Micro/PDP-11 | UNIBUS         |

| DECsystem-10 | PDP          | VAX            |

| DECSYSTEM-20 | P/OS         | VMS            |

| DECUS        | Professional | VT             |

| DECwriter    | Q-Bus        | Work Processor |

| DIBOL        | Rainbow      |                |

#### CONTENTS

| CHAPTER 1                                                               | L | INTRODUCTION                                                                                                                                                                                                                                                    |                                                                                    |

|-------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 1.1<br>1.2<br>1.3<br>1.4                                                |   | General Information<br>Related Documentation<br>General Description<br>Features                                                                                                                                                                                 | 1-1<br>1-2<br>1-2<br>1-2                                                           |

| CHAPTER 2                                                               | 2 | CONFIGURATION AND INSTALLATION                                                                                                                                                                                                                                  |                                                                                    |

| 2.1<br>2.2<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.4   |   | Introduction<br>Subsystem Configurations<br>Jumper Configurations<br>Device Address Selection<br>Logical Unit Number Selection<br>Device Type Selection<br>Interrupt Request Level<br>Long- or Short-Line Selection<br>Subsystem Installation                   | $\begin{array}{c} 2-1\\ 2-1\\ 2-2\\ 2-2\\ 2-4\\ 2-4\\ 2-4\\ 2-4\\ 2-6 \end{array}$ |

| CHAPTER 3                                                               | 3 | THEORY OF OPERATION                                                                                                                                                                                                                                             |                                                                                    |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1 |   | Introduction<br>Circuit Overview<br>UNIBUS Interface Circuits<br>T-11 Processor Circuits<br>DMA Control Circuits<br>Diskette Drive Controller Circuits<br>Circuit Details<br>UNIBUS Interface Circuits<br>UNIBUS Address Transceivers/Address                   | 3-1<br>3-1<br>3-3<br>3-3<br>3-4<br>3-4<br>3-4                                      |

| 3.3.1.2<br>3.3.1.3<br>3.3.1.4<br>3.3.1.5<br>3.3.1.6<br>3.3.2<br>3.3.2.1 |   | Match Detector<br>UNIBUS Data Buffer/Transceivers<br>UNIBUS Control Transceivers<br>PIO Read/Write SA Registers<br>MSCP PIO Controller/IP Register<br>Interrupt Controller and Vector Register<br>T-11 Processor Circuits<br>Interrupt Request, Initialize, and | 3-6<br>3-6<br>3-6<br>3-6<br>3-7<br>3-7<br>3-7                                      |

|                                                                         |   | Asychronous Hold Registers                                                                                                                                                                                                                                      | 3-7                                                                                |

| 3.3.2.2<br>3.3.2.4<br>3.3.2.5<br>3.3.2.6<br>3.3.3<br>3.3.3.1<br>3.3.3.2<br>3.3.4<br>3.3.4.1<br>3.3.4.2<br>3.3.4.3<br>3.3.4.4                                                       | T-ll Microprocessor, Mode buffer, Address<br>Latch, I/O Bit Map, and Memory Decoder<br>RAM and ROM<br>Display Register and LEDS<br>Device Type Register<br>LUN Register<br>DMA Control Circuits<br>DMA Controller, Timers, and Data Buffer<br>CSRs<br>UNIBUS DMA Address Pointer/Buffer and<br>UNIBUS Address Extension Register<br>Diskette Drive Controller Circuits<br>Diskette Drive CSR and Data CSR<br>Diskette Drive Controller<br>Diskette Drive Controller<br>Diskette Drive Controller | 3-11<br>3-11<br>3-11<br>3-11<br>3-11<br>3-13<br>3-13<br>3-13 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| CHAPTER 4                                                                                                                                                                          | INTERCONNECTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                              |

| 4.1<br>4.2<br>4.3                                                                                                                                                                  | Introduction<br>UNIBUS Connector<br>Drive Interface Connector Jl                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                              |

| CHAPTER 5                                                                                                                                                                          | TROUBLESHOOTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                              |

| 5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.2.1<br>5.3.2.1<br>5.3.3.1<br>5.3.3.1<br>5.3.3.1<br>5.3.3.1<br>5.3.4.1<br>5.3.4.2<br>5.3.4.2<br>5.3.4.3<br>5.3.4.5<br>5.3.4.5<br>5.3.4.7 | Introduction<br>Self-Test<br>Diagnostics<br>Initialization Test<br>Initialization Drop Unit Summary<br>Performance Exerciser<br>Performance Exerciser Drop Unit Summary<br>Operating Instructions<br>Hardware Configuration Questions<br>Software Parameter Questions<br>Diagnostic Error Reporting<br>Initialization Errors<br>Performance Exerciser Errors<br>Errorlog Messages<br>MSCP Errors<br>Sample Error Message<br>Performance and Progress Reports<br>Error Codes                      | 5-12<br>5-12<br>5-12<br>5-12<br>5-13<br>5-13                 |

| CHAPTER 6                                                                                                                                                                          | PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                              |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.3<br>6.4<br>6.4.1                                                                                                                                | Introduction<br>Control Protocols<br>Mass Storage Control Protocol<br>Diagnostics and Utilities Protocol<br>Bus Protocols<br>Programmable Registers<br>IP Register                                                                                                                                                                                                                                                                                                                               | 6-1<br>6-1<br>6-2<br>6-2<br>6-3<br>6-3                       |

| 6.4.2<br>6.5<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.5.5<br>6.5.6<br>6.5.7<br>6.5.8<br>6.5.9<br>6.5.10<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.13<br>6.5.14<br>6.5.15<br>6.5.16<br>6.5.17<br>6.5.18<br>6.5.19<br>6.5.19<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.12<br>6.5.20<br>6.5.21<br>6.5.22<br>6.5.23<br>6.5.23<br>6.5.24 | SA Register<br>Internal Hardware Registers<br>Load Interrupt Vector<br>Load System Display<br>Load UNIBUS Pointer<br>Load UNIBUS Extension<br>Clear DMA Error Flags<br>Load Drive CSR<br>Load Transmitter Buffer<br>Load Data CSR<br>Diskette Drive Controller Write Command<br>Diskette Drive Controller Write Sector<br>Diskette Drive Controller Write Sector<br>Diskette Drive Controller Write Data<br>Diagnostic Interrupt<br>Interrupt UNIBUS<br>Read PIO Status/Address<br>Read Receive Buffer<br>Read LUN<br>Read Drive CSR<br>Read Drive CSR<br>Read Drive CSR<br>Read Drive CSR<br>Read Drive CSR<br>Diskette Drive Controller Read Status<br>Diskette Drive Controller Read Status | -33355566666777777777788999999                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| CHAPTER 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.6.1<br>7.6.2<br>7.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Introduction<br>Physical Specification<br>Electrical Specifications<br>Environmental Specifications<br>Operating Characteristics<br>Data Formats<br>Digital's Data Format<br>Alternate Data Format<br>Supported Drives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-1<br>7-1<br>7-1<br>7-2<br>7-2<br>7-2<br>7-2<br>7-2<br>7-2<br>7-4 |

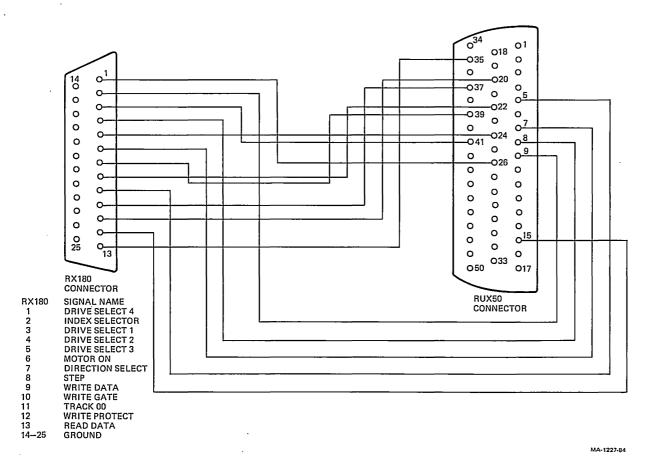

| APPENDIX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RX18Ø CABLING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    |

| FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |

| 2-1<br>2-2<br>2-3<br>3-1<br>3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RUX50 Jumper Locations<br>RUX50 Subsystem Installation<br>Long-Line Adapter Installation<br>RUX50 Circuits<br>UNIBUS Interface Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-3<br>2-7<br>2-7<br>3-2<br>3-5                                    |

3-3T-ll Processor Circuit3-83-4DMA Control Circuits3-123-5Diskette Drive Controller Circuit3-134-1Connector Jl Pin Functions4-6

.

| 6-1 | Device Type Register  | 6-8 |

|-----|-----------------------|-----|

| 7-1 | Digital's Data Format |     |

| 7–2 | Alternate Data Format |     |

| 7-3 | Supported Drives      | 7-4 |

| A-1 | RX180 Cabling         | A-1 |

#### TABLES

| 2-1 | Subsystem Configurations                 | 2-1  |

|-----|------------------------------------------|------|

| 2-2 | Device Address Jumper Configuration      | 2-2  |

| 2-3 | Logical Unit Number Jumper Configuration | 2-5  |

| 2-4 | Device Type Jumper Configuration         | 2-5  |

| 4-1 | UNIBUS Signal Pin Assignments            | 4-2  |

| 4-2 | UNIBUS Signal Descriptions               | 4-3  |

| 4-3 | Drive Interface Signals                  |      |

| 5-1 | Self-Test Sequence                       | 5-2  |

| 5-2 | Generic Error Code Definitions           | 5-3  |

| 53  | Error Codes Generated by ZRQA Exerciser  | 5-14 |

| 6-1 | Hardware Register Definitions            | 6-4  |

.

CHAPTER 1 INTRODUCTION

#### 1.1 GENERAL INFORMATION

This manual describes the configurations, installation, and operation of the RUX50 controller module as a diskette drive subsystem. The manual identifies associated diskette drives, but it does not describe them in detail.

- Chapter 1 briefly describes the RUX50 and presents its features.

- Chapter 2 tells how to configure and install the RUX50 as a subsystem.

- Chapter 3 describes the RUX50's operation.

- Chapter 4 provides detailed information on the RUX50 connectors.

- Chapter 5 covers troubleshooting. It explains how to interpret errors detected by the RUX50's self-test and diagnostics.

- Chapter 6 describes the programmable registers that are UNIBUS addressable on the RUX50. It briefly covers mass storage control protocol (MSCP) and diagnostics and utilities protocol (DUP). To give you a better understanding of the RUX50's operation, Chapter 6 also describes the internal hardware registers.

- Chapter 7 lists environmental and functional specifications for the RUX50 as well as data formats and supported drive characteristics.

#### 1.2 RELATED DOCUMENTATION

The following documents provide more information on the RUX50.

| Title                                                           | Number      |

|-----------------------------------------------------------------|-------------|

| RUX50 Field Maintenance Print Set                               | MPØ2ØØ6     |

| UDA50 Programmer's Documentation Kit                            | QP-905-GZ   |

| RX5Ø-D, -R Dual Flexible Disk Drive<br>Subsystem Owner's Manual | EK-LEPØ1-OM |

For extra information, refer to documentation for the system in which the RUX50 is installed.

#### 1.3 GENERAL DESCRIPTION

The RUX50 (M7522) is a UNIBUS controller for 5-1/4-inch diskette drives. It is a quad-size, single-board controller that recognizes a subset of MSCP.

The RUX50 interfaces RX50 diskette drives to any hex-size backplane that implements an 18-bit/16-bit UNIBUS. It also supports other drives:

Single-density, single-sided, dual diskette drives Single-density, double-sided, single diskette drives Double-density, double-sided, single diskette drives.

#### 1.4 FEATURES

The RUX50 has the following features.

- Is a single, quad-size module.

- Supports direct memory access (DMA) data transfers in 18-bit/16-bit addressing modes.

- Supports 18-bit addressing on a UNIBUS.

- Interfaces up to four logical units.

- Implements drives other than Digital Equipment Corporation's.

- Is compatible with Micro/PDP-11 and Professional RX50 diskettes.

#### CHAPTER 2 CONFIGURATION AND INSTALLATION

#### 2.1 INTRODUCTION

The RUX50 is a direct memory access (DMA) device that mounts in any small peripheral controller (SPC) slot of the UNIBUS backplane. A single RUX50 interfaces up to four logical units to the host processor. The RUX50 must conform to valid subsystem (Paragraph 2.2), jumper (Paragraph 2.3), and cabling configurations (Paragraph 2.4).

The RX50 diskette drive is a random access storage device that uses two single-sided, 133.4-mm (5-1/4-in) RX50K diskettes. The total storage capacity of the RX50 is 800 kilobytes of formatted data.

#### **2.2** SUBSYSTEM CONFIGURATIONS

Typically, the RUX50 interfaces one or two RX50s to the host system. Each RX50 is two logical units. The device type jumpers (Paragraph 2.3) must be set for each logical unit attached to the RUX50. Table 2-1 lists acceptable RUX50 subsystems. Dual diskette drives must start on the first and third logical unit boundaries assigned to the RUX50 (Paragraph 2.3.2).

| Configuration | Number and Type of<br>Diskette Drives         | Logical Diskette<br>Drive Numbers         |

|---------------|-----------------------------------------------|-------------------------------------------|

| 1             | One RX5Ø                                      | Units $\emptyset$ , 1 = RX5 $\emptyset$   |

| 2             | Two RX5Øs                                     | Units Ø, 1 = RX5Ø<br>Units 2, 3 = RX5Ø    |

| 3             | One single logical unit<br>drive              | Unit Ø = single unit                      |

| 4             | One RX5Ø and one single<br>logical unit drive | Units Ø, 1 = RX5Ø<br>Unit 2 = single unit |

Table 2-1 Subsystem Configurations

#### 2.3 JUMPER CONFIGURATIONS

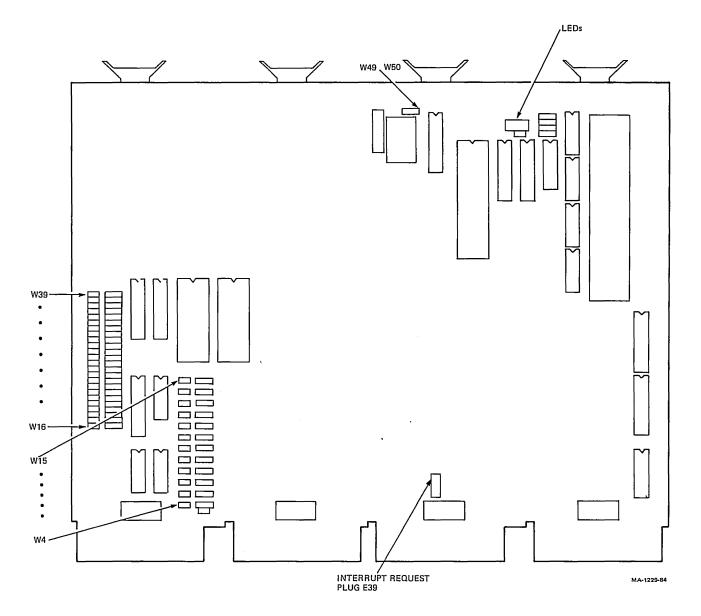

To change the RUX50's device address, logical unit number, device type, logical location, and long- or short-line transmission from their standard settings, reconfigure the jumpers on the RUX50. Figure 2-1 shows the jumper locations.

#### 2.3.1 Device Address Selection

Figure 2-1 shows the location of the RUX50 address jumpers. Table 2-2 lists the jumper configuration for the standard address, 772150. To configure the RUX50 for an address other than 772150, use Table 2-2 to determine the appropriate configuration for address bits A2 through A13 on jumpers W4 through W15.

| Jumper            | UNIBUS<br>Address<br>Bit | Standard<br>77215Ø<br>State | Standard Standard<br>Binary Octal<br>State State                                                                                        |

|-------------------|--------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| W4                | A2                       | in                          |                                                                                                                                         |

| W5<br>W6<br>W7    | A3<br>A4<br>A5           |                             | $\begin{array}{c} 0 \\ H \\ 0 \\ 1 \\ - \\ 0 \\ 1 \\ - \\ \end{array} \begin{array}{c} 5 \\ 5 \\ 5 \\ 5 \\ 5 \\ 5 \\ 5 \\ 5 \\ 5 \\ 5 $ |

| W8<br>W9<br>W1Ø   | A6<br>A7<br>A8           | in                          | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                    |

| W11<br>W12<br>W13 | A9<br>A1Ø<br>A11         | in r<br>out r<br>in H       |                                                                                                                                         |

| W14<br>W15        | A12<br>A13               | out rout o                  | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                    |

ΙΧ

#### Table 2-2 Device Address Jumper Configuration

Figure 2-1 RUX50 Jumper Locations

#### 2.3.2 Logical Unit Number Selection

Figure 2-1 shows the location of the RUX50's logical unit number (LUN) jumpers. Set these jumpers to the lowest LUN assigned to any diskette drive controlled by the RUX50. The standard configuration for the LUN jumpers is 0. Use Table 2-3 to configure the RUX50 for its LUN.

#### 2.3.3 Device Type Selection

Sixteen jumpers identify each device connected to the RUX50. These jumpers are standardly configured for the RX50. They are organized in four groups of four jumpers. The RUX50 supports four logical units, so each jumper group defines the device for each logical unit. Dual logical units must occupy the first or third jumper group. Single logical units can occupy any jumper group as long as the dual logical units have the first or third. Table 2-4 defines the jumper states for various drive types. (Refer to the appendix for drive type descriptions.)

#### 2.3.4 Interrupt Request Level

The RUX50 interrupts at priority level 5, which is determined by the interrupt request plug in E39. Figure 2-1 shows E39 on the module.

#### 2.3.5 Long- or Short-Line Selection

The RUX50 supports drive cable configurations that are long and short. A long-line configuration (standard) allows 40 ft (maximum) or less of cable between the RUX50 and the drive. A short-line configuration allows 10 ft (maximum) or less of cable between the RUX50 and the drive.

Install jumper W49 for long-line configurations and jumper W50 for short-line configurations.

NOTE For most applications, the long-line configuration is typical. If the total cable length between the RUX50 and drive is less than 10 ft, you can use the short-line configuration.

| First<br>Logical | Jumpe | er Stat | tes |     |     |     |     |     |  |

|------------------|-------|---------|-----|-----|-----|-----|-----|-----|--|

| Unit             | W32   | W33     | W34 | W35 | W36 | W37 | W38 | W39 |  |

| Ø                | out   | out     | out | out | out | out | out | out |  |

| 1                | out   | out     | out | out | out | out | out | in  |  |

| 2                | out   | out     | out | out | out | out | in  | out |  |

| 3                | out   | out     | out | out | out | out | in  | in  |  |

| 4                | out   | out     | out | out | out | in  | out | out |  |

| 5                | out   | out     | out | out | out | in  | out | in  |  |

| б                | out   | out     | out | out | out | in  | in  | out |  |

| 7                | out   | out     | out | out | out | in  | in  | in  |  |

| 8                | out   | out     | out | out | in  | out | out | out |  |

| • • •            |       |         |     |     |     |     |     |     |  |

| 255              | in    | in      | in  | in  | in  | in  | in  | in  |  |

| Table 2-3 | Logical | Unit | Number | Jumper | Configuration |

|-----------|---------|------|--------|--------|---------------|

|-----------|---------|------|--------|--------|---------------|

Table 2-4 Device Type Jumper Configuration

| Jumper | Bit | Logical Unit<br>Location | Jumper<br>1 | States<br>2 | for Devi<br>3 | .ce Type<br>4 |

|--------|-----|--------------------------|-------------|-------------|---------------|---------------|

| W31    | Ø   | First                    | in          | out         | in            | out           |

| W3Ø    | 1   | First                    | out         | in          | in            | out           |

| W29    | 2   | First                    | out         | out         | out           | in            |

| W28    | 3   | First                    | out         | out         | out           | out           |

| W27    | ø   | Second                   | in          | out         | in            | out           |

| W26    | 1   | Second                   | out         | in          | in            | out           |

| W25    | 2   | Second                   | out         | out         | out           | in            |

| W24    | 3   | Second                   | out         | out         | out           | out           |

| W23    | Ø   | Third                    | in          | out         | in            | out           |

| W22    | 1   | Third                    | out         | in          | in            | out           |

| W21    | 2   | Third                    | out         | out         | out           | in            |

| W2Ø    | 3   | Third                    | out         | out         | out           | out           |

| W19    | Ø   | Fourth                   | in          | out         | in            | out           |

| W18    | 1   | Fourth                   | out         | in          | in            | out           |

| W17    | 2   | Fourth                   | out         | out         | out           | in            |

| W16    | 3   | Fourth                   | out         | out         | out           | out           |

Legend

Single-sided, dual drive or RX50 (96 tracks per inch) Single-sided, dual drive (48 TPI) Double-sided, single drive (96 TPI) Double-sided, single drive (48 TPI) 1

2

3

4

.

#### 2.4 SUBSYSTEM INSTALLATION

Install the RUX50 (M7522) in any slot of the UNIBUS backplane. Follow these rules when installing the RUX50 into the UNIBUS backplane.

- After installing the RUX50, make sure all empty slots have a grant card (PN G727 or G7273).

- Remove the nonprocessor request (NPR) grant jumper for the slot containing the RUX50 from the backplane.

Before installing the RUX50, make sure its jumpers for device address, logical unit number, device type, logical location, and long- or short-line transmission are configured correctly (Paragraph 2.3).

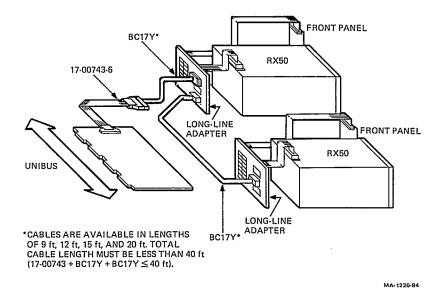

The RUX50 subsystem consists of the controller module, the signal cable to the interconnect panel, and the long-line adapter that installs in the diskette drive. Figure 2-2 shows a typical subsystem.

Connect the 50-conductor signal cable (PN 17-00743-06) to the Jl connector on the RUX50. Connect the other end of this cable to the signal distribution panel in the host cabinet.

NOTE

FCC cabinets already have the mounting bracket and interconnect panel. For other cabinets, install a mounting bracket (PN 74-27292) if necessary.

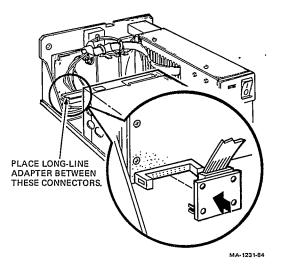

For all long-line configurations, install the long-line adapter in the diskette drive (Figure 2-3). The adapter goes between the drive's interconnect panel and flat ribbon cable. Four jumpers are on the long-line adapter (Wl, W2, W3, and W4). Jumper Wl is always removed for RX50s. Jumpers W2, W3, and W4 are installed when the diskette drive is the last unit or a single unit for daisychained diskette drives. Remove all the jumpers if the drive is the center unit in a daisychain configuration.

Figure 2-2 RUX50 Subsystem Installation

Figure 2-3 Long-Line Adapter Installation

#### CHAPTER 3 THEORY OF OPERATION

#### 3.1 INTRODUCTION

This chapter gives a general description of how the circuits on the RUX50 function. Then it gives a detailed description of each circuit.

#### 3.2 CIRCUIT OVERVIEW

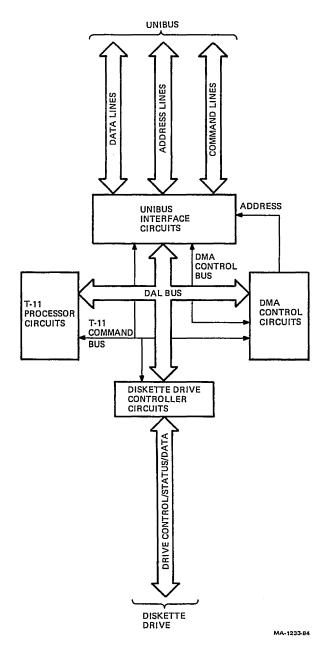

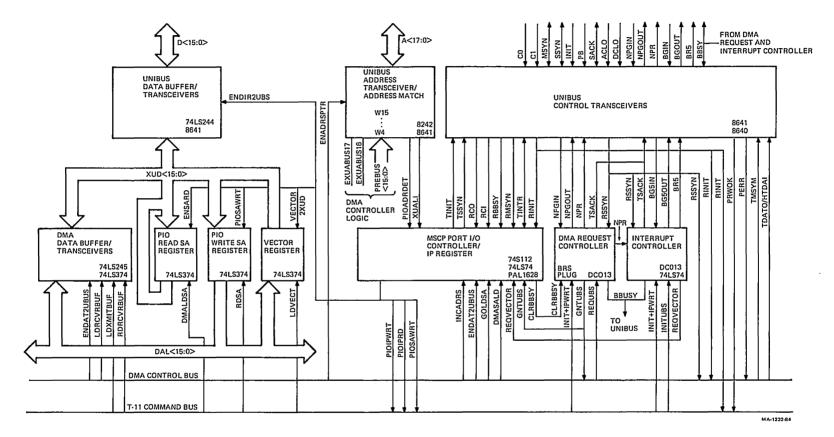

The RUX50 has four major circuit functions that interface 5-1/4-inch diskette drives to the UNIBUS. These circuits interact to store and retrieve data between the UNIBUS controller (host processor) and the diskette drives. Figure 3-1 shows these circuits.

UNIBUS interface circuits T-ll processor circuits DMA control circuits Diskette drive controller circuits

#### 3.2.1 UNIBUS Interface Circuits

These circuits (Figure 3-1) contain the MSCP registers and the UNIBUS interfacing circuits required by a SPC UNIBUS device. They perform the following standard UNIBUS operations.

- Initialize the entire RUX50 via an initialization and poll (IP) write.

- Initiate the RUX50 to start polling via a IP read.

- Read and write the status and address (SA) register from the UNIBUS.

- Enable the vector address onto the UNIBUS data lines.

- Perform DMA request handshaking between the UNIBUS and DMA control circuits.

•

Figure 3-1 RUX50 Circuits

#### 3.2.2 T-ll Processor Circuits

These circuits (Figure 3-1) control the operation of the RUX50. They contain the microcode that interprets and responds to the MSCP accesses that the RUX50 receives from the UNIBUS interface circuits. The T-11 processor circuits perform the following standard operations.

- Read and write the SA register from T-ll memory.

- Load the vector register in the UNIBUS interface circuits from T-ll memory.

- Initialize the RUX50 when the UNIBUS interface circuits detect a IP write. This function includes the following operations.

T-ll runs preliminary diagnostics.

T-ll reads the SA write register for the length of the MSCP command/response rings and the interrupt enabling, and places this data in the RUX50's RAM.

T-ll writes the SA read register with its command and ring lengths.

T-ll then reads the SA write register for ring base low and ring base high starting addresses.

- For DMA accesses, the T-ll processor circuits move data between the DMA data buffer register in the UNIBUS interface circuits and T-ll memory.

- T-ll reads and writes the drive control and status register (CSR) in the diskette drive controller circuits.

- T-ll reads and writes between the diskette drive controller chip (WD1793) and the T-ll or T-ll memory.

#### 3.2.3 DMA Control Circuits

These circuits (Figure 3-1) interact with the UNIBUS interface and T-11 processor circuits to perform DMA transfers between the host's main memory and T-11 memory. To perform this function, the DMA control circuits do the following operations.

- Initiate and monitor DMA transfer requests to the UNIBUS interface circuits.

- Generate bus and data transfer synchronization signals for the UNIBUS interface circuits.

- Provide DMA status information on request to the T-ll processor circuits.

- Provide memory address for DMA transfer to the UNIBUS interface circuits.

#### 3.2.4 Diskette Drive Controller Circuits

The T-ll processor circuits control the diskette drive controller circuits (Figure 3-1) to access the diskette drives. To perform this function, these circuits do the following operations.

- Receive control information from the T-ll for the drives.

- Receive status information from the drives for the T-ll.

- Convert data in T-11 memory to diskette drive formatted data and send it to the drive.

- Retrieve diskette drive formatted data from the drive and convert it to 8-bit words for T-ll memory.

#### 3.3 CIRCUIT DETAILS

This section describes the RUX50's basic architecture and data path relationships for each major circuit function. Figure 3-1 shows that the RUX50 is a bus-oriented subsystem. The host system controls the subsystem, and the T-11 processor and DMA control circuits share it.

#### 3.3.1 UNIBUS Interface Circuits

These circuits (Figure 3-2) consist of the following components.

UNIBUS address transceivers/address match detector UNIBUS data buffer/transceivers UNIBUS control transceivers Port input/output (PIO) read/write SA registers PIO controller/IP register DMA request controller Interrupt controller DMA data buffer/transceivers Vector register

Figure 3-2 UNIBUS Interface Circuit

3.3.1.1 UNIBUS Address Transceivers/Address Match Detector --This circuit compares the jumpered address to the UNIBUS address. When an address match occurs (indicating an SA or IP read/write), this circuit asserts PIOADRDET. PIOADRDET alerts the PIO controller to enable the appropriate data paths and interrupts in the RUX50.

This circuit also receives the UNIBUS DMA address (PREBUS<15:0>) and UNIBUS address extension (EXUABUS<17:16>) from the DMA control circuits. The DMA control signal ENADRSPTR enables this address onto the UNIBUS address lines.

3.3.1.2 UNIBUS Data Buffer/Transceivers -- This circuit is 16 bits wide and passes data between the UNIBUS and the XUD bus. It is enabled by the DMA controller (through the pio controller) or by the PIO controller during MSCP accesses.

3.3.1.3 UNIBUS Control Transceivers -- The UNIBUS control transceivers buffer and transfer the UNIBUS control signals between the UNIBUS controller (host processor) and the RUX50.

3.3.1.4 PIO Read/Write SA Registers -- These SA registers are used by the T-11 and the UNIBUS processor (host computer) for the MSCP port initialization sequence. These registers occupy the same UNIBUS I/O page address. The SA write register is written by the UNIBUS processor and read by the T-11. The SA read register is written by the T-11 and read by the UNIBUS processor. During the initialization sequence, the UNIBUS controller writes the MSCP command buffer address and interrupt vector to the SA write register for the T-11. The T-11 writes the SA read register with the initialization status data for the UNIBUS processor. The SA read and write registers are both 16 bits wide.

3.3.1.5 MSCP PIO Controller/IP Register -- This circuit performs the following functions simultaneously.

- It detects MSYN and sends SSYN to or from the UNIBUS control transceivers after the host processor receives or sends data.

- The PIO control logic also enables output and direction of the UNIBUS data transceiver.

- The PIO controller decodes the type of transfer by the CØ and Cl signals for an IP read, IP write, SA read, or SA write.

After the UNIBUS address transceivers/address match detector detects a valid address, the PIO controller/IP register loads the SA write register from the UNIBUS or enables the SA read register to the UNIBUS.

After receiving a request signal from the interrupt controller (REQVECTOR), the PIO controller gates the vector from the vector register the UNIBUS through the UNIBUS data onto buffer/transceivers and the UNIBUS interrupt signal (TINTR) through the UNIBUS control transceivers. The PIO controller sends interrupt signals (PIOIPWRT, PIOIPRD, PIOSAWRT) to the T-11 processor circuits whenever the host processor reads or writes the SA or IP registers.

3.3.1.6 Interrupt Controller and Vector Register -- The interrupt vector register contains the vector that is gated to the UNIBUS during an interrupt sequence. The MSCP initialization sequence supplies the T-11 with the vector. The T-11 then loads the interrupt vector register. The contents of this register transfers to the UNIBUS under control of the interrupt controller (via the PIO controller). The vector register is 8-bits wide and ranges in value from  $\emptyset$  to 774. The normal interrupt vector is 154 and the priority level is 5.

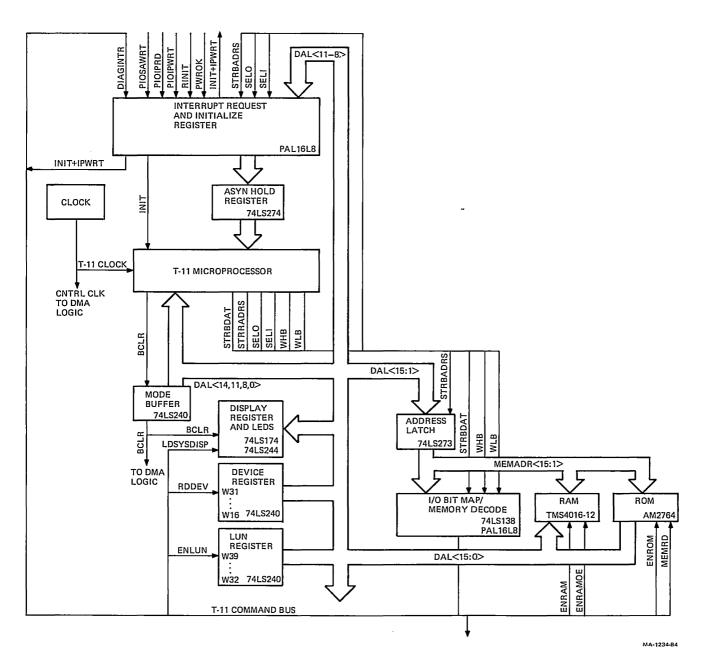

#### 3.3.2 T-ll Processor Circuits

These circuits (Figure 3-3) consist of the following components.

Interrupt, request, initialize, and asynchronous hold registers T-ll microprocessor Mode buffer Address latch I/O bit map and memory decode Random access memory (RAM) Read-only memory (ROM) Display register and light emitting diodes (LEDs) Device register LUN register

3.3.2.1 Interrupt Request, Initialize, and Asynchronous Hold Registers -- The interrupt request register performs conditional priority on interrupt requests to the T-11. It stores the results in the asynchronous holding register (AHR) every T-11 column address strobe (CAS) cycle. The output of the AHR goes directly into the T-11 interrupt port.

The initialize register monitors the UNIBUS AC LO and DC LO (PWROK) signals to determine when to perform power-up or power-down functions. The register also begins an initialization sequence when the host processor writes to the IP register or during UNIBUS initialization.

Figure 3-3 T-11 Processor Circuit

3.3.2.2 T-11 Microprocessor, Mode Buffer, Address Latch, I/O Bit Map, and Memory Decoder -- The supervisory control of the RUX50 is done by the T-11 with an input clock frequency of 7.5 MHz. During a power-up sequence, the initialize register (Paragraph 3.3.2.1) configures the T-11 for the 16-bit mode and enables the T-11 to use static RAM.

The address latch latches the T-ll memory address onto the memory address lines (MAL) during the address phase of the bus cycle. This allows the T-ll to point to any specific location in the ROM, RAM, or I/O bit map memory decoder. The I/O bit map and memory decoder enables and loads all the registers and devices that the T-ll can access.

The T-ll performs the following operations.

- Sends the host processor status information through the DMA data buffer register. The DMA controller moves data from the DMA data buffer to the SA read register. If prior to the T-11 loading the DMA data buffer register, the T-11 sets the GOLDSA flag in the DMA data buffer.

- 2. Reads the host processor's status information through the SA write register.

- 3. After receiving the host vector address from the SA write register during port initialization, the T-11 loads the vector address into the vector register.

- 4. The T-ll initiates an interrupt to the host processor when the T-ll finishes performing the instructions in the host command ring in T-ll RAM. This happens if interrupts were enabled during port initialization.

- 5. Reads and writes the drive CSR and reads the LUN and device type register.

- 6. Reads and writes all data from or to the diskette drive controller chip from T-11 RAM.

- 7. Interaction between the T-ll and the DMA control circuits brings host command rings and data to be written to the drives into T-ll RAM.

- a. The T-11 loads the source UNIBUS address into the UNIBUS address registers. The DMA state machine increments these registers after each word transfer.

- b. The T-11 then polls the DMADONE bit in the DMA data buffer CSR (DDBCSR).

- c. If the DMADONE bit is set, the T-11 sets the GODMAFUBS bit in the DDBCSR, which initiates the DMA control circuits to get a word from host memory referenced from the UNIBUS DMA address pointer.

- d. The T-11 then polls the RCVRFUL bit in the DDBCSR. If this is set, the T-11 writes the contents of the DMA data buffer register into the T-11 RAM.

- e. The T-11 then checks its internal word counter to determine if it should repeat the process. If the internal word counter is not equal to the number of words of a particular transfer, then the T-11 increments its internal T-11 word counter and repeats steps b through e until the end of a particular transfer.

- Interaction between the T-ll and the DMA control circuits brings RUX50 response rings and data from the drives to T-ll RAM for transfer to host memory.

- a. The T-ll loads the destination UNIBUS address into the UNIBUS address registers. The DMA state machine increments these registers after each word transfer.

- b. The T-11 then polls the XMITFUL bit in the DMA data buffer CSR (DDBCSR).

- c. If the DMA data buffer is empty (XMITFUL = Ø), then the T-11 loads the DMA data buffer register with the data to be transferred to the host memory from T-11 RAM. The loading of the DMA data buffer initiates the DMA controller to transfer the word from the DMA data buffer register to the host memory referenced from the UNIBUS DMA address pointer.

- d. The T-ll then checks its internal word counter to determine if it should repeat the process. If the internal word counter is not equal to the number of words of a particular transfer, then the T-ll increments its internal T-ll word counter and repeats steps b through d until the end of a particular transfer.

3.3.2.3 RAM and ROM -- The 8K X 16 RAM has three major sections.

T-ll work space Device control block Sector buffer

The T-11 address space allocated to the RAM lies between 100000 and 120000 (octal). The 8K  $\times$  16 PROM just stores the T-11 instructions. Its T-11 address space lies between 000000 and 020000.

3.3.2.4 Display Register and LEDs -- T-ll processor circuits load the display register. This register controls the LEDs that show the RUX50's status.

3.3.2.5 Device Type Register -- The device type register is a jumper-configured, 16-bit register. It indicates the type of drive for each of the four logical units attached to the RUX50. (See Paragraphs 2.3.3 and 6.5.18 for details.)

3.3.2.6 LUN Register -- The LUN register is an 8-bit jumper-configured register. The T-11 reads this register. (See Paragraphs 2.3.2 and 6.5.17 for details.)

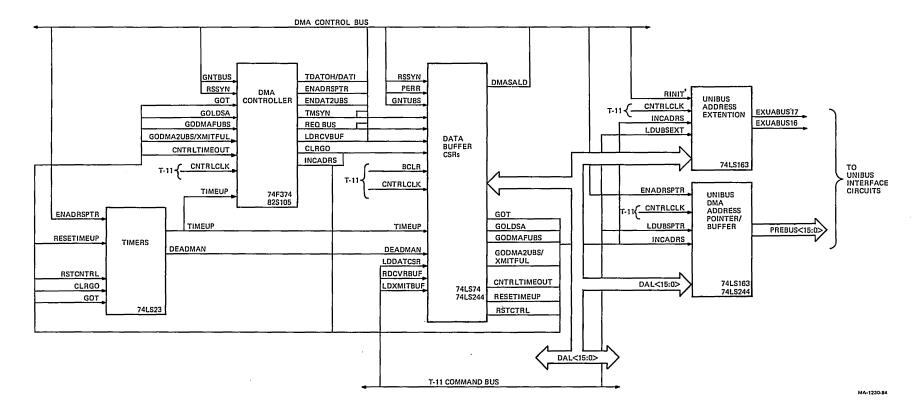

#### 3.3.3 DMA Control Circuits Detail

The DMA control circuits (Figure 3-4) are made up of the following components.

DMA controller

Timers

Data buffer CSRs

UNIBUS DMA address pointer/buffer and UNIBUS address extension register

3.3.3.1 DMA Controller, Timers, and Data Buffer CSRs -- The DMA controller, when enabled, controls the UNIBUS DMA address pointer, UNIBUS address extention register, and the UNIBUS address and data transceivers. It also controls the loading of the SA read register, the DMA data buffer, and the DMA data buffer CSR. It operates with a 15-MHz clock input. In a DMA read, the source of the data is the DMA data buffer register and the destination of the data is the host memory. Similarly, in a write, the source of the data is the host memory and the destination of the data buffer.

The data transfer occurs as an NPR operation and obeys the UNIBUS DMA protocol. DMA transfers occur in one word transfers per bus acquisition. The DMA controller sets error flags and process complete flags in the DMA data buffer CSR after it does a DMA.

Figure 3-4 DMA Control Circuits

3.3.3.2 UNIBUS DMA Address Pointer/Buffer and UNIBUS Address Extension Register --The UNIBUS DMA address pointer/buffer and UNIBUS address extension register consists of five loadable T-11 loads the beginning UNIBUS addresses into the The counters. address extension DMA counters. The T-11 loads the before extended address The extended operation if an is necessary. incremented if a transfer occurs across a 16-bit address is boundary. The output of these buffers goes to the UNIBUS interface circuit and is placed on the UNIBUS by the DMA controller.

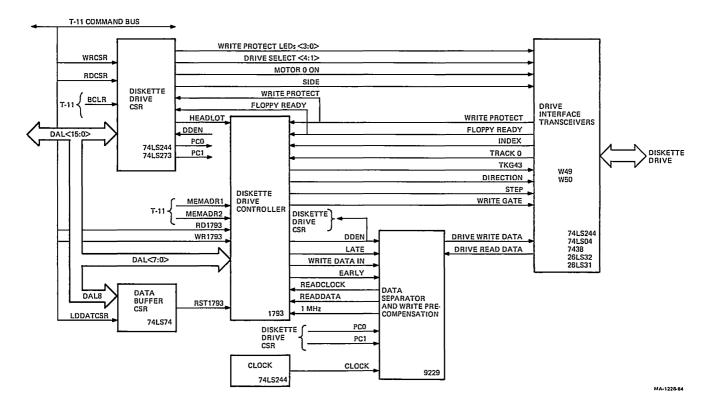

#### 3.3.4 Diskette Drive Controller Circuits

These circuits (Figure 3-5) are made up of the following components.

Diskette drive CSR Data CSR Diskette drive controller Data separator/write precompensation Drive transceivers

Figure 3-5 Diskette Drive Controller Circuit

3.3.4.1 Diskette Drive CSR and Data CSR -- The T-ll reads and writes the diskette drive CSR. The command register accepts a T-ll word that selects one of the four diskette drives and one of three precompensation values. This word also controls reads and writes in a single-density or double-density diskette drive format. It turns the drive motors on and lights the write protect LEDs on the drives.

> NOTE The T-ll turns all the drive motors off after no diskette activity has occurred for about 6 seconds or more to prolong the life of the drives.

The status register provides the T-ll with a data word that indicates the selected drive and the precompensation values. This word indicates whether the RUX50 reads and writes in a single-density or double-density diskette drive format. It shows the status of the drive motors and the write protect LEDs. It also shows whether the drive is ready and whether the selected diskette is write protected.

The T-ll processor circuits also load the data buffer CSR. This control register allows the T-ll to reset the diskette drive controller.

3.3.4.2 Diskette Drive Controller -- This controller (WD1793) performs all drive motor and data manipulations. It controls stepper motor direction. It also controls the conversion of data from serial to parallel and parallel to serial from the data separator/write precompensation circuit. This controller can read and write serial data in MFM (double density) or FM (single density) formats.

The T-ll loads the diskette drive controller with sector, track, data, and command information. The controller checks or generates a 16-bit cyclic redundancy check (CRC) from or to the selected drive.

3.3.4.3 Data Separator/Write Precompensation -- The data separator synchronizes the raw read signal from the selected drive and the free-running clock signal. It does this through a phase lock loop circuit, which captures the raw data directly from the drive within the pulse window of the clock.

The write precompensation circuit receives the serial data to be written to the drive and performs the following functions.

- Automatically generates a modified frequency modulated (MFM) bit stream.

- Automatically precompensates the MFM bit stream.

It has three possible precompensation values, depending on the position of the head. These precompensation values are selected from the diskette drive CSR. Depending on whether the early or late signals are generated from the WD1793, the write precompensation circuit adjusts the delivery timing of the serial data written to the drive. The operating frequency of the this circuit is 16 MHz.

3.3.4.4 Drive Interface Transceivers -- The drive interface transceiver communicates directly between the RUX50 and the diskette drives. Two jumpers allow the the drive transceivers to pass the read data from long-line or short-line ports on the connector to the data separator. The output and input of the transceiver go to a 50-pin connector.

#### CHAPTER 4 INTERCONNECTIONS

.

#### 4.1 INTRODUCTION

This chapter provides detailed descriptions of the UNIBUS connector (Paragraph 4.2) and the drive interface connector (Paragraph 4.3).

#### 4.2 UNIBUS CONNECTOR

Table 4-1 lists the UNIBUS signal pin assignments that the RUX50 uses, and Table 4-2 defines the signals.

#### 4.3 DRIVE INTERFACE CONNECTOR J1

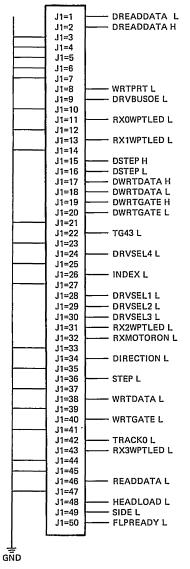

The drive interface transceivers on the RUX50 connect to a 50-pin connector (J1). The transceivers allow direct communication between the RUX50 and the diskette drives. The transceivers also provide open collector line driver output. Figure 4-1 shows the pins on connector J1. Table 4-3 lists pin signals and their functions.

| Pin | Name    | Pin  | Name    | Pin | Name   | Pin | Name   |

|-----|---------|------|---------|-----|--------|-----|--------|

| CAl | NPG IN  | CA2  | +5V     | EAl |        | EA2 | +5V    |

| CBl | NPG OUT | CB2  |         | EBl |        | EB2 |        |

| CCl | PA L    | CC2  | GND     | ECl | A12 L  | EC2 | GND    |

| CDl |         | CD2  | D15 L   | EDl | A17 L  | ED2 | A15 L  |

| CEl |         | CE2  | D14 L   | EEl | MSYN L | EE2 | Al6 L  |

| CFl |         | CF2  | D13 L   | EFl | AØ2 L  | EF2 | Cl L   |

| CHl | Dll L   | CH2  | D12 L   | EHl | AØ1 L  | EH2 | AØØ L  |

| CJl |         | CJ2  | DlØ L   | EJl | SSYN L | EJ2 | CØ L   |

| CKl |         | CK2  | DØ9 L   | EKl | A14 L  | EK2 | A13 L  |

| CL1 |         | CL2  | DØ8 L   | ELl | All L  | EL2 |        |

| CM1 |         | CM2  | DØ7 L   | EMl |        | EM2 |        |

| CN1 | DC LO   | CN2  | DØ4 L   | ENl |        | EN2 | AØ8 L  |

| CPl |         | CP2  | DØ5 L   | EPl | AlØ L  | EP2 | AØ7 L  |

| CRl |         | CR2  | DØ1 L   | ERl | AØ9 L  | ER2 |        |

| CSl | PB L    | CS2  | DØØ L   | ESl |        | ES2 |        |

| CTl | GND     | CT2  | DØ3 L   | ETl | GND    | ET2 |        |

| CUl |         | CU2  | DØ2 L   | EUl | AØ6 L  | EU2 | AØ4 L  |

| CVl | AC LO   | CV2  | DØ6 L   | EVl | AØ5 L  | EV2 | AØ3 L  |

| DAl |         | DA2  | +5V     | FAl |        | FA2 | +5V    |

| DB1 |         | DB 2 |         | FB1 |        | FB2 |        |

| DC1 |         | DC2  | GND     | FCl | SSYN L | FC2 |        |

| DD1 |         | DD2  | BR7 L   | FDl | BBSY L | FD2 |        |

| DEl |         | DE2  | BR6 L   | FEL |        | FE2 |        |

| DFl |         | DF 2 | BR5 L   | FFl |        | FF2 |        |

| DHl |         | DH2  | BR4 L   | FH1 |        | FH2 |        |

| DJl |         | DJ2  |         | FJl | NPR L  | FJ2 |        |

| DKl |         | DK2  | BG7 IN  | FKl |        | FK2 |        |

| DLl | INIT L  | DL2  | BG7 OUT | FLl |        | FL2 |        |

| DM1 |         | DM 2 | BG6 IN  | FM1 | INTR L | FM2 |        |

| DNl |         | DN2  | BG6 OUT | FN1 |        | FN2 |        |

| DP1 |         | DP2  | BG5 IN  | FPl |        | FP2 |        |

| DR1 |         | DR2  | BG5 OUT | FRl |        | FR2 |        |

| DS1 |         | DS2  | BG4 IN  | FSl |        | FS2 |        |

| DT1 | GND     | DT2  | BG4 OUT | FT1 | GND    | FT2 | SACK L |

| DUl |         | DU2  | ***     | FUl |        | FU2 |        |

| DV1 |         | DV2  |         | FVl |        | FV2 |        |

Table 4-1 UNIBUS Signal Pin Assignments

| Name                  | Mnemonic | Number<br>of Lines | Function                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|-----------------------|----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Data Transfer Signals |          |                    |                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Address               | A17:ØØ   | 18                 | The current bus master<br>asserts the address lines.<br>The host processor can<br>address the RUX50 registers<br>and the RUX50 can address<br>memory locations during DMA<br>data transfers.                                                                                                      |  |  |  |  |  |

| Data lines            | D15:ØØ   | 16                 | The data lines carry the<br>word of information that is<br>being transferred between<br>the bus master and slave.<br>Data lines carry commands,<br>responses, DMA data, and<br>interrupt vectors.                                                                                                 |  |  |  |  |  |

| Control lines         | C1:CØ    | 2                  | The bus master asserts the<br>select lines and specifies<br>the type of data transfer to<br>take place. The KLESI-UA<br>uses and recognizes three<br>operations.                                                                                                                                  |  |  |  |  |  |

|                       |          |                    | Name/Cl:CØ/Function                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                       |          |                    | Data in/00/One word of data<br>from slave to master                                                                                                                                                                                                                                               |  |  |  |  |  |

|                       |          |                    | Data out/10/One word of data<br>from master to slave                                                                                                                                                                                                                                              |  |  |  |  |  |

|                       |          |                    | Data out/ll/One byte of data<br>from master to slave                                                                                                                                                                                                                                              |  |  |  |  |  |

| Master sync           | MSYN     | 1                  | The bus master asserts and<br>negates MSYN, which and is<br>received by the bus slave.<br>When MSYN is asserted, the<br>master tells the slave to<br>perform the function<br>dictated by the C lines.<br>When MSYN is negated, the<br>master tells the slave that<br>a data transfer is complete. |  |  |  |  |  |

### Table 4-2 UNIBUS Signal Descriptions

| Name                      | Mnemonic     | Number<br>of Lines | Function                                                                                                                                                                                                                                                                                                                       |

|---------------------------|--------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Transfer             | Signals (Con | nt)                |                                                                                                                                                                                                                                                                                                                                |

| Slave sync                | SSYN         | 1                  | The bus slave asserts and<br>negates SSYN, which is<br>received by the master. When<br>SSYN is asserted during a<br>data transfer, the slave<br>tells the master that it has<br>received the data. The host<br>(slave) asserts SSYN during<br>an interrupt to tell the<br>master that it has received<br>the interrupt vector. |

| Parity                    | PA, PB       | 2                  | The bus slave asserts the<br>parity error indicators and<br>the master receives them.                                                                                                                                                                                                                                          |

|                           |              |                    | $PA = \emptyset$ , $PB = \emptyset$ : no parity error exists.                                                                                                                                                                                                                                                                  |

|                           |              |                    | PA = Ø, PB = 1: parity error<br>exists.                                                                                                                                                                                                                                                                                        |

|                           |              |                    | The RUX50 does not use PA.                                                                                                                                                                                                                                                                                                     |

| Interrupt                 | INTR         | 1                  | The RUX50 asserts INTR to<br>the host processor after the<br>RUX50 becomes bus master. It<br>signals that an interrupt is<br>to be performed and that an<br>interrupt vector is on the D<br>lines.                                                                                                                             |

| Priority Arbit            | ration Signa | als                |                                                                                                                                                                                                                                                                                                                                |

| Bus request               | BR7:4        | 4                  | The RUX50 asserts the<br>appropriate BR line to<br>request a bus interrupt.                                                                                                                                                                                                                                                    |

| Bus grant                 | BG7:4        | 4                  | The host processor asserts<br>the appropriate BG line in<br>response to a BR and grants<br>use of bus.                                                                                                                                                                                                                         |

| Selection<br>acknowledged | SACK         | 1                  | The RUX50 asserts SACK in response to a bus grant.                                                                                                                                                                                                                                                                             |

# Table 4-2 UNIBUS Signal Descriptions (Cont)

| Name                    | Mnemonic     | Number<br>of Lines | Function                                                                                                                                                                      |

|-------------------------|--------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Priority Arbit          | cation Signa | ls (Cont)          |                                                                                                                                                                               |

| Nonprocessor<br>request | NPR          | 1                  | The RUX5Ø asserts NPR<br>anytime it is ready to start<br>a data transfer.                                                                                                     |

| Nonprocessor<br>grant   | NPG          | 1                  | The host processor asserts<br>NPG to the RUX50 and grants<br>use of bus for data<br>transfers.                                                                                |

| Bus busy                | BBSY         | 1                  | The current bus master<br>asserts BBSY to all other<br>devices, indicating that the<br>data section is in use.                                                                |

| Initialization          | Signals      |                    |                                                                                                                                                                               |

| Initialize              | INIT         | 1                  | The host processor asserts<br>INIT and starts a subsystem<br>reset operation.                                                                                                 |

| AC low                  | AC LO        | 1                  | AC LO is asserted by any<br>device on the UNIBUS and is<br>received by the RUX50. AC LO<br>indicates possible failure<br>and aborts a RUX50 data<br>transfer if in operation. |

| DC low                  | DC LO        | 1                  | DC LO is asserted by any<br>device on the UNIBUS and is<br>received by the RUX50. DC LO<br>indicates possible failure<br>and causes a subsystem reset<br>operation.           |

# Table 4-2 UNIBUS Signal Descriptions (Cont)

MA-1222-84

Figure 4-1 Connector Jl Pin Functions

Table 4-3 Drive Interface Signals

| Name and State | Pin            | Function                                                                                                                                                                                                                                                                                                      |

|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DREADDATA L/H  | 1, 2           | Read Data is the data signal input from<br>the drive for long-line configurations.<br>It is a twisted pair signal. Data is a<br>low-going pulse from a minimum of 750<br>ns to a maximum of 1250 ns for each<br>flux transition.                                                                              |

| WRTPRT L       | 8              | Write Protect is sampled whenever a<br>write command is received. When<br>asserted, it terminates the write<br>command and reports a write protected<br>error.                                                                                                                                                |

| DRVBUSOE L     | 9              | Drive Present indicates that a diskette<br>drive is present and powered up.                                                                                                                                                                                                                                   |

| RXØWPTLED L    | 11             | Logical unit Ø write protect LED enable                                                                                                                                                                                                                                                                       |

| RX1WPTLED L    | 13             | Logical unit l write protect LED enable                                                                                                                                                                                                                                                                       |

| DSTEP H/L      | 15 <b>,</b> 16 | Step Pulse is a twisted pair signal for<br>long-line configurations. It carries a<br>2-us pulse, which is output to the<br>drive. For every step pulse (6 ms per<br>step) issued, the drive moves one track<br>in a direction determined by the<br>direction control signal (DIRECTION<br>L/H).               |

| DWRTDATA H/L   | 17 <b>,</b> 18 | Write Data is a twisted pair signal for<br>long-line configurations. It carries a<br>250-ns pulse that is generated for each<br>flux transition. Precompensation is<br>generated according to the position of<br>the read/write head. (Precompensation<br>values and track separation will be<br>determined.) |

| DWRTGATE H/L   | 19 <b>,</b> 2Ø | Write Gate is a twisted pair signal for<br>long-line configurations. This output<br>is made valid before writing can be<br>done on the diskette.                                                                                                                                                              |

| TG43 L         | 22             | Track Greater than 43 indicates that<br>the read/write head is between track 44<br>and 79, which lowers the write current<br>of the head on the drive during a write<br>operation. The output is valid only<br>during read and write commands.                                                                |

Table 4-3 Drive Interface Signals (Cont)

| Name and State | Pin | Function                                                                                                                                                                                                                                 |

|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRVSEL4 L      | 24  | Select Unit 4                                                                                                                                                                                                                            |

| INDEX L        | 26  | Index Pulse informs the RUX50 when the<br>index hole is found on the diskette.<br>Minimum pulse width is 20 us.                                                                                                                          |

| DRVSEL1 L      | 28  | Select Unit 1                                                                                                                                                                                                                            |

| DRVSEL2 L      | 29  | Select Unit 2                                                                                                                                                                                                                            |