Computer Science Department

114 Lind Hall

Institute of Technology

University of Minnesota

Minneapolis, Minnesota 55455

MICRO/40 Assembler Primer

Ъу

H. K. Berg and E. Dekel

Technical Report 78-9

July 1978

#### MICRO/40 Assembler Primer

bу

Helmut K. Berg and Eliezer Dekel

Department of Computer Science

University of Minnesota

#### Abstract

This report is a tutorial guide to the concept and use of the MICRO/40 assembler. It is intended to familiarize new users with the microassembler as the fundamental microprogram development aid in the PDP-11/40E microprogramming support system. The introduction of the MICRO/40 syntax in BNF and a commented list of all error messages make this report also usable as a reference for advanced users. Microprogramming techniques that scope with the effects of hardware idiosyncrasies on PDP-11/40E microprogramming are presented in the form of a tutorial. The report covers the basics needed for the day-to-day use of the microassembler, such as the microprogram input formats, the invokation of MICRO/40, and the interpretation of microassembler outputs. The use of MICRO/40 under the UNIX operating system is demonstrated by a commented protocol of a complete terminal session. This terminal session also illustrates the techniques for error corrections using the UNIX text editor.

### 1. Introduction

The microassembler described in this report is the language facility in our microprogramming laboratory that assists the user in writing PDP-11/40E microcode. MICRO/40 was developed at Carnegie-Mellon University, Department of Computer Science, to run as cross assembler on a PDP-10 computer [1]. The MICRO/40 version we refer to in this report is an improved PDP-11 version of the original microassembler that was written at the Technical University Berlin, Institut für Softwaretechnik und Theoretische Informatik, Fachgebiet Betriebssysteme. It runs on a PDP-11/40 under the UNIX operating system [2,3] and is written in the "C" programming language [4]. MICRO/40 interfaces to a microsimulator [5] and a microprogram test system [6,7] which, together with the microassembler, constitute the kernel of our PDP-11/40E microprogramming support system.

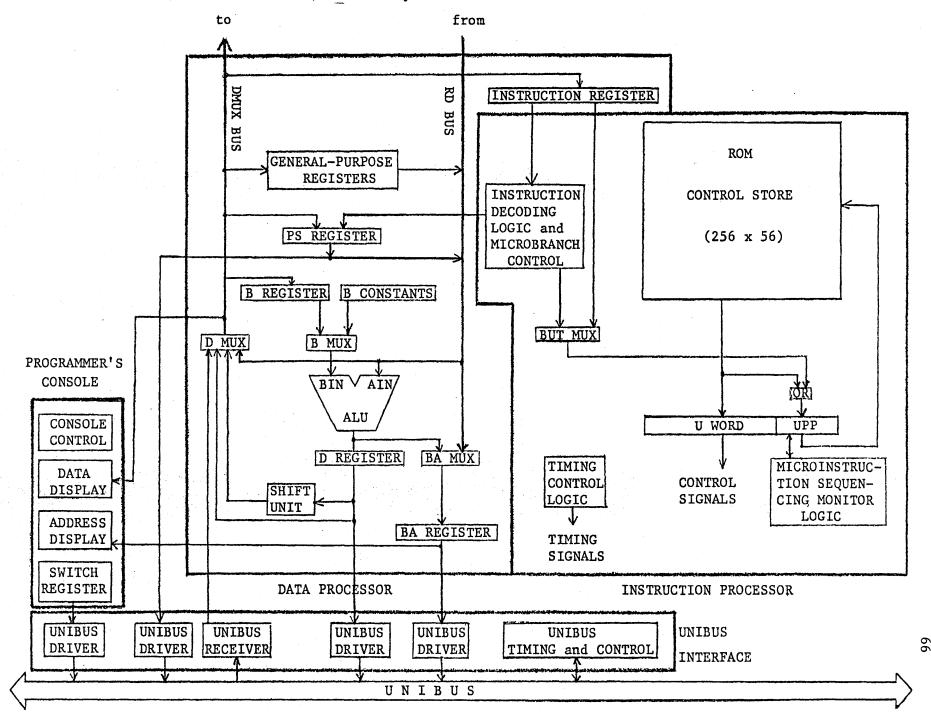

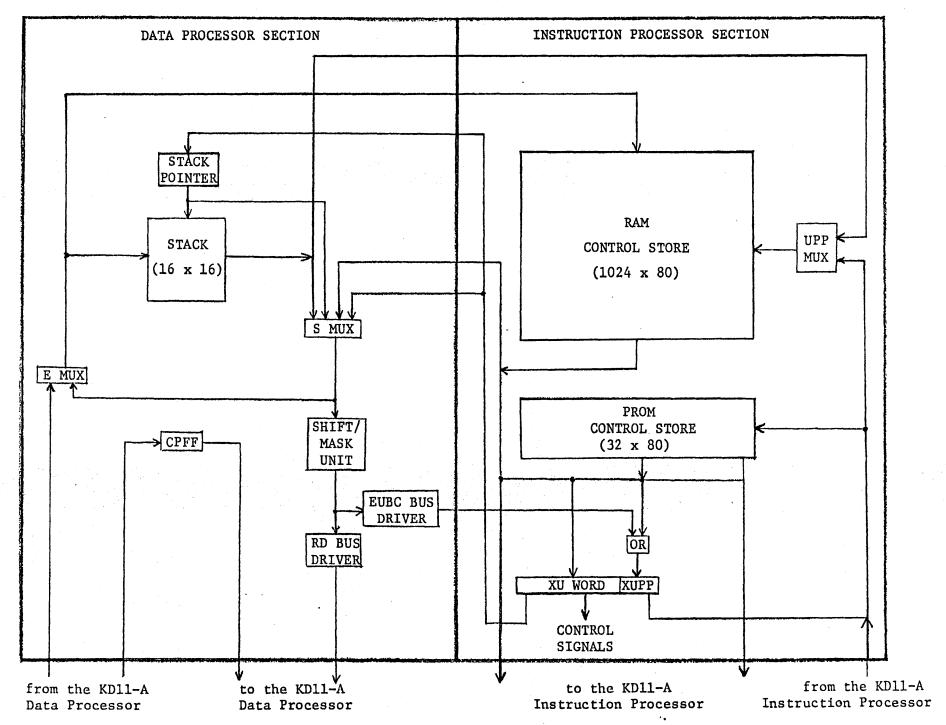

The PDP-11/40E is a standard PDP-11/40 computer that has been extended by the following hardware features which were developed at Carnegie-Mellon University [1,8]:

- 1K 80-bit words of random access (RAM) control store for storing user microprograms.

- 32 80-bit words of read-only (PROM) control store for bootstrapping microprograms.

- a 16-word stack for temporary data storage.

- a shift and mask unit and a carry control unit which extend the data manipulation capabilities of the basic PDP-11/40 processor.

The 3-River Computer Corporation offers these hardware accessories as a writable control store option (WCS 11/40) for the PDP-11/40. The PDP-11/40E has a horizontal microinstruction format that allows user microprograms access to all functional hardware units and data paths in the basic PDP-11/40 processor and in the WCS 11/40. The MICRO/40 assembler supports the construction of microinstructions from any combination of microoperations in this microinstruction format. The microprogramming features of the PDP-11/40E are described in [1,9].

In a typical microassembler, mnemonics are defined for each legal microoperation. Microinstructions are constructed by combining these menmonics in assembly code lines. For vertical microinstruction formats, only a single (relatively complex) microoperation can generally be defined in each microinstruction. Contrastingly, several (relatively primitive) microoperations can be combined into a single horizontal microinstruction. That is, horizontal microinstruction formats allow the specification of parallel actions (microoperations) to be performed by the machine hardware. In addition to mnemonic microoperation definitions, microassemblers usually provide for the use of mnemonic labels. Furthermore, the placement of microinstructions in the control store is usually supported by microassemblers, although microcode is generally not relocatable.

More sophisticated microassemblers may include macro facilities, in addition to the above features. Microassemblers for horizontal microinstruction formats may also automatically insert default values into microoperation fields which have not been filled by the microprogrammer. Furthermore, attempts have been made to make microassemblers partly machine-independent. These attempts make a single assembly language usable to generate microcode for several different microprogrammable machines. To this end, the assembly language syntax is parameterized and the hardware of the target machine is described at the assembler directive level. Finally, self-documenting assemblers have been developed that generate a commentary for each microinstruction written by the microprogrammer and thus, support microcode documentation.

The MICRO/40 assembler described in the following sections includes all the standard features of a microassembler for horizontal microinstructions. Additionally, a macro definition facility is provided. Furthermore, compound statements are included into MICRO/40 to support some of the idiosyncrasies of the PDP-11/40E. Microprogramming in the MICRO/40 assembly language is facilitated by the fact that the assembler transforms (register-transfer) assignment statements into appropriate microoperation field specifications, and the automatic insertion of default values into unspecified microoperation fields.

Microcode testing and debugging are integral parts of the microcode construction process and should not be delayed until after a microprogram is written. Therefore, microprogramming languages must support microcode testing and debugging. Analogous to the relationship between high-level programming languages and assembly languages for software, high-level microporgramming languages have many advantages over microcode assembly languages, with respect to microcode construction. For example, program development techniques, such as structured programming, become applicable to microprogramming through the use of machine-independent high-level microprogramming languages. Although structured, high-level microcode generation also greatly facilitates error location and correction, there exists no widely accepted high-level microprogramming language. This situation is primarily due to the fact that hard-

ware-dependent timing conditions (especially for asynchronous operations) and the inherent parallelism hinder the compiler construction for machines with horizontal microinstruction formats. The fundamental problem, in this respect, is the generation of optimized microcode, and the lack of realistic models of microinstruction and microoperation semantics which, by nature, are considerably more complex than corresponding models for software semantics. That is, in essence, the provision of high-level microprogramming tools is hindered by the necessity to exploit hardware characteristics to produce efficient microcode. Unoptimized microcode is generally unacceptable, because of the frequency with which microinstructions are executed.

As a result of the discussed difficulties in developing high-level micro-programming facilities, typical microprogramming support systems are still based on a microassembler and the associated loader and simulator software. Microassemblers leave the task of microcode optimization to the microprogrammer, as they do not offer any assistance in exploiting the inherent parallelism in microinstructions. Generally, a microassembler merely checks the legality of the combination of microoperations which the microprogrammer specified within a microinstruction. These syntax checks in a microassembler may be considered as a type of static microprogram testing and therefore, are usually restricted to the detection of static errors. Dynamic microprogram testing via microprogram execution requires the availability of an off-line (soft) test system, such as a microcode simulator, or of on-line (hard) test systems, such as an interactive debugger or special hardware accessories for the instrumentation of microprogram executions.

The error detection capabilities of the MICRO/40 assembler are enhanced by the WCS 11/40 microinstruction format [1,9] which makes certain conflicts detectable through microcode examination. The typical conflicts that are detected by the MICRO/40 assembler are the illegal use of data paths, registers, and functional hardware units. With respect to timing errors, the micro-assembler checks the specified microoperations against the length of the specified processor clock cycle, and attempts to enforce the proper timing for each microinstruction. Nevertheless, the detection of timing conflicts by the MICRO/40 assembler is restricted to static errors.

MICRO/40 supports microcode testing and debugging by generating files to be used by a microcode simulator [5]. The microsimulator allows the investigation of effects of simulated microinstruction executions. The facilities for detecting and locating of errors are basically restricted to static errors which can be observed by investigating processor registers, including the microprogram pointer. For the detection of dynamic, hardware-dependent micro-

program errors, an on-line test system, SMILE [6,7], for microprogram load and examination is available in our microprogramming support system. The SMILE system loads the binary object microcode as supplied by MICRO/40 into the writable control store, and allows microprogram testing at the microprogram level by executing PDP-11/40 machine language instructions which call upon the execution of the loaded microcode. However, using the SMILE system, erroneous microoperations usually cannot be located by tests at the microprogram level. Therefore, the microprogramming support system has been complemented with a logic state analyzer whose use as an on-line test facility at the microinstruction and microoperation level is documented in [10].

This report is intended to provide a tutorial guide to the concept and use of MICRO/40 that expands and complements the available documentation [1,8]. To this end, we first introduce the MICRO/40 syntax in section 2. Based on the content of section 2, we proceed, in section 3, with a discussion of the conceptual features of MICRO/40 and associated programming techniques. Guidelines for the use of MICRO/40 and the interpretation of assembler output are presented in section 4. Finally, in section 5, we demonstrate a complete example of the microassembler operation in the form of a terminal session.

## 2. MICRO/40 Syntax

MICRO/40 has many of the limitations of a software assembler. Furthermore, being a microassembler for a specific machine (PDP-11/40E), register and microoperation field names as well as operator symbols are predeclared and cannot be redefined. The nature of register-transfer operations in the PDP-11/40E processor as described by MICRO/40 assembly language lines implies that all names and operator symbols are global.

# 2.1 Input Format

Each line of MICRO/40 input is assembled into a single 80-bit microinstruction (for exceptions to this rule, cf. subsection 2.5). A line of MICRO/40 input is defined as all the characters between two consecutive line-feeds. Any line ending with a hyphen(-) has the next line concatenated to it, i.e., the hyphen is the line continuation symbol. Each line is read and processed individually, and no distinction is made between lower case and upper case letters. The MICRO/40 assembly language is a free-format language in which statements can be placed anywhere on the line with as many blanks as needed to make the described microinstruction legible. Anything following an exclamation point(!) on a line is considered a comment and is ignored.

#### 2.1.1 Identifiers

A MICRO/40 identifier is a character string starting with an alphabetic (A-Z, a-z) and followed by an arbitrary number of alphabetics (A-Z, a-z), digits (0-9), a dot(.), a slash(/), or an underline(\_). The number of significant identifier characters is limited to 20.

#### 2.1.2 Numbers

A numeric constant is a sequence of one or more digits. All numeric constants are considered to be octal, unless the number contains the digits 8 or 9, or a decimal point in which case, it is interpreted as a decimal number. The syntax of a negative number is, -<number>. Negative numbers may be parenthesized. The above rules define the following equivalences, e.g.,

137 is equivalent to 95, 102 is equivalent to 66., -32 is equivalent to (-32).

# 2.1.3 Labels

A label declaration is an identifier followed by a colon(:), i.e.,

<label declaration>::=<label>:

<label>::=<identifier>

A line may contain an arbitrary number of labels which may be placed anywhere on the line.

## 2.2 Microoperation Field Assignments

The generic use of the MICRO/40 assembler is to assign specific values to each microoperation field in the horizontal microinstruction. The syntax 1) for a field assignment is:

<field name> = <value> {;} .

The semi-colon (;) separates multiple field assignments on a single MICRO/40 input line. The semi-colon following the last field assignment on a line may be omitted.

Throughout this text, we use the meta symbol {}to enclose optional objects in syntax definitions (i.e., 0 or 1 repetitions of the enclosed object are allowed).

## 2.2.1 Microoperation Fields

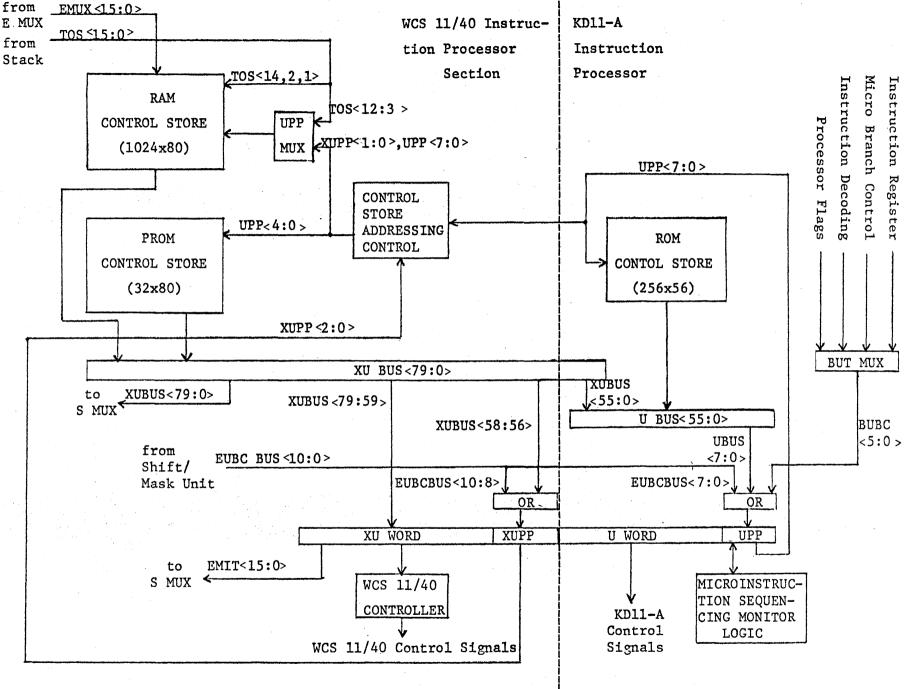

The format of the 80-bit PDP-11/40E microinstruction (XU) and the bit position assignment of the microoperation fields are shown in Fig. 1. The 36 microoperation field in XU may be divided into 14 groups [9]. The

|       |        | EMI  | Т      |        |       |       |       |       |     |     |    | •     |       |        |

|-------|--------|------|--------|--------|-------|-------|-------|-------|-----|-----|----|-------|-------|--------|

| SCOM  | PP     | E    | CP     | cs     | RM    | L     | MIL . | DEST  |     | MS  | C  | XUP   | F     | UPF    |

| 79    | 78 7   | 7    | 76     | 75 7   | 72 71 | 68 6  | 7 64  | 63 (  | 62  | 61  | 59 | 58    | 56 55 | 48     |

| CLKL  | CLKOFF | CL   | KIR    | WRH    | WRL   | CLKB  | CLK   | D CLI | ΚBA | CBU | IS | BGBUS | DAD   | SPS    |

| 47 46 | 45     | 4    | 4      | 43     | 42    | 41    | 40    | 39    | 9   | 38  | 37 | 36    | 35 3  | 2 31 2 |

| SALUM | SALU   | SBC  | SBMH   | SBML   | SDM   | SBAM  | UBF   | SRS   |     | SRD | SR | BA S  | RI R  | IF     |

| 28 2  | 27 24  | 23 2 | 0 19 1 | 8 17 1 | .6 15 | L4 13 | 12    | 8 7   |     | 6   | 5  | 4     | 3     | 0      |

#### Figure 1: XU Format

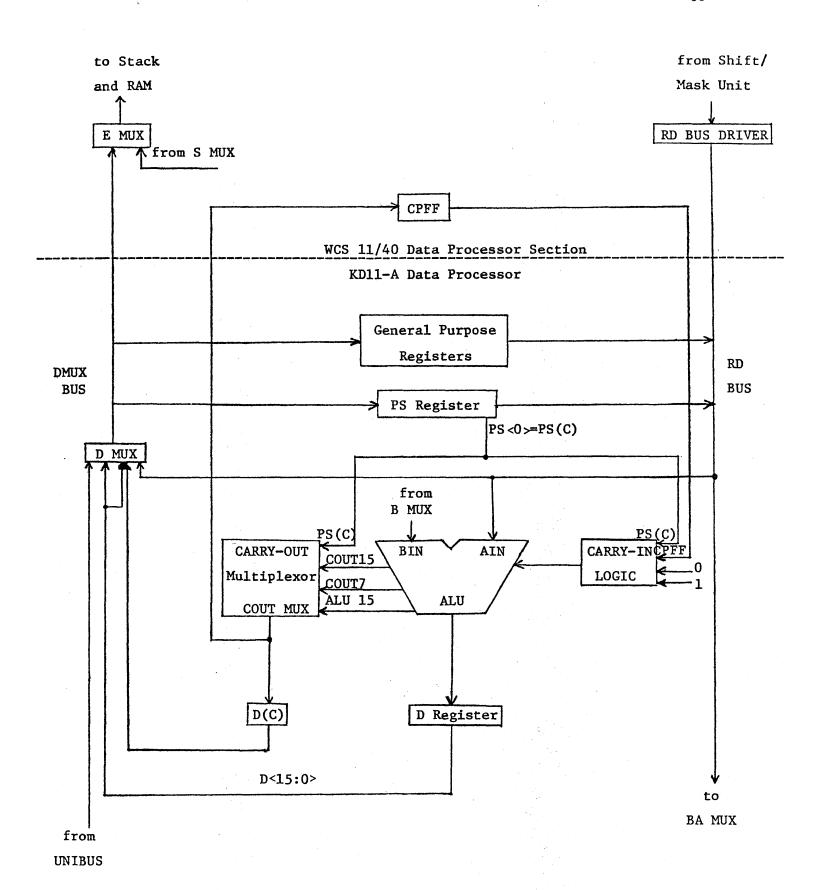

PDP-11/40E registers, data paths and functional units associated with the microoperations are depicted in the register-transfer block diagrams of the PDP-11/40 processor, the WCS 11/40, and their mutual interfaces as given in the appendix.

## Clock Control

CLKL (XU<47:46>): Processor Clock Length Control

Allows a selection from three basic PDP-11/40 processor cycle times.

CLKOFF (XU<45>): Processor Clock Off

When set, turns processor clock off.

## Register Load Control

CLKIR (XU<44>): Clock Instruction Register

Allows clocking the D MUX output into the instruction register.

WRH (XU<43>): Write High Order Byte of DMUX BUS

Allows writing the high order byte of the D MUX output into a selected general purpose register.

WRL (XU<42>): Write Low Order Byte of DMUX BUS

Allows writing the low order byte of the D MUX output into a selected general purpose register.

CLKB (XU<41>):  $\underline{Clock} \ \underline{B} \ Register$

Allows clocking the D MUX output into the B Register.

CLKD (XU<40>): Clock D Register

Allows clocking the ALU output into the D Register.

CLKBA (XU<39>): Clock BA Register

Allows clocking the BA MUX output into the BA Register

# UNIBUS Control

CBUS (XU<38:37>): Control of UNIBUS

Allows the specification of UNIBUS data transfers.

BGBUS (XU<36>): Begin a UNIBUS Transfer

Allows the initiation of a UNIBUS data transfer specified in CBUS.

### Instruction Processor Logic Control

DAD (XU<35:32>): Discrete Alteration of Data

Directs the ALU control logic (which is associated with the instruction decoding logic) as to alterations of operations to be performed by functional hardware units in the data processor.

### Processor Status Control

SPS (XU<31:29>): Select Processor Status

Determines loading of the PS Register from the DMUX BUS, clocking of condition codes into the PS Register, and gating of the PS Register onto the RD BUS.

# ALU Control

SALUM (XU<28>): Select ALU Mode

Selects ALU mode of operation (arithmetic or logic)

SALU (XU<27:24>): Select ALU Function

Allows the selection of up to 16 arithmetic or 16 logic ALU functions.

## Multiplexor Control

SBC (XU<23:20>): Select Input to B MUX from B Constants

Allows the selection of a constant to be gated to the ALU B-input.

SBMH (XU<19:18>): Select Input to B MUX's High Order Byte

Allows the selection of bytes from the B Register and the B Constants to be gated to the high order byte of the ALU B-input.

- SBML (XU<17:16>): Select Input to B MUX's Low Order Byte

Allows the selection of bytes from the B Register and the B

Constants to be gated to the low order byte of the ALU B-input.

- SDM (XU<15:14>): Select Input to  $\underline{D}$   $\underline{M}UX$  Select the RD BUS, the UNIBUS data lines, the D Register, or the right-shifted D Register as the input to D MUX.

- SBAM (XU<13>): Select Input to BA MUX

Selects the output of the ALU or the RD BUS as the input to BA MUX.

# General Purpose Register Addressing Control

- SRS (XU<7>): Select General Purpose Register Address from IR Source Field

Allows IR <8:6> to be used as a source of a general purpose register address.

- SRD (XU<6>): Select General Purpose Register Address from IR Destination Field

Allows IR <2:0> to be used as a source of a general purpose register address.

- SRBA (XU<5>): Select General Purpose Register Address from the  $\underline{BA}$  Register Allows BA <3:0> to be used as a source of a general purpose register address.

- SRI (XU<4>): Select General Purpose Register Address from RIF

Allows XU <3:0> = RIF to be used as a source of a general purpose register address.

- RIF (XU<3:0>): Register Immediate Field

Used as source of a general purpose register address when enabled by SRI.

#### Microinstruction Sequencing Control

- UBF (XU<12:8>): Micro Branch Field

Specifies the branch micro test (BUT) to be performed, in order to generate the address of the successor microinstruction by ORing the determined basic microbranch code (BUBC) into UPP<5:0>.

- UPF (XU<55:48>): Microprogram Pointer Field

Used to specify the address of the next microinstruction to be executed. The specified address may be modified as a result of a branch micro test (BUT) specfied in UBF.

- XUPF (XU<58:56>): Extended Microprogram Pointer Field

Concatenated with UPF (XU<55:48>), this field froms an 11-bit microinstruction address in the extended control store address space (addition of the RAM and PROM control stores to the ROM control store),

# WCS 11/40 Data Paths Control

MSC (XU<61:59>): Mask/Shift Control

DEST (XU<63:62>): Destination

The DEST and MSC fields are combined into a 5-bit field that specifies how the bits XU<79:64> are to be interpreted (as function fields or EMIT field) and how the WCS 11/40 data paths are set up for the interpretation of the current microinstruction.

# Mask/Shift Control

LML (XU<67:64>): Left Mask Limit

Specifies the number of bits of the S MUX output that are to be masked off from the left.

RML (XU<71:68>): Right Mask Limit

Specifies the number of bits of the S MUX output that are to be masked off from the right.

SC (XU<75:72>): Shift Count

Specifies the number of bit positions (between 0 and 15) for a right rotate of the S MUX output

Depending on the specification of DEST/MSC, this field might also be used to specify a 4-bit value to be transferred into the stack pointer SP.

#### Carry Control

CP (XU<76>): Carry Propagate Control

Specifies the application of the content of CPFF (Carry Propagate Flip-Flop) to the carry input of the ALU and the storage of a new carry bit (as determined by SCOM) into CPFF.

SCOM (XU<79:78>): Select Carry Out Multiplexer

Specifies the selection of a carry bit from the ALU carry-out bits (ALU15, word carry, byte carry) or the condition code bit PS(C) of the processor status word to be stored into the high-order bit extension of the D Register (D(C)) and into CPFF.

### Stack Control

PPE (XU<77>): Push/Pop Enable

Specifies, if stack read/write operations are combined with pop/ push operations, respectively.

# Arithmetic and Addressing Constants

EMIT (XU<79:64>): Microliteral Field

Used to specify 16-bit arithmetic or addressing constants. The use of XU<79:64> for microliterals is determined by the specification in DEST/MSC. If XU<79:64> is used as a microliteral field, the fields LML, RML, SC, CP, PPE, SCOM of the XU WORD serve as a data register whose content is transferred to the input of S MUX.

# 2.2.2 Use of Field Assignments

With each field assignment in a MICRO/40 assembly language program, the appropriate microoperation field is cleared and the assigned value is stored in it. If a single MICRO/40 input line contains two different assignments to the same field, only the last (right-most in the lint) value is considered and a warning is issued. That is, the microassembler does not prevent double field assignment on the same line. All values assigned to microoperation fields are expected to be assembly time constants (numbers), except for values assigned to the EMIT and XUPF fields.

The EMIT field may store a 11-bit control store address that is associated with a mnemonic label in the assembly microprogram, or the 16-bit address of a 16-bit field in the writable control store. The latter option allows the writable control store (RAM) to be accessed as a data scratch pad (cf. subsections 2.5.7 and 2.5.8).

MICRO/40 uses the name XUPF to denote the extended microprogram pointer field, XU<58:48> = XUPF, UPF (cf. subsection 2.2.1). This field always holds the base address of the next microinstruction, as there is no microinstruction counter in the PDP-11/40E. If no assignment is made to the XUPF field, the increment of the current microinstruction (control store) address is automatically assigned as a default. This assignment corresponds to a 'goto next consecutive microinstruction'. Assigning a constant to XUPF causes a 'goto' to that absolute control store location. However, mnemonic labels may also be assigned

to XUPF, in which case, the associated 11-bit microinstruction address is inserted into XU<58:48>.

For MICRO/40 field assignments, some of the microoperation fields discussed in the preceding subsection are concatenated into compound fields:

ALU = SALUM, SALU

BUS = CBUS, BGBUS

CLK = CLKL, CLKOFF

SBM = SBMH, SBML

SRX = SRS, SRD, SRBA, SRI

WR = WRH, WRL

XUPF = XUPF, UPF

The microinstruction generated by the following field assignments transfers the constant 10 into the B Register.

emit = 10;

$$msc = 1$$

;  $c1k = 6$ ;  $c1kb = 1$

The assembler sets all other microoperation fields to 0, except for the XUPF field which is assigned the control store address of the next consecutive microinstruction, if there exists one. The assignment of the binary value, 00 001, to the DEST/MSC fields specifies the data transfer, RD  $\leftarrow$  EMIT. The assignment clkb=1 opens the data path, B  $\leftarrow$  DMUX, while the implicit setting sdm=0 defines the transfer DMUX  $\leftarrow$  RD BUS. Hence, we have the compound transfer:

$$B \leftarrow DMUX \leftarrow RD BUS \leftarrow EMIT = 10$$

.

The assignment clk=6, i.e., CLKL=3, selects a P3 processor clock cycle for this data transfer (cf.[9]). Generally, MICRO/40 automatically assigns an appropriate clock cycle length for each microinstruction. Thus, the field assignment, clk=6, is redundant.

To further illustrate the use of field assignments in the MICRO/40 assembly language we give the following example microprogram for adding the numbers from 1 to 10 that stores the result in the general purpose register R[0]. The verification of this microprogram is left to the reader (cf.[1],[9]).

```

wr=3; clkd=1; alu=23; sdm=2; srx=1

! R[0]=0

emit=10; msc=1; clkb=1

! B+ 10

```

loop:emit=177777;msc=1;clkb=1;clkd=1;alu=11;sdm=2;ubf=12;xupf=n

$!D\leftarrow B-1;B\leftarrow D;$ goto n;skip the microinstruction following -

!the microinstruction with label n, if D=0

xupf = next

! goto next

n:wr=3;c1kd=1;a1u=11;sdm=2;srx=1;xupf=1oop

!  $R[o] \leftarrow R[o] + B$ ; goto loop

next: <whatever comes next>

# 2.3 Assignment Statements

As discussed in the preceding subsection, microprograms may be written in the form of field assignments. However, the exclusive use of field assignments makes microprogramming a tedious task. Therefore, MICRO/40 provides for the specification of carrier-to-carrier transfers in the form of assignment statements. A carrier is a facility for accommodating bit strings which represent the information in a computer. A carrier may be a register, a memory, or a data paths. The microoperation fields associated with a carrier-to-carrier transfer are automatically set to appropriate values, when an assignment statement is assembled.

## 2.3.1 Carrier Identification

# R: General Purpose Registers

The PDP-11/40 has 16 16-bit general purpose registers which are implemented as a data scratch pad. They are loaded from the DMUX BUX, supply output to the RD BUS, and are addressed by 4-bit addresses. In each microinstruction, only a single general purpose register can be addressed, i.e., simultaneous register read and write operations are not permissible.

The syntax for general purpose registers is:

A number directly specifies one of the 16 general purpose registers. Registers are specified indirectly by using the specifiers BA, DF, or SF. Using the specifier BA, BA<3:0> is taken as the source of the register address, whereas the specifiers DF and SF specify the destination field, IR<2:0>, and the source field, IR<8:6>, of the instruction register as the source of the register address, respectively. Furthermore, the optional selector allows the selection of either the low-order byte (1), R<7:0>, or the high-order byte (h), R<15:8>, of a general purpose register R.

### D: Data Register

The D Register is a 16-bit register for the temporary storage of ALU output data.

Syntax: <D Register>::=d

## DSHIFT: Right-Shifted D Register

The D Register is right-shifted at D MUX, such that DSHIFT = D(C), D<15:1>. D(C) is a 1-bit extension of the D Register that may be loaded with ALU carry outputs (ALU15, word carry, byte carry) or the condition code bit, PS(C), of the processor status word. DSHIFT can only appear on the right hand side of an assignment statement.

Syntax: <Right-Shifted D Register>::=dshift | d/2

# B: ALU B-input Register

The B Register is a 16-bit register for the temporary storage of ALU B-input data. The syntax for the B Register is:

<B Register>::= b{<<B modifier>>}

<B modifier>::= <high selector><low selector>

<high selector>::= H E L C

<low selector>::= H|Z|L|C

The optional B modifier can only be used, if the B Register appears on the right hand side of an assignment statement. The high selectors select the following gating mechanisms:

H: BMUX<15:8> + B<15:8>

E: BMUX<15:8> + B<7>

L: BMUX<15:8> + B<7:0>

C: BMUX<15:8> + B CONSTANT<15:8>

The low selectors select the following gating mechanisms:

H: BMUX<7:0>  $\leftarrow$  B<15:8>

Z:  $BMUX<7:0> \leftarrow B<7:0>$

L:  $BMUX<7:0> \leftarrow B<7:0>$

C BMUX<7:0>  $\leftarrow$  B CONSTANT<7:0>

If no B modifier is specified, the default b<HZ> is assumed.

#### C: ALU B-input Constants

The C Register is a combinatorial network that provides basic constants to be used in processor operations (cf. [1,9]). The syntax for the Constant Register is:

<Constant Register>::=c[<number>]

<number>::= 0|1|2|3|4|5|6|7|10|11|12|13|14|15|16|17|

8.|9.|10.|11.|12.|13.|14.|15.

# BA: UNIBUS Address Register

The BA Register is a 16-bit register for the temporary storage of UNIBUS addresses. It is decoded to detect processor register addresses in the UNIBUS addressing scheme. The BA Register can only occur on the left hand side of an assignment statement.

Syntax: <BA Register>::= ba

### IR: Instrustion Register

The instruction register is a 16-bit register that holds PDP-11/40 machine language instructions. Its output is applied to the instruction decoding logic, is used to control microbranching, and specifies general purpose register addresses. The instruction register can only appear on the left hand side of an assignment statement.

Syntax: <Instruction Register>::= ir

## PS: Processor Status Register

The processor status register is a 16-bit register which holds the processor status word that specifies condition codes, processor priority, trap condition, and operational modes.

Syntax: <Processor Status Register>::= ps

## S: Stack

The WCS 11/40 stack is a 16 16-bit word register-memory that can be used as a data or address push-pop stack. It is addressed from the stack pointer (SP), receives input from E MUX, and can supply output to S MUX and UPP MUX.

Syntax: <stack>::= s

The use of the identifier s in a MICRO/40 line implies that the WCS 11/40 stack is used as a push-pop stack.

# TOS: Top of Stack

TOS refers to the current top of the WCS 11/40 stack. However, references to TOS do not push/pop the stack.

Syntax: <Top of Stack>::= tos

### SP: Stack Pointer

The stack pointer is a 4-bit register that holds the stack address. It can be set from XU<75:72> = SC<3:0>, and is incremented or decremented for pop or push operations, respectively.

Syntax: <Stack Pointer>::= sp

## UNIBUS

In MICRO/40, the UNIBUS data lines can only be used as a source (right hand side of an assignment statement) that provides input data to registers on the DMUX BUS.

Syntax: <UNIBUS>::= unibus

### EUBC: Extended Microbranch Condition BUS

The EUBC BUS supplies 11-bit microinstruction control store addresses to the XUPP section of the microinstruction buffer. The EUBC BUS can only occur on the left hand side of an assignment statement. Input to the EUBC BUS may be supplied from the stack and from the EMIT field in the microinstruction.

Syntax: <EUBC BUS>::= eubc

#### RAM: Writable Control Store

The writable control store has a capacity of 5K 16-bit words. It receives 16-bit data inputs and supplies 80-bit words at the output. It can be used to store 1K of 80-bit microinstructions, to store 5K of 16-bit data words, or as a combination of control store and data scratch pad. The syntax for RAM references is:

<RAM reference>::= RAM[<specifier>]

<specifier>::= s|tos .

## 2.3.2 Syntax of Assignment Statements

The basic form of an assignment statement is:

<expression>::= <simple expression> | <compound expression>

A <left carrier> is any of the carriers that can occur on the left hand side of

an assignment statement. The assignment operator is the underline (\_).

Assignment statements within a single line are separated by a semi-colon(;).

The semi-colon following the last statement in a line is optional.

A simple expression is a right hand side of an assignment statement in which only a single carrier is specified, i.e.,

(for the definition of ,cf. subsection 2.5.7). All numbers given in an extension operand specification are interpreted as decimal numbers, despite of their representation. The field selection defines a masking by specifying the right-most and the left-most bit position to be masked out of the specified extension carrier. The result of a mask operation is always right-adjusted at the output of the shift/mask unit in the WCS 11/40. The shift is a left shift by the specified number of bit positions. The combination of the shift and the right/left mask allows the extraction of any contiguous n-bit field  $(1 \le n \le 16)$  from an extension carrier.

A compound expression includes an ALU operation. The syntax for the ALU operators is:

```

<negation>::= not | \sim | \setminus 5 | \setminus 32

<disjunction>::= or | \cdot \cdot | \setminus 37

<conjunction>::= and | \cdot \cdot | \setminus 4

<exclusive-or>::=xor | \setminus 26

<addition>::= plus | \cdot | \cdot |

<subtraction>::= minus | \cdot |

```

To define an operator by a code number requires that a backslash (\) is typed before the code number. The syntax of a compound expression is defined:

```

<A-op> plus <A-op> and <B-op> |<A-op> plus <B-op>

(<A-op> or not <B-op>) plus <A-op> and <B-op>

<A-op> and <B-op> minus 1

<A-op> plus <A-op> (<A-op> or <B-op>) plus <A-op>

(<A-op> or not <B-op>) plus <A-op>

A-op> \min 1 A-op> plus 1 (A-op> or B-op>) plus 1 0

<A-op> plus <A-op> and not <B-op> plus 1

(<A-op> or <B-op>) plus <A-op> and not <B-op> plus 1

<A-op> minus <B-op> | <A-op> and not <B-op> |

<A-op> plus <A-op> and <B-op> plus 1

(<A-op> or not <B-op>) plus <A-op> and <B-op> plus 1

<A-op> and <B-op> | <A-op> plus <A-op> plus 1 |

(<A-op> or <B-op>) plus <A-op> plus 1

(<A-op> or not <B-op>) plus <A-op> plus 1 not <A-op>

not (<A-op> or <B-op>)

not <A-op> and <B-op> not (<A-op> and <B-op>)

not <B-op> <A-op> xor <B-op>

<A-op> and not <B-op> not <A-op> or <B-op>

not (<A-op> xor <B-op>)

<A-op> and <B-op> |<A-op> or not <B-op> |

<A-op> or <B-op>

```

<A-op> may be anything that can be placed on the RD BUS, i.e.,

<B-op>::=<B Register> | <Constant Register> .

To demonstrate the use of MICRO/40 assignment statements, we rewrite the microprogram for adding the numbers from 1 to 10 (cf. subsection 2.2.2).

d\_0; R[0] \_d

!clear our accumulator R[0]

b 10

!clock the value 10 from the EMIT field into the B Register

loop: d\_177777+b; b\_d; ubf=12; xupf=n

!decrement the B Register using the constant -1 from the !EMIT field, break the loop if D=0.

xupf=next

!goto next

n:  $d_R[0] + b$ ;  $R[0]_d$ ; xupf=100p

!add the content of the B Register to R[0].

next: <whatever comes next>

Note that the use of assignment statements does not reduce the number of code lines, as each MICRO/40 line is assembled into a single microinstrucion.

## 2.3.3 Semantics of Assignment Statements

When writing assignment statements, it must be remembered that MICRO/40 assignments represent carrier-to-carrier transfers. That is, each transfer must be described explicitly. Hence, an assignment statement

is not permissible. To decrement (add -1) the content of the B Register requires that the constant 177777 from the EMIT field is gated to the A-input of the ALU, the B Register is gated to the ALU B-input, and the ALU performs an addition. The result of this addition is transferred into the D Register. Then, the content of the D Register can be transferred, via D MUX, into the B Register. Therefore, it is necessary to write the assignment statements,

to affect the two transfer operations. The assignment statements,

are identical in their effect to writing them in reversed order, as both transfers are performed quasi parallel, i.e., within the same microinstruction execution cycle.

To further stress the point that MICRO/40 assignment statements correspond to carrier-to-carrier transfers, we consider the following example:

The microprogrammer might hope that these assignment statements would set R[6] to  $000400_8$ . MICRO/40 permits these assignment statements, however, their semantics deviate from the microprogrammers intention. As R[6] is referenced, its content is clocked onto the RD BUS. At the same time, the constant 400 in the EMIT field is clocked onto the RD BUS, and the contents of R[6] and EMIT are ORED. Hence, the new value of R[6] is its old value with bit 8 set of 1. To perform the intended task, the assignment statments given above have to be executed in two consecutive microinstructions, i.e.,

Note that, in general, gating two sources onto the same carrier causes an error. However, in the case of the RD BUS, any of the three potential sources (general purpose registers, processor status register, and extension) can idenpendently gate (OR) a word onto the bus.

Whenever the identifier, s, is used on the left hand side of an assignment statement, the stack is pushed before the value is stored. When tos is used, the new value is written over the current top of stack. On the right hand side of an assignment statement, s results in the value being read out of the stack and the stack being popped. Contrastingly, tos results in the value on the current top of stack being read out.

The semantics of WCS 11/40 shift/mask operations, which may be combined with any extension operand, are illustrated by the following example:

The assignment statement places 9 bits (S<11:3>) of the 16-bit value popped off the stack into D<10:2>. That is, after bits 11 to 3 of S have been masked out, they are right-adjusted. Then, the resulting 16-bit word is rotated two positions to the left. The net effect is a 1-bit right shift of S<11:3>

## 2.4 Comments and Continuation Lines

Anything following an exclamation point (!) on a line is considered a comment and is ignored by the assembler. Any line that ends with a hyphen (-) has the next line concatenated to it. That is, two or more MICRO/40 lines may be concatenated into a single logical line to produce a single microinstruction after assembly. Lines may also be continued within a comment. Hence, the following six examples are equivalent.

- 1. R[7]\_d

- 2. c1k=2; rif=7; wr=3; srx=1; sdm=2

- 3. c1k=2; rif=7; wr=3; srx=1; sdm=2 ! D Register to R[7]

- 4. rif=7; wr=3; c1k=2; srx=1; sdm=2 ! D Register to R[7]

- 5. sdm=2; srx=1; clk=2;! P1 is a sufficient clock cycle time rif=7; wr=3;

- 6. rif=7; wr=3; srx=1;sdm=2 ! no need to specify clock cycle time A microinstruction may be described by any number of concatenated lines, provided that the so constructed logical line does not exceed 300 characters.

#### 2.5 Pseudo Operators

A number of pseudo operators are provided by MICRO/40 to make some of the idiosyncrasies of PDP-11/40E microprogramming transparent to the user and to further relieve the microprogrammer of the tedious task of constructing microprograms through explicit microoperation field assignments. Pseudo operators range from field assignments to compound statements that comprise several microinstructions. They facilitate processor clock control, structuring of microcode in the control store, microinstruction sequencing, and the use of the writable control store as a data scratch pad.

## 2.5.1 CLKOFF

MICRO/40 concatenates the clock length field and the clockoff field into a single 3-bit clock field, i.e., CLK=CLKL,CLKOFF. Hence, the CLKOFF bit can only be set, if, at the same time, a processor clock cycle length is specified by the microprogrammer. This restriction is due to the fact that all bits in a microoperation field are cleared, before a field value is stored. Furthermore, it is generally not possible to exploit the microassemblers capability to determine an appropriate clock cycle length and to automatically set the CLKL field, in microinstructions in which the CLKOFF bit is to be set. Therefore, the clkoff pseudo operator was implemented to overcome these difficulties.

The clkoff pseudo operator has the effect of turning on the CLKOFF bit in the CLK field. When the CLKOFF bit is set, the processor clock will be turned off at the end of the execution of the current microinstruction. The clkoff pseudo operator is independent of field assignments to the CLK field and may occur anywhere on a MICRO/40 line. That is, the microassembler implicity combines the clkoff pseudo operator with the specification of the processor clock cycle length.

### 2.5.2 NOOP

The noop pseudo operator is implemented to provide a means for generating a null (all microoperation fields set to o) microinstruction. This operator is needed, as a blank line is skipped by the microassembler and does not generate a microinstruction. The noop pseudo operator is to be used on a line by itself. It is ignored, if it occurs together with other MICRO/40 statements, such as field assignments or assignment statements.

## 2.5.3 FINIS

The finis pseudo operator indicates the end of the microcode source file. Any text following finis is ignored by MICRO/40. The finis pseudo operator is to be used on a line by itself. It does not generate an object microinstruction. If the microcode source file does not contain finis, the microassembler issues a warning and automatically inserts the finis pseudo operator into the source microcode (as the last line of the source file).

# 2.5.4 Dot(.)

The pseudo operator, dot(.), generally stands for the control store address of the microinstruction in which it occurs. There are two alternative applications of '.'.

The dot (.) may be used in field assignments (cf. subsection 2.2.2) to assign the control store address of the current microinstruction to the XUPF or EMIT fields. In these field assignments, the dot is used as follows:

emit = .

or xupf = .

Note that the address of the current microinstruction need not explicity be stated in the microinstruction, but is determined during assembling. MICRO/40 automatically assigns values to the xupf field, and thereby, may even rearrange the microinstructions as given in the source microcode into a different ordering in the object code, in order to guarantee that the xupf field of a microinstruction that must proceed any particular microinstruction points to the correct control store location.

The second application of '.' is to force MICRO/40 to locate a micro-instruction at a particular control store location. To this end, an octal control store address is explicity assigned to the dot. The syntax for assignments to the dot is:

. = <value>

where <value> must be in the range  $[2000_8: 3777_8]$  (RAM address space). The 'dot' assignment may occur anywhere on a MICRO/40 line.

## 2.5.5 LOWLIM

This pseudo operator provides a means to set the lowest control store address into which object microcode will be stored. The lowlim pseudo operator is used as follows:

lowlim = <value>

where <value> must be in the range[2000<sub>8</sub>: 3777<sub>8</sub>]. If this pseudo operator does not occur in a microcode source file, lowlim is automatically set to the default value 2000. If used, lowlim = <value> should be the first MICRO/40 line in the microcode source file.

# 2.5.6 C., N.Z.V., N.Z.V.C.

These pseudo operators set the SPS (Select Processor Status) field in the microinstruction and enforce an appropriate processor clock cycle length in the CLK field. The condition codes N,Z,V, and C in the processor status word are defined as follows:

- N=1, if the result of the last ALU operation was negative,

- Z=1, if the result of the last ALU operation was zero,

- V=1, if the last ALU operation resulted in an arithmetic overflow,

- C=1, if the last ALU operation resulted in a carry from the most significant bit.

The pseudo operators c.,n.z.v., and n.z.v.c. set the SPS field to the values 1, 2, and 3, respectively, to cause the associated condition code bits in the processor status word to be set to the current conditions. Microinstructions which contain one of these pseudo operators must have a P1 or P3 processor clock cycle (cf. [1,9]). The pseudo operators c., n.z.v., and n.z.v.c. are mutually exclusive and may occur anywhere on a MICRO/40 line.

### 2.5.7 TABLE

The table pseudo operator facilitates the use of parts of the writable control store as a data scratch pad. Using explicit field assignments (cf. RAM references, subsection 2.2.2) the RAM may also be utilized as data scratch pad. However, it is difficult to explicitly generate addresses of 16-bit RAM fields at run time. The table pseudo operator greatly supports the microprogrammer in this address generation by allowing for relative addressing within a declared data scratch pad. It allocates four 16-bit data words in an 80-bit control store location and treats a table as a zero origin array. Note that five 16-bit entries are actually available in an 80-bit control store location, but that it is difficult to generate the address of the fifth entry (cf. [1,9]).

The syntax for table declarations and references is:

::= table <size>

::= <identifier>

<size>::= <number>

::= [],

where is a number in the range [0:<size>]. The following example illustrates the above syntax definition.

table INFO 15

INFO [0] refers to the first table entry.

INFO [1] refers to the second table entry.

:

INFO [14] refers to the fifteenth table entry.

The pseudo operator, table, would reserve 4 control store locations for the table, INFO, as  $15_8$  corresponds to  $13_{10}$ . The table reference INFO[14] is equivalent to INFO[12.].

A table declaration should be placed on a line by itself, and may appear anywhere in the microprogram. The legal occurrences of table references in MICRO/40 assignment statements are defined in subsection 2.3.2. However, table references can only be made following table declarations. The number of table declarations is limited to 20 tables. The size of tables is limited by the number of RAM locations that are not utilized by the code of the microprogram that contains the table declarations.

## 2.5.8 PRELOAD

The preload pseudo operator is similar to a table declaration, except that instead of a size specification, a list of values that are preloaded into the table is specified. The table size corresponds to the number of elements in the list. The syntax of preload is:

::= preload <value list>

::= <identifier>

<value list>::= <number> | | <value</pre>

list>{,}<number>|<value list>{,}

The elements of the value list are considered to be assembly time constants. Hence, references to declared tables may occur in the value list.

The use of the preload pseudo operator is demonstrated by the following example:

preload DATASET 5,2,3,4, INFO[2]

This statement causes the reservation of two control store locations to store the following five table entries:

| DATASET[0] | contains the value 5,                    |

|------------|------------------------------------------|

| DATASET[1] | contains the value 2,                    |

| DATASET[2] | contains the value 3,                    |

| DATASET[3] | contains the value 4,                    |

| DATASET[4] | contains the control store field address |

|            | allocated for the storage of INFO[2].    |

The preload pseudo operator must be placed on a line by itself. The violation of this rule causes an error.

## 2.5.9 SET...TES

This compound pseudo operator supports microinstruction sequencing and conditional branching. As the PDP-11/40E has no microinstruction counter, each microinstruction contains the control store location of the microinstruction to be executed next in its xupf field. Conditional branches are specified in the ubf field and cause basic microbranch conditions (BUBCs) to be ORed into the low-order bits of the XUPP segment (xupf field) of the microinstruction buffer. Furthermore, the EMIT field or values from the WCS 11/40 stack may be gated onto the 11-bit EUBC BUS, in order to be ORed into the XUPP segment of the microinstruction buffer. The timing of microbranches in the PDP-11/40E is such that BUBC and EUBC address bits alter the xupf field of the microinstruction whose execution succeeds the execution of the microinstruction that contains the microbranch specification. Additionally, ORing of address bits allows only for forward conditional branches. Therefore, it is necessary that the control store locations of the expected branch destinations have identical address bits, except for those bits which may be turned on by the BUBC or EUBC address bits.

The PDP-11/40E microbranch mechanism may be enforced by using the dot pseudo operator (. = <value>) to put the microinstructions to be reached as branch destinations into the appropriate control store locations. The set... tes pseudo operator is implemented to obviate this need for explicit control store address allocation. That is, it makes the PDP-11/40E microbranch mechanism transparent for the microprogrammer. The set...tes pseudo operator is used as follows:

```

("controlled"  \begin{cases} < microinstructions \ to \ be \ reached \ as \\ branch \ destinations > \\ tes \end{cases} .

```

The keywords, set and tes, must each appear on separate lines by themselves. The number of set...tes groups in a microprogram must not exceed 150.

In the assembly process, MICRO/40 counts the "controlled" microinstructions, finds an appropriate number of contiguous control store locations with 2<sup>n</sup> address boundaries, and stores the "controlled" microinstructions into these locations. Therefore, it is illegal to assign a microinstruction that is controlled by a set...tes pseudo operator to a specific control store location (by using . = <values>). The xupf field of all microinstructions that are affected by BUBC or EUBC address bits that provide an entry into a group of "controlled" microinstructions are set to the control store address of the first microinstruction of that set...tes group. The default value of the xupf fields of all "controlled" microinstructions (which is automatically set by MICRO/40, if no field assignment is made to xupf) is the control store location of the microinstruction following the set...tes group. Note that the assembly of the set...tes pseudo operator may rearrange the microinstructions as given in the source microcode into a different ordering in the object microcode.

We may now rewrite the microprogram for adding the numbers from 1 to 10 using the set...tes pseudo operator (cf. subsection 2.3.2).

d\_0; R[0]\_d

b\_10

set

tes

d\_R[0]+b; R[0]\_d; xupf=loop

next: <whatever comes next>

Note that the field assignment, xupf=n, in the microinstruction with label, loop, can be omitted, as the appropriate microinstruction is reached by the default xupf field assignment in the set...tes group. Furthermore, the first microinstruction of <whatever comes next> may be concatenated to the microinstruction, xupf=next, in the set...tes group.

#### 2.5.10 START...END

The basic set...tes mechanism does not lend itself to the execution of more than a single microinstruction at each branch destination. To overcome this difficulty, the start...end pseudo operator has been implemented. It can only be used within a set...tes group, i.e.,

<"controlled" microinstructions>

start

<microinstructions to be executed at a single branch destination>

end

<"controlled" microinstructions>

tes

.

The keywords, start and end, must each appear on separate lines by themselves.

A compound set...tes - start...end construct is assembled, such that the first microinstruction of each start...end group and all single "controlled" microinstructions are placed into the block of microinstructions associated with the set...tes pseudo operator. The remaining microinstructions in the start...end groups are linked to the set...tes group by setting the xupf field of the first instructions in the set...tes group to the control store address of its start...end group successor. The xupf default value of the last microinstruction in each start...end group is the control store address of the microinstruction following the set...tes group.

<microinstruction 0>

set

<microinstruction 1>

<microinstruction 2>

start

<microinstruction 3>

<microinstruction 4>

<microinstruction 5>

set

<microinstruction 6>

<microinstruction 7>

tes

<microinstruction 8>

end

<microinstruction 9>

tes

<microinstruction 10>

:

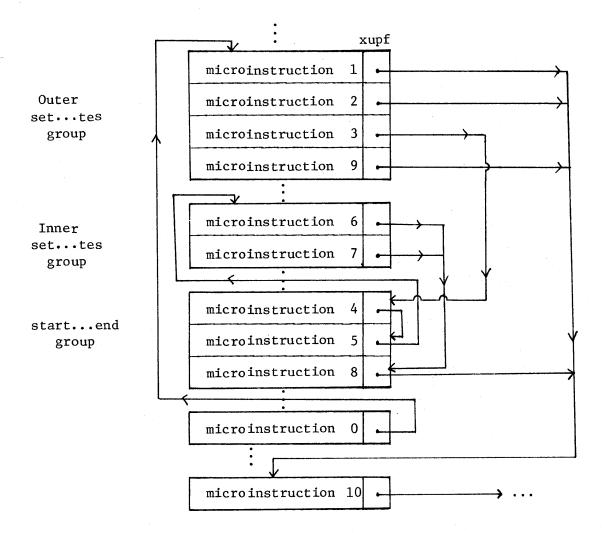

Figure 2: A Compound set...tes - start...end Construct

Figure 3: Control Store Allocation for a Compound set...tes - start...end Construct

The nesting of set...tes groups is generally permissible. However, they can only be nested within start...end groups, as the delay effect of conditional microbranches in the PDP-11/40E prohibits the placement of the first "controlled" microinstruction of an inner set...tes block within the outer set...tes group. That is, the pseudo operator, set, may appear anytime after the first microinstruction in a start...end group. There is no limit on the depth of set...tes group nestings, as long as the internal stack of MICRO/40 does not overflow. The control store allocation mechanism for a compound set...tes - start...end construct is illustrated in Fig.2 and Fig.3.

#### 2.6 Macros

MICRO/40 has a macro definition facility which allows the microprogrammer to identify sequences of assembly language statements by mnemonics. The primary use of macros is to make hardware dependencies of the MICRO/40 assembly language transparent for the user by generating macro libraries in the form of common source files. Appropriate macro name selections may greatly enhance the legibility of microprograms.

## 2.6.1 Macro Definition

A macro definition consists of a header, a body, and a terminator. The macro header is composed of a macro name and a declaration symbol (:=). Note that macros take no parameters. The macro body is a sequence of MICRO/40 statements that does not contain a dollar sign (\$) or an exclamation point(!). Any legal MICRO/40 statement is allowed in the macro body, except for macro definitions and set...tes pseudo operators. Note that macro definitions may contain other macros. The dollar sign is the macro definition terminator. The syntax of a macro definition is:

Fig. 4 shows a listing of the MICRO/40 source file, defs. mic, which includes macro definitions which have been found to be of general use.

```

! standard definitions for micro -- 11 October 1974

rev: 19 November 1974

rev:

7 December 1974

rev: 11 June 1975

r2 := r[2]$;

r0 := r[0]$; ·

r1 := r[1]$;

r5 := r[5]$;

r7 := r[7]$

r6 := r[6]$;

r4 := r[4]$;

r13 := r[13]$

r10 := r[10]$;

r11 := r[11]$;

r12 := r[12]$;

r15 := r[15]$;

r16 := r[16]$;

r17 := r[17]$

r14 := r[14]$;

PSP 1= PFA75;

rpc := r[7]$;

rdf := rEdf3$;

rsf := r[sf]$

temp := r[10]$; rsrc := r[11]$; rdst := r[12]$

rir := r[13]$; vect := r[14]$; temc := r[15]$

spus := r[16]$; adrsc := r[17]$;

rba := r[ba]$

dati := bus=1$;

dato := bus=5$

datob := bus=7$

datip := bus=3$;

₽3 :=clk =6$

besin := bes: .=2000;$

soto := xuef =$;

case := eubc_$; popst := d_s$

case := euoc_*; popst := d_s:

but := ubf = $\frac{1}{2}$ ! skip on d = 0

return := eubc_s$; endproc := xupf=0$

smod := 11:9$; dmod := 5:3$; prop := cp=1$

! end of macros

! ADDITIONAL MACROS

POP:=DEST=1;MSC=4*

PUSH:=DEST=1;MSC=3$

```

## 2.6.2 Macro References

Macros are referenced by their names. They may be referenced any-where in a microprogram, as long as they are preceded by their definition in the MICRO/40 source file. Upon reference, the macro name is substituted by its macro body. This substitution is a strict text substitution. After a macro is expanded, the macro text is checked again for macro references. If further macro references are encountered, they are substituted, before the assembler proceeds processing of the actual source microcode.

All macros that are referenced within a macro must be defined outside that macro, as macro definitions are not allowed within macros. Furthermore, recursive macro expansion is not permissible. Macro expansions do not place a delimiter at the end of the expanded text. Hence, it is possible to concatenate MICRO/40 statements across the macro expansion. That is, a single microinstruction may be generated from a combination of macros and MICRO/40 statements, or macros may be referenced within MICRO/40 statements. Obviously, the control store allocation mechanism of the set... tes pseudo operator (cf. subsection 2.5.9) is not supported by this macro expansion technique, and thus, the use of set...tes groups in macros is not permissible.

#### 2.6.3 Common Source Files

It is often desirable to include the same source microcode into several assemblies. This is especially true for macro files of a macro library. For example, the file, defs.mic, should be included into every source file to make microprograms more legible. To this end, the 'require' statments has been implemented.

The syntax for the use of common source files in a microprogram is:

'require' files.

To illustrate the use of macros and common source files we revisit the microprogram for adding the numbers from 1 to 10 (cf. subsection 2.5.9).

require defs.mic

d\_0; r0\_d

b\_10

set

loop: d\_177777 +b; b\_d; skipzero

goto next; <first microinstruction of whatever comes next>

tes

d\_r0+b; r0\_d; goto loop

next: <whatever comes next>

# 3. Features of MICRO/40

In this section, some of the more subtle features of the PDP-11/40E are outlined, that should be remembered when microcoding. Some microprogramming techniques that proved to be of general use [1] are described. However, as mentioned in the introduction, microprogramming requires careful algorithm design and coding on the basis of a solid understanding of both the algorithm and the machine. This is especially true for machines with horizontal microinstructions, where any arbitrary bit pattern may be assigned to a microinstruction, and the machine tries to execute any of these bit patterns. The microprogram testing and debugging facilities in our microprogramming support system are not comprehensive, and may not be sufficient to scope with unpredictable and hardware-dependent microprogram errors.

#### 3.1 Microinstruction Timing

One of the major objectives in the development of the WCS 11/40 was to retain the processor cycle times of the basic PDP-11/40 processor. Therefore, the three processor clock cycles length, CLKL 1, CLKL 2, and CLKL 3, as provided by the PDP-11/40 timing control logic have been adopted for the execution of microinstructions from the WCS 11/40 control stores. The processor clock cycles are defined as follows:

- CLKL 1 generates a P1 pulse 140 ns after the start of the microinstruction execution,

- CLKL 2 generates a P2 pulse 200 ns after the start of the microinstruction execution,

- CLKL 3 generates a P2 pulse and a P3 pulse 200 ns and 300 ns after the start of the microinstruction execution, respectively.

A detailed description of PDP-11/40E timing characteristics is given in [9]. Table 1 associates permissible processor clock cycle times with the basic carrier-to-carrier transfer in the PDP-11/40E.

| Carrier-to-Carrier                         | Permissible  |

|--------------------------------------------|--------------|

| Transfer                                   | Clock Cycles |

| B ← DMUX BUS                               | P1, P3       |

| B ← SMUX                                   | Р3           |

| PS ← DMUX BUS                              | P1, P3       |

| PS ← SMUX                                  | Р3           |

| R[i] ← DMUX BUS                            | P1, P3       |

| R[i] SMUX                                  | Р3           |

| IR ← DMUX BUS                              | P1, P3       |

| IR ← SMUX                                  | Р3           |

| CLK PS(C)                                  | P1, P3       |

| CLK PS(N,Z,V)                              | P1, P3       |

| CLK PS(N,Z,V,C)                            | P1, P3       |

| BA ← BA MUX                                | P1, P2       |

| D ← ALU                                    | P2           |

| D(C) ← COUT MUX                            | P2           |

| D ←ALU; DMUX BUS ← D                       | Р3           |

| ALU CIN ← CPFF                             | Р3           |

| CPFF ← COUT MUX[SCOM]                      | Р3           |

| TOS ← EMUX                                 | P1, P2, P3   |

| TOS ← RD BUS                               | P2, P3       |

| SP ← SP+1                                  | P1, P2, P3   |

| SP ← SP-1                                  | P1, P2, P3   |

| SP + XU < 75: 72>                          | P1, P2, P3   |

| $SP \leftarrow SP-1$ ; $S \leftarrow EMUX$ | P2, P3       |

| SP + SP+1; SMUX + S                        | P1, P2, P3   |

| EUBC ← SMUX                                | P2, P3       |

| RAM ← DMUX                                 | Р3           |

| SMUX ← RAM                                 | Р3           |

Table 1: Carrier-to-Carrier Transfer Timing

The microassembler analyzes the microoperations (carrier-to-carrier transfers) specified in an input line and assigns a proper processor clock cycle for the execution of that microinstruction. If the processor cycle time is set by the microprogrammer, the microassembler check is skipped. Thus, an incorrect processor cycle time setting is not detected by MICRO/40, and no error message is given. This feature of the microassembler is due to the fact that microinstructions are assembled individually, but the appropriate processor cycle times may depend on preceding microinstructions. For example, the microinstruction following a microinstruction that contains the clkoff pseudo operator must have a CLKL 1 or CLKL 3 processor clock cycle. Although it is advisable (and convenient) to let the microassembler assign appropriate processor clock cycle lengths, the microprogrammer should know the execution time requirements for each microinstruction to be able to determine the relative performance of alternative microinstruction sequences.

#### 3.2 UNIBUS Control

The PDP-11/40 processor control is a combination of synchronous and asynchronous operations. Carrier-to-carrier transfers as discussed in the preceeding subsection are synchronous operations. Asynchronous timing conditions evolve in UNIBUS operations and are controlled by the UNIBUS timing and control logic. To synchronize UNIBUS operations with synchronous precessor operations, the processor clock may be turned off upon microinstruction execution and restarted by the UNIBUS timing and control logic (for more detail, cf. [1], [8], [9]).

The microprogrammer must explicity control UNIBUS operations, which allow uniform access to main memory and peripheral registers. On the one hand, explicit UNIBUS control provides an opportunity to optimize the implementation of machine language instructions which involve UNIBUS transfers. On the other hand, it represents a source of timing errors.

UNIBUS operations are controlled by the microoperation field, BUS=CBUS, BGBUS, with CBUS= C1,C0 (cf. subsection 2.2.1). The BUS field definitions are given below.

| BUS | C1 | C0 | BG | Operation                     |

|-----|----|----|----|-------------------------------|

| 0   | 0  | 0  | 0  | not defined                   |

| 1   | 0  | 0  | 1  | DATI (word operation)         |

| 2   | 0  | 1  | 0  | await BUS BUSY                |

| 3   | 0  | 1  | 1  | DATIP (read-modify-write)     |

| 4   | 1  | 0  | 0  | not defined                   |

| 5   | 1  | 0  | 1  | DATO (word operation)         |

| 6   | 1  | 1  | 0  | restart on peripheral release |

| 7   | 1  | 1  | 1  | DATOB (byte operation)        |

C1 and C0 determine which of the four possible read/write operations will occur and BGBUS initiates the action. During UNIBUS operations, the UNIBUS address is held in the BA Register. Output data are stored in the D Register, and input data are received at D MUX.

# 3.2.1 UNIBUS READ Operations

For a READ operation (data input), the UNIBUS address must be available in the BA Register, when the DATI UNIBUS control code is asserted. Succeeding microinstructions may be executed while the UNIBUS READ is carried out, as long as they do not modify the BA Register or assert another UNIBUS control code. However, it is necessary to set clkoff, before the input data are accepted. Upon completion of the READ operation, the data will be present on the UNIBUS and the processor clock is restarted. If the UNIBUS completes its read cycle before a clkoff is asserted, the processor clock does not stop. The microinstruction following the microinstruction containing the pseudo operator clkoff must have a CLKL 1 or CLKL 3 processor clock cycle, and must pull the input data off the UNIBUS immediately.

A typical UNIBUS READ cycle has the following form (cf. Fig. 4).

ba\_R[i]; dati !BUS=1, put UNIBUS address into BA

{any number of microinstructions that do not modify BA or

assign a value to the BUS field}

<last microinstruction>; clkoff

R[j]\_unibus; <other statements> !CLKL 1 or CLKL 3 clock cycle

As a more specific example, we may consider the following microinstruction sequence for popping the PDP-11/40 main memory stack.

ba\_R[6]; dati ! read top of stack

d\_R[6] + 2; R[6]\_d; clkoff ! increment stack pointer

R[2]\_unibus

The DATI UNIBUS control code is used for both word and byte operations. It always returns a 16-bit word to D MUX. To select a byte the main memory address must be tested. If this address is even (BA<0>= 0), the byte is in the lower half of the word. If this address is odd (BA<0>=1), the byte is in the upper half of the word. BUT 35 (ubf=35) may be used to perform the address test. Alternatively, the assignment statement, EUBC  $\leftarrow$  TOS<0>, may be used, if the UNIBUS address is stored in TOS. The B Register, together with B MUX, may be used to align the appropriate byte.

## 3.2.2 UNIBUS WRITE Operations

UNIBUS WRITE operations are similar to READ operations. The following differences should be observed. For a WRITE operation (data output), the UNIBUS address must be available in the BA Register and the output datum must be clocked to the D Register, when the DATO UNIBUS control code is asserted. Succeedingly executed microinstructions must keep the BA Register and the D Register constant.

A typical UNIBUS write cycle has the following form (cf. Fig. 4).

ba R[i] ! put UNIBUS address into BA

d R[j]; dato ! BUS=5, put datum into D

{any number of microinstructions that do not modify BA

and D, or assign a value to the BUS field}

<last microinstruction>; clkoff

<any microinstruction with a CLKL 1 or CLKL 3 clock cycle>

As a specific example, we consider the following microinstruction sequence for pushing the PDP-11/40 main memory stack.

d,ba\_R[6]-2; R[6]\_d ! decrement stack pointer

d R[2]; dato; clkoff ! write to top of stack

The DATOB UNIBUS control code specifies a byte WRITE operation. The microinstruction for the implementation of a byte WRITE operation is similar to that for DATO. It is the microprogrammer's responsibility to place the byte to be written into the proper byte of the D Register. As a safeguard for the case that the main memory address may either be even (low-order byte) or odd (high-order byte), the byte to be written should be duplicated in both bytes of the D Register. The B Register, together with B MUX, may be used for this purpose.

## 3.2.3 UNIBUS READ - MODIFY - WRITE Cycle

The DATIP UNIBUS control code specifies a READ - MODIFY - WRITE cycle. It uses the address in the BA Register both for the READ and the WRITE operation. A microinstruction sequence for a UNIBUS read-modify-write cycle is given below. This microinstruction sequence implements a modification of the top of the PDP-11/40 main memory stack.

ba\_R[6]; datip; clkoff ! put UNIBUS address into BA

! BUS=3

R[10]\_unibus ! read top of stack

d\_R[10]+1; dato; clkoff ! modify top of stack, BUS=5

<any microinstruction with a CLKL 1 or CLKL 3 cycle>

## 3.2.4 Exceptional Conditions

The ability to perform UNIBUS operations and execute microinstructions in parallel provides the microprogrammer with the opportunity to keep the processor totally UNIBUS-bound, while doing processing in addition to UNIBUS control. Care must be taken that all initiations of UNIBUS operations are followed by a clkoff. Otherwise, the UNIBUS becomes locked. On the other hand, setting clkoff, without setting BGBUS halts the processor and requires a restart from the processor console, except for interrupt sequences.

Whenever an odd address is clocked into the BA Register, or the DATOB UNIBUS control code is asserted, the following two conditions must be met. First, the instruction register must contain a valid machine language byte instruction. Second, bit 0 of the DAD field must be set (allow odd address and DATO for byte instruction). If these conditions are not met, a jam into the 8 low-order bits of XUPP (segment of the microinstruction buffer) occurs and the flow of control in the user microcode will be distorted. This effect is due to the fact that the jam addresses are associated with the standard PDP-11/40 emulator microinstructions, not with the user microporgram.

# 3.3 Data Flow

The following idiosyncrasies which are caused by the PDP-11/40E data paths and functional hardware units should be remembered when writing microcode.

## 3.3.1 RD BUS

As discussed in section 2.3.3, the result of gating several independent sources onto the RD BUS is the ORing of the source contents. This feature of

the RD BUS may be exploited to produce a positive effect, when a table lookup is to be performed into a table of fixed main memory locations that is indexed by a general purpose register.

For example, let R[0] be assumed to hold the table index, which must be even for word addressing. Let BASE be the base address of the table in main memory. Then, the following microinstruction implements a table access,

ba\_R[0]; dest=0; msc=1; emit=BASE; dati

The field assignments, dest=0, msc=1, specify the transfer RD BUS  $\leftarrow$  EMIT. Hence, the content of R[0] and the EMIT field are ORed on the RD BUS, i.e., RD BUS  $\leftrightarrow$  R[0] or BASE. BASE should be chosen such that it has at least as many zeros in its low-order bits as there are non-zero low-order bits in the binary representation of the largest table index, i.e., such that R[0] + BASE = R[0] or BASE. Then, the value clocked into the BA Register is the effective word address of a table entry, R[0] + BASE = <index> + <base address>.

To obtain the same result, without using the ORing feature of the RD BUS, requires the following two microinstruction

d\_R[0]; b\_d

ba\_BASE + B; DATI

# 3.3.2 CONSTANTS

The WCS 11/40 provides the microprogrammer with arbitrary arithmetic and addressing constants via the EMIT field. However, EMIT field constants must be A-inputs to the ALU or must temporarily be stored in the B Register to be usable as ALU B-inputs. The latter mechanism requires the execution of two consecutive microinstructions for the use of an EMIT field constant at the ALU. This difficulty can often be overcome by using one of the B CONSTANTS as provided by the basic PDP-11/40E processor. The use of B CONSTANTS instead of EMIT field constants at the ALU B-input may save up to 300 ns in the execution of the associated microinstruction sequence.

# 3.3.3 Instruction Register

The PDP-11/40 processor is implemented for the specific PDP-11/40 machine instruction set and, as a consequence, is not of general-purpose nature. The basic machine instruction decoding generates basic microbranch codes (BUBCs) for several branch microtests (BUTs), signals required by the microbranch control logic, the condition code control logic, and the ALU control logic. Hence, the contents of the instruction register (IR) may affect the data paths and the ALU, as they are not exclusively controlled by the micro-

instruction. Some PDP-11/40 machine language instructions (e.g., SBC, RESET, MFPI, MTPI) may even have an effect on the data paths, when the instruction register is clocked the next time [8]. Therefore, great care must be taken, if IR is used by user microprograms. In user microprograms, it is advisable to decode machine instruction from TOS by using the WCS 11/40 shift/mask unit to pull various instruction fields from TOS onto the EUBC BUS(for conditional branching).

#### 3.4 Control Flow

In this section, we discuss basic mechanisms for the sequencing of microinstruction executions.

#### 3.4.1 Microinstruciton Execution

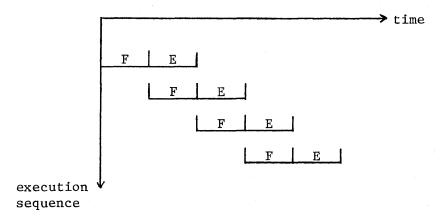

With the last pulse edge of each processor cycle, a microinstruction is gated into the microinstruction buffer. Thus, the interval between the loading of two seccessive microinstructions into the microinstruction buffer is a function of the processor cycle length of the first microinstruction. This organization requires that the execution (E) of the current microinstruction and the fetch (F) of the successor microinstruction are overlapped in time. This overlap is illustrated in Fig. 5.

Figure 5: Microinstruction Fetch/Execute Overlap

## 3.4.2 Unconditioned Microinstruction Sequences

MICRO/40 handles unconditioned microinstruction sequences by assigning control store addresses to the xupf fields in microinstructions. The basic rule is to assign consecutive addresses to successive microinstructions, unless a 'goto' (xupf field assignment) is assembled. In the latter case, the control store address specified in the 'goto' is assigned to the xupf field. Hence, at the beginning of the execution of a microinstruction with an unconditioned

successor, the address of the next microinstruction is available in the XUPP segment of the microinstruction buffer.

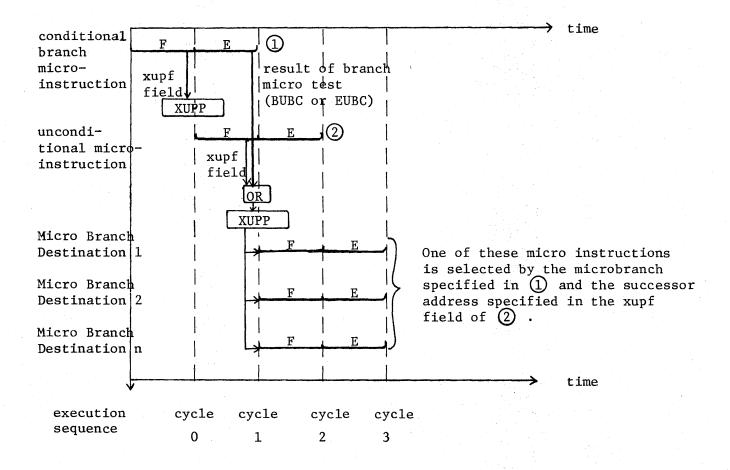

# 3.4.3 Conditioned Microinstruction Sequences

Whenever a microinstruction is clocked into the microinstruction buffer, XUPP is modified by ORing the 11 bits of the EUBC BUS and the six BUBC bits (into the six low-order bits of XUPP). The modified XUPP is immediately used to address the successor microinstruction. At this point, an alteration of the address of the successor microinstruction as specified in the current microinstruction has not occurred. Hence, it is impossible for a microinstruction to influence the address of its successor. Instead, conditional branching is performed by setting the EUBC/BUBC lines such that the address in the xupf field of the successor microinstruction are altered. This organization of conditional microbranches is illustrated in Fig. 6.

Figure 6: Conditional Microbranching

The delayed microbranching in the PDP-11/40E is unnatural to most programmers and requires great care, as it makes microprograms difficult to modify, because of the interdependence of microinstructions in a branching sequence. Furthermore, since conditional branching is due to ORing into XUPP, the proper bits in XUPP must be 0 for the ORing to have the right effect. MICRO/40 supports the microprogrammer in satisfying this requirement by the provision of the set...tes pseudo operator. A set...tes construct is assembled by allocating a block of RAM locations with 2<sup>n</sup> address boundaries for the storage of the microinstructions at the branch destinations. As MICRO/40 allocates control store blocks for all set...tes groups, before it assigns RAM locations to the rest of the microinstructions, the base addresses of set...tes blocks can be chosen to include an appropriate number of 0's.

The PDP-11/40E provides the following two mechanisms for setting the bits to be ORed into XUPP. Examples for the application of these mechanisms are discussed in the next two subsections.

#### BUT

The branch micro test (BUT) is a feature of the basic PDP-11/40. It consists of about thirty different tests which are invoked by field assignments to ubf (cf.[1], [8]). Branch micro tests detect particular processor states and, in response, set appropriate values on the BUBC lines. The generally useful BUTs are:

| ubf | BUT       | BUBC   |

|-----|-----------|--------|

| 12  | D=0       | 000001 |

| 16  | interrupt | 000001 |

#### EUBC

The extended microbranch control (EUBC) is based on the shift/mask unit in the WCS 11/40. Using this field extraction unit, arbitrary contiguous fields of the word at the top of the stack, the EMIT field, or any 16-bit RAM field can be gated onto the 11-bit EUBC BUS.

## .3.4.4 IF Statement

A simple IF statment,

IF<condition>THEN<microinstructions1>ELSE<microinstructions2>, may be implemented using the BUT mechanism or the EUBC mechanism.

The following timing characteristics must be taken into account, when a BUT 12 is used. If the microinstruction containing BUT 12 has a CLKL 1 or

CLKL 2 processor clock cycle, then the value of the D Register at the beginning of the microinstruction execution is tested. If the microinstruction has a CLKL 3 clock cycle, the value clocked into the D Register with the P2 pulse is tested. The effect of this timing condition is demonstrated by the following two implementations of an IF statement with BUT 12.