# PDP-10 System Reference Manual

ORDER NO. DEC-10-HGAA-D FROM PROGRAM LIBRARY, MAYNARD, MASSACHUSETTS

PRICE \$5.00

DIRECT COMMENTS CONCERNING THIS MANUAL TO SOFTWARE QUALITY CONTROL, MAYNARD, MASSACHUSETTS

April 1968 Second printing, May 1968

Changes are indicated by a triangle (**A**) in the outside margin.

Copyright 1968 by

Digital Equipment Corporation

Written and designed for Digital Equipment Corporation by William English, Wayland, Massachusetts Manufactured in the United States of America

## 1

# Introduction

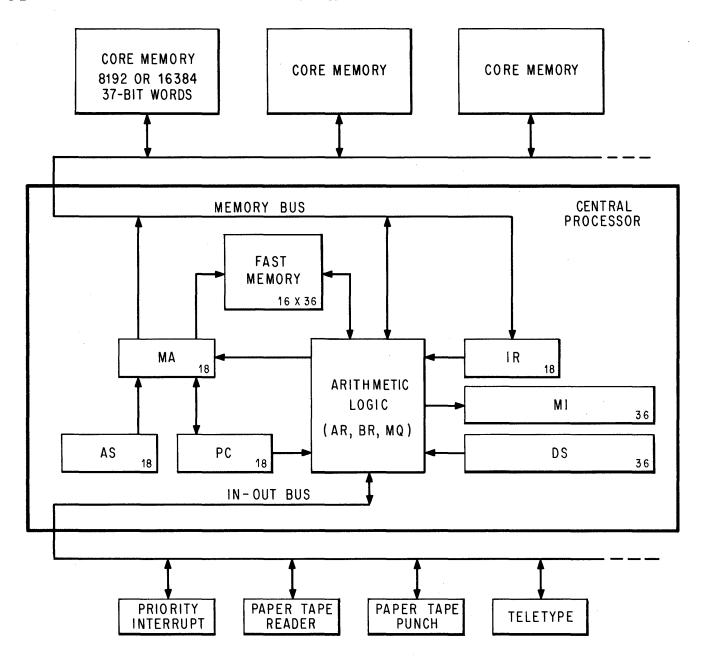

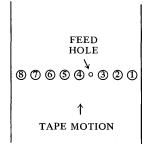

The PDP-10 is a general purpose, stored program computer that includes a central processor, a memory, and a variety of peripheral equipment such as paper tape reader and punch, teletype, card reader, line printer, DECtape, magnetic tape, disk file and display. The central processor is the control unit for the entire system: it governs all peripheral in-out equipment, sequences the program, and performs all arithmetic, logical and data handling operations. The processor is connected to one or more memory units by a memory bus and to the peripheral equipment by an in-out bus. The fastest devices, such as the disc file, although controlled by the processor over the in-out bus, have direct access to memory over a second memory bus.

The processor handles words of thirty-six bits, which are stored in a memory with a maximum capacity of 262,144 words. Storage in memory is usually in the form of 37-bit words, the extra bit producing odd parity for the word. The bits of a word are numbered 0-35, left to right, as are the bits in the registers that handle the words. The processor can also handle half words, wherein the left half comprises bits 0-17, the right half, bits 18-35. Optional hardware is available for byte manipulation — a byte is any contiguous set of bits within a word. Registers that hold addresses have eighteen bits, numbered 18-35 according to the position of the address in a word. Words are used either as computer instructions in the program, as addresses, or as operands (data for the program).

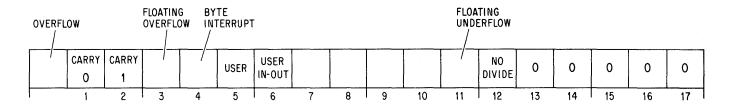

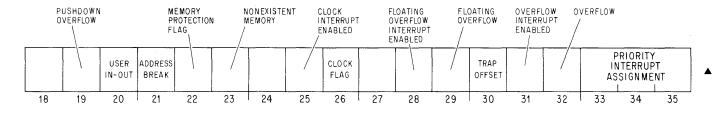

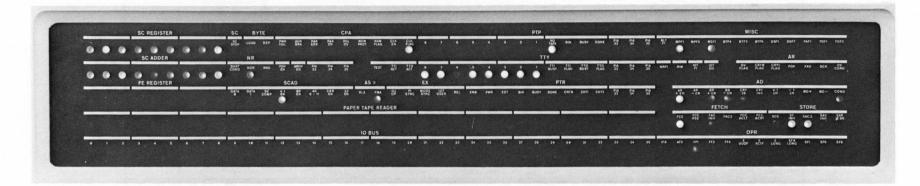

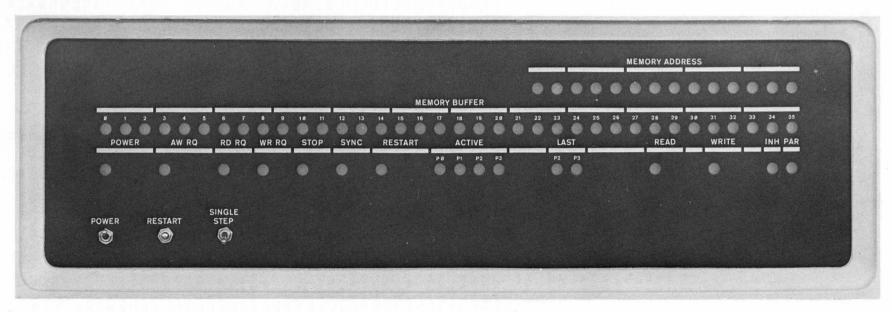

Of the internal registers shown in the illustration on the next page, only PC, the 18 bit program counter, is directly relevant to the programmer. The processor performs a program by executing instructions retrieved from the locations addressed by PC. At the beginning of each instruction PC is incremented by one so that it normally contains an address one greater than the location of the current instruction. Sequential program flow is altered by changing the contents of PC, either by incrementing it an extra time in a skip instruction or by replacing its contents with the value specified by a jump instruction. Also of importance to the programmer is the 36-bit data switch register DS on the processor console: through this register the program can read data supplied by the operator. The processor also contains flags that detect various types of errors, including several types of overflow in arithmetic and pushdown operations, and provide other information of interest to the programmer.

The processor has other registers but the programmer is not usually concerned with them except when manually stepping through a program to debug it. By means of the address switch register AS, the operator can

PDP-10 SIMPLIFIED

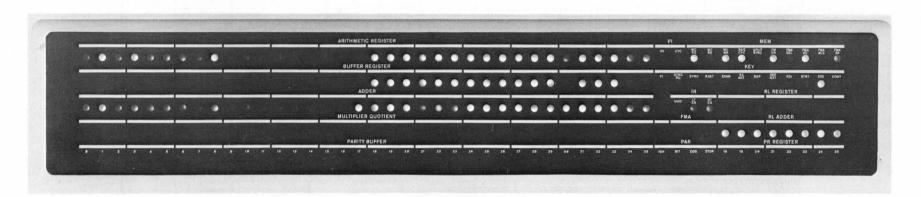

examine the contents of, or deposit information into, any memory location; stop or interrupt the program whenever a particular location is referenced; and through AS the operator can supply a starting address for the program. Through the memory indicators MI the program can display data for the operator. The instruction register IR contains the left half of the current instruction word, *ie* all but the address part. The memory address register MA supplies the address for every memory access. The heart of the processor is the arithmetic logic, principally the 36-bit arithmetic register AR.

This register takes part in all arithmetic, logical and data handling operations; all data transfers to and from memory, peripheral equipment and console are made via AR. Associated with AR are an extremely fast full adder, a buffer register BR that holds a second operand in many arithmetic and logical instructions, a multiplier-quotient register MQ that serves primarily as an extension of AR for handling double length operands, and smaller registers that handle floating point exponents and control shift operations and byte manipulation.

From the point of view of the programmer however the arithmetic logic can be regarded as a black box. It performs almost all of the operations necessary for the execution of a program, but it never retains any information from one instruction to the next. Computations performed in the black box either affect control elements such as PC and the flags, or produce results that are always sent to memory and must be retrieved by the processor if they are to be used as operands in other instructions.

An instruction word has only one 18-bit address field for addressing any location throughout all of memory. But most instructions have two 4-bit fields for addressing the first sixteen memory locations. Any instruction that requires a second operand has an accumulator address field, which can address one of these sixteen locations as an accumulator; in other words as though it were a result held over in the processor from some previous instruction (the programmer usually has a choice of whether the result of the instruction will go to the location addressed as an accumulator or to that addressed by the 18-bit address field, or to both). Every instruction has a 4-bit index register address field, which can address fifteen of these locations for use as index registers in modifying the 18-bit memory address (a zero index register address specifies no indexing). Although all computations on both operands and addresses are performed in the single arithmetic register AR, the computer actually has sixteen accumulators, fifteen of which can double as index registers. The factor that determines whether one of the first sixteen locations in memory is an accumulator or an index register is not the information it contains nor how its contents are used, but rather how the location is addressed. There need be no difference physically between these locations and other memory locations, but an optional, fast flipflop memory contained in the processor can be substituted for the bottom sixteen locations in core. This allows much quicker access to these locations whether they are addressed as accumulators, index registers or ordinary memory locations. They can even be addressed from the program counter, gaining faster execution for a short but oft-repeated subroutine.

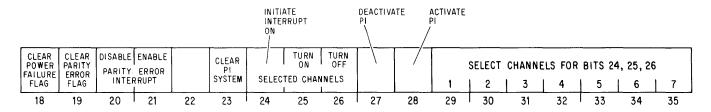

Besides the registers that enter into the regular execution of the program and its instructions, the processor has a priority interrupt system and can contain optional equipment to facilitate time sharing. The interrupt system facilitates processor control of the peripheral equipment by means of a number of priority-ordered channels over which external signals may interrupt the normal program flow. The processor acknowledges an interrupt request by executing the instruction contained in a particular location assigned to the channel. Assignment of channels to devices is entirely under program control. One of the devices to which the program can assign a channel is the processor itself, allowing internal conditions such as overflow or a parity

error to signal the program.

The time share hardware provides memory protection and relocation. Without time sharing, all instructions and all memory are available to the program. Otherwise a number of programs share processor time, with each program relocated and restricted to a specific area in core, and certain instructions are usually illegal. An attempt by any user to execute an illegal instruction or address a memory location outside of his area results in a transfer of control back to the time-sharing monitor.

#### 1.1 NUMBER SYSTEM

The program can interpret a data word as a 36-digit, unsigned binary number, or the left and right halves of a word can be taken as separate 18-bit numbers. The PDP-10 repertoire includes instructions that effectively add or subtract one from both halves of a word, so the right half can be used for address modification when the word is addressed as an index register, while the left half is used to keep a control count.

The standard arithmetic instructions in the PDP-10 use twos complement, fixed point conventions to do binary arithmetic. In a word used as a number, bit 0 (the leftmost bit) represents the sign, 0 for positive, 1 for negative. In a positive number the remaining 35 bits are the magnitude in ordinary binary notation. The negative of a number is obtained by taking its twos complement. If x is an n-digit binary number, its twos complement is  $2^n - x$ , and its ones complement is  $(2^n - 1) - x$ , or equivalently  $(2^n - x) - 1$ . Subtracting a number from  $2^n - 1$  (ie, from all 1s) is equivalent to performing the logical complement, ie changing all 0s to 1s and all 1s to 0s. Therefore, to form the twos complement one takes the logical complement (usually referred to merely as the complement) of the entire word including the sign, and adds 1 to the result. In a negative number the sign bit is 1, and the remaining bits are the twos complement of the magnitude.

Zero is represented by a word containing all 0s. Complementing this number produces all 1s, and adding 1 to that produces all 0s again. Hence there is only one zero representation and its sign is positive. Since the numbers are symmetrical in magnitude about a single zero representation, all even numbers both positive and negative end in 0, all odd numbers in 1 (a number all 1s represents -1). But since there are the same number of positive and negative numbers and zero is positive, there is one more negative number than there are nonzero positive numbers. This is the most negative number and it cannot be produced by negating any positive number (its octal representa-

tion is  $400000\,000000_8$  and its magnitude is one greater than the largest positive number).

If ones complements were used for negatives one could read a negative number by attaching significance to the 0s instead of the 1s. In twos complement notation each negative number is one greater than the complement of the positive number of the same magnitude, so one can read a negative number by attaching significance to the rightmost 1 and attaching significance to the 0s at the left of it (the negative number of largest magnitude has a 1 in only the sign position). In a negative integer, 1s may be discarded at the left, just as leading 0s may be dropped in a positive integer. In a negative fraction, 0s may be discarded at the right. So long as only 0s are discarded, the number remains in twos complement form because it still has a 1 that possesses significance; but if a portion including the rightmost 1 is discarded, the remaining part of the fraction is now a ones complement.

The computer does not keep track of a binary point — the programmer must adopt a point convention and shift the magnitude of the result to conform to the convention used. Two common conventions are to regard a number as an integer (binary point at the right) or as a proper fraction (binary point at the left); in these two cases the range of numbers represented by a single word is  $-2^{35}$  to  $2^{35} - 1$  or -1 to  $1 - 2^{-35}$ . Since multiplication and division make use of double length numbers, there are special instructions for performing these operations with integral operands.

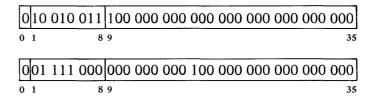

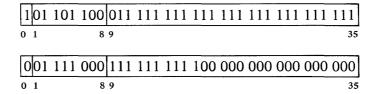

Floating Point Arithmetic. Optional PDP-10 hardware is available for processing floating point numbers. A floating point instruction interprets bit 0 of a word as the sign, but interprets the rest of the word as an 8-bit exponent and a 27-bit fraction. For a positive number the sign is 0, as before. But the contents of bits 9-35 are now interpreted only as a binary fraction, and the contents of bits 1-8 are interpreted as an integral exponent in excess  $128 (200_8)$  code. Exponents from -128 to +127 are therefore represented by the binary equivalents of 0 to  $255 (0-377_8)$ . Floating point zero and negatives are represented in exactly the same way as in fixed point: zero by a word containing all 0s, a negative by the twos complement. A negative number has a 1 for its sign and the two complement of the fraction, but since every fraction must ordinarily contain a 1 unless the entire number is zero (see below), it has the ones complement of the exponent code in bits 1-8. Since the exponent is in excess 128 code, an actual exponent x is represented in a positive number by x + 128, in a negative number by 127 - x. The programmer, however, need not be concerned with these representations as the hardware compensates automatically. Eg, for

$$+153_{10} = +231_{8} = +.462_{8} \times 2^{8} =$$

$$\boxed{0 | 10 | 001 | 000 | 100 | 110 | 010 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 000 | 00$$

mendery

Multiplication produces a double length product, and the programmer must remember that discarding the low order part of a double length negative leaves the high order part in correct twos complement form only if the low order part is null.

the instruction that scales the exponent, the hardware interprets the integral scale factor in standard twos complement form but produces the correct ones complement result for the exponent.

Except in special cases the floating point instructions assume that all non-zero operands are normalized, and they normalize a nonzero result. A floating point number is considered normalized if the magnitude of the fraction is greater than or equal to  $\frac{1}{2}$  and less than 1. These numbers thus have a fractional range in magnitude of  $\frac{1}{2}$  to  $1-2^{-27}$  and an exponent range of -128 to +127. The hardware may not give the correct result if the program supplies an operand that is not normalized or that has a zero fraction with a nonzero exponent.

The precaution about truncation given for fixed point multiplication applies to all floating point operations as they all produce extra length results; but here the programmer may request rounding, which automatically restores the high order part to twos complement form if it is negative. In division the two words of the result are quotient and remainder, but in the other operations they form a double length number which is stored in two accumulators if the instruction is executed in "long" mode. This number contains a 54-bit fraction, half of which is in bits 9-35 of each word. The sign and exponent are in bits 0 and 1-8 respectively of the word containing the more significant half, and the standard twos complement is used to form the negative of the entire 63-bit string. In the remaining part of the less significant word, bit 0 is 0, and bits 1-8 contain a number 27 less than the exponent, but this is expressed in positive form even though bits 9-35 may be part of a negative fraction. Eg the number  $2^{18} + 2^{-18}$  has this two-word representation:

whereas its negative is

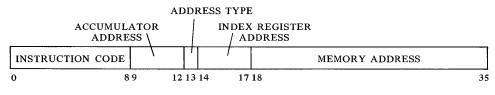

#### 1.2 INSTRUCTION FORMAT

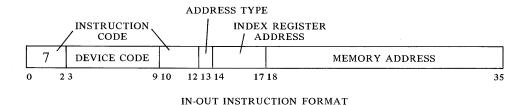

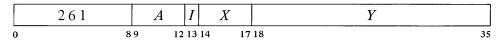

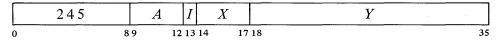

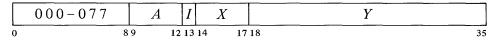

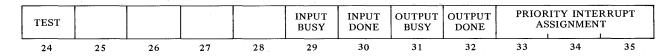

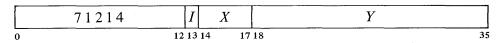

In all but the input-output instructions, the nine high order bits (0-8) specify the operation, and bits 9-12 usually address an accumulator but are sometimes used for special control purposes, such as addressing flags. The

rest of the instruction word usually supplies information for calculating the effective address, which is the actual address used to fetch the operand or alter program flow. Bit 13 specifies the type of addressing, bits 14–17 specify an index register for use in address modification, and the remaining eighteen bits (18–35) address a memory location. The instruction codes

BASIC INSTRUCTION FORMAT

that are not assigned as specific instructions are executed by the processor as so-called "unimplemented operations", as are the codes for floating point and byte manipulation in any PDP-10 that does not have the optional hardware for these instructions. When the processor encounters one of these unimplemented codes in a program, it stores bits 0-12 of the instruction word and the calculated effective address in a particular memory location and then executes the instruction contained in a second location.

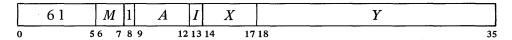

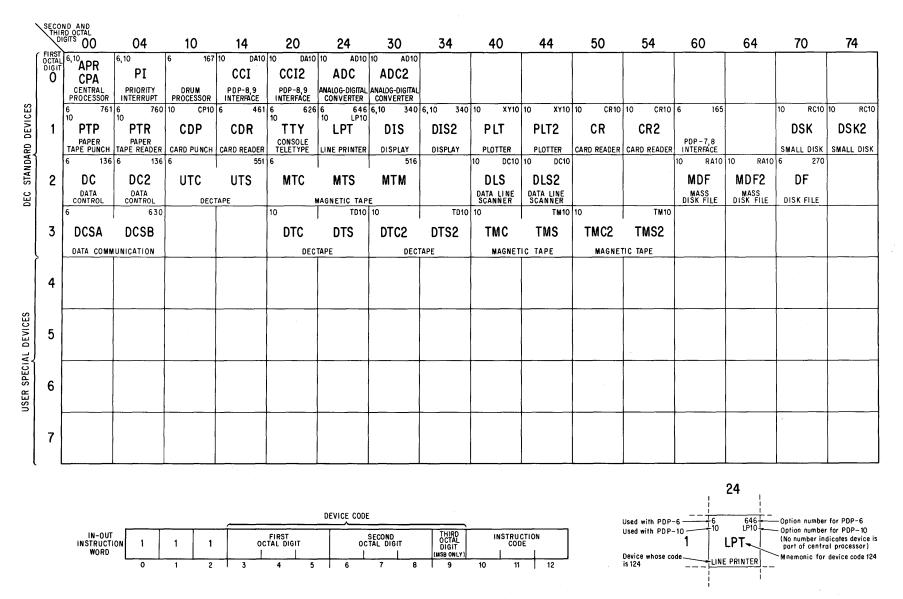

An input-output instruction is designated by three 1s in bits 0-2. Bits 3-9 address the in-out device to be used in executing the instruction, and bits 10-12 specify the operation. The rest of the word is the same as in other instructions.

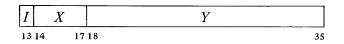

Effective Address Calculation. Bits 13–35 have the same format in *every* instruction whether it addresses a memory location or not. Bit 13 is the

indirect bit, bits 14-17 are the index register address, and if the instruction must reference memory, bits 18-35 are the memory address Y. The effective address E of the instruction depends on the values of I, X and Y. If X is nonzero, the contents of index register X are added to Y to produce a modified address. If I is 0, addressing is direct, and the modified address is the effective address used in the execution of the instruction; if I is 1, addressing is indirect, and the processor retrieves another address word from the location specified by the modified address already determined. This new word is processed in exactly the same manner: X and Y determine the effective address if I is 0, otherwise they are used for yet another level of address

retrieval. This process continues until some referenced location is found with a 0 in bit 13; the 18-bit number calculated from the X and Y parts of this location is the effective address E.

The calculation outlined above is carried out for every instruction even if it need not address a memory location. If the indirect bit in the instruction word is 0 and no memory reference is necessary, then Y is not an address. It may be a mask in some kind of test instruction, conditions to be sent to an in-out device, or part of it may be the number of places to shift in a shift or rotate instruction or the scale factor in a floating scale instruction. Even when modified by an index register, bits 18-35 do not contain an address when I is 0. But when I is 1, the number determined from bits 14-35is an indirect address no matter what type of information the instruction requires, and the word retrieved in any step of the calculation contains an indirect address so long as I remains 1. When a location is found in which I is 0, bits 18-35 (perhaps modified by an index register) contain the desired effective mask, effective conditions, effective shift number, or effective scale factor. Many of the instructions that usually reference memory for an operand even have an "immediate" mode in which the result of the effective address calculation is itself used as a half word operand instead of a word taken from the memory location it addresses.

The important thing for the programmer to remember is that the same calculation is carried out for every instruction regardless of the type of information that must be specified for its execution, or even if the result is ignored. In the discussion of any instruction, E refers to the actual quantity derived from I, X and Y and used in the execution of the instruction, be it the entire half word as in the case of an address, immediate operand, mask or conditions, or only part of it as in a shift number or scale factor.

#### 1.3 MEMORY

All timing in the PDP-10 is asynchronous. The internal timing for each inout device and each memory is entirely independent of the central processor. Because core memory readout is destructive, every word read must be written back in unless new information is to take its place. The basic read-write cycle time of the standard core memory is either 1.00 or 1.65 microseconds, but the processor need never wait the entire cycle time. To read, it waits only until the information is available and then continues its operations while the memory performs the write portion of the cycle; to write, it waits only until the data is accepted, and the memory then performs an entire cycle to clear and write. To save time in an instruction that fetches an operand and then writes new data into the same location, the memory executes a read-pause-write cycle in which it performs only the read part initially and then completes the cycle when the processor supplies the new data.

Access times for the accumulator-index register locations are decreased considerably by substitution of a fast memory (contained in the processor) for the first sixteen core locations. Readout is nondestructive, so the fast memory has no basic cycle: the processor reads a word directly, but to write

it must first clear the location and then load it. Access times in nanoseconds (including 20 feet of cable delay) for the three memories are as follows.

|                                     | Read       | Write     |

|-------------------------------------|------------|-----------|

| MA10 or MA10A Core Memory (1.00 μs) | 550        | 200       |

| MB10 Core Memory (1.65 $\mu$ s)     | 600 (700)* | 200 (300) |

| KM10 Fast Memory (18-bit address)   | 210        | 210       |

\*Numbers in parentheses are the longer times required in a multiprocessor system.

Note: When a fast memory location is addressed as an accumulator or index register, the access time is usually considerably shorter than that listed here.

From the simple addressing point of view, the entire memory is a set of contiguous locations whose addresses range from zero to a maximum dependent upon the capacity of the particular installation. In a system with the greatest possible capacity, the largest address is octal 777777, decimal 262,143. (Addresses are always in octal notation unless otherwise specified.) But the whole memory would usually be made up of a number of core memories each having a capacity of 8192 or 16,384 words. Hence a single 18-bit address actually selects a particular memory and a specific location within it. For an 8K memory the high order five address bits select the memory, the remaining thirteen bits address a single location in it; selecting a 16K memory takes four bits, leaving fourteen for the location. The times given above assume the addressed memory is idle when access is requested. To avoid waiting for a previously requested memory cycle to end, the program can make consecutive requests to different memories by taking instructions from one memory and data from another. The hardware also allows pairs of memories to be interleaved in such a way that consecutive addresses actually alternate between the two memories in the pair (thus increasing the probability that consecutive references are to different memories). Appropriate switch settings at the memories interchange the least significant address bits in the memory and location parts, so that in any two memories numbered n and n+1 where n is even, all even addresses are locations in the first memory, all odd addresses are locations in the second. Hence memories 0 and 1 can be interleaved as can 6 and 7, but not 3 and 4 or 5 and 7.

**Memory Allocation.** The use of certain memory locations is defined by the hardware.

| 0       | Holds a pointer word during a bootstrap readin                                                                                                                                                                                                      |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-17    | Can be addressed as accumulators                                                                                                                                                                                                                    |

| 1 - 17  | Can be addressed as index registers                                                                                                                                                                                                                 |

| 40-41   | Trap for unimplemented user operations (UUOs)                                                                                                                                                                                                       |

| 42-57   | Priority interrupt locations                                                                                                                                                                                                                        |

| 60-61   | Trap for remaining unimplemented operations: these include<br>the unassigned instruction codes that are reserved for future<br>use, and also the byte manipulation and floating point instruc-<br>tions when the hardware for them is not installed |

| 140-161 | Allocated to second processor if connected (same use as 40–61                                                                                                                                                                                       |

140–161 Allocated to second processor if connected (same use as 40–6 for first processor)

All information given in this manual about memory locations 40-61 applies instead to locations 140-161 for programming a second central processor connected to the same memory.

The initial control word address for the DF10 Data Channel must be less than 1000.

#### 1.4 PROGRAMMING CONVENTIONS

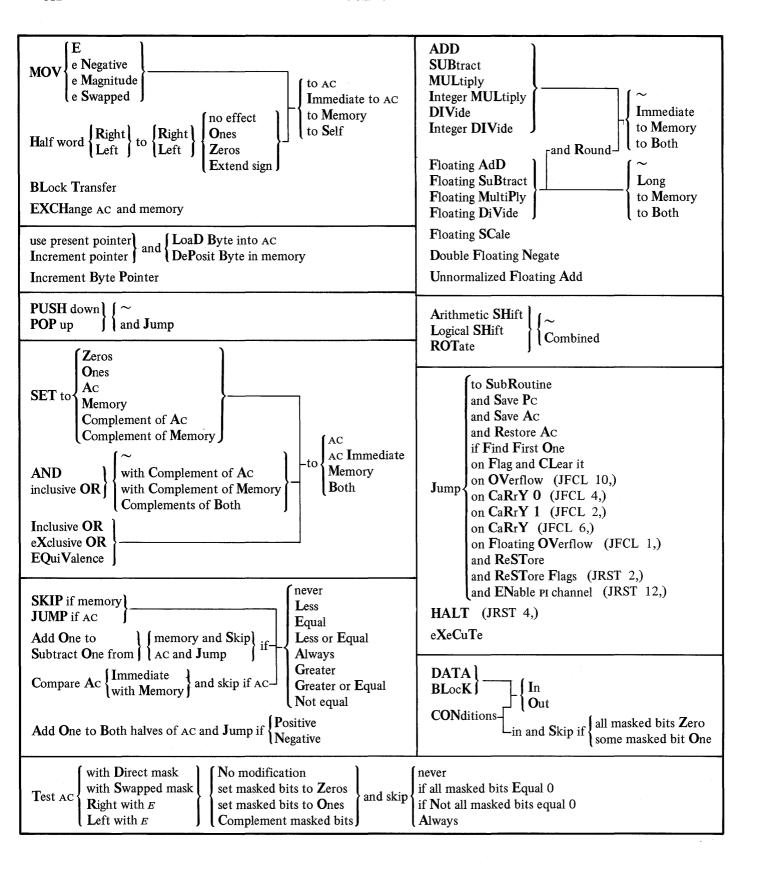

The computer has five instruction classes: data transmission, logical, arithmetic, program control and in-out. The instructions in the in-out class control the peripheral equipment, and also control the priority interrupt and time sharing, control and read the processor flags, and communicate with the console. The next chapter describes all instructions mentioned above, presents a general description of input-output, and describes the effects of the in-out instructions on the processor, priority interrupt and time share hardware. Effects of in-out instructions on particular peripheral devices are discussed with the devices.

The Macro-10 assembly program recognizes a number of mnemonics and other initial symbols that facilitate constructing complete instruction words and organizing them into a program. In particular there are mnemonics for the instruction codes (Appendix A), which are six bits in in-out instructions, otherwise nine or thirteen bits. Eg the mnemonic

**MOVNS**

assembles as 213000 000000, and

MOVNS 2570

assembles as 213000 002570. This latter word, when executed as an instruction, produces the twos complement negative of the word in memory location 2570.

#### Note

Throughout this manual all numbers representing instruction words, register contents, codes and addresses are always octal, and any numbers appearing in program examples are octal unless otherwise indicated. On the other hand, the ordinary use of numbers in the text to count steps in an operation or to specify word or byte lengths, bit positions, exponents, etc employs standard decimal notation.

The initial symbol @ preceding a memory address places a 1 in bit 13 to produce indirect addressing. The example given above uses direct addressing, but

MOVNS @2570

assembles as  $213020\ 002570$ , and produces indirect addressing. Placing the number of an index register (1-17) in parentheses following the memory address causes modification of the address by the contents of the specified register. Hence

MOVNS @2570(12)

which assembles as 213032 002570, produces indexing using index register 12, and the processor then uses the modified address to continue the effective address calculation.

An accumulator address (0-17) precedes the memory address part (if any)

The assembler translates every statement into a 36-bit word, placing 0s in all bits whose values are unspecified.

and is terminated by a comma. Thus

assembles as 213232 002570, which negates the word in location E and stores the result in both E and in accumulator 4. The same procedure may be used to place 1s in bits 9-12 when these are used for something other than addressing an accumulator, but mnemonics are available for this purpose.

The device code in an in-out instruction is given in the same manner as an accumulator address (terminated by a comma and preceding the address part), but the number given must correspond to the octal digits in the word (000-774). Mnemonics are however available for all standard device codes. To control the priority interrupt system whose code is 004, one may give

which assembles as 700600 0001302, or equivalently

The programming examples in this manual use the following addressing conventions:

♦ A colon following a symbol indicates that it is a symbolic location name.

indicates that the location that contains ADD 6,5704 may be addressed symbolically as A.

◆ The period represents the current address, eg

is equivalent to

A: ADD

$$5,A+2$$

lacktriangle Square brackets specify the contents of a location, leaving the address of the location implicit but unspecified. Eg

and

A: 7256004

are equivalent.

Anything written at the right of a semicolon is commentary that explains the program but is not part of it.

## Central Processor

This chapter describes all PDP-10 instructions but does not discuss the effects of those in-out instructions that address specific peripheral devices. In the description of each instruction, the mnemonic and name are at the top, the format is in a box below them. The mnemonic assembles to the word in the box, where bits in those parts of the word represented by letters assemble as 0s. The letters indicate portions that must be added to the mnemonic to produce a complete instruction word.

For many of the non-IO instructions, a description applies not to a unique instruction with a single code in bits 0-8, but rather to an instruction set defined as a basic instruction that can be executed in a number of modes. These modes define properties subsidiary to the basic operation; eg in data transmission the mode specifies which of the locations addressed by the instruction is the source and which the destination of the data, in test instructions it specifies the condition that must be satisfied for a jump or skip to take place. The mnemonic given at the top is for the basic mode; mnemonics for the other forms of the instruction are produced by appending letters directly to the basic mnemonic. Following the description is a table giving the mnemonics and octal codes (bits 0-8) for the various modes.

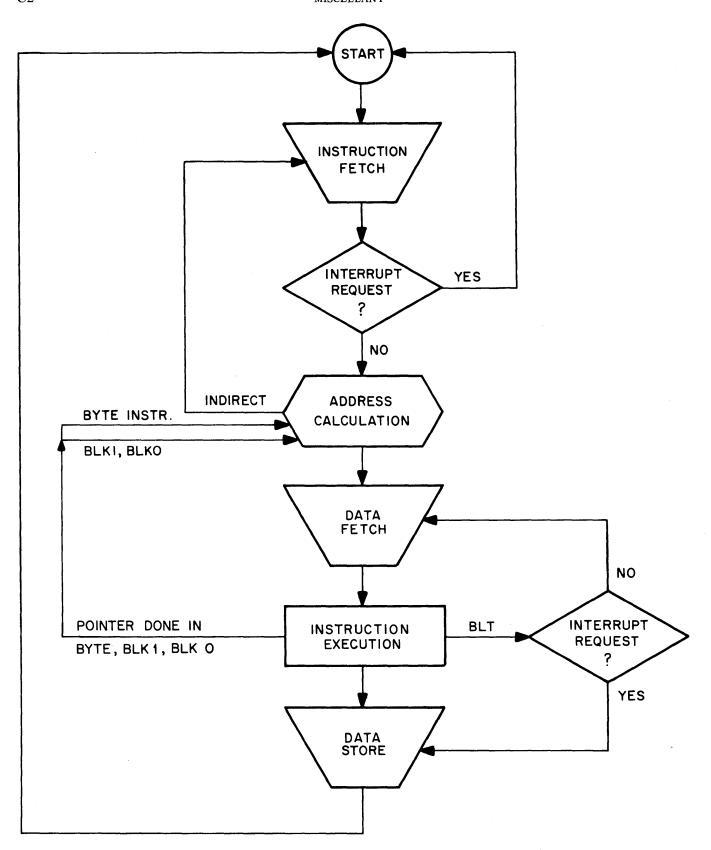

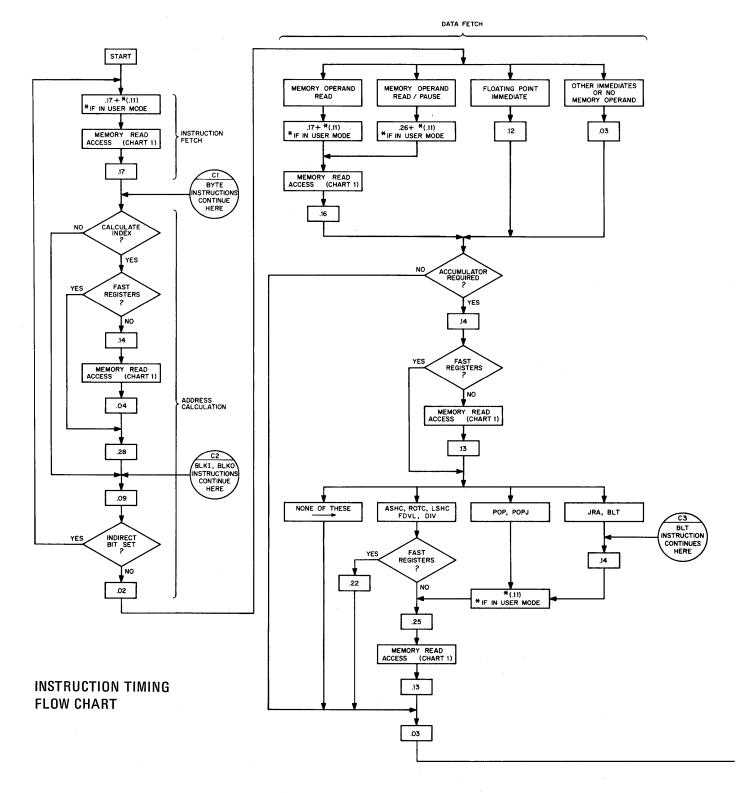

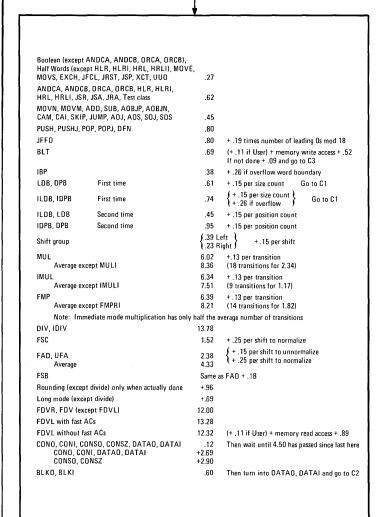

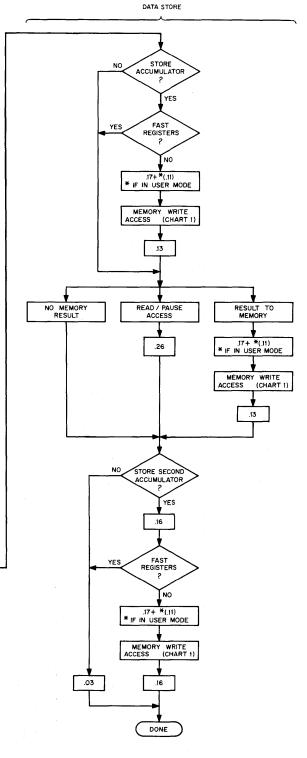

The processor execution time for each instruction is also given at the top unless the time differs from one mode to another. The time listed is that required for direct addressing without indexing (ie with no effective address calculation), assuming the instruction and location E are both in the same 1.00 microsecond core memory, and that an accumulator is addressed only if necessary and is in fast memory. The time that can be saved (if any) by interleaving or keeping instructions and operands in different memories is indicated either with the description or with the discussion of the modes preceding a group of instructions. To determine the exact time required for an instruction under any circumstances, refer to the timing chart in Appendix C.

In a description E refers to the effective address, half word operand, mask, conditions, shift number or scale factor calculated from the I, X and Y parts of the instruction word. In an instruction that ordinarily references memory, a reference to E as the source of information means that the instruction retrieves the word contained in location E; as a destination it means the instruction stores a word in location E. In the immediate mode of these instructions, the effective half word operand is usually treated as a full word that contains E in one half and zero in the other, and is represented either as 0, E or E, 0 depending upon whether E is in the right or left half.

Letters representing modes are suffixes, which produce new mnemonics that are recognized as distinct symbols by the assembler. Most of the non-IO instructions can address an accumulator, and in the box showing the format this address is represented by A; in the description, "AC" refers to the accumulator addressed by A. "AC left" and "AC right" refer to the two halves of AC. If an instruction uses two accumulators, these have addresses A and A+1, where the second address is 0 if A is 17. In some cases an instruction uses an accumulator only if A is nonzero: a zero address in bits 9-12 specifies no accumulator.

It is assumed throughout that time sharing is not in effect, and the program is unrestricted. For completeness, however, the effects of restrictions on particular instructions are noted; and execution times are given both for unrestricted operation and including relocation in a user program (the latter time is given in parentheses). § 2.15 lists all restrictions on user programs and explains the special effects produced by certain instructions when executed under control of the monitor while the processor is in user mode.

Some simple examples are included with the instruction descriptions, but more complex examples using a variety of instructions are given in § 2.11.

#### 2.1 HALF WORD DATA TRANSMISSION

These instructions move a half word and may modify the contents of the other half of the destination location. There are sixteen instructions determined by which half of the source word is moved to which half of the destination, and by which of four possible operations is performed on the other half of the destination. The basic mnemonics are three letters that indicate the transfer

| HLL | Left half of source to left half of destination   |

|-----|---------------------------------------------------|

| HRL | Right half of source to left half of destination  |

| HRR | Right half of source to right half of destination |

| HLR | Left half of source to right half of destination  |

plus a fourth, if necessary, to indicate the operation.

| Operation  | Suffix | Effect on Other Half of Destination                                                                                                                                                                                                                                                                                                                                               |

|------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Do nothing |        | None                                                                                                                                                                                                                                                                                                                                                                              |

| Zeros      | Z      | Places 0s in all bits of the other half                                                                                                                                                                                                                                                                                                                                           |

| Ones       | O      | Places 1s in all bits of the other half                                                                                                                                                                                                                                                                                                                                           |

| Extend     | E      | Places the sign (the leftmost bit) of the half word moved in all bits of the other half. This action extends a right half word number into a full word number but is valid arithmetically only for positive left half word numbers — the right extension of a number requires 0s regardless of sign (hence the Zeros operation should be used to extend a left half word number). |

An additional letter may be appended to indicate the mode, which determines the source and destination of the half word moved.

| Mode      | Suffix | Source                    | Destination       |

|-----------|--------|---------------------------|-------------------|

| Basic     |        | E                         | $\mathbf{AC}$     |

| Immediate | I      | The word $0, E$           | AC                |

| Memory    | M      | AC                        | E                 |

| Self      | S      | $\boldsymbol{\mathit{E}}$ | E, but also AC    |

|           |        |                           | if $A$ is nonzero |

Note that selecting the left half of the source in immediate mode merely clears the selected half of the destination.

Keeping instructions and operands in different memories saves .20 (.09)  $\mu$ s in self mode; in memory mode the same saving results if no action is taken on the other half, otherwise .47 (.36)  $\mu$ s is saved.

When E addresses a fast memory location, a half word transfer takes .34  $\mu$ s less in basic mode, either .46 (.35) or .54 (.43)  $\mu$ s less in memory mode depending respectively on whether or not any action is taken on the other half, and .54 (.43)  $\mu$ s less in self mode.

**HLL** Half Word Left to Left

|   | 500 | M     | $\overline{A}$ | I     | X  | Y  |    |

|---|-----|-------|----------------|-------|----|----|----|

| 0 |     | 67 89 | 12             | 13 14 | 17 | 18 | 35 |

Move the left half of the source word specified by M to the left half of the specified destination. The source and the destination right half are unaffected; the original contents of the destination are lost.

| Half Left to Left           | 500                                                  | $2.35 (2.57) \mu s$                                          |

|-----------------------------|------------------------------------------------------|--------------------------------------------------------------|

| Half Left to Left Immediate | 501                                                  | $1.50 (1.61) \mu s$                                          |

| Half Left to Left Memory    | 502                                                  | $2.90(3.01) \mu s$                                           |

| Half Left to Left Self      | 503                                                  | $2.76 (2.87) \mu s$                                          |

|                             | Half Left to Left Immediate Half Left to Left Memory | Half Left to Left Immediate 501 Half Left to Left Memory 502 |

HLLI merely clears AC left. If A is zero, HLLS is a no-op, otherwise it is equivalent to HLL.

**HLLZ** Half Word Left to Left, Zeros

|   | 5 1 0 | M    | A | I     | X  |       | Y |    |

|---|-------|------|---|-------|----|-------|---|----|

| 0 |       | 67 8 | 9 | 12 13 | 14 | 17 18 |   | 35 |

Move the left half of the source word specified by M to the left half of the specified destination, and clear the destination right half. The source is unaffected, the original contents of the destination are lost.

| HLLZ  | Half Left to Left, Zeros            | 510                 |

|-------|-------------------------------------|---------------------|

|       |                                     | $2.21 (2.43) \mu s$ |

| HLLZI | Half Left to Left, Zeros, Immediate | 511                 |

|       |                                     | $1.36 (1.47) \mu s$ |

| HLLZM | Half Left to Left, Zeros, Memory    | 512                 |

|       |                                     | $2.47 (2.58) \mu s$ |

| HLLZS | Half Left to Left, Zeros, Self      | 513                 |

|       |                                     | $2.76 (2.87) \mu s$ |

HLLZI merely clears AC. If A is zero, HLLZS merely clears the right half of location E.

## **HLLO** Half Word Left to Left, Ones

CENTRAL PROCESSOR

|   | 5 2 0 | M   | A    | I  | X     | Y     |   |

|---|-------|-----|------|----|-------|-------|---|

| C | ) (   | 7 8 | 9 12 | 13 | 14 17 | 18 35 | ; |

Move the left half of the source word specified by M to the left half of the specified destination, and set the destination right half to all 1s. The source is unaffected, the original contents of the destination are lost.

| HLLO  | Half Left to Left, Ones            | 520                 |

|-------|------------------------------------|---------------------|

|       |                                    | 2.21 (2.43) µs      |

| HLLOI | Half Left to Left, Ones, Immediate | 521                 |

|       |                                    | $1.36 (1.47) \mu s$ |

| HLLOM | Half Left to Left, Ones, Memory    | 522                 |

|       |                                    | $2.47 (2.58) \mu s$ |

| HLLOS | Half Left to Left, Ones, Self      | 523                 |

|       |                                    | 2.76 (2.87) us      |

HLLOI sets AC to all 0s in the left half, all 1s in the right.

HLLEI is equivalent to HLLZI (it merely clears AC).

### HLLE Half Word Left to Left, Extend

|   | 530 | M    | A   | I    | X     | Y     |  |

|---|-----|------|-----|------|-------|-------|--|

| ( | )   | 67 8 | 9 1 | 2 13 | 14 17 | 18 35 |  |

Move the left half of the source word specified by M to the left half of the specified destination, and make all bits in the destination right half equal to bit 0 of the source. The source is unaffected, the original contents of the destination are lost.

| HLLE  | Half Left to Left, Extend            | 530                 |

|-------|--------------------------------------|---------------------|

|       | ,                                    | 2.21 (2.43) μs      |

| HLLEI | Half Left to Left, Extend, Immediate | 531                 |

|       |                                      | $1.36 (1.47) \mu s$ |

| HLLEM | Half Left to Left, Extend, Memory    | 532                 |

|       |                                      | $2.47 (2.58) \mu s$ |

| HLLES | Half Left to Left, Extend, Self      | 533                 |

|       |                                      | $2.76 (2.87) \mu s$ |

# HRL Half Word Right to Left

|   | 5 0 4 | M   | A   | I    | X     |    | Y |    |

|---|-------|-----|-----|------|-------|----|---|----|

| 0 | 6     | 7 8 | 9 1 | 2 13 | 14 17 | 18 |   | 35 |

Move the right half of the source word specified by M to the left half of the specified destination. The source and the destination right half are unaffected; the original contents of the destination left half are lost.

| HRL  | Half Right to Left           | 504 | $2.70 (2.92) \mu s$ |

|------|------------------------------|-----|---------------------|

| HRLI | Half Right to Left Immediate | 505 | $1.85 (1.96) \mu s$ |

word E,0

| HRLM | Half Right to Left Memory | 506 | 2.90 (3.01) μs |

|------|---------------------------|-----|----------------|

| HRLS | Half Right to Left Self   | 507 | 2.76 (2.87) μs |

#### HRLZ Half Word Right to Left, Zeros

| 5 1 4 | M   | A    | I  | X     | Y     |

|-------|-----|------|----|-------|-------|

| ) 6   | 7 8 | 9 12 | 13 | 14 17 | 18 35 |

Move the right half of the source word specified by M to the left half of the specified destination, and clear the destination right half. The source is unaffected, the original contents of the destination are lost.

| HRLZ  | Half Right to Left, Zeros            | 514                   |                   |

|-------|--------------------------------------|-----------------------|-------------------|

| HRLZI | Half Right to Left, Zeros, Immediate | 2.21 (2.43) µs<br>515 | HRLZI loads the v |

|       |                                      | 1.36 (1.47) μs        | into AC.          |

| HRLZM | Half Right to Left, Zeros, Memory    | 516<br>2.47 (2.58) μs |                   |

| HRLZS | Half Right to Left, Zeros, Self      | 517<br>2.76 (2.87) µs |                   |

|       |                                      | 2.70 (2.07) [2.8      |                   |

### HRLO Half Word Right to Left, Ones

|   | 5 2 4 | M    | A | I     | X  |       | Y |    |

|---|-------|------|---|-------|----|-------|---|----|

| 0 |       | 57 8 | 9 | 12 13 | 14 | 17 18 |   | 35 |

Move the right half of the source word specified by M to the left half of the specified destination, and set the destination right half to all 1s. The source is unaffected, the original contents of the destination are lost.

| HRLO  | Half Right to Left, Ones            | 524                 |

|-------|-------------------------------------|---------------------|

|       |                                     | $2.21 (2.43) \mu s$ |

| HRLOI | Half Right to Left, Ones, Immediate | 525                 |

|       |                                     | $1.36 (1.47) \mu s$ |

| HRLOM | Half Right to Left, Ones, Memory    | 526                 |

|       |                                     | $2.47 (2.58) \mu s$ |

| HRLOS | Half Right to Left, Ones, Self      | 527                 |

|       | ·                                   | $2.76 (2.87) \mu s$ |

#### HRLE Half Word Right to Left, Extend

|   | 5 3 4 | M   | $\overline{A}$ | I    | X  |       | Y |    |

|---|-------|-----|----------------|------|----|-------|---|----|

| 0 | 6     | 7 8 | 9 1            | 2 13 | 14 | 17 18 |   | 35 |

Move the right half of the source word specified by M to the left half of the

specified destination, and make all bits in the destination right half equal to bit 18 of the source. The source is unaffected, the original contents of the destination are lost.

| HRLE  | Half Right to Left, Extend            | 534            |

|-------|---------------------------------------|----------------|

|       |                                       | 2.21 (2.43) µs |

| HRLEI | Half Right to Left, Extend, Immediate | 535            |

|       | •                                     | 1.36 (1.47) μs |

| HRLEM | Half Right to Left, Extend, Memory    | 536            |

|       |                                       | 2.47 (2.58) µs |

| HRLES | Half Right to Left, Extend, Self      | 537            |

|       |                                       | 2.76 (2.87) μs |

#### HRR Half Word Right to Right

|   | 5 4 0 | M   | A   | I    | X  |       | Y |    |

|---|-------|-----|-----|------|----|-------|---|----|

| 0 | 6     | 7 8 | 9 1 | 2 13 | 14 | 17 18 | 3 | 35 |

Move the right half of the source word specified by M to the right half of the specified destination. The source and the destination left half are unaffected; the original contents of the destination right half are lost.

| HRR  | Half Right to Right           | 540 | $2.35 (2.57) \mu s$ |

|------|-------------------------------|-----|---------------------|

| HRRI | Half Right to Right Immediate | 541 | 1.50 (1.61) μs      |

| HRRM | Half Right to Right Memory    | 542 | 2.90 (3.01) μs      |

| HRRS | Half Right to Right Self      | 543 | 2.76 (2.87) µs      |

|      |                               |     |                     |

If A is zero, HRRS is a no-op; otherwise it is equivalent to HRR.

HRRZI loads the word 0, Einto AC. If A is zero, HRRZS merely clears the left half of

location E.

#### HRRZ Half Word Right to Right, Zeros

|   | 5 5 0 | M    | A    | I  | X     | Y     |  |

|---|-------|------|------|----|-------|-------|--|

| ( | ) (   | 57 8 | 9 12 | 13 | 14 17 | 18 35 |  |

Move the right half of the source word specified by M to the right half of the specified destination, and clear the destination left half. The source is unaffected, the original contents of the destination are lost.

| μs<br>51       |

|----------------|

| μs<br>52       |

| us<br>53<br>us |

|                |

#### HRRO Half Word Right to Right, Ones

|   | 560 | M   | A | I     | X    | Y    |    |

|---|-----|-----|---|-------|------|------|----|

| 0 | 6   | 7 8 | 9 | 12 13 | 14 1 | 7 18 | 35 |

Move the right half of the source word specified by M to the right half of the specified destination, and set the destination left half to all 1s. The source is unaffected, the original contents of the destination are lost.

| HRRO  | Half Right to Right, Ones            | 560                   |

|-------|--------------------------------------|-----------------------|

| HRROI | Half Right to Right, Ones, Immediate | 2.21 (2.43) μs<br>561 |

|       | ,                                    | 1.36 (1.47) μs        |

| HRROM | Half Right to Right, Ones, Memory    | 562<br>2.47 (2.58) μs |

| HRROS | Half Right to Right, Ones, Self      | 563                   |

|       |                                      | $2.76 (2.87) \mu s$   |

#### HRRE Half Word Right to Right, Extend

|   | 570 | M   | A | I     | X  |       | Y  |

|---|-----|-----|---|-------|----|-------|----|

| 0 | 6   | 7 8 | 9 | 12 13 | 14 | 17 18 | 35 |

Move the right half of the source word specified by M to the right half of the specified destination, and make all bits in the destination left half equal to bit 18 of the source. The source is unaffected, the original contents of the destination are lost.

| Half Right to Right, Extend            | 570                                                                        |

|----------------------------------------|----------------------------------------------------------------------------|

|                                        | 2.21 (2.43) μs                                                             |

| Half Right to Right, Extend, Immediate | 571                                                                        |

|                                        | 1.36 (1.47) μs                                                             |

| Half Right to Right, Extend, Memory    | 572                                                                        |

|                                        | $2.47 (2.58) \mu s$                                                        |

| Half Right to Right, Extend, Self      | 573                                                                        |

|                                        | 2.76 (2.87) μs                                                             |

|                                        | Half Right to Right, Extend, Immediate Half Right to Right, Extend, Memory |

#### HLR Half Word Left to Right

| Γ | 5 1 1 | 14    |   | 7        | v  | T/       |    |

|---|-------|-------|---|----------|----|----------|----|

| Į | 344   | IVI   | A |          | X  | <u> </u> |    |

| ( | )     | 67 89 | 9 | 12 13 14 | 17 | 8        | 35 |

Move the left half of the source word specified by M to the right half of the specified destination. The source and the destination left half are unaffected; the original contents of the destination right half are lost.

| HLR  | Half Left to Right           | 544 | $2.70 (2.92) \mu s$ |

|------|------------------------------|-----|---------------------|

| HLRI | Half Left to Right Immediate | 545 | 1.85 (1.96) μs      |

HLRI merely clears AC right.

| HLRM | Half Left to Right Memory | 546 | 2.90 (3.01) μs |

|------|---------------------------|-----|----------------|

| HLRS | Half Left to Right Self   | 547 | 2.76 (2.87) μs |

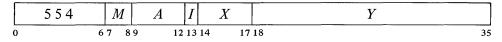

#### HLRZ Half Word Left to Right, Zeros

Move the left half of the source word specified by M to the right half of the specified destination, and clear the destination left half. The source is unaffected, the original contents of the destination are lost.

| HLRZ  | Half Left to Right, Zeros            | 554                   |

|-------|--------------------------------------|-----------------------|

|       |                                      | $2.21\ (2.43)\ \mu s$ |

| HLRZI | Half Left to Right, Zeros, Immediate | 555                   |

|       |                                      | $1.36 (1.47) \mu s$   |

| HLRZM | Half Left to Right, Zeros, Memory    | 556                   |

|       |                                      | $2.47 (2.58) \mu s$   |

| HLRZS | Half Left to Right, Zeros, Self      | 557                   |

|       |                                      | $2.76 (2.87) \mu s$   |

|       |                                      |                       |

HLRZI merely clears AC and is thus equivalent to HLLZI.

#### HLRO Half Word Left to Right, Ones

|   | 564 | M    | A    | I  | X     | Y     |

|---|-----|------|------|----|-------|-------|

| C |     | 67 8 | 9 12 | 13 | 14 17 | 18 35 |

Move the left half of the source word specified by M to the right half of the specified destination, and set the destination left half to all 1s. The source is unaffected, the original contents of the destination are lost.

| HLRO  | Half Left to Right, Ones            | 564                   |

|-------|-------------------------------------|-----------------------|

|       |                                     | $2.21\ (2.43)\ \mu s$ |

| HLROI | Half Left to Right, Ones, Immediate | 565                   |

|       |                                     | $1.36 (1.47)  \mu s$  |

| HLROM | Half Left to Right, Ones, Memory    | 566                   |

|       |                                     | $2.47 (2.58) \mu s$   |

| HLROS | Half Left to Right, Ones, Self      | 567                   |

|       |                                     | 2.76 (2.87) us        |

HLROI sets AC to all 1s in the left half, all 0s in the right.

#### HLRE Half Word Left to Right, Extend

|     | 574 | M    | A | I    | X     | $\underline{\hspace{1cm}} Y$ |

|-----|-----|------|---|------|-------|------------------------------|

| . ( | 0 ( | 57 8 |   | 2 13 | 14 17 | 18 35                        |

Move the left half of the source word specified by M to the right half of the specified destination, and make all bits in the destination left half equal to

bit 0 of the source. The source is unaffected, the original contents of the destination are lost.

| HLRE  | Half Left to Right, Extend            | 574                 |                              |

|-------|---------------------------------------|---------------------|------------------------------|

|       | -                                     | $2.21 (2.43) \mu s$ |                              |

| HLREI | Half Left to Right, Extend, Immediate | 575                 | HLREI is equivalent to       |

|       |                                       | 1.36 (1.47) μs      | HLRZI (it merely clears AC). |

| HLREM | Half Left to Right, Extend, Memory    | 576                 |                              |

|       |                                       | $2.47 (2.58) \mu s$ |                              |

| HLRES | Half Left to Right, Extend, Self      | 577                 |                              |

|       |                                       | $2.76 (2.87) \mu s$ |                              |

|       |                                       |                     |                              |

Examples. The half word transmission instructions are very useful for handling addresses, and they provide a convenient means of setting up an accumulator whose right half is to be used for indexing while a control count is kept in the left half. Eg this pair of instructions loads the 18-bit numbers M and N into the left and right halves respectively of an accumulator that is addressed symbolically as XR.

$$\begin{array}{ccc} \text{HRLZI} & \text{XR}, M \\ \text{HRRI} & \text{XR}, N \end{array}$$

Of course the source program must somewhere define the value of the symbol XR as an octal number between 1 and 17.

Suppose that at some point we wish to use the two halves of XR independently as operands (taken as 18-bit positive numbers) for computations. We can begin by moving XR left to the right half of another accumulator AC and leaving the contents of XR right alone in XR.

#### 2.2 FULL WORD DATA TRANSMISSION

These are the instructions whose basic purpose is to move one or more full words of data from one place to another, usually from an accumulator to a memory location or vice versa. In a few cases instructions may perform minor arithmetic operations, such as forming the negative or the magnitude of the word being processed.

It is not necessary to clear the other half of XR when loading the first half word. But any instruction that modifies the other half is faster than the corresponding instruction that does not, as the latter must fetch the destination word in order to save half of it. (The difference does not apply to self mode, for here the source and destination are the same.)

| EXCH | Exchange | 2.90 (3.01) μs |

|------|----------|----------------|

|      |          |                |

| 250 | A    | $I \mid X$ | Y  |    |

|-----|------|------------|----|----|

| ) 8 | 9 12 | 13 14 17   | 18 | 35 |

Move the contents of location E to AC and move AC to location E.

Keeping instructions and operands in different memories saves .20 (.09)  $\mu$ s.

The time depends on the number and type of transfers. Assuming at least one word is moved a BLT takes .97 (1.08)  $\mu$ s plus 2.26 (2.48)  $\mu$ s per transfer from fast memory to core and 2.61 (2.83)  $\mu$ s per transfer from core to fast memory or from one core location to another.

#### **BLT** Block Transfer

|   | 251 | A   | I       | X  | Y     |   |

|---|-----|-----|---------|----|-------|---|

| 0 | 8   | 9 1 | 2 13 14 | 17 | 18 35 | ; |

Beginning at the location addressed by AC left, move words to another area of memory beginning at the location addressed by AC right. Continue until a word is moved to location E. The total number of words in the block is thus  $E - AC_R + 1$ .

#### CAUTION

Priority interrupts are allowed during the execution of this instruction, following the processing of each word. If an interrupt occurs, the BLT stores the source and destination addresses for the next word in AC, so when the processor restarts upon the return to the interrupted program, it actually resumes at the correct point within the BLT. Therefore, unless the interrupt system is inactive, A and X must not address the same register as this would produce a different effective address calculation upon resumption should an interrupt occur; and the program must not attempt to load an accumulator addressed either by A or X unless it is the final location being loaded. Furthermore, the program cannot assume that AC is the same after the BLT as it was before.

Examples. This pair of instructions loads the accumulators from memory locations 2000–2017.

| HRLZI | 17,2000 | ;Put 2000 000000 in AC 17 |

|-------|---------|---------------------------|

| BLT   | 17 17   |                           |

But to transfer the block in the opposite direction requires that one accumulator first be made available to the BLT:

| MOVEM | 17,2017 | ;Move AC 17 to 2017 in memory  |

|-------|---------|--------------------------------|

| MOVEI | 17,2000 | ;Move the number 2000 to AC 17 |

| BLT   | 17.2016 |                                |

If at the time the accumulators were loaded the program had placed in location 2017 the control word necessary for storing them back in the same block (2000), the three instructions above could be replaced by

#### **Move Instructions**

Each of these instructions moves a single word, which may be changed in the process (eg its two halves may be swapped). There are four instructions,

each with four modes that determine the source and destination of the word moved.

| Mode      | Suffix | Source          | Destination      |

|-----------|--------|-----------------|------------------|

| Basic     |        | E               | AC               |

| Immediate | I      | The word $0, E$ | AC               |

| Memory    | M      | AC              | $\boldsymbol{E}$ |

| Self      | S      | E               | E, but also AC   |

|           |        |                 | if A is nonzero  |

Keeping instructions and operands in different memories saves .47 (.36)  $\mu$ s in memory mode, .20 (.09)  $\mu$ s in self mode.

When E addresses a fast memory location, a move instruction takes .34  $\mu$ s less in basic mode, .46 (.35)  $\mu$ s less in memory mode, .54 (.43)  $\mu$ s less in self mode.

#### MOVE Move

|   | 200 | M   | A    | I  | X     | Y     |

|---|-----|-----|------|----|-------|-------|

| ( | ) 6 | 7 8 | 9 12 | 13 | 14 17 | 18 35 |

Move one word from the source to the destination specified by M. The source is unaffected, the original contents of the destination are lost.

| MOVE  | Move           | 200 | 2.21 (2.43) μs Δ |

|-------|----------------|-----|------------------|

| MOVEI | Move Immediate | 201 | 1.36 (1.47) μs   |

| MOVEM | Move to Memory | 202 | 2.47 (2.58) μs Δ |

| MOVES | Move to Self   | 203 | 2.76 (2.87) μs   |

MOVEI loads the word 0, E into AC and is thus equivalent to HRRZI. If A is zero, MOVES is a no-op; otherwise it is equivalent to MOVE.

#### MOVS Move Swapped

|   | 204 | M   | A    | I  | X     | Y     |

|---|-----|-----|------|----|-------|-------|

| ( | ) 6 | 7 8 | 9 12 | 13 | 14 17 | 18 35 |

Interchange the left and right halves of the word from the source specified by M and move it to the specified destination. The source is unaffected, the original contents of the destination are lost.

| MOVS  | Move Swapped           | 204 | 2.21 (2.43) μs Δ    |

|-------|------------------------|-----|---------------------|

| MOVSI | Move Swapped Immediate | 205 | $1.36 (1.47) \mu s$ |

| MOVSM | Move Swapped to Memory | 206 | 2.47 (2.58) μs 🔺    |

| MOVSS | Move Swapped to Self   | 207 | 2.76 (2.87) µs      |

Swapping halves in immediate mode loads the word E,0 into AC. MOVSI is thus equivalent to HRLZI.

#### MOVN Move Negative

|   | 210 | ) M  | A   | I     | X  |      | Y |    |

|---|-----|------|-----|-------|----|------|---|----|

| Č | )   | 67 8 | 3 9 | 12 13 | 14 | 1718 |   | 35 |

Negate the word from the source specified by M and move it to the specified destination. If the source word is fixed point  $-2^{35}$  (400000 000000) set the

Overflow and Carry 1 flags. (Negating the equivalent floating point  $-1 \times 2^{127}$  sets the flags, but this is not a normalized number.) If the source word is zero, set Carry 0 and Carry 1. The source is unaffected, the original contents of the destination are lost.

MOVNI loads AC with the negative of the word 0, E and can set no flags.

| ▲        | MOVN  | Move Negative           | 210 | $2.39(2.61) \mu s$ |

|----------|-------|-------------------------|-----|--------------------|

|          | MOVNI | Move Negative Immediate | 211 | 1.54 (1.65) μs     |

| <b>A</b> | MOVNM | Move Negative to Memory | 212 | 2.65 (2.76) μs     |

|          | MOVNS | Move Negative to Self   | 213 | 2.94 (3.05) μs     |

#### MOVM Move Magnitude

|   | 214 | M   | $\overline{A}$ | I  | X     | Y     |

|---|-----|-----|----------------|----|-------|-------|

| ( | ) 6 | 7 8 | 9 12           | 13 | 14 17 | 18 35 |

Take the magnitude of the word contained in the source specified by M and move it to the specified destination. If the source word is fixed point  $-2^{35}$  (400000 000000) set the Overflow and Carry 1 flags. (Negating the equivalent floating point  $-1 \times 2^{127}$  sets the flags, but this is not a normalized number.) The source is unaffected, the original contents of the destination are lost.

The word 0,E is equivalent to its magnitude, so MOVMI is equivalent to MOVEI.

| • | MOVM  | Move Magnitude           | 214 | $2.39(2.61) \mu s$ |

|---|-------|--------------------------|-----|--------------------|

|   | MOVMI | Move Magnitude Immediate | 215 | 1.54 (1.65) μs     |

| • | MOVMM | Move Magnitude to Memory | 216 | 2.65 (2.76) μs     |

|   | MOVMS | Move Magnitude to Self   | 217 | $2.94(3.05) \mu s$ |

An example at the end of the preceding section demonstrates the use of a pair of immediate-mode half word transfers to load an address and a control count into an accumulator. The same result can be attained by a single move instruction. This saves time but still requires two locations. Eg if the number 200 001400 is stored in location M, the instruction

loads 200 into AC left and 1400 into AC right. If the same word, or its negative, or with its halves swapped, must be loaded on several occasions, then both time and space can be saved as each transfer requires only a single move instruction that references M.

#### **Pushdown List**

These two instructions insert and remove full words in a pushdown list. The address of the top item in the list is kept in the right half of a pointer in AC, and the program can keep a control count in the left half. There are also

two subroutine-calling instructions that utilize a pushdown list of jump addresses [§ 2.9].

| PUSH | Push Down | $3.85 (4.07) \mu s$ |

|------|-----------|---------------------|

|------|-----------|---------------------|

Add  $1\,000001_8$  to AC to increment both halves by one, then move the contents of location E to the location now addressed by AC right. If the addition causes the count in AC left to reach zero, set the Pushdown Overflow flag. The contents of E are unaffected, the original contents of the location added to the list are lost.

Keeping instructions and the pushdown list in different memories saves .47  $(.36) \mu s$ .

When the word added to the list is from fast memory, PUSH takes .34  $\mu$ s less than the time given.

POP Pop Up 3.93 (4.15) μs

|   |     |      |       |      |      | _ |

|---|-----|------|-------|------|------|---|

| İ | 262 | A    | I     | X    | Y    |   |

| ( | 8   | 9 12 | 13 14 | 4 17 | 18 3 | 5 |

Move the contents of the location addressed by AC right to location E, then subtract  $1\,000001_8$  from AC to decrement both halves by one. If the subtraction causes the count in AC left to reach -1, set the Pushdown Overflow flag. The original contents of E are lost.

Because of the order in which the operands are stored, the instruction POP AC, AC would load the contents of the location addressed by AC right into AC on top of the pushdown count, destroying it.

the list is placed in fast memory, POP takes .46 (.35)  $\mu$ s less than the time given.

When the word taken from

The incrementing and decrementing of both halves of AC simultaneously is effected by adding and subtracting  $1\,000001_8$ . Hence a count of -2 in AC left is increased to zero if  $2^{18}-1$  is incremented in AC right, and conversely, 1 in AC left is decreased to -1 if zero is decremented in AC right.

A pushdown list is simply a set of consecutive memory locations from which words are read in the order opposite that in which they are written. In more general terms, it is any list in which the only item that can be removed at any given time is the last item in the list. This is usually referred to as "first in, last out" or "last in, first out". Suppose locations a, b, c, ... are set aside for a pushdown list. We can deposit data in a, b, c, d, then read d, then write in d and e, then read e, d, c, etc.

Note that by using the Pushdown Overflow flag and a control count in AC left, the programmer can set a limit to the size of the list by starting the count negative, or he can prevent the program from extracting more words than there are in the list by starting the count at zero, but he cannot do both at once.

Pushdown storage is very convenient for a program that can use data stored in this manner as the pointer is initialized only once and only one accumulator is required for the most complex pushdown operations. To initialize a pointer P for a list to be kept in a block of memory beginning at BLIST and to contain at most N items, the following suffices.

Of course the programmer must define BLIST elsewhere and set aside locations BLIST to BLIST +N-1. Using Macro to full advantage one could instead give

where the pseudoinstruction

IOWD

$$J, K$$

is replaced by a word containing -J in the left half and K-1 in the right. Elsewhere there would appear

BLIST: BLOCK

$$N$$

which defines BLIST as the current contents of the location counter and sets aside the N locations beginning at that point.

In the PDP-10 the pushdown list is kept in a random access core memory, so the restrictions on order of entry and removal of items actually apply only to the standard addressing by the pointer in pushdown instructions — other addressing methods can reference any item at any time. The most convenient way to do this is to use the right half of the pointer as an index register. To move the last entry to accumulator AC we need simply give

Of course this does not shorten the list – the word moved remains the last item in it.

One usually regards an index register as supplying an additive factor for a basic address contained in an instruction word, but the index register can supply the basic address and the instruction the additive factor. Thus we can retrieve the next to last item by giving

MOVE

$$AC,-1(P)$$

and so forth. Similarly

PUSH

$$P,-3(P)$$

adds the third to last item to the end of the list;

POP

$$P,-2(P)$$

removes the last item and inserts it in place of the next to last item in the shortened list.

#### 2.3 BYTE MANIPULATION

This set of five instructions allows the programmer to pack or unpack bytes of any length anywhere within a word. Movement of a byte is always between AC and a memory location: a deposit instruction takes a byte from the right end of AC and inserts it at any desired position in the memory location; a load instruction takes a byte from any position in the memory location and places it right-justified in AC.

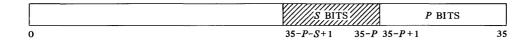

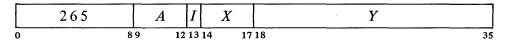

The byte manipulation instructions have the standard memory reference format, but the effective address E is used to retrieve a pointer, which is used in turn to locate the byte or the place that will receive it. The pointer has the format

|   | P | S   |    | I  | X  |    | Y |

|---|---|-----|----|----|----|----|---|

| o | 5 | 6 1 | 12 | 13 | 14 | 17 |   |

where S is the size of the byte as a number of bits, and P is its position as the number of bits remaining at the right of the byte in the word (eg if P is 3 the rightmost bit of the byte is bit 32 of the word). The rest of the pointer is interpreted in the same way as in an instruction: I, X and Y are used to calculate the address of the location that is the source or destination of the byte. Thus the pointer aims at a word whose format is

where the shaded area is the byte.

To facilitate processing a series of bytes, several of the byte instructions increment the pointer, ie modify it so that it points to the next byte position in a set of memory locations. Bytes are processed from left to right in a word, so incrementing merely replaces the current value of P by P-S, unless there is insufficient space in the present location for another byte of the specified size (P-S<0). In this case Y is increased by one to point to the next consecutive location, and P is set to 36-S to point to the first byte at the left in the new location.

#### CAUTION

Do not allow Y to reach maximum value. The whole pointer is incremented, so if Y is  $2^{18}-1$  it becomes zero and X is also incremented. The address calculation for the pointer uses the original X, but if a priority interrupt should occur before the calculation is complete, the incremented X is used when the instruction is repeated.

Among these five instructions one simply increments the pointer, the others load or deposit a byte with or without incrementing. Brackets enclose the additional time required when incrementing overflows the word boundary.

Keeping the pointer in fast memory saves .34  $\mu$ s. Taking bytes from a fast memory location saves another .34  $\mu$ s.

Retrieve a byte of S bits from the location and position specified by the pointer contained in location E, load it into the right end of AC, and clear the remaining AC bits. The location containing the byte is unaffected, the original contents of AC are lost.

Keeping the pointer in fast memory saves .34  $\mu$ s. Keeping instructions and the packing area in different memories saves .20 (.09)  $\mu$ s. Packing bytes in fast memory saves .54 (.43)  $\mu$ s.

DPB Deposit Byte

$$4.87 (5.20) + .15(P + S) [+.26]$$

μs  $137$   $A$   $I$   $X$   $Y$   $Y$   $0$  89 12 13 14 17 18 35

Deposit the right S bits of AC into the location and position specified by the pointer contained in location E. The original contents of the bits that receive the byte are lost, AC and the remaining bits of the deposit location are unaffected.

Keeping the pointer in fast memory saves .54 (.43)  $\mu$ s; keeping it in a different memory from the instruction saves .20 (.09)  $\mu$ s

The A portion of this instruction is ignored.

Keeping the pointer in fast memory saves .34  $\mu$ s. Taking bytes from a fast memory location saves another .34  $\mu$ s.

Increment the byte pointer in location E as explained above.

## ILDB Increment Pointer and Load Byte

$$4.24(4.57) + .15(P + S) [+.26] \mu s$$

Increment the byte pointer in location E as explained above. Then retrieve a byte of S bits from the location and position specified by the newly incremented pointer, load it into the right end of AC, and clear the remaining AC bits. The location containing the byte is unaffected, the original contents of AC are lost.

Keeping the pointer in fast memory saves .34  $\mu$ s. Keeping instructions and the packing area in different memories saves .20 (.09)  $\mu$ s. Packing bytes in fast memory saves .54 (.43)  $\mu$ s.

#### IDPB Increment Pointer and Deposit Byte

$$5.29(5.51) + .15(P + S)[+.26] \mu s$$

Increment the byte pointer in location E as explained above. Then deposit

the right S bits of AC into the location and position specified by the newly incremented pointer. The original contents of the bits that receive the byte are lost, AC and the remaining bits of the deposit location are unaffected.

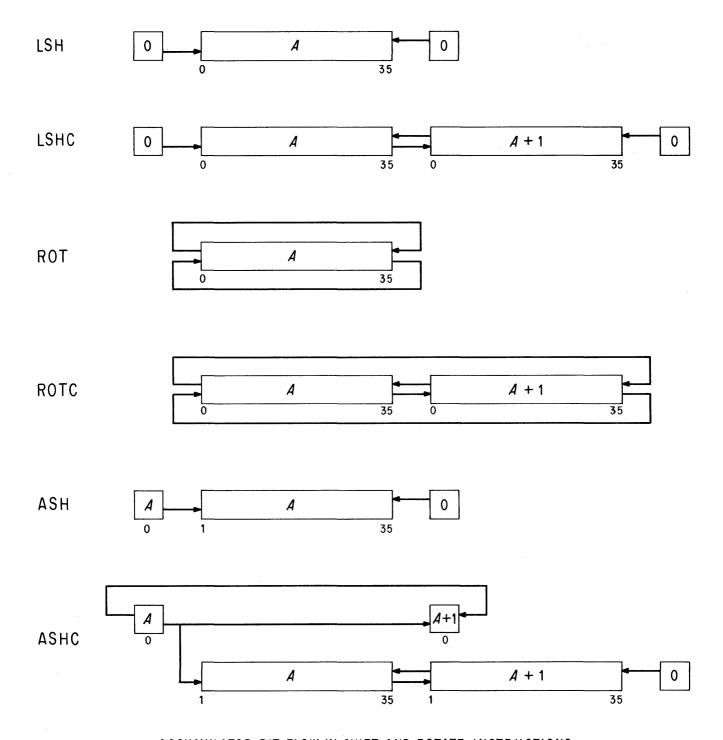

Note that in the pair of instructions that both increment the pointer and process a byte, it is the *modified* pointer that determines the byte location and position. Hence to unpack bytes from a block of memory, the program should set up the pointer to point to a byte just *before* the first desired, and then load them with a loop containing an ILDB. If the first byte is at the left end of a word, this is most easily done by initializing the pointer with a P of 36 (448). Incrementing then replaces the 36 with 36 – S to point to the first byte. At any time that the program might inspect the pointer during execution of a series of ILDBs or IDPBs, it points to the last byte processed (this may not be true when the pointer is tested from an interrupt routine [§2.13]).