EK-UDA50-UG-002

# UDA50 USER GUIDE

# UDA50 USER GUIDE

Prepared by Educational Services Digital Equipment Corporation

1st Edition, December 1981 2nd Edition, October 1982

# Copyright © 1982 by Digital Equipment Corporation

# All Rights Reserved

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

# This document was set on DIGITAL's computerized typesetting system.

# • Class A Computing Devices:

**Notice:** This equipment generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference in which case the user at his own expense may be required to take measures to correct the interference.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC          | DECnet              | OMNIBUS |

|--------------|---------------------|---------|

| DECUS        | DECsystem-10        | OS/8    |

| DIGITAL      | <b>DECSYSTEM-20</b> | PDT     |

| Digital Logo | DECwriter           | RSTS    |

| PDP          | DIBOL               | RSX     |

| UNIBUS       | EduSystem           | VMS     |

| VAX          | IAS                 | VT      |

|              | MASSBUS             |         |

# CONTENTS

# Page

| <b>CHAPTER 1</b> | INTRODUCTION                           |                   |

|------------------|----------------------------------------|-------------------|

| 1.1              | UDA50 DISK CONTROLLER                  | 1-1               |

| 1.2              | UDA50 UPGRADE                          | 1-2               |

| 1.3              | UDA50 DIFFERENCES                      | 1-2               |

| 1.4              | MASS STORAGE CONTROL PROTOCOL          | 1-2               |

| 1.5              | UDA50 SPECIFICATIONS                   | 1-2               |

| 1.6              | RELATED DOCUMENTATION                  | 1-5               |

| CHAPTER 2        | INSTALLATION                           |                   |

| 2.1              | INTRODUCTION                           | 2-1               |

| 2.2              | CABINET JOINING PROCEDURE              | 2-3               |

| 2.2              | MODULE PREPARATION AND INSTALLATION    | 2-9               |

| 2.3.1            | I/O Page Address Switches and Jumpers  | 2-9               |

| 2.3.2            | UNIBUS Overloading                     | 2-11              |

| 2.3.3            | UNIBUS Overload Exceptions             | 2-12              |

| 2.3.4            | UDA50 Priority Plug                    | 2-12              |

| 2.3.5            | SDI Cable Installation                 | 2-13              |

| 2.3.6            | UNIBUS Backplane SPC Slots             | 2-13              |

| 2.3.7            | UNIBUS Backplane Slot Preparation      | 2-17              |

| 2.3.8            | UDA50 Module Insertion                 | 2-18              |

| 2.3.9            | Flat Ribbon Cable Installation         | $\frac{2}{2}$ -18 |

| 2.4              | INSTALLATION OF BOOTSTRAP ROM          | 2-28              |

| 2.5              | FIELD ACCEPTANCE TEST PROCEDURE        | 2-28              |

| 2.5.1            | UDA50-Resident Diagnostics             | 2-30              |

| 2.5.2            | Drive-Resident Diagnostics             | 2-32              |

| 2.5.3            | Subsystem Diagnostics                  | 2-32              |

|                  |                                        |                   |

| CHAPTER 3        | UDA50 PROGRAMMER INFORMATION           |                   |

| 3.1              | GENERAL PROGRAMMING INFORMATION        | 3-1               |

| 3.1              | UDA50-SPECIFIC PROGRAMMING INFORMATION | 3-1               |

| FIGURES          |                                        |                   |

| 1-1              | UDA50 Disk Subsystem Configuration     | 1-1               |

| 2-1              | UDA50 Illustrated Parts                | 2-2               |

| 2-2              | Joining Cross Product Cabinets         | 2-3               |

| 2-3              | Removing Front End Panel Lock          | 2-4               |

| 2-4              | Removing Rear End Panel Lock           | 2-5               |

| 2-5              | Removing Lower Key Buttons             | 2-6               |

| 2-6              | Joining the Cabinets                   | 2-7               |

| 2-7              | Removing the Filler Panel Brackets     | 2-8               |

# FIGURES (Cont)

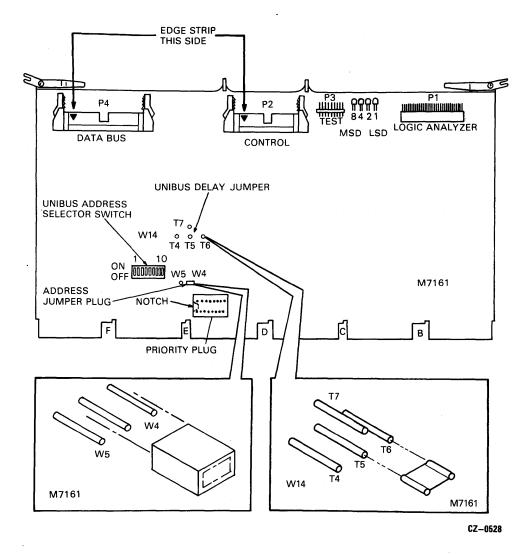

| 2-8A | M7161 UNIBUS Address Switch and Jumper Locations | 2-9  |

|------|--------------------------------------------------|------|

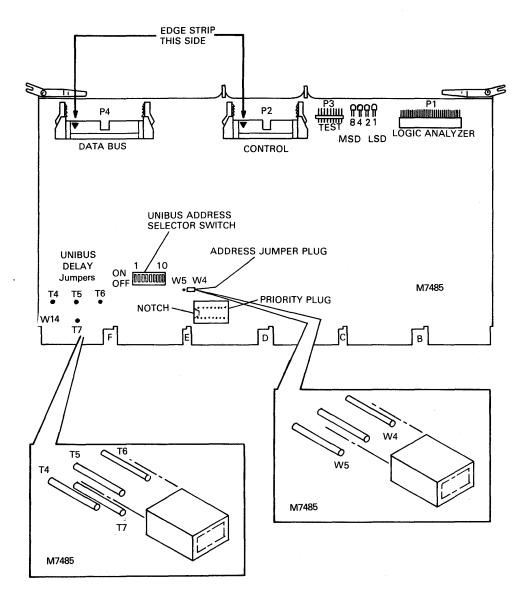

| 2-8B | M7485 UNIBUS Address Switch and Jumper Locations | 2-10 |

| 2-9  | UDA50 Switch Setting for Address 772150          | 2-11 |

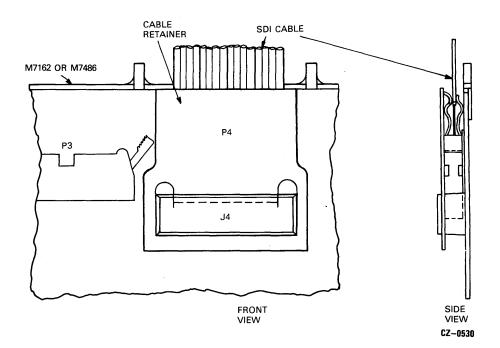

| 2-10 | M7162 or M7486 SDI Cable Assembly Installation   | 2-13 |

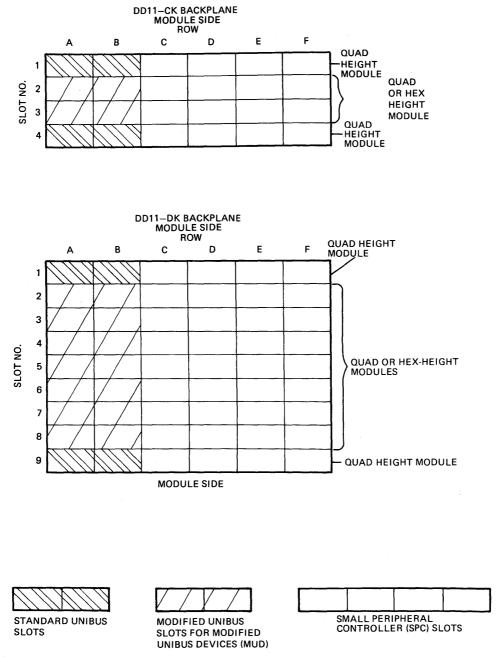

| 2-11 | Optional Backplane Slot Assignments              | 2-14 |

| 2-12 | Standard and Modified Backplane Pin Assignments  | 2-15 |

| 2-13 | SPC PRIME Backplane Pin Assignments              | 2-16 |

| 2-14 | MPG Jumper and Lead Routing                      | 2-17 |

| 2-15 | UDA50 Intermodule Flat Ribbon Cables             | 2-19 |

| 2-16 | I/O Panel and MASSBUS Cable Slot Locations       | 2-20 |

| 2-17 | I/O Bulkhead Installation                        | 2-21 |

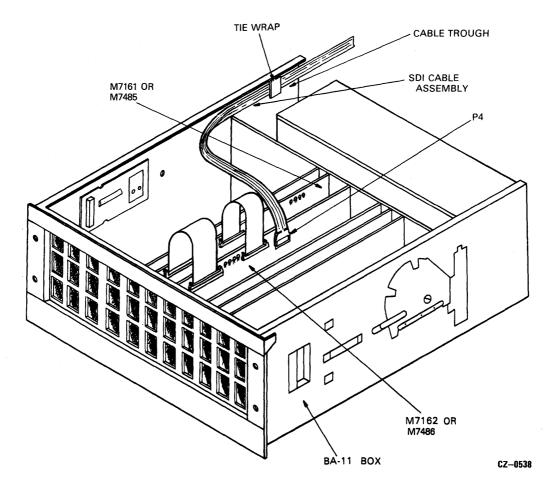

| 2-18 | SDI Cable Routing Inside BA-11 Box               | 2-22 |

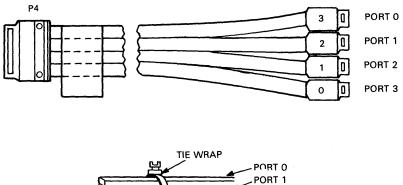

| 2-19 | SDI Cable Assembly with Tie Wrap                 | 2-23 |

| 2-20 | SDI Cable Assembly Installation                  | 2-24 |

| 2-21 | SDI Cable Retainer Bracket                       | 2-25 |

| 2-22 | SDI Cable Shield Terminator Installation         | 2-26 |

| 2-23 | Clamping the SDI Cables to the Support Bracket   | 2-27 |

| 2-24 | Alternate SDI Cable Installation                 | 2-29 |

| 2-25 | Diagnostic LED Locations on UDA50 Modules        | 2-30 |

|      |                                                  |      |

Page

# TABLES

| 1-1 | UDA50 Modules               | 1-2  |

|-----|-----------------------------|------|

| 1-2 | Old UDA50 Specifications    | 1-3  |

| 1-3 | New UDA50 Specifications    | 1-4  |

| 2-1 | UNIBUS Delay                | 2-11 |

| 2-2 | Backplane Signal Checks     | 2-17 |

| 2-3 | LED Error and Symptom Codes | 2-31 |

# CHAPTER 1 INTRODUCTION

# 1.1 UDA50 DISK CONTROLLER

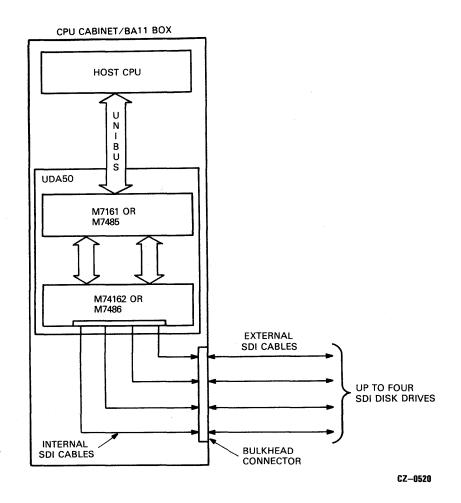

The UDA50 is a two-module disk controller that operates on the UNIBUS. It controls up to four Standard Disk Interconnect (SDI) disk drives. Each SDI disk drive is connected to the UDA50 by a separate shielded SDI cable. The basic configuration for the UDA50 Disk Subsystem is illustrated in Figure 1-1.

The operation of the UDA50 is controlled by two resident processors known as the U and the D processors. The U processor controls the interface between the UNIBUS and the UDA50 controller. The D processor controls the interface between the SDI disk drives and the UDA50 Disk Controller.

Figure 1-1 UDA50 Disk Subsystem Configuration

## **1.2 UDA50 UPGRADE**

The UDA50 has been upgraded to increase its performance. The difference between the old UDA50 and the upgraded UDA50 will be called out in this manual where applicable.

## **1.3 UDA50 DIFFERENCES**

The upgraded UDA50 consists of two new modules. Refer to Table 1-1. Some of the features which increase the performance of the new UDA50 are:

- Increased RAM size on the M7486 module from 4K to 16K.

- Minor hardware modification to make buffering easier.

- Etched-in capability to use larger PROMS.

- Selectable jumpers for UNIBUS delays, for various systems.

## Table 1-1UDA50 Modules

| OLD UDA50<br>MODULES | NEW UDA50<br>MODULES |  |

|----------------------|----------------------|--|

| M7161<br>M7162       | M7485<br>M7486       |  |

#### CAUTION

The new UDA50 M7485 and M7486 modules are not upward or downward compatible with the old UDA50 M7161 and M7162 modules. Under no circumstances should a new UDA50 module be used to replace a failing old UDA50 module unless both modules are replaced as a set.

## 1.4 MASS STORAGE CONTROL PROTOCOL

The UDA50 Disk Controller is a Mass Storage Control Protocol (MSCP) device. MSCP is a communication protocol used with intelligent mass storage controllers. MSCP hides device-dependent requirements, such as disk geometry and error recovery strategies, from the host. It thus enables several different device drivers to be replaced by one class driver.

A detailed description of the Mass Storage Control Protocol is provided in the MSCP Basic Disk Functions Manual (AA-L619A-TK).

# **1.5 UDA50 SPECIFICATIONS**

The UDA50 Disk Controller Specifications are described in Table 1-2 and 1-3.

| Characteristics                                | Specification                                                                                                                                                                 |  |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Physical components                            | UDA module #1 (M7161-YA)<br>UDA module #2 (M7162)<br>50-pin flat cable assembly<br>40-pin flat cable assembly<br>SDI cable assembly<br>I/O bulkhead assembly                  |  |

| Power consumption                              | 80 watts nominal                                                                                                                                                              |  |

| Heat dissipation                               | Approximately 256 Btu/hour                                                                                                                                                    |  |

| Electrical voltage<br>and current requirements | 11 amps at +5 volts<br>60 millamps at +15 volts<br>2 amps at15 volts                                                                                                          |  |

| Operating temperature range                    | 10° C to 40° C (5° F to 109° F) with a temperature gradient of 20° C/hour (36° F/hour)                                                                                        |  |

| Operating relative<br>humidity range           | 10% to 90% with a wet bulb temperature of 28° C (82° F) and a minimum dew point of 2° C (36° F)                                                                               |  |

| Operating altitude<br>range                    | Sea level to 2400 meters (8000 ft). Derate<br>the maximum allowable operating temperature<br>by $1.8^{\circ}$ C/1000 meters (1° F/1000 feet) for<br>operation above sea level |  |

| Mounting restrictions                          | Mounts in two hex-height UNIBUS SPC slots in<br>the following UNIBUS and VAX mounting boxes:                                                                                  |  |

|                                                | BA11-A<br>BA11-K<br>BA11-L                                                                                                                                                    |  |

# Table 1-2 Old UDA50 Specifications

| Characteristics                                | Specifications                                                                                                                                                                |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physical components                            | UDA module 1 (M7485)<br>UDA module 2 (M7486)<br>50-pin flat cable assembly<br>40-pin flat cable assembly<br>SDI cable assembly<br>I/O bulkhead assembly                       |

| Power consumption                              | 83 watts nominal                                                                                                                                                              |

| Heat dissipation                               | Approximately 256 Btu/hour                                                                                                                                                    |

| Electrical voltage<br>and current requirements | 12 amps at +5 volts<br>60 millamps at +15 volts<br>1.4 amps at                                                                                                                |

| Operating temperature range                    | 10° C to 40° C (50° F to 109° F) with a temperature gradient of 20° C/hour (36° F/hour)                                                                                       |

| Operating relative<br>humidity range           | 10% to 90% with a wet bulb temperature of 28° C (82° F) and a minimum dew point of 2° C (36° F)                                                                               |

| Operating altitude range                       | Sea level to 2400 meters (8000 ft). Derate<br>the maximum allowable operating temperature<br>by $1.8^{\circ}$ C/1000 meters (1° F/1000 feet) for<br>operation above sea level |

| Mounting restrictions                          | Mounts in two hex-height UNIBUS SPC slots in<br>the following UNIBUS and VAX mounting boxes:                                                                                  |

|                                                | BA11-A<br>BA11-K<br>BA11-L                                                                                                                                                    |

# Table 1-3 New UDA50 Specifications

# **1.6 RELATED DOCUMENTATION**

The UDA50 Disk Controller related documentation is listed below.

Documentation is available from the Printing and Circulation Services, 444 Whitney St., Northboro, Massachusetts 01532.

- UDA50 Disk Controller User Guide (EK-UDA50-UG)

- UDA50 Disk Controller Service Manual (EK-UDA50-SV)

Documentation is available from the Software Distribution Center Order Administration/Processing, 20 Forbes Rd., Northboro, Massachusetts 01532.

- UDA50 Field Maintenance Print Set (MP-01331)

- UDA50 Programmer's Documentation Kit (QP905-GZ) This kit consists of the following three software manuals.

- *MSCP Basic Disk Function Manual* (AA-L619A-TK)

- Storage System Diagnostic and Utilities Protocol (AA-L620A-TK)

- Storage System UNIBUS Port Description (AA-L621A-TK)

- UDA50 Maintenance Documentation Kit (QP904-GZ) This kit consists of a small looseleaf binder, the UDA50 Maintenance Guide, and the current drive maintenance guides that operate on the UDA50.

- UDA50 Maintenance Guide (AA-M185B-TC) The above maintenance guide is a  $6^{34} \times 4$  inch looseleaf.

- *RA80 Maintenance Guide* (AA-M186A-TC) The above maintenance guide is a  $6\frac{34}{4} \times 4$  inch looseleaf.

- *RA8l Maintenance Guide* (AA-M879A-TC) The above maintenance guide is a  $6\frac{3}{4} \times 4$  inch looseleaf.

- *Maintenance Guide Looseleaf Binder* (AV-L980A-TK)

# CHAPTER 2 INSTALLATION

# **2.1 INTRODUCTION**

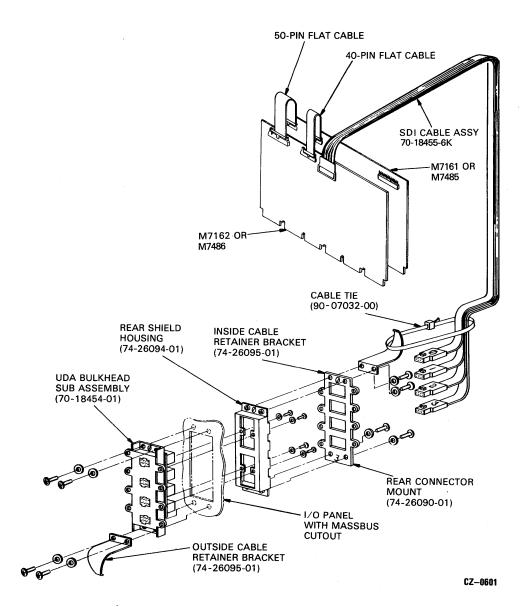

The installation procedure for the UDA50 Disk Controller requires the insertion of two hex-height modules into a UNIBUS backplane. If the UDA50 Disk Controller is to control disk drives located outside the same cabinet that the controller is in, then an I/O bulkhead assembly must be mounted on the rear of the CPU cabinet. SDI cables must be connected between the UDA50 Disk Controller and the I/O bulkhead assembly and from the I/O bulkhead to each disk drive. Figure 2-1 gives an illustrated parts breakdown of the UDA50 assembly.

Use the following checklist to perform the UDA50 installation. The list indicates the paragraph number where each procedure is described.

| • | Join the CPU cabinet to the drive cabinet (2.2)                 |       |

|---|-----------------------------------------------------------------|-------|

| • | Check the I/O page address switches and jumpers (2.3.1)         |       |

| • | Check the UDA50 priority plug (2.3.4)                           |       |

| • | Insert and clamp the SDI cable to J4 (2.3.5)                    |       |

| • | Select the backplane slot (2.3.6)                               |       |

| • | Prepare the backplane slot (2.3.70                              |       |

| • | Insert the UDA50 modules (2.3.8)                                |       |

| • | Install two flat ribbon cables (2.3.9)                          |       |

| • | Install the I/O bulkhead connector (2.3.9.1)                    |       |

| • | Install the internal SDI cable to<br>the I/O bulkhead (2.3.9.3) |       |

| • | Install the external SDI cable to<br>the I/O bulkhead (2.3.9.4) | · · . |

| • | Install the bootstrap ROM (2.4)                                 |       |

| • | Perform the field acceptance test (2.5)                         |       |

Figure 2-1 UDA50 Illustrated Parts

# 2.2 CABINET JOINING PROCEDURE

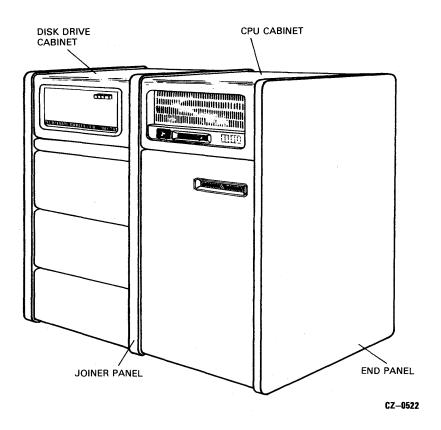

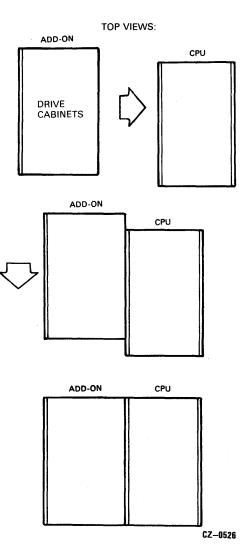

The disk drives that operate with the UDA50 Disk Controller come in an H9642 cabinet with a joiner panel. The joiner panel allows the disk drive cabinet to be joined to the cross-product CPU cabinet in which the UDA50 is located. Figure 2-2 shows how two cross-product cabinets are joined. Use the following procedure to join cross-product cabinets.

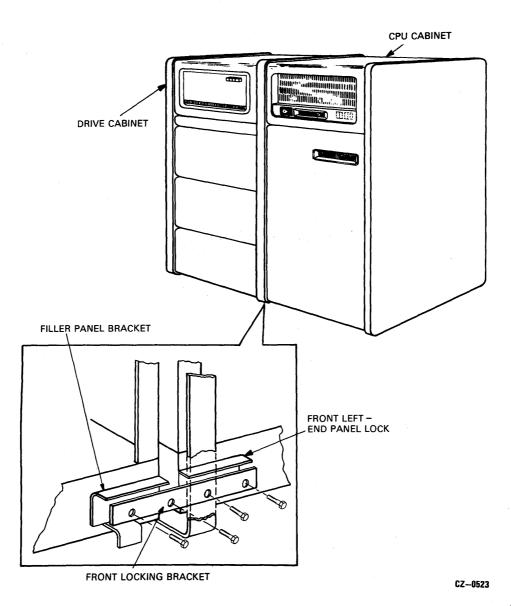

- 1. Open the front door of the CPU cabinet. If the CPU cabinet does not have a front door, remove the lowest front filler panel to expose the end panel lock shown in Figure 2-3.

- 2. Remove the front left-end panel lock from the CPU cabinet.

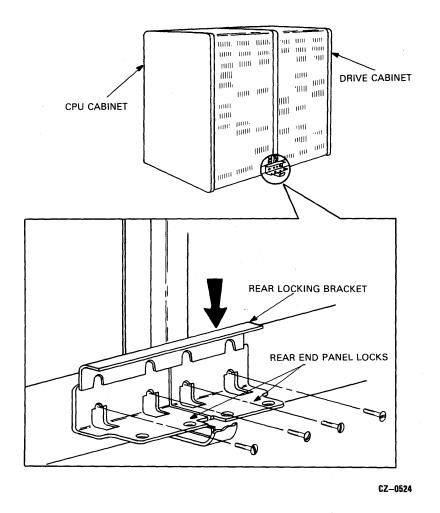

Figure 2-2 Joining Cross Product Cabinets

Figure 2-3 Removing Front End Panel Lock

- 3. Open the rear door of the CPU cabinet.

- 4. Loosen the screws that secure the right rear-end panel lock. Refer to Figure 2-4.

Figure 2-4 Removing Rear End Panel Lock

- 5. Remove the CPU cabinet end panel and its ground strap, if there is one.

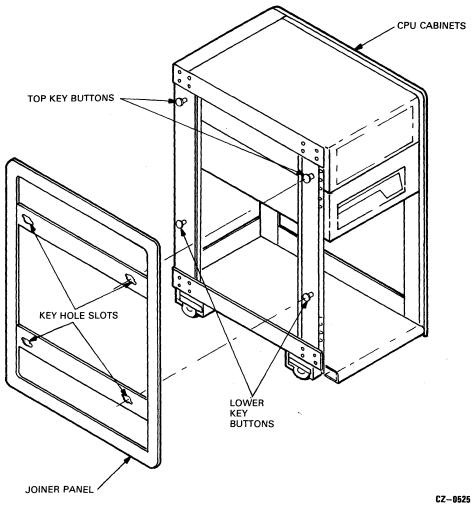

- 6. Remove the two lower key buttons from the left side of the CPU cabinet uprights. These are removed by unscrewing the Phillips head screws in their center. Refer to Figure 2-5.

- 7. Slide the two cabinets together and engage the top two key buttons on the CPU cabinet in the keyhole slots on the drive cabinet joiner panel. Adjust the cabinets until their fronts are flush. Refer to Figures 2-5 and 2-6.

Figure 2-5 Removing Lower Key Buttons

Figure 2-6 Joining the Cabinets

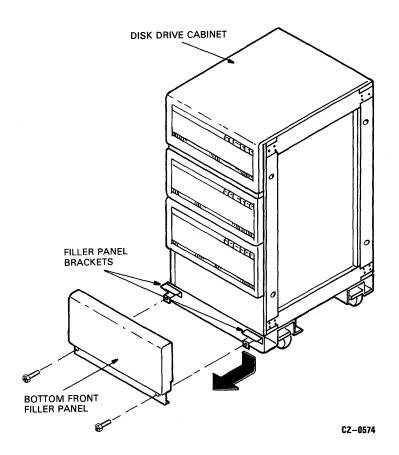

- 8. Remove the bottom front filler panel from the disk drive cabinet by removing the two screws at its base. Refer to Figure 2-7.

- 9. Remove the front right filler panel bracket from the disk drive cabinet.

- 10. Place the front locking bracket over the filler panel bracket and end panel lock as shown in Figure 2-3. Then bolt the two cabinets together with the existing hardware.

- 11. Open the rear door of the disk drive cabinet and loosen the screws that secure the rear left-end panel lock. Refer to Figure 2-4.

- 12. Slide the rear locking bracket over the end panel locks as shown in Figure 2-4. Then tighten the four screws.

- 13. Install the end panel that was removed from the left side of the CPU cabinet onto the left side of the drive cabinet. If an end panel is needed for drives in cross product cabinets, order part number H9544-AA. Be sure to reattach any ground straps to the end panel that might have been removed.

Figure 2-7 Removing the Filler Panel Brackets

# 2.3 MODULE PREPARATION AND INSTALLATION

The following paragraphs describe how to install the UDA50 modules, I/O bulkhead, and cables once the CPU and disk drive cabinets have been joined.

#### 2.3.1 I/O Page Address Switches and Jumpers

The UDA50 Disk Controller contains two registers that are visible to the I/O page. They are the initializing and polling (IP) register and the status and address (SA) register. The IP and SA registers are assigned an octal UNIBUS address of 772150 and 772152, respectively.

The UNIBUS address selector switches and jumper plugs W4 and W5 are used to set the UNIBUS address for the IP register. The location of these switches and jumpers on UDA50 module (M7161) is shown in Figures 2-8A and 2-8B. The location of these switches and jumpers on UDA50 module (M7485) is shown in Figure 2-8A. Set the UNIBUS address switches and jumpers for both modules to the positions shown in Figure 2-9 to select UNIBUS address 772150.

In past disk products, a vector address was also physically selectable. This is not true with the UDA50 Disk Controller. A vector address of 154 (octal) will be supplied by the software.

Figure 2-8A M7161 UNIBUS Address Switch and Jumper Locations

CZ-0795

Figure 2-8B M7485 UNIBUS Address Switch and Jumper Locations

| UNIBUS<br>ADDRESS<br>BITS  | 17 16 15 | 14 13 12                   | 11 10 9                | 876                    | 543                   | 210             |

|----------------------------|----------|----------------------------|------------------------|------------------------|-----------------------|-----------------|

| OCTAL<br>CODE              | 7        | 7                          | 2                      | 1                      | 5                     | 0               |

| BINARY<br>CODE             | 1 1 1    | 1 1 1                      | 010                    | 001                    | 101                   | 000             |

| UDA50<br>SWITCH<br>SETTING | 1 1 1    | 1 1 S10<br>  <sup>ON</sup> | S9 S8 S7<br>OFF ON OFF | S6 S5 S4<br>OFF OFF ON | S3 S2 S1<br>ON OFF ON | W4 0 0          |

|                            | ALWAYS   | ONES                       |                        |                        |                       | ALWAYS<br>ZEROS |

CZ-0529

Figure 2-9 UDA50 Switch Setting for Address 772150

#### NOTE

UNIBUS address bit 2 is selected by jumper plugs W4 and W5. Only one jumper plug can be in place at a time. When jumper W4 is IN, bit 2 equals 0. When jumper W5 is IN, bit 2 equals 1.

### NOTE

The UNIBUS address switches and jumpers should be set for a floating address when a second UDA50 is installed on a system. Check the system configuration and UNIBUS addresses of all devices already installed.

### 2.3.2 UNIBUS Overloading

A set of jumpers has been inserted on both the M7161 and M7485 modules to prevent UNIBUS overloading. The location of these jumpers on UDA50 module (M7161) is shown in Figure 2-8A. The location of these jumpers on UDA50 module (M7485) is shown in Figure 2-8B. Table 2-1 shows the amount of delay, jumper configuration, and system configuration.

| Amount<br>of Delay | Jumper<br>Config. | Type of System                                                                                                               |

|--------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------|

| 0 usec             | T4-T5             | UDA installed and the only other disk<br>drive is a RL02 or a RK07 (11/70 system<br>with a RK07 and 1mb DMR will not work *) |

| 6.2 usec           | T5-T6             | UDA installed with multiple DMR11s or DMC11s or DZ11s                                                                        |

|                    |                   | 11/44 system (or any other PDP-11 with ECC memory) using RM02 or RP04/05/06 disk drives                                      |

|                    |                   | 11/44 with RL02 or RK07 disk drives                                                                                          |

| Table 2-1 UN | IBUS | Delay |

|--------------|------|-------|

|--------------|------|-------|

| Amount<br>of Delay | Jumper<br>Config. | Type of System                                                                                                                                            |

|--------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |                   | 11/24 system (or any other PDP-11 with<br>non-ECC memory) with 1 or 2 UDAs<br>installed with other disk controllers<br>and a DZ11                         |

|                    |                   | VAX systems should be treated as an 11/24 for UNIBUS configuration                                                                                        |

|                    |                   | UDA installed on the UNIBUS with one or<br>more real time data acquistion devices,<br>and real time data overrun or underflow<br>is observed <sup>†</sup> |

| 10 usec            | T5-T7             | 11/44 system with RL02 and RK07 disk drives                                                                                                               |

|                    |                   | 11/70 system with a UDA/RL02/DMR11<br>(1mb) mix                                                                                                           |

# Table 2-1 UNIBUS Delay (Cont)

- \* The UDA/RK07/DMR11 configuration gives data late errors from the RK07 regardless of the UDAs jumper setting. Because of this, either an RK07 or a UDA, but not both can be configured on the 11/70 when a 1mb DMR11 is present.

- \* If underflow or overrun conditions are observed after setting the UDAs jumper to the 6.2 usec. position, the UDA's jumper must be set to the 10 usec. position (T5-T7).

### **2.3.3 UNIBUS Overload Exceptions**

There are exceptions to using the UNIBUS delay in preventing overload and the number of UDAs that can be installed on a system. They are:

- 1. The UDA should not be installed on a UNIBUS system which has a bus repeater because the repeater slows the UNIBUS. Other devices such as RK07, RM02, and RP04/05/06 may also experience data late conditions.

- 2. The UDA must be installed after all non-buffered devices on the UNIBUS.

- 3. On PDP-11 systems, there may be no more than two UDAs installed on a UNIBUS. However on VAX systems, no more than one UDA should be installed on a UNIBUS with non-buffered UNIBUS peripheral devices.

#### NOTE

The old UDA50 M7161 module has the UNIBUS delay jumpers installed starting with M7161 module revision E. Check this module and its delay jumpers if you are having UNIBUS overload problems.

### 2.3.4 UDA50 Priority Plug

All UDA50 M7161 or M7485 modules are shipped with a level 5 priority plug. This is the recommended priority level for UDA50 Disk Subsystems and thus, the priority plug need not be changed for the majority of installations. If another priority level is required in some special circumstance, then the current priority plug must be removed and the new one inserted. The location of the priority plug is shown in Figures 2-8A and 2-8B. It should be inserted so that the notch on the priority plug aligns with the hole on the module socket.

## 2.3.5 SDI Cable Installation

Insert plug P4 of the internal SDI cable assembly into connector J4 on UDA50 module M7162 or M7486 as shown in Figure 2-10. Slide the cable retainer over connector J4 until the connector protrudes through the plastic cutout. The cable retainer should lock the SDI cable in place.

Figure 2-10 M7162 or M7486 SDI Cable Assembly Installation

### 2.3.6 UNIBUS Backplane SPC Slots

The UDA50 Disk Controller will operate in either the standard UNIBUS or modified UNIBUS hex-height small peripheral connector (SPC) slots. Locate two adjacent empty SPC slots for the two UDA50 modules. Illustrations of the UNIBUS backplanes and pin assignments are shown in Figures 2-11 and 2-12, respectively.

The early SPCs did not utilize direct memory access (DMA) data transfers to and from memory; therefore, the signals now used for this purpose are not part of the original SPC pin assignments. Newer options, such as the UDA50 Disk Controller, do utilize DMA transfers. There is a new pin assignment called SPC PRIME that includes these signals. Refer to Figure 2-13. If the UDA50 Disk Controller is used in an older (non-SPC PRIME) slot, it is then necessary to make sure that the signals shown in Table 2-2 are wired on the backplane.

CZ--0531

Figure 2-11 Optional Backplane Slot Assignments

#### STANDARD UNIBUS PIN DESIGNATIONS

|      | ROW<br>A |      | ROW<br>B |     |

|------|----------|------|----------|-----|

| Side |          |      |          |     |

| Pin  | 1        | 2    | 1        | 2   |

| Α    | INIT     | +5V  | BG6      | +5V |

| A    | L        |      | н        |     |

|      | INTR     | GND  | BG5      | GND |

| в    | L        |      | н        |     |

|      | D00      | GND  | BR5      | GND |

| С    | L        |      | L,       |     |

|      | D02      | D01  | GND      | BR4 |

| D    | L        | L    |          | Ĺ   |

| -    | D04      | D03  | GND      | BG4 |

| E    | L        | L    |          | н   |

| F    | D06      | D05  | AC       | DC  |

| ۴    | L        | L    | LOL      | LOL |

| н    | D08      | D07  | A01      | A00 |

|      | L        | L    | L        | L   |

| J    | D10      | D09  | A03      | A02 |

| J    | L        | L    | L        | L   |

| к    | D12      | D11  | A05      | A04 |

|      | L        | L    | L        | L   |

| L    | D14      | D13  | A07      | A06 |

|      | L        | L    | L        | L   |

|      | РА       | D15  | A09      | A08 |

| Μ    | L        | L    | L        | L   |

|      | GND      | РВ   | A11      | A10 |

| N    |          | L.   | L        | L   |

| Р    | GND      | BBSY | A13      | A12 |

| ٣    |          | L    | L        | L   |

|      | GND      | SACK | A15      | A14 |

| R    |          | L    | L        | L   |

| 6    | GND      | NPR  | A17      | A16 |

| S    |          | L    | L        | L   |

|      | GND      | BR7  | GND      | C1  |

| т    |          | L    |          | L   |

|      | NPG      | BR6  | SSYN     | C0  |

| U    | н        | L    | L        | L   |

|      | BG7      | GND  | MSYN     | GND |

| V    | so       |      | L        |     |

#### MODIFIED UNIBUS PIN DESIGNATIONS

|          | 1      | ROW<br>A |      | ROW<br>B |  |

|----------|--------|----------|------|----------|--|

| SIDE     |        |          |      |          |  |

| PIN      | 1      | 2        | 1    | 2        |  |

| A        | INIT   | +5V      | RESV | +5V      |  |

|          | L      |          | PIN  |          |  |

| в        | INTR   | ТР       | RESV | ΤР       |  |

|          | L      |          | PIN  |          |  |

| с        | D00    | GND      | BR5  | GND      |  |

| ľ        | L      |          | L    |          |  |

| D        | D02    | D01      | +5   | BR4      |  |

|          | L      | L        | ВАТ  | L        |  |

|          | D04    | D03      | INT  | PAR      |  |

| E        | L      | L        | SSYN | DET      |  |

|          | D06    | D05      | AC   | DC       |  |

| F        | L      | L        | LOL  | LO L     |  |

| <b>F</b> | D08    | D07      | A01  | A00      |  |

| н        | L.     | L        | L    | L        |  |

| J        | D10    | D09      | A03  | A02      |  |

|          | L      | L        | L    | L        |  |

| к        | D12    | D11      | A05  | A04      |  |

|          | L      | L        | L    | L        |  |

|          | D14    | D13      | A07  | A06      |  |

| L L      | L      | L        | L    | L        |  |

|          | ΡΑ     | D15      | A09  | A08      |  |

| м        | L      | L        | L    | L        |  |

|          | PAR    | РВ       | A11  | A10      |  |

| N        | P1     | L        | L    | L        |  |

|          | PAR    | BBSY     | A13  | A12      |  |

| Р        | PO     | L        | L    | L        |  |

|          | +15    | SACK     | A15  | A14      |  |

| R        | ВАТ    | L        | L    | L        |  |

|          | ·15    | NPR      | A17  | A16      |  |

| s        | ВАТ    | L        | L    | L        |  |

|          | GND    | BR7      | GND  | C1       |  |

| Т        |        | . L      |      | L        |  |

| <b> </b> | +20    | BR6      | SSYN | CO       |  |

| U        | (CORE) | Ľ        | L    | L        |  |

|          | +20    | +20      | MSYN | -5       |  |

| V V      | (CORE) | (CORE)   | L    | (CORE)   |  |

# NOTE:

INDICATES A REDESIGNATED PIN.

CZ-0532

Figure 2-12 Standard and Modified Backplane Pin Assignments

|      | RO<br>C       |          | RO<br>D       |             | RO'<br>E      |              | RO<br>F        |                |

|------|---------------|----------|---------------|-------------|---------------|--------------|----------------|----------------|

| SIDE | 1             | 2        | 1             | 2           | 1             | 2            | 1              | 2              |

| A    | NPG<br>(IN)   | +5V      | TP            | +5V         | GND<br>A      | +5V          | ABG<br>OUT     | +5V            |

| в    | NPG<br>(OUT)  | -15V     | ТР            | ·15V        | ASSYN<br>IN H | -15V         | ABG<br>IN      | ·15V           |

| С    | PA<br>L       | GND      | A SEL<br>6    | GND         | A12<br>L      | GND          | SSYN<br>L      | GND            |

| D    | LTC           | D15<br>L | A OUT<br>LOW  | BR7<br>L    | A17<br>L      | A15<br>L     | BBSY<br>L      | FO1<br>N1      |

| E    | ТР            | D14<br>L | A SEL<br>4    | BR6<br>L    | MSYN<br>L     | A16<br>L     | F01<br>V2      | D02<br>L       |

| F    | ΤР            | D13<br>L | A SEL<br>O    | BR5<br>L    | A02<br>L      | C1<br>L      | D05<br>L       | D06<br>L       |

| н    | D11<br>L      | D12<br>L | A IN          | BR4<br>L    | A01<br>L      | A00<br>L     | D07<br>L       | A INT<br>ENB B |

| J    | A INT<br>B    | D10<br>L | A SEL<br>2    | A BR<br>OUT | SSYN<br>L     | CO<br>L      | NPR<br>L       | GND<br>A       |

| к    | ТР            | D09<br>L | A OUT         | BG7<br>SO   | A14<br>L      | A13<br>L     | D08<br>L       | A INT<br>B     |

| L    | A INT<br>ENBB | D08<br>L | INIT<br>L     | BG7<br>OUT  | A11<br>L      | ТР           | D03<br>L       | FO1<br>L2      |

| м    | ТР            | D07<br>L | AINT<br>ENBA  | BG6<br>SO   | AIN           | AOUT<br>HIGH | INTR<br>L      | FO1<br>M2      |

| N    | DC<br>LO      | D04<br>L | A INT<br>A    | BG6<br>OUT  | A OUT         | A08<br>L     | FO1<br>N1      | D04<br>L       |

| Р    | HALT<br>REQ   | D05<br>L | ТР            | BG5<br>S0   | A10<br>L      | A07<br>L     | ABR<br>OUT     | F01<br>P2      |

| R    | HALT<br>GRT   | D01<br>L | ТР            | BG5<br>OUT  | A09<br>L      | ASEL<br>4    | F01<br>L2      | FO1<br>N1      |

| s    | PB<br>L       | D00<br>L | ТР            | BG4<br>SO   | ASEL<br>6     | ASEL<br>0    | F01<br>M2      | F01<br>P2      |

| т    | GND           | D03<br>L | GND           | BG4<br>OUT  | GND           | ASEL<br>2    | GND            | SACK<br>L      |

| U    | +15           | D02<br>L | ТР            | ABG<br>IN   | A06<br>L      | A04<br>L     | A INT<br>A     | ABR<br>OUT     |

| v    | AC<br>LO      | D06<br>L | ASSYN<br>IN H | ABG<br>OUT  | A05           | A03<br>L     | A INT<br>ENB A | F01<br>F01     |

CZ-0533

Figure 2-13 SPC PRIME Backplane Pin Assignments

| Backplane<br>Pins | Signal<br>Names | Used<br>On     |                                       |

|-------------------|-----------------|----------------|---------------------------------------|

| Pin CA1           | NPG IN          | M7161 or M7485 | · · · · · · · · · · · · · · · · · · · |

| Pin CB1           | NPG OUT         | M7161 or M7485 |                                       |

| Pin FJ1           | NPR             | M7161 or M7485 |                                       |

| Pin CV1           | AC LO1          | M7161 or M7485 |                                       |

| Pin CU1           | +15V            | M7162 or M7486 |                                       |

| Table 2-2 Backplane Signal Che |

|--------------------------------|

|--------------------------------|

# 2.3.7 UNIBUS Backplane Slot Preparation

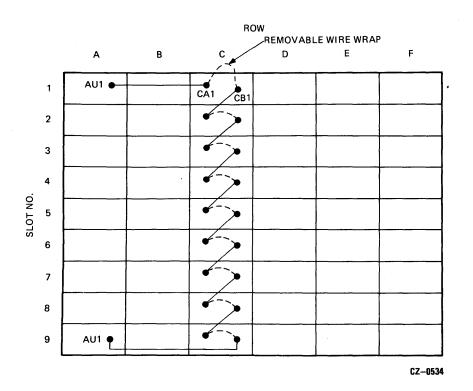

If the slot has SPC PRIME pinning, the NPG jumper will have to be removed. The NPG line is the UNIBUS grant line for devices that perform data transfers without processor intervention. Continuity of the NPG line is provided by wirewrap jumpers on the backplane. When an NPR device is placed in a slot, the corresponding jumper wire from pin CA1 to pin CB1 of that slot must be removed. The routing of the NPG signal through the backplane is shown in Figure 2-14. Grant priority decreases from slot 1 to slot 9 (slot 1 has the highest priority).

Figure 2-14 NPG Jumper Lead Routing

The NPG jumper must be removed from the slot that will be occupied by UDA50 module M7161 or M7485. Module M7161 or M7485 will not operate with the NPG jumper in place. The NPG jumper may also be removed from the slot occupied by the second UDA50 Module, M7162 or M7486, since the module will provide continuity on the NPG line. Module M7162 or M7486 will operate whether or not the NPG jumper is in place. If both NPG jumpers are removed from these two module slots, the module location can be interchanged and the UDA50 will still operate. However, remember that the NPG continuity line will be interrupted whenever Module M7162 or M7486 is removed.

#### NOTE

# If an NPR device is removed from a slot, the jumper wire from pin CA1 to pin CB1 must be reconnected.

The bus grant lines (BG4 through BG7) for devices requiring processor intervention during data transfers are routed through each small peripheral control section in slot D. Each of the four grant signals is routed on a separate line. Grant priority for each level decreases from slot 1 to slot 9.

A bus grant jumper card (G727, G7270, or G7271) must be placed in connector D of any unoccupied SPC section. If an SPC section is left open, bus grant continuity will be lost.

## 2.3.8 UDA50 Module Insertion

Insert the two UDA50 modules into the two adjacent SPC slots prepared for them. The two modules may be inserted in any order if the NPG jumpers have been removed from both SPC slots. Otherwise, make sure that module M7161 or M7485 is in the SPC slot without the NPG jumper.

## 2.3.9 Flat Ribbon Cable Installation

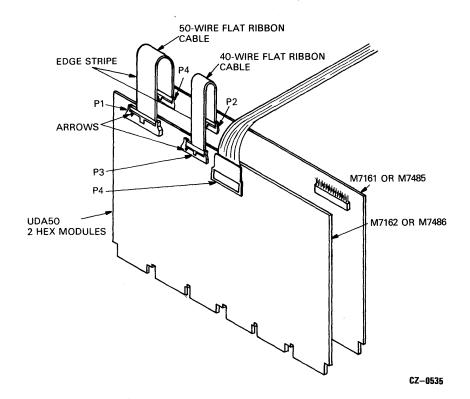

The two UDA50 hex-height modules must be interconnected by two 4 inch long flat ribbon cables as shown in Figure 2-15. The outer cable is a 50-conductor flat ribbon cable which connects M7162 or M7486 (P1) to M7161 or M7485 (P4). The inner cable is a 40-conductor flat ribbon cable which connects M7162 or M7486 (P3) to M7161 or M7485 (P2).

The order in which the two UDA50 modules are inserted into the backplane does not matter to these cables. Install the cables so that the arrows on the plugs align with the sockets. The edge stripe on the cables is on the same edge as the arrow.

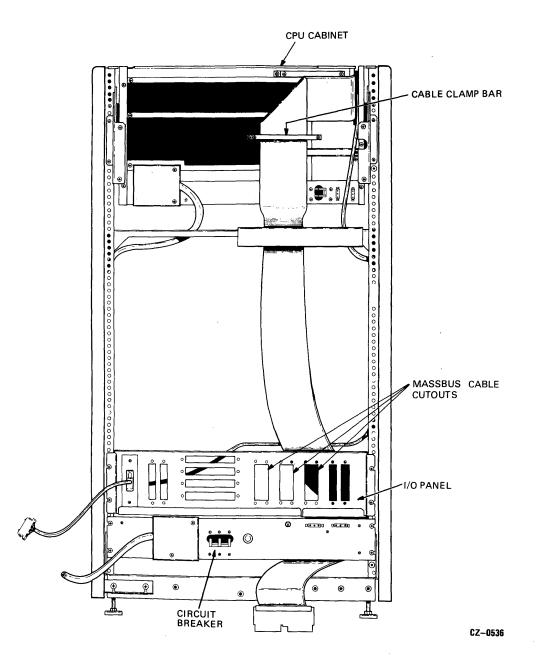

**2.3.9.1** I/O Bulkhead Connector Installation – An I/O bulkhead connector must be installed on the I/O panel at the rear of the CPU cabinet. The I/O bulkhead provides a feedthrough connection for all SDI cables leaving the CPU cabinet. Figure 2-16 shows the location of the I/O panel on a PDP-11/44 cabinet. Other CPU cabinets use this same I/O panel. If no I/O panel is available, refer to Paragraph 2.3.9.5 (Alternate SDI Cable Installation). On the I/O panel are three wide cutouts intended for MASSBUS cable use. The location of these three MASSBUS cable cutouts is also shown in Figure 2-16. Select any empty MASSBUS cable cutout to mount the I/O bulkhead connector. Once an empty MASSBUS cable cutout is found, use the following procedure to install the I/O bulkhead.

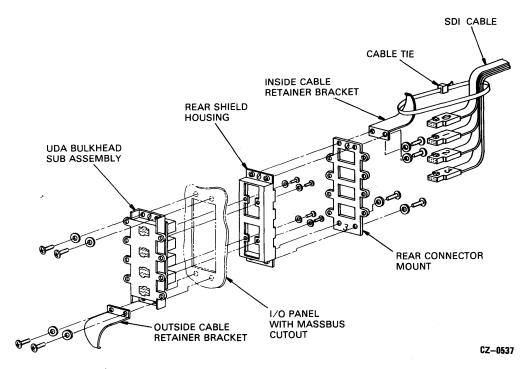

- 1. Install the UDA bulkhead sub-assembly and its outside cable retainer bracket as shown in Figure 2-17. Connector number 0 on the bulkhead should be on the top. Four screws and lock washers are used for mounting.

- 2. Install the rear shield housing next. Connector number 0 should be on the top. Four screws and lock washers are used for mounting.

- 3. Install the rear connector mount and the inside cable retainer bracket next. Again, connector number 0 should be on the top.

Figure 2-15 UDA50 Intermodule Flat Ribbon Cables

Figure 2-16 I/O Panel and MASSBUS Cable Slot Locations

Figure 2-17 I/O Bulkhead Installation

.

.

**2.3.9.2** SDI Cabling Procedures – Standard Disk Interconnect (SDI) cables must be installed both inside and outside the CPU cabinet. The internal SDI cabling procedure will be described first.

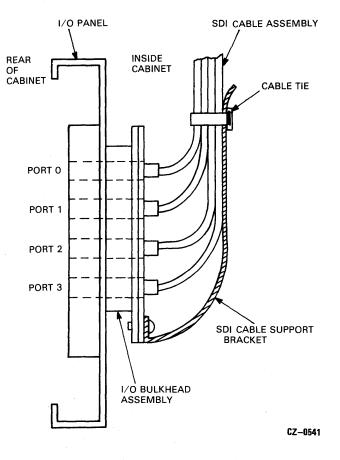

**2.3.9.3** Internal SDI Cables – One end of the internal SDI cable is already connected to UDA50 Module M7162 and M7486. This is described in paragraph 2.3.5. Now the other end of the SDI cable assembly must be plugged into the I/O bulkhead on the I/O panel at the rear of the CPU cabinet. Use the following procedure to install this cable.

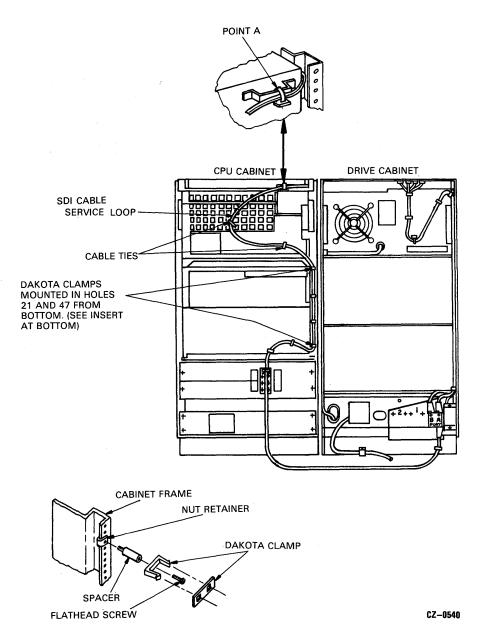

- 1. Bring the SDI cable assembly out of the CPU UNIBUS BA-11 box through the cable trough shown in Figure 2-18.

- 2. Install a tie wrap on the SDI cable assembly approximately where it passes through the cable trough. Refer to Figures 2-18 and 2-19.

Figure 2-18 SDI Cable Routing Inside BA-11 Box

NOTE 1. TIE WRAP THE SDI CABLE ASSEMBLY SO THAT CABLES ARE STACKED ONE ABOVE THE OTHER WITH PORT 0 AT TOP

- 3. Tie wrap the SDI cable at point A where it exits the rear of the BA-11 box. Refer to Figure 2-20.

- 4. Install the two Dakota clamps as shown in Figure 2-20 and insert the SDI cable assembly in them.

- 5. Install the remaining seven cable ties on the SDI cable assembly as shown in Figure 2-20. The seventh cable tie is hidden behind the bottom I/O panel.

Figure 2-20 SDI Cable Assembly Installation

6. Insert the SDI cable plugs into the I/O bulkhead with the port 0 cable in the top connector. The I/O bulkhead connectors are numbered 0, 1, 2, and 3 from the top. Clamp the SDI cables to the retainer bracket. Refer to Figure 2-21.

Figure 2-21 SDI Cable Retainer Bracket

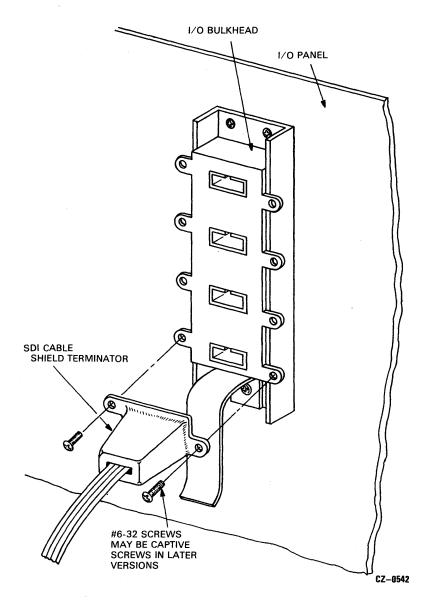

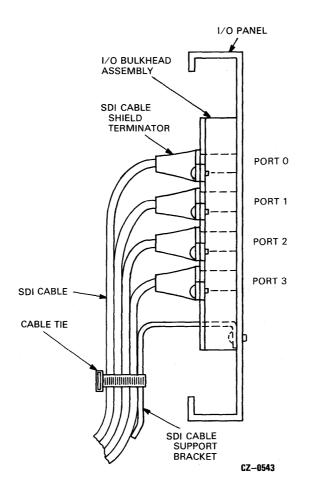

**2.3.9.4** External SDI Cables – The external SDI cables are shielded cables that must be grounded to the I/O bulkhead by mounting the shield terminators with screws. Use the following procedure to install these cables.

- 1. Plug the first SDI cable into the top I/O bulkhead connector (Port 0).

- 2. Screw the SDI cable shield terminator to the I/O bulkhead as shown in Figure 2-22.

Figure 2-22 SDI Cable Shield Terminator Installation

- 3. Install an SDI cable for each disk drive, starting at I/O bulkhead connector 0 and going down sequentially.

- 4. Secure the SDI cables to the SDI cable retainer bracket shown in Figure 2-23.

- 5. Install the drive end of the SDI cables into the drive I/O bulkhead connectors as described in the disk drive user guide. The UDA50 port 0 SDI cable should attach to drive 0, UDA50 port 1 to drive 1, etc.

Figure 2-23 Clamping the SDI Cables to the Support Bracket

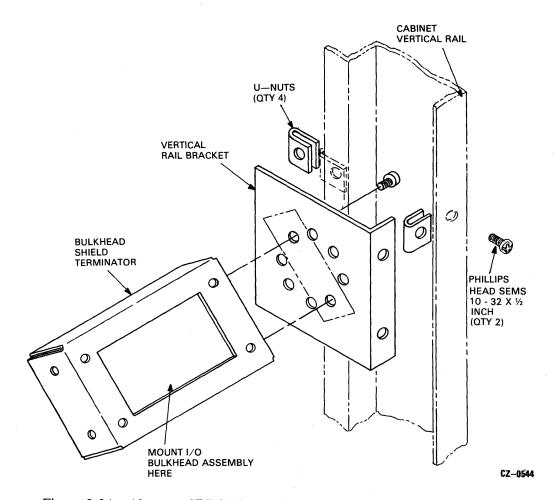

**2.3.9.5** Alternate SDI Cable Installation – The SDI cable installation procedures described in paragraph 2.3.9.3 and 2.3.9.4 should be used whenever an I/O panel is available and room permits. When no I/O panel is present, an alternate means of SDI cable installation is provided. This alternate procedure requires the parts shown in Figure 2-24. Use Figure 2-24 as a reference and perform the following steps.

- 1. Select a suitable location on either rear vertical cabinet rail where this alternate I/O bulkhead can be mounted without interfering with existing equipment. Choose the lowest available location in the cabinet.

- 2. Push on the four u-nuts to align with the holes in the vertical rail bracket.

- 3. Select the best angle and mount the bulkhead shield terminator onto the vertical rail bracket with two' Phillips head sems (10-32  $\times$  1/2 inch).

- 4. Mount the vertical rail bracket onto the vertical cabinet rail with the four Phillips head sems (10-32  $\times$  1/2 inch).

- 5. Install the I/O bulkhead connector onto the bulkhead shield terminator using the same procedure described in paragraph 2.3.8. Mount the I/O bulkhead so that connector number 0 is towards the right.

#### 2.4 INSTALLATION OF BOOTSTRAP ROM

The proper bootstrap ROMs will be shipped with the UDA50. Bootstrap ROM # 23-767A9-00 must be installed on the PDP-11 bootstrap ROM module M9312.

Bootstrap ROM # 23-990A9-00 must be installed on the VAX 11/750.

## **2.5 FIELD ACCEPTANCE TEST PROCEDURE**

The field acceptance and test procedure for the UDA50 Disk Subsystem has three parts. The first part is to run the UDA50 Disk Controller resident diagnostic test. The second part involves running the disk drive field acceptance test found in the disk drive user guide. After each subsystem device has been tested separately, the UDA50 host-resident diagnostics are run to complete the third part of this procedure.

Figure 2-24 Alternate SDI Cable Installation

### 2.5.1 UDA50-Resident Diagnostics

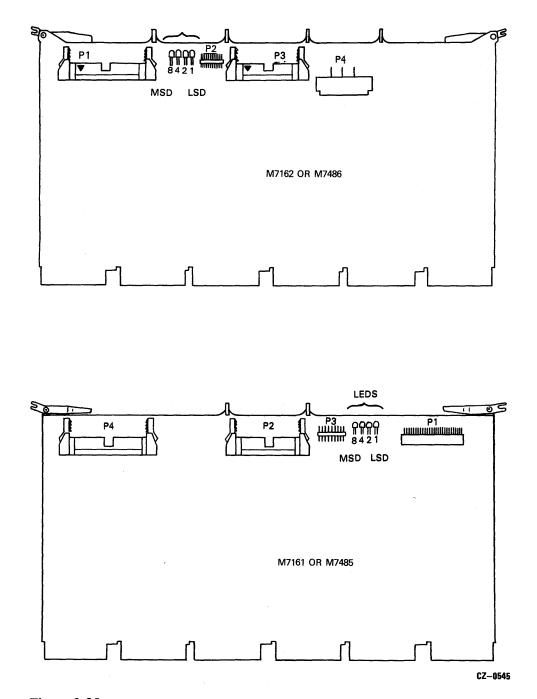

The UDA50-resident diagnostics is initiated when power is applied to the UDA50 Disk Controller. The CPU should be halted during this test. The four LED indicators on each UDA50 module should display a cycling pattern in the LEDs. The cycling pattern in the LEDs signifies the completion of a successful UDA50 diagnostic test. Figure 2-25 shows the location of the four LEDs on each UDA50 module.

If the UDA50 LEDs do not display the cycling pattern after power is applied, look up the LED code in Table 2-3 to locate the problem.

Figure 2-25 Diagnostic LED Locations on UDA50 Modules

| M7161 or<br>M7485<br>LEDs   | M7162 or<br>M7485<br>LEDs                                                                                                          | Error                                                               | Most<br>Likely                                     |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------|--|

| 8421 8421                   |                                                                                                                                    | Symptoms                                                            | Failure                                            |  |

| 000•                        | X X X X                                                                                                                            | Hex 1; undefined                                                    | Undefined                                          |  |

| 0000                        | 0000                                                                                                                               | Hex 2; microcode stuck in init step 2                               | M7161 or M7485<br>or software                      |  |

| 000                         | 0000                                                                                                                               | Hex 3; microcode stuck in init step 3                               | M7161 or M7485<br>or software                      |  |

| 000                         | 0000                                                                                                                               | Hex 4; microcode stuck in<br>init step 4 or UNIBUS<br>timeout error | M7161 or M7485<br>or host<br>inactive              |  |

| B<br>L<br>○ ● ○ I<br>N<br>K | 0000                                                                                                                               | Hex 4/5; test complete                                              | No problem                                         |  |

| ○ ● ● ○<br>x x x x          | $\begin{array}{c} \mathbf{X} \ \mathbf{X} \ \mathbf{X} \ \mathbf{X} \\ \mathbf{O} \ \bullet \ \bullet \ \mathbf{O} \end{array}$    | Hex 6; undefined                                                    | Undefined                                          |  |

| ○ ● ● ●<br>x x x x          | $\begin{array}{c} \mathbf{X} \mathbf{X} \mathbf{X} \mathbf{X} \\ 0 \mathbf{\bullet} \mathbf{\bullet} \mathbf{\bullet} \end{array}$ | Hex 7; undefined                                                    | Undefined                                          |  |

|                             | 0000                                                                                                                               | Hex 8; wrap bit 14 set in SA register                               | M7161 or M7485<br>or software                      |  |

| • • • •<br>• • • •          | 0 0 0 0<br>● 0 0 ●                                                                                                                 | Hex 9; board one error                                              | M7161 or M7485                                     |  |

|                             |                                                                                                                                    | Hex A; board two error                                              | M7162 or M7486                                     |  |

| • • • •<br>x x x x          | $\begin{array}{c} \mathbf{X} \ \mathbf{X} \ \mathbf{X} \ \mathbf{X} \\ \bullet \ \circ \ \bullet \ \bullet \end{array}$            | Hex B; undefined                                                    | Undefined                                          |  |

| <b>X X X X</b><br>● ● ○ ○   | • • • • • • • • • • • • • • • • • • •                                                                                              | Hex C; ROM parity error                                             | M7161 or M7485                                     |  |

| • • • •<br>x x x x          | $\begin{array}{c} \mathbf{X} \mathbf{X} \mathbf{X} \mathbf{X} \\ \bullet \mathbf{\bullet} \mathbf{O} \mathbf{\bullet} \end{array}$ | Hex D; RAM parity error                                             | M7162 or M7486                                     |  |

| • • • o<br>x x x x          | $\begin{array}{c} \mathbf{X} \mathbf{X} \mathbf{X} \mathbf{X} \\ \bullet \bullet \bullet \mathbf{O} \end{array}$                   | Hex E; ROM or RAM parity<br>error<br>Hex F; sequencer error         | M7161 or M7485<br>M7162 or M7486<br>M7161 or M7485 |  |

# Table 2-3 LED Error and Symptom Codes

| M7161 or<br>M7485<br>LEDs<br>8 4 2 1 | M7162 or<br>M7485<br>LEDs<br>8 4 2 1 | Error<br>Symptoms                                                                                                   | Most<br>Likely<br>Failure | - |

|--------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------|---|

| Cycling<br>pattern                   | Cycling<br>pattern                   | UDA responds to host if<br>cycling pattern lasts less<br>than 2 seconds after host<br>sends step 1 data.            | No problem                |   |

|                                      |                                      | UDA does not respond to<br>host if cycling pattern<br>lasts more than 2 seconds<br>after host sends step 1<br>data. | M7161 or M7485            |   |

| Note: $\bullet =$                    | LED ON o                             | = LED OFF $x = Does not c$                                                                                          | are condition             |   |

# Table 2-3 LED Error and Symptom Codes (Cont)

When two codes are given for the same error, both indicate the same failure.

#### 2.5.2 Drive-Resident Diagnostics

Each disk drive should be tested separately by running the drive-resident diagnostics. The procedure for running the resident diagnostics is found in the installation chapter of the disk drive user guide. Perform the drive field acceptance tests found in the installation chapter and then go to Paragraph 2.4.3 for the subsystem diagnostic procedures.

#### 2.5.3 Subsystem Diagnostics

The subsystem diagnostic procedures for the UDA50 controller are different, depending on whether they are used on a PDP-11 CPU or a VAX CPU. The following paragraphs first cover the PDP-11 diagnostics and then secondly, the VAX diagnostics.

#### NOTE

If the diagnostic program reports errors, refer to the UDA50 Service Manual or Maintenance Guide.

## 2.5.3.1 PDP-11 Subsystem Diagnostics –

• CZUDEC0 (UDA disk formatter)

Most disk drives will be shipped with formatted disk packs. On these disk drives, it will not be necessary to run the formatter program. Refer to the disk drive user guide to determine if you must run the formatter before the diagnostic program.

• CZUDCC0 (UDA and disk drive diagnostic)

This diagnostic consists of the following four tests:

- Test 1 UNIBUS Addressing Test

- Test 2 Disk-Resident Diagnostic Test

- Test 3 Disk Functional Test

- Test 4 Disk Exerciser Test

The hardware and software questions asked by this diagnostic are shown in the following two samples along with their default conditions < X >.

## NOTE Refer to the software documentation for detailed description, error messages, etc.

Sample hardware questions:

CHANGE HW (L) ? N

# UNITS (D) ? 1

UNIT O UNIBUS ADDRESS OF UDA (0) 172150 VECTOR (0) 154? BR LEVEL (D) 5 ? UNIBUS BURST RATE (D) 0? DRIVE NUMBER (D) 0?

EXERCISE ON CUSTOMER DATA AREA IN TEST 4 (L) N ? N

Sample software questions:

CHANGE SW (L) ? N

ENTER MANUAL INTERVENTION MODE FOR SPECIAL DIAGNOSDIS (L) Y ? N

REMAINING SOFTWARE QUESTIONS APPLY TO TEST 4 ONLY

ERROR LIMIT (D) 32 ? READ TRANSFER LIMIT IN MEGABYTES - O FOR NO LIMIT (D) O ? SUPRESS PRINTING SOFT ERRORS (L) Y ? DO INITIAL WRITE ON START (L) Y ? ENABLE ERROR LOG (L) N ?

## 2.5.3.2 VAX Subsystem Diagnostics –

• ZZ-EVRLB (UDA50 disk formatter)

Most disk drives will be shipped with formatted disk packs. It will not be necessary nor desirable to run the formatter program on these disk drives. Refer to the disk drive user guide to determine if you must run the formatter before the diagnostic program.

• ZZ-EVRLA (UDA50 disk subsystem diagnostic)

The VAX UDA host-resident diagnostic contains the following four tests.

- Test 1 UNIBUS addressing test

- Test 2 Disk-resident diagnostic test

- Test 3 Disk functional test

- Test 4 Disk exerciser test

Use the verify section of this diagnostic for system installation.

• ZZ-EVRLC (Generic disk drive exerciser)

This program tests the read and write ability of any SDI type disk drive, and will display differences in the read and write data to the operator.

#### NOTE

Refer to the software documentation for detailed descriptions, error messages, etc.

# CHAPTER 3 UDA50 PROGRAMMER INFORMATION

# 3.1 GENERAL PROGRAMMING INFORMATION

The UDA50 operates according to the rules defined in three separate documents. The following is a list of these documents.

- *MSCP Basic Disk Functions Manual* (AA-L619A-TK)

- Storage System Diagnostic and Utilities Protocol (AA-L620A-TK)

- Storage System UNIBUS Port Description (AA-L621A-TK)

All three documents may be purchased separately or as a kit called the *UDA50 Programmer's Documentation Kit* (QP905-GZ) from the Software Distribution Center, Order Administration/Processing, 20 Forbes Road (NR4), Northboro, Massachusetts 01532.

#### 3.2 UDA50-SPECIFIC PROGRAMMING INFORMATION

The following information is UDA50-specific and is necessary for anyone needing to write his own software for the UDA50.

- The address of the UDA50 IP register is 772150 (octal).

- The address of the UDA50 SA register is 772152 (octal).

- The UDA50 supports a host-settable interrupt vector address. A vector address of 154 (octal) is assigned to the UDA50.

- The UDA50 has a command limit value of 13. This includes 12 MSCP commands plus 1 immediate-only command.

- The UDA50 supports an NPR burst value of 1 to 32 long words. One long-word is the default condition.

- The UDA50 supports only 512 byte disk formats.

- The UDA50 supports both the MSCP and the diagnostic and utilities protocols (DUP).

- The diagnostic option capabilities available on the UDA50 are the purge and poll and the diagnostics wrap.

- The UDA50 supports maintenance read and maintenance write to and from the UDA RAM.

- The UDA50 supports last fail log packets.

| Your comments | and suggestions | will help us in | our continuous | effort to improve | the quality a | and usefulness of our |

|---------------|-----------------|-----------------|----------------|-------------------|---------------|-----------------------|

| publications. |                 |                 |                |                   |               |                       |

What is your general reaction to this manual? In your judgment is it complete, accurate, well organized, well written, etc.? Is it easy to use?

|                                    | · · · · · · · · · · · · · · · · · · · |  |

|------------------------------------|---------------------------------------|--|

|                                    |                                       |  |

|                                    |                                       |  |

|                                    |                                       |  |

|                                    |                                       |  |

|                                    | manual?                               |  |

| -                                  |                                       |  |

|                                    |                                       |  |

|                                    |                                       |  |

|                                    | it was intended to satisfy?           |  |

| Does it satisfy <i>your</i> needs? | Why?                                  |  |

|                                    |                                       |  |

|                                    |                                       |  |

|                                    |                                       |  |

□ Please send me the current copy of the *Technical Documentation Catalog*, which contains information on the remainder of DIGITAL's technical documentation.

| Name       | Street        |

|------------|---------------|

| Title      | City          |

| Company    | State/Country |

| Department | Zip           |

Additional copies of this document are available from:

Digital Equipment Corporation 444 Whitney Street Northboro, Ma 01532 Attention: Communications Services (NR2/M15) Customer Services Section

Order No. \_\_\_\_\_EK-UDA50-UG-002

CX

Fold Here

Do Not Tear - Fold Here and Staple

# BUSINESS REPLY MAIL

POSTAGE WILL BE PAID BY ADDRESSEE

DIGITAL EQUIPMENT CORPORATION EDUCATIONAL SERVICES/QUALITY ASSURANCE 12 CROSBY DRIVE (BUO/E08) BEDFORD, MA 01730

Digital Equipment Corporation • Bedford, MA 01730