# SECTION 1

# INTRODUCTION AND DESCRIPTION

DECtape provides the flexibility, speed, and storage capabilities of magnetic tape while maintaining the convenience of paper tape. Its size and portability, in addition to the reliability obtained by the tape format and track head arrangement, render its integration into overall systems on easily accomplished task. The 550 Control together with the DECtape Transport is used with either a PDP-1, -4, or -7 to provide a fast, convenient input-output device.

This manual will emphasize the operation of the 550 control since a complete description of the transport is available in the 555 DECtape Dual Transport manual (H-555).

#### DECTAPE CONTROL TYPE 550

The DECtape Control Unit 550 is a program break control. That is, it allows the transfer of information word by word between the computer and the DECtape Transport. Since the control does not deal with blocks of information from the tape, words can be individually read and written within certain general limits. Since the computer is required to attend to the needs of the control on a word by word basis, however, more of its time is spent in handling the needs of the control than would be the case if the control were of the block transfer type.

The DECtape Control Unit 550 contains electronic circuitry necessary for performing the logical and timing functions essential to the operation of the system; the transport unit contains the tape handling elements, the drive mechanism, and relays for switching the tape heads onto a master bus system.

Operation of the DECtape transport is, normally, controlled by an associated computer. However, manual control is also afforded, by means of the controls located on the front panel of the unit.

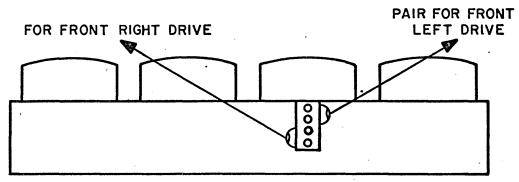

A maximum of four tape transport units (eight drivers) may be controlled by the Type 550 Control unit by means of the mark track, which gives format information to the control, and the

a **]-]**

program interrupt facility of the PDP-7, -4, or -1. The computer is permitted to do computation in the main program during tape operations. Information is transferred with programmed checking by means of the subroutines supplied, but these routines do not allow simultaneous computation during word transfers since these programs are general purpose and take most of the computer's time for their operations.

### USES OF DECTAPE

DECtape is particularly suitable for certain applications. Some of these are covered briefly below.

#### Storage

The first application is simply as a storage device for programs and data. Since the tape handling is extremely simple, it is easy, and in fact desirable, to store the program on DECtape and simply carry it to the computer when needed. To carry the same amount of data on either cards or paper tape would be unwieldy to say the least. Different library tapes can be changed easily, if necessary, and retrieval of any portion of the tape is relatively fast.

# Editing

If modifications to the programs are necessary, the tape need not be either rewritten entirely to preserve the order, or added to at the end. The program can be read in, modified, and rewritten in the same location on the tape if its block length is not changed. This indicates also that many programs can be written utilizing a minimum number of drives.

# On-Line System Data Handling

On an on-line system, use of individual DECtapes to store information keyed in by individual users provides a cheap and efficient way of handling data. The ability to multiprogram during searching (which requires, by far, the greatest amount of time) means that more than one individual can have access to the computer without appreciably affecting internal processing, and without causing an inordinate amount of waiting time for the user. An extension of this is discussed in the next application.

Since the DECtape reel is only 3-1/2 inches in diameter, and the system can read or write in both directions, random access to any point on the reel is relatively fast. A fairly large amount of data can be stored, however. For example, one tape can hold more than 28 complete 4K memories. In a real-time, multiple-user, random access system, many tapes can be moving simultaneously even though data can be transferred on only one tape at a time. For example, take a system with several remote Teletypes, each of which requires random access to information stored on several DECtapes. When the first request occurs, the program can place the appropriate tape in search mode and begin searching for the block. If another request occurs, the program can note approximate position of the first tape in relation to the block requested, select the new tape (leaving the old tape moving), and start searching for the new block. A programmed clocking device or timing loop can be used to determine when to reselect the first tape, check for the correct block, and transfer the data. As new inquiries enter the system, a queue can be formed with the request for the nearest information and the time needed to reach it at the top of the queue. As information is found, the clock is reset to the time necessary to reach the next request and so on:

In this way, multiple requests for information on a single tape can be easily handled if both records can be found by searching in the same direction. There are times, of course, when data is reached on more than one tape simultaneously. In this case, the tape searching for the later request can either be stopped before the record is reached or can be turned around if the record has been bypassed. In terms of overall time to the user, very little difference will be noticed. Of course if two separate DECtape controls are used, data can actually be transferred on more than one tape simultaneously, if the program is fast enough to react to the various flags.

# Sampling of Data

A fourth type of application involves the continuous movement of the tape. In many instances it is desirable to store sampled data on a tape for future analysis by other programs. Memory fills up rapidly, however; and during the time information is transferred onto the tape, sampling is usually stopped to avoid synchronization problems. Thus, the information stored usually consists of data relating to many relatively short samples. With DECtape, one whole tape can be written with one command, and therefore an extremely long sample of fairly rapid

1--3

data can be achieved. If desired, the entire tape can be considered as one long block of information. Storing of information from an analog-to-digital converter would be a logical use of such a system.

# SPECIFICATIONS

Listed below are the characteristics of the 550 DECtape Control. All values are approximate.

WORD TRANSFER RATE

One 18-bit word each 200 ( $\pm$ 10) µsec. Bit rate is constant when moving forward. Although velocity varies slightly, bit density changes serve to maintain a constant bit rate due to the constant rate timing tack. In reverse direction the variation in time between words becomes  $\pm$  30% depending on location along the tape.

BLOCK SIZE

Arbitrary segments of any length determined by format control tracks.

POWER REQUIREMENTS

115 v, 60 cps, 1.5 amp

WRITE CURRENT

180 ma

READ SIGNAL

5 mv, p-p, minimum

# **FEATURES**

The general features incorporated in the DECtape system are: bidirectional reading and writing; Manchester type polarity sensing; prerecorded mark and timing tracks; pretested subroutines; individually addressable blocks; and in the sense explained elsewhere in this manual, individually addressable words.

#### **Recording Technique**

Most of the above features are the result of the type of recording technique used in the system (Manchester, or polarity sensed). Briefly, this technique utilizes a change in magnetic flux for every data bit on the tape. Of importance in this technique is the direction of each flux

change. A "negative-going" change represents a 1; a "positive-going" change is 0. The polarity of the voltage generated by these flux changes is sensed to determine the type of bit written at a particular location on tape. A timing track is recorded on the tape for purposes of strobing the data tracks. The timing strobe is issued to coincide with the maximum rate of change in flux of a data bit, thus at the point of maximum read voltage.

#### **Preprogrammed Subroutines**

Information is transferred with programmed checking by means of the subroutines which may be obtained from Digital. There are three types of subroutines currently available. The first is a basic set of subroutines for searching, reading, and writing. The second, called Microtog, is a set of maintenance and diagnostic programs entirely under control of toggle switches on the main computer console. The third, called Microtrieve, is a routine which permits the saving of programs or data on DECtape, with a quick retrieval feature using toggle switches. A more detailed description of these programs is included at the end of Section 4.

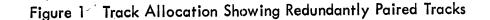

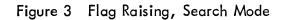

# FORMAT

DECtape uses a ten track recording head to read and write five duplexed channels. The five tracks actually written consist of the timing track, used to strobe the other tracks; the mark track, used to raise flags in the program, create sequence breaks, detect block mark numbers, and protect control portions of the tape; and three data tracks. An 18-bit word therefore uses six lines of three bits each on the tape.

# Tape Skew

Some tape systems strobe on the first bit of a slot, then impose some arbitrary delay after which all signals present are read. This produces problems since differences may occur in the two directions. Variations in tape speed between write time and read time would result in noncompensated changes in the necessary delay. In the DECtape system the redundant heads are placed in a relationship to each other which eliminates most of the cross-talk between the most important tracks. This relationship also places the timing tracks at the edges of the tape so that strobing on the analog sum of the timing track signals guarantees that the data tracks are read when they are in the most favorable position. The data tracks are placed in the middle of the tape where the effect of skew is at a minimum.

# Timing and Mark Tracks

The heart of the DECtape system is the prerecorded timing and mark tracks. It is necessary to understand the meaning of the word "prerecorded." At present, one of the programs provided with the DECtape system writes the timing track and block format desired for the individual user. The DECtape system includes a programmed mode of operation called "write timing and mark track" and a manual switch which both permits writing on the timing and mark tracks and also activates a clock which produces the timing track and flags for program control. Unless both the mode and the switch are used simultaneously, it is physically impossible to write on the mark or timing tracks. A red indicator lights on all transports connected to the appropriate control when the manual switch is in the "on" position. In this mode only, information channel "one" is also connected to the mark track channel.

The sequence in which the bits are placed on tape is shown in Figure 1. <sup>1</sup> Thus bits 0, 3, 6, 9, 12, and 15 are duplicated in the mark track when writing timing and mark information on tape.

Two posses are therefore required to generate a virgin tape or a tape which has the timing and mark information, block numbers, and a counting pattern in the data portion of tape. The block numbers and the counting pattern are written on the second poss.

| ·                                            |       | a second provide the second |                                                                                                                                                                                                                                                                                                                                                        |                                          |         |

|----------------------------------------------|-------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------|

| TIMING TRACK 1                               |       |                             |                                                                                                                                                                                                                                                                                                                                                        |                                          | 1       |

| MARK TRACK 1                                 | 1 1 1 | 0 0 0 1 1                   | 1 0 0 0 1 1 1 0                                                                                                                                                                                                                                                                                                                                        | 0 0 1 1                                  | 1 0     |

| INFORMATION TRACK 1                          | 1 1 0 | 1 0 1 1 1                   | 0 0 0 1 0 1 1 1                                                                                                                                                                                                                                                                                                                                        | 1 1 0 1                                  | 0 1     |

| INFORMATION TRACK 2 0                        | 1 0 1 | 0 1 1 0 1                   | 0 1 0 0 0 1 1 1                                                                                                                                                                                                                                                                                                                                        | 0 1 1 1                                  | 0 1     |

| INFORMATION TRACK 3 1                        | 0 1 0 | 1 0 1 1 0                   | 1 1 0 1 1 0 1 0                                                                                                                                                                                                                                                                                                                                        | 1 1 0 0                                  | 1       |

| INFORMATION TRACK 1A<br>(Seme as IT I)       | 1 1 0 | 1 0 1 1 1                   | 0 0 0 1 0 1 1 1                                                                                                                                                                                                                                                                                                                                        | 1 1 0 1                                  | 0 3/4 " |

| INFORMATION TRACK 2A (Same as IT 2)          | 1 0 1 | 0 1 1 0 1                   | 0 1 0 0 0 1 1 1                                                                                                                                                                                                                                                                                                                                        | 0 1 1 1                                  | O       |

| INFORMATION TRACK 3A<br>(Same as IT 3) 1 0 1 | 0 1 0 | 1 0 1 1 0                   | 1 1 0 1 1 0 1 0                                                                                                                                                                                                                                                                                                                                        | 1 1 0 0                                  | TRACKS  |

| MARK TRACK 1A<br>(Same as MT 1) 0 0 0        | 1 1 1 | 0 0 0 1 1                   | 1 0 0 0 1 1 1 0                                                                                                                                                                                                                                                                                                                                        | 0 0 1 1                                  |         |

| TIMING TRACK 1A<br>(Same as TT 1)            | 1     |                             | an de la calencia de<br>En esta de la calencia de la calencia<br>En esta de la calencia | n<br>19 - Al C<br>19 - Al C<br>19 - Al C |         |

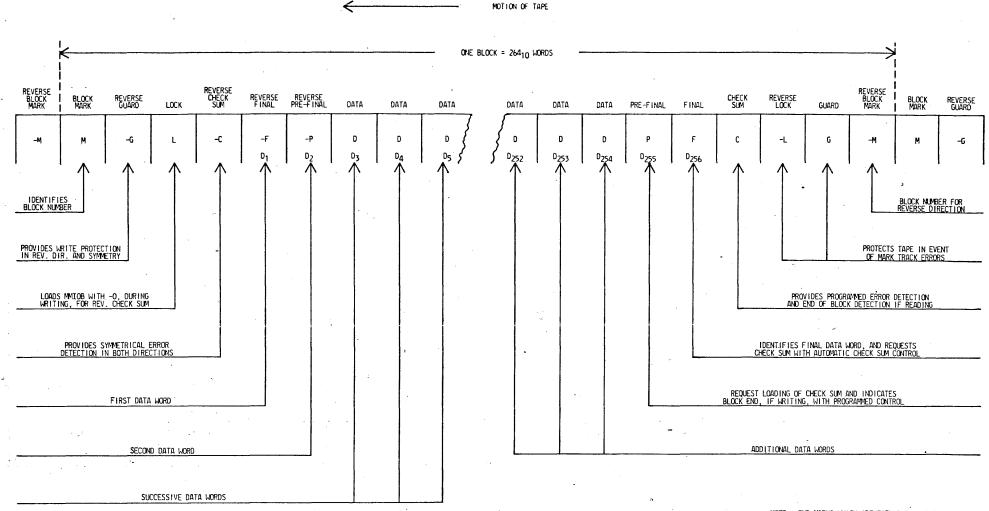

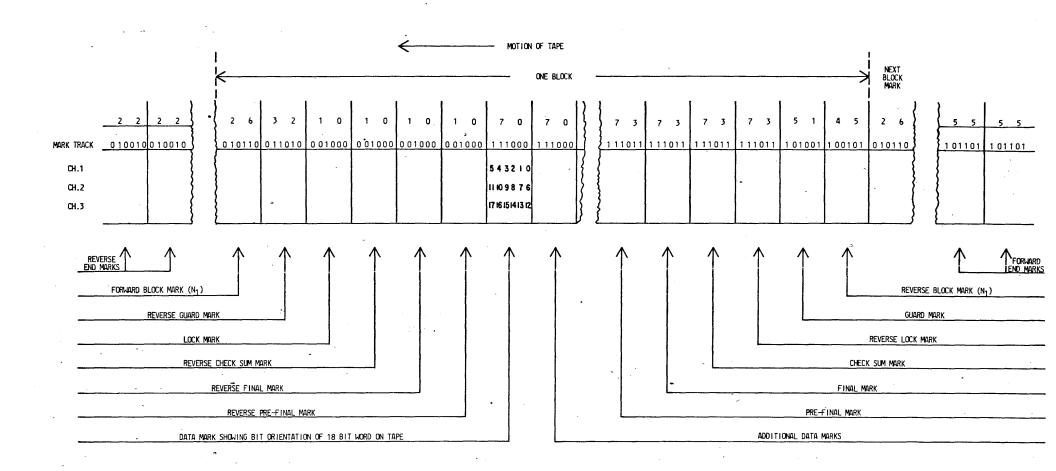

The actual mark track which is written on the tape (see Figure 2) was selected after careful consideration and provides many functions not readily discernible at a casual glance. Some of these are listed below

Porgram synchronization Block end detection Error checking and prevention Protection of control information Block and word addressability Automatic bidirectional compatibility End of tape detection Variable block format Inclusion of marks to allow expansion for more automatic systems of the future.

For complete understanding of the questions of program synchronization and block end detection, Figures 2 through 6 should be studied closely, using the explanation which follows to clarify certain main points.

# Modes of Operation

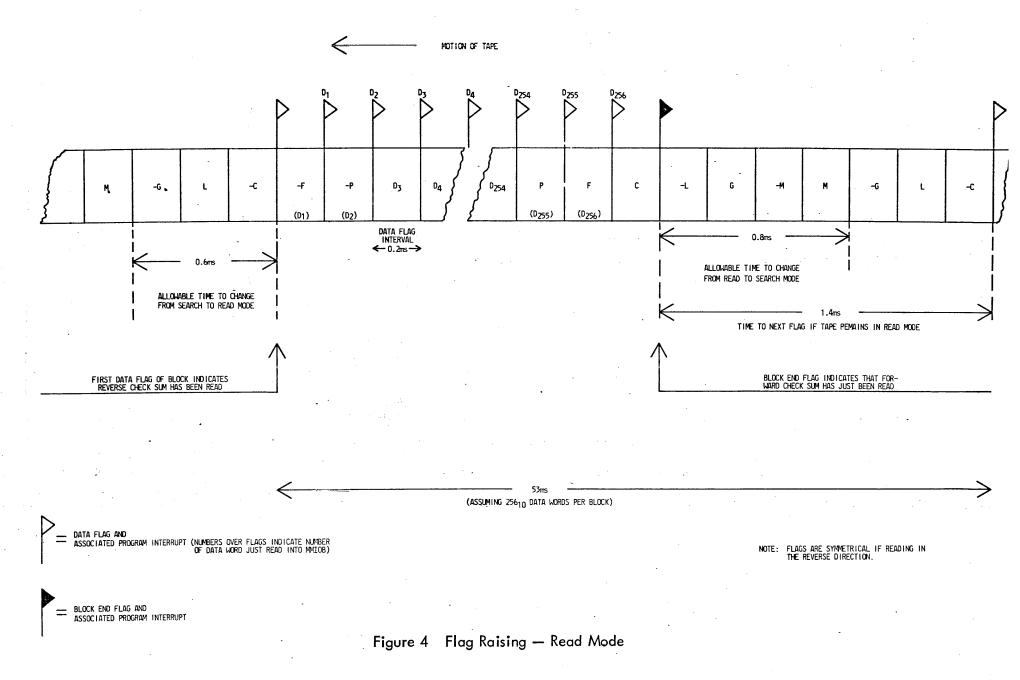

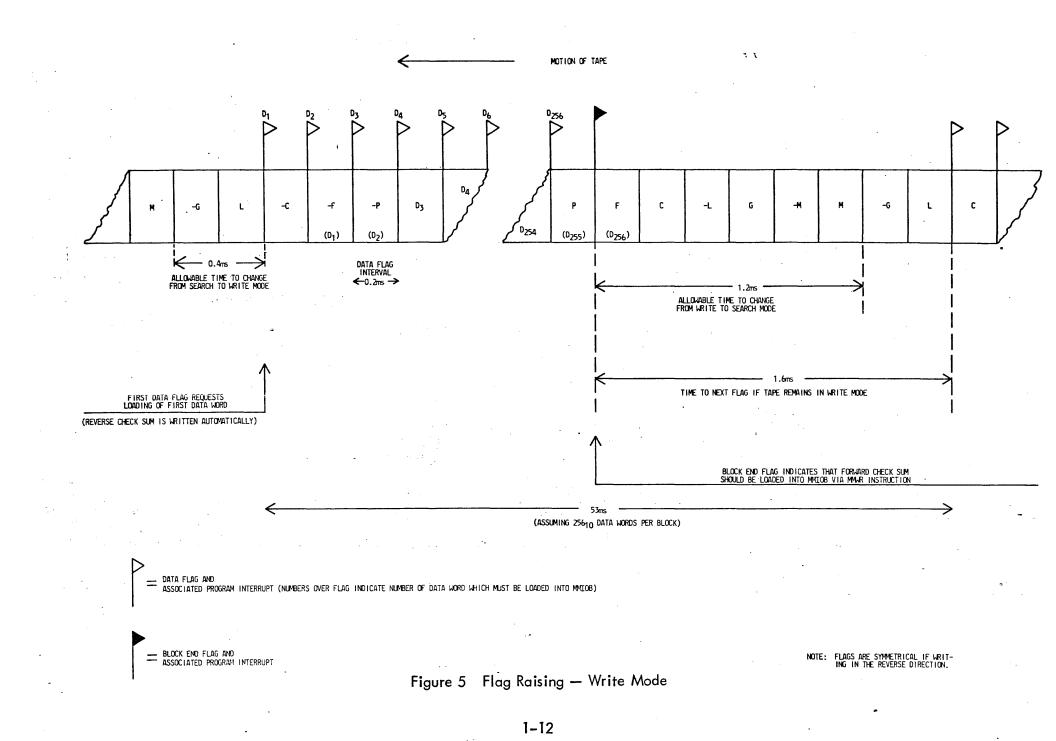

There are three main programmed modes of operation which require that the user either provide information to the DECtape system or accept information from the DECtape system. These are the search, read, and write modes. A fourth mode, move simply moves the tape without supplying or requesting information. In order to indicate to the programmer that the system is ready to transfer information, certain flags are raised. When these occur, the programmer must either load new information to be written, or unload information just read, and must do so within a specified time to prevent loss of information and error indications. If the program interrupt mode is being used, the raising of any of the flags mentioned also causes a break in which the individual flags must be interrogated.

In order to produce these flags, the mark track is read by passing the bits through an 8-bit "moving window" which shifts bit by bit as the tape moves. A decoder associated with the window interprets the pattern present, and raises the appropriate flags, if necessary. An 8-bit window is used, even though each mark is six bits long, to provide greater reliability, since

NOTE: END MARKS WHICH IDENTIFY THE PHYSICAL ENDS OF THE TAPE, ARE THE ONLY MARKS NOT SHOWN.

Figure 2 DECtape Mark Track Format (Assumes 256<sub>10</sub> Data Words Per Block)

a mark will not be recognized as legitimate unless the last two bits of the previous mark were legitimate. This is one of the reasons which requires ordering of the marks on the tape. Note that whether the program is reading or writing, the mark and timing tracks are always being read.

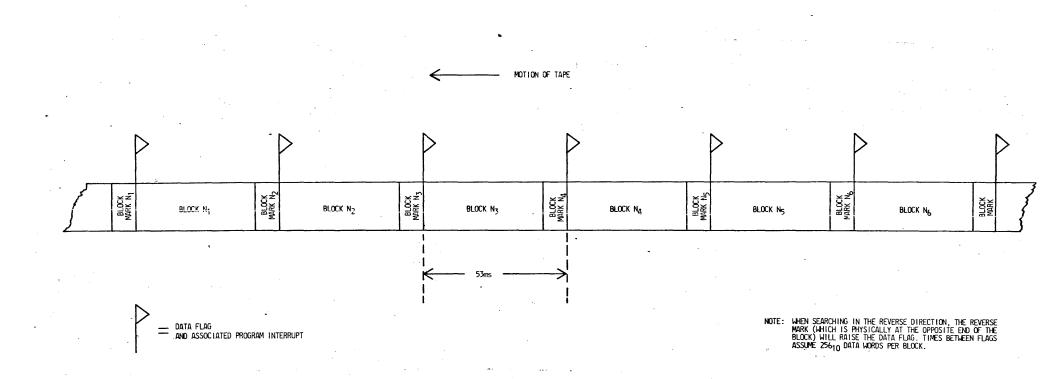

#### Search Mode

In the search mode the data flag is raised only when a block mark is read (see Figure 3). The program must unload the buffer within 53 msec, and bits 6–17 contain the block mark number.

#### Write Mode

In write mode, the DECtape system automatically writes the reverse check sum and raises data flags when it requires information to be written on the tape (see Figure 5). The first data flag requests the first data word of the block, and the last data flag requests the last data word of the block; therefore there are a total of 256 data flags for a 256 word block. Note that the program loads each data word as the DECtape system is writing the previous one; thus a flag is raised requesting a data word when it has just passed the place on the tape two words ahead of where the word is to be written. Compare this with read mode discussed below. Time between data flags is approximately 200 µsec. When the prefinal mark is detected, a block-end flag is raised which accomplishes two things. First it is a request for the program to load the cal– culated check sum (normally the complement of the 18-bit ring sum of the reverse check sum and the data words); and second, it allows the program to detect that a block has been completed without the use of any programmed counters. After the check sum is written, the writers are turned off to avoid any possibility of destroying the control portion of the block. Approximately 1.2 msec are available to switch to search mode if a check of the next block mark number is desired. If the control remains in write mode, the DECtape system writes the next reverse check sum and raises the next data flag after approximately 1.6 msec.

#### **Read Mode**

In the read mode the first data flag is raised when the reverse check sum has been read (see Figure 4. The reason for this becomes obvious since a block may be read in either direction independent of the direction in which it may have been written. The first word read, therefore,

Page Missing From Original Document

Figure 6 Mark and Information Track Bit Format

of the window or if a legitimate mark is not found after each six shifts of the window. These combinations of checks make it virtually impossible to misinterpret the mark track and thereby destroy information.

Nothing in the system prohibits the changing of modes at any time during the movement of the tape. However, care should be taken to include the difference in counting words when switching from read to write or from write to read, the recovery of the read amplifiers after writing (about two word times), and the fact that writing in various locations in the block invalidates the check sum at end of the block. Within those limits almost any combination of modes can be used; and because of the polarity sensed recording technique, even individual words can be replaced.

# Complement Obverses

One other unique feature of the mark track is that the six control marks before the data marks are "complement obverses" of the six control marks after the data marks. The complement obverse of a word is defined as the complement of a word with the bits read in the reverse direction, for example:

> 010110 (26) and 100101 (45) 001000 (10) and 111011 (73)

The data mark is the complement obverse of itself. When reading in the reverse direction, the flux reversals on the tape are opposite to those when reading forward and the bits are read in the reverse order. Therefore, the mark track window sees exactly the same thing in both directions.

# **Bidirectional Ability**

With one exception, no special logic is required to distinguish the format of the tape in either direction. The one exception involves the shifting of information into the DECtape buffer. Since the assembling of the 18-bit word is done by the hardware, it is necessary to shift the buffer in opposite directions for opposite movement of the tape in order to present words to the computer as they were originally written. This means that if a record is read opposite to the way in which it was written, each 18-bit word appears in the buffer exactly as it originally appeared in memory; however, the last word written would be the first one read, etc.

The end marks on either end of the tape illustrate this bidirectional ability even better. As the end marks are complement obverses of each other, only recognized is that end of tape which will physically come off the reel if further movement continues. Again, no special hardware is needed for opposite ends of the tape, and there is no harm in coasting into or turning around in the end zones. Errors are indicated only if attempting to go further into the end zone. The particular bit structure of the end marks is a repetitive one, so that any shift of three bits in the window appears as another end mark. This makes it virtually impossible to pull the tape off the reel in any of the normal modes. Sensing of the appropriate end mark stops the tape and raises the error flag if the tape is in any of the normal modes.

There are only two "abnormal" modes. One is the write timing and mark track mode, mentioned previously, in which no marks can be detected since they are being written. The other is the case where a tape has been left moving but not connected to the control (deselected). In this case, only the marks on the actually selected tape are recognized. In only these two circumstances can the tape be pulled off the reel.

# Block Size

Although the blocks are structurally alike in terms of the types of marks on the mark track, they need not contain the same number of data words. Indeed every block on the tape can be of different length, if such a format was created originally. The system will operate in the manner outlined no matter what the length of the block. One other feature exists which may prove useful, especially in the future designs. If for any reason the distance between blocks must be lengthened, it can be done simply by adding "01" codes between the reverse block mark of block N and the forward mark of block N+1 (see Figure 6). Since the pattern "01010101" already appears at the junction of the two marks, it may be continued indefinitely without harm.

# PERTINENT DOCUMENTS

#### Publications

The following documents serve as source material and complement the information in this manual. These publications may be obtained from the nearest Digital office or from:

Customer Relations Department Digital Equipment Corporation 146 Main Street Maynard, Massachusetts

Digital Module Catalog, C-1105 contains information pertaining to the function and specifications for the basic modules and accessories comprising the DECtape Control Type 550.

<u>DECtape brochure</u>, F-03-550-presents a general description of the DECtape system.

<u>PDP-4 Reference Manual, F-75</u> contains programming information pertinent to DECtape when used with a PDP-7

<u>PDP-4 Handbook, F-45A</u> gives programming information for DECtape used with the PDP-4.

PDP-1 Handbook, F-15D gives basic IOT programming information.

#### Library Programs

The following programming brochures are available now and may be ordered from the Digital Program Library at the address given above.

PDP-4/7 Programs

<u>Microtrieve</u>, 4–29–10 allows the programmer to save areas of memory on DEC tape and quickly retrieve such information using the toggle switches on the PDP-4/7.

<u>Microtog</u>, <u>4-46-10</u> describes various programs to detect any errors in the DECtape control.

DECtape Subroutines, 4-45-10 are programs which allow the programmer to read, write, or search the DECtape using prewritten and tested subroutines.

#### PDP-1 Programs

DECtape Control PGM, 1-26-10 is a subroutine which transfers data to or from DECtape.

DECtape Format Pack, 1-127-10 writes the mark track, timing track, and block numbers from 0 to  $1077_8$  on tape. It also allows the operator to check the tape after it is written.

Data Transfer Test, 1-128-10 enables the operator to check data transfer to and from the computer and the DECtape control. This program also indicates which flags are being detected during the test.

DECtape Rocker Program, 1–129–10 allows the user to oscillate tape over a desired area for debugging purposes.

DECtape Exerciser, 1-130-10 evaluates the performance of DECtape and determines the nature of any errors that might occur.

<u>DECtape Dump and Retrieve</u>, 1–130–10 allows the operator to store data on DECtape or retrieve data from DECtape using the TEST WORD switches.

Error Message, 1-132-10 functions with a DECtape control to type out errors on the on-line typewriter.

#### SECTION 2

# THEORY OF OPERATION

#### ENGINEERING DRAWINGS

All the DECtape prints are fully cross referenced. The numbers shown at the inputs or outputs of the logic blocks on the block diagram refer to the block schematic print numbers and geographical references as follows: The first two characters (EM, IN, C2, C1, etc.) indicate the mnemonic title of the appropriate block schematic, and the second two characters (B4, C2, etc.) indicate to which zone on the print the reference is made. The letter indicates the vertical dimension, which is shown on the right and left hand margins; and the number indicates the horizontal direction, which is shown across the top or across the bottom. The destinations (or origins) of all signals are shown within the block schematics. If a given signal goes two places, both at the same geometrical print location, this location is indicated twice. In this way a section of the wiring list can be built up for purposes of detailed troubleshooting or corrections to the hardware. Wiring lists are not maintained once the machinery is shipped. Refer to Appendix 1 for a detailed explanation of DEC symbology as well as reduced copies of the engineering drawings.

#### DECTAPE SYSTEM

The basic block diagram of the DECtape system is shown in D-550-0-BD. At the top of this diagram, a horizontal line representing information and control plugs 0J1 and 0J2 serves to separate the computer (above) from the DECtape system (below). Another horizontal line located at the bottom of the diagram, representing the information bus plugs at C21, 22 and the control bus at B3, 4, serves to separate the tape drive mechanism (below) from the control system above it. The purpose of this diagram is to depict the inter-relationship of major signals utilized in the DECtape system. Some of these signals are shown as input-output transfers (IOT's). These are located at the top of the diagram, and are designated as being relevant to either the PDP-1 or PDP-4/7 computer. Input-output transfers without such designations are common to both computers. Thus, the IOT MMRD as shown is common to both computers; whereas the IOT MMEF is relevant only to the PDP-4/7.

#### Data Transfers

Information transfers are routed to or from the accumulator (AC) if a PDP-4/7 is used, or to or from the input-output buffer (I/O) if a PDP-1 is used.

Data transfers between computer and tape are via the in-out register and the shift register in the control unit, as shown at the left of the diagram (D-550-0-BD). From the AC or I/O of the computer, information flows to the tape through 18 lines which connect the AC or I/O to the in-out register. These lines are one-directional only; a binary 1 is indicated by a ground on a line.

Information from the tape is forwarded to the AC or I/O from the in-out register of the control unit by means of another set of 18 lines; a 1 is indicated by -3 on a line.

A transfer of information between the in-out register of the control unit and the shift register is accomplished by a double set of 18 lines. Information flow between these registers is accomplished by simultaneously pulsing their in gates by means of an interchange pulse. During writing, the contents of the shift register are transferred to the tape through the write amplifiers and tape heads; during reading, information is transferred from the tape through the read amplifiers to the shift register. A detailed discussion of the shift register, in-out register, and read and write amplifiers is included later in this section.

# CONTROL FUNCTIONS

The basic control functions of the control unit are listed below. The titles of the block schematics which contain the indicated circuitry are shown in parentheses.

Reading of timing track. The bits on the timing track are read and transformed into timing pulses which control the sequence of DEC tape operation. (TM).

Reading of mark track. The mark track is read and decoded to obtain flag signals, sequence breaks, mark numbers, and block ends. (W).

Transfer of information. Signals are generated to denote the direction of information exchange between the computer and DECtape. Information to or from the computer is transferred in parallel form; information to or from the tape itself is transferred in serial form (IN).

Generation of control responses. The timing pulses (TP), the marks, and the mode of operation (read, write, search, etc.) are used to generate proper control responses (flags, shift signals, interchange pulses, etc.). (C62, TM). Memory of mode, selection, and motion commands of the program are shown in (C1).

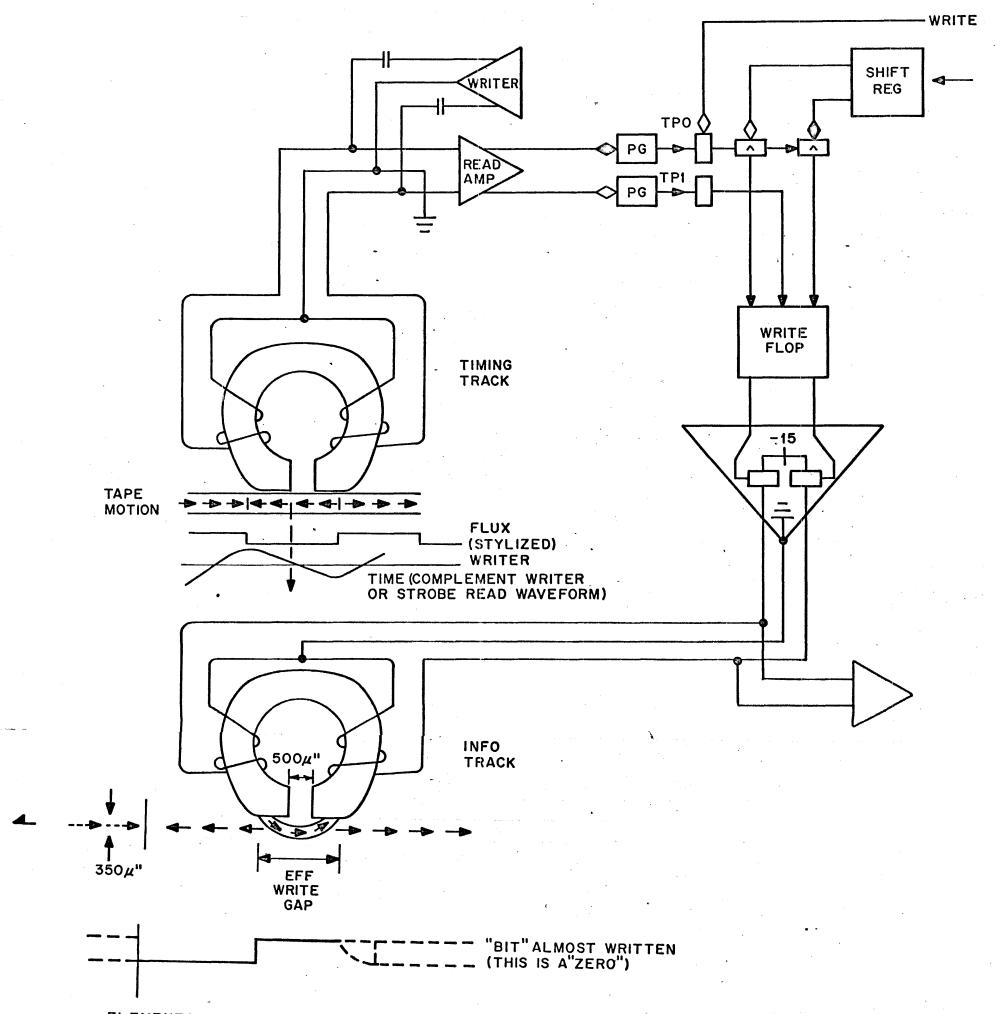

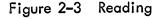

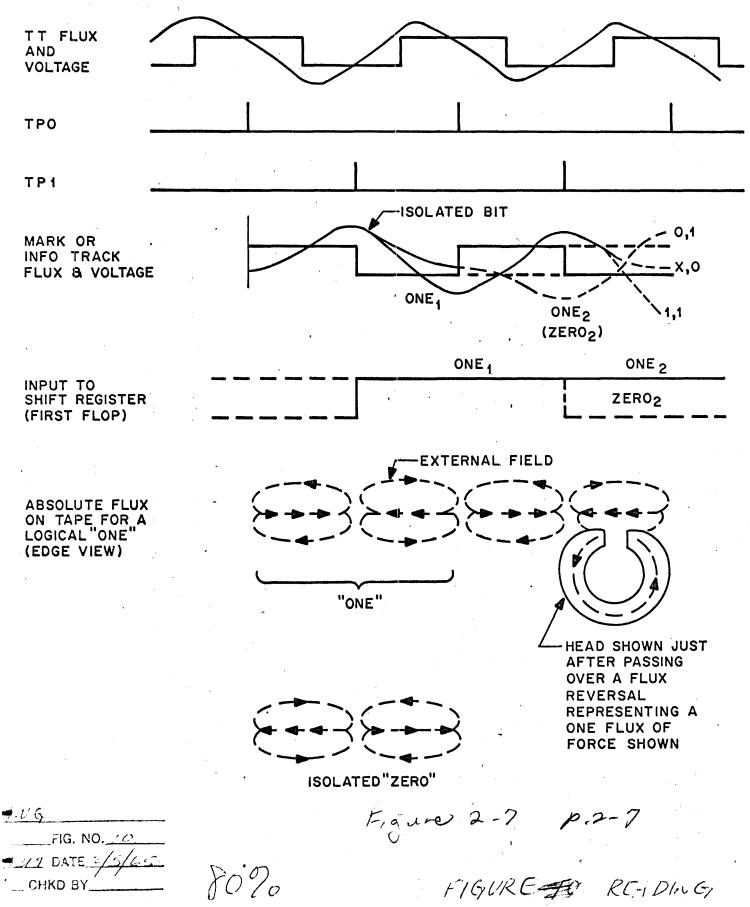

### Reading of Timing Track

The basic timing pulses (TP1 and TP0) are derived from the timing tracks of the tape. Refer to the TM print. TP1 is generated during the negative-going zero-crossings of the timing track voltages peiked up by the tape head, and TP0 is generated from the positive-going zero-crossings. Tape head voltages appear as sign waves. The zero-crossings of the voltages picked up by the head are transformed by the read amplifier of the 4523 module into square waves, the transitions of which occur in synchronism with the zero-crossings of the original head voltages. The read amplifiers, which have high and uncontrolled gain, saturate at any input signal over 100µv, p-p.

Timing pulse TP1 marks the time the change in direction of flux of the data or mark bits is at maximum, and therefore ready for transfer to storage registers. During writing it is used to write the flux reverse which represents the bit. Timing pulse TP0 denotes between-bit time, i.e., the appropriate time to shift into the writers the next bits that are to be written. In effect, TP0 designates the time that the head is passing through the boundary region between bit loca-tions on the tape.

Another timing pulse designated as TP2 is obtained by delaying TP1 approximately 4.5 µsec. TP2 is used to check mark track information picked up by the TP1 preceding it. The time interval between TP1 and TP2 is sufficient to allow the CD gates to set up. In effect, TP2 commands an inspection of the control word (if any). TP0 is sometimes used to accomplish the same thing.

#### Relay Timing and Mark Signal

The relay timing and mark signal (RELTM) functions to suppress timing pulses picked up from the tape during this mode of operation. In addition, the RELTM signal enables the timing and mark track writers and physically connects them to the TT and MT. It also starts the WRTM (write timing and mark MODE) clock. In addition to the above, the RELTM signal lights a red lamp on the drivers.

# Figure 2–1 Method of Writing on DECtape

# ELEMENTS OF FIXED POSITION WRITING

READ VOLTAGE (LATER ON READ PASS) HEAD FIELD INTENSITY (ALONG THE TAPE)

Fig 2-1 12 2 - 14

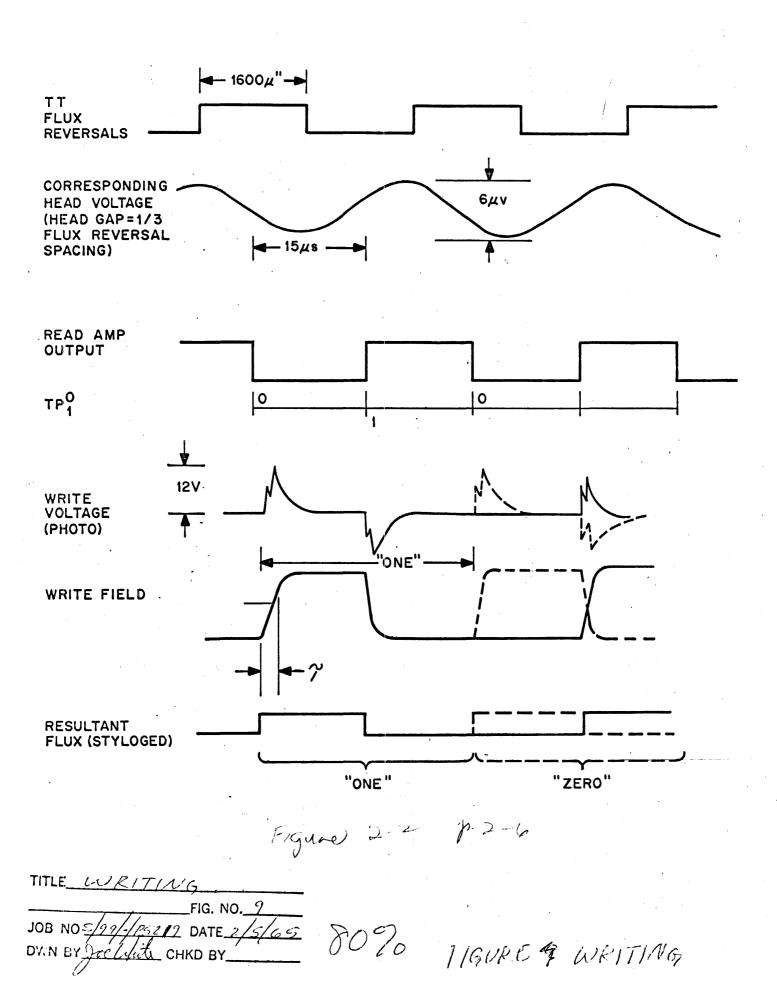

Figure 2-1 shows the physical position of the heads at time T after a timing track voltage zero crossing has passed under center of the TT read head, eg., the zero crossing produced a TP1 which complemented the writer. The field around the head has just completed switching and the bit just written will be centered under the zero crossing if the tape has moved 1/2 of an effective write gap in the time T taken to complete the switch of the head.

سر ۱۰ و The clock mentioned in the paragraph above drives a gray code counter which, in turn, drives the track writers and generates quadrature phase TP pulses by means of the same pulse amplifiers which normally buffer the timing pulses. It should be noted that the TT writers are switches at times which are inquadrature with the timing pulses. This ensures the preservation of the relationship between the negative-going, zero-crossing of a timing signal and the coincidence of the flux reversal of the data or mark bit.

# Reading the Mark Track

The mark track is read in the same manner as are the information or data tracks. That is, timing pulse TP1 loads the first flip-flop of a shift register from the (push-pull) outputs of the read amplifier. This occurs at the time of maximum flux reversal of a data or mark bit passing under the head. This same flux reversal was previously written on the tape during an earlier writing operation by means of the same TP1. Since the head senses maximum flux reversal at TP1, an accurate output is obtained from the associated read amplifier. The direction of the flux change determines the polarity of the read amplifier output, hence the kind of bit being read 1 or 0. Figure 2-2 shows the relationship between flux directions and binary value as recorded on the tape.

Unlike the data words, which are routed as described above between tape and computer, the mark track bits are routed only to the control unit. In the control unit, the mark track bits are shifted into the window register. This 8-bit register always holds the last eight bits read from the mark track. Each new reading of a new mark track bit shifts the register so that the new bit is shifted in, and the old eighth bit shifted out. Since mark track bits are read in succession, there is a succession of shiftings of the window register. After each shift, however, the window register accurately reflects the last eight bits read from the mark track.

Note that time displacement,  $\mathcal{T}$ , indicated does not result in a displacement of bits since the bit is "written" at the trailing edge of gap and "read" at the center of the gap. The physical displacement (LAG) tends to cancel the effect of time displacement (LAG).

# Figure 2-2 Writing

# Window Register

The outputs of the flip-flops of the window register are fed to a group of AND circuits. Refer to print W. The function of these latter circuits is to detect particular patterns as they appear in the register. Any particular pattern of bits in the register remains the same only for a period

2-6

al

of approximately 33 µsec; at the end of this time, the next TP1 pulse shifts the register to create (possibly) a new pattern. Accordingly, the AND circuit outputs can be asserted only for 33 µsec. Thus, after the mark track heads read into the window register a particular pattern as created by the last bit read, the AND circuits, fed by the register, are allotted a time interval of 33 µsec in which to recognize the pattern and produce the appropriate responses.

The AND circuits are comprised of diodes which drive inverters. The circuits are arranged so that any particular inverter output is at ground whenever its associated flip-flop in the register is enabled. (During the writing of timing and mark tracks, the RELTM signal is used to inhibit the shifting of the window register to prevent the accidental detection of marks during this process.)

Although referred to as an 8-bit register above, the window register stores a ninth bit which, although not part of the pattern fed into the AND gates, serves to control the accurate reading of marks during starting or when switching to a running transport. Bit 9 is set into the register on a shift pulse only if bit 8 is a 1. Bit 9 is cleared by the clear window pulse, which clears all other flip-flops in the register. When not present, bit 9 prohibits operation of the AND circuits into which the window register feeds. When present, bit 9 enables these circuits.

The importance of bit 9 resides in its power to prohibit the reading of mark track patterns until the proper conditions are met. Thus, at the start of the mark track reading process, after clearing of the window register, a one from the mark track must be shifted through the window register, to position nine in the register in order that a pattern (bit arrangement) in the register may be detected by the AND circuitry mentioned above. In this way, bit 9 prevents partial patterns from being erroneously detected. (Other circuits also function to prevent erroneous detection; these circuits clear the entire window register when activated.)

The patterns or bit arrangements presented by the window register to the AND gates for detection are six bits long. The window register itself holds eight bits. The ninth bit, although forming a part of the register, is in no way utilized by it in the pattern detection process. Because of this circuit configuration, the window register is capable of providing 8-bit patterns; the order of code patterns is fixed in the shift register patterns. The 8-bit pattern capability utilizes the last two bits of the preceding pattern.

#### MSY Register

The window register and the associated decoding circuitry do not completely decode the mark track patterns. To achieve complete decoding, the MSY register circuit is used. The function of this MSY register is to decode the four blockstart marks (LOCK, REV CHECK, D1, and D2), and the four block end marks (prefinal, final, check, and spare).

The MSY register is loaded when a block mark is detected. Loading of a MSY register consists of inserting the binary arrangement 1000 into the register. Each time a block start mark is detected, a shift in the MSY register occurs. This shift causes the initial 1 to travel down through the register as other ones follow it. Thus, the first shift would cause the register to read 1000; the second, 1100; the third, 1110; and the fourth, 1111. The MSY register states are ANDed with detected block start marks to obtain the initial four marks mentioned above.

The four block-end marks also cause four shifts of the MSY register. However, zeros rather than ones are propagated or shifted down the register. In this case, the initial state of the register is 1111. At the first shift, the state of the register is 0111; at the second, 0011; the third, 0001; and the fourth, 0000. This last, or fourth, state is decoded during troubleshooting procedures.

The shifting of the MSY register occurs at TP2. The block start and block end marks are detected between one TP1 and the next. As a consequence of this, the useful output of the mark detection circuitry considered as a whole occurs at TP2.

# Writing the Mark Channel

Mark track words furnished by the computer are written on the mark track of the tape when the DECtape system is in the RELTM mode. The WRTM command (a result of the computer-issued MMLC instruction) must also be issued to effect mark track writing. Normally, the writing of the mark track is initiated when the DECtape system is in the stop condition. This permits the delay inherent in start up, at which time the DIP signal is effective, to render the timing pulses from the local clock ineffective. In this way, flags normally raised by the timing pulses are kept absent.

#### Word Counter

After start up, data flags are raised automatically at each word time. These flags are raised by the EK (or word counter) circuit. This circuit consists of a ring arrangement of six flip-flops in which a single one is caused to circulate. At the issuance of each data flag, the computer loads the word to be written on the mark track into the IOB. The word remains in the IOB until issuance of the next flag request, at which time the word is shifted into the shift register. From

the shift register it is transferred through the write amplifiers and tape heads to the mark track. Since the shift register is logically divided into three sections, the writing of a mark channel is accompanied by an identical writing of data channel number one.

# Mark Track Errors

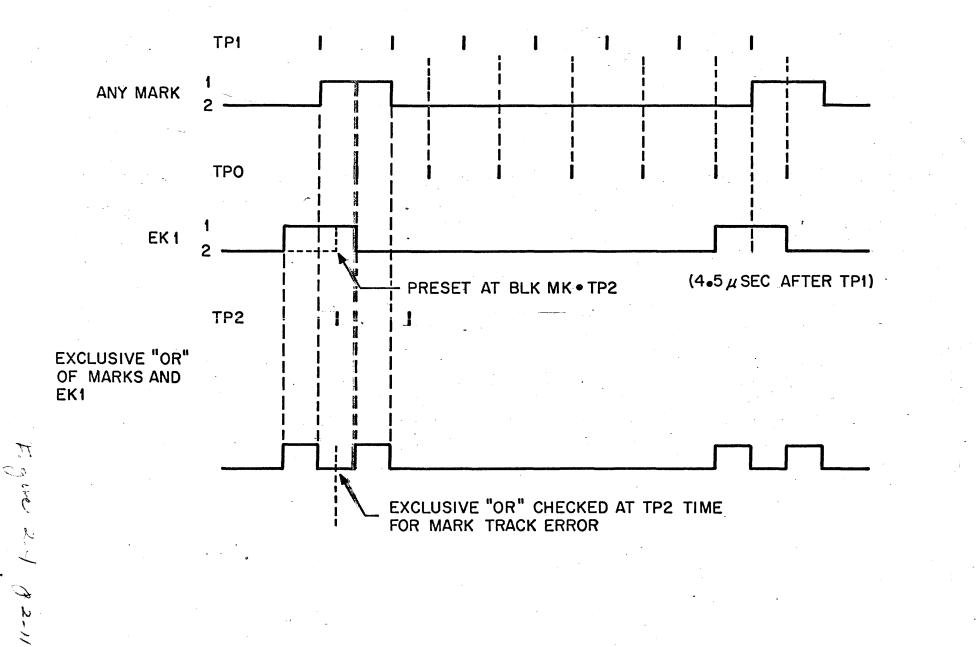

Mark track errors are detected, if present, as follows. There are specific marks which occur each sixth time the window register is shifted. By using these specific marks, <u>an error check</u> procedure based on verifying the passage of six timing pulses between each such specific mark is effected. Utilized for this procedure is the EK (word counter) used also in the mark track writing process.

The EK is present at the same time that a block mark is detected (at TP2). The EK is rotated by TPO's. After six such rotations, caused by six successive TPO's, the EK is returned to its initial condition. As each initial position is reached, a new specific block mark should also be present. Thus, assuming no error, the initial condition of the EK and the detection of a specific block mark should exist concurrently. Should the two not exist concurrently, an error has occurred.

Since the EK is shifted at TPO, and since the window register is shifted at TP1, the concurrency of the initial state of the EK and the existence of the specific block mark are valid only after TP1 is issued and only before the following TPO is issued. Because of this, the concurrency is checked, or strobed (since it is in gate form) at TP2.

It should be noted that there are particular times during DECtape operation when any error checking procedure is superfluous. For instance, during search, errors obtained from portions of the tape not yet read or written are irrelevant. Similarly, in the WRTM mode and the MOVE any MTE is also irrelevant.

For the above reasons, the negative (for error) output of the error detecting circuitry is clamped to ground and rendered inoperative unless a particular mode such as write, read, write all, or read all, unclamps it.

# Figure 2-4 EK Waveforms

Indications resembling errors, but not errors as such, are eliminated by clearing the window register during their "presence." In this respect, the two areas on the mark track located near the block mark errors are suppressed.

During the interval of time which elapses between the start of tape operation and the attainment of proper tape speed, the synchronization signals for the EK are nonexistent. Thus, error-detection cannot be performed. The BMF flag is set by the block mark and is used to gate out MTE's detected during this period. The tape system, when in this condition, would normally be in the search mode, rendering error detection superfluous, as described above. However, when in this condition, the tape system may be in the read mode. The BMF flag is then cleared by the clear window pulses.

# Transfer of Information

In addition to furnishing information for, or receiving information from, the tape, the AC or 1/O can also forward a portion of its contents to the control unit for purposes of control only.

By means of IOT instructions, the computer is able to select a tape unit (1 out of a possible 8 plus zero, or no unit), direct the motion of the tape, and command one of several possible, modes. The selection of a tape unit is controlled by the arrangement of bits 2 through 5 in the AC or I/O. These bits are loaded into the selection register by the MMSE instruction. A ground on any of these lines indicates a binary 1.

#### Load Control Instruction

The MMLC instruction, or load control instruction, is formed by the arrangement of bits 12 through 17 in the AC or I/O. These bits are transferred by means of six lines to the command logic circuitry and the motion control circuitry. This circuitry then translates the bit arrangement into a specific tape direction and a specific equipment mode (move, search, read, write, WRTM, read all, write all, and readin mode). A ground on any of these six lines represents a binary 1. There are eight possible modes which can be commanded by the command to the logic circuitry.

# Timing Pulses and Mark Track Information

Like the accumulator or I/O, the tape can furnish information to the control unit for control purposes only. This information comes from the mark and timing tracks and is not passed through to the computer as data information. Instead, it is routed to the timing pulse generator circuitry and mark detection network (and window register). The information so routed consists of the timing pulses and mark track information derived from the tape.

The timing bits from the tape are picked up from the bus which is connected to a particular timing track head by the selection circuits, fed through a read amplifier and forwarded to the timing pulse generator. This generates three timing pulses: TP1, TP2, and TP0. These timing pulses are forwarded to other circuits in the control unit.

Mark track information, picked up by the mark track heads, is forwarded to the mark detection network circuitry. In accordance with the information received, the mark detection network circuitry issues signals signifying that one of the various mark codes written on the mark track has just passed over the head.

Operating in conjunction with the timing pulse generator is the WRTM clock circuitry. The purpose of this circuitry is to write timing track information on the tape. Information is forwarded from the clock to the tape through a write amplifier.

# **Read Status Instruction**

سر ۱۰ The DECtape control unit transfers nondata information into the AC or I/O by means of the MMRS instruction. Although the bits constituting this instruction are temporarily stored in the AC or I/O, they do not represent any part of the data work or words. As shown on the overall block diagram (D-550-0-BD), the six leads composing the MMRS consist of REV, GO, UNABLE MK TK ERROR, MISS, and END. The MMRS command also reads the three flag levels into bits 0-2.

# Flags

Another major group of signal leads of importance in DEC tape system operation are those generated by the flag response net circuitry. This circuit issues to the computer the data flag, block end flag, and error flag signals. In the PDP-4/7, these signals are used to produce a program break request, enable the skip logic, and are sent to the AC on a MMRS.

In the PDP-1, the data flag signal (MMDF) is an indication to the computer that a particular data word being read or written is assembled and ready for transfer. The block-end flag (MMBF) indicates to the computer to unload the check sum if reading, or to load the calculated check sum if writing—indications to which the computer can respond by issuing a MMRD instruction or a MMWR instruction. An error flag (MMEF) indicates to the computer that one of four error conditions has occurred; accompanying this error flag signal is the MMRS format (described above) stipulating the type of error responsible for issuance of error flag.

# Generation of Control Responses

In general, the timing relationships between the computer and the DECtape system are governed by the ordinary program break control function. That is, the computer selects the mode of DECtape system operation by furnishing it with a MMLC instruction; this instruction directs the DECtape system to search, read, or write. The DECtape system, in accordance with mode

generates the flags appropriate to the mode. The generation of flags and other responses continues until the tape is stopped by command, the mode is changed, or the tape end is reached.

The DECtape system control is in large part based on actions caused by reading of the mark track. These actions consist in the main of the initiating flag signals. A block mark is detected each time the tape heads encounter the boundary between data words. Depending upon the type of mark detected, and the mode of operation, a flag signal is issued. For example, in the search mode, the data flag is issued if the block mark is detected at TP2. The block mark and the TP2 signal and its attendant flag cause issuance of the interchange pulse, which shifts data between the shift register and the in-out register.

#### Searching

In the search mode, block number codes as read from the tape are forwarded to the computer for comparison purposes. Such forwarding is accomplished by means of the interchange pulses which transfer the block number codes from tape to the in-out register. During search, such transfers occur every 53 msec (for a 256-word block). Each block number code so transferred is accompanied by the data flag. Should the computer fail to recognize the data flag before the next raise data flag pulse is issued, an error flag signal is issued. This flag signal is generated by a CD gate which has as inputs the RDF signal and DF signal. The output of this gate sets the miss flip-flop to the 1 state. The encountering of an end mark automatically sets the END flip-flop, and the GO flip-flop is reset, stopping the tape.

#### Writing

The commanding of the write mode by the computer results in the issuance of a data flag by the control unit to the computer. The purpose of this flag is to indicate to the <u>computer that</u> the in-out register is prepared to accept a word from the computer for writing on the tape. The computer then transfers the word to be written to the in-out register by means of a MMWR command. The MMWR command extinguishes the data flag. (The WDA level results from a ORing of the block start and data marks. This level appears when the write data flags are to be raised.) During write, after the computer has transferred a word into the in-out register, the word is then interchanged and shifted. This process requires between 140 and 480 µsec, depending on speed and program timing. During this time, neither the stop mode nor the read mode can be commanded.

Should the computer direct the writing of information exceeding a block length, the DEC tape system responds by shifting to the reading mode (in the block end area), writing the reverse check sum, and raising the first flags; the DEC tape system then reverts to the write mode and utilizes TPO's for shifting purposes in writing.

Since the command to stop writing is inhibited in the boundary region between the last data word and the check sum, any read command given during this time is temporarily held in abeyance. At the raising of the block flag (read mode), a minimum delay of 240 additional µsec is necessary in order that a stop command be carried out.

# Reading

Entry into the read mode is accompanied by the issuance of data flags signifying readiness of words for transfer to the computer. The data flags are generated by the RDA signals and the TP2 pulses. The RDA signals, in turn, are generated by the OR formed by combining the third and fourth block start marks, data mark, prefinal, and final signals.

Data flags are lowered by the computer-issued MMRD signals. The MMRD signal strobes the word in the in-out register into the computer.

#### Switching from Write to Read Mode

In the read mode, any switching to the write mode within a particular block cause the following to occur. The data flag (read mode), signifying the readiness of the word in the in-out register for transfer to the computer, is lowered by an MMRD. Assuming an MMLC (write) is issued just prior to the transfer, the first word to be written in the new write mode is written in the third word space following the word space from which the last word was read. Switching from read to write within a block necessitates the loss of two word spaces, which are neither written into nor read from. The first data flag raised after the switchover indicates that the last word read has been transferred to the computer, and that the second word to be written can be released by the computer.

There is an exception to the above: if the first word to be written after switchover occupies the last data word space in the block, an RBF is raised. Also, if the first word so written falls into the check sum word space, no flag is immediately raised; instead the next flag is issued at the start of the next block. Any switching from write to read occurs in the boundary region following the last word loaded for writing. In this boundary region, a dummy flag signal is issued. However, this flag signal corresponds to no special action; this flag is lowered when the first flag for read is raised. Because of the switchover, no validity check of the first three or four words read is possible.

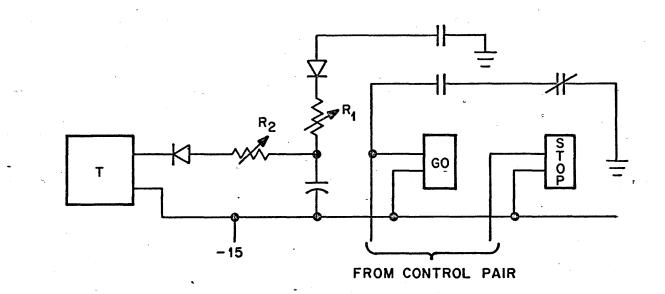

# Selection (Refer to print C1)

Complementary inputs formed via inverters tied to AC bits (or I/O) 2 through 5 are connected to the CD gate level inputs of four Type 4218 Flip-Flops. The CD gate pulse input is generated by a select command from the computer (see DECtape Instruction List).

This instruction code loads the contents of the AC into the 4218 Flip-Flops. A 4671 Octal to Decimal Decoder then decodes the FF outputs and pulls the example selected lint to approximately - 3v from a more negative voltage. The selection lines are connected to a selection relay located in the 555 Transport, one side of which is tied to -15vdc. Selecting a transport connects the motion control and data bus from the 550 Control to the selected transport.

# Motion Control (Refer to print C1)

Complementary inputs are formed via inverters tied to AC bits 12 and 13. The outputs from the inverter on AC bit 12 are tied to CD gates wired to the GO flip-flop. These same lines are combined with the complementary ACB13 input through two negative AND gates. The AND gates enable the CD gate set input to the Rev flip-flop and are provided to inhibit a change of direction command at the same time a stop command is given.

The GO and REV flip-flops are used directly for control functions as well as for motion commands to the DECtape transport. Solenoid drivers Type 4608 are used to buffer the motion commands to the transport since 100 ma from -15vdc is required to drive the relays in the transport. Additional buffering for control function is provided by standard inverters.

The pulse input to the CD gates comes from a 4606 Pulse Amplifier, which initiates a pulse when the computer instruction to load control is given. Thus, if ACB 12 and ACB 13 are set to a 1 and the load control instruction is issued, the CONTROL MOTION flip-flop will be set to command GO in reverse to both the transport and control.

# **Function Control**

AC bits 15, 16, and 17 are used in conjunction with the load control instruction to load the control with the function commands. This is accomplished by forming complementary inputs with 4102 Inverters and sending them to the level inputs of the CD gates of a 4218 Flip-Flop. The 4218 acts as a buffer which returns the function commands given when load control instructions are issued. These flip-flop outputs are then decoded by a 4151 Binary to Octal Decoder. The functions provided are MOVE, SEARCH, READ, WRITE, RDALL, WRALL, and WRTM. Refer to the Instruction List for details.

Pin D of the function decoder is connected to the output of an inverter whose input is from the GO flip-flop. Therefore, no asserted level (gnd) is issued from the decoder until the GO command is given to the control.

# All Halt

The ALL HALT feature stops all moving transports whenever the computer programs stops. This feature is provided by two paralleled 4680 Solenoid Drivers which provide a ground to the go relay latching circuit in the transport when the computer RUN flip-flop is in a 1 state. In addition, an inverter is connected to the GO flip-flop from the RUN input in such a manner that when the RUN state is 0, the GO flip-flop is pulled to a 0 state, thereby stopping the motion of the selected transport.

#### Delay in Progress (DIP)

The delay in progress circuitry places the control in a timed state of abeyance whenever the transport is commanded to start or turnaround.

This allows the tape to attain a reliable operating speed before normal control functions are permitted to resume. Two separate 4303 Delays are OR combined to form the DIP state.

One delay accounts for the time required for a transport to reverse direction (TA delay) and one allows the transport to reach full speed from a stop condition (start delay). The start delay is inhibited via the CD gate input whenever the tape moves into an end zone. This is necessary when searching for the first or last block on tape since the detection of an end mark automatically

sets the GO flip-flop to 0. The computer would quickly reverse the direction of tape, and if not inhibited in the above manner, this GO flip-flop would initiate the start delay, thus causing the transport to miss the first block on tape.

# Write Interlock Circuits (WR-Interlock)

The write interlock circuit enables the 4523 Read-Write to write only when the WRITE LOCK switch is in WRITE position. Although somewhat redundent, the NR-interlock circuit shown on print Cl location Al-4 has been included for reasons of clarity. Basically, the interlock circuit originates in the transport with the WRITE LOCK switch and a contact on one of the selection relays. With the interlock open, the resistor-diode network shown at ClB5 places 25vdc across the contacts (for contact reliability) and places a negative level at the 4141 2-Input Positive AND Circuit. When the interlock circuit is closed, the resistor-diode network places a gnd level on one input to the AND circuit. The second input is gnd when the write enable (WREN) flip-flop is a 1.

To insure switches speed and reliability the output from the 4141 is inverted then buffered with three parallel inverters. The buffered output is tied directly to the enabling level of the information channel writer amplifiers. The timing and mark channels writer amplifiers, however, are enabled via the RELTM relay only when the RELTM switch is on. This switch is used only when timing and mark information must be written on the tape. Further protection against failures which could cause the timing and mark track to be destroyed is afforded through contacts on the RELTM relay which completely disconnect the write amplifiers from the timing and mark channel.

It is therefore impossible to write in the timing (TT) and mark channel (MT) unless the RELTM switch located on panel A of the control logic is turned on.

A red indicator lamp on each transport and a white indicator lamp next to the filter switch warns the operator that the TT and MT writers will be enabled if the command to write is given.

# Clear Inputs

Refer to print C1 unless otherwise noted. When the system is turned on, POWER CLEAR pulses for the computer are sent to a 4606 Power Clear pulse amplifier and to one of the preset inputs of the EK counter (W). The output from the power clear pulse amplifier clears the selection, motion, function and WREN flip-flops (C2). In addition this power clear pulse is connected to a PA which clears the ERROR STATUS flip-flop which in turn clears the data flag and block flag via a third pulse amplifier.

# Timing Control

The output of the 4523 Read Amplifier is sent to a 4410 Pulse Generator which standardizes transitions from the read amplifier to DEC 400-nsec pulses (see the TM print). The negative output of both 4410 Pulse Generators are combined with the number of conditional inputs via a 4117 Negative AND Gate. One such enabling level is the delay in progress (DIP) signal which was previously discussed. In addition, an enabling level from a cross talk delay is used to reduce the effect of cross talk during writing. This writing introduces an 8-µsec delay after actual origination of any TP signal mentioned above. After writing (or before writing) the time lapse between TP1 and TP0 or between TP0 and TP1 is 16-2/3 µsec. The OFF level occurs whenever the GO flip-flop is cleared provided the write enable flip-flop (WREN) is in the 0 state. This AND function of the WRITE ENABLE signal allows the timing pulses to continue even though the GO signal may be absent. Finally a RELTM level is used to inhibit the pulses from the pulse generator during write timing and mark track mode since in this mode the time pulses are generated directly from this CK counter.

The output from each AND gate is then sent to a pulse amplifier for buffering. It is the output from each of these PAs, TP1, and TPO, which is used for timing throughout the control. During write timing and mark track mode, the time pulses are generated by the CK counter via the CD gate input to the buffer pulse amplifiers mentioned above. A third time pulse, TP2, is derived from time pulse 1 by using time pulse 1 to strobe a 4.5 psec delay. The output of this delay is a pulse which is then buffered by a 4606 Pulse Amplifier, the output of which becomes TP2. Reference is made to TP2A which is nothing more than the unbuffered TP2 directly from the output of the 4301 Delay. For all practical purposes both TP2 and TP2A occur at the same time.

#### Decoding the Mark Track

With the knowledge of how the computer selects the unit, transfers motion and function commands to the control, and knowing how time pulses are generated, it is now possible to describe in detail the decoding of the mark track. Refer to the print designated Timing Diagram (TD). This print outlines the sequence in which the bits appear in the mark track. As may be seen, a flag is raised every sixth IOT. Each complete block on tape is organized in the following manner. The block begins with a block mark flag followed by a reverse guard; this is followed by four block starts, N number of data words, four block N's, and a guard and reverse block mark. To allow for expansion of the block number, two code 25's are placed between the reverse block mark and the forward block mark. Code 25's are not decoded by the mark track decoder, therefore they do not interfere with normal operation. The block starts are further sub-divided into a lock, a reverse check, and data word 1 and data word 2. The block ends are subdivided into prefinal, final, check, and spare. The octal number which defines the sequence of bits as decoded by the mark track decoder is found written just above each of the previously mentioned six slots or six bit words on the mark track. This sequence as outlined remains the same no matter in which direction the tape is moving.

#### Mark Track Decoding

Refer now to Print W, Mark Track Decoding Error. Since the mark track is a single channel, the bits are read serially. Location D2 on Print W shows a representation of the head. The signals read from the head are sent to 4532 Read Amplifier. Only one output of this amplifier is used; that is Pin Z. This output is sent to a 9-bit shift register or window as was previously described. Only when the series of bits shifted into this window form a pattern shown in the block just above the shift register will there be flags raised as indicated. These flags will be at a ground level. The one mark that was not previously described is the end mark. This comes up whenever the tape reaches an end zone.

The window is shifted by a circuit which comprises TP1 and RELTM located a C6 on Print W. A second input, clear window input to the shift register, is found at location D2. Please note that the output from the clear window PA is produced for both beginning and end of the delay in progress (DIP) for a block mark present at TP0, a guard mark present at TP0, and whenever the GO flip-flop goes to a 1 or POWER CLEAR pulses are present. The period of time for which the window is nonoperative or the window is cleared is shown as a "window shut" period indicated on print TD or Timing Diagram. Please note that the "window shut" condition remains for one slot more when initiated by the block mark than when initiated by the guard mark.

This is due to the fact that the code following the block mark is a 32 which has a 0 bit in the first slot after the block mark whereas the reverse mark has a 1 in the first slot after the guard mark.

Referring again to Print W, the block ends and block starts are subdivided by a second decoder, a 4261. This decoder has somewhat of a window also. It is a 4-bit register which is filled or cleared with ones at specific times in the shift process. The shift register flip-flops are designated MSY<sub>1</sub> through <sub>4</sub>. These flip-flops are preset to a 1000 with the condition of a block mark and TPO. A somewhat more complicated gate allows the shift register to shift at TP2 only with either block starts or block ends. However shifting of ones is done exclusively with block starts, and shifting of zeros is done with block ends. Block ends actually load at the MSY<sub>1</sub> flip-flop with zeros; therefore after four TP2's and block ends, the MSY register is cleared.

This register in conjunction with block ends, block starts, and data marks produces the outputs indicated in the block just above the MSY register. For example, the preset condition in conjunction with the first block start produces what is called a lock output at pin X. As a further example, please note that the read data (RDA) output is available with either data or block starts or block ends and the MSY shift register, containing ones in the MSY<sub>2</sub> and MSY<sub>3</sub> flip-flops. The inverters to the right of the 4261 Decoder are used primarily for inversion and buffering of the outputs from the two decoders.

The presence or absence of a mark from the mark track decoder is checked through the use of an EK counter located on Print W at location C2. This EK counter is a 6-bit register which is wired to shift a single one sequentially through each of the six registers. Thus looking at an output from any one of the flip-flops in the register, a change in state of the output would occur for 33-1/3 usec out of 200 usec essentially duplicating the pattern shown on the timing

and by the computer. During

normal read consumptions whenever a block mark is decoded by the mark track decoder. This puts the EK counter in synchronism with the marks from the mark track. Error checking of the mark track is accomplished through an exclusive OR circuit which checks for both the absence and presence of a mark. The exclusive OR circuit is located at D5 on Print W. The guard mark, block mark, block ends, block starts,

and data marks are ORed together in a 4117. The output of this gate is sent directly to one input of a 2-input AND gate, then inverted and sent to one input of a second 2-input AND gate. The second input to both AND gates is  $EK_1^0$  and  $EK_1^1$  respectively. The ORed outputs of both the AND gates thus form the exclusive OR of the EK counter and the marks as decoded from the mark track. This output is sent to a 3-input AND gate which enables the mark track error to occur only when the window is open and a block mark is found.

The block mark found or BMF input is derived from a flip-flop located at C3 on Print W. This flip-flop is zeroed at TP2A time when a check mark is decoded as well for all conditions of clear window except block mark. The BLOCK MARK FOUND flip-flop is set to a 1 at TP2A time only when a block mark is found. Referring once again to the mark track error output located at C6 on Print W, the 3-input AND circuit inhibits mark track error detection within each block in the inter block zone. A 4-input OR circuit is tied to the output of the mark track error detection circuit. This gate inhibits mark track errors for all modes except read, write, read all, and write all. In essence, mark track errors can occur only in the data portion of a block and only in the read, write, read all and write all modes. The output from the mark track error circuit enters a CD gate on Print C2 entitled "flag response data control outputs." It is strobed at TP2 time to set the MTE or mark track error flip-flop to a 1. The output of the MTE flip-flop is inverted and sent to control plug D1 where it is made available to the computer AC input as a status bit. The MTE output also goes to an OR circuit located at A5 on Print C2. This OR circuit forms the OR of all error conditions which will be explained in detail later. The output of the OR circuit is inverted and is also made available to the AC through data control plug D1.

# Data Transfer

سر ۲۰

> Data transfer to and from the control is handled through 4228 modules. These modules were especially designed for use in the DECtape controls and consist of an input/output buffer and shift register combination. Each package or module is capable of handling three bits. Refer to the print entitled information handling (IN). Note that the 550 Control is an 18-bit machine and six 4228 packages are required. Further, since there are three information chancels, two 4228 packages are wired to each channel. To write information on tape, data is accepted from the computer through information plug D2. It is strobed into the input/output buffer (IOB) with

an MMWR pulse or load pulse. This is tied to Pin Y, print location A1. The data in the IOB is then transferred to the shift register via a pulse labeled B - J - SR entering Pin W, print location B1. From here the data is shifted serially into the 4523 Write Amplifier. The shift pulses are either shift right or shift left, Pin Z and U respectively of the 4228, depending upon tape direction.

The data transfer from the input/output buffer to the shift register is a parallel transfer handled internally by the 4228 modules. To read information from the tape data is read by the head, amplified by the 4523 Read Amplifier, and assembled bit by bit by the shift register until six bits are assembled. The shift right and shift left pulses actually load the output of the reader into the shift registers. When six bits have been assembled, in each of the three information channels, a pulse labeled SR  $\rightarrow$  IOB transfers the information from the shift register into the input/output buffer. All 18 bits are then available to the computer via information plug D2. Note that the pulses B  $\rightarrow$  SR and SR  $\rightarrow$  IOB are one and the same pulse. Thus this single pulse has become known as an interchange pulse which does just that. It exchanges the data in the input/output buffer with the data in the shift register.

#### Operation of the Control in Search Modes

In search mode the control raises a data flag every time it passes over a block mark. Refer to print C2, location C4. A 1011 AND Gate is used to combine the search mode with a block mark track input to enable a CD gate. This CD gate is strobed at TP2 time and if enabled, pulses the input to a pulse amplifier located at B2. The output of this pulse amplifier is sent to the base input of an inverter located at B5. The output of this inverter then sets the DATA FLAG flip-flop, print location plug D1. The raise data flag pulse or RDF pulse is also sent to the pulse input of a CD gate input to the interchange PA located on PM print, print location A6. Thus whenever a block mark is found an interchange takes place which transfers the data from the shift register into the IOB. The data in this mode is the block number. As mentioned before the shift right and shift left pulses shift the data in the shift register to the right or to the left depending upon the direction of tape. However, in the search mode information is shifted right only. This may be seen by referring to print TM location B5. Two 4606 PA's are used for the shift right and shift left pulses. Pin N input to the shift right pulse amplifier comes from a 4127 CD Gate whose pulse input is TP1. The level input comes from a 1011 AND Gate whose

whose inputs consist of SEARCH and WRENB<sup>0</sup>. Thus, if in search mode and not writing, the shift register is shifted right at TP1.

This is the only mode in which shifting is not dependent upon the direction of tape. The reason for this is that the reverse block mark is written as the complement obverse. Therefore rearrangement of the bits is not necessary.

### Operation of the Control in Read Mode

In read mode the control raises a data flag for each 18-bit data word just assembled and transferred to the IOB or input/output buffer. Refer to location C4, print C2 entitled "flag response data control outputs." A 2-input AND gate whose inputs consist of read and RDA is used to enable a CD gate which is pulsed at TP2. The output of the CD gate pulses the raise data flag amplifier and the same sequence of events takes place as was described for the conditions of search. The RDA input to the 2-input AND gate originates from the 4261 module shown on Print W entitled "mark track decoding error" at location A5. The RDA output is formed by the jumpering of Pins S and W thus referring also to print TD or timing diagram. Note that the RDA flags consist of the reverse check flag, the last two block start flags, all the data flags, the prefinal flag, and the final flag.

The first 18-bit data word transferred in this mode is the reverse check word. This word is combined by the computer with the rest of the data and the check sum word at the end of the block to determine if the data transfer was done correctly. The check word is the last word transferred when reading a block. Since the block length could be variable, it is necessary to indicate to the computer when the last word is read. This is accomplished by raising what is known as a block flag. Refer once again to print C2, location C5. A 2-input AND gate whose inputs consist of both READ and CHECK enables a CD gate whose output strobes the raise block flag PA at TP2. The block flag pulse amplifier is located at B1. The output of this PA enters the base of an inverter located at B6. This inverter in turn sets the BLOCK FLAG flip-flop located at B4 to a 1. The output of the block flag then is inverted and made available to the computer through a control plug D1. Thus, in read mode the check flag signals the computer that the end of the block has been reached and that the data should be checked for errors. Refer to Print TM, location A6. Note that interchange pulses occur each time the data flag or a block flag is raised.