# COGAR SYSTEM 4°

### SYSTEM SUMMARY

# Table of Contents

| System Applications      |

|--------------------------|

| Software                 |

| System Modularity        |

| External Interfaces      |

| System Organization      |

| Processor Architecture   |

| Processor Hardware       |

| The Memory               |

| Instruction Set          |

| Programming the System 4 |

| Application Packages     |

| Programmer's Utilities   |

| Peripherals              |

| Specification Summary    |

Page

i

### Designed

for users who require a total and daily commitment from their Data Processing Equipment.

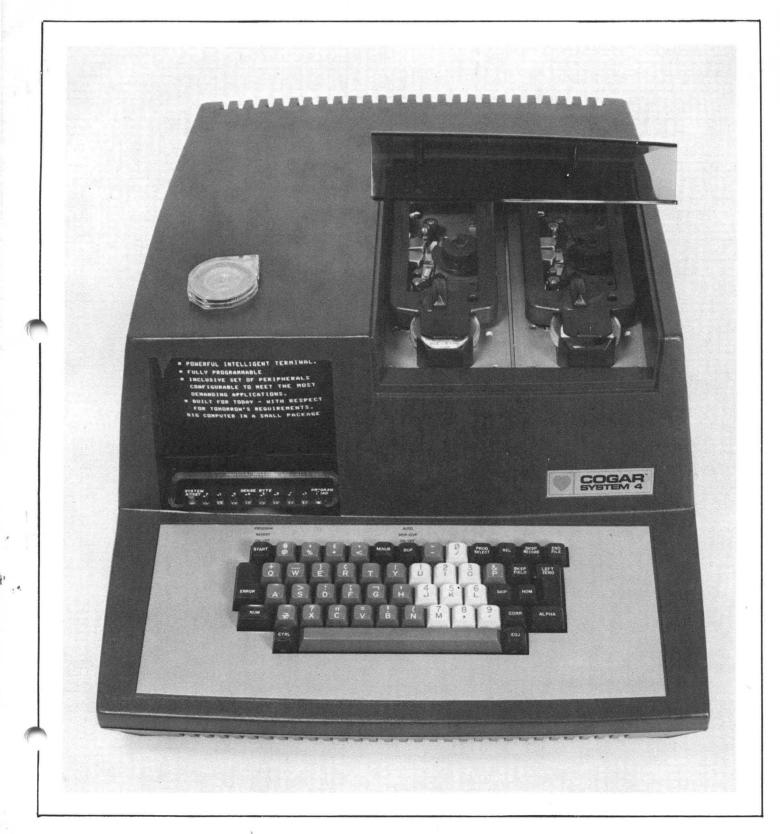

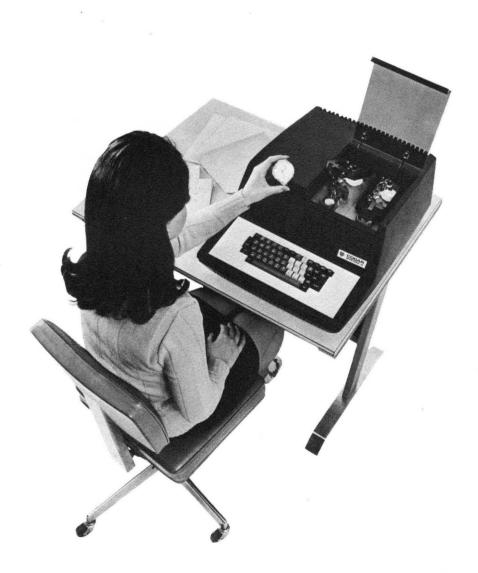

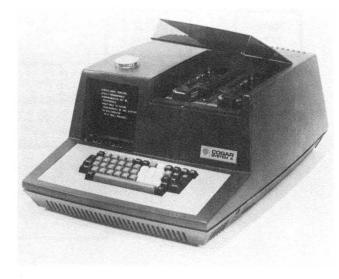

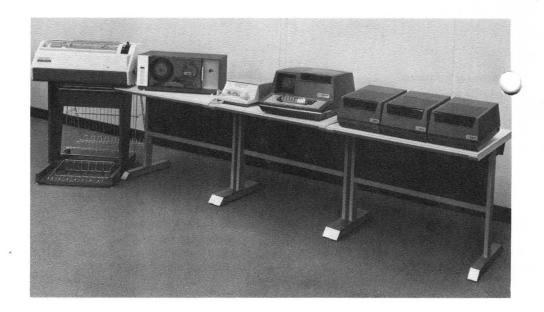

The Cogar System 4<sup>®</sup> is a compact, operator oriented, general purpose data processing system. In a single desk-top unit, it combines magnetic tape transports, input keyboard, visual CRT display, I/O interfaces, solid state memory and a versatile processor.

The System 4 features transparency of coding and graphics, with all major functions under processor program control. Both the hardware and the software are designed to allow and assist operator interaction, while retaining sophisticated data manipulation capabilities.

The processor architecture is designed to optimize byte handling and interpretation, and to provide automatic threading of recursive subroutines. Designed specifically for the efficient processing of graphics data, it incorporates a high performance byte-oriented processor, and a flexible, modularly expandable I/O system.

The application flexibility of the System 4 makes it a suitable building block in every type of installation, including data entry systems, communications terminals, small programmable processors, off-line printing stations, multifunction data stations, or as a full standalone EDP installation with complete peripheral complement.

The esthetic design of the System 4 is in complete accord with any office environment. It is simple for even the most unskilled operator to use. The use of the display to provide conversational interaction with the operator obviates the requirement for extensive training and allows the operator to be immediately at ease with the equipment.

1

# System Applications

Applications range from conventional data entry to a full stand-alone data processing system capable of meeting the requirements of small and medium size installations. However, the System 4 is designed to grow right along with future application requirements. The easy-to-use instruction language allows the user to program it to perform new or specialized functions for unique applications. The system's design flexibility, technology, and simplicity ensure its staying power as a cost-effective tool.

DATA ENTRY APPLICATION

#### **Data Entry**

As a data entry device, the Cogar System 4 provides all the conventional features usually found in a data entry environment, plus the convenience and flexibility of operator interaction with the machine by providing a CRT display at every key station. A software system specifically designed for high-volume, validated data entry and verification is contained on a self-loading program tape. Three levels of program formatting are available, which may be interchangeably selected by the operator without reloading the program tape.

All keypunch functions, as well as all key-to-tape functions are standard. Functions like automatic skipping and duplicating, field balancing, automatic program selection, automatic formatting, sight or key verification, editing, blocking, and record searching.

Extremely reliable data storage, combined with powerful off-line data editing and validating capabilities result in virtual elimination of errors while the data is being keyed. A complete set of interlocks insure that the machine is prepared to accept the data before the operator can begin the keying-in process, thus eliminating procedural errors.

### **Programming Tool**

The Cogar System 4 provides the program designer with a unique software tool which allows program design and debugging to be carried out interactively The standard programming language of the System 4 functions at several different interlocking levels and may be used in whatever mode best suits the programmer or the application. Programs may be created in Object language or in Symbolic language, using only the System 4 processor. The program may then be examined visually, individual instructions may be modified, or entire sections or subroutines within the program may be rearranged. The machine thus allows the programmer the option of fragmenting and restructuring his program without intervening action by peripheral assemblers or other equipments. This capability provides unprecedented flexibility and economy in the performance of program editing and debugging, as well as providing the ability to utilize existing subroutines in a program which is being newlygenerated.

### **Remote Terminal**

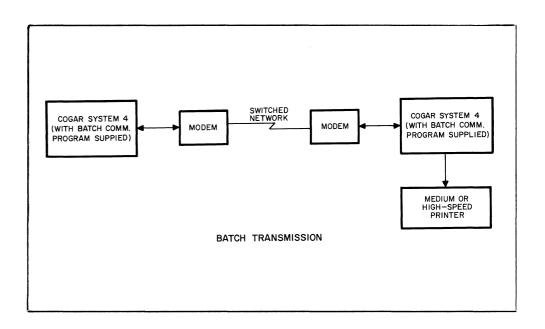

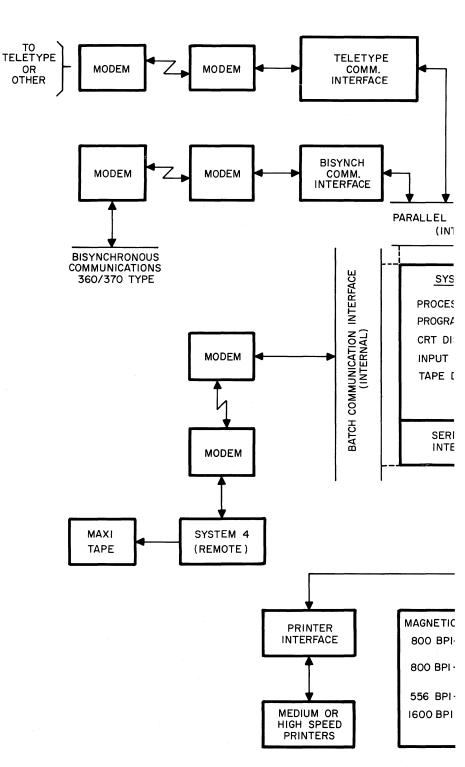

With its communications option, the Cogar System 4 becomes an intelligent remote terminal. The processor's ability to handle editing, formatting, communication, calculation, control and decoding duties can mean considerable savings in central computer and communication line time. Varieties of communication options include: Batch Transmission, Bisynchronous Communications, Teletype Simulation and System 4 to Systems 360/370.

Using Batch Transmission, records and messages may be transferred from System 4 to System 4 over switched networks. The grade of the transmission line is continually sampled by the program and the transmission speed adjusted accordingly in the range of 1200 to 1800 baud. The package provides for full error detection, operator alert, and error recovery.

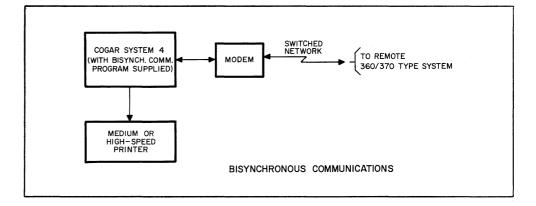

Using Bisynchronous Communications, the System 4 transfers data and messages over switched networks to a large computing system. Communication is in a high-speed, synchronous mode at transmission rates of 2000, 2400, and 4800 baud. Operator intervention during transmission, automatic answer, error detection and recovery are included.

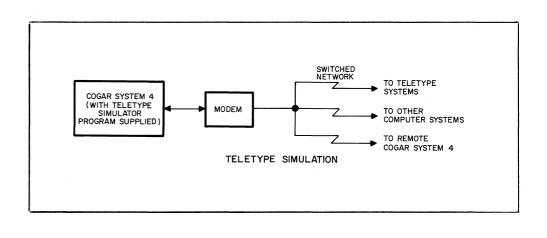

In the Teletype Simulation mode, the System 4 can be dialed into any computer supporting remote teletypes (including another System 4), for exchange of data. Transmission over switched networks is at a speed of up to 60 characters per second.

#### System Controller

The System 4 offers an integrated operator interface as well as a versatile processor, so that implementation of larger special purpose systems using the System 4 as a controller can offer special advantages. Programmable component and logic testers are excellent examples of such applications.

### Education

The Cogar System 4, because it contains all the basic elements of a complete data processing system, makes an excellent teaching aid for computer concepts. It also can provide a good hands-on introduction to various programming languages.

### Software

The Cogar System 4 is provided with fully supported software to make is immediately available for use in a variety of tasks. Pre-packaged programs provided by Cogar are stored on cartridge tapes and loaded into the machine as required by the user to perform specific functions. Master Function tapes are also provided, to allow the user to generate a custom-made program which may then be executed on the System 4 to perform tasks which are unique to the user's requirements. The Cogar software provides for interactive program design and debugging at several levels, including machine language.

The "Program Summary Catalog" which is available from the Cogar Software Distribution Center, gives a complete listing of the programs which are currently available, and a brief description of each. Detailed descriptions of the use of each program are also available from the Software Distribution Center.

### **Software Features**

- Completely programmable

- Self-contained operating system

- Remote and local data communications

- Multiple language levels

- Byte-oriented processor

- Program interrupts

- Subroutine relocatability

- Extensive subroutine library

#### Software Packages

Basic Assembler Background Libraries Diagnostic Libraries

Data Entry Data Verify Tape Search 9 or 7 track computer compatible Editor

Program Trace Utility Cogar Batch Communications Bisynchronous Communication

Teletype Simulator Sort/Merge Package Dot Pattern Converter

High Speed Record Search General Ledger Print Gang Punch, and others.

All software packages are operable on a 4K byte system.

4

### System Modularity

The superior reliability of the System 4 is the result of a modular packaging concept that eliminates internal wiring and complex interconnections that are the major cause of failures. Maintenance of any of the major components is simple. Four bolts are all that are required to remove and replace every major component. Each major sub-assembly is a functional entity permitting simple and rapid fault diagnosis and replacement. Cogar provides their customers a full capability in technical and systems support including training in field engineering and systems programming. Additionally, Cogar provides base level spare parts depots and repair services.

Product designs are implemented to provide for functional sub-assemblies which permit simple fault diagnosis and replacement. Functional sub-assemblies also permit more extensive in-process quality checks, enhancing the overall integrity and reliability of the total system. The packaging utilizes high-density, multi-layered printed circuit boards, minimizing the number of manually implemented interconnects. The casework and internal chassis are molded of lightweight, impact-resistant plastic, vacuum coated with metal to provide maximum safeguard against electrical interferences.

### **External Interfaces**

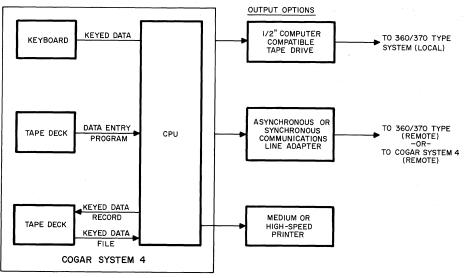

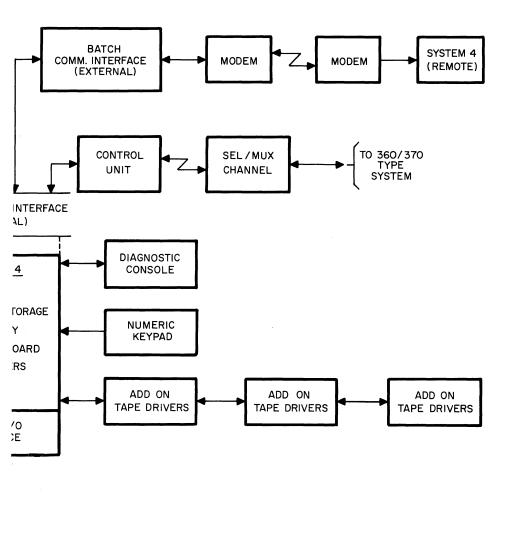

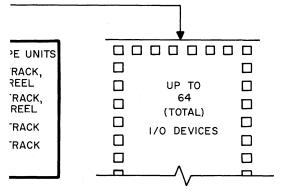

The Cogar System 4 includes provision for three I/O interfaces. Included as a standard feature, a Serial I/O interface utilizing a single coaxial cable is connectable to up to 64 individual I/O devices. Data transfer on the cable is bidirectional. allowing one line to handle all activity. The use of high frequency, phase encoded techniques and address polling provides for system economy and flexibility without compromising reliability and thruput. The System 4 can transfer information to or from any one of the 64 peripheral devices at a rate of 58.8 kilobytes per second, in bit serial format. A wide variety of system configurations is easily realized. The use of a single coaxial cable permits reliable and economical attachment of peripheral devices through the Serial I/O Interface at distances of up to 1500 feet. In a system configuration where multiple System 4's are attached to the Serial I/O Interface through the coaxial cable, along with other I/O devices such as printers and computer-compatible tape drives, each System 4 may communicate with any other I/O device, under program control.

The Cogar peripherals designed to connect to the Serial I/O include:

• Magnetic Tape Units

800 BPI, 9 Track, 7" Reel 800 BPI, 9 Track, 10" Reel 556 BPI, 7 Track 1600 BPI, 9 Track

- Universal Printer Adapter

- Medium or High-Speed Printer IBM 735 Centronics

- Additional System 4s

Additionally, the System 4 has the ability to accommodate up to four peripheral devices via a Parallel I/O channel, which can be operated by software concurrent with the activities of the Serial I/O channel. This optional communications interface connects to standard telephone datasets. The transmission rate is program selectable from 1200 to 2400 baud, and may be dynamically varied in response to communications line error rates. Communications to or from a local 360/370 system is accomplished through the multiplex channel link, or through the bisynchronous channel link for remote 360/370 communications.

The System also has an inherent provision for direct memory access, permitting transfer rates of up to one million bytes per second. This feature provides for multi-processor configurations with direct memory-to-memory interchange.

The flexibility of the system allows the user to add compatible peripherals and interfaces at will, without disrupting the processor configuration, and seldom any down-time in normal work activity.

System 4 to System 4 communications may be accomplished through the coaxial line of the Serial I/O channel, or through the Batch Transmission interface, for remote installation communications. The Batch Communications interface may be installed internally to the System 4, or may be installed in its external adapter enclosure.

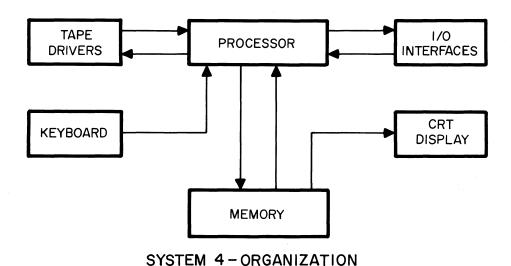

# System Organization

The Cogar System 4 is a self-contained data processing system. In its minimal configuration, it completely satisfies the requirements of a data capture system. As a media conversion device, any character which can be formed by a 5X8 matrix may be generated, without a change in the hardware. Performing as an intelligent terminal, it incorporates a high performance byte-oriented processor, along with flexibility in a modularly expandable I/O system.

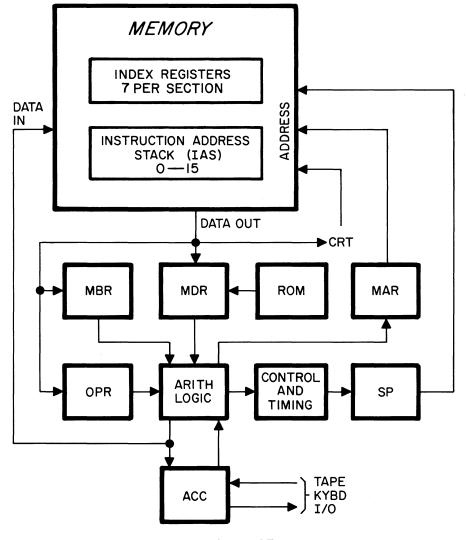

The program controlled CRT display has direct access to memory. The key-

board, the tape drives, and the I/O interfaces gain access to memory through the processor. Interaction between the System 4 and the operator is accomplished through the display and the keyboard; therefore, no control panel is required. The two tape drives are used to enter and receive processor data and program material. The I/O interfaces provide bidirectional data paths for external peripheral devices, including special customer attachments. All major system functions are under the direct control of the processor program.

#### **System Options**

In addition to the optional external peripheral devices which may be attached to the Cogar System 4, the following internal options may be specified. All of these options are factory installable only, and are configured within the standard System 4 package.

- Parallel I/O Interface

- Sense Switches

- 8K Byte Memory

- 16K Byte Memory

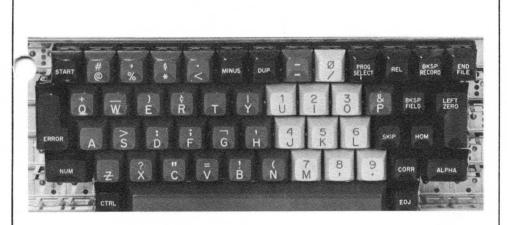

### Keyboard

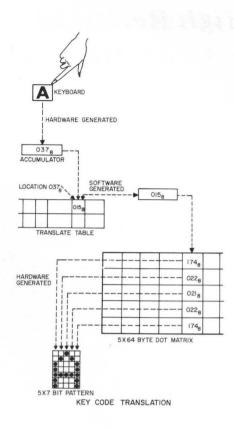

Many of the System 4 functions have been designed to be operated under pron control, in order to facilitate the customizing of the system to particular user applications. The codes generated from the keyboard for example, correspond to the physical location of the key, rather than to the character shown on the key. A translate table located in the processor memory is used to convert the key location code to the dot pattern for the character to be displayed. The translate table is completely programmable. and thus may be easily modified to produce any desired character configuration for any key location. This allows easy adaptation to particular keyboard configurations such as keypunch, typewriter, or teletype.

The system contains an inherent provision for N-key rollover, and the software provides for the formation of a keyboard queue, allowing keyboard input to be totally independent of other concurrent system operations. An acoustic transducer is included that may be set to sound a tone with every keystroke, or for silent keying, at the preference of the operator.

The illustration on this page shows the correlation of the key codes to the position of the keys. Actual data code assignment for each key is accomplished by table look-up techniques within the controlling software. For example, if the key for an "A" is depressed, an eight-bit octal code for  $\emptyset$ 37 is generated. Location  $\emptyset$ 37 (in the standard translate table) contains octal  $\emptyset$ 15, which is the address of the character dot pattern for "A". This address is stored in an appropriate display buffer in memory, and is accessed each time that character is to be displayed.

### KEYPUNCH KEYBOARD

| 01  | 01 | 10<br>00 |   | 065                                                                                                                                                                                       |              | 104        |            | 105<br>005 |            | 006 | 00         | )7     | 01        | 0        | 11<br>01   |          | 01         | 2        | 01  | 3  | 0   | 14 | 015 |

|-----|----|----------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|------------|------------|------------|-----|------------|--------|-----------|----------|------------|----------|------------|----------|-----|----|-----|----|-----|

|     | 11 | 16<br>16 |   | 17<br>17                                                                                                                                                                                  | 1 20<br>0 20 |            | 121<br>021 |            | 022        |     | 23<br>23   | 1<br>0 | 24<br>24  | 12<br>02 |            | 12<br>02 | 26<br>26   | 12<br>02 |     | 03 | 0   |    | )31 |

| 032 |    | 03       | 7 | 140<br>040                                                                                                                                                                                |              | 141<br>)41 | 14<br>04   |            | 143<br>043 |     | 144<br>044 |        | 45<br>)45 |          | 146<br>046 |          | 147<br>047 |          | 050 | 1  | 051 |    |     |

| 053 |    |          | 3 | 156         160         161         162         163         164         165         166           056         060         061         062         063         064         065         066 |              |            |            |            |            |     |            | 067    |           |          |            |          |            |          |     |    |     |    |     |

|     |    |          |   |                                                                                                                                                                                           | 070          |            |            |            |            |     |            |        |           | 071      |            |          |            |          |     |    |     |    |     |

|     |    |          |   |                                                                                                                                                                                           |              | 1          | KE         | YB         | DA         | RD  | к          | Έì     | ' (       | 0        | DE         | ES       |            |          |     |    |     |    |     |

### Visual Display

The visual display forms the primary channel of information from the processor to the operator. It consists of a 5 inch CRT, with its associated video electronics and addressing logic. Up to 256 characters may be displayed on the screen in 8 lines of 32 characters each. A 5 x 8 dot pattern may be displayed in each character position. The processor memory stores the dot pattern for each character type, and the screen is refreshed directly from the memory. With the display functions (including underline capability) under processor control, a programmer can directly manipulate not only the dot patterns available for display, but also which character code is associated with each pattern. The display has direct memory access with specifically assigned time slots to preclude impact on instruction execution times. Memory areas displayed are program selectable from any one of 16 memory pages (256 bytes per page), with provision for selective interlace of half pages. Provisions are included for cursor or underscore with selective blanking and an alternate graphic set which permits utilization of 128 unique graphics.

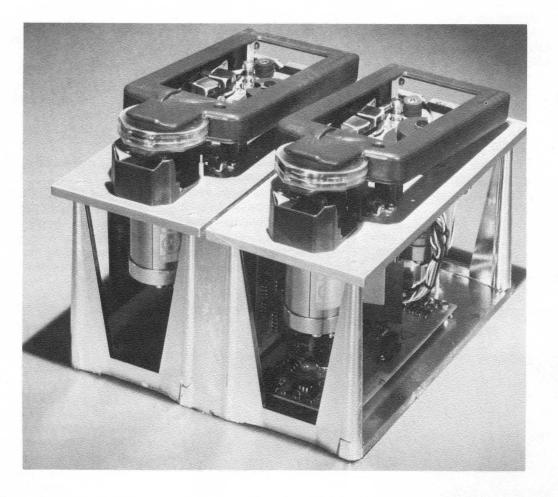

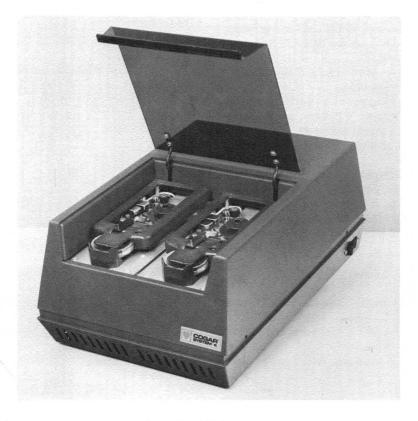

# High Reliability High Performance Tape Drives

- Servo controlled capstan drive, providing precise control of tape acceleration and deceleration, thus, insuring long tape life.

- Reel-to-reel tape control with independently controlled tension drives.

- Precision tape guiding, independent of cartridge characteristics and precluding contact with the oxide side of the tape.

- Snap-in load and automatic threading.

- Bidirectional read with peak transfer rate of 2000 bytes per second. High speed record search feature.

- Full interlocks to insure against operator error:

- a. File protection sensing.

- b. Cartridge in place.

- c. Cartridge in use interlock.

- d. Tape rewound, providing for rewind with or without interlock.

- e. End of tape detection.

- High density, self-clocking write and read recovery, providing maximum reliability and guarantee of drive-to-drive compatibility plus the inherent selfchecking afforded by phase modulation recording.

- Full read after write check.

- In addition to the inherent advantages of a self-clocking read system, the Cogar Tape System is further complemented by the automatic compensation for apparent speed changes which can occur from physical changes to the tape itself.

- System expandability up to eight cartridge drives can be configured with a single System 4, permitting high performance sort and file merge operations.

The Cogar System 4 contains a unique tape system, developed by Cogar, which combines the convenience and simplicity of a "snap in" self-loading cartridge with the standards of reliability and guaranteed data integrity attainable by the most advanced of the industry compatible tape drives. Utilizing the same basic design principles proven in the designs of industry compatible tape drives, the system consists of two mechanically independent tape transports, which are functionally identical and utilize an exclusive Cogar tape cartridge. The cartridge houses a reel containing 100 feet of computer grade, one mil polyester magnetic tape 150 mils wide. The cartridges are provided with a write-enable pin, to preclude erasing or writing on the tape, except when the pin is in the write-enable position. An inner reel functions independently of the outer cartridge, thus providing a true reel-toreel tape handling mechanism. Tape threading is accomplished automatically through the use of a leader system connected to the takeup reel. The transports contain sensors to detect three tape status conditions: the presence of a cartridge properly loaded, tape not fully rewound, and end of tape. Mechanical interlocks are included to prevent cartridge removal, except when the tape is fully rewound into the reel; and to prevent tape motion, unless the cartridge is properly seated in its holder.

A write pin sensor in the C4 requires that if a tape is to be written on, the write enable pin plug must be in the proper position. Otherwise, tape will not move and no operation can be performed on that deck until a cartridge is inserted with the write pin in place.

Tape formatting, read forward/backward, and read/write checking is under processor control. Record size, interrecord gaps, check data and number of retrys are variable as functions of software. This allows the tape system to be optimized by program control, for particular user applications. The tape parameters contained in the standard Cogar software systems provide for a nominal 900 records of 136 bytes each per cartridge. Recording density is 1600 bits per inch, phase encoded on a single track. The write track width is 80 mils, and the read width is 50 mils. The tape recovery system utilizes an energy averaging technique to determine the presence or absence of data, thus effecting an essentially infinite gain data recovery system.

Read/Write tape speed is 10 inches per second, as determined by a servocontrolled capstan which maintains a very close tape speed tolerance and allows maximum recording density. As a means of further enlarging the allowable cumulative tolerances within the tape system, the read electronics employs a servoed recovery clock, capable of tracking both intermediate and long term time displacement variations in the recovered data.

The tape transports also provide a high speed mode of 40 inches per second, that is utilized during rewind and bidirectional searches. The energy averaging detectors are used to count records for high speed searching.

The tape logic contains the hardware to allow reading backward without requiring the software to invert and shift the data. The only requirement is that a data block must be ended by a reverse read start pattern consisting of a 001 byte followed by two bytes of 000.

The tape logic also contains an 8-bit buffer that will hold a character on queue for 512 microseconds, allowing that much time for data processing before releasing the character.

### **Processor** Architecture

The processor contained within the Cogar System 4 is fully general purpose, with a repertoire of more than 45 instructions. In addition to the conventional arithmetic and logical instructions, there is a class of powerful branch instructions that facilitate byte manipulation and sub-routine linkage. The processor design is highly memory oriented and all processor activity is memory dependent. The memory used in the Cogar System 4 is a monolithic semi-conductor memory.

### **Processor Cycle**

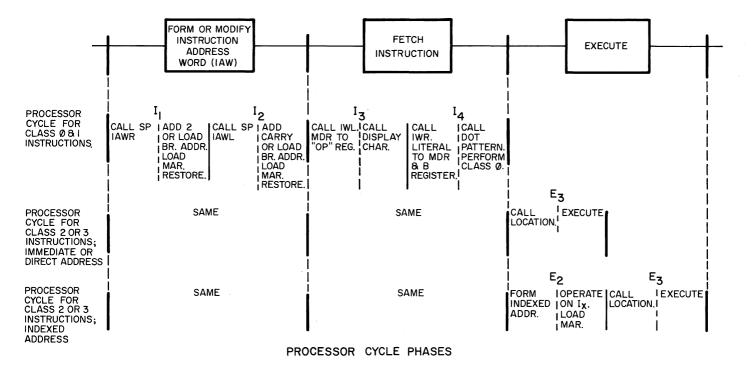

One cycle of processor operation is divided into a maximum of 6 processor subcycles (phases) that are labeled  $I_1$ ,  $I_2$ ,  $I_3$ ,  $I_4$ ,  $E_2$ ,  $E_3$ . Each phase is one microsecond long.

$I_1$  through  $I_4$  are the instruction phases of the processor and all four are required for every machine cycle. During  $I_1$  and  $I_2$  phases the address of the last instruction is retrieved from an Instruction Address Work (IAW) located in Memory. During  $I_3$  and  $I_4$  phases the current instruction is extracted from memory and decoded.

$E_2$  and  $E_3$  are the execution phases of the processor. The E phases are conditional, based on the specific instruction being executed. Byte transfer instructions skip  $E_2$ . Branch and I/O instructions skip all E phases.

Phases  $I_3$  and  $I_4$  are also the display phases of the processor. One phase will locate the character to be displayed on the basis of the CRT beam position. The succeeding phase will call a segment of a dot pattern corresponding to that character and the current horizontal position of the CRT beam. The display is scanned vertically, and has access to one byte segment of dot pattern data for each character position it passes through. Seven of the eight bits of the byte contain the vertical portion of the 5x8 matrix. The specific display buffer area is presettable under program control. Any page (8 line display) or sub-page (4 line display) within the first 4 pages of Sections 0-3 of memory may be displayed.

Many of the registers used by the processor are "soft" registers and buffers located in memory. The keyboard translation table is in memory, as are the display dot matrix and the display character buffer; as well as several utility subroutines for tape and I/O control. There are seven Index Registers (IX), per 2K section of memory, of one byte each, occupying memory locations 001 through 007 of each section, that may be used for indexed addressing or as general registers. There are 16 Instruction Address Words of two bytes each, in memory that are addressed by the hardware Stack Pointer.

### **Processor Hardware**

Initial program load (bootstrap) is accomplished by an 8 instruction subroutine contained in a Read Only Memory (ROM). The addressing of this Read Only Memory is congruent with main memory addresses  $400_8$  through  $417_8$  during power-on sequencing or activating the program load switch. Execution of the first stack instruction resets the bootstrap mode and returns control to main memory addressing. A switch initiated program restart causes an automatic branch to location  $1000_8$ .

The Memory Data Register (MDR) is one byte long and is used to hold data during the formation of an effective address and during arithmetic and logical operations. The Memory Buffer Register (MBR) is one byte long and is used to hold the offset value for jump instructions, the literal value for indexing arithmetic operations and in the formation of indexed addresses. The Operation Register (OPR) receives and decodes the operand byte during phase  $I_3$ including the address of the index register to be used (if any) or the accumulator shift count. The Memory Address Register (MAR) is 14 bits long, allowing indexed addressing of up to 16K bytes of memory.

The arithmetic and logic section of the processor executes all arithmetic, logic and compare instructions, including the overhead operations such as incrementing the index registers and the instruction address words. The accumulator is one byte long, and is the object of all arithmetic and logic operations, except those performed on index registers. The accumulator serves as the data interface for all external processor activity, except CRT refresh. The stack pointer is a 4 bit hardware counter that addresses the instruction address stack in memory.

When the processor is waiting for input (from the keyboard, for example), it enters the "stall mode." In this condition the arithmetic logic is inhibited, so that the IAW does not get incremented. In this way the processor continues to cycle, so that the display can function, no program progress is made.

SYSTEM 4 PROCESSOR

### Memory

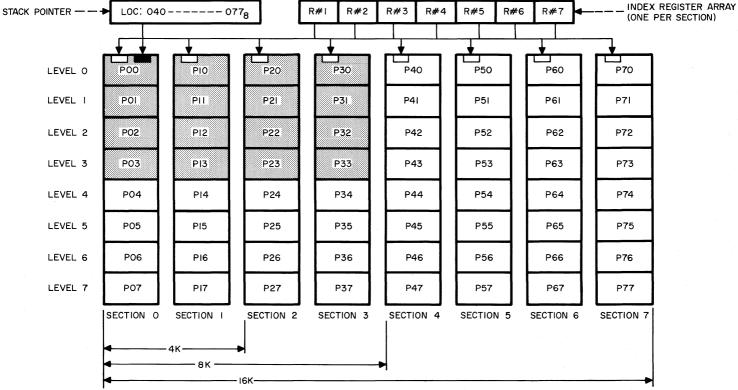

The standard Cogar System 4 is equipped with 4K bytes of monolithic memory, expandable to 8K or 16K bytes. The memory provides processor storage, display refresh, and data buffers and registers.

The memory is divided into eight Sections, each containing 2K bytes. Each Section contains eight pages, of 256 bytes each.

The Instruction Address Stack (IAS) occupies memory locations  $040_8$  through  $077_8$ . Access to the stack is under control of the hardware Stack Pointer (SP) which functions modulo  $10_8$ . The SP is incremented upon execution of a stack and branch instruction, and decremented upon execution of an exit instruction.

The current value of SP may be determined by program which facilitates the linkage of data between relocatable subroutines. By convention the linkage data would occupy contiguous locations following the last executed stack and branch instruction.

\* SHADED AREA DISPLAYABLE PAGES

SYSTEM 4 MEMORY MAP

### **Instruction Set**

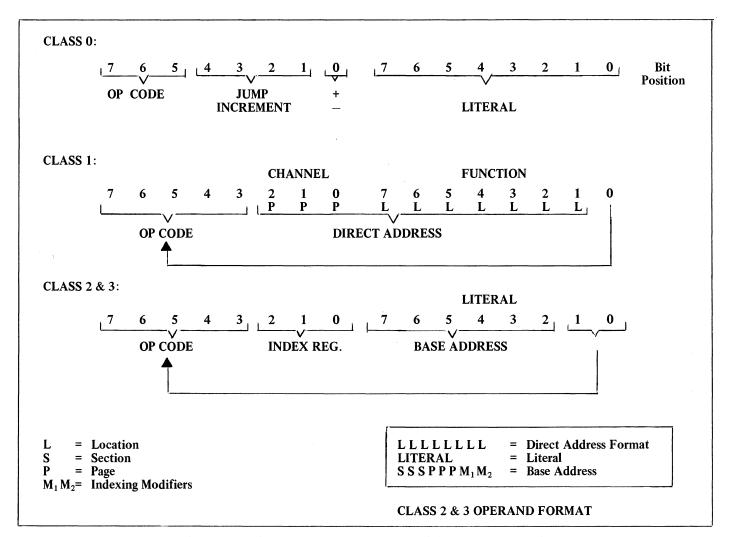

There are four general classes of instructions utilized in the Cogar System 4. They cover all the types of actions required from a general purpose processor. Instruction formats are shown below.

- Class 0: Jump Instructions

- Class 1: Branch and I/O Instructions

- Class 2: Transfer and Arithmetic

- Instructions

- Class 3: Boolean and Compare Instructions

The Cogar System 4 can contain a maximum of 16K bytes of memory, requiring an instruction address word (IAW) of 14 bits. This memory capacity is divided in 8 sections of 2K bytes each. The sections are further divided into 8 pages of 256 bytes each. All Cogar System 4 operations require addressing of instructions or data, and each mode has several types of addressing that apply to it.

### **Instruction Addressing**

Instructions may be executed sequentially, in which case one of the 16 instruction address words within the instruction address stack is incremented during phases  $I_1$  and  $I_2$  of each instruction cycle.

A Jump to a new instruction location uses relative addressing by  $\pm$  30 locations with respect to the current instruction.

Direct branching may be within a page or within a section, depending on the controls set by the program. In the one case only the least significant 8 bits of the IAW are changed and in the second case the least significant 11 bits are changed.

For addressing outside a Section, a set section instruction is executed. This operation changes the three bits in the IAW which designated the Section.

### Data Addressing

Information may be addressed by an instruction in three modes. Immediate addressing mode assumes the instruction itself is the desired location and uses the data carried in the instruction directly.

The direct addressing mode uses the data carried in the instruction as the address of a desired memory location.

Indexed Addressing mode combines the data carried in the instruction with the contents of a specified index register to produce the address of a desired memory location. This allows addressing of a field range of 16K memory locations.

# Instruction Set

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            | ·                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CODE                                                                                                                       | INSTRUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Class 0: Jump Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TLJ<br>TMJ                                                                                                                 | Test Literal and Jump                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Jump instructions transfer control within a context to a location that is relative to the current instruction location. All jump instructions are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TMJ<br>TLX                                                                                                                 | Test Mask and Jump<br>Test Literal and Exit                                                                                                                                                                                                                                                                                                                                                                                                |

| conditional and depend on the result of a test of the contents of the accumulator. The test comparison, the test mask, the jump direction and the jump increment may all be specified in the instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TMX                                                                                                                        | Test Mask and Exit                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Class 1: Branch and I/O Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Branch instructions transfer control outside a context to any direct address location. Direct branch instructions may be conditioned by previous compare operations. Stack and branch instructions are used to access subroutines and may be conditioned by previous compare operations. When executed, the stack and branch instruction increments the stack pointer and stores the target instruction address into the instruction address stack. The exit and the exit and branch instructions are used to return from subroutines. When executed, they decrement the stack pointer, thus changing program control to the next previous IAW. Hardware controls that are set by instructions allow branch instructions that alter only the 8 low order bits of the instruction address. This provides the capability to create page oriented subroutines that may be moved to any page of memory desired. The I/O, set section and load processor status instructions are also part of this class. They include control, status and data exchange between the processor and its interface devices. Tape channels may be selected, tape motions initiated, and read or write commanded; the keyboard may be read, or clicked; the CRT may be enabled or disabled; the I/O interface transmission may be started or stopped, and data or control bytes written. Several status checks are available for the processor to interrogate. | BRU<br>BRE<br>BRH<br>BRL<br>SBU<br>SBE<br>SBH<br>SBL<br>EXB<br>EXU<br>SMS<br>SMC<br>SSC<br>SAC<br>LSW<br>LPS<br>DPI<br>EPI | Branch Unconditional<br>Branch on Equal<br>Branch on High<br>Branch on Low<br>Stack and Branch Unconditional<br>Stack and Branch on Equal<br>Stack and Branch on Equal<br>Stack and Branch on Low<br>Exit and Branch on Low<br>Exit unconditional<br>Set Memory Section<br>Set Memory Section<br>Set Memory Section and Control<br>Set Arithmetic Condition<br>Load Sense Switches<br>Load Processor Status<br>Disable Processor Interrupt |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | СРІ                                                                                                                        | Clear Processor Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Class 2: Transfer and Arithmetic Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| This class of instructions includes the load and store operations that allow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | LDA                                                                                                                        | Load Accumulator                                                                                                                                                                                                                                                                                                                                                                                                                           |

| data to be moved between memory and the accumulator, or the index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | LDX                                                                                                                        | Load Index Register                                                                                                                                                                                                                                                                                                                                                                                                                        |

| registers. These instructions use immediate, direct or indexed addressing modes. When loading or storing through indexed addressing, the index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | LIA                                                                                                                        | Load Instruction Address                                                                                                                                                                                                                                                                                                                                                                                                                   |

| register used may be automatically incremented or decremented. The IWR of<br>this instruction class may be specified as the direct address (referring to the<br>low order page of a section), or as the base address (specifying one of 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | STA                                                                                                                        | Store Accumulator                                                                                                                                                                                                                                                                                                                                                                                                                          |

| pages for indexed addresses), or as a literal for loading the accumulator or the index registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ADA                                                                                                                        | Add to Accumulator                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ADX                                                                                                                        | Add to Index Register                                                                                                                                                                                                                                                                                                                                                                                                                      |

| The arithmetic instructions in this class include add and subtract<br>operations on the accumulator or the index registers. Literal, direct or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SUA                                                                                                                        | Subtract from Accumulator                                                                                                                                                                                                                                                                                                                                                                                                                  |

| indexed addressing may be used. Automatic increment or decrement of index<br>registers may be specified when using indexed address. All operations are<br>available for use with the accumulator. Some operations may also be<br>performed on index registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SUX                                                                                                                        | Subtract from Index Register                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## Instruction Set

|                                                                                                                                                                                                       | CODE | INSTRUCTION                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------|

| Class 3: Boolean and Compare Instructions                                                                                                                                                             |      |                                     |

| The Boolean instructions in this class include immediate, direct or indexed                                                                                                                           | ANA  | Logical AND to Accumulator          |

| addressing of And, inclusive Or and exclusive Or operations. The literal                                                                                                                              | SAN  | Shift & logical AND to Accumulator  |

| instructions allow for up to seven right circular shifts of the accumulator prior to the execution of the literal.                                                                                    | ERA  | Exclusive OR to Accumulator         |

|                                                                                                                                                                                                       | SER  | Shift & Exclusive OR to Accumulator |

| The compare class of instructions compares the contents of the accumula-                                                                                                                              | IRA  | Inclusive OR to Accumulator         |

| tor with a location specified by immediate, direct or indexed addressing. Any<br>index register may be compared with a literal. The comparison results may be<br>tested in any following instruction. | SIR  | Shift & Exclusive OR to Accumulator |

| tostou in my fonowing instruction.                                                                                                                                                                    | СРА  | Compare Accumulator                 |

| Automatic increment or decrement of an index register may be specified when using indexed addressing.                                                                                                 | СРХ  | Compare Index Register              |

|                                                                                                                                                                                                       |      |                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | GET<br>PUT                               | <b>Group I</b><br>Get Data (Read)<br>Put Data (Write)                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Group Instructions<br>This group of instructions allow complex functions to be performed by<br>the System 4, using only a few Macro instructions. The important difference<br>between these groups and the Class 0 through 3 instructions is that the Class<br>instructions are directly executable by the processor, whereas the Group<br>instructions must be interpreted and operated upon by a supervisory routine                                                                                                                                                                                                                          | MOV<br>ADD<br>SUB<br>MUL<br>DIV          | Group II<br>Move Storage to Storage<br>Add Storage to Storage<br>Subtract Storage to Storage<br>Multiply<br>Divide |

| before actual execution.<br>However, since the Group type instruction is procedure-oriented rather<br>than machine-oriented, each instruction causes routines composed of relative-<br>ly large numbers of machine-language instructions to be executed. For<br>example, the Group 1 instruction GET; 128, T#1, 000 calls out a routine<br>which reads a string of characters from Tape Drive #1 and stores each<br>character in sequential memory locations beginning at location 000. This<br>routine is composed of approximately 75 machine instructions, and will<br>automatically loop on itself 128 times to satisfy the single command. | SEL;EQL<br>SEL;HGH<br>SEL;NHG<br>SEL;NEQ |                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TCL<br>PCL<br>SET                        | <b>Group IV</b><br>Tape Control Commands<br>Printer Control Commands<br>Set Page                                   |

# Programming the System 4

The language base for the Cogar System 4 is flexible, easy to learn and use, yet permits the programmer to take full advantage of the System 4's power. The Cogar Language Base is comprised of a comprehensive set of "Pre-packaged" functions to facilitate modular program construction. The Cogar Assembler provides linkage between these functions and the specialized routines necessary to a given application.

Programs are written and assembled in symbolic notation, with the final stage of the assembly effecting a merge of the specialized routines and the pre-packaged background functions. This method of assembly allows easy and rapid modification or correction of programs or the re-configuration of a program to accommodate different peripheral devices or the selection of a new or modified graphic set, or keyboard configuration.

All features of the Cogar Assembler are operable on a 4K System. Capitalizing on the high performance of the System 4 Tape Drives, an average program can be assembled in less than 12 minutes.

The packaged functions are available to the programmer from a Library Tape which provides for automatic retrieval and filing of specific functions. The library contains a standard set of subroutines for:

- Controlling the various peripherals

- Keyboard supervision

- Display graphics

- String oriented macros including signed arithmetic

- Communications

The programmer has complete freedom in the inter-mixing of machine language statements and macro-functions, with linkages provided by the assembler.

The sample subroutine shown above illustrates the ease with which a relatively complex function may be programmed,

| _ |                      |                  |   |          |       |       |                  | and the second |

|---|----------------------|------------------|---|----------|-------|-------|------------------|------------------------------------------------------------------------------------------------------------------|

|   |                      |                  |   |          |       |       |                  |                                                                                                                  |

|   | PPP-LLL:             | MP1-MP2-MP3-MP4. | Ε | SEQ.NO.  | LAB:  | VERB  | OPERANDS         | COMMENTS                                                                                                         |

|   |                      |                  |   | 01-010.  | RDD:  | EOU:  | P00, 009.        | READ DECK NUMBER                                                                                                 |