## Burroughs MEDIUM SYSTEMS B 3700/B 4700 CENTRAL PROCESSOR

**REFERENCE MANUAL**

COPYRIGHT © 1966, 1968, 1969, 1972 AA828689 AA995115 AA120798 **Burroughs Corporation** Detroit, Michigan 48232

\$2.00

#### TABLE OF CONTENTS

#### TITLE

| INTRODUCTION                         |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 1               |

|--------------------------------------|-----|-----|-----|----|---|---|---|-----|----|---|---|---|-----|-----|---|---|---|---|---|---|-----------------|

| System Description                   |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 1               |

| B 3700                               |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 1               |

| B 4700                               |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 1               |

| Variable Field Length Floating Point | (Op | tic | ona | l) |   | • | • |     |    |   |   | • | •   |     |   |   |   |   |   |   | 1               |

| B 3700/B 4700 System Configurations  |     |     |     |    |   |   |   |     |    |   |   |   | • • | • • |   |   |   |   |   |   | 1               |

| Data Representation                  |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 1               |

| Processor Instruction Format         |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | $\overline{7}$  |

| Operation Code                       |     |     |     |    |   |   |   |     |    |   |   |   |     |     | • |   |   |   |   |   | 7               |

| Variant Digits                       |     |     |     |    |   |   |   |     |    | • |   |   |     |     |   |   |   |   |   |   | 7               |

| AF, BF Variants                      |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 7               |

| Indirect Field Length                |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | $\frac{1}{7}$   |

| Literal                              |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 8               |

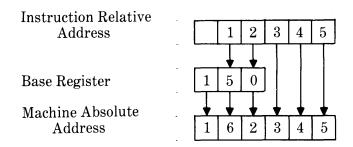

| Addresses                            |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 8               |

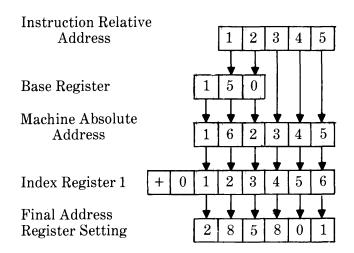

| Indexing                             |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 8               |

| Indirect Addressing                  |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 8               |

| Extended Address                     |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 9               |

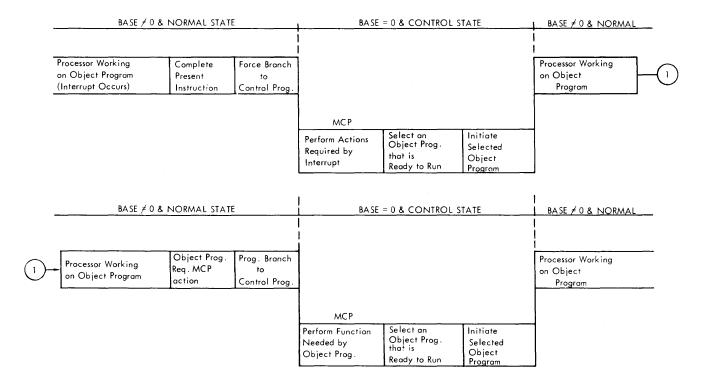

| Interrupts                           | • • | •   | •   | ·  | · | • | • | ••• | ·  | • | • | • | •   | ••• | • | • | • | • | · | • | 9<br>9          |

| Control State Interrupts             |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 9               |

| Normal State Interrupts              |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   |                 |

| Logical Units                        |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 10              |

|                                      |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 10              |

| Logic Section                        |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 10              |

| Comparison Flip-flops                | • • | •   | ·   | •  | · | · | · |     | •  | · | · | · | •   | ••• | · | • | • | · | • | · | 10              |

| Overflow Flip-flop                   |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 11              |

| Data Registers                       |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 11              |

| Bussing                              |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 12              |

| Arithmetic Section                   |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 12              |

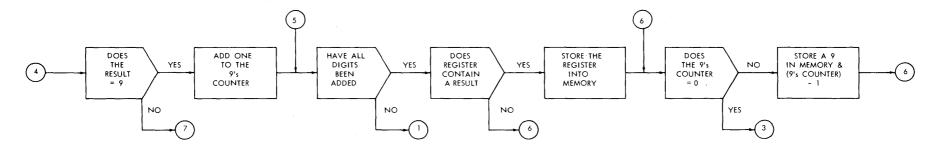

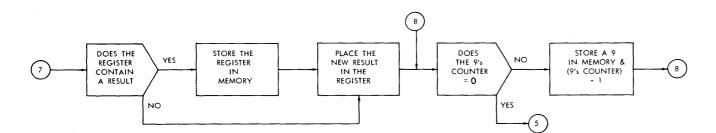

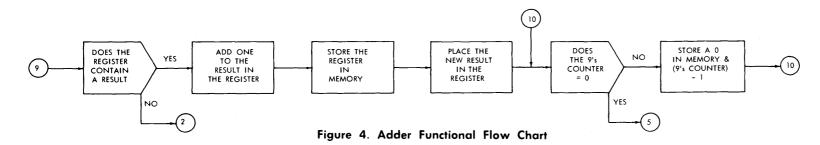

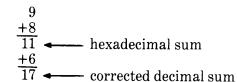

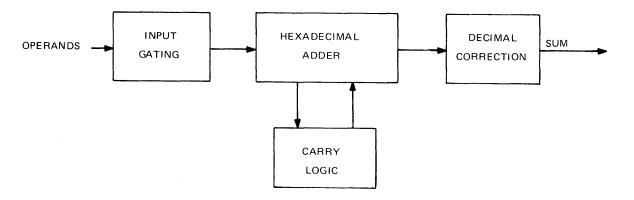

| Adder                                |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 12              |

| Floating Point Arithmetic            | ••• | •   | ·   | •  | · | • | • | ••• | •  | • | • | · | •   | ••• | • | • | • | • | • | • | 12              |

| Floating Point Adapter (Optional)    | ••• | •   | •   | •  | • | • | • |     | •  | ٠ | • | • | •   | • • | • | • | • | • | • | • | 14              |

| Fixed Length Arithmetic Unit .       | •   | •   | •   | •  | • | • | : |     | •  | • | • | • | •   | • • | • | • | • | • | • | • | 14              |

| Accumulator, Exponent Register       |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 14              |

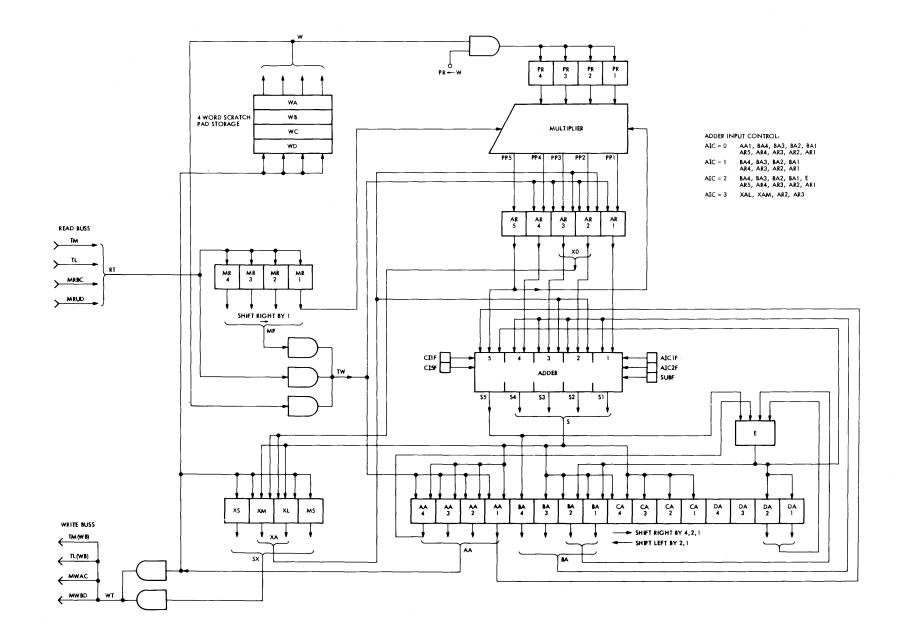

| Adder                                |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 16              |

| Scratchpad Memory                    |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 16              |

| Arithmetic Register                  |     | •   |     |    | • |   |   |     |    | • | • | • | •   |     |   | • |   |   |   |   | 16              |

| Multiplier                           | • • | •   |     |    | • | • | • |     | •  | • | • | • | •   |     | • |   | • | • | • | • | 16              |

| Control Section                      |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 17              |

| Interrupts                           |     |     |     |    |   |   |   |     | •  |   |   |   |     |     |   |   |   |   |   |   | 18              |

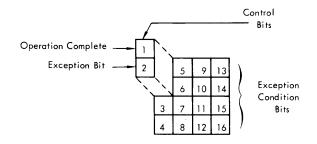

| Result Descriptors                   |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 18              |

| Processor Result Descriptor          |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 18              |

| Invalid I/O                          |     |     |     |    |   |   |   |     |    |   |   |   | •   |     |   |   |   |   |   |   | 19              |

| Invalid Instruction                  |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 19              |

| Memory Parity Error                  |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 19              |

| Address Error                        |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 19              |

| Instruction Time-Out                 |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 19              |

| Timer                                |     |     |     |    |   |   |   |     |    |   |   |   | -   |     |   | - |   |   | • | • | $\frac{10}{20}$ |

| Operator Interrupt                   |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   | • | • | • | $\frac{20}{20}$ |

| Normal/Control State Operation       |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 20<br>20        |

| OP Register                          |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | 20<br>21        |

| Logic Counter-Sequence Counter       |     |     |     |    |   |   |   |     |    |   |   |   |     |     |   |   |   |   |   |   | $\frac{21}{21}$ |

| Logic Counter Dequence Counter       | • • | •   | •   | •  | • | • | • | • • | •• | • | • | • | •   | • • | • | • | • | • | • | • | 41              |

PAGE

#### TABLE OF CONTENTS (Cont)

#### TITLE

| PAG | GE |

|-----|----|

|-----|----|

-----

| Addressing Section                  |     |      |    |     |     | •   |     | • |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   | 21             |

|-------------------------------------|-----|------|----|-----|-----|-----|-----|---|---|---|---|---|---|---|---|---|-----|---|---|---|---|---|---|---|---|---|----------------|

| Address Register                    |     |      |    |     |     |     | • • |   |   |   |   | 0 |   |   |   |   | ,   |   |   |   |   |   |   |   |   |   | $\frac{1}{22}$ |

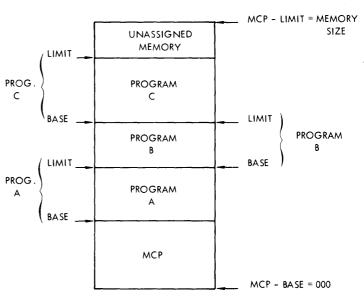

| Base-Limit Registers .              |     |      |    | •   | •   | •   | • • |   |   |   |   | ٠ |   |   |   |   |     |   |   |   |   |   |   |   |   |   | 22             |

| Addressing Techniques               |     |      |    |     |     | •   |     | e |   | ۰ | ۰ |   |   | ٠ |   |   | •   | • |   |   |   |   |   | • |   |   | 22             |

| Address Memory                      |     | •    |    |     | •   | •   | • • |   |   |   |   |   | 0 |   |   | ٥ |     |   |   | • |   |   |   | • |   |   | 23             |

| I/O Address Memory .                |     | •    | •  | •   |     |     |     |   |   | ٠ | ٠ |   | • |   | • | • |     | • |   | • |   | • | • | • | • | • | 23             |

| I/O Address Register .              |     | •    |    | •   |     |     | • • |   |   | • |   |   | • |   |   |   |     |   |   | • |   |   |   |   |   |   | 23             |

| Memory Control Section .            |     | •    |    |     | •   |     |     |   |   |   |   |   |   |   |   |   |     | • |   |   |   | • |   |   |   | • | 23             |

| Translator                          |     | •    |    | •   |     | •   |     | ٠ | • | ۰ |   | 0 | • |   |   | ۰ |     |   |   | • |   | • |   |   | • |   | 23             |

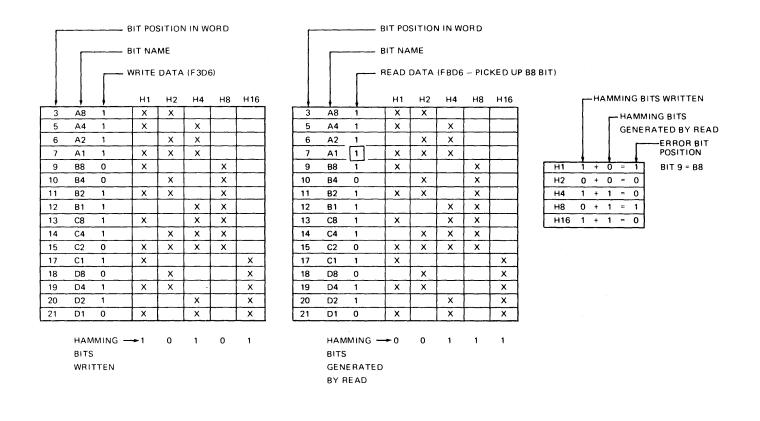

| Error Correction                    |     |      |    |     | •   | •   |     |   | • | ۰ |   |   |   |   |   |   | •   | • |   |   |   |   | • |   |   |   | 24             |

| Operator Console and Display        |     | •    | •  | •   | •   | • • | • • |   | e | o | ٠ |   | ٠ |   |   |   | •   | • |   | • |   | • | • |   |   |   | 24             |

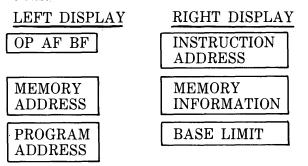

| Operator Display                    |     | •    | 9  | •   |     | •   | • • |   |   |   | • | ٠ |   |   | • |   | • ' | • |   | • |   | • |   |   | • | • | 24             |

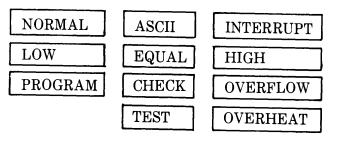

| Console Controls                    |     |      |    |     |     |     |     |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   | 26             |

| Load Function                       |     |      |    |     |     |     |     |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   | 28             |

| Universal Load                      |     |      |    |     |     |     |     |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   | 28             |

| Normal Load                         | •   | •    | •  | •   | •   | •   |     | • | • | ۰ | ٠ | • | ٠ | • | ٠ | • | •   | • | • | • | • | • | • | • |   | • | 28             |

| Central System Power                | • . | •    |    | •   |     |     |     |   |   | • |   | • |   | • | • |   | •   | • | ۰ | • |   |   | • |   | • | • | 28             |

| +4.75, -2, DC Common .              | •   |      | •  | •   | •   | •   |     | • |   | • |   | • | • | • | • | • | •   | • | • |   | • | • | • | • | • |   | 29             |

| +170 Volts                          | •   | •    |    | •   | • • | •   |     |   |   | ۰ | • | ٠ | ٠ | • | • | • | •   | • | • | • | • | • | • | • | • | • | 29             |

| $\pm 12$ Volts and $\pm 10$ Volts . |     |      |    |     |     |     |     |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   | 29             |

| 30  Volts AC  .  .  .  .            |     |      |    |     |     |     |     |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   | 29             |

| Air Sense                           | •   | • •  | ,  |     | • • | •   |     | ٥ | ۰ | ۰ | ٠ | ٥ | • | ٩ | • | • |     | • | • | • | • | • | • | ٠ | • | • | 29             |

| Power On/Off                        |     |      |    |     |     |     |     |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   | 29             |

| +4 Volts, $+22$ Volts               | •   |      | ,  | •   |     | , , |     | ٠ | ۰ | • |   | • | ٠ |   | • | • | •   | • | • | 0 | • | • | • | • | • | • | 29             |

| APPENDIX A B 3700/B 4700 I          | lns | stri | 1C | tio | n î | Se  | t   | • |   |   |   | • | ٠ | • |   | • | •   | • |   |   | • |   |   |   |   | • | A-1            |

#### LIST OF ILLUSTRATIONS TITLE

#### FIGURE

#### PAGE

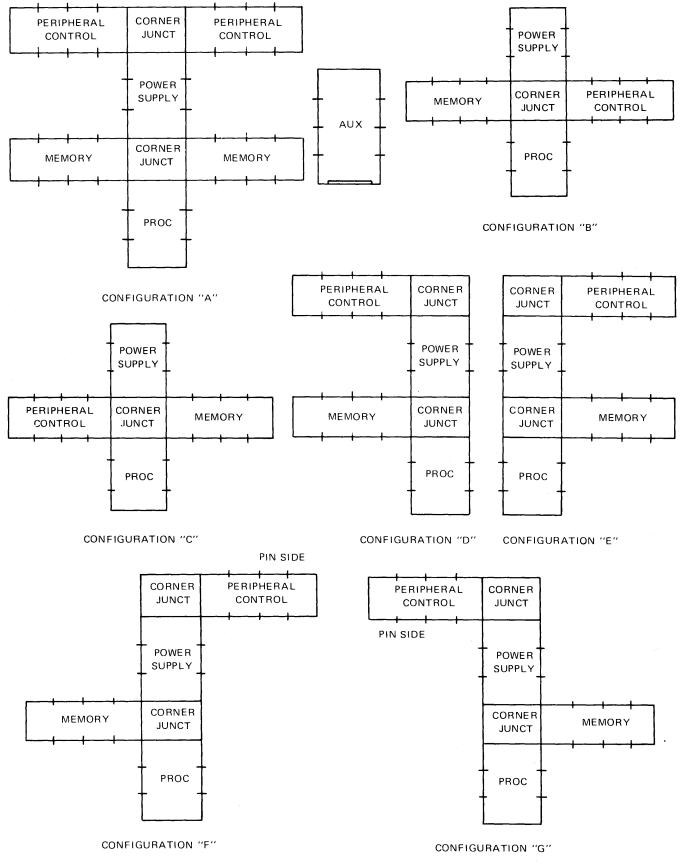

| 1  | Typical B 4700 Configurations      |

|----|------------------------------------|

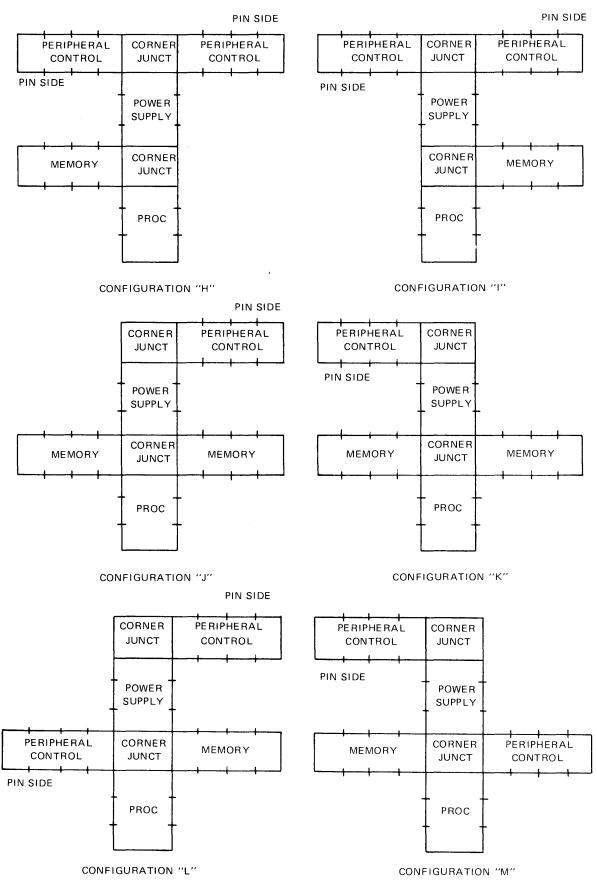

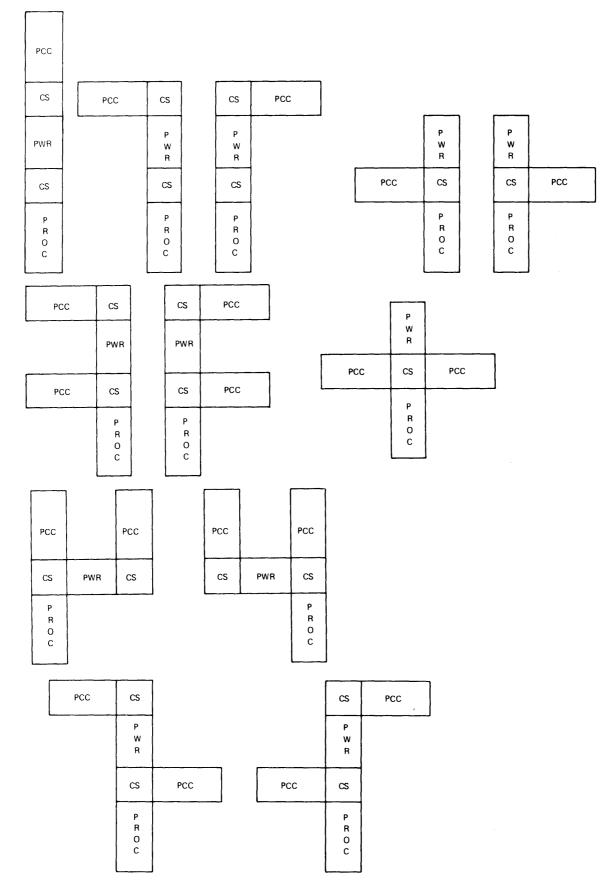

| 2  | Typical B 3700 Configurations    5 |

| 3  | Extended Address                   |

| 4  | Adder Functional Flow Chart13      |

| 5  | Adder Examples                     |

| 6  | Fixed Length Arithmetic Unit15     |

| 7  | Fixed Length Adder                 |

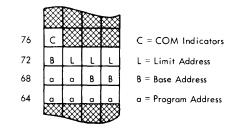

| 8  | Memory Allocation                  |

| 9  | R/D Format                         |

| 10 | Processor Result Descriptor        |

| 11 | Operational Block Diagram          |

| 12 | Interrupt and BRE Reserved Memory  |

| 13 | Error Correction                   |

| 14 | Processor Voltages                 |

#### LIST OF TABLES

# TABLE TITLE PAGE 1 B 3700/B 4700 Processor Styles 2

#### INTRODUCTION

The B 3700 system and the even more powerful B 4700 system constitute Burroughs response to the EDP equipment users' demand for more efficient, faster, and more sophisticated dataprocessing systems. The B 3700 and B 4700 systems are character-oriented toward business and data communications applications. They consist of highly efficient modular hardware/ program products, plus a wide range of exceptional peripheral devices that fulfill the requirements involved in solving the data gathering and immediate response requirements that confront data processing installations today and in the near future.

It is the purpose of this manual to acquaint the reader with the Central Processor and associated components offered by Burroughs Corporation which are applicable to the B 3700 and B 4700 systems.

#### SYSTEM DESCRIPTION

#### B 3700

The B 3700 is characterized by a 3 MHz clock speed and a memory cycle time of **667** nanoseconds. Memory sizes range from 100,000 to 300,000 bytes of solid state (IC) memory. A unique method of overlapping memory cycles has been implemented in the B 3700, to enhance the processor's response characteristics during high I/O activity periods. Due to this feature, an I/O bandpass of 3 million bytes per second is possible.

The B 3700 can accommodate up to 20 concurrent I/O channels, 10 for high speed peripheral subsystems and 10 for low speed peripheral devices. The I/O subsystem can be expanded to accommodate integrated data communication controls which will accommodate up to 36 lines.

#### B 4700

The B 4700 system has a higher clock rate (4 MHz) than does the B 3700. The B 4700 has the

### B 3700/B 4700 CENTRAL PROCESSOR

capability to handle 20 standard I/O channels, or up to 56 channels for data communication applications. The memory subsystem may contain up to one million directly addressable digits of high-speed core memory having a cycle time of 500 nanoseconds.

Both systems can utilize all medium systems peripheral devices as well as the full mix of medium systems controls, exchanges and adapters.

Power for the system, excluding peripheral devices, is derived from one central power supply, which contains all the required regulator and sensing circuitry. These supplies are internally compensated so as to reduce to a minimum any power fluctuation to the system. Several detectors are utilized to sense fault conditions such as low input voltage, dropped cycles, or input voltage that is too high. In addition, temperature sensors are employed to warn users of excessive room temperature.

#### Variable Field Length Floating Point (Optional)

This adapter is available for those users who require the Floating Point commands, OP 80 through 83. Installation of this adapter enables the user to perform real-arithmetic operation, with up to 100 digits of accuracy. Basically, the function of this adapter is to handle the alignment and normalization of operands as generally required in real-arithmetic operations.

#### **B 3700/B 4700 SYSTEM CONFIGURATIONS**

The configurations for the B 3700 and B 4700 systems are described in table 1, which lists various cabinets and operating characteristics. Figure 1 shows various B 4700 configurations, and figure 2 shows the typical B 3700 equipment configurations.

#### DATA REPRESENTATION

The basic unit of data used in the B 3700 and B 4700 processors is the bit, which represents

the presence or absence of a specific piece of information. By assigning particular values to specific bits, these bits can be combined to form larger, more efficient units of information. Because of the overall system orientation toward COBOL and the business applications by the majority of users, analysis indicated that four bits would be the optimum size of this unit of information, designated as the digit. By assigning binary weights of 1, 2, 4, and 8 to each of the bits, the combined value can represent any number from 0 through 15. The digits shown below illustrate how various bit combinations are used to represent numerical values:

| 8 Bit | 1   | 0   | 1   | 1    |

|-------|-----|-----|-----|------|

| 4 Bit | 0   | ,1  | 1   | 0    |

| 2 Bit | 0   | 0   | 0   | 1    |

| 1 Bit | 1   | 1   | 0   | 1    |

|       | (A) | (B) | (C) | (D). |

Table 1. B 3700/B 4700 Processor Styles

|        | FEATURES                                 |           |                                  |                   |                                     |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |              |

|--------|------------------------------------------|-----------|----------------------------------|-------------------|-------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|

| SYSTEM | C. C | P. Mumber | Louisons<br>Louisons<br>Conter S | (c) Date Transles | Putting Participation of the second | P. M. C. | And a state of the | (D), (100 (C)), (100 ( | Men Prod | Aurilian vor |

| B 3771 | 3MHz                                     | 1         | 8                                | 3M                | 100                                 | 300                                          | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | No       | No           |

| B 3772 | 3MHz                                     | 2         | 18                               | 3M                | 100                                 | 300                                          | 600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Yes      | Yes          |

| B 4704 | 4MHz                                     | 1         | 8                                | 2M                | 150                                 | 500                                          | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | No       | No           |

| B 4711 | 4MHz                                     | 1         | 10                               | 2M                | 150                                 | 500                                          | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (b)      | (b)          |

| B 4712 | 4MHz                                     | 2         | 18                               | 2M                | 150                                 | 500                                          | 1,000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Yes      | Yes          |

| B 4713 | 4MHz                                     | 3         | 26                               | 2M                | 150                                 | 500                                          | 1,500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Yes      | Yes          |

| B 4714 | 4MHz                                     | 4         | 34                               | 2M                | 150                                 | 500                                          | 2,000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Yes      | Yes          |

| B 4708 | 4MHz                                     | 1         | 8                                | 4M                | 150                                 | 500                                          | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | No       | No           |

| B 4731 | 4MHz                                     | 1         | 10                               | 4M                | 150                                 | 500                                          | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (b)      | (b)          |

| B 4732 | 4MHz                                     | 2         | 18                               | 4M                | 150                                 | 500                                          | 1,000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Yes      | Yes          |

| B 4733 | 4MHz                                     | 3         | 26                               | 4M                | 150                                 | 500                                          | 1,500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Yes      | Yes          |

| B 4734 | 4MHz                                     | 4         | 34                               | 4M                | 150                                 | 500                                          | 2,000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Yes      | Yes          |

NOTES

(a) Minimum.

(b) Included if multiple disk file controls.

(c) Amounts shown are millions of bytes per second per system.

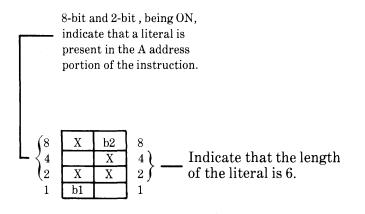

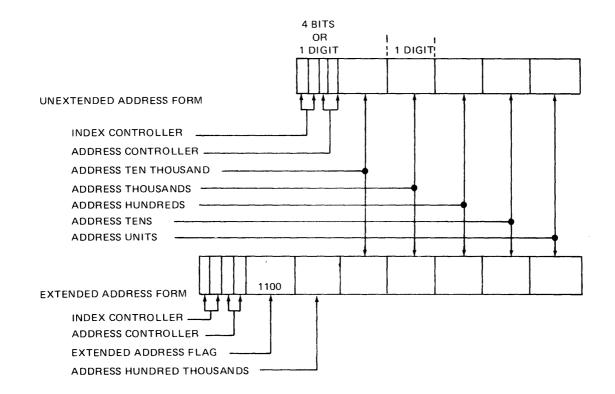

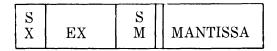

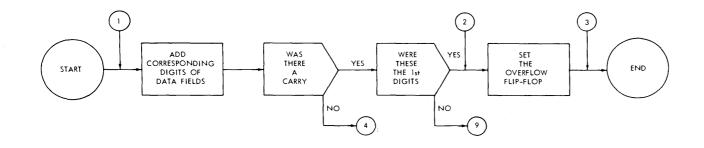

Figure 1. Typical B 4700 Configurations (Sheet 1 of 2)