MVS/SP Assist Release 1.0 Software Logic Manual

andah

amdahl®

MVS/SP Assist Release 1.0 Software Logic Manual

LICENSED MATERIAL - PROPERTY OF AMDAHL CORPORATION

Publication Number: L1020.0-02A

October 1982

## **REVISION NOTICE**

This is the second edition. It replaces L1020.0-01A, September 1982. It incorporates new technical information shown with revision bars.

### ABSTRACT

This manual provides technical information for the Amdahl MVS/SP Assist (MVS/SPA) Release 1.0 program product (4PZ0-C3-U). It is intended for systems programming and support personnel who are responsible for problem determination and diagnosis of MVS/SP Assist problems. The MVS/SP Assist General Information Manual (Amdahl M1130.0) is recommended as a prerequisite.

### **RESTRICTION ON USE**

The information contained in this manual is the licensed property of Amdahl Corporation. Use of the information contained herein is restricted pursuant to the terms and conditions of the License Agreement for Amdahl Program Products.

This manual has not been published or otherwise placed in the public domain.

### **READER COMMENT FORM**

A reader comment form is provided at the end of this manual. If this form is not available, comments and suggestions may be sent to Amdahl Corporation, Technical Publications Department, Mail Stop 323, P.O. Box 470, Sunnyvale, CA 94086. All comments and suggestions become the property of Amdahl Corporation.

annciani, annciani 470 and annciac are registered trademarks of the Amdahl Corporation.

© 1982 Amdahl Corporation. All rights reserved. Printed in U.S.A.

All specifications are subject to change without notice.

ij

# LICENSED MATERIAL - PROPERTY OF AMDAHL CORPORATION

# CONTENTS

9

| CHAPTER | $1 - INTRODUCTION \dots \dots$                                                                                                                                                                                                                                                                                           | 1–1                                                         |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 1.1     | RELATED DOCUMENTATION                                                                                                                                                                                                                                                                                                                                                                                                          | 1–2                                                         |

| CHAPTER | 2 – OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-1                                                         |

| CHAPTER | 3 - METHOD OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                        | 3—1                                                         |

| 3.1     | EXTENDED FACILITY/FEATURE (EF) INSTRUCTIONS3.1.1Test Protection Simulator - SPAE5013.1.2Fix Page Simulator - SPAE5023.1.3SVC Assist Simulator3.1.4Obtain Local Lock Simulator - SPAE5043.1.5Release Local Lock Simulator - SPAE5053.1.6Obtain CMS Lock Simulator - SPAE5063.1.7Release CMS Lock Simulator - SPAE5073.1.8Trace Instruction Simulations - SPAE508,9,A,B,C,D3.1.9Invalidate Page Table Entry Simulation - SPAE221 | 3-1<br>3-2<br>3-3<br>3-3<br>3-4<br>3-4<br>3-5<br>3-5<br>3-7 |

| 3.2     |                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-9<br>3-9<br>3-10<br>3-10<br>3-11                          |

| 3.3     | EXTENDED ADDRESSING (EA) SUPPORTED INSTRUCTIONS 3.3.1 Insert Storage Key Extended Simulator - SPAB229A . 3.3.2 Reset Reference Bit Extended Simulator - SPAB22AA 3.3.3 Set Storage Key Extended Simulator - SPAB22BA                                                                                                                                                                                                           | 3-15                                                        |

| 3.4     | IPK/SPKA IN PROBLEM STATE                                                                                                                                                                                                                                                                                                                                                                                                      | 3—15<br>3—15<br>3—16                                        |

| 3.5     | EXIT PROCESSING                                                                                                                                                                                                                                                                                                                                                                                                                | 3 - 16                                                      |

| 3.6     | SPA RECURSION ROUTINE - IEAVEXM2                                                                                                                                                                                                                                                                                                                                                                                               | 3–18                                                        |

| 3.7     | RESERVING PSA PATCH AREA                                                                                                                                                                                                                                                                                                                                                                                                       | 3–19                                                        |

MVS/SP Assist Release 1.0 Software Logic Manual Licensed Material - Property of Amdahl Corporation

12

iii

| 3.8 SUPPORT FOR THE EXECUTE INSTRUCTION                  | 0 00        |

|----------------------------------------------------------|-------------|

| 3.9 PER CONSIDERATIONS                                   | 3–20        |

|                                                          | 3–20        |

| CHAPTER 4 – FLOWCHARTS                                   | 4-1         |

| APPENDIX A - DYNAMICALLY CONSTRUCTED CODE                | A-1         |

| A.1 DYNAMIC OVERLAYS                                     | <b>A</b> —1 |

| A.2 PAGE FIX ASSIST PROLOGUE                             | A-2         |

| A.3 SVC ASSIST NOPS                                      | A-2         |

| A.4 LINKAGE TO LOCK-HANDLING INSTRUCTIONS                |             |

| •                                                        | A-2         |

|                                                          | A-2         |

| APPENDIX B - EXCEPTIONS GENERATED                        | <b>B</b> –1 |

| APPENDIX C - INSTRUCTION TRAP/SIMULATION CROSS REFERENCE | C-1         |

| APPENDIX D - MVS/SPA ON A 370/168 OR UNDER VM            | <b>D</b> –1 |

| APPENDIX E - IMPLEMENTATION DIFFERENCES                  | E-1         |

| E.1 UNSUPPORTED FEATURES                                 |             |

| E.2 DEVIATIONS                                           | <b>E</b> —1 |

|                                                          | E-1         |

| APPENDIX F - SCP MODIFICATIONS                           | F-1         |

| F.1 MVS/SPA UNDER VM OR ON A 370/168                     | F-1         |

| F.2 MVS/SPA ON A MACHINE WITHOUT 370/EF                  | F-1         |

| F.3 MVS/SPA ON AN EXTENDED MEMORY 470 CPU                | F-1         |

|                                                          |             |

# FIGURES

| Figure 3-1. Trace  | Table Entry Formats                | c  |

|--------------------|------------------------------------|----|

|                    | 01 - Test Protect Simulation       | -0 |

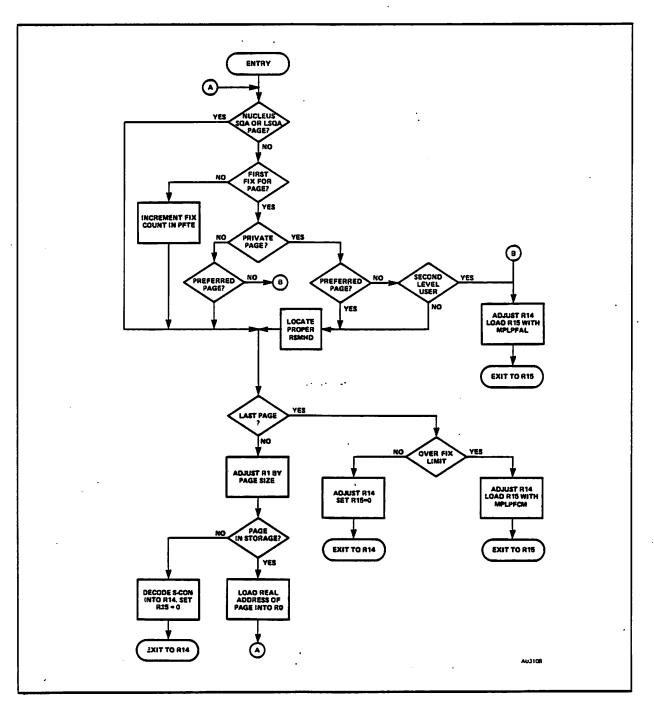

| Figure 4-2. SPAE5  | 02 - Fix Page Simulation 4-        | -2 |

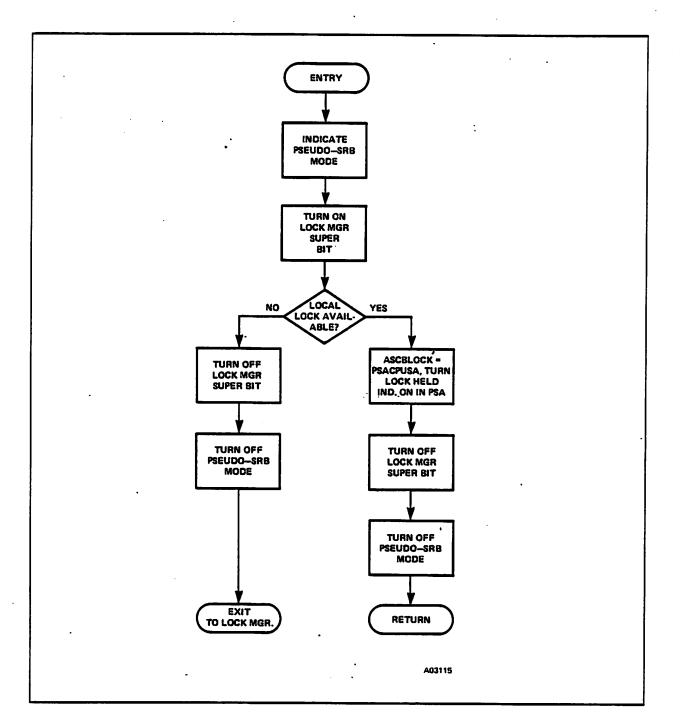

|                    | 04 - Obtain Local Lock Simulation  | -3 |

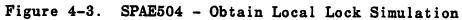

|                    | 05 - Release Lees Lock Simulation  | -4 |

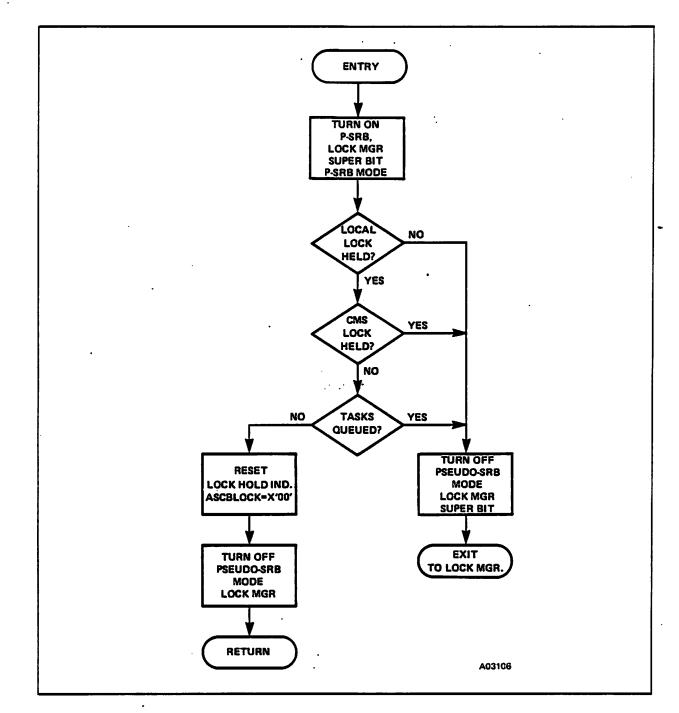

| Figure 4-5. SPAE5  | 05 - Release Local Lock Simulation | -5 |

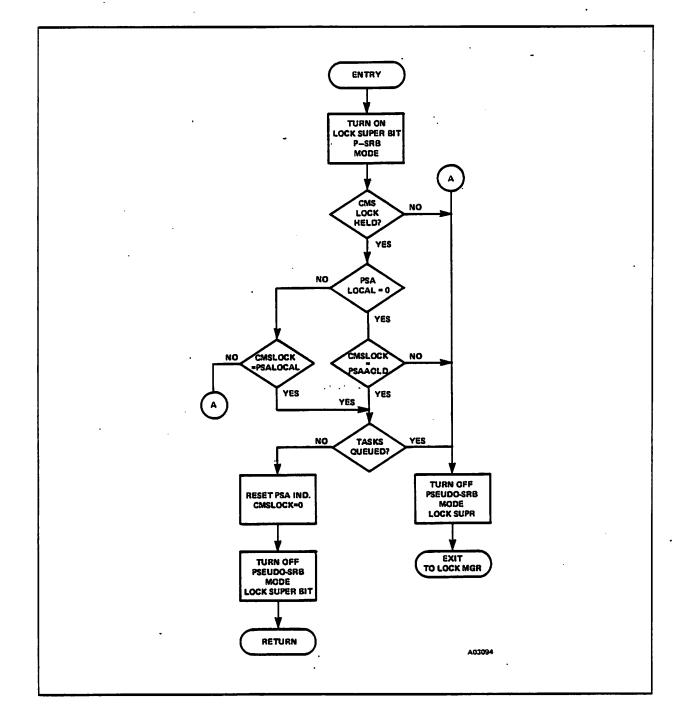

| Figure 4-6. SPAE50 | 06 - Obtain CMS Lock Simulation    | -6 |

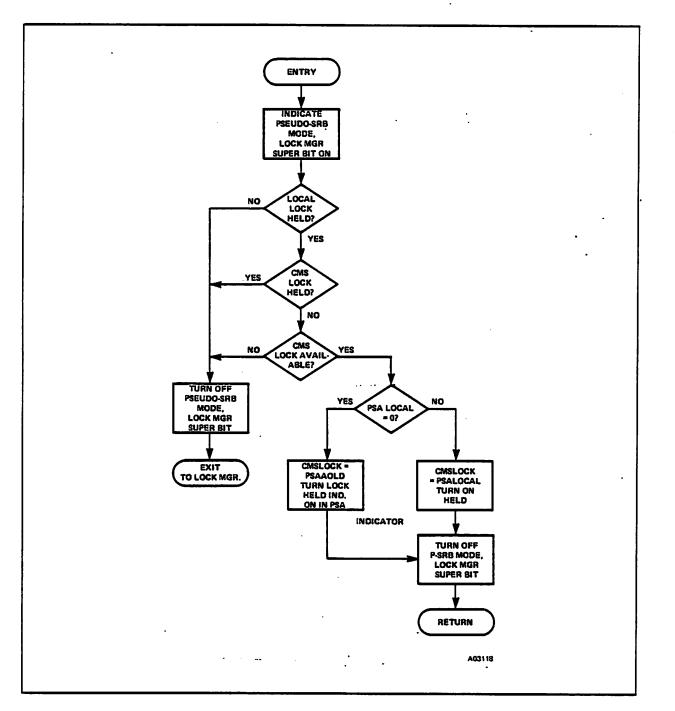

| FIGULE TO. SPAES   | 07 - Release CMS Lock Simulation   | -7 |

2

Licensed Material - Property of Amdahl Corporation

iv

•

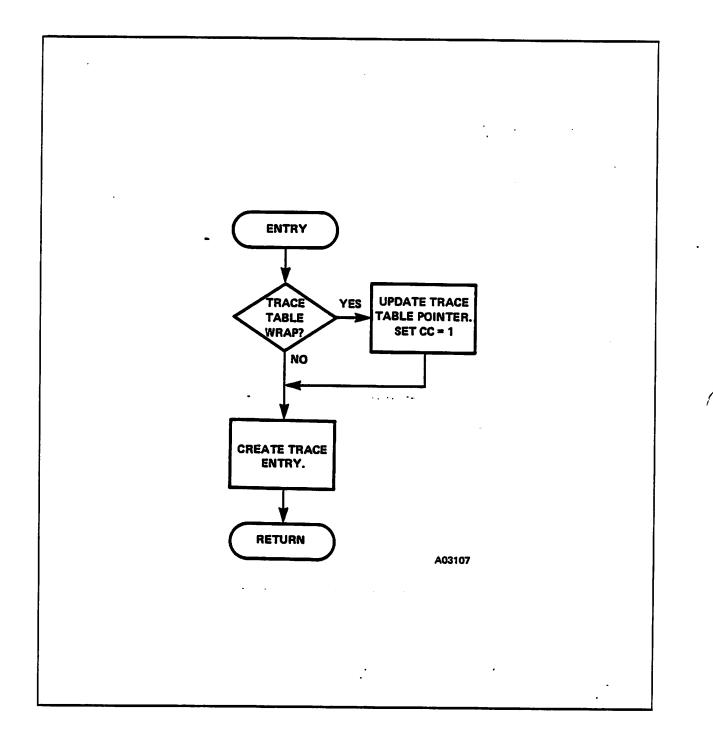

| Figure 4-7.                                                                                                  | SPAE508-D - Trace Instruction Simulation 4-8                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

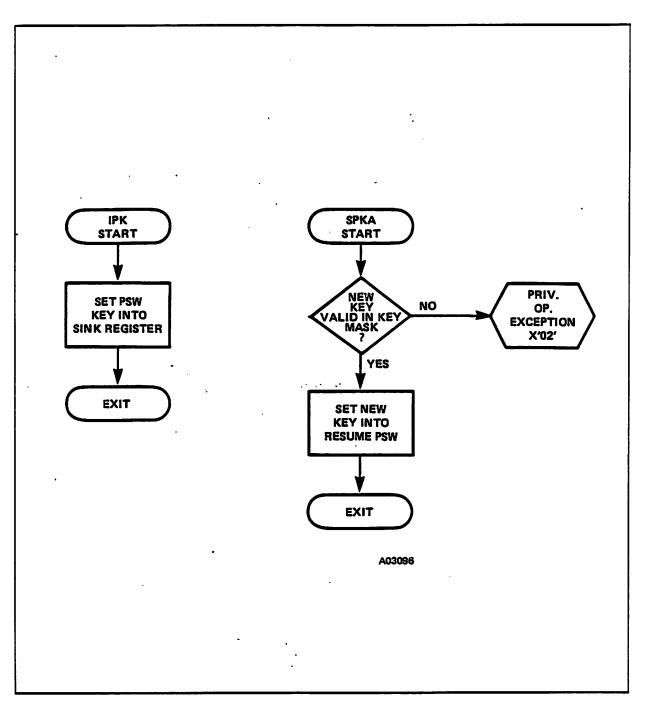

| Figure 4-8.                                                                                                  | CHECKPI2 - IPK and SPKA in Problem State 4-9                                                                                                                                                                                                                  |

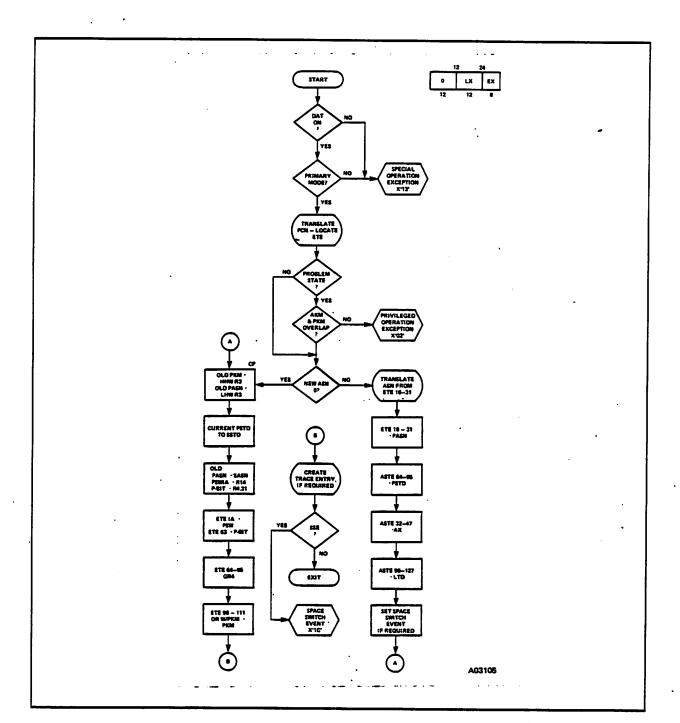

| Figure 4-9.                                                                                                  | SPAR218A - Program Call Simulation 4-10                                                                                                                                                                                                                       |

| Figure 4-10.                                                                                                 | Program Call Number Translation 4-11                                                                                                                                                                                                                          |

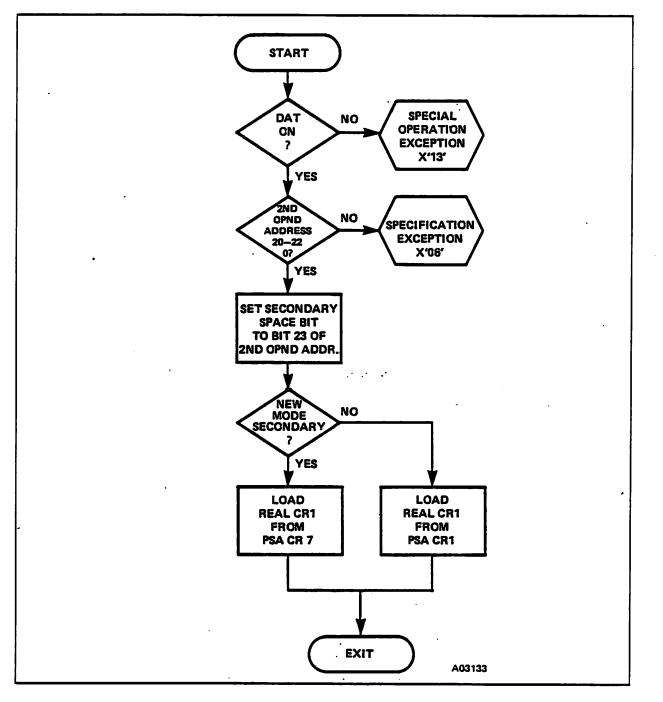

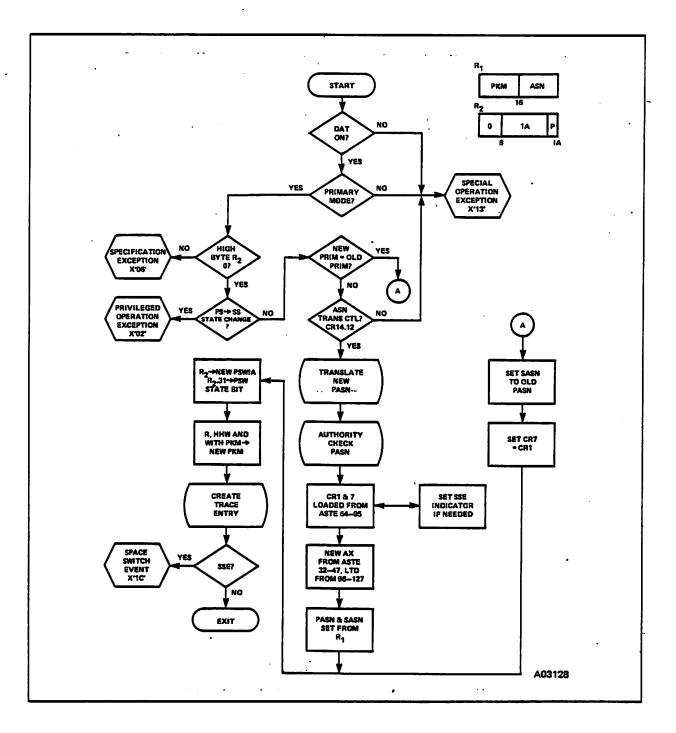

| Figure $4-11$ .                                                                                              | SDAR919A - Set Address Space Control Simulation 4-12                                                                                                                                                                                                          |

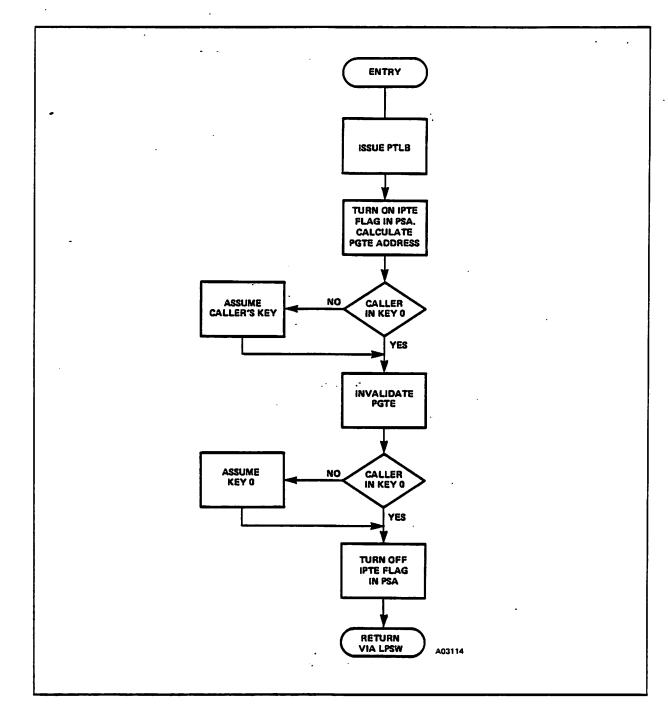

| Figure $4-12$ .                                                                                              | $SPAB221A = IPTE Simulation \dots \dots$                                                                                                                |

| Figure $4-12$ .<br>Figure $4-13$ .                                                                           | SPAB221A - IPTE Simulation                                                                                                                                                                                                                                    |

|                                                                                                              |                                                                                                                                                                                                                                                               |

| Figure 4-14.                                                                                                 | SFAD224A - Histori Marciss Space control 4-15                                                                                                                                                                                                                 |

|                                                                                                              | tion                                                                                                                                                                                                                                                          |

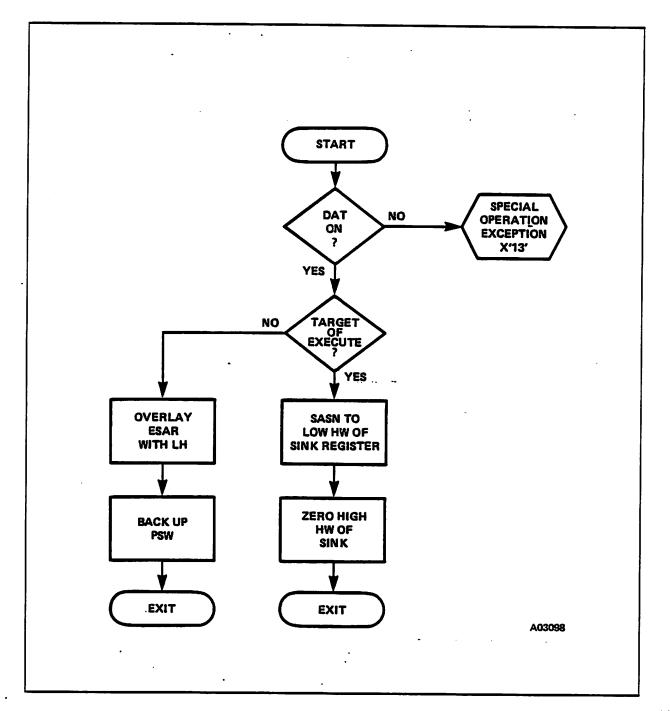

| Figure 4-15.                                                                                                 | SPAB226A - Extract Primary ASN Processing 4-17                                                                                                                                                                                                                |

| Figure 4-16.                                                                                                 | SPAB220A - Extract Filmary ASN Processing 4-18                                                                                                                                                                                                                |

| Figure 4-17.                                                                                                 |                                                                                                                                                                                                                                                               |

| Figure 4-18.                                                                                                 |                                                                                                                                                                                                                                                               |

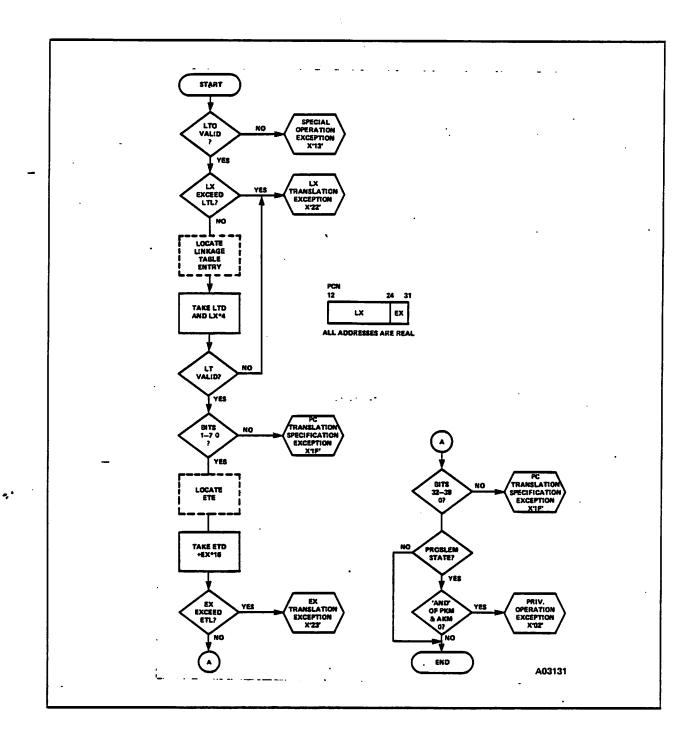

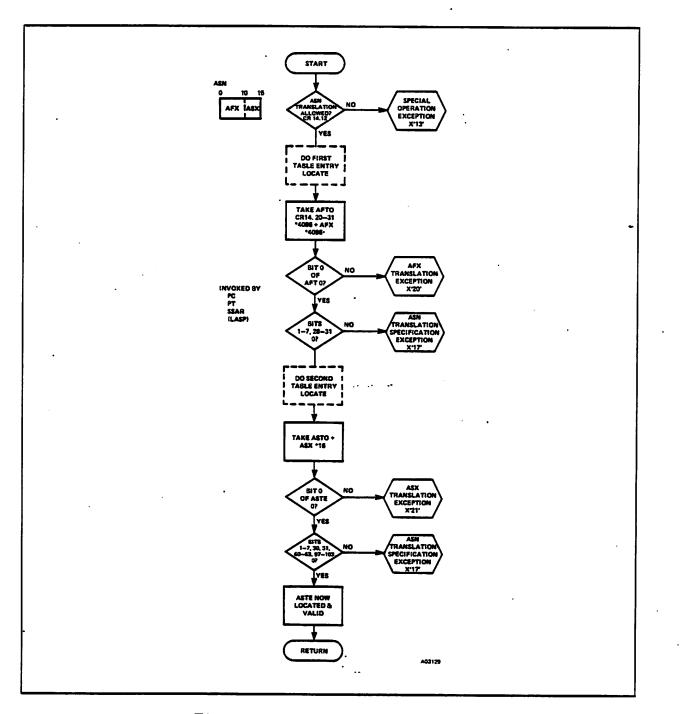

| Figure 4-19.                                                                                                 | ASN Translation $\dots \dots \dots$                                                                                                                           |

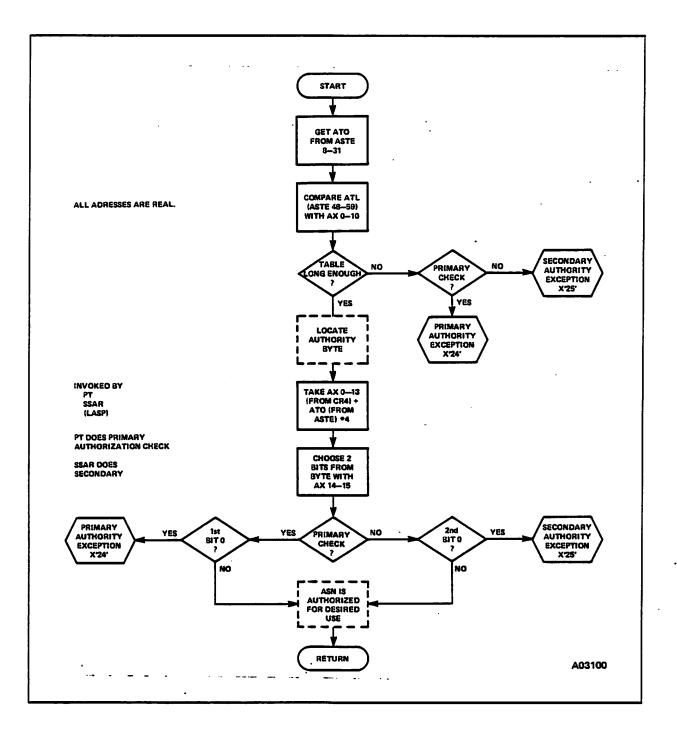

| Figure 4-20.                                                                                                 | ASN Authorization                                                                                                                                                                                                                                             |

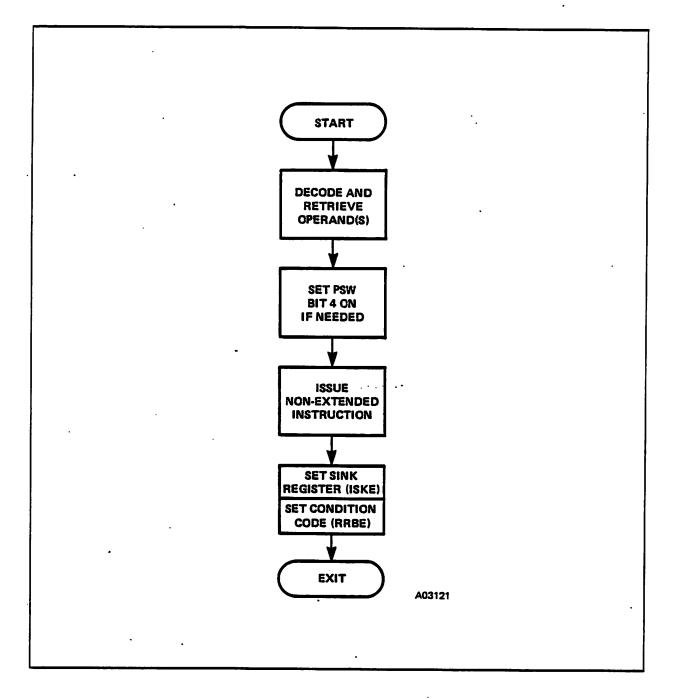

| Figure 4-21.                                                                                                 | SPAB229A-BA - Extended Storage Key Instruction                                                                                                                                                                                                                |

| -                                                                                                            | Simulations                                                                                                                                                                                                                                                   |

| Figure 4-22.                                                                                                 | Simulations                                                                                                                                                                                                                                                   |

|                                                                                                              | lation $\ldots \ldots \ldots$                                                                                                                 |

| Figure 4-23.                                                                                                 | lation                                                                                                                                                                                                                                                        |

| Figure 4-24.                                                                                                 | 4-27                                                                                                                                                                                                                                                          |

|                                                                                                              | TEAVEANS EFFOR EXIL                                                                                                                                                                                                                                           |

| Figure 4-25.                                                                                                 | Special Program Exception Handling 4-20                                                                                                                                                                                                                       |

| Figure 4-25.                                                                                                 | Special Program Exception Handling                                                                                                                                                                                                                            |

| Figure 4-25.<br>Figure 4-26.                                                                                 | EF Instruction Non-Unique Trap Building                                                                                                                                                                                                                       |

| Figure 4-25.<br>Figure 4-26.<br>Figure 4-27.                                                                 | Special Program Exception Handling                                                                                                                                                                                                                            |

| Figure 4-25.<br>Figure 4-26.<br>Figure 4-27.<br>Figure 4-28.                                                 | Special Program Exception Handling                                                                                                                                                                                                                            |

| Figure 4-25.<br>Figure 4-26.<br>Figure 4-27.<br>Figure 4-28.<br>Figure 4-29.                                 | Special Program Exception Handling4-20EF Instruction Non-Unique Trap Building4-29Common Unique Trap Processing4-30RRE Unique Trap Processing4-31SSE Unique Trap Processing4-32Trap Completion4-33                                                             |

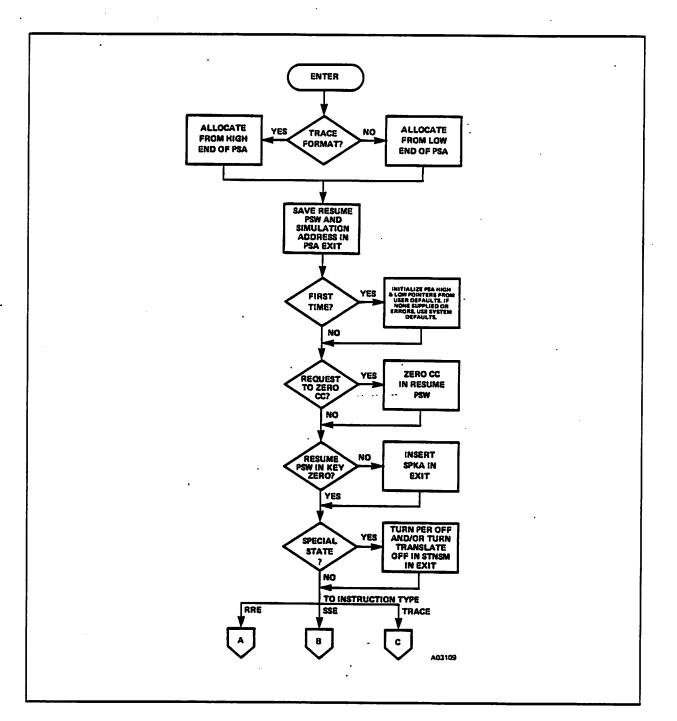

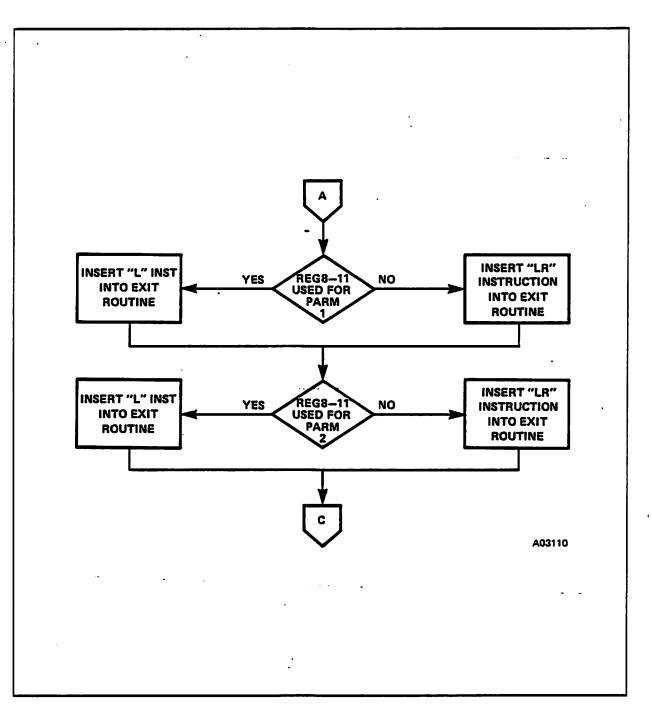

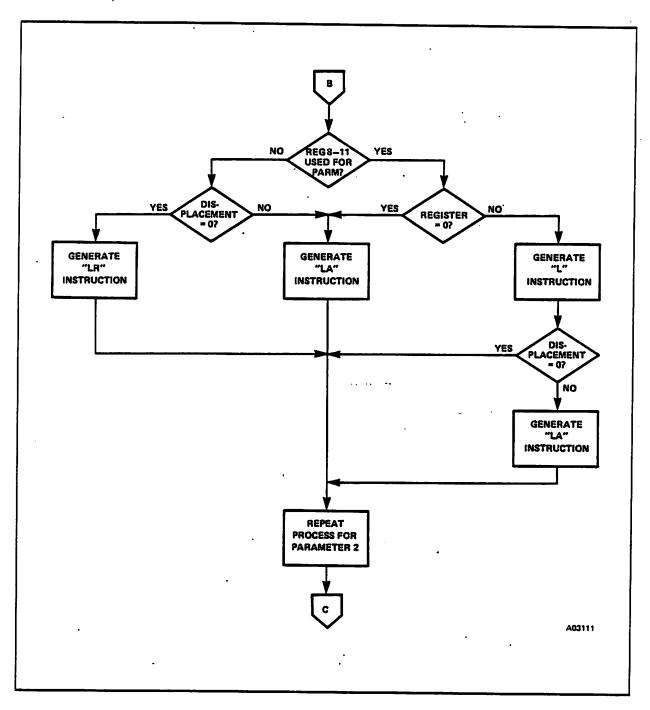

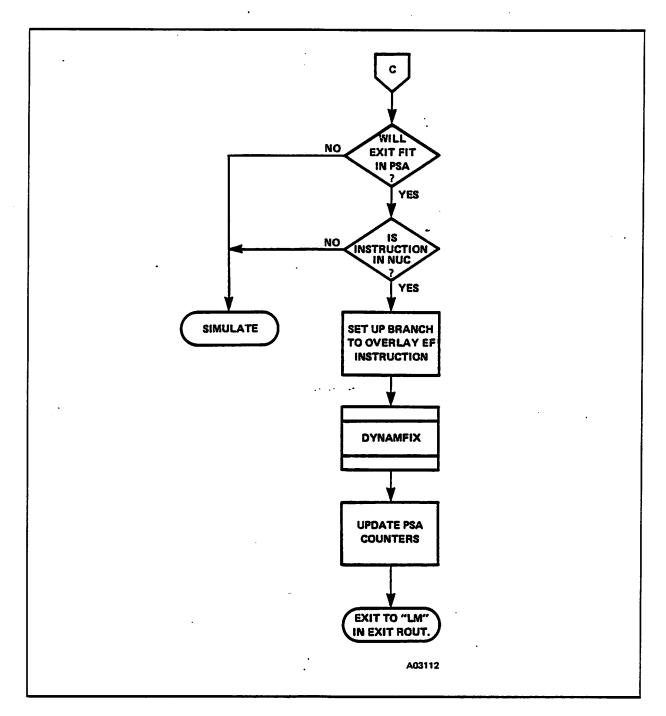

| Figure 4-25.<br>Figure 4-26.<br>Figure 4-27.<br>Figure 4-28.<br>Figure 4-29.<br>Figure 4-30.                 | Special Program Exception Handling4-20EF Instruction Non-Unique Trap Building4-29Common Unique Trap Processing4-30RRE Unique Trap Processing4-31SSE Unique Trap Processing4-32Trap Completion4-33PSA Allocation4-34                                           |

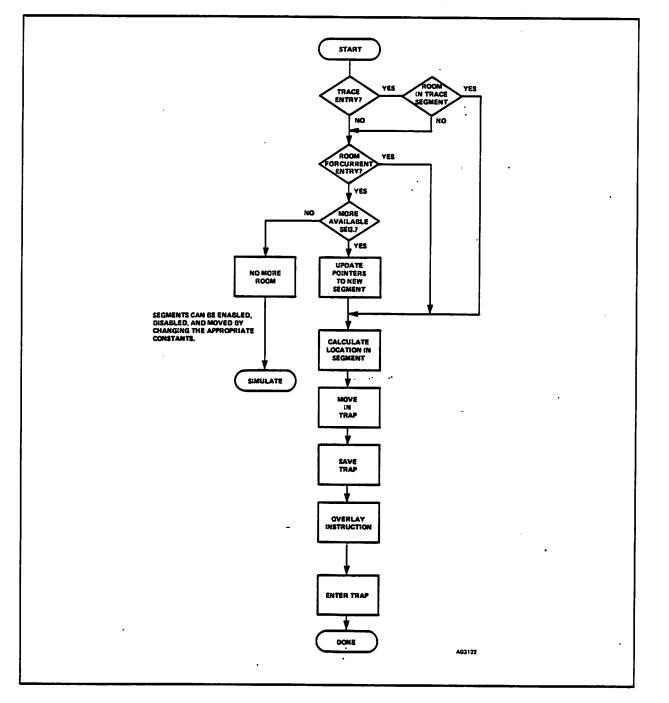

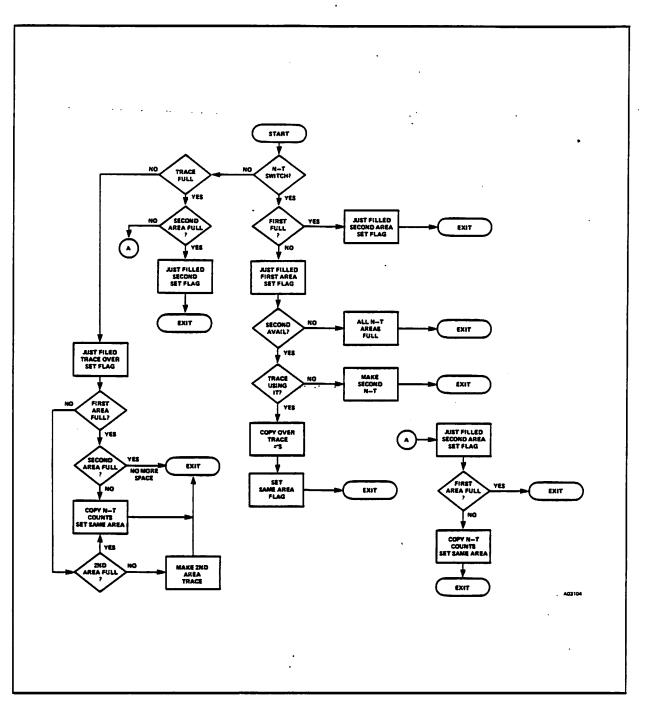

| Figure 4-25.<br>Figure 4-26.<br>Figure 4-27.<br>Figure 4-28.<br>Figure 4-29.<br>Figure 4-30.<br>Figure 4-31. | Special Program Exception Handling4-20EF Instruction Non-Unique Trap Building4-29Common Unique Trap Processing4-30RRE Unique Trap Processing4-31SSE Unique Trap Processing4-32Trap Completion4-33PSA Allocation4-34OVERBUN - Dynamic Patch Area Switching4-35 |

| Figure 4-25.<br>Figure 4-26.<br>Figure 4-27.<br>Figure 4-28.<br>Figure 4-29.<br>Figure 4-30.                 | Special Program Exception Handling4-29EF Instruction Non-Unique Trap Building4-29Common Unique Trap Processing4-30RRE Unique Trap Processing4-31SSE Unique Trap Processing4-32Trap Completion4-33PSA Allocation4-34OVERRUN - Dynamic Patch Area Switching4-35 |

# TABLES

| Table 1-1. | Supported Systems and Features                    | 1-2         |

|------------|---------------------------------------------------|-------------|

| Tabla A_1  | Instruction Replacement Code                      | <u>A</u> -1 |

| T-1 D-1    | Interrupts Caused by Simulations                  | <u>B</u> -1 |

| Table R_9  | Cross Reference of Interrunt Code to ABEND Code . | B-5         |

| Table C-1. | Cross Reference of Instruction Trap/Simulation    | 1-J         |

MVS/SP Assist Release 1.0 Software Logic Manual Licensed Material - Property of Amdahl Corporation

V

### CHAPTER 1 - INTRODUCTION

MVS/SP Assist (MVS/SPA) Release 1.0 is an Amdahl licensed program product that allows the MVS/System Products (5740-XYN and 5740-XYS) at Version 1 Release 3 to run on Amdahl 470 processors and System/370 uniprocessors that do not have the 370 Extended Facility/Feature (EF) installed. In addition, it provides support for the 3033 Extension (XF) for those 470, 370, 303X and 4300 systems that do not have the 3033 Extension available or installed. It also provides support for Extended Addressing (EA) on the Amdahl 470 systems. See table 1-1 for supported combinations.

| MVS/SPA supersedes MVS/SEA Release 3.0 and, because of a different design, does not require most of the operating system changes required by MVS/SEA; therefore the installation procedure is much simpler. It gives additional performance gains for an MVS/SP 1.3 system that currently uses MVS/SEA and/or the IBM-provided XF simulation routines.

MVS/SPA will produce results functionally equivalent to any of the following environments:

MVS/SP 1.3 with IBM XF simulations and MVS/SEA

MVS/SP 1.3 with IBM XF simulations and 370/EF

MVS/SP 1.3 with the 3033 Extension

Unsupported features and exceptions to the operation of the supported instructions, as defined in the <u>System/370 Principles of Operation</u> or <u>System/370 Assists for MVS</u>, are listed in Appendix E.

#### NOTE

As is the case with MVS/SEA, MVS/SPA assumes that it will be the only user of the unused sections of the PSA. Should any other user installed products also require use of some or all of this area, please see paragraph 3.7 for information on how to resolve these conflicts.

MVS/SP Assist Release 1.0 Software Logic Manual Licensed Material - Property of Amdahl Corporation 1–1

# Introduction

### 1.1 RELATED DOCUMENTATION

The documents listed below provide the user with additional information about the Amdahl MVS/SPA and MVS/SEA products, and the IBM 370/Extended Facility, the 3033 Extension and Extended Addressing. <u>IBM System/370 Principles of Operation</u> (IBM GA22-7000) <u>IBM System/370 Assists for MVS</u> (IBM GA22-7079) <u>Cross Memory Services User's Guide</u> (IBM GG22-9231) <u>MVS/SP Assist Release 1.0 General Information Manual</u> (Amdahl M1130.0) <u>MVS/SE Assist Release 3.0 General Information Manual</u> (Amdahl M1109.0) Amdahl MVS/SPA Microfiche (Amdahl Licensed Material)

| 370/EF  | 3033E                   | EA                                                                                 |

|---------|-------------------------|------------------------------------------------------------------------------------|

| X       | X                       | X                                                                                  |

| X       | X                       |                                                                                    |

|         | X                       |                                                                                    |

|         | X                       |                                                                                    |

| Not Use | d - Completely          | Transparent                                                                        |

| X       | . X                     |                                                                                    |

|         | X                       |                                                                                    |

| Not Use | d - Completely          | Transparent                                                                        |

|         | As Required             |                                                                                    |

|         | X<br>X<br>Not Used<br>X | X X<br>X X<br>X<br>X<br>Not Used - Completely<br>X X<br>X<br>Not Used - Completely |

Table 1-1. Supported Systems and Features

Licensed Material - Property of Amdahl Corporation

#### CHAPTER 2 - OVERVIEW

A CPU running MVS/SP 1.3 without the 3033 Extension will program check when it encounters one of the XF instructions. This program check is passed to nucleus-resident module IEAVEXMS to see if the instruction is indeed one of the XF instructions and not a coding error. If it is an XF instruction, it is simulated, and return is made either to the next sequential instruction or otherwise as the instruction dictates.

The MVS/SPA product takes advantage of this design to also intercept the program checks from the EF and EA instructions; module IEAVEXMS is completely replaced, and SPA simulates or traps all three types of instructions. The simulations are faster in most cases than those in the standard IEAVEXMS, and the construction of the MVS/SPA IEAVEXMS eliminates the possibility of a program check recursion caused by the issuance of EF instructions in the standard IEAVEXMS. In some cases the existence of an MVS coding convention is checked for, allowing a fast path in the decoding and fetching of operands - for example, in the Program Call and Program Transfer simulations.

Normally, all EF (and some XF) instructions are replaced by valid instructions that either directly enter the simulation routines or simulate the original instruction.

For program interruptions that are not related to EF, XF or EA instructions, MVS/SPA passes control back to the program check FLIH to continue with normal RTM processing. Also, should a simulation routine encounter a cause for exception while simulating an instruction, the exception is passed to the program FLIH as it would have been had the hardware feature been installed.

The MVS/SPA product consists of one module, a replacement for IEA-VEXMS. In addition, a small superzap change to module IEAVNIPO is required for CPUs without the 370/EF implemented in hardware to allow MVS/SP to IPL without it. On 370/168 CPUs without EF, or under non-SP VM systems, a change is also required to IEAVNPX1 to ensure that the common segment bits are not turned on, as the MVS/SPA product cannot intercept the resulting program checks that would result. See appendix D for further information.

The 470 Extended Addressing feature requires some additional changes to the operating system. The feature is checked for proper enablement by a zap to IEAVNIPO, and three standalone dump modules are updated to support the Amdahl implementation of the extended key instructions. Paragraph 3.3 describes the necessary feature settings to enable the 470 Extended Memory feature after it has been installed.

Appendix F summarizes the operating system modules changed and the nature of the changes.

MVS/SP Assist Release 1.0 Software Logic Manual Licensed Material - Property of Amdahl Corporation

## CHAPTER 3 - METHOD OF OPERATION

Flowcharts for most of the MVS/SP Assist routines are provided in chapter 4.

Module IEAVEXMS is passed control from the Program Check First Level Interrupt Handler (FLIH) whenever a program interrupt occurs for an operation exception (interrupt code X'01') or a privileged operation exception (interrupt code X'02'). The type of interrupt is determined from the program interrupt code (location X'8F' in the PSA), and the instruction address is determined by subtracting the instruction length code (PSA location X'8D') from the address in the program old PSW (PSA location X'28'). The cause of the interrupt will be an operation exception for a supported instruction, a privileged operation exception for an IPK or SPKA, or some other non-supported reason.

Supported instructions are handled in one of three ways: simulating, trapping or ignoring them. In general, EF instructions are trapped, and XF and EA instructions are simulated. The difference between trapping and simulating is that while both result in the instruction being simulated, the trapped instruction uses an exit in the PSA, and operand decodes are already done. The non-trap simulation routines require that the operands be decoded on all occurrences.

### 3.1 EXTENDED FACILITY/FEATURE (EF) INSTRUCTIONS

When an EF instruction is recognized, the program check old PSW is checked to ensure the issuer was in supervisor state. If not, the interruption code is changed to X'0002' to indicate a privileged operation exception, and control is passed via the error exit to RTM.

The opcode is next checked to ensure that it is within the range X'E501' to X'E50D'. If not, the interrupt is passed back to the program FLIH via the error exit. If the opcode is supported, an address located via table look-up is used to locate the specific simulation routine and to control further processing.

The trace, IPTE and TPROT simulations require trap areas in the PSA. These areas are allocated and the traps are built by the PSAALLOC routine. Appendix A describes this routine in more detail.

### 3.1.1 Test Protection Simulator - SPAE501

Routine SPAE501 receives control from the PSA exit routine built on the first occurrence of the instruction. On entry, two registers have been loaded with the instruction operands and a third with the routine base register. (See appendix A for details of the PSA exit.)

MVS/SP Assist Release 1.0 Software Logic Manual Licensed Material - Property of Amdahl Corporation

After setting a recursion indicator into PSAPCFB4, SPAE501 changes the PSW key to that specified in the second operand. The storage address designated by the first operand is then fetched (via a TM instruction) and tested for store permission (via a non-destructive OI). The PSW key is reset to zero to allow resetting of the recursion indicator, and control is returned to the original code via LPSW. The default condition code in the resume PSW is zero (set during trap construction) so the condition code is valid.

If either fetch or store is disallowed, the references by the TM or OI cause a program check. Due to the setting of PSAPCFB4, control is passed to the SPA recursion entry, IEAVEXM2, by the program FLIH. IEAVEXM2 then examines the register contents to decide whether the fetch or the store was disallowed (a register contains 'F' during the fetch trial and 'S' on the store trial). It sets the appropriate condition code in the resume PSW and returns to the original code.

### 3.1.2 Fix Page Simulator - SPAE502

Routine SPAE502 receives control from the PSA exit routine built on the first occurrence of the instruction. On entry, registers are as follows:

| Register O     | - Real address in the first page frame to be fixed.                                                 |

|----------------|-----------------------------------------------------------------------------------------------------|

| Register 1     | - Virtual address in the first page to be fixed.                                                    |

| Register 2     | - Virtual address in the last page to be fixed.                                                     |

| Registers 8-10 | - Saved                                                                                             |

| Register 11    | - Routine base register                                                                             |

| Register 14    | - Pointer to S-type address constant of successful-<br>fix exit point. (Instruction first operand.) |

After locating the MAPL, the routine loops, attempting to fix all the pages in the range specified by registers 1 and 2. (The microcode implementation does only one page per issuance of the instruction, but as a performance enhancement, the simulation fixes all possible pages on each issuance.) The following description applies to each pass through the loop.

If the page to be fixed is already fixed by default (nucleus, L/SQA or V=R page), the fix count is not examined, and control passes to the end of the loop.

If the page frame is being fixed for the first time and is not in the preferred area, or if it does not belong to either the common area or a second-level preferred user, the simulation terminates by calling

3-2

the MVS exception routine, located from MPLPFAL. In all other cases the fix count is incremented for the page. If this is the first fix for the page (fix count is now one), the total system fixed frame count (MPLCNTRS in the PVT) is incremented. If the page is a common area page, the common area fix count is also incremented. If it is a private area page, the address space fix count in the RSM header is incremented. The proper RSMHD is located from the ASCB either in PSA-AOLD (during early NIP), or the ASCB located (via the ASVT) from the ASN in control register 3 or 4, depending on the setting of the secondary mode bit.

If the last page in the range has not yet been fixed, the address of the current page to fix is incremented by X'1000'. If the page exists in storage or the Extended Main Storage feature is not enabled, processing begins again at the start of the loop. If not, the S-constant pointed to by register 14 is decoded and branched to.

If the last page in the range has been fixed, the total system fix count is compared with the maximum number of pages allowed to be fixed contained in the MAPL (MPLMAXFX). If the maximum count has not been exceeded, return is made to the instruction after the FIX PAGE instruction trap. If the count is exceeded, exit is made to the SRM frame fix excession routine, located in the MAPL (MPLPFCM).

### 3.1.3 SVC Assist Simulator

The function performed by the SVC Assist hardware implementation instruction is identical to that of normal SVC FLIH processing; therefore, there is no SVC Assist simulation routine. Whenever the SVC Assist instruction is encountered, it is overlaid with NOPs so that control passes to standard FLIH processing.

### 3.1.4 Obtain Local Lock Simulator - SPAE504

Routine SPAE504 receives control directly from the instream code via a | LOAD/BALR sequence which replaced the original instruction on first occurrence. Register 12 contains the return address, 13 the base address, and 11 is free. (See appendix A for further details of the linkage.)

First, pseudo-SRB mode (PSAPSRBM) is set to avoid preemption during interrupts, then the PSA super bit for the lock manager (PSALOCK) is set to disable any PER processing that may occur. Because the lock simulators run enabled, these bit-settings prevent any possibility of loss of control during update of the lock word and indicators.

The current ASCB is located via PSAAOLD and the lock status checked. If it is held, exit is made to the 'Local Lock Obtain Failed' entry point in the Lock Interface Table prefix (LITOLOC). If it is not held, the CPU physical address is set into the lock word, the PSAHLHI

MVS/SP Assist Release 1.0 Software Logic Manual Licensed Material - Property of Amdahl Corporation

bit for the local lock is set, and exit is made to the caller. In both cases, the condition code is restored to what it was on entry, and both the SUPER and MODE bits set on entry are reset.

# 3.1.5 Release Local Lock Simulator - SPAE505

Routine SPAE505 receives control directly from the instream code via a | LOAD/BALR sequence which replaced the original instruction on first occurrence. Register 12 contains the return address, 13 the base address, and 11 is free. (See appendix A for further details of the linkage.)

First, pseudo-SRB mode (PSAPSRBM) is set to avoid preemption during interrupts, then the PSA super bit for the lock manager (PSALOCK) is set to disable any PER processing that may occur. Because the locksimulators run enabled, these bit-settings prevent any possibility of loss of control during update of the lock word and indicators.

The 'locks held' bit string is checked to ensure that a CMS lock is not held and the local lock is held. The current ASCB is located via PSAAOLD and the local lock suspend queue is checked. If a CMS lock is held, the local lock is not, or there is an entry in the suspend queue, exit is made to the 'Local Lock Release Failed' entry point in the LIT prefix (LITRLOC). If all the checking is passed, the lockword is zeroed, the lock held indicator (PSAHLHI) is reset, and exit is made to the caller. In both cases, the condition code is restored to what is was on entry, and both the SUPER and MODE bits set on entry are reset.

# 3.1.6 Obtain CMS Lock Simulator - SPAE506

Routine SPAE506 receives control directly from the instream code via a LOAD/BALR sequence which replaced the original instruction on first occurrence. Register 12 contains the return address, 13 the base address, and 11 points to the CMS lockword to be used. (See appendix A for further details of the linkage.)

First, pseudo-SRB mode (PSAPSRBM) is set to avoid preemption during interrupts, then the PSA super bit for the lock manager (PSALOCK) is set to disable any PER processing that may occur. Because the lock simulators run enabled, these bit-settings prevent any possibility of loss of control during update of the lock word and indicators.

The specified lockword is first inspected to ensure that it is free. If it is not, or a CMS lock is already held, or the local lock is not, exit is made to the 'CMS Lock Obtain Failed' entry point in the Lock Interface Table prefix (LITOCMS). Field PSALOCAL is then used to locate the proper ASCB (if it is zero, PSAAOLD is used). The CMS lock held indicator is then turned on in the PSAHLHI field, and the ASCB address is stored into the lock to mark it held. Exit is then made to

3-4

the caller. In all cases, the condition code is restored to what it was on entry, and both the SUPER and MODE bits set on entry are reset.

## 3.1.7 Release CMS Lock Simulator - SPAE507

Routine SPAE507 receives control directly from the instream code via a LOAD/BALR sequence which replaced the original instruction on first occurrence. Register 12 contains the return address, 13 the base address, and 11 points to the lockword to be used. (See appendix A for further details of the linkage.)

First, pseudo-SRB mode (PSAPSRBM) is set to avoid preemption during interrupts, then the PSA super bit for the lock manager (PSALOCK) is set to disable any PER processing that may occur. Because the lock simulators run enabled, these bit-settings prevent any possibility of loss of control during update of the lock word and indicators.

The 'locks held' bit string is checked to ensure that both a CMS lock and the local lock are held. If either lock is not held, or there is an entry in the suspend queue, exit is made to the 'CMS Lock Release Failed' entry point in the LIT prefix (LITRCMS). If all the checking is passed, the lockword is zeroed, the lock held indicator (PSAHLHI) is reset, the condition code is restored to what it was on entry, both the SUPER and MODE bits are reset, and exit is made to the caller.

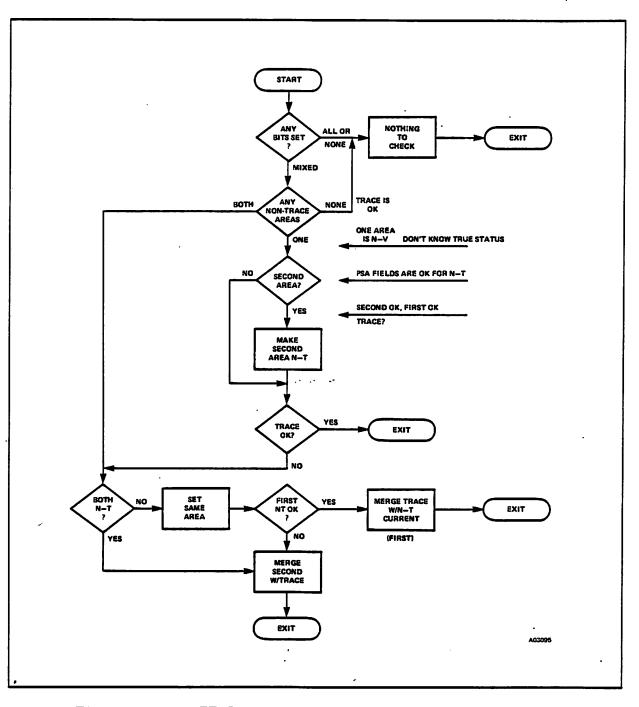

3.1.8 Trace Instruction Simulations - SPAE508,9,A,B,C,D

The method of operation is the same for all of the trace instruction simulations: the simulation routine is entered from a unique PSA trap that disables the machine, saves some registers, moves the model resume PSW to the resume area (PSAXMPSW) and calls the simulation routine. (See appendix A for further details of the linkage.)

| The trace table header is first checked to see if the table has wrapped. If so, the table start address is used for the new entry address and condition code 1 is set in the resume PSW. Otherwise the current entry pointer is incremented by 32, and the new entry address is stored back into the current entry pointer.

The format of each entry is defined in <u>IBM System/370 Assists for MVS</u>. The only difference is that in some cases an operand is assumed and fetched from the PSA, instead of decoding the instruction operand and using that address. Results should be identical in both cases. Figure 3-1 contains a layout of the trace entries.

The specific trace routines are:

Ż

- SPAE508 Trace SVC Interrupt

- SPAE509 Trace Program Interrupt

MVS/SP Assist Release 1.0 Software Logic Manual Licensed Material - Property of Amdahl Corporation

| INSTRUCTION        | TRACE SVC                | TRACE POM                           | TRACE DUITIAL                         | TRACE I/O                | TRACE TASK                                                                                                     | TRACE BVC                | TRACE             | TRACE PROGRAM         | TRACE LET           |

|--------------------|--------------------------|-------------------------------------|---------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------|-------------------|-----------------------|---------------------|

| +                  | DAEKO                    | CALEGO                              | SAS UNITALICH<br>SPASSOA              | EPAESO                   | DURATCH<br>BAEGOC                                                                                              | RETURN<br>CARGOD         | PROGRAM CALL      | TRANSFER              | RECONDARY ASN       |

| OVTES 0, 1         | FLCSOPSW<br>RVTES 0, 1   | FLCPOPEN<br>BYTER 0. 1              | PLACEMPEUR<br>BYTELS O. 1             | FLCIOPSW<br>AVTES 0. 1   | PLAPENER<br>AVTER 0.1                                                                                          | PLAPSHOV                 | NEW PSW           | NEW PSW               | MSM MEN             |

| _                  | 4                        | 4                                   | ŀ                                     | ŀ                        | ł                                                                                                              | Þ                        | 4                 | 1 'Dealta             |                     |

|                    | þ                        | Þ                                   | þ                                     |                          | 4                                                                                                              | 4                        | Þ                 | 4                     | •                   |

| PME 3              | FLOWOR                   | FLCHICOD                            | PEASABEL                              | 12 - 23                  | REINTCOD                                                                                                       | RENTCOD                  | NEW PSW           | 2                     | •                   |

| evres<br>4-7       | FLCEPSEN                 | FLCPOPSH<br>FLCPOPSH<br>BYTEE 4 - 7 | PLACEPCIN<br>PLACEPCIN<br>EVTER 4 - 7 | FLCIOPSIN<br>MYTER A - 7 | BVTE 1<br>PLAPSHEV<br>BVTECA _ 2                                                                               | PEAPSWEV                 | EVTE 3<br>NEW POW | NEW PON<br>BYTE 3 - 7 | NEW PSW<br>NYTE 3-7 |

| BYTES 8,0          | GENERAL                  | GENERAL                             | þ                                     |                          | , and the second se |                          | NEW PARM          | NEW PASH              | PACU                |

| BYTER 10, 11       | REGISTER<br>15           | AEQUITER<br>15                      | SRIFASID                              | FLCCEN                   | NEGISTER<br>NEGISTER                                                                                           | NEGISTER<br>15           | NEW SAGN          | þ                     | NEWSAIN             |

| - BYTES<br>12 - 16 | GENERAL<br>REGISTEN 0    | FLCTEA                              | GENERAL<br>REGISTER 0                 |                          | GENERAL<br>REGISTER D                                                                                          | GENERAL<br>BEGISTER D    | GENERAL REGISTER  | N2A9010               | Þ                   |

| VTE8<br>1 - 10     | GENERAL<br>REGISTER 1    | GENERAL<br>REGISTER 1               | GENERAL<br>REGUTTER 1                 |                          | GENERAL<br>REQUERER 1                                                                                          | GENERAL<br>BECIETER 1    | 4. u              | ¢ 4                   | OLD EASY            |

| BYTE 0-1           | FLCSILC<br>BITS 5, 0     | FLCPULC<br>BUTSE, 6                 |                                       | FLCIOPSIN                | RENALMTH<br>Butta 6, 6                                                                                         | REWLMTH<br>GUTE 6. 0     | -191              | -10-                  | 10                  |

| -                  | FLC30P3W<br>BITS 13 - 23 | FLCPOPSW<br>BITE 12 - 23            | >                                     | BYTER                    | FEADSWEV<br>F1 = 21 = 21                                                                                       | PEAPSHEV<br>BUTE 13 - 23 |                   | FLCSOPEN<br>MTB 13-23 |                     |

| AVTE 21            |                          |                                     |                                       |                          | PACPULA-1                                                                                                      |                          |                   |                       |                     |

| BVTES 23, 23       | ASCRASID                 | AICBASID                            | ASCAASID                              | ASCANED                  | ASCENED                                                                                                        | Ascanico                 | þ                 | ķ                     | þ                   |

| avtes 24 – 27      | PLATOLD                  | PLATOLD                             | <b>ENAFTCE</b>                        | PLATOLD                  | MATOLD                                                                                                         | PATOLD                   | # 04              | þ                     | þ                   |

| AVTES 23 – 31      |                          |                                     | -C 131/1                              | LOF DOUBLEWORD T         | BYTES 3-6 OF DOUBLEWORD THAT IS STORED BY INSTRUCTION "STORE CLOCK"                                            | STRUCTION "STORE         | clock"            |                       |                     |

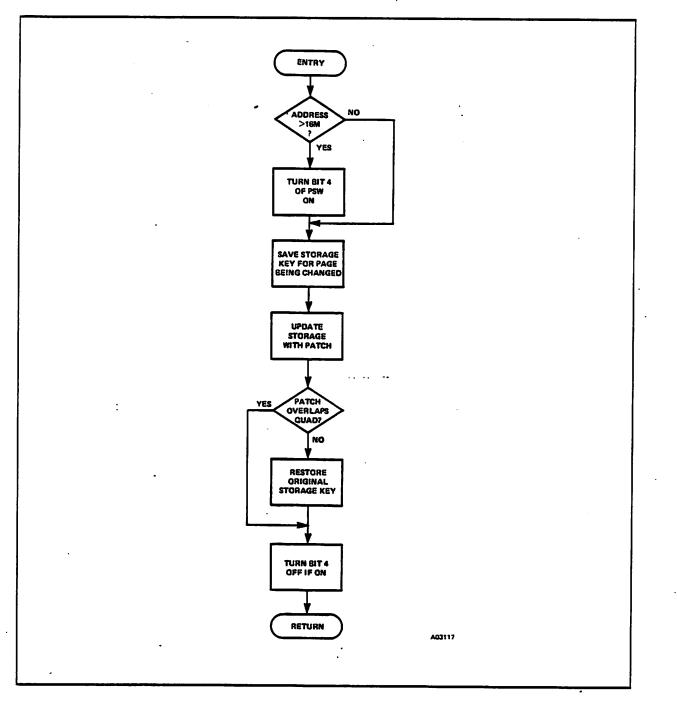

Figure 3-1. Trace Table Entry Formats

Licensed Material - Property of Amdahl Corporation

- SPAE50A Trace Initial SRB Dispatch

- SPAE50B Trace I/O Interrupt

- SPAE50C Trace Task Dispatch

- SPAE50D Trace SVC Return

## 3.1.9 Invalidate Page Table Entry Simulation - SPAB221

Routine SPAB221 receives control from the PSA exit routine built on the first occurrence of the instruction. On entry, two registers have been loaded with the instruction operands and a third with the routine base register. The fourth register has been loaded by a BAL that calls the simulation routine, to provide the condition code on entry. (See appendix A for details of the PSA exit.)

A PURGE TLB (PTLB) is done immediately upon entry to allow the purge to execute asynchronously. After setting the recursion indicator (PSAPCFB4), input operand values are used to locate the proper page table entry to be marked invalid. If the issuer of the instruction was not in key zero, a SPKA is done to enter user key, and the page table entry is marked invalid. After housekeeping, return is made directly to the caller via the resume PSW.

#### 3.2 3033 EXTENSION (3033E, XF) SUPPORTED INSTRUCTIONS

All of the 3033 Extension supported instructions have X'B2' opcodes. After housekeeping at entry point IEAVEXM1, the second byte of the opcode is retrieved, validity checked (it must be between X'21' and X'2B'), multiplied by 4 and used as an index into a table. The table contains the addresses of the various simulation routines for the B2 opcodes.

# 3.2.1 Program Call Simulator - SPAB218A

After setting the recursion indicator, SPA checks to ensure the caller has translate on and is not in secondary mode. The instruction operand is then decoded, with a fast path if the operand is 'O(R2)', the MVS convention. If the fast path is not used, the base register (if any) is retrieved and the displacement (if any) added in.

The program call number (PCN) is now translated, in a process very similar to virtual address translation. After ensuring that PCN translation is allowed (bit 8 of CR5), the Linkage Index (LX) is isolated from bits 17-23 of the PCN, and used as an index to the proper Linkage Table Entry to retrieve the Entry Table Origin. The low-order byte of the PCN is used as an Entry Index (EX) into the Entry Table, and byte four of the located Entry Table Entry (ETE) is then checked

MVS/SP Assist Release 1.0 Software Logic Manual Licensed Material - Property of Amdahl Corporation

for zero. If the caller is in supervisor state, the PCN translation process is now complete. If the caller is in problem state, the Entry Key Mask in the ETE is checked to see if he is authorized to invoke that particular program call function. If so, translation is complete. (If not, a Privileged Operation exception is generated.)

Next, the routine handles address space switching requirements. If the destination ASID field in the ETE is non-zero, switching is required and the ASID is used as input to the ASN translation process to locate the proper ASN Second Table Entry (ASTE) that contains all the new address space's control information. (Paragraph 3.2.10 describes the ASN translation process.) When the ASTE is returned, the following status changes are made:

- The current primary address space is made the secondary.

- The Linkage Table Designator address (CR5) is set from the ASTE.

- The new Authorization Index (AX) is set from the ASTE.

- If required, a Space Switch Event is noted for later processing.

- The new STO is loaded into CR1.

- The old primary ASID is put into general register 3.

If space switching is not required, the primary address space is also made the secondary, and the old primary ASID is put into general register 3.

At this point, any address space switching and/or housekeeping that is required has been done, and all that is left is program linkage. General register 14 is loaded with the address of the next instruction after the Program Call (the program old PSW instruction address), and the low bit of the register is set to correspond to the PSW problem state bit. The old Program Key Mask (PKM) is OR'd with the Entry Key Mask from the ETE to create the new PKM. General register 4 is loaded with the latent parm word from the ETE. The resume PSW instruction address is then set to the entry point address of the invoked routine. If the new routine is to run in problem state (ETE byte 7, bit 7 is 1), the problem bit is set on in the resume PSW. At this point the actual program call processing is done. If the MVS system trace is disabled, a check is made for the Space Switch Event required flag. If on, an SSE is simulated. If not, exit is made to the new routine via the resume PSW. If tracing is enabled, a trace table entry is made in the same manner as for the EF trace instructions, as described in paragraph 3.1.8. (The format of the entry is given in figure 3-1). Processing then continues as if trace was disabled.

Chapter 4 contains a flowchart of this process.

3-8

### 3.2.2 Set Address Space Control Simulator - SPAB219A

If the caller has translate on, the instruction operand is decoded, the base register (if any) retrieved and the displacement (if any) added in. If bits 20-23 of the resulting address are zero, the request is for primary mode, and the XM mode flag (PSAXMODE) is zeroed to set the mode, the primary STO is loaded to CR1, and control returns to the caller.

If bits 20-23 are not zero, bits 20-22 are checked to ensure that they are zero. If so, the request is a valid request for secondary mode, the XM mode flag is set to X'80' (secondary mode), and the secondary STO is loaded to CR1. Control then returns to the caller. If bits 20-22 are not zero, a specification exception is simulated.

#### 3.2.3 Insert Virtual Storage Key Simulator - SPAB223A

After setting the recursion indicator (PSAPCFB4) and ensuring the caller has translate on, the instruction second operand is decoded and the resulting virtual address is tested for validity. If a valid translation does not exist, the page is referenced and the ensuing program check is reflected to the program FLIH for resolution.

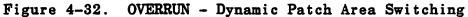

If the address has a valid translation, the real address from the translation is checked to see if it is over the 16Mb boundary, meaning Extended Addressing is active. If so, bit 4 of the PSW is turned on. An ISK is then done to get the storage key, and the first operand register is decoded and retrieved. If bit 4 of the PSW was turned on, it is now turned off. The retrieved operand value then has the retrieved key OR'd into it, and the result is stored back into the register or save area, as required. Exit is then made to the caller.

#### **3.2.4** Insert Address Space Control Simulator - SPAB224A

If the caller has translate on, the instruction operand is decoded and the register contents retrieved. The resume PSW condition code is set to zero, and the result byte from the instruction (byte 2 of the operand register) is also zeroed. If the CPU is in primary mode, the register is saved with the zero byte, and control returns to the caller. If the CPU is in secondary mode, the result byte is set to X'01' and condition code 1 is set before control is returned.

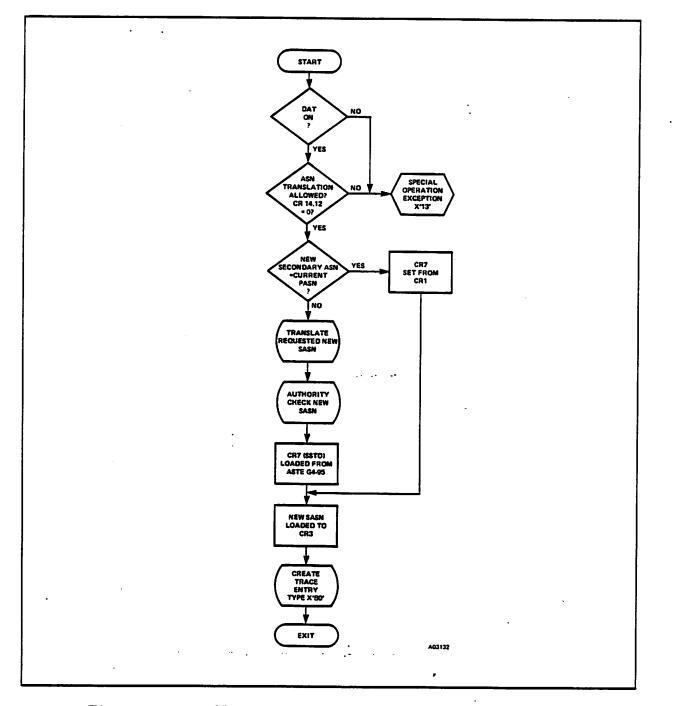

#### 3.2.5 Set Secondary ASN Simulator - SPAB225A

If the caller has translate on, the instruction operand register is decoded and retrieved, and the destination ASN is compared to the current primary ASN. If they are the same, and ASN translation is allowed, the secondary ASN and STO are set to the values of the primary.

MVS/SP Assist Release 1.0 Software Logic Manual Licensed Material - Property of Amdahl Corporation

If the destination ASN is not the same as the current primary, then the new ASN must be translated to obtain the necessary control information. Dat is turned off, and the ASN translate routine is called to ensure that the target ASN is a valid secondary address space for this user. (See paragraph 3.2.10 for an explanation of ASN translation and authorization checking.) If the ASN has a valid translation, the new secondary STO and ASN are copied from the retrieved ASTE and set into the proper control register images. If the CPU is in secondary mode, the new secondary STO is loaded to real control register 1.

If tracing is enabled, a trace table entry is made in the same manner as for the EF trace instructions, as described in paragraph 3.1.8. (The format of the entry is given in figure 3-1). After the trace table entry is created, or if trace is not active, control returns to the caller.

Chapter 4 contains a flowchart of this process.

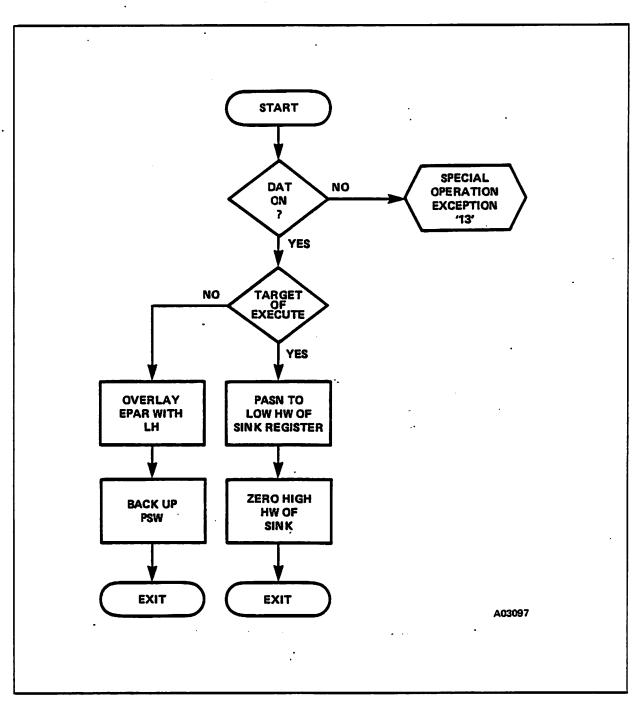

#### 3.2.6 Extract Primary/Secondary ASN - SPAB226A/SPAB227A

If the caller has translate on, and if the EPAR/ESAR is not the subject of an execute, the instruction is overlaid with a Load Halfword (LH) (since the operation of EPAR/ESAR in this case is identical to that of LH). The target register of the LH is that of the EPAR/ESAR and the displacement is that of the primary (EPAR) or secondary (ESAR) ASN in the PSA simulated control registers. After the patch has been built, DYNAMFIX is called to place the patch, and exit is made to the caller.

If the instruction is EXECUTEd, it cannot be overlaid and must be decoded and simulated each time it is encountered. The destination register is decoded, the proper ASN set into it, and return made to the caller.

#### 3.2.7 Program Transfer Simulator - SPAB228A

If the caller has translate on and is not in secondary mode, the instruction operand is decoded, with a fast path if the operand is 'R3,R14', the MVS convention. The state requested by the issuer in the low bit of the second operand is checked to ensure the caller has not requested a transfer to supervisor state from problem state.

The simulation next handles address space switching. If the destination ASID field in the first operand (low halfword) is the same as the current primary, space switching is not required, and the resume PSW instruction address is set from the second operand, secondary ASN and STO are set to those of the primary, and the proper state (supervisor or problem) is set. Trace and Space Switch Events are then checked.

3-10

If space switching is required, the destination ASID is used to locate the proper ASN Second Table Entry (ASTE) that contains all the new address space's control information. Authorization checking is done to ensure that this caller is authorized to use the requested address space as a primary address space. Paragraph 3.2.10 describes the ASN translation and authorization process. When the ASTE is returned, the following status changes are made:

- The Linkage Table Designator address (CR5) is set from the ASTE.

- The new Authorization Index (AX) is set from the ASTE.

- If required, a Space Switch Event is noted for later processing.

- The new STO is loaded into CR1 and set into simulated CR1 and CR7.

- Supervisor or problem state is set as requested.

- The primary and secondary ASN are set to the requested new ASN.

- The PKM is reset to what it was on entry to the PC.

- The resume PSW instruction address is set from the second operand.

If a Space Switch Event is required, a flag is set for later inspection.

If the MVS system trace is disabled, a check is made for the 'Space Switch Event Required' flag. If on, an SSE is simulated. If not, exit is made to the new routine via the resume PSW. If tracing is enabled, a trace table entry is made in the same manner as for the EF. trace instructions, as described in paragraph 3.1.8. (The format of the entry is given in table 3-1.)

Chapter 4 contains a flowchart of this process.

Ŧ

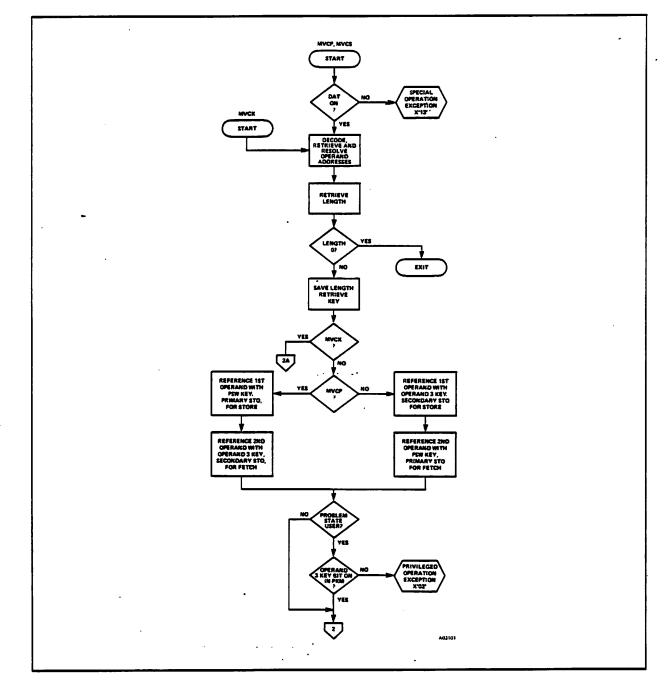

3.2.8 Move to Primary and Move to Secondary Simulations - MVCXCOMM

Routine MVCXCOMM receives control when an MVCP or MVCS opcode (X'D9' or X'DA') is encountered. If the caller has translate on, the instruction operands are decoded, the base registers (if any) are retrieved and the displacements added in. (The length register is decoded, retrieved, and saved into a work area for use in setting the condition code at the end of the simulation.) If the length was zero, the move is a NOP and control returns to the caller with condition code zero. If the length is greater than 256, it is set to 256, then decremented by one for working purposes. The key register, used for access checking for the secondary space operand, is then decoded and retrieved.

MVS/SP Assist Release 1.0 Software Logic Manual Licensed Material - Property of Amdahl Corporation

At this point, the source and sink data operands must be checked for accessability. There must be a valid translation for the addresses, and the storage keys must agree with the PSW key or secondary key, as required. There are four routines that do the checking, depending on the instruction being simulated and whether the CPU is in primary or secondary mode. The simulation is optimized for MVCS in primary mode, by far the most common simulation. The checking involves testing both ends of the operand for access, using the proper keys and segment table. The routines that do the checking, and the origin of the keys and STOs are:

- MVCP, primary mode after label MVCPPORS

- Operand 1 PSW key, Active STO

- Operand 2 R3 key, STO from CR7

- MVCP, secondary mode Label MVCPS

- Operand 1 PSW key, STO from CR1

- Operand 2 R3 key, Active STO

- MVCS, primary mode (No Label, fall through)

- Operand 1 R3 key, Active STO

- Operand 2 PSW key, STO from CR7

- MVCS, secondary mode Label MVCSS

- Operand 1 R3 key, STO from CR1

- Operand 2 PSW key, Active STO

If there is no valid translation for part of the data, or the keys do not match, a program check occurs that will be handled by IEAVEXM2.

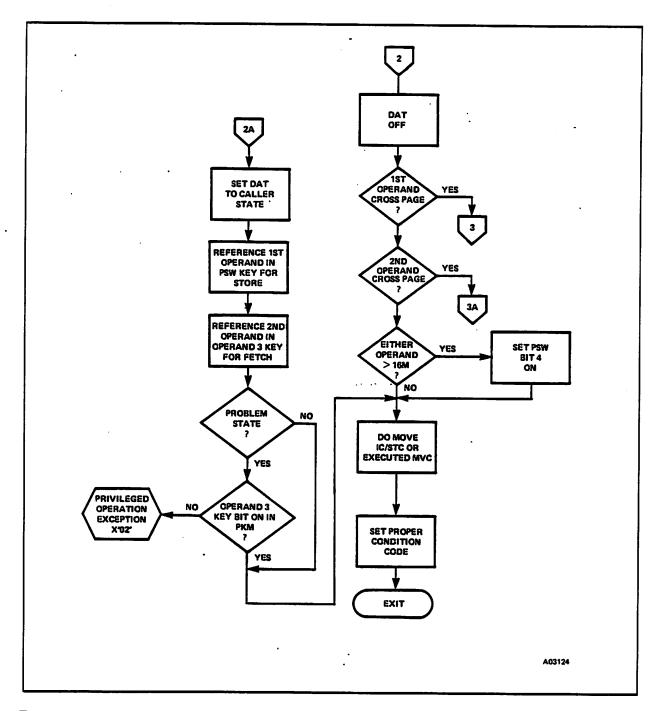

If the caller is in problem state, and is not allowed to use the secondary space key, a protection exception is generated. If the user is authorized, or in supervisor state, DAT is turned off and the operands are checked for page crossing. If the move is one byte the page crosser checking is skipped.

After page crossing checks, there are extended addressing checks. If extended addressing is active on the system (determined from the inspection of PSAHWFB) and either of the operand addresses is above the 16Mb boundary, bit 4 of the PSW is turned on to allow the accessing of the high storage.

3 - 12

The move is then simulated by either an EXECUTEd MVC or an IC/STC sequence (for one byte moves). Condition code 3 is set if the original length was greater then 256; otherwise, condition code zero is set. Control then passes to the resume exit.

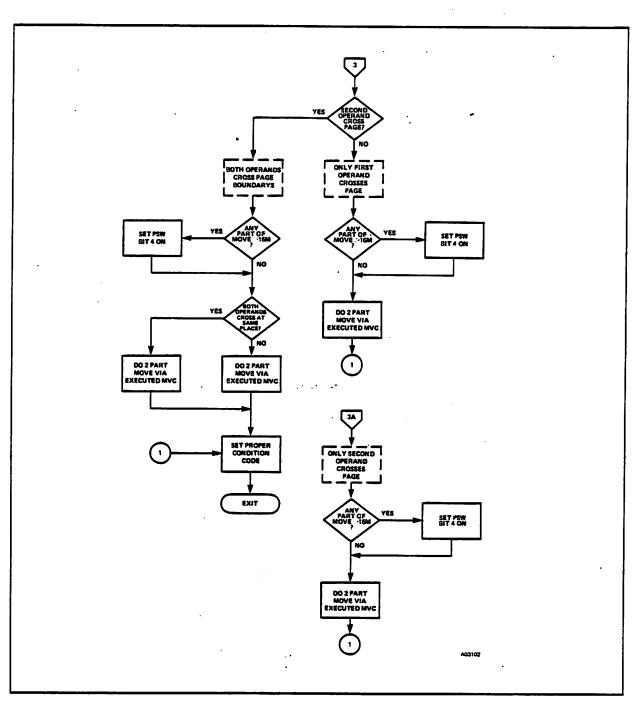

If a page crosser has been detected, further processing depends on which operand(s) crossed. If only one crossed, the move is done with two EXECUTED MVCs. If both operands crossed, three moves are required. In all cases, the addresses involved are checked for residence above the 16Mb boundary, and PSW bit 4 turned on before the moves if a high address has been found.

### 3.2.9 Move With Key Simulation

The initial part of the MVCK simulation is common with that for the MVCP and MVCS simulations up to the point that the operands are decoded and retrieved. After the key register has been retrieved, the simulation becomes unique to MVCK. The MVCK instruction uses only one segement table, so the checking with different segment tables for access is not required. Also, DAT is not required to be on. Since page crossing checks are not required, it is only necessary to access the first and last byte of each operand in the proper key. (A check for page crossing is not needed because moves are done DAT on or DAT off, depending on the caller's mode, so all storage will be logically contiguous. The other XF moves are always done DAT off, so this will not usually be the case for them.) The first operand key is checked with the PSW key, and the second with the R3 key. If one of the keys is improper, or if DAT is on and access to of one of the operands causes a page fault, the resulting program check is reflected to the original instruction by IEAVEXM2.

If the user is in problem state, the R3 key is checked against the PSW key mask. When all checks have been successfully passed, the move is done with an EXECUTEd MVC, the proper condition code is set (depending on the length register), and control returns to the caller via the standard resume exit.

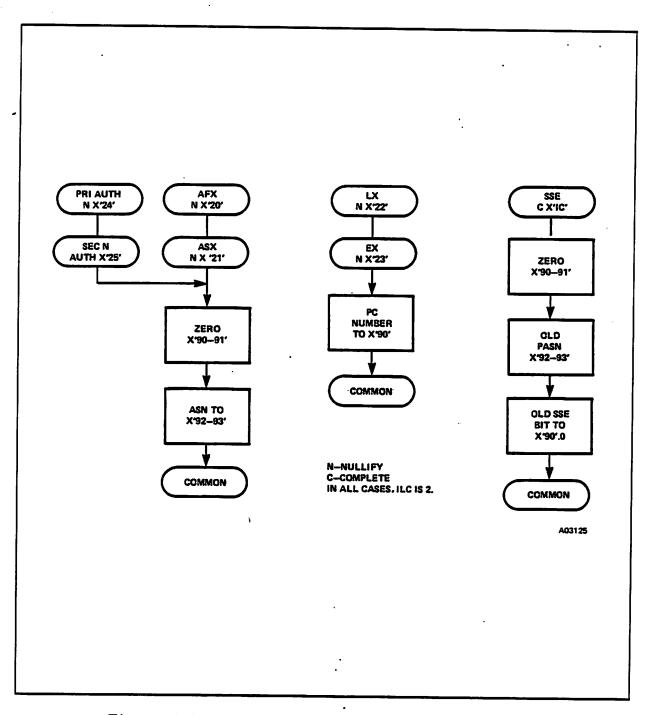

### 3.2.10 ASN Translation and Authorization - ASNTRAN

The ASN translation routine is called by the Program Call, Program Transfer and Set Secondary ASN simulation routines when a space switch is required. The ASNTRAN routine takes as input an ASN (ASID), and using the ASN translation tables built during IPL, returns an ASTE that contains information about the target address space. This information includes such things as the segment table origin address and the LTD, AX and Authority Table Origin.

The ASN translation process is similar to that of a virtual to real address translation. The index into the ASN First Table (AFT) is the high ten bits of the ASN, called the AFX. The AFX is multiplied by 4

MVS/SP Assist Release 1.0 Software Logic Manual Licensed Material - Property of Amdahl Corporation

to provide the offset into the AFT to locate the AFTE. The start of the AFT, the AFTO, is contained in CR14 bts 12-31, and is the same for all users of the system. If bit 12 is zero, translation is not allowed, and a special operation exception is generated.

The valid/invalid bit of the AFTE is first inspected, and then the AFTE itself is format checked. If it passes these tests, the AFTE is used as the start of the AST (ASN Second Table). The low-order 6 bits of the ASN are multiplied by 16 to get the index into the second table (ASX), and are added to the ASTO obtained from the AFTE. The result is a pointer to the ASTE, the ASN Second Table Entry. The ASTE is then format checked, and if the format is valid and the invalid bit is not on, the translation process is complete.

If the translation was performed for the Program Call simulation, the process is complete and control returns to the simulation routine. If the call was from PT or SSAR (the caller is identified from the value in PSAPCFB4), ASN authorization checking is required. This process ensures that the issuer of the PT or SSAR is authorized to request the address space he has specified in the instruction as either a primary or secondary space, respectively.

ASN authorization involves locating the Authorization Table Origin (ATO) from the ASTE, and indexing in using the caller's AX to do the actual check. Each byte in the AT (Authorization Table) contains information for four AX's. The AX is divided by 4 to locate the proper byte, and the proper pair of bits is located from the last two bits of the AX. For primary authorization, the first of the pair must be one; for secondary the second bit must be one. The proper bit is calculated and a TM instruction is EXECUTEd to perform the check. If the check passes, control returns to the appropriate simulation routine. Otherwise, an authorization exception is generated.

Chapter 4 contains a flowchart of this process.

# 3.3 EXTENDED ADDRESSING (EA) SUPPORTED INSTRUCTIONS

Extended Addressing on the Amdahl 470 rests on three assumptions:

- 1. Storage key instructions operate only in 4K mode.

- 2. Turning on bit 4 of the PSW enables 31-bit real addressing.

- 3. The Extended Memory hardware feature is installed.

MVS/SPA expects all three conditions to be met. (A modification to IEAVNIPO ensures that the appropriate hardware features are enabled if present.)

3-14

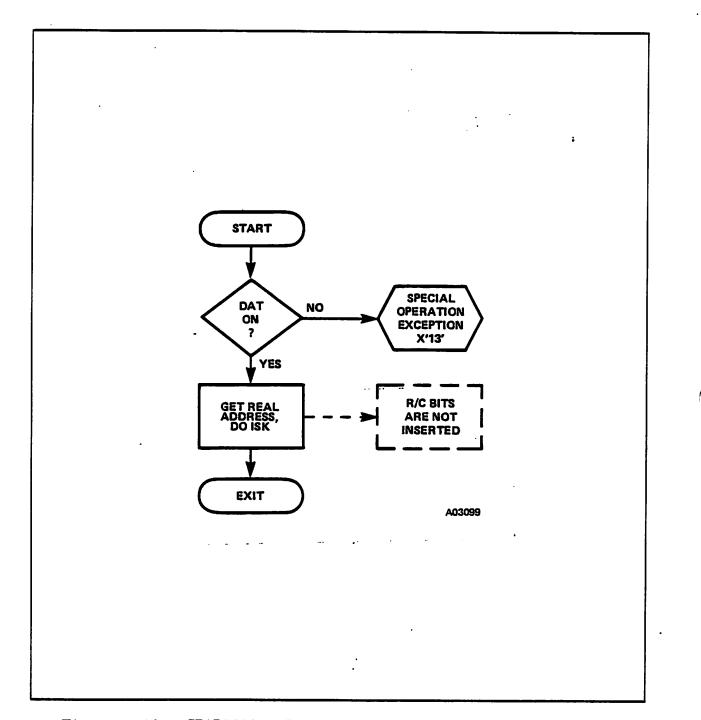

#### 3.3.1 Insert Storage Key Extended Simulator - SPAB229A

First, the instruction operand registers are decoded and their contents retrieved. Then bit 4 of the PSW is turned on if required, an ISK is done to get the storage key, and PSW bit 4 is turned off. The retrieved first operand is used as the first operand of the ISK, and the second operand provides the address to use. After the ISK, the first operand register is stored back into the proper location, and control the returns to the caller from the resume exit.

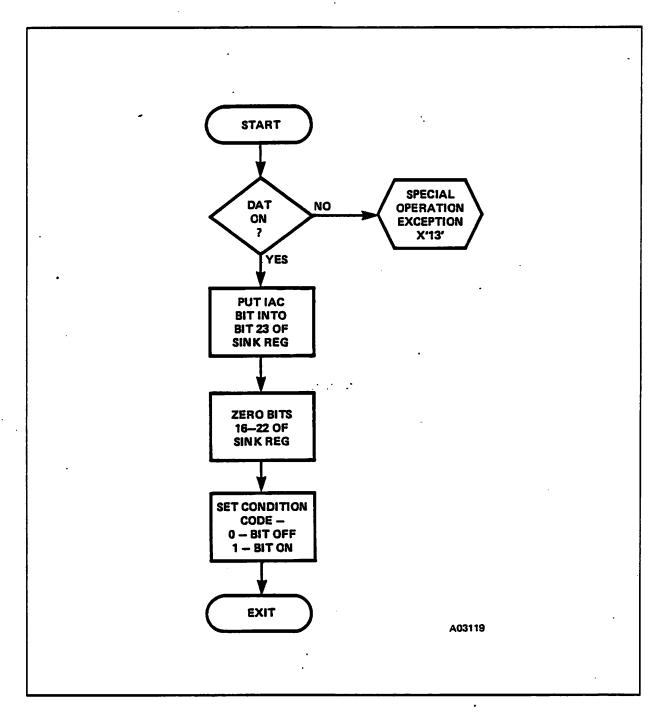

### 3.3.2 Reset Reference Bit Extended Simulator - SPAB22AA

First, the instruction operand register is decoded and its contents retrieved. Then bit 4 of the PSW is turned on if required, and an RRB is done to set the condition code and reset the reference and change bits. The resulting condition code is then set into the resume PSW, and control passes back to the caller from the resume exit.

### 3.3.3 Set Storage Key Extended Simulator - SPAB22BA

First, the instruction operand registers are decoded and their contents retrieved. Then bit 4 of the PSW is turned on if required, an SSK is done to set the storage key, and PSW bit 4 turned off. Control then returns to the caller from the resume exit.

#### 3.4 IPK/SPKA IN PROBLEM STATE

Part of the implementation of the DAS feature is the changing of the two PSW key handling instructions, Insert PSW Key and Set PSW Key From Address, from privileged instructions to 'semi-privileged'. With appropriate authorization, any problem program is now allowed to use these instructions. A CPU without the DAS feature will not support this execution, and causes a privileged operation exception (interrupt code X'02'). This exception is detected and reflected to IEAVEXMS to handle. Routine CHECKP12 is given control when a privileged operation exception is detected. It then chooses the proper simulation routine to receive control.

### 3.4.1 Insert PSW Key Simulator

The IPK simulator sets the key from the program old PSW into the low byte of register 2, and then ANDs out the low nibble. No authorization checking is done, as the only requirement is extraction authority. Control is then returned to the caller via the standard resume exit.

MVS/SP Assist Release 1.0 Software Logic Manual Licensed Material - Property of Amdahl Corporation

# 3.4.2 Set PSW Key From Address Simulator

The SPKA simulator decodes the operand register, and if non-zero, retrieves its contents and adds in the displacement to obtain the requested new PSW key. The bit in the PSW key mask corresponding to the new key is checked. If it is one, the new key is placed into the resume PSW key field, and control returns to the user via the resume exit. If the PSW key mask bit is zero, the original privileged operation exception is reflected back to normal RTM processing through the error exit.

### 3.5 EXIT PROCESSING

The simulation routines and the recursion routine will exit either directly back to the caller, in the case of a successful simulation, or to the program check FLIH in the event of an error detected during format checking, operand validation in a simulation, a Space Switch Event or a PER event. Due to MVS/SPA being imbedded in the program check handler, some housekeeping must be done to avoid problems in either case.

#### 3.5.1 Resume Exit

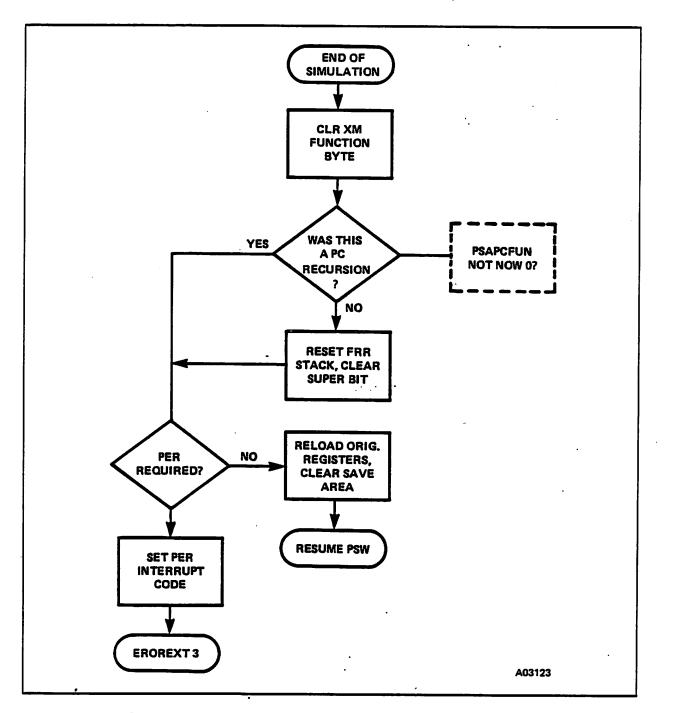

The resume exit is used after a successful simulation to return control to the instruction stream as directed by the simulation. The point of return is either the next sequential instruction after the one being simulated, or another location. The resume exit will first clear out the recursion indicator byte, PSAPCFB4, to ensure that IEA-VEXM2 will not receive control for program checks not related to SPA processing. If the program check that initiated the simulation was not a recursion, the FRR stack is reset to what it was on entry. (The program FLIH had set it to the program check handler stack.) The PI super bit is then reset to avoid the next program check being considered a recursion. If one of the other bits was on in the program check status word (PSAPCFUN), the SUPER bit and FRR stack are not reset. (An example of this would be an occurrence of an EF 'Trace Program Interrupt' instruction.) Checking is now done to see if a PER event was reported with this interrupt. If so, the rest of the interrupt code is zeroed out, and the error exit routine is called at label EROREXT3. If no PER interrupt was indicated, the SPA control flag is reset, as it is only valid during simulation. The caller's registers are then reloaded, and control returns by LPSW of the resume PSW prepared by the simulation routine or low core trap.

### 3.5.2 Error Exit

The error exit is used when control must be passed on to the program FLIH and/or RTM. Some of these cases are:

A simulation routine has detected an error in an operand.

3-16

- An instruction has been issued in an improper environment.

- An interrupt was passed to IEAVEXMS that it can not process.

- A page fault has been encountered accessing an operand.

- A Space Switch Event is to be signaled.

- A PER event has occurred.

There are five points of entry into the error exit, depending on the processing required. Each falls through to the next.

- 1. EROREXIT PSA protection is disabled.

- 2. EROREXT1 The resume PSW is made the program new PSW.

- 3. EROREXT2 The PSW address set in the program old PSW is checked to ensure that it is not the address of the work area where the target instruction of an EXECUTE has been built.

- 4. EROREXT3 PSA protection is re-enabled.

- 5. EROREXT4 The remainder of the exit processing.

The specific entry points are called as required, depending on what part of the exit processing has already been done by the simulation routine or is already correct.

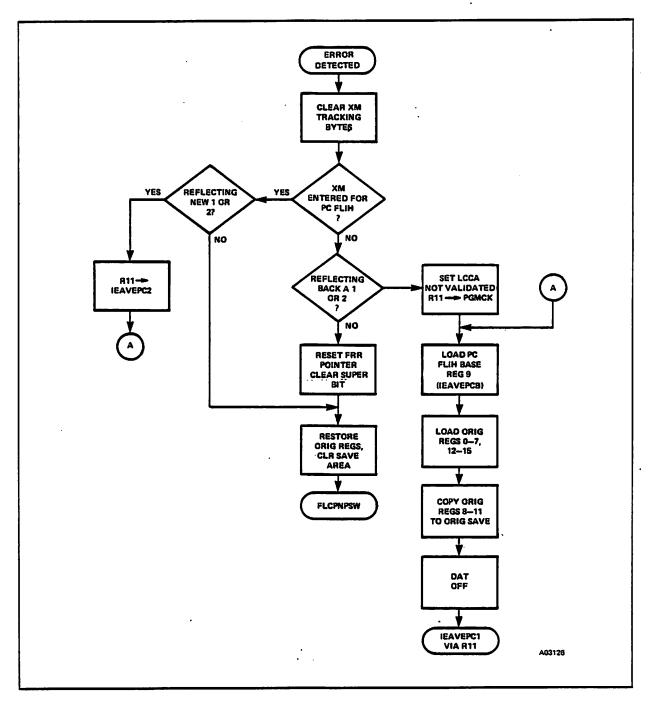

The remainder of the exit processing is primarily MVS housekeeping and clean-up. The SPA control flag and recursion bytes are cleared, and the rest of the program check recursion word (PSAPCFUN) is checked to see if the program check that resulted in the entry to IEAVEXMS was a true recursion. If not, the program interrupt code being passed on is checked for an operation exception or a privileged operation exception. If the interrupt is not to be either of these, the previously current FRR stack is restored to the current, and the program interrupt handler SUPER bit is turned off. The caller's registers then are restored and the program new PSW loaded, entering normal program check processing. If the interrupt being passed back is one of the two, a special entry point in the program check FLIH (IEAVEPC1) is used to ensure that the interrupt is not routed back to IEAVEXMS in a loop. The program FLIH base address is set into register 9, (entry IEA-VEPCB), the special entry point address into register 11, the 'LCCA not validated' bit is set (program FLIH housekeeping), the user's registers are copied to the program FLIH register save area, DAT is turned off if it is on, and the FLIH is branched to.

MVS/SP Assist Release 1.0 Software Logic Manual Licensed Material - Property of Amdahl Corporation

If the interrupt being passed back is from an instruction in the program check handler itself, the recursion return point must be used. Recursion exit processing is identical to that of the non-recursion processing, save that if the interrupt to be passed is a 1 or 2, the entry point IEAVEPC2 is used.

### 3.5.3 Setting Exceptions

When a simulation exit detects a format, environment or other error, the program interrupt to be generated is usually not the same as the current interrupt code indicated. In that case, the simulation branches to an exception creation routine that sets up the proper interrupt code and instruction length code.

The exception creation routines restore registers 12-15 if requested and then disable PSA low storage protection. The new interrupt code is then set, including the PER bit if it was on in the original interrupt. The ILC is set to either the length of the instruction or zero, depending on whether the definition of the new interrupt causes suppression or nullification, respectively. The PSW is also backed up if required to agree with the ILC. In some cases a translation exception address is set. Control then passes to the normal error exit at label EROREXT1.

# 3.6 SPA RECURSION ROUTINE - IEAVEXM2

Entry point IEAVEXM2 is called directly from the program FLIH when a program check occurs and a non-zero value has been set into field PSAPCFB4. (PSAPCFB4 is the one-byte field that is used as an indicator of which simulation routine is running.) The various values that can be put in this field are given in table 3-2.

IEAVEXM2 first checks to see if a TPROT instruction was being simulated; if so, the proper condition code is set into the resume PSW to reflect the cause of the interruption: a page or segment fault or a protection exception. If another type of exception occurred, the exception is reflected back to the program check handler through the normal error reflection exit (see paragraph 3.5.2).