# DEP

Ľ

ľ

# DECISION PROCESSOR

CHAPTER 6

#### 6.0 INTRODUCTION

The DEP executes comparison and modification instructions involving two 128 word register files within the DEP. One of these register files is shared with the MAP and is used by the MAP for indexed addressing. This allows the DEP, through a logical decision process, to cause the MAP to access data from arrays stored in DATA MEMORY in a very efficient manner.

# 6.1 ORGANIZATION OF THE DEP

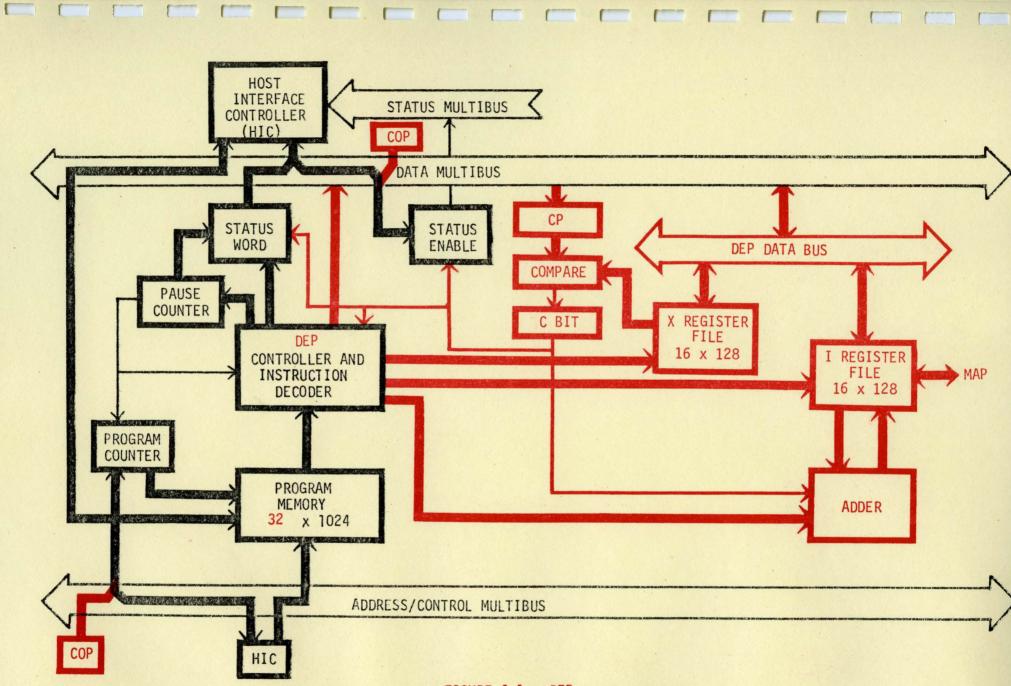

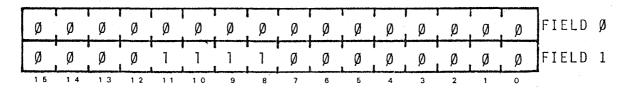

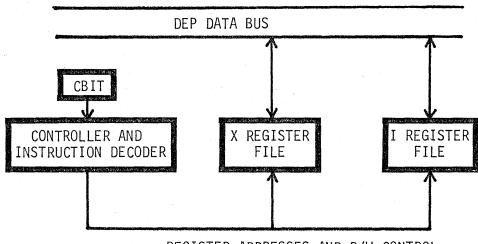

Figure 6.1 provides a general block diagram of the DEP. That part of Figure 6.1 which is in black is common to all processors and is described in Section 2.6. The elements in Figure 6.1 which are in red are those which are unique to the DEP.

The DEP is physically located on the same circuit card assembly which contains the Memory Address Processor (MAP). The I Register File shown in Figure 6.1 is shared between the DEP and the MAP in the sense that this file may be accessed by either processor. These operations of MAP and DEP are transparent and fully overlapped. See Chapter 7 for more information on this subject.

In Figure 6.1 a connection is shown in red from the Control Processor (COP) to the Processor Status Enable Register via the DATA MULTIBUS. A similar connection is shown from the COP to the Program Counter through the ADDRESS/CONTROL MULTIBUS. The contents of the Processor Status Enable Register and the Program Counter can be modified by COP program instructions when the AD 10 is in the run mode.

Sections 6.2.3 through 6.2.7 contain diagrams showing the parts of the DEP which are involved with each of the categories of DEP instructions.

#### 6.1.1 Processor Address

The processor address for the DEP is  $\emptyset 2$ .

FIGURE 6.1 DEP BLOCK DIAGRAM

| СМР     | CBIT  | Ø    | Ø    | Ø    | Ø    | А           | Р     | Ø          | Ø    | Ø              | Ø    | Ø    | PAL  | JSE  | ÇNT    |         |

|---------|-------|------|------|------|------|-------------|-------|------------|------|----------------|------|------|------|------|--------|---------|

| 15      | 14    | 13   | 12   | 11   | 10   | 9           | 8     | 7          | 6    | 5              | 4    | 3    | 2    | 1    | 0      |         |

| BIT     |       | D    | ESCR | IPTI | ON   |             |       |            |      |                |      |      |      |      |        |         |

| Ø-2     |       |      |      |      |      | se C        | ount  |            |      |                |      |      |      |      |        |         |

| 3-7     |       |      | nass | •    |      |             |       | <b>م</b> ل |      |                |      |      |      |      |        |         |

| 8<br>9  |       |      |      |      |      | t wh<br>whe |       |            |      |                |      |      |      |      | •      |         |

| 1ø-1    | 3     |      | nass |      |      | whe         | 11 30 |            |      |                |      |      |      |      |        |         |

| 14      |       |      |      |      |      | ind         | icat  | es t       | he r | esul           | t of | the  | las  | t co | ompare |         |

|         |       |      | nstr |      |      |             |       |            |      |                |      |      |      |      |        |         |

| 15*     |       | I    | fa   | comp | are  | inst        | ruct  | ion        | has  | been           | per  | form | ed,  | this | s bit  | is set. |

| * 0     | nce s | set, | thi  | s bi | t re | main        | s se  | t un       | til  | clea           | red  | by a | REA  | Dop  | perati | on.     |

| The     | DEP F | roc  | esso | r St | atus | Wor         | d (P  | SW)        | cont | ains           | inf  | orma | tion | on   | the c  | urrent  |

|         | us of |      |      |      |      |             | -     | -          |      |                |      |      |      |      |        | . •     |

| 2 6 6 6 | us 01 | un   |      | •    | ine  | 1 3 14      | 13 u  | rea        |      | <u>1</u> y 1 1 | eyrs | CCI. |      |      |        |         |

6.1.3 Processor Status Enable

| E<br>1         | E<br>Ø  | Ø  | Ø            | Ø           | Ø          | Ø | Ø | øø               | Ø | ø | Ø | ø | Ø | ø |

|----------------|---------|----|--------------|-------------|------------|---|---|------------------|---|---|---|---|---|---|

| 15<br>BI       | 14<br>T | 13 | 12<br>DESC   | 11<br>RIPT  | 10<br>FION | 9 | 8 | 76               | 5 | 4 | 3 | 2 | 1 | 0 |

| Ø-<br>14<br>15 | 13      |    | Unas<br>Enat | sigr<br>les | ned<br>the |   |   | n CBIT<br>n CBIT |   |   |   |   |   |   |

The Processor Status Enable Register (PSE) is a <u>write-only</u> register. This register has the same address as the DEP Processor Status Word.

# 6.1.4 Program Memory

The DEP program memory contains 1,024 words. Each 32-bit instruction word is divided into two 16-bit fields. A DEP instruction is normally loaded as a sequence of two 16-bit words (one per field) from the host processor. However, each field is individually addressable and can be accessed from the host processor for a READ or WRITE operation.

6-3

# 6.2 THE DEP INSTRUCTION SET

# 6.2.1 DEP Instruction Word Format

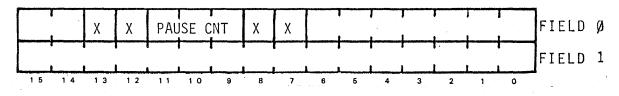

The DEP instruction word format is:

The bits labelled "X" in the above diagram are unused. The unused bits cannot be set and are always read as a  $\emptyset$ .

The categories of DEP instructions are:

COMPARE Instructions LOAD IMMEDIATE DATA Instructions LOAD CONDITION Instructions LOAD/STORE REGISTER Instructions MOVE REGISTER Instructions PAUSE/NOP Instructions

6.2.2 Microprogramming DEP Instructions

Figure 6.2 provides a summary of the DEP instruction set. This summary has been organized into several groupings of instructions to indicate as clearly as possible the microprogramming possibilities which exist.

A DEP instruction can consist of any of the following:

- a.) <A> <PAUSE>

- b.) <B> <PAUSE>

- c.) <C> <D> <PAUSE>

- d.) <C> <E> <PAUSE> (See Note 1.)

- e.) <CC><DC><PAUSE>

- f.) <CC><EC><PAUSE> (See Note 2.)

6-4

FIELD Ø

FIELD 1

| PAGE GROUP STAATSONNOGANNOG                                                                                                             | 01534567899111123452<br>015345678991123452 |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 6-9 CMM (A) 1ØXXØØØXX ← INDEX→                                                                                                          | ← I N C R E M E N T →                      |

| 6-10 CMP (A) $\emptyset$ 1 X X $\emptyset \emptyset \emptyset$ X X $\leftarrow$ I N D E X $\rightarrow$                                 | ← INCREMENT→                               |

| 6-13 LDI (B) 1 1 X X Ø Ø Ø X X Ø Ø Ø Ø Ø 1 1                                                                                            | ←IMMEDIATE DATA→                           |

| 6-14 LFI (B) 1 1 X X Ø Ø Ø X X Ø Ø Ø Ø Ø Ø 1 Ø                                                                                          | ←IMMEDIATE DATA→                           |

| 6-15 LSI (B) 1 1 X X Ø Ø Ø X X Ø Ø Ø Ø Ø Ø 1                                                                                            | $\leftarrow$ IMMEDIATE DATA $\rightarrow$  |

| 6-25 LIF (C) ØØX XØØØX X ←S O U R C E→                                                                                                  | 110100000000000000                         |

| 6-21 LTCF (C) ØØXXØØØXXØØØØØØ                                                                                                           | 111100000000000000                         |

| 6-33 LXF (C) ØØX XØØØX X ←S O U R C E→                                                                                                  | 111000000000000000                         |

| 6-29 SIF (C) ØØX XØØØX X ←DESTINATION→                                                                                                  | Ø111ØØØØØØØØØØØØØ                          |

| 6-37 SXF (C) ØØX XØØØX X ←DESTINATION→                                                                                                  | 1 Ø 1 1 Ø Ø Ø Ø Ø Ø Ø Ø Ø Ø Ø              |

| 6-19 LCF (CC) ØØX XØØØX XØØØØØØ                                                                                                         | 1111000010000000                           |

| 6-26 LIFC (CC) ØØX XØØØX X ←S O U R C E→                                                                                                | 1101000010000000                           |

| 6-34 LXFC (CC) ØØX XØØØX X ↔S O U R C E→                                                                                                | 1110000100000000                           |

| 6-30 SIFC (CC) ØØX XØØØX X ←DESTINATION→                                                                                                | Ø111ØØØØ1ØØØØØØ                            |

| 6-38 SXFC (CC) ØØX XØØØX X ←DESTINATION→                                                                                                | 1 Ø 1 1 Ø Ø Ø Ø 1 Ø Ø Ø Ø Ø Ø              |

| 6-27 LIS (D) ØØX XØØØX XØØØØØØ                                                                                                          | ØØØØ11Ø1Ø +S O U R C E→                    |

| 6-22 LTCS (D) ØØX XØØØX XØØØØØØ                                                                                                         | ØØØØ1111ØØØØØØØØ                           |

| 6-35 LXS (D) ØØX X ØØØX X ØØØØØØ                                                                                                        | ØØØØ111ØØ                                  |

| 6-31 SIS (D) ØØXXØØØXXØØØØØØ                                                                                                            | ØØØØØ111Ø ←DESTINATION→                    |

| 6-39 SXS (D) ØØX X ØØØX X ØØØØØØØ                                                                                                       | ØØØØ1Ø11Ø ←DESTINATION→                    |

| 6-20 LCS (DC) ØØX XØØØX XØØØØØØ                                                                                                         | ØØØØ11111ØØØØØØØØ                          |

| 6-28 LISC (DC) ØØX XØØØX XØØØØØØ                                                                                                        | Ø Ø Ø Ø 1 1 Ø 1 1 +S O U R C E+            |

| 6-36 LXSC (DC) ØØX XØØØX XØØØØØØ                                                                                                        | ØØØØ11101+SOURCE→                          |

| 6-32 SISC (DC) ØØXXØØØXXØØØØØØ                                                                                                          | ØØØØØ1111 + DESTINATION→                   |

| 6-40 SXSC (DC) ØØX X ØØØX X ØØØØØØØ                                                                                                     | ØØØØ1Ø111 + DESTINATION→                   |

| 6-43 MII (E) $\emptyset \emptyset X X \emptyset \emptyset \emptyset X X \leftrightarrow S O U R C E \rightarrow$                        | ØØØØØ 1 Ø 1 Ø ←DESTINATION→                |

| 6-45 MIX (E) $\emptyset \emptyset X X \emptyset \emptyset \emptyset X X \leftrightarrow S O U R C E \rightarrow$                        | ØØØØ1ØØ1Ø ←DESTINATION→                    |

| 6-47 MXI (E) $\emptyset \emptyset X X \emptyset \emptyset \emptyset X X \leftrightarrow S O U R C E \rightarrow$                        | ØØØØØØ11ØØ ←DESTINATION→                   |

| 6-49 MXX (E) $\emptyset \emptyset X X \emptyset \emptyset \emptyset X X \leftrightarrow S O U R C E \rightarrow$                        | ØØØØ1Ø1ØØ ←DESTINATION→                    |

| 6-44 MIIC (EC) $\emptyset \ \emptyset \ X \ X \ \emptyset \ \emptyset \ \emptyset \ X \ X \leftarrow S \ O \ U \ R \ C \ E \rightarrow$ | ØØØØØØ1Ø11 ←DESTINATION→                   |

| 6-46 MIXC (EC) $\emptyset \emptyset X X \emptyset \emptyset \emptyset X X \leftrightarrow S O U R C E \rightarrow$                      | ØØØØÍØØ1 1 ←DESTINATION→                   |

| 6-48 MXIC (EC) $\emptyset \emptyset X X \emptyset \emptyset \emptyset X X \leftrightarrow S O U R C E \rightarrow$                      | ØØØØØ11Ø1 ←DESTINATION→                    |

| 6-50 MXXC (EC) $\emptyset \emptyset X X \emptyset \emptyset \emptyset X X \leftrightarrow S O U R C E \rightarrow$                      | ØØØØ1Ø1Ø1 ←DESTINATION→                    |

| 6-54 NOP ØØX X ØØØX X ØØØØØØ                                                                                                            |                                            |

| 6-53 PAUSE $\emptyset \emptyset X X \leftarrow d \rightarrow X X \emptyset \emptyset \emptyset \emptyset \emptyset \emptyset$           |                                            |

и 4 по 1 по 1

FIGURE 6.2 DECISION PROCESSOR INSTRUCTION SET

Note 1. If the instruction from group C is a register Load instruction, the source register for the Move instruction must be the same numerical address as the source register for the Load instruction. Thus,

> LIFn<sub>s</sub>; MIXn<sub>s</sub>,n<sub>f</sub> and LXFn<sub>s</sub>; MIXn<sub>s</sub>,m<sub>f</sub>

are both valid microprogrammed instructions. If the instruction from group C is a register store instruction, the source register for the Move instruction must have the same numerical address as the destination register for the Store instruction.

Note 2. The comments of Note 1 apply with each of the instructions from groups C and E replaced by their counterparts from group CC and EC respectively.

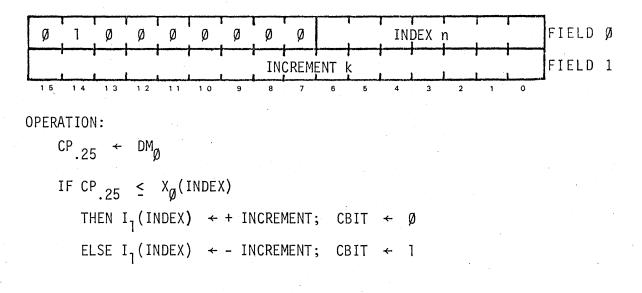

# 6.2.3 COMPARE INSTRUCTIONS

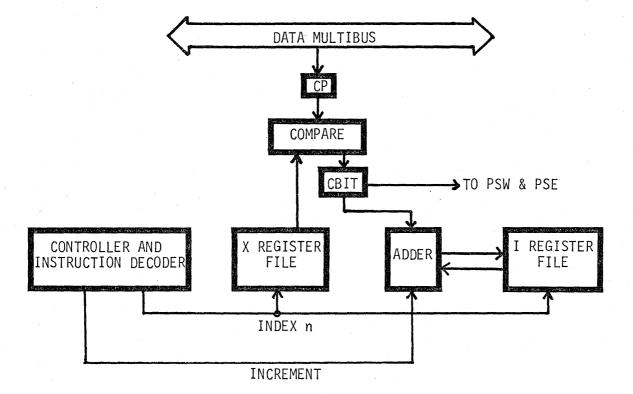

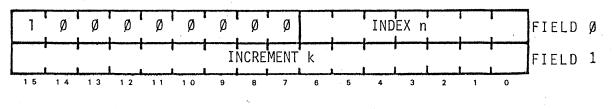

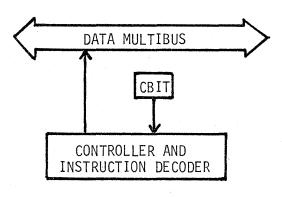

The DEP has two COMPARE instructions. That part of the DEP which is involved in COMPARE operations is shown below.

The COMPARE Instructions are:

- CMM Compare and Modify

- CMP Compare

CMM n,k

COMPARE AND MODIFY

**OPERATION:**

$CP_{.25} \leftarrow DM_{\emptyset}$

IF CP  $_{25} \leq X_{\emptyset}(INDEX)$

THEN  $I_1(INDEX) \leftarrow I_0(INDEX) + INCREMENT; CBIT \leftarrow 0$ ELSE IF INCREMENT  $\neq 0$ THEN  $I_1(INDEX) \leftarrow I_0(INDEX) - INCREMENT; CBIT \leftarrow 1$ ELSE  $I_1(INDEX) \leftarrow I_0(INDEX) - 1; CBIT \leftarrow 1$

ERROR CONDITION(S):

CBIT if enabled to the AER line.

DESCRIPTION:

The contents of the DATA MULTIBUS FIRST are saved in register CP. The contents of the specified X register are then compared with the contents of CP. If X register is greater than or equal to CP, the I register is incremented by INCREMENT; otherwise, it is decremented. If INCREMENT is zero, this instruction will increment by zero or decrement by one.

EXAMPLE:

CMM X1,8

6-9

#### CMP n,k

COMPARE

ERROR CONDITION(S):

CBIT if enabled to the AER line.

DESCRIPTION:

The contents of the DATA MULTIBUS FIRST are saved in register CP. The contents of the specified X register are then compared with the contents of CP. If X register is greater than or equal to CP, the I register is loaded with INCREMENT; otherwise it is loaded with -INCREMENT.

EXAMPLE:

. CMP X4,32

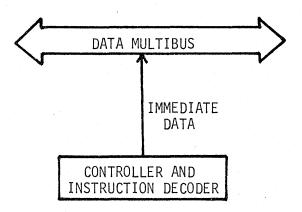

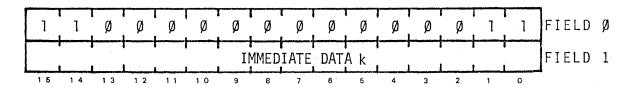

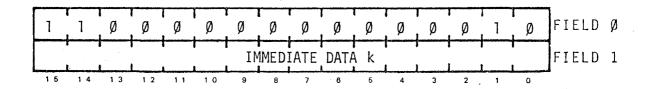

# 6.2.4 LOAD IMMEDIATE DATA INSTRUCTIONS

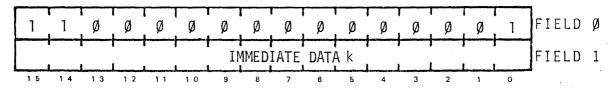

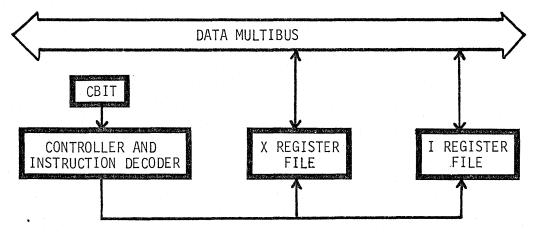

The DEP has three LOAD IMMEDIATE DATA instructions. That part of the DEP which is involved with these instructions is shown below.

The instructions are often used to load registers in the various register files (i.e., the I and X Register Files in DEP, the Temporary Register File in ARP, and the General Register File in COP).

The LOAD IMMEDIATE DATA Instructions are:

| LDI | Load | Double Immediate |

|-----|------|------------------|

| LFI | Load | First Immediate  |

| LSI | Load | Second Immediate |

LOAD DOUBLE IMMEDIATE

**OPERATION:**

DM<sub>1</sub> ← IMMEDIATE DATA

DM<sub>1.5</sub> + IMMEDIATE DATA

ERROR CONDITION(S):

BUS CONFLICT (DATA), if there is other data on the DM in the above specified BUS cycle.

**DESCRIPTION:**

The immediate data is placed on the DATA MULTIBUS FIRST and SECOND.

EXAMPLE:

LDI DATA

#### LOAD FIRST IMMEDIATE

**OPERATION:**

DM<sub>1</sub> ← IMMEDIATE DATA

ERROR CONDITION(S):

BUS CONFLICT (DATA), if there is other data on the DM in the above specified BUS cycle.

#### **DESCRIPTION:**

The immediate data is placed on the DATA MULTIBUS FIRST.

EXAMPLE:

. LFI DATA

# LOAD SECOND IMMEDIATE

**OPERATION:**

DM<sub>1.5</sub> + IMMEDIATE DATA

ERROR CONDITION(S):

BUS CONFLICT (DATA), if there is other data on the DM in the above specified BUS cycle.

**DESCRIPTION:**

The immediate data are placed on the DATA MULTIBUS SECOND.

EXAMPLE:

LSI DATA

# 6.2.5 LOAD CONDITION INSTRUCTIONS

The DEP has four LOAD CONDITION instructions. These four instructions are bit load instructions (i.e., they only affect bit 15 of the DATA MULTIBUS). The part of the DEP involved in these instructions is shown below.

The LOAD CONDITION Instructions are:

| LCF  | Load | Condi | tion  | First | t      |

|------|------|-------|-------|-------|--------|

| LCS  | Load | Condi | tion  | Secor | nd     |

| LTCF | Load | True  | Condi | ition | First  |

| LTCS | Load | True  | Condi | ition | Second |

#### LOAD CONDITION FIRST

**OPERATION:**

IF CBIT IS TRUE

THEN  $DM_1(15) \leftarrow 1$

ERROR CONDITION(S):

BUS CONFLICT (DATA), if there is other data on the DM in the above specified BUC cycle.

**DESCRIPTION:**

If the condition bit is true, bit 15 of the DATA MULTIBUS FIRST is set.

EXAMPLE:

. LCF

#### LOAD CONDITION SECOND

**OPERATION:**

IF CBIT IS TRUE

THEN  $DM_{1.5}(15) + 1$

ERROR CONDITION(S):

BUS CONFLICT(DATA), if there is other data on the DM in the above specified BUS cycle.

**DESCRIPTION:**

If the condition bit is true, bit 15 of the DATA MULTIBUS SECOND is set.

EXAMPLE:

. LCS

# LOAD TRUE CONDITION FIRST

**OPERATION:**

DM<sub>1</sub>(15) ← 1

ERROR CONDITION(S):

BUS CONFLICT (DATA), if there is other data on the DM in the above specified BUS cycle.

# DESCRIPTION:

Bit 15 of the DATA MULTIBUS is set.

EXAMPLE:

LTCF

• .

# LOAD TRUE CONDITION SECOND

**OPERATION:**

$DM_{1.5}(15) \leftarrow 1$

ERROR CONDITION(S):

BUS CONFLICT (DATA), if there is other data on the DM in the above specified BUS cycle.

#### DESCRIPTION:

Bit 15 of the DATA MULTIBUS SECOND is set.

EXAMPLE:

LTCS

•

# 6.2.6 LOAD/STORE REGISTER INSTRUCTIONS

The DEP has sixteen LOAD/STORE REGISTER instructions. The LOAD instructions are used to load data from an I register or an X register to the DATA MULTIBUS. Similarly, the STORE instructions are used to store data obtained from the DATA MULTIBUS into an I or an X register. That part of the DEP which is involved with these instructions is shown below.

REGISTER ADDRESS & R/W CONTROL

The LOAD/STORE instructions for the I registers are:

| LIF  | Load I First                 |

|------|------------------------------|

| LIFC | Load I First Conditionally   |

| LIS  | Load I Second                |

| LISC | Load I Second Conditionally  |

| SIF  | Store I First                |

| SIFC | Store I First Conditionally  |

| SIS  | Store I Second               |

| SISC | Store I Second Conditionally |

# The LOAD/STORE instructions for the X registers are:

| LXF  | Load X First                 |

|------|------------------------------|

| LXFC | Load X First Conditionally   |

| LXS  | Load X Second                |

| LXSC | Load X Second Conditionally  |

| SXF  | Store X First                |

| SXFC | Store X First Conditionally  |

| SXS  | Store X Second               |

| SXSC | Store X Second Conditionally |

LOAD I FIRST

**OPERATION:**

$DM_1 \leftarrow I_0(SOURCE)$

ERROR CONDITION(S):

BUS CONFLICT (DATA), if there is other data on the DM in the above specified BUS cycle.

DESCRIPTION:

The contents of the specified I  $% \left( {{{\mathbf{T}}_{{\mathbf{T}}}}_{{\mathbf{T}}}} \right)$  register are placed on the DATA MULTIBUS FIRST.

EXAMPLE:

•

LIF I4

# LIFC nf

# LOAD I FIRST CONDITIONALLY

**OPERATION:**

IF CBIT IS TRUE

THEN  $DM_1 \leftarrow I_{\emptyset}(SOURCE)$

ERROR CONDITION(S):

BUS CONFLICT (DATA), if there is other data on the DM in the above specified BUS cycle.

DESCRIPTION:

If the condition bit is true, the contents of the specified I register are placed on the DATA MULTIBUS FIRST.

EXAMPLE:

LIFC I4

.

LOAD I SECOND

**OPERATION:**

$DM_{1.5} \leftarrow I_{.5}(SOURCE)$

ERROR CONDITION(S):

BUS CONFLICT ( DATA), if there is other data on the DM in the above specified BUS cycle.

**DESCRIPTION:**

The contents of the specified I register are placed on the DATA MULTIBUS SECOND.

EXAMPLE:

LIS I4

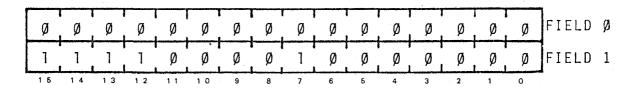

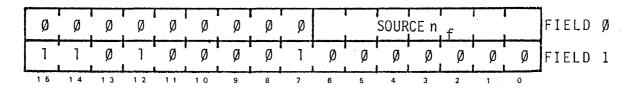

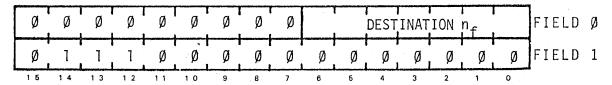

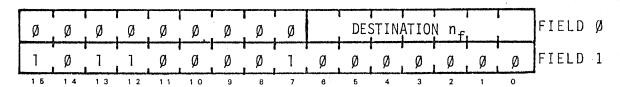

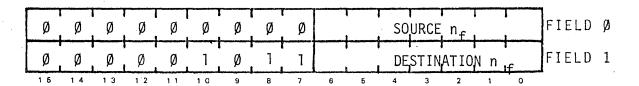

LOAD I SECOND CONDITIONALLY

| Ø  | Ø  | Ø  | Ø  | ø  | ø   | Ø | Ø | Ø | Ø | Ø | Ø    | Ø    | Ø | Ø | Ø   | FIELD | ø |

|----|----|----|----|----|-----|---|---|---|---|---|------|------|---|---|-----|-------|---|

| Ø  | Ø  | Ø  | Ø  | 1  | ]   | Ø | 1 | 1 |   | l | SOUR | CE n | S |   |     | FIELD | 1 |

| 15 | 14 | 13 | 12 | 11 | 1 0 | 9 | 8 | 7 | 6 | 5 | 4    | 3    | 2 | 1 | 0 . |       |   |

**OPERATION:**

IF CBIT IS TRUE

THEN  $DM_{1.5} \leftarrow I_{.5}(SOURCE)$

ERROR CONDITION(S):

BUS CONFLICT (DATA), if there is other data on the DM in the above specified BUS cycle.

**DESCRIPTION:**

If the condition bit is true, the contents of the specified I register are placed on the DATA MULTIBUS SECOND.

EXAMPLE:

LISC 14

<u>SIF</u>nf

STORE I FIRST

**OPERATION:**

I.5 (DESTINATION)  $\leftarrow DM_{\phi}$

ERROR CONDITION(S):

None

**DESCRIPTION:**

The specified I register is loaded with the data on the DATA MULTIBUS FIRST.

EXAMPLE:

. SIF I4 STORE I FIRST CONDITIONALLY

OPERATION:

IF CBIT IS TRUE

THEN I (DESTINATION)  $\leftarrow DM_{0}$

ERROR CONDITION(S):

None

**DESCRIPTION:**

If the condition bit is true, the specified I register is loaded with the data on the DATA MULTIBUS FIRST.

EXAMPLE:

. SIFC I4 SIS ns

STORE I SECOND

OPERATION:

$I_1(DESTINATION) \leftarrow DM_5$

ERROR CONDITION(S):

None

**DESCRIPTION:**

The specified I **register** is loaded with the data on the DATA MULTIBUS SECOND.

EXAMPLE:

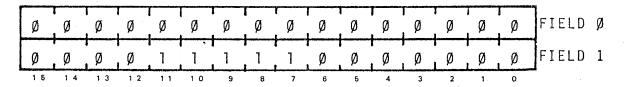

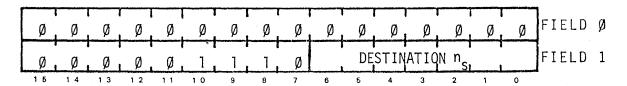

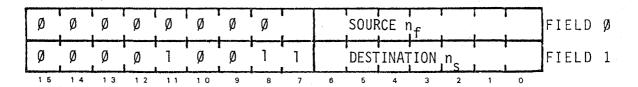

. SIS I4 . STORE I SECOND CONDITIONALLY

| Ø  | Ø  | Ø  | ø  | Ø   | Ø  | Ø | Ø | Ø | Ø | Ø | Ø    | Ø    | ·Ø   | Ø | ı<br>Ø | FIELD | ø |

|----|----|----|----|-----|----|---|---|---|---|---|------|------|------|---|--------|-------|---|

| Ø  | Ø  | Ø  | Ø  | Ø   | 1  | 1 | 1 | 1 |   | D | ESTI | NATI | ON n |   | 1      | FIELD | 1 |

| 15 | 14 | 13 | 12 | 1 1 | 10 | 9 | 8 | 7 | 6 | б | 4    | 3    | 2    | 1 | 0      |       |   |

**OPERATION:**

IF CBIT IS TRUE

THEN I<sub>1</sub> (DESTINATION)  $\leftarrow$  DM.5

ERROR CONDITION(S):

None

**DESCRIPTION:**

If the condition bit is true, the specified I register is loaded with the data on the DATA MULTIBUS SECOND.

EXAMPLE:

SISC 14

LOAD X FIRST

**OPERATOR:**

$DM_1 \leftrightarrow X_0(SOURCE)$

ERROR CONDITION(S):

BUS CONFLICT (DATA), if there is other data on the DM in in the above specified BUS cycle.

**DESCRIPTION:**

The contents of the specified X register are placed on the DATA MULTIBUS FIRST.

EXAMPLE:

.

.

LXF X4

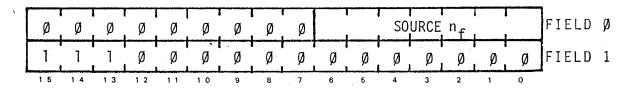

LOAD X FIRST CONDITIONALLY

| Ø  | Ø  | Ø  | ø   | Ø   | Ø  | Ø | Ø | Ø |   | l | SOUR | CE n | f |   |   | FIELD | ø |

|----|----|----|-----|-----|----|---|---|---|---|---|------|------|---|---|---|-------|---|

| 1  | 1  | 1  | Ø   | Ø   | ø  | ø | Ø | 1 | Ø | Ø | Ø    | Ø    | Ø | Ø | Ø | FIELD | 1 |

| 15 | 14 | 13 | 1 2 | 1 1 | 10 | 9 | 8 | 7 | 6 | 5 | 4    | 3    | 2 | 1 | 0 |       |   |

**OPERATION:**

IF CBIT IS TRUE

THEN  $DM_1 \leftarrow X_0(SOURCE)$

ERROR CONDITION(S):

BUS CONFLICT (DATA), if there is other data on the DM in the above specified BUS cycle.

**DESCRIPTION:**

If the condition bit is true, the contents of the specified X register are placed on the DATA MULTIBUS FIRST.

EXAMPLE:

.

LXFC X4

LOAD X SECOND

OPERATION:

$DM_{1.5} \leftarrow X_{.5}(SOURCE)$

ERROR CONDITION(S):

BUS CONFLICT (DATA), if there is other data on the DM in the above specified BUS cycle.

**DESCRIPTION:**

The contents of the specified  ${\tt X}$  register are placed on the DATA MULTIBUS SECOND.

EXAMPLE:

•

LXS X4

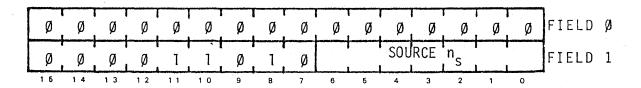

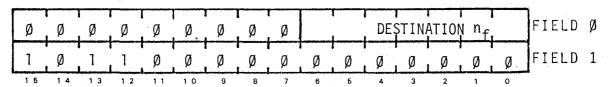

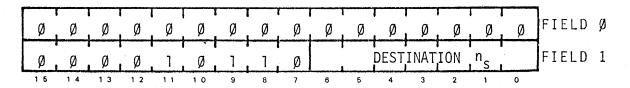

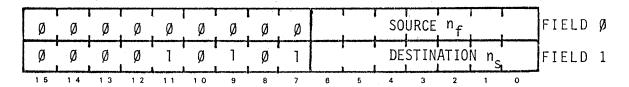

LOAD X SECOND CONDITIONALLY

| Ø  | Ø, | Ø  | Ø  | Ø   | Ø  | Ø | Ø | Ø | Ø | Ø | Ø  | Ø    | Ø              | , Ø    | , Ø | FIELD | ø |

|----|----|----|----|-----|----|---|---|---|---|---|----|------|----------------|--------|-----|-------|---|

| Ø  | Ø  | Ø  | Ø  | . 1 | 1  | 1 | Ø | 1 |   |   | S0 | URCE | n <sub>s</sub> | 1<br>1 | 1 . | FIELD | 1 |

| 15 | 14 | 13 | 12 | 11  | 10 | 9 | 8 | 7 | 6 | 5 | 4  | 3    | 2              | 1      | 0   |       |   |

OPERATION:

IF CBIT IS TRUE

THEN  $DM_{1.5} \leftarrow X_{.5}(SOURCE)$

ERROR CONDITION(S):

BUS CONFLICT (DATA), if there is other data on the DM in the above specified BUS cycle.

**DESCRIPTION:**

If the condition bit is true, the contents of the specified X register are placed on the DATA MULTIBUS SECOND.

EXAMPLE:

LXSC X4

SXF nf

STORE X FIRST

OPERATION:

X<sub>.5</sub>(DESTINATION) ← DM<sub>Ø</sub>

ERROR CONDITION(S):

None

**DESCRIPTION:**

The specified  $\boldsymbol{X}$  register is loaded with the data on the DATA MULTIBUS FIRST.

EXAMPLE:

. SXF X4 SXFC nf

STORE X FIRST CONDITIONALLY

**OPERATION:**

IF CBIT IS TRUE

THEN  $X_{5}$  (DESTINATION)  $\leftarrow DM_{0}$

ERROR CONDITION(S):

None

**DESCRIPTION:**

If the condition bit is true, the specified X register is loaded with the data on the DATA MULTIBUS FIRST.

EXAMPLE:

. SXFC X4 SXS ns

STORE X SECOND

**OPERATION:**

$X_1$ (DESTINATION)  $\leftarrow DM_{.5}$

ERROR CONDITION(S):

None

**DESCRIPTION:**

The specified  $\boldsymbol{X}$  register is loaded with the data on the DATA MULTIBUS SECOND.

EXAMPLE:

SXS X4

# SXSC n<sub>s</sub>

STORE X SECOND CONDITIONALLY

OPERATION:

IF CBIT IS TRUE

THEN  $X_1$  (DESTINATION)  $\leftarrow$  DM<sub>.5</sub>

ERROR CONDITION(S):

None

DESCRIPTION:

If the condition bit is true, the specified X register is loaded with the data on the DATA MULTIBUS SECOND.

EXAMPLE:

SXSC X4

# 6.2.7 MOVE REGISTER INSTRUCTIONS

The DEP has eight MOVE instructions which are used to transfer the contents of one I or X register to another I or X register. These data transfers take place via the internal DEP Data Bus (DEP DB). That part of the DEP involved in these internal MOVE instructions is shown below.

REGISTER ADDRESSES AND R/W CONTROL

The DEP MOVE instructions are:

| MII  | Move | I | to | I |               |

|------|------|---|----|---|---------------|

| MIIC | Move | I | to | I | Conditionally |

| MIX  | Move | Ι | to | Х |               |

| MIXC | Move | I | to | X | Conditionally |

| MXI  | Move | X | to | Í |               |

| MXIC | Move | Х | to | I | Conditionally |

| MXX  | Move | Ι | to | X |               |

| MXXC | Move | Ι | to | X | Conditionally |

6 11

MII n<sub>f</sub>,n<sub>s</sub>

MOVE I  $(n_f)$  to I  $(n_s)$

| Ø  | Ø  | Ø   | Ø  | Ø   | ø  | Ø | ø | ø |   | 1<br>, | SOUR | CE n | 1<br>. f | 1             | 1 | FIELD | ø |

|----|----|-----|----|-----|----|---|---|---|---|--------|------|------|----------|---------------|---|-------|---|

| Ø  | Ø  | Ø   | Ø  | Ø   | 1  | Ø | 1 | Ø |   | l      | DEST | INAT | ION      | 1<br>n<br>1.5 | ı | FIELD | 1 |

| 15 | 14 | 1 3 | 12 | 1 1 | 10 | 9 | 8 | 7 | 6 | 5      | 4    | 3    | 2        | 1             | 0 |       |   |

**OPERATION:**

$I_1(DESTINATION) \leftarrow I_{\emptyset}(SOURCE)$

ERROR CONDITION(S):

None

**DESCRIPTION:**

The contents of the source I register are placed in the destination  $\ensuremath{\mathrm{I}}$  register.

EXAMPLE:

. MII I**4,**I5

# MIIC n<sub>f</sub>,n<sub>s</sub>

MOVE  $I(n_f)$  to  $I(n_s)$  CONDITIONALLY

**OPERATION:**

IF CBIT IS TRUE

THEN  $I_1$  (DESTINATION)  $\leftarrow$   $I_0$  (SOURCE)

ERROR CONDITION(S):

None

**DESCRIPTION:**

If the condition bit is true, the contents of the source I register are placed in the destination I register.

EXAMPLE:

. MIIC 14,15

# MIX n<sub>f</sub>,n<sub>s</sub>

MOVE  $I(n_f)$  to  $X(n_s)$

|   | ø   | ø  | Ø  | ø   | ø   | ø   | Ø | Ø | ø |   | l | SOUR | CE n | r<br>f | 1 1    |   | FIELD | ø |

|---|-----|----|----|-----|-----|-----|---|---|---|---|---|------|------|--------|--------|---|-------|---|

| , | Ø   | Ø  | Ø  | ø   | 1   | ø   | ø | 1 | Ø |   | l | DEST | INAT | ION    | n<br>n |   | FIELD | 1 |

|   | 1 5 | 14 | 13 | 1 2 | 1 1 | 1.0 | 9 | 8 | 7 | 6 | 5 | 4    | 3    | 2      | 1      | 0 |       |   |

**OPERATION:**

$X_1$ (DESTINATION)  $\leftarrow I_q$ (SOURCE)

ERROR CONDITION(S):

None

**DESCRIPTION:**

The contents of the source I register are placed in the destination  ${\tt X}$  register.

EXAMPLE:

MIX I4,X5

MOVE  $I(n_f)$  to  $X(n_s)$  CONDITIONALLY

**OPERATION:**

IF CBIT IS TRUE

THEN  $X_1$  (DESTINATION)  $\leftarrow I_{\emptyset}$  (SOURCE)

ERROR CONDITION(S):

None

DESCRIPTION:

If the condition bit is true, the contents of the source I register are placed in the destination X register.

EXAMPLE:

. MIXC I4,X5

# MXI nf,ns

MOVE X(n<sub>f</sub>) to I(n<sub>s</sub>)

**OPERATION:**

$I_1$  (DESTINATION)  $\leftarrow X_{\emptyset}$  (SOURCE)

ERROR CONDITION(S):

None

DESCRIPTION:

The contents of the source  $\boldsymbol{X}$  register are placed in the destination  $\boldsymbol{I}$  register.

EXAMPLE:

. MXI X4,I5

# MXIC nf,ns

MOVE X(n<sub>f</sub>) to I(n<sub>s</sub>) CONDITIONALLY

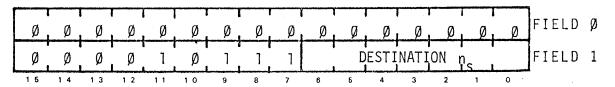

|   | ø  | Ø  | Ø   | Ø   | Ø   | ø  | Ø | Ø | Ø  |   | SC | URC |      | 1    | 1   | 1 | FIELD | ø |

|---|----|----|-----|-----|-----|----|---|---|----|---|----|-----|------|------|-----|---|-------|---|

|   | Ø  | ø  | Ø   | Ø   | Ø   | 1  | 1 | Ø | 1. |   | DE | STI | ITAV | ON n | I S | 1 | FIELD | 1 |

| Ē | 15 | 14 | 1 3 | 1 2 | 1 1 | 10 | 9 | 8 | 7  | 6 | 5  | 4   | 3    | 2    | 1   | 0 | _     |   |

**OPERATION:**

IF CBIT IS TRUE

THEN  $I_1$  (DESTINATION)  $\leftarrow X_0$  (SOURCE)

ERROR CONDITION(S):

None

**DESCRIPTION:**

If the condition bit is true, the contents of the source X register are placed in the destination I register.

EXAMPLE:

MXIC X4,15

MOVE  $X(n_f)$  to  $X(n_s)$  $0 0 0 0 0 0 0 0 0 SOURCE n_f$

| Ø  | Ø  | Ø  | Ø  | ø   | Ø. | Ø | Ø | Ø |   | ı<br>ı | SOU | RCE  | n<br>f | 1   | l<br>1 | FIELD | ø |

|----|----|----|----|-----|----|---|---|---|---|--------|-----|------|--------|-----|--------|-------|---|

| ø  | Ø  | Ø  | Ø  |     | Ø  |   | Ø | Ø |   | 1      | DES | TINA | TION   | n n | 1<br>1 | FIELD | 1 |

| 15 | 14 | 13 | 12 | 1 1 | 10 | 9 | 8 | 7 | 6 | б      | 4   | 3    | 2      | . 1 | 0      | -     |   |

**OPERATION:**

$X_1$  (DESTINATION)  $\leftarrow X_0$  (SOURCE)

ERROR CONDITION(S):

None

DESCRIPTION:

The contents of the source  $\boldsymbol{X}$  register are placed in the destination  $\boldsymbol{X}$  register.

EXAMPLE:

. MXX X4,X5

# MXXC nf,ns

MOVE X(n<sub>f</sub>) to X(n<sub>s</sub>) CONDITIONALLY

**OPERATION:**

IF CBIT IS TRUE

THEN  $X_1$  (DESTINATION)  $\leftarrow X_0$  (SOURCE)

ERROR CONDITION(S):

None

DESCRIPTION:

If the condition bit is true, the contents of the source X register are placed in the destination X register.

EXAMPLE:

MXXC X4,X5

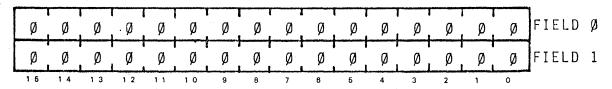

# 6.2.8 PAUSE/NOP INSTRUCTIONS

The PAUSE instruction may be microprogrammed with any other DEP instruction or it may be issued as a stand-alone instruction. The NOP instruction is only used as a stand-alone instruction. The NOP and PAUSE instructions are defined below.

## PAUSE d

PAUSE FOR d INSTRUCTION CYCLES

| ø  | ø  | Ø  | Ø  |    | d  | l<br> | ø | Ø | Ø | Ø | Ø | ø | Ø | Ø | ø | FIELD | ø |

|----|----|----|----|----|----|-------|---|---|---|---|---|---|---|---|---|-------|---|

| Ø  | Ø  | Ø  | Ø  | Ø  | ø  | Ø     | Ø | Ø | Ø | Ø | Ø | ø | ø | ø | ø | FIELD | 1 |

| 15 | 14 | 13 | 12 | 11 | 10 | 9     | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |       |   |

**OPERATION:**

None

ERROR CONDITION(S):

None

#### **DESCRIPTION:**

Suspend execution for d instruction cycles following the PAUSE instruction. This has the same effect as (d+1) NOP's.

EXAMPLE:

PAUSE 6

NO OPERATION

**OPERATION:**

None

ERROR CONDITION(S):

None

DESCRIPTION:

Suspends execution for one instruction cycle.

EXAMPLE:

NOP

### INTRODUCTION

7.

7.0

7.1

The MEMORY ADDRESS PROCESSOR (MAP) initiates Data Memory read/write operations and may be viewed as the AD 10 Data Memory controller. The MAP has instructions to perform both direct addressing and indexed addressing as well as instructions for two types of address mapping, aligned and unaligned. The MAP is only concerned with addressing Data Memory and has no control over the corresponding data to be written to or read from Data Memory.

#### ORGANIZATION OF THE MAP

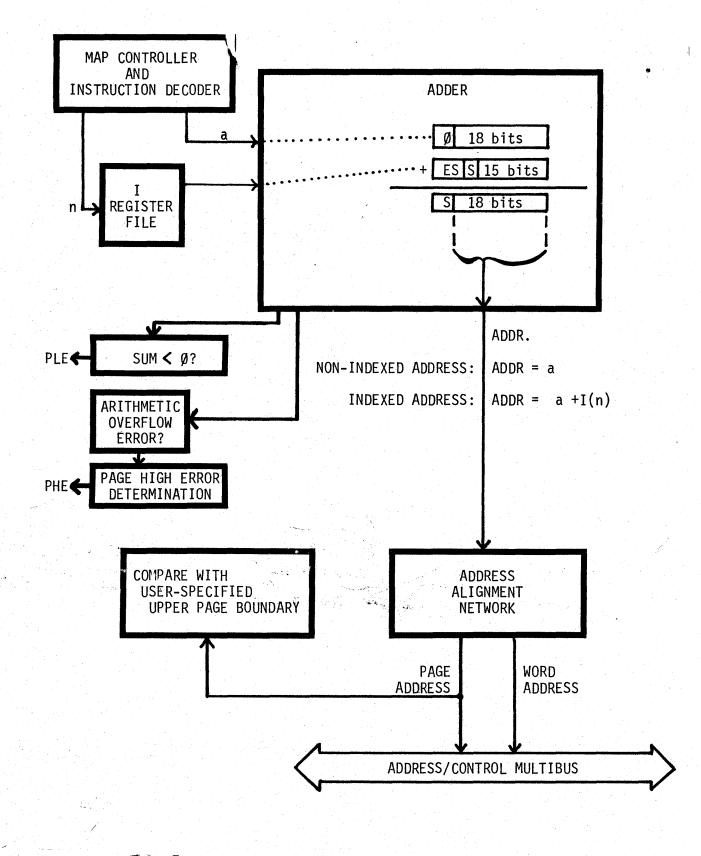

A block diagram of the MAP is shown in Figure 7.1. That part of Figure 7.1 which is in black is common to all processors and is described in Section 2.6. The elements in Figure 7.1 which are in red are those which are specific to the MAP. A more detailed diagram of key MAP elements is presented in Figure 7.2.

Data Memory read/write operations may be either indexed or non-indexed. The I register file and the adder are involved in indexed address operations. Indexed address operations are discussed in Section 7.2.3.1.

The MAP is physically located on the same circuit card assembly which contains the Decision Processor (DEP). The I register file, shown in Figures 7.1 and 7.2, is shared between MAP and DEP in the sense that it may be accessed by either processor. The MAP is limited to readonly access to the I register file. The DEP may perform either read or write operations on the I register file. See Chapter 6 for more information in this regard. NOTE: It is possible for a given register in the I register file to be accessed by both MAP and DEP in one instruction required by MAP is performed before the register operation specified by the DEP instruction and no conflict occurs.

## FIGURE 7.2 MAP INSTRUCTION ADDRESS OPERATIONS

The MAP instructions allow the address output to the Data Memory to be either "aligned" or "unaligned". If the MAP instruction calls for an unaligned address read or write operation, the address specified as part of the MAP instruction or the computed indexed address is output directly to the Data Memory via the ADDRESS MULTIBUS as described in Section 7.2.3.2. Thus, an unaligned addressing operation may be viewed as an absolute addressing operation. If an aligned address read or write operation is specified, the address output from the MAP to Data Memory is obtained as the result of an operation performed by the address alignment network (see Figure 7.1) on the address specified as part of the MAP instruction or on the computed indexed address. The operation performed by the address alignment network is described in Section 7.2.3.3.

Connections from the COP to the Processor Status Enable Register via the DATA MULTIBUS and from the COP to the Program Counter via the ADDRESS/CONTROL MULTIBUS are shown in red in Figure 7.1. These connections indicate that the Processor Status Enable Register and the Program Counter can be changed by instructions in a COP program when the AD 10 is in the RUN mode.

7.1.1 Processor Address

The Processor add, iss for the MAP is Ø1.

#### 7.1.2 Processor Status Word

|                      |             |             | 100 C      | 1.1                               | 1.12 A.     | 1.1 |      |     | e da la | 5 |   |   |                   |     | <u> </u>          |

|----------------------|-------------|-------------|------------|-----------------------------------|-------------|-----|------|-----|---------|---|---|---|-------------------|-----|-------------------|

| P<br>E               | P<br>H<br>E | P<br>L<br>E | Ø          | Ø                                 | ø           | A   | Р    | Ø   | Ø       | Ø | ø | Ø | PAUSE             | CNT |                   |

| 15<br><u>BIT</u>     | 14          | 13          | 1 2<br>DES | 11<br>SCRIP                       | 10<br>TION  | 9   | 8    | 7   | 8       | 5 | 4 | 3 | 2 1               | 0   |                   |

| Ø-2<br>3-7<br>8<br>9 |             |             | Una<br>MAP | naini<br>Issig<br>Iis<br>Is<br>Is | ned<br>pres | ent | when | set |         |   |   |   |                   |     |                   |

| 10-]<br>13*<br>14*   |             | > 9         | Pag        |                                   | wEr         |     |      |     |         |   |   |   | s is a<br>ss exce |     | ive number.<br>he |

programmer specified upper page boundary or if an arithmetic overflow occurs on the computation of an indexed address.

Page Error. Set if either PLE or PHE occurs.

\* Once set, these bits remain set until cleared by a read operation.

The MAP Processor Status Word (PSW) contains information on the current status of the MAP. The PSW is a read-only register.

7.1.3 Processor Status Enable

| E<br>P | E<br>P<br>H | E<br>P<br>L | ø   | Ø   | ø  | øø  | ø | Ø | UPP | <b>L</b> IX 1 | 1EMOR<br>JNDAR |   | PAGE |   |

|--------|-------------|-------------|-----|-----|----|-----|---|---|-----|---------------|----------------|---|------|---|

| 1 5    | 1.4         | 13          | 1 2 | 1.1 | 10 | 9 8 | 7 | 6 | 5   | 4             | 3              | 2 | 1    | 0 |

### BIT DESCRIPTION

Ø-5 Upper memory page boundary. User specified upper page in Data Memory. Since there is no hardware protection in the Data Memory to indicate that a page addressed is not physically present, this allows the user to protect him/her self. NOTE: The upper memory page boundary should be specified in any instruction which set bit 14, since the hardware does not provide a default setting for these bits. 6-12 Unassigned. 13 Enable the PLE line to the AER line. Enable the PHE line to the AER line. 14 15 Enable error on above two conditions (i.e., PE) to the AER line.

The Processor Status Enable Register (PSE) is a write-only register. This register has the same address as the MAP Processor Status Word.

7.1.4 Program Memory

The MAP program memory contains 1,024 words. Each 48-bit instruction word is divided into three 16-bit fields. A MAP instruction is normally loaded as a sequence of three 16-bit words (one per field) from the host processor. However, each field is individually addressable and can be accessed from the host processor for a read/write operation.

# 7.2 THE MAP INSTRUCT AN SET

7.2.1 Map Instruction Word Format

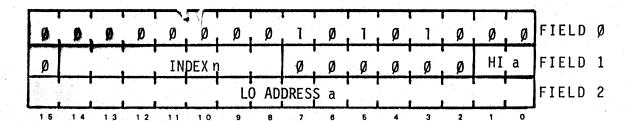

The MAP instruction word format is:

| X  | Х   | X   | Χ  | X  | X  | Х | X |   |        |   |   |                                       | PA                                      | JSE ( | COUNT | FIELD Ø |

|----|-----|-----|----|----|----|---|---|---|--------|---|---|---------------------------------------|-----------------------------------------|-------|-------|---------|

| X  |     |     |    |    |    |   |   | Х | X      | Х | Х | X                                     | Х                                       |       |       | FIELD 1 |

|    |     |     |    |    |    |   |   |   | •<br>• | • |   | · · · · · · · · · · · · · · · · · · · | • · · · · · · · · · · · · · · · · · · · |       |       | FIELD 2 |

| 15 | 1.4 | 1 3 | 12 | 11 | 10 | 9 | 8 | 7 | 6      | 5 | 4 | 3                                     | 2                                       | 1     | 0     |         |

The bits labelled "X" in the above diagram are unused. The unused bits cannot be set and are always read as a  $\emptyset$ .

Figure 7.3 provides a summary of the MAP instruction set.

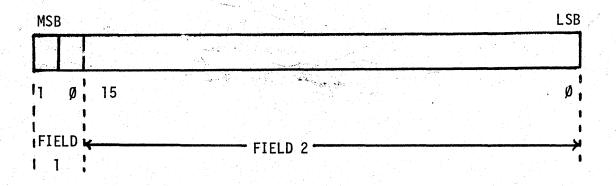

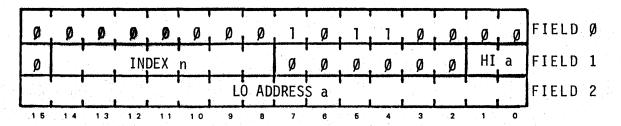

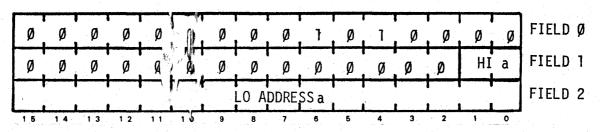

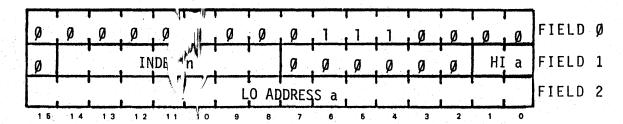

In each MAP read or write instruction, bits  $\emptyset$  and 1 of Field 1 are appended to Field 2 to form the address portion of the instruction. The format for this address information is:

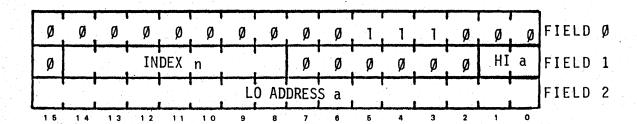

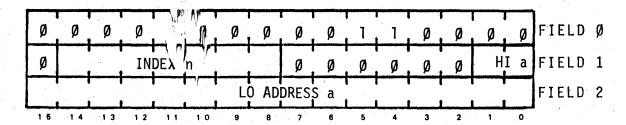

Bits 8 through 14 of Field 1 are used to specify the address of the register in the I register file which contains the index to be used in a read or write instruction which involves indexed addressing.

Map Instruction Microprogramming

7.2.2

The only microprogramming allowed in a MAP instruction is that of a PAUSE instruction with a read instruction or a write instruction.

# 7.2.3 Read/Write Instructions

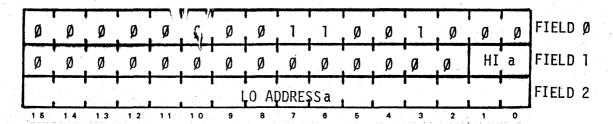

Figure 7.2 shows details of that part of the MAP which determines the page and word addresses to be transmitted via the ADDRESS/CONTROL MULTIBUS to Data Memory in a read or write operation.

Every read and write instruction specifies an 18-bit address "a" to be used in determining the actual address to be transmitted to Data Memory. In addition, the instruction also specifies whether or not the address "a" is to be indexed and/or aligned.

## 7.2.3.1 Indexed Addressing

-----

An indexed address is obtained by adding the contents of one of the 128 registers in the I register file to the address "a" specified in the read or write instruction. An instruction which involves an indexed address contains a 7-bit number "n" which specifies the register in the I register file which is to be used.

The adder shown in Figure 2.7 is used to compute indexed addresses. Both the address "," and the contents of the specified I register are treated as int pers in two's-complement format by the adder. This allows the in pers address to lie anywhere in the range [a - 32,768] to [a - 32,767]. Depending on the specified address "a \* and the contents of the specified I register, it is possible for the computed indexed address to be a negative number. Since all valid Data Memory addresses are non-negative, a computed indexed address which is a negative number represents an error situation. The output of the adder is checked to determine whether or not the computed indexed address is negative. If it is negative, a Page Low Error (PLE) condition is generated. (See Figure 7.2).

\* NOTE: The address "a" is a positive integer. See Figure 7.2.

|      | FIELD Ø                                                  | FIELD 1                                                     | FIELD 2                     |

|------|----------------------------------------------------------|-------------------------------------------------------------|-----------------------------|

| PAGE | 9110108009540018<br>9110108                              | 545019<br>5450018                                           | 91111190000040019<br>911019 |

| 7-25 | RAD X X X X X X X X Ø Ø Ø 1 1 Ø Ø Ø                      | ΧØØØØØØΧΧΧΧΧΧΑΑ                                             | TA MEMORY ADDR.→            |

| 7-26 | RAF X X X X X X X Ø Ø Ø Ø 1 Ø Ø Ø                        | ΧΦΦΦΦΦΦΦΧΧΧΧΧΧΑΑ                                            | TA MEMORY ADDR.→            |

| 7-28 | RAID XXXXXXXXØØ111ØØØ                                    | $X \leftarrow I N D E X \rightarrow X X X X X X D A$        | TA MEMORY ADDR.→            |

| 7-29 | RAIF                                                     | $X \leftarrow I N D E X \rightarrow X X X X X X D A$        | TA MEMORY ADDR.→            |

| 7-30 | RAIS <sup>1</sup> X X X X X X X X Ø Ø 1 1 Ø Ø Ø Ø        | X + I N D E X + X X X X X X D A                             | TA MEMORY <b>A</b> DDR.→    |

| 7-27 | RAS' ¬ X X X X X X X Ø Ø Ø 1 Ø Ø Ø Ø                     | . Χ Ø Ø Ø Ø Ø Ø Ø Χ Χ Χ Χ Χ Χ Ο Α                           | TA MEMORY ADDR.→            |

| 7-11 | RUD X X X X X X X X 1 Ø Ø 1 1 Ø Ø Ø                      | ΧØØØØØØΧΧΧΧΧΧΑΑ                                             | TA MEMORY ADDR.→            |

| 7-12 | RUF X X X X X X X 1 Ø Ø Ø 1 Ø Ø Ø                        | ΧØØØØØØΧΧΧΧΧΧΟΑ                                             | TA MEMORY ADDR.→            |

| 7-14 | RUID X X X X X X X X 1 Ø 1 1 1 Ø Ø Ø                     | $X \leftarrow I N D E X \rightarrow X X X X X X D A$        | TA MEMORY ADDR.→            |

| 7-15 | RUIF X X X X X X X X 1 Ø 1 Ø 1 Ø Ø Ø                     | $X \leftarrow I N D E X \rightarrow X X X X X X D A$        | TA MEMORY ADDR.→            |

| 7-16 | RUIS X X X X X X X X 1 Ø 1 1 Ø Ø Ø Ø                     | $X \leftrightarrow I / N D E X \rightarrow X X X X X X D A$ | TA MEMORY ADDR.→            |

| 7-13 | RUS X X X X X X X X 1 Ø Ø 1 Ø Ø Ø Ø                      | ΧØØØØØØΧΧΧΧΧΑΛΑ                                             | TA MEMORY ADDR.→            |

| 7-31 | WAD X X X X X X X X Ø 1 Ø 1 1 Ø Ø Ø                      | ΧØØØØØØΧΧΧΧΧΧΟΑ                                             | TA MEMORY ADDR.→            |

| 7-32 | WAF X X X X X X X X Ø 1 Ø Ø 1 Ø Ø g                      | X Ø Ø Ø Ø Ø Ø Ø X X X X X X D A                             | TA MEMORY ADDR.→            |

| 7-34 | WAID X X X X X X X X Ø 1 1 1 1 Ø Ø Ø                     | $X \leftarrow I N D E X \rightarrow X X X X X X D A$        | TA MEMORY ADDR.→            |

| 7-35 | WAIF X X X X X X X X Ø 1 1 Ø 1 Ø Ø Ø                     | $X \leftarrow I N D E X \rightarrow X X X X X X D A$        | TA MEMORY ADDR.→            |

| 7-36 | WAIS X X X X X X X X Ø 1 1 1 Ø Ø Ø Ø                     | . X ← I N D E X → X X X X X X D A                           | TA MEMORY ADDR.→            |

| 7-33 | WAS X X X X X X X X Ø 1 Ø 1 Ø Ø Ø Ø                      | ΧØØØØØØΧΧΧΧΧΧΑΑ                                             | TA MEMORY ADDR.→            |

| 7-17 | WUD X X X X X X X X 1 1 Ø 1 1 Ø Ø Ø                      | ΧØØØØØØΧΧΧΧΧΧΟΑ                                             | TA MEMORY ADDR.→            |

| 7-18 | WUF X X X X X X X X 1 1 Ø Ø 1 Ø Ø Ø                      | ΧØØØØØØΧΧΧΧΧΧΟΑ                                             | TA MEMORY ADDR.→            |

| 7-20 | WUID X X X X X X X X 1 1 1 1 1 Ø Ø Ø                     | $X \leftarrow I N D E X \rightarrow X X X X X X D A$        | TA MEMORY ADDR.→            |

| 7-21 | WUIF X X X X X X X X 1 1 1 Ø 1 Ø Ø Ø                     | $X \leftarrow I N D E X \rightarrow X X X X X X D A$        | TA MEMORY ADDR.→            |

| 7-22 | WUIS X X X X X X X X 1 1 1 1 Ø Ø Ø Ø                     | $X \leftarrow I N D E X \rightarrow X X X X X X D A$        | TA MEMORY ADDR.→            |

| 7-19 | WUS X X X X X X X X 1 1 Ø 1 Ø Ø Ø Ø                      | ΧØØØØØØΧΧΧΧΧΧΟΑ                                             | TA MEMORY ADDR.→            |

| 7-40 | ΝΟΡ ΧΧΧΧΧΧΧΧΦΦΦΦΦΦΦ                                      | x ø ø ø ø ø ø ø ø x x x x x x ø ø                           | ØØØØØØØØØØØØØØØØ            |

| 7-39 | PAUSE $X X X X X X X X Ø Ø Ø Ø \leftarrow d \rightarrow$ | x ø ø ø ø ø ø ø ø x x x x x x ø ø                           | ØØØØØØØØØØØØØØØØ            |

|      | 111111<br>940070070070040016                             | 01004000000000000000000000000000000000                      | Ø112045967899172945         |

FIGURE 7.3 MEMORY ADDRESS PROCESSOR INSTRUCTION SET

The output of the defer is also checked to determine if an arithmetic overflow has occuved on the computation of an indexed address. Because of the modulo  $2^{19}$  wraparound which occurs in an arithmetic overflow situation, the resulting page address could lie within the range of **valid page addresses** (i.e., between page Ø and the user specified upper memory page boundary). This is clearly an error situation as the indexed address is trying to call for a memory page whose address is greater than 63. Thus, a Page High Error (PHE) condition is generated if an arithmetic overflow occurs in the adder.

7.2.3.2 Unaligned Read/Write Instructions

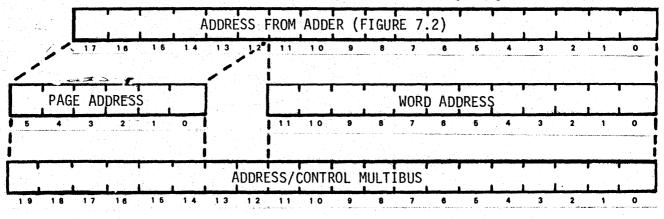

In Figure 7.2, the output of the adder is labelled ADDR. For nonindexed read or write operations:

ADDR  $\leftarrow$  a

For indexed read or write instructions:

ADDR  $\leftarrow$  a + I(n)

If the read or write instruction specifies an unaligned address, the address alignment network simply outputs ADDR to the ADDRESS/CONTROL MULTIBUS as follows:

$AM_1(14:19) \leftarrow ADDR_{\emptyset}(12:17)$  (PAGE ADDRESS)  $AM_1(\emptyset:11) \leftarrow ADDR_{\emptyset}(\emptyset:11)$  (WORD ADDRESS)

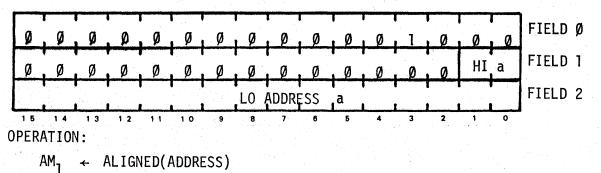

The operation of the address alignment network for an unaligned read or write instruction is illustrated in the following diagram:

The unaligned read/write instructions are:

|   | RUD a    | READ UNALIGNED DOUBLE          |

|---|----------|--------------------------------|

|   | RUF a    | READ UNALIGNED FIRST           |

| • | RUS a    | READ UNALIGNED SECOND          |

|   | RUID a,n | READ UNALIGNED INDEXED DOUBLE  |

|   | RUIF a,n | READ UNALIGNED INDEXED FIRST   |

|   | RUIS a,n | READ UNALIGNED INDEXED SECOND  |

|   | WUD a    | WRITE UNALIGNED DOUBLE         |

|   | WUF a    | WRITE UNALIGNED FIRST          |

|   | WUS a    | WRITE UNALIGNED SECOND         |

|   | WUID a,n | WRITE UNALIGNED INDEXED DOUBLE |

|   | WUIF a,n | WRITE UNALIGNED INDEXED FIRST  |

|   | WUIS a,n | WRITE UNALIGNED INDEXED SECOND |

|   |          |                                |

£ C

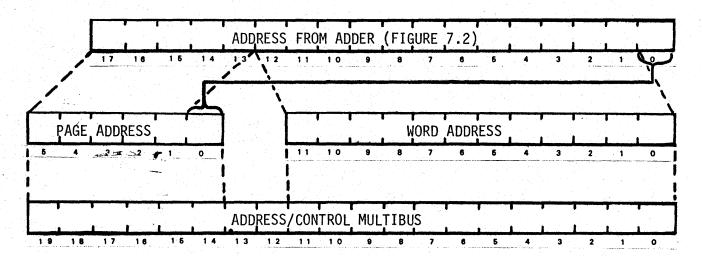

# READ UNALIGNED DOUBLE

| Ø Ø Ø Ø Ø Ø Ø Ø Ø Ø Ø Ø Ø HI a                                                                        | ØFIELD | Ø | Ø  | Ø | 1 | 1 | Ø | Ø  | 1    | Ø    | Ø | Ø | Ø | Ø | Ø | Ø | Ø |

|-------------------------------------------------------------------------------------------------------|--------|---|----|---|---|---|---|----|------|------|---|---|---|---|---|---|---|

| فمج جميعتها ومعتمة ومحمدا وتتعادي وتجاري وتحقيتها وتصحينا أتسمحه ومعتمي ومعتما ومعتما المتناط التقاري | FIELD  | a | ΗÌ | ø | Ø | Ø | Ø | Ø  | Ø    | Ø    | Ø | Ø | Ø | Ø | Ø | Ø | Ø |

| LO ADDRESS a                                                                                          | FIELD  |   |    |   |   |   |   | Sa | DRES | O AD | L |   |   |   |   |   |   |

**OPERATION:**

$AM_1 \leftarrow UNALIGNED(ADDRESS)$

$AM_{1.5} \leftarrow UNALIGNED(ADDRESS+1)$

$DM_{5} \leftarrow MEM_{1}(ADDRESS)$

$DM_{5,5} \leftarrow MEM_{1,5}(ADDRESS+1)$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- BUS conflict (ADDRESS, DATA), if there is other data on the AM or the 2. DM in the above specified BUS cycles. Page address overrange if enabled to AER line.

- 3.

## **DESCRIPTION:**

An address pair is sent out on the ADDRESS MULTIBUS to Data Memory.\* After a delay, data will appear on the DATA MULTIBUS.

\*This instruction is included primarily for maintenance purposes; a memory page access error will occur if ADDRESS is not the last address of a memory page.

EXAMPLE:

~ 3

RUD FUNT

#### RUF a

# READ UNALIGNED FIRS

| ø  | Ø     | Ø  |    | Ø  | • · · · · · | Ø                              | Ø | 1 | ø | ø | Ø | 1 | Ø | Ø  | Ø       | FIELD Ø |

|----|-------|----|----|----|-------------|--------------------------------|---|---|---|---|---|---|---|----|---------|---------|

| Ø  | Ø     | Ø  | Ø  | Ø  | Ø           | Ø                              | Ø | Ø | Ø | Ø | Ø | Ø | Ø | HI | a       | FIELD 1 |

|    | V<br> |    |    |    |             | 0000000000 HIa<br>LO ADDRESS a |   |   |   |   |   |   |   |    | FIELD 2 |         |

| 15 | 1.4   | 13 | 12 | 11 | 10          | 9                              | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0       |         |

#### **OPERATION:**

$AM_1 \leftarrow UNALIGNED(ADDRESS)$

$DM_5 \leftarrow MEM_1 (ADDRESS)$

# ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS,DATA), if there is other data on the AM or the DM in the above specified BUS cycles.

- 3. Page address overrange if enabled to AER line.

## **DESCRIPTION:**

The address is sent out on the ADDRESS MULTIBUS to Data Memory. After a delay, data appears on the DATA MULTIBUS.

#### **EXAMPLE:**

.•

RUF FUN1

# RUS a

# READ UNALIGNED SECOND

| ø      | 1 | Ø  | Ø  | ø  | Ø   | Ø   | Ø | Ø    | 1    | Ø    | Ø | , 1 | Ø | Ø             | Ø  | ø | FIELD Ø |

|--------|---|----|----|----|-----|-----|---|------|------|------|---|-----|---|---------------|----|---|---------|

| Ø      |   | Ø  | Ø  | Ø  | Ø   | Ø   | ø | Ø    | ø    | Ø    | Ø | Ø   | ø | Ø             | HI | a | FIELD 1 |

|        |   | -  |    |    | 1   |     |   | LO A | DDRE | SS a |   |     | r | 1 · · · · · · |    |   | FIELD 2 |

| <br>15 |   | 14 | 13 | 12 | 1 1 | 1.0 | 9 | 8    | 7    | 6    | 5 | 4   | 3 | 2             | 1  | 0 |         |

**OPERATION:**

$AM_{1.5} \leftarrow UNALIGNED(ADDRESS)$  $DM_{5.5} \leftarrow MEM_{1.5}(ADDRESS)$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS,DATA), if there is other data on the AM or the DM in the above specified BUS cycles.

Same She

3. Page address overrange if enabled to AER line.

#### **DESCRIPTION:**

The address is sent out on the ADDRESS MULTIBUS to Data Memory. After a delay, data will appear on the DATA MULTIBUS.

EXAMPLE:

RUS FUNI

1. 1.25

#### RUID a,n

#### READ UNALIGNED INDEXED DOUBLE

| Ø   | Ø   | Ø  | Ø   | Ø   | Ø     | Ø     | Ø    | 1    | Ø  | 1 | 1 | 1 | ø      | Ø  | Ø | FIELD | ø |

|-----|-----|----|-----|-----|-------|-------|------|------|----|---|---|---|--------|----|---|-------|---|

| Ø   |     |    |     | IN  | DEX r | )<br> |      | Ø    | Ø  | Ø | ø | Ø | Ø      | HI | a | FIELD | 1 |

|     |     |    |     |     |       | L     | ) AD | DRES | Sa |   |   |   | ,<br>, | 1  |   | FIELD | 2 |

| 1 5 | 1.4 | 13 | 1 2 | 1 1 | 10    | 9     | 8    | 7    | 6  | 5 | 4 | 3 | 2      | 1  | 0 |       |   |

**OPERATION:**

$AM_{1} \leftarrow UNALIGNED(ADDRESS+I_{\emptyset}(INDEX))$   $AM_{1.5} \leftarrow UNALIGNED(ADDRESS+I_{\emptyset}(INDEX)+1)$   $DM_{5} \leftarrow MEM_{1}(ADDRESS+I_{\emptyset}(INDEX))$   $DM_{5.5} \leftarrow MEM_{1.5}(ADDRESS+I_{\emptyset}(INDEX)+1)$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS,DATA), if there is other data on the AM or the DM in the above specified BUS cycles.

- 3. Page address overrange/underrange if enabled to AER line.

#### **DESCRIPTION:**

The address is obtained by adding the given address with the specified INDEX register. An address pair is sent out on the ADDRESS MULTIBUS Data Memory.\* After a delay, data will appear on the DATA MULTIBUS.

\* This instruction is included primarily for maintenance purposes; a memory page access error will occur if the indexed address is not the last address of a memory page.

#### **EXAMPLE:**

RUID FUN1,16

1 III >

#### RUIF a,n

# READ UNALIGNED IND FIRST

**OPERATION:**

$AM_1 \leftarrow UNALIGNED(ADDRESS+I_{\emptyset}(INDEX))$

$DM_5 \leftarrow MEM_1 (ADDRESS+I_0(INDEX))$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS, DATA), if there is other data on the AM or the

- DM in the above specified BUS cycles.

- 3. Page address overrange/underrange if enabled to AER line.

#### **DESCRIPTION:**

The address sent out on the ADDRESS MULTIBUS to Data Memory is obtained by adding the given address to the contents of the specified INDEX register. After a delay, data will appear on the DATA MULTIBUS.

EXAMPLE:

RUIF FUN2, 19

1× >

۳.

#### RUIS a,n

#### READ UNALIGNED INDEXED SECOND

**OPERATION:**

$AM_{1.5} \leftarrow UNALIGNED(ADDRESS+I_{g}(INDEX))$  $DM_{5.5} \leftarrow MEM_{1.5}(ADDRESS+I_{g}(INDEX))$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS, DATA), if there is other data on the AM or the

- DM in the above specified BUS cycles.

- 3. Page address overrange/underrange if enabled to AER line.

### **DESCRIPTION:**

The address sentrout on the ADDRESS MULTIBUS to Data Memory is obtained by adding the given address to the contents of the specified INDEX register. After a delay, data will appear on the DATA MULTIBUS.

EXAMPLE:

RUIS A,I4

#### WUD a

## WRITE UNALIGNED DOUBLE

| ø   | Ø   | Ø  | Ø   | Ø   | Ø  | Ø | ø    | 1    | 1  | ø | 1 | 1 | Ø | Ø  | ø | FIELD | ø             |

|-----|-----|----|-----|-----|----|---|------|------|----|---|---|---|---|----|---|-------|---------------|

| Ø   | Ø   | Ø  | Ø   | Ø   | Ø  | Ø | Ø    | ø    | ø  | Ø | Ø | ø | ø | HI | a | FIELD | 1             |

|     | 1   | 1  |     |     |    | L | O AD | DRES | Sa |   |   | t | l |    |   | FIELD | 2             |

| 1:5 | 1.4 | 13 | 1 2 | 1 1 | 10 | 9 | 8    | 7    | 6  | 5 | 4 | 3 | 2 | 1  | 0 | -     | $ \cdot ^{2}$ |

**OPERATION:**

$AM_1 \leftarrow UNALIGNED(ADDRESS)$

$AM_{1.5} \leftarrow UNALIGNED(ADDRESS+1)$

$MEM_{E}(ADDRESS) \leftarrow DM_{1}$

$MEM_{5.5}(ADDRESS+1) \leftarrow DM_{1.5}$

ERROR CONDITION(S):

1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS, DATA), if there is other data on the AM or the DM in the above specified BUS cycles.

- 3. Page address overrange if enabled to AER line.

## DESCRIPTION:

An address pair is sent out on the ADDRESS MULTIBUS to Data Memory. Data Memory takes the data pair from the DATA MULTIBUS, and, after a delay, stores the data at the specified addresses.\*

\*This instruction is included primarily for maintenance purposes; a memory page access error will occur if ADDRESS is not the last address of a memory page.

EXAMPLE:

WUD FUN1

WUF a

# WRITE UNALIGNED FIRST

**OPERATION:**

$AM_1 \leftarrow UNALIGNED(ADDRESS)$

$MEM_{5}(ADDRESS) \leftarrow DM_{1}$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS, DATA), if there is other data on the AM or the DM in the above specified BUS cycles.

- 3. Page address overrange if enabled to AER line.

#### **DESCRIPTION:**

The address is sent out on the ADDRESS MULTIBUS to Data Memory. Data Memory takes the data on the DATA MULTIBUS and, after a delay, stores the data at the specified address.

EXAMPLE:

WUF FUN1

#### WUS a

# WRITE UNALIGNED SECOND

| <br>ø | ø  | Ø  | ø   | ø     | ø  | ø | ø    | 1    | ]    | ø | 1 | ø      | Ø     | Ø | ø | FIELD Ø |

|-------|----|----|-----|-------|----|---|------|------|------|---|---|--------|-------|---|---|---------|

| Ø     | ø  | ø  | ø   | ø     | Ø  | ø | Ø    | Ø    | Ø    | Ø | Ø | Ø      | Ø     | H | a | FIELD 1 |

|       |    |    | 1   | 1     |    |   | 0 AI | DRES | SS a | 1 |   | 1<br>1 | 1<br> |   |   | FIELD 2 |

| 1.5   | 14 | 13 | 1 2 | . 11. | 10 | 9 | 8    | 7    | 6    | 5 | 4 | 3      | 2     | 1 | 0 |         |

**OPERATION:**

AM<sub>1.5</sub> + UNALIGNED(ADDRESS)

$MEM_{5.5}(ADDRESS) \leftarrow DM_{1.5}$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS, DATA), if there is other data on the AM or the DM in the above specified BUS cycles. 3. Page address overrange if enabled to AER line.

#### **DESCRIPTION:**

The address is sent to Data Memory on the ADDRESS MULTIBUS. Data Memory takes the data on the DATA MULTIBUS, and, after a delay, stores the data at the specified address.

EXAMPLE:

WUS FUN1

# WUID a,n

#### WRITE UNALIGNED INDEXED DOUBLE

| ø | Ø      | Ø | ø  | Ø   | Ø | Ø | Ø    | ,    | 1  | 1 | 1 | 1 | Ø | Ø  | Ø | FIELD | ø |

|---|--------|---|----|-----|---|---|------|------|----|---|---|---|---|----|---|-------|---|

| ø |        |   | IN | DEX | n |   |      | ø    | Ø  | Ø | Ø | Ø | ø | HI | a | FIELD | 1 |

|   | r<br>r |   |    |     |   | L | O AD | DRES | Sa |   |   |   |   |    |   | FIELD | 2 |

**OPERATION:**

$AM_{1} \leftarrow UNALIGNED(ADDRESS+I_{\emptyset}(INDEX))$   $AM_{1.5} \leftarrow UNALIGNED(ADDRESS+I_{\emptyset}(INDEX)+1)$  $MEM_{5}(ADDRESS+I_{\emptyset}(INDEX)) \leftarrow DM_{1}$

$MEM_{5.5}(ADDRESS+I_0(INDEX)+1) \leftarrow DM_{1.5}$

ERROR CONDITION(S):"

- 1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS, DATA), if there is other data on the AM or the DM in the above specified BUS cycles.

- 3. Page address overrange/underrange if enabled to AER line.

#### **DESCRIPTION:**

The address sent out on the ADDRESS MULTIBUS to DATA MEMORY is obtained by adding the given address to the contents of the specified INDEX register. DATA MEMORY takes the data pair on the DATA MULTIBUS, and, after a delay, stores the data at the specified addresses.\*

\*This instruction is included primarily for maintenance purposes; a memory page access error will occur if the indexed address is not the last address of a memory page.

**EXAMPLE:**

WUID FUN1, 17

WUIF a,n

# WRITE UNALIGNED IN T D FIRST

| Ø | Ø | Ø | Ø   | A.   | Þ | Ø | Ø    | 1    | 1  |   | Ø |        | Ø     | Ø  | Ø | FIELD | ø |

|---|---|---|-----|------|---|---|------|------|----|---|---|--------|-------|----|---|-------|---|

| Ø |   |   | IND | EX n |   |   |      | Ø    | Ø  | Ø | Ø | ø      | ø     | HI | a | FIELD | 1 |

|   |   |   |     |      |   | L | O AD | DRES | Sa |   |   | l<br>L | l<br> |    |   | FIELD | 2 |

**OPERATION:**

$AM_1 \leftarrow UNALIGNED(ADDRESS+I_0(INDEX))$

$MEM_5(ADDRESS + I_0 (INDEX)) \leftarrow DM_1$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- BUS conflict (ADDRESS, DATA), if there is other data on the AM or the DM in the above specified BUS cycles. 2.

- 3. Page address overrange/underrange if enabled to AER line.

## **DESCRIPTION:**

The address sent out on the ADDRESS MULTIBUS to Data Memory is obtained by adding the given address to the contents of the specified INDEX register. Data Memory takes the data on the DATA MULTIBUS, and, after a delay, stores the data at the specified address.

**EXAMPLE:**

WUIF FUN1,18

## WRITE UNALIGNED INDEXED SECOND

| Ø | Ø | Ø | Ø    | Ø | ø | Ø     | Ø    | 1    | 1  | 1 | 1 | Ø | Ø | Ø  | ø | FIELD | Ø |

|---|---|---|------|---|---|-------|------|------|----|---|---|---|---|----|---|-------|---|

| Ø |   | I | VDEX | n |   |       |      | Ø    | Ø  | Ø | Ø | ø | Ø | ΗI | a | FIELD | 1 |

|   |   |   |      |   |   | са LC | ) AD | DRES | Sa |   |   |   |   |    |   | FIELD | 2 |

**OPERATION:**

$AM_{15} \leftarrow UNALIGNED(ADDRESS+I_{a}(INDEX))$  $MEM_{5.5}(ADDRESS + I_{\emptyset}(INDEX)) \leftarrow DM_{1.5}$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- BUS conflict (ADDRESS, DATA), if there is other data on the AM or the 2. DM in the above specified BUS cycles. Page address overrange/underrange if enabled to AER line.

- 3.

# /DESCRIPTION:

The address sent out on the ADDRESS MULTIBUS to Data Memory is obtained by adding the given address to the contents of the specified INDEX register. Data Memory takes the data on the DATA MULTIBUS, and, after a delay, stores the data at the specified address,

EXAMPLE:

12

. a

WUIS FUN1, 15

### 7.2.3.3 Aligned Read/Write Instructions

In general, an address alignment network is a hardware device which maps the program address space into the physical address space of the memory. The purpose of an address alignment network in the AD 10 is to allow data transfers to or from Data Memory to be performed for a specific type of application in such a way as to take maximum advantage (from the standpoint of data transfer rate) of the overlapped page architecture of the Data Memory.

The address alignment network in MAP is designed to map a linear array in program address space into Data Memory such that any pair of words with consecutive addresses (i.e., addresses ADDR and ADDR+1) in program address space will be located in adjacent pages in Data Memory.

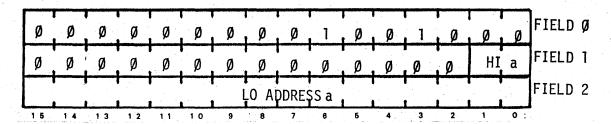

If a MAP read or write instruction specifies an aligned address, the address alignment network takes the program address, ADDR, (see Figure 7.2) and converts it to a Data Memory address which it outputs to the ADDRESS/CONTROL MULTIBUS. The conversion performed by the address alignment network on ADDR is:

$AM_1(14:19) \leftarrow ADDR_{\emptyset}(\emptyset, 13:17)$  (PAGE ADDRESS)  $AM_1(\emptyset:11) \leftarrow ADDR_{\emptyset}(1:12)$  (WORD ADDRESS)

The operation of the address alignment network for an aligned read or write instruction is illustrated in the diagram below.

The aligned address read/write instructions are:

|          | we have a second se |

|----------|----------------------------------------------------------------------------------------------------------------|

| RAD a    | READ MINED DOUBLE                                                                                              |

| RAF a    | READ LIGHED FIRST                                                                                              |

| RAS a    | READ N IMGED SECOND                                                                                            |

| RAID a,n | READ ALIGNED INDEXED DOUBLE                                                                                    |

| RAIF a,n | READ ALIGNED INDEXED FIRST                                                                                     |

| RAIS a,n | READ ALIGNED INDEXED SECOND                                                                                    |

| WAD a    | WRITE ALIGNED DOUBLE                                                                                           |

| WAF a    | WRITE ALIGNED FIRST                                                                                            |

| WAS a    | WRITE ALIGNED SECOND                                                                                           |

| WAID a,n | WRITE ALIGNED INDEXED DOUBLE                                                                                   |

| WAIF a,n | WRITE ALIGNED INDEXED FIRST                                                                                    |

| WAIS a,n | WRITE ALIGNED INDEXED SECOND                                                                                   |

|          |                                                                                                                |

#### READ ALIGNED DOUBLE

**OPERATION:**

$AM_1 \leftarrow ALIGNED(ADDRESS)$  $AM_{1.5} \leftarrow ALIGNED(ADDRESS+1)$  $DM_5 \leftarrow MEM_1(ADDRESS)$  $DM_{5.5} \leftarrow MEM_{1.5}(ADDRESS+1)$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- BUS conflict (ADDRESS,DATA), if there is other data on the AM or the DM in the above specified BUS cycles. Page address overrange if enabled to AER line. 2.

- 3.

**DESCRIPTION:**

A pair of addresses is sent on the ADDRESS MULTIBUS to Data Memory. After a delay, the data will appear on the DATA MULTIBUS.

**EXAMPLE:**

RAD FUN1 **!GET TWO FUNCTION VALUES**

## RAF a

# **READ ALIGNED FIRST**

$DM_5 \leftarrow MEM_1 (ADDRESS)$

ERROR CONDITION(S):

1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS,DATA), if there is other data on the AM or the DM in the above specified BUS cycles.

- 3. Page address overrange if enabled to AER line.

### **DESCRIPTION:**

The address is sent on the ADDRESS MULTIBUS to Data Memory. After a delay, the data will appear on the DATA MULTIBUS.

EXAMPLE:

RAF FUN1 !GET DATA POINT

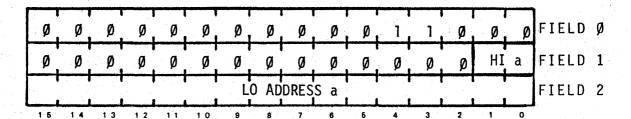

RAS a

# READ ALIGNED SECOND

| ø   |    | Ø  |     |    |          | p |    |      |     |                | , <u> </u> | Ø | Ø | Ø  | Ø | FIELD Ø |

|-----|----|----|-----|----|----------|---|----|------|-----|----------------|------------|---|---|----|---|---------|

| Ø   | Ø  | Ø  | Ø   | Ø  | <u> </u> | Ø | Ø  | Ø    | Ø   | Ø              | Ø          | ø | Ø | HI | a | FIELD 1 |

|     |    |    |     | 1  | y 1      | 1 | LO | ADDR | ESS | l <sup>a</sup> | l<br>I     |   | 1 |    |   | FIELD 2 |

| 1.5 | 14 | 13 | 1 2 | 11 | 1.0      | 9 | 8  | 7    | 6   | 5              | 4          | 3 | 2 | 1  | 0 | -       |

**OPERATION:**

$AM_{1.5} \leftarrow ALIGNED(ADDRESS)$

$DM_{5.5} \leftarrow MEM_{1.5}(ADDRESS)$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS,DATA), if there is other data on the AM or the DM in the above specified BUS cycles.

- 3. Page address overrange if enabled to AER line.

#### DESCRIPTION:

The address is sent out on the ADDRESS MULTIBUS to Data Memory. After a delay, data will appear on the DATA MULTIBUS.

EXAMPLE:

RAS FUN1 !GET DATA VALUE

## RAID a,n

# READ ALIGNED INDEXED DOUBLE

**OPERATION:**

$AM_{1} \leftarrow ALIGNED(ADDRESS+I_{\emptyset}(INDEX))$   $AM_{1.5} \leftarrow ALIGNED(ADDRESS+I_{\emptyset}(INDEX)+1)$   $DM_{5} \leftarrow MEM_{1}(ADDRESS+I_{\emptyset}(INDEX))$   $DM_{5.5} \leftarrow MEM_{1.5}(ADDRESS+I_{\emptyset}(INDEX)+1)$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS, DATA), if there is other data on the AM or the DM in the above specified BUS cycles.

- 3. Page address overrange/underrange if enabled to AER line.

#### **DESCRIPTION:**

The address sent out on the ADDRESS MULTIBUS to Data Memory is obtained by adding the given address to the contents of the specified INDEX register. After a delay, data will appear on the DATA MULTI

EXAMPLE:

RAID FUN1, IØ !GET FUNCTION PAIR

#### READ ALIGNED INDEXED FIRST

|   |   | Ø | Ø | Ø  | Ø   | Ø | Ø | Ø    | Ø    | Ø  | 1 | Ø | 1 | Ø | Ø | ø  | FIELD | Ø |

|---|---|---|---|----|-----|---|---|------|------|----|---|---|---|---|---|----|-------|---|

| Ø | 0 |   |   | IN | DEX | n |   |      | ø    | Ø  | ø | Ø | Ø | Ø | Н | Ιa | FIELD | 1 |

|   |   |   |   |    |     |   | L | ) Ad | DRES | Sa |   |   |   |   |   |    | FIELD | 2 |

**OPERATION:**

$AM_1 \leftarrow ALIGNED(ADDRESS+I_0(INDEX))$

$DM_5 \leftarrow MEM_1(ADDRESS+I_0(INDEX))$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS, DATA), if there is other data on the AM or the DM in the above specified BUS cycles.

- 3. Page address overrange/underrange if enabled to AER line.

# DESCRIPTION:

The address sent out on the ADDRESS MULTIBUS to Data Memory is obtained by adding the given address to the contents of the specified INDEX register. The address is sent out on the ADDRESS MULTIBUS to Data Memory. After a delay, data will appear on the DATA MULTIBUS.

EXAMPLE:

RAIF FUN1, I2 !GET DATA VALUE

# READ ALIGNED INDEXED SECOND

**OPERATION:**

$AM_{1.5} \leftarrow ALIGNED(ADDRESS+I_{0}(INDEX))$  $DM_{5,5} \leftarrow MEM_{1,5}(ADDRESS+I_{0}(INDEX))$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- BUS conflict (ADDRESS, DATA), if there is other data on the AM or the 2.

- 3.

- DM in the above specified BUS cycles. Page address overrange/underrange if enabled to AER line.

DESCRIPTION:

The address sent out on the ADDRESS MULTIBUS to Data Memory is obtained by adding the given address to the contents of the specified INDEX register. After a delay, data will appear on the DATA MULTIBUS.

EXAMPLE:

RAIS FUN1, I3 IGET DATA VALUE

#### WRITE ALIGNED DOUBLE

|              | <u> </u> | . <u>Р</u> | μ, | Ø | , Ø | Ø | 1 | Ø | , 1 . | 1 | Ø | Ø | Ø       | FIELD Ø |

|--------------|----------|------------|----|---|-----|---|---|---|-------|---|---|---|---------|---------|

|              | N +      |            |    |   |     |   | • | • | •     |   |   |   |         |         |

| LO ADDRESS a |          |            |    |   |     |   |   |   |       |   |   |   | FIELD 2 |         |

**OPERATION:**

ALIGNED(ADDRESS) AM<sub>1</sub> +

AM<sub>1.5</sub> ALIGNED(ADDRESS+1) \*

$MEM_{5}(ADDRESS) \leftarrow DM_{1}$

$MEM_{5.5}(ADDRESS+1) \leftarrow DM_{1.5}$

## ERROR CONDITION(S):

1. Memory page accessed too soon after previous access.

BUS conflict (ADDRESS, DATA), if there is other data on the AM or the DM in the above specified BUS cycles. Page address overrange if enabled to AER line. 2.

3.

## DESCRIPTION:

An address pair is sent out on the ADDRESS MULTIBUS to Data Memory. Data Memory takes the data pair on the DATA MULTIBUS, and, after a delay, stores the data at the specified addresses.

EXAMPLE:

WAD FUNOUT1

#### WAF a

# WRITE ALIGNED FIRST

**OPERATION:**

$AM_1 \leftarrow ALIGNED(ADDRESS)$

$MEM_{5}(ADDRESS) \leftrightarrow DM_{1}$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous address.

- 2. BUS conflict (ADDRESS, DATA), if there is other data on the AM or the DM in the above specified BUS cycles.

- 3. Page address overrange if enabled to AER line.

#### **DESCRIPTION:**

The address is sent out to DATA MEMORY on the ADDRESS MULTIBUS. Data Memory takes the data on the DATA MULTIBUS, and, after a delay, stores the data at the specified address.

EXAMPLE:

WAF FUN2

WRITE ALIGNED SECOND

**OPERATION:**

$AM_{1.5} \leftarrow ALIGNED(ADDRESS)$

$MEM_{5.5}(ADDRESS) + DM_{1.5}$

ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS, DATA), if there is other data on the AM or the DM in the above specified BUS cycles.

- 3. Page address overrange if enabled to AER line.

#### **DESCRIPTION:**

The address is sent out on the ADDRESS MULTIBUS to Data Memory. Data Memory takes the data on the DATA MULTIBUS, and, after a delay, stores the data at the specified address.

EXAMPLE:

WAS FUN1

# WAID a,n

#### WRITE ALIGNED INDEXED DOUBLE

| Ø | Ø | Ø | Ø  | Ø   | Ø      | Ø | Ø    | Ø    | 1  | 1 | 1 | 1 | Ø      | Ø  | Ø | FIELD | Ø |

|---|---|---|----|-----|--------|---|------|------|----|---|---|---|--------|----|---|-------|---|

| Ø |   | 1 | IN | DEX | n      |   | 1    | Ø    | ø  | Ø | Ø | Ø | Ø      | HI | a | FIELD | 1 |

|   |   | 1 |    |     | ۱<br>۱ | L | 0 AC | DRES | Sa |   | l |   | I<br>I |    |   | FIELD | 2 |

**OPERATION:**

$AM_1 \leftarrow ALIGNED(ADDRESS+I_{\alpha}(INDEX))$

$AM_{1.5} \leftarrow ALIGNED(ADDRESS+I_d(INDEX)+1)$

$MEM_5(ADDRESS+I_0(INDEX)) \leftarrow DM_1$

$MEM_{5.5}(ADDRESS+I_{\emptyset}(INDEX)+1) \leftarrow DM_{1.5}$

## ERROR CONDITION(S):

- 1. Memory page accessed too soon after previous access.

- 2. BUS conflict (ADDRESS, DATA), if there is other data on the AM or the DM in the above specified BUS cycles.

- 3. Page address overrange/underrange if enabled to AER line.

#### **DESCRIPTION:**

The address pair sent out on the ADDRESS MULTIBUS to Data Memory is obtained by adding the given address to the contents of the specified INDEX register. Data Memory takes the data pair on the DATA MULTIBUS, and, after a delay, stores the data at the specified addresses.

EXAMPLE:

WAID FUN1, 16

#### WAIF a,n

## WRITE ALIGNED INDEXED FIRST

| Ø |     |   | Ø  | Ø                                                                                                                                                                                                                                  | Ø   | Ø   | Ø | ø    | Ø    | 1      | ,<br>, 1, | Ø            | 1 | Ø | Ø | Ø  | FIELD | ø |

|---|-----|---|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---|------|------|--------|-----------|--------------|---|---|---|----|-------|---|