QUARTERL JOURNAL FOR XILINX PROGRAMMABLE LOGIC USERS ΗE γ

The Programmable Logic Company<sup>SM</sup>

### **InsideThisIssue:**

#### **GENERAL**

| Fawcett: PLDs, Pins, PCBs     | 2       |

|-------------------------------|---------|

| Guest Editorial               | 3       |

| Foundry Joint Venture         | 4       |

| Wim Roelandts New CEO         | 6       |

| Xilinx Ireland Earns ISO 9002 | 6       |

| Customer Success Story        | 7       |

| New Product Literature        | 8       |

| Financial Results             | 8       |

| Upcoming Events               | 9       |

| Xilinx Wins Awards in Japan   | 9       |

| Alliance Program Now On-Line  | 10      |

| Training Information on Web   | 10      |

| Introducing SmartSearch       | 11      |

| Component Availability Chart  |         |

| Alliance Program Charts       | . 14-16 |

| Programming Support Charts    | . 17-19 |

| Development Systems Chart     | 20      |

#### PRODUCTS

| Introducing the XC4000E/EX   | 21-23 |

|------------------------------|-------|

| Low Voltage Line Expands     | 24-25 |

| Designing with XC9500 CPLDs  |       |

| XC4000E in Production        | 26    |

| DSP Design Contest           | 26    |

| XC5200 Family on Record Pace | 26    |

#### **DEVELOPMENTSYSTEMS**

| LogiCore Modules            | 27,32 |

|-----------------------------|-------|

| XABEL-CPLD on CD            |       |

| Series 8000 Adds Schematics | 28-29 |

| New XC7000 Core Software    |       |

| PowerGuide                  |       |

#### **HINTS & ISSUES**

| Selecting a Product Family      | 33    |

|---------------------------------|-------|

| JTAG Support for XC9500 Family  | 34-35 |

| FIFO Buffer Design              | 36-38 |

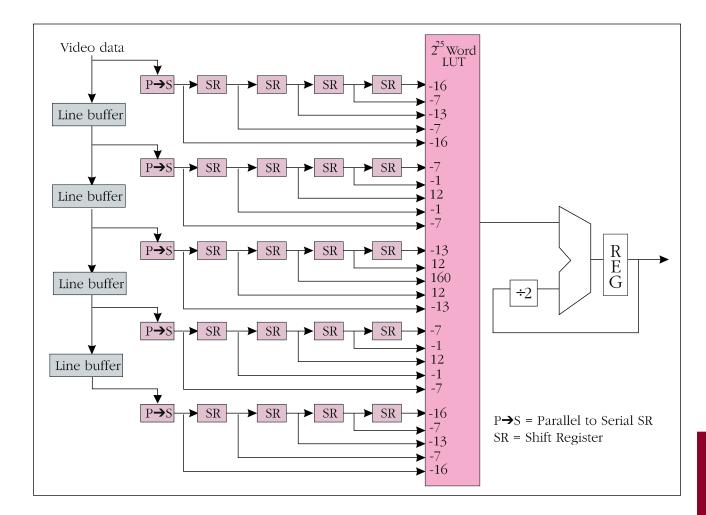

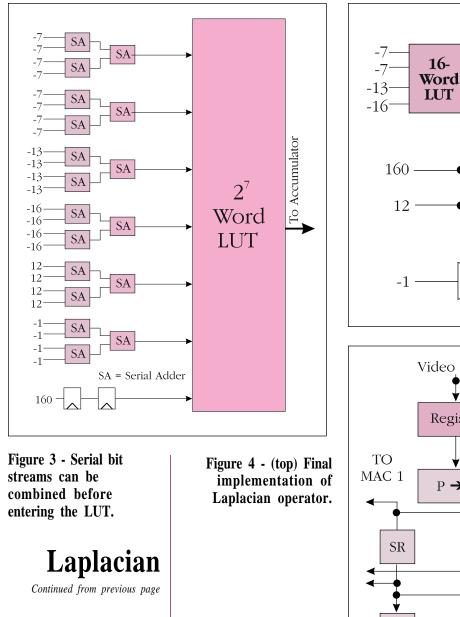

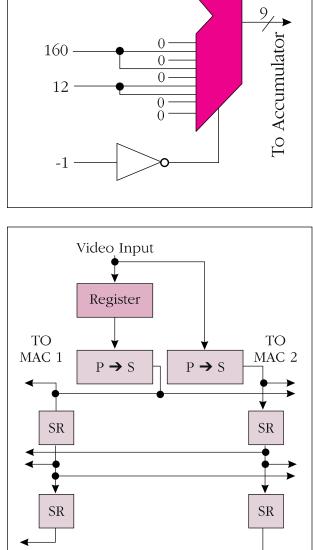

| Laplacian Filters               | 38-40 |

| Retargeting in Design Architect | 41    |

| FPGA Audio Processing           | 42-43 |

| Using Decoupling Capacitors     | 42-43 |

| Questions & Answers             | 44-47 |

| Technical Support Resources     | 47    |

| Fax Response Form               | 48    |

|                                 |       |

### PRODUCTINFORMATION

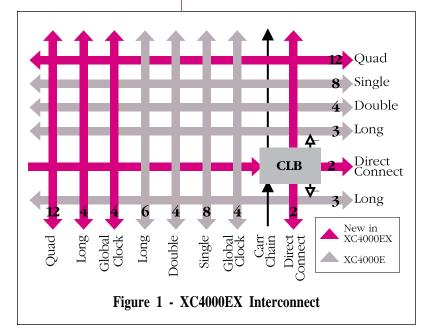

125K Gates: Introducing The XC4000EX FPGA Family

**Extending FPGA capacities beyond** 125,000 gates, Xilinx adds to its powerful series of XC4000-based architectures...

See Page 21

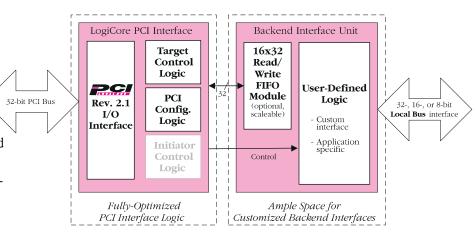

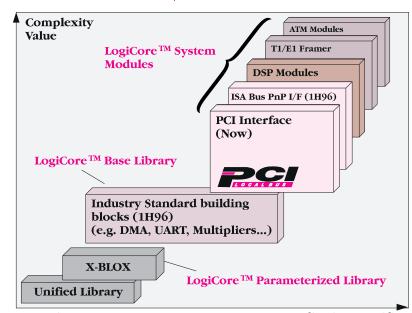

### LogiCore<sup>™</sup> Modules Accelerate Time-to-Market

The LogiCore PCI Interface is the first in a series of pre-implemented and fully verified "drop-in modules" for FGPA designs created to accelerate the already fast development process for FPGA devices...

See Page 27

### DESIGN TIPS & HINTS

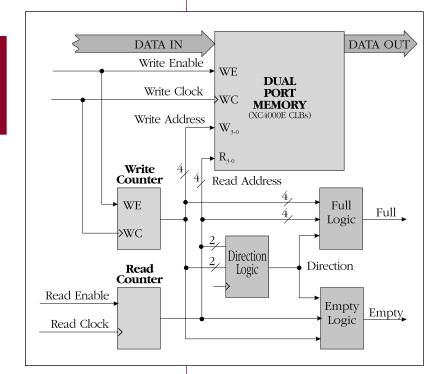

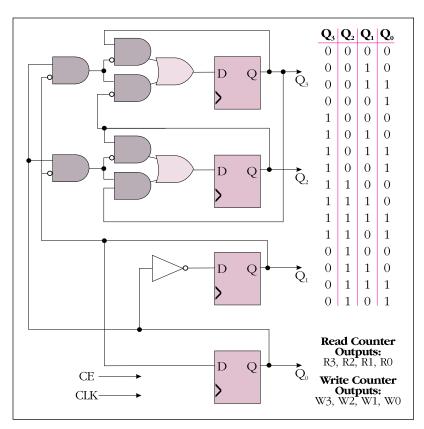

### **FIFO Buffer Design** in the XC4000E/EX

Using distributed RAM to build high performance FIFO buffers... See Page 36

### **Exploiting Rapid Reconfiguration** in an Audio Processor

Metalithic Systems' FPGA-based audio authoring system debuts...

See Page 42

Enter the DSP Design Contest. See page 26 for details.

#### FROMTHEFAWCETT

Part 1 of 2

# PLDs, Pins and PCBs

#### By BRADLY FAWCETT $\blacklozenge$ Editor

Change is inevitable. The best system designers recognize this axiom and incorporate tolerance for change into their schedules, design methodologies, and

even the physical realizations of their designs.

Changes can occur during all stages of a product's life cycle. Surveys suggest that as much as 50% of the typical product's development time is spent in the debug/modify/reimplement cycle that

occurs after the first prototype is created. Even if the designer is skilled (and lucky) enough to create a working prototype on the first try, the product specification can change in the meantime in response to changing market conditions. In some cases, products that already have been

produced and sold for months or even years have been modified to extend the product's life (or, heaven forbid, to correct some previously undetected flaw).

Tolerance of change is one of the prime attractions of program-

mable logic devices. With PLDs, design changes can be implemented quickly and easily, especially as compared to custom and semicustom IC technology. However, when it comes to tolerating changes, printed circuit boards (PCBs) are more like custom ICs than PLDs. To modify a PCB, new drawings (masks) must be created, and new prototypes must be manufactured, with all the associated expenses and delays. Thus, to garner the true benefits of the adaptability of programmable logic, programmable logic device architectures should isolate the PCB design from logic changes that occur within the device. As a result, two concepts that should be of primary concern to PLD users are pinlocking and footprint compatibility.

Pin-locking refers to the ability to establish a fixed pin location for all the signals entering and leaving a PLD so that the PCB layout, in turn, can be fixed. Since PCB design and production is often a critical path in product development, most designers would prefer to lock PLD pin locations early in the design cycle. However, with some PLDs, this can be a risky proposition; the chosen pinout may prove to be less than optimal after the implementation of the inevitable design changes, leading to decreased performance, or, in the worse case, a design that

••Tolerance of change is one of the prime attractions of programmable logic devices." cannot be implemented at all due to routing limitations within the PLD. Designers that used the earliest generations of CPLDs and FPGAs may recall that PLD manufacturers routinely warned their users not to begin their

PCB design until the PLD design was completed and debugged. This reputation, established in the early days of high-density PLDs — that is, that design changes can be difficult or impossible to implement without changing the device pinout lingers on today (and deservedly so, for some of our competitors' offerings!).

However, those days have long passed for Xilinx FPGA and CPLD devices.

# XCELL

Please direct all inquiries, comments and submissions to:

Editor: Bradly Fawcett

#### Xilinx, Inc.

2100 Logic Drive San Jose, CA 95124 **Phone:** 408-879-5097 **FAX:** 408-879-4676 **E-Mail:** brad.fawcett@xilinx.com

©1996 Xilinx Inc. All rights reserved.

XCELL is published quarterly for customers of Xilinx, Inc. Xilinx, the Xilinx logo and XACT are registered trademarks; all XC-designated products, UIM, HardWire, XACTstep and XACT-Performance are trademarks; and "The Programmable Logic Company" is a service mark of Xilinx, Inc. All other trademarks are the property of their respective owners.

#### **GUESTEDITORIAL**

### In-System Programming and Flash Technology for CPLDs

**By NICK KUCHAREWSKI** • Vice President, EPLD Division

The latest wave of complex programmable logic devices (CPLDs) has been targeted at an emerging applications area: In-System Programmability (ISP). In-system programmable CPLDs allow the user to mount an unprogrammed device on the PC board, then program the device as part of the manufacturing flow. This greatly eases the handling problems associated with fine pitch packages such as the popular plastic quad flat pack (PQFP). But this is far from the only advantage of ISP CPLDs.

Designers can use ISP devices to meet a wide range of needs — from facilitating an integrated design, program, and test environment that allows easy prototyping and system debug, all the way to providing the ability to upgrade a design in the field through CPLD reconfiguration. Of course, manufacturing support must be provided for integrated device programming and board-level test. We refer to supporting this range of user requirements as "supporting the total product life cycle" with in-system programmable CPLDs. As more and more users begin to take full advantage of ISP capabilities during all stages of a product's life, the use of ISP CPLDs will continue to increase. In turn, CPLD manufacturers will need to offer device architectures and development tools that support this full range of user needs in order to remain competitive.

#### Introducing the FastFLASH<sup>TM</sup> XC9500<sup>TM</sup> Family

The XC9500 family is the first CPLD family specifically developed to meet all the typical user requirements for in-system programmability. Xilinx used those requirements to drive the XC9500 development process, including basic device architecture decisions and process technology choices. Let's take a closer look at some of these requirements, and their impact on the CPLD.

As mentioned in Brad Fawcett's editorial (*see page 2*), the flexibility of ISP is enhanced by the ability to fix the chip pinouts ("lock the pins") while continuing to implement design changes. Obviously, the reconfiguration of CPLDs already in the field requires maintaining fixed pinouts to be successful. The approach we have taken to solving this challenge is quite complex and involves several architectural innovations as well as improvements to the optimization and fitter software. The result is the industry's best pin-locking CPLD.

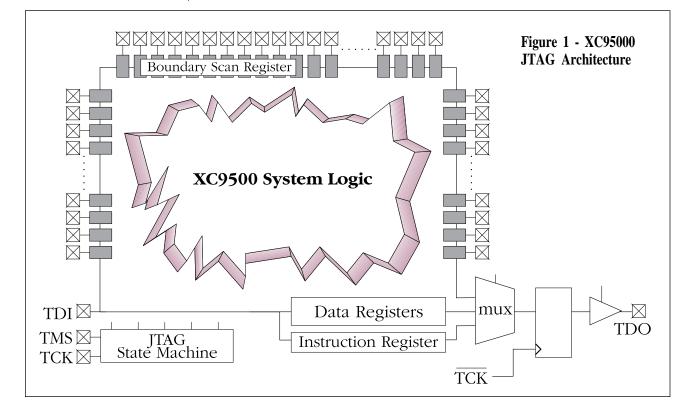

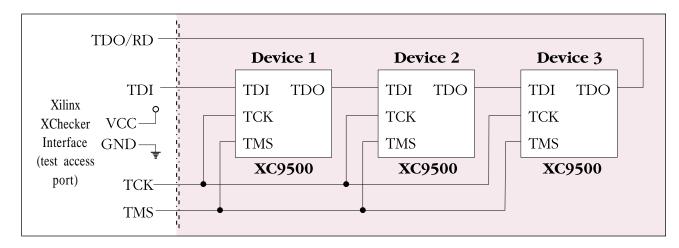

Many users require complete support of industry-standard IEEE 1149.1 JTAG boundary scan test capabilities. By including the in-system programming control within the JTAG controller, both board test and device programming are accomplished with a single interface, and in an integrated environment. This greatly simplifies the manufacturing engineering requirements. The XC9500 is the only CPLD to include support for JTAG instructions such as INTEST and USERCODE. The INTEST instruction is used to test internal logic after device programming on the PC board,

•

•

**66**The XC9500 family is the first CPLD family specifically developed to meet all the typical user requirements for in-system programmability. **9**

Continued on the next page

### Xilinx Enters Into Joint Venture for Foundry Capacity

In a joint venture with United Microelectronics Corporation (UMC) and others, Xilinx has invested a 25% equity stake in a semiconductor manufacturing facility in Hsin Chu City, Taiwan.

Xilinx is one of more than 100 semiconductor companies that use independent silicon "foundries" rather than their own wafer fabrication facilities. Being "fabless" allows the company to focus on what Xilinx does best — the design and marketing of programmable logic devices. Xilinx transcends the scope of traditional customer-supplier relationships by employing its own process experts, who work closely with our foundry partners in the development and implementation of process technology improvements.

The Taiwan facility will ensure a steady and reliable supply of product as the demand for programmable logic devices continues to grow. Starting its two-year ramp up cycle in early 1996, the factory will produce eight-inch wafers using submicron CMOS processes. In the meantime, UMC will provide Xilinx with interim capacity at its other facilities in Taiwan.

Xilinx will maintain its existing foundry partnerships with Seiko Epson, Yamaha, Taiwan Semiconductor Manufacturing Company (TSMC) and IC Works. While the UMC investment marks the first time Xilinx has taken an equity position in a foundry, it is not the first Xilinx investment involving its foundry partners. For example, in early 1994, Xilinx helped fund Seiko Epson's expansion of an IC facility in Sakata, Japan.

"This new venture ensures foundry capacity of leading-edge process technologies to meet the rising demand for FPGAs," noted Xilinx CEO Bernie Vonderschmitt. "This agreement, combined with our other foundry partnerships, favorably positions the company to meet customer demand to the end of the decade." ◆

#### **GUESTEDITORIAL**

Continued from the previous page

while the USERCODE function allows the user to "program in" information such as version numbers, assembly locations, or dates as part of the manufacturing process.

#### Flash Process Technology

An easy-to-use, integrated design and programming environment allows designers to implement multiple design iterations per day. This can translate into a need to support hundreds, and perhaps thousands, of program-erase cycles. Flash process technology provides this capability, with margin to spare. The Xilinx proprietary FastFLASH Technology is the industry's first 5-volt flash technology developed specifically for CPLD applications. It is an extension of industry-standard flash memory technology, and offers the proven reliability of 10,000 program-erase cycles — a factor of up to 100 times more than competing ISP CPLDs.

The benefits of flash technology extend beyond program-erase endurance. The flash memory cell provides the basic programmable "switch" in the XC9500 CPLDs. The size of the flash memory cell is about 1/3 that of other non-volatile technologies, allowing the implementation of many more "switches" in the same chip area. These added resources lead to improved routability and pin-locking capability.

In-system programmability is an increasingly important requirement for CPLDs. The needs of ISP CPLD users extend beyond easier handling of PQFP packages to more complete support of "the total product life cycle." The architecture, process technology and development tools of the XC9500 FastFLASH family meet these needs, allowing users to take full advantage of the flexibility of ISP technology. ◆

#### THEFAWCETT

#### Continued from page 2

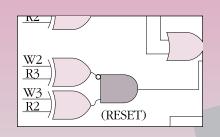

Pin-locking is not an issue with Xilinx CPLDs. The XC7300 and XC9500 CPLD families offer the ultimate in pin-locking capability, with 100% connectivity through the CPLD's internal switch matrix. Thus, any I/O pin can be connected to any function block input or output, regardless of utilization levels. Design changes internal to the CPLD will seldom force pinout changes.

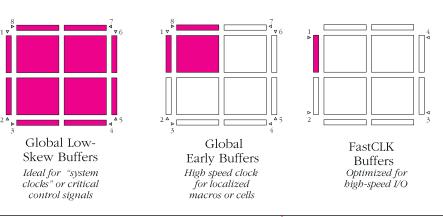

While the Xilinx FPGA families cannot provide the same guarantee of full connectivity offered by the Xilinx CPLDs, the latest generations do provide a high degree of flexibility in their I/O connections. All recent Xilinx FPGA architectures, including the XC5200, XC4000E, XC4000EX, XC6200, and XC8100 families, embrace the VersaRing<sup>™</sup> concept introduced in the XC5200 family. Simply put, these FPGAs include an extra layer of routing resources along the perimeter of the logic array to increase routing flexibility between the internal array and the I/O blocks. User feedback is confirming that these devices deliver on the promise of allowing lastminute design changes without changes to the I/O pin locations.

Actually, this capability also is present to a large degree in the "older" XC4000 series FPGAs. The popular XC4000 family was the subject of the only independent research study (that I know of) that examined pin-locking in FPGA architectures. As reported at the 3rd Canadian Workshop on Field-Programmable Devices last May, researchers at the University of Toronto implemented sixteen different designs in XC4000 devices. The designs were first routed with no placement constraints, then with "bad" pin constraints (wherein signals that were assigned to adjacent pins in the unconstrained design were now assigned to opposite ends of the device), and, lastly, with a randomly-generated pin

placement. In every case, the designs routed to completion, albeit with a slight performance impact; the average signal delay increase was less than 5% for the "bad" constraints and 3% for the random constraints. Significantly, the researchers concluded that "Fixed pin assignment does impact routability significantly, because the amount of routing resources used was increased, but the Xilinx XC4000 series architecture provided sufficient resources to handle the increased demand". Inciden-

tally, a major competitor's FPGA family — the only other device included in the study — did not fare nearly as well; several designs were unroutable with bad or random pin constraints, and the researchers recommended that users of that FPGA "should leave about 20% of the logic elements and I/O pins free to avoid routability problems due to pin constraints."

In conclusion, while "intelligent" placement of I/O pins is still recommended, Xilinx FPGA and CPLD devices are quite tolerant of design changes without forcing the redesign of the PCB layout. This facilitates an early

release of the PCB design and eases the debugging process, thereby accelerating time-to-market, and accommodates the inevitable changes that occur throughout a product's total life cycle.

In the next issue, part 2 of this article will examine the benefits of footprint compatibility both within and across Xilinx PLD product families.

•These FPGAs include an extra layer of routing resources along the perimeter of the logic array to increase routing flexibility between the internal array and the I/O blocks. User feedback is confirming that these devices deliver on the promise of allowing last-minute design changes without changes to the I/O pin locations."

# Wim Roelandts New Xilinx CEO

New Xilinx CEO Wim Roelandts

In late January, Bernie Vonderschmitt retired as Chief Executive Officer of Xilinx. His successor is Willem "Wim" Roelandts, a 28-year veteran of Hewlett-Packard. Vonderschmitt, 72, who co-founded Xilinx in 1984, remains with the company as chairman of the board of directors, and continues to be active in the business affairs of the company.

Roelandts joined HP in 1967 as a service engineer in his native Belgium and most recently served as a senior vice president in Hewlett-Packard's Computer Systems Organization. He was responsible for all aspects of the computer systems business worldwide, including research and development, manufacturing, marketing and sales.

"Wim Roelandts is a seasoned veteran who possesses the right mix of leadership and management skills to guide Xilinx through its next period of growth," Vonderschmitt stated. "Employees, customers, and shareholders can be confident he is the right man to take the helm at Xilinx."

### Xilinx Ireland Earns ISO 9002 Certification

Xilinx Ireland, the new manufacturing facility in Dublin, was awarded ISO 9002 certification in November. The Xilinx manufacturing facility in San Jose, California, obtained ISO 9002 certification last October. The ISO quality standards were developed by the International Organization for Standardization, a Geneva-based organization with representatives from 91 countries.

As noted by Derek Kernan, quality manager at Xilinx Ireland, "The ISO standard is widely-recognized in Europe and is a very good means of measuring the quality of our processes and the extent to which the development of the company is keeping pace with our overall strategy. Acquiring ISO certification has made us look at all our processes and all our customers' requirements and understand what we can do better. For us, it represented a good external measure of the value and quality of our systems."

Xilinx Ireland, the company's first wholly-owned manufacturing facility outside of the United States, produces and distributes component products for Europe and other international markets. More than one million FPGA devices were shipped from Xilinx Ireland within the first six months of operation. The facility will

> eventually replicate all the activities of the company headquarters in San Jose, with the exception of field sales and marketing.

The first group of Xilinx Ireland's software engineers has returned from training in California and has begun development work in Ireland. More than 80 staff members are now employed in Dublin. ◆

The team of Xilinx Ireland

### **30-Day Design Cycle With XC8100 FPGA Family**

Design engineers at SIXNET (Clifton Park, NY), a manufacturer of industrial control equipment, faced a daunting challenge: to build a new I/O module (from concept to installation at a customer's site) within eight weeks.

The device, a digital counter board, was required to provide position and/or velocity information for eight independent incoming signals. The digital count signals can be used singly to provide total count or velocity information, or in pairs to provide quadraturedecoded position information. Typical applications are flow metering (where a small turbine pulses at a rate proportional to the flow of a liquid) and position measurement (where a quadrature decoder tracks the motion of precision machinery).

All previous designs at SIXNET had employed 22V10 (or smaller) PLDs, using equation-based design entry as the primary development tool. While time restrictions dictated the use of programmable logic, severe space limitations drove the need for a more highly-integrated, single-chip solution. The SIXNET design team quickly narrowed its choices to a competitor's SRAM-based FPGA or the Xilinx XC8100 FPGA family.

The main elements of the design include registers to capture and synchronize incoming data, state machines for quadrature decoding, and eight 16-bit counters and latches used for position and velocity measurement. The outputs of the counters and state machines are multiplexed and output on an 8-bit bus. The clock frequency is a modest 4 MHz.

SIXNET engineers quickly discovered that it would be difficult to fit the design using the relatively large logic blocks of the SRAM-based FPGA. The counter logic is register-intensive, requiring very little logic between flip-flops, resulting in substantial "wasted" logic in each logic block. Similarly, the wide multiplexers were not a "good fit," requiring the use of many blocks, but with relatively low utilization of the logic in each block. (These problems would have been even more prevalent in the combinatorial-intensive architecture of a CPLD device.)

The same design was easily implemented in a less-expensive XC8103 FPGA. In the XC8100 FPGA architecture, each fine-grained logic cell can implement either combinatorial or sequential logic, allowing high utilization regardless of the unequal mix of combinatorial functions and flip-flops. The counters were implemented as ripple counters, both to minimize area and avoid switching noise; the flexible clocking structure of the XC8100 architecture enabled this approach. An inter-

nal quad latch with output enable — a primitive in the XC8100 library was used to latch and multiplex the eight counters onto a common bus, eliminating the multiplexing logic needed with the competitor's product.

The design was entered and implemented on a PC

using a Viewlogic schematic editor and the Xilinx XACT*step*<sup>TM</sup> Series 8000 development system, respectively. "The transition from equation entry to Viewlogic schematics was easy, " claims Dave Ellis, vice president of Engineering at SIXNET. "It was just like doing the schematic for a printed circuit board. The XC8100 tools were very easy and intuitive to use. We were able to complete the design phase from concept to a working board in less than four weeks, including learning the Viewlogic and XC8100 design tools." The controller fits on a compact 3.3"x4.3" circuit board.

In conclusion, Mr. Ellis noted, "The Xilinx XC8103 was by far the most cost-effective solution for our needs."

## <u>SIXNET</u>°

### New Product Literature

Learn about the newest Xilinx products and services through our extensive library of product literature. The most recent pieces are listed below. To order or to obtain a complete list of all available literature, please contact your local Xilinx sales representative.

| me                                                      | DESCRIPTION         | NUMBER      |

|---------------------------------------------------------|---------------------|-------------|

| FPGAs                                                   |                     |             |

| XC4000EX Overview                                       | Features & Benefits | #0010284-01 |

| XC4000 Data Sheet                                       | Technical Data      | #0010278-01 |

| XC4000E Data Sheet                                      | Technical Data      | #0010274-01 |

| Xilinx XC5200 vs. Altera FLEX 8000A FPGAs White Paper   | Technical Data      | #0010270-01 |

| LogiCore PCI Target Interface for 4000E FPGA Data Sheet | Technical Data      | #0010288-01 |

| XC3100L Data Sheet                                      | Technical Data      | #0010285-01 |

| Design Migration from XC3000/XC3000A to XC5200          | Technical Data      | #0010275-01 |

| EPLDs                                                   |                     |             |

| XABEL-CPLD Overview                                     | Features & Benefits | #0010277-01 |

| XABEL-CPLD Evaluation Software                          | CD-ROM              | #500354     |

| XC9500 Data Sheet                                       | Technical Data      | #0010280-01 |

| XC9500 Applications Guide                               | Technical Data      | #0010286-01 |

| Development Systems                                     |                     |             |

| XACT step Advanced Development System Overview          | Features & Benefits | #0010271-01 |

| XACT step 5.2 Overview                                  | Features & Benefits | #0010289-01 |

#### **FINANCIAL RESULTS**

### Revenue Grows by 58%

Xilinx sales revenues achieved a record \$144.1 million for the third quarter of fiscal year 1996 (ended December 31, 1995). This is 58% larger than the same quarter in fiscal year 1995. It shows a 2% increase from the second quarter of fiscal year 1996. This quarter's performance was affected by a slowdown in bookings, particularly in the early portion of the quarter.

Growth was particularly strong for the new XC5200 FPGA family. Revenues from this family have "ramped up" faster than any other new product family in Xilinx history.

Sales revenues for the first nine months of fiscal 1996 totaled \$411.1 million, an increase of 67% from the comparable period last year.

Looking ahead to the next quarter, CEO Bernie Vonderschmitt stated that, "We are encouraged by recent indications of a return to more normal bookings. Customer inventory corrections that we witnessed this past quarter appear to be mostly completed. Most importantly, we are encouraged by the new products that we have recently introduced, which will begin to contribute meaningful reveunes in calendar 1996."

Founded in 1984, Xilinx is the world's largest supplier of programmable logic devices. Xilinx stock is traded on the NASDAQ exchange under stock symbol XLNX.

Sales revenue up 58% over same quarter in 1995!

Fast XC5200 FPGA family production ramp up!

# Xilinx and XC8100 Receive Excellence Awards in Japan

Hitachi, Ltd. bestowed the prestigious "Hitachi Award for Excellence" on Xilinx in December. Eiji Aoki, deputy general manager of Hitachi's Telecommunications Division, presented the award to representatives of Xilinx KK in Japan.

The XC8100 FPGA was a finalist in the "ASIC of the Year" competition sponsored

by Sanyo Times Ltd., publisher of *The Semiconductor Industry News*, a weekly journal. The prize is awarded for products or technologies developed using EDA/ ESDA technology. The XC8100 FPGA family was awarded third place in a field of more than 110 entries. ◆

#### **UPCOMING EVENTS**

Look for Xilinx technical papers and/or product exhibits at these upcoming industry forums. For further information about any of these conferences, please contact Kathleen Pizzo (Tel: 408-879-5377 FAX: 408-879-4676).

| International IC Conference       | Advanced PLD & FPGA Conference        |

|-----------------------------------|---------------------------------------|

| Mar. 27-29                        | May 15                                |

| Shanghai, China                   | London, UK                            |

| DOL (AZ                           | ····································· |

| PCI '96                           | Canadian Workshop on Field Pro-       |

| Apr. 14-18                        | grammable Devices                     |

| San Jose, California              | May 20-21                             |

|                                   | Toronto, Canada                       |

| Digitronics                       |                                       |

| Apr. 17-18                        | Design Automation Conference (DAC)    |

| Birmingham, UK                    | June 3-7                              |

|                                   |                                       |

| IEEE Symposium on FPGAs for Custo | om Las Vegas, Nevada                  |

| <b>Computing Machines (FCCM)</b>  |                                       |

| Apr. 17-19                        | Intertronic                           |

| Napa, California                  | June 4-7                              |

| Napa, Camonna                     | Paris, France                         |

|                                   |                                       |

| Custom IC Conference (CICC)       | 和城区 计正式计算机 计文字系统 机转换路线 众              |

| May 5-8                           | 12%% 女人名法国东住马法法德德国法法的举举               |

| San Diego, California             | 1.1.1.素的七弦龙门竹环弦方枪路管船发袖                |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   | 后,2000年,夏天于打到夏安美国公司在11年级后,            |

|                                   | 1 一下在海南部门建筑被留然发展的做新馆                  |

|                                   | 1.4.2.多见正弦曲杆化设态始终也加杆发转的               |

|                                   | 1品法领望的众效11名法众应及努力11                   |

|                                   |                                       |

|                                   | 1 Martin Martin Martin Martin Martin  |

|                                   |                                       |

# **Xilinx Alliance Goes On-Line**

he Xilinx Alliance has been going strong for six years, and 1996 promises to be the most exciting year ever. In addition

to bringing you more world-class tools for your world-class products, we will provide easier and innovative ways to find out about the wide variety of high-quality, thirdparty design tools available through the Alliance.

One example is WebLINX, the Xilinx site on the World Wide Web. In March, the Xilinx Alliance will go on-line. An initial listing of our Alliance partners will allow you to

easily search our web pages (and our partners' pages) for product and contact information. The Xilinx SmartSearch and SmartSearch Agents utilities (see related article at right) will allow you to quickly find the information you need - whether it be product functionality, updates, or compatibility data.

As of February, the Xilinx Alliance includes more than 80 partners who have been selected for their contribution to Xilinx development systems and their ability to provide the widest variety and highest quality of design/programming

tools for Xilinx programmable logic. These vendors offer well over 100 products, including schematic editors, logic synthesis tools, simulators, third party cores, reconfigurable computing products and device programmers. (See Alliance Program EDA tool vendor and product list on pages 14-16.)

The breadth and depth of the Xilinx Alliance is not accidental. Today's programmable logic users are required to complete ever more complex and dense designs more quickly than ever before. Xilinx has recognized those needs by adopting an open systems approach to enable engineers to select the best tools for the task at hand.

So come visit Xilinx and our Alliance partners on the World Wide Web. E-mail your comments to alliance@xilinx.com. Tell us about what products you are building, what tools you are using and what tools you need - we will continue to offer you the best programmable logic development solution anywhere. The Xilinx Alliance is dedicated to your success by bringing together complete development solutions for your needs. With Xilinx programmable logic and the Xilinx Alliance, the possibilities are limitless.  $\blacklozenge$

Xilinx is adding new training courses and scheduling additional locations in 1996! To get the latest information on available classes, use the Xilinx site on the World Wide Web (http//www.xilinx.com). From the home page, select Customer Support and then Training Classes. You can even register for classes on-line.

Both schematic-based and synthesis-based three-day introductory classes are offered. In January, Xilinx began offering a series of one-day update classes on XACT step<sup>™</sup> v6, targeted at customers familiar with XACT® 5.0. Watch the web site for new training class support as new products are introduced.

Wallace Westfeldt is the

manager of the Xilinx Alliance Program. He can be

reached by telephone at 303-

wallace.westfeldt@xilinx.com.

**Alliance Program**

alliance@xilinx.com

See pages 14-16

**Vendors and Contacts**

**Alliance Program E-Mail:**

413-3280 or by E-mail at

# Introducing WebLINX SmartSearch

The Best Programmable Logic Related Web Searching

From WebLINX, the Xilinx site on the World Wide Web, you can now search and monitor the Web like never before. WebLINX *SmartSearch* is the most effective web search engine for finding information related to programmable logic. WebLINX *SmartSearch* Agents will proactively inform you when new Web information becomes available that meets your specific interests.

#### SmartSearch provides:

• Selective Multi-site Indexing WebLINX SmartSearch spans multiple

sites, not just the Xilinx site. You get "one-stop" searching of leading industry magazines such as *EE Times* and *Electronic News*, all the major EDA companies, and programmable logic-related organizations, universities and distributors. Unlike generic search engines, WebLINX *Smart*Search yields better results by only searching known content-rich sites.

For example, if you enter "PCI" in the search engine Lycos, you get pages on Berkeley UNIX pci structs and the PCI home page for geographic management software. With WebLINX *Smart*Search, you'll get more pertinent results like Synopsys' PCI Design Kit, NuHorizons' Technical Forum, the PCI SIG Group, and more.

#### • User-selectable Search Domain

WebLINX *Smart*Search allows greater control by letting users search by specific site location, such as Xilinx or Cadence. For example, you can search for "Power Dissipation" at only the EDN and Cadence web sites by entering the keywords and selecting the EDN and Cadence checkboxes before starting your search.

#### • Intra-site Searching

You can even search specific sources within a site. For example, you can search for "counters" and "XC3000A" within Xilinx Application Notes only. Simply type in "counters, XC3000A" and select the Application Notes checkbox.

#### • SmartSearch Topics

When you select topics<br/>such as "CPLD" by select-<br/>ing one of the listed<br/>check-boxes, WebLINXSmartSmartSearch will auto-<br/>matically search for all<br/>related keywords and<br/>phrases like "Program-<br/>mable Logic Device" and<br/>"EPLD," so that you don't<br/>miss results you might<br/>want. Alternatively, you<br/>can also specify literal<br/>keywords and phrases that must match<br/>precisely to make the results list.Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/>Smart<br/

#### **Proactive User Notification**

Say you're interested in the new Xilinx XC9500 family, for example. WebLINX *Smart*Search Agents will monitor the Web for XC9500 information and notify you automatically when new or modified documents become available. You can train WebLINX *Smart*Search Agents to watch for specific information at specific sites or at all of them!

SmartSearch and SmartSearch Agents are the first web information retrieval tools of their kind in any industry. Check them out by visiting our home page at http://www.xilinx.com and selecting the Search button.

#### Xilinx Web Site:

http://www.xilinx.com

**Generation** SmartSearch Agents are the first web information retrieval tools of their kind in any industry. Check them out by visiting our home page at http://www.xilinx.com."

> We're counting on you to keep our search engine useful — if there's a good web site that we're not indexing or a new topicspecific search form you'd like to see, let us know by sending e-mail to webmaster@xilinx.com.

| COMPONENT AVAILABILITY CHART |                              |                |           |                 |           |           |           |           |           |             |                  |           |         |         |            |                  |          |                  |                 |         |         |         |         |           |         |           |         |           |           |          |            |           |           |           |                  |  |

|------------------------------|------------------------------|----------------|-----------|-----------------|-----------|-----------|-----------|-----------|-----------|-------------|------------------|-----------|---------|---------|------------|------------------|----------|------------------|-----------------|---------|---------|---------|---------|-----------|---------|-----------|---------|-----------|-----------|----------|------------|-----------|-----------|-----------|------------------|--|

| PINS                         | TYPE                         |                | XC3020A   | XC3030A         | XC3042A   | XC3064A   | XC3090A   | XC3020L   | XC3030L   | XC3042L     | XC3064L          | XC3090L   | XC3142L | XC3190L | XC3120A    | XC3130A          | XC3142A  | XC3164A          | XC3190A         | XC3195A | XC4003E | XC4005E | XC4006E | XC4008E   | XC4010E | XC4013E   | XC4020E | XC4025E   | XC4028EX  | XC4036EX | XC4044EX   | XC4052EX  | XC4062EX  | XC4085EX  | XC40125EX        |  |

|                              | PLASTIC LCC                  | PC44           |           |                 |           |           |           |           |           | '           |                  |           |         |         |            | ۲                |          | Ц                |                 |         |         |         |         |           |         |           |         |           |           |          |            | L         |           | L         |                  |  |

|                              | PLASTIC QFP                  | PQ44           |           |                 |           |           |           |           |           | Ľ'          |                  |           |         |         |            |                  |          | Ц                |                 | 4       |         |         |         |           |         |           |         |           |           |          |            | L         | L         | L         |                  |  |

| 44                           | PLASTIC VQFP                 | VQ44           |           |                 |           |           |           | Ľ         |           | Ľ           |                  | $\Box$    |         |         |            |                  |          | Гļ               |                 |         |         |         |         |           |         |           |         |           |           |          |            |           | L         |           |                  |  |

|                              | CERAMICLCC                   | WC44           |           |                 |           |           |           |           |           | [_'         |                  | $\square$ |         |         | [          |                  |          |                  |                 |         |         |         |         |           |         |           |         |           |           |          | [          |           |           | Ľ         |                  |  |

| 48                           | PLASTIC DIP                  | PD48           |           |                 |           |           |           |           |           | $\Box'$     |                  |           |         |         |            |                  |          |                  |                 |         |         |         |         |           |         |           |         |           |           |          |            |           |           |           |                  |  |

| 64                           | PLASTIC VQFP                 | VQ64           |           |                 |           |           |           |           |           | ,[]'        |                  |           |         |         |            | ۲                |          |                  |                 |         |         |         |         |           |         |           |         |           |           |          |            |           |           |           |                  |  |

|                              | PLASTIC LCC                  | PC68           | ٠         |                 |           |           |           |           |           | []          |                  |           |         |         | ۲          |                  |          |                  |                 |         |         |         |         |           |         |           |         |           |           |          |            |           |           |           |                  |  |

| 68                           | CERAMIC LCC                  | WC68           |           |                 |           |           |           |           |           |             | $\square$        |           |         |         |            |                  |          |                  |                 |         |         |         |         |           |         |           |         |           |           |          |            |           |           |           |                  |  |

|                              | CERAMIC PGA                  | PG68           |           |                 |           |           |           |           |           |             |                  |           |         |         |            |                  |          |                  |                 |         |         |         |         |           |         |           |         |           |           |          |            | $\square$ | $\square$ |           | $\square$        |  |

|                              | PLASTICLCC                   | PC84           |           |                 |           |           |           |           |           |             |                  |           |         |         |            |                  |          |                  |                 |         |         |         |         |           |         |           |         |           |           |          | $\vdash$   | $\square$ | $\vdash$  | $\square$ | $\square$        |  |

| 84                           | CERAMICLCC                   | WC84           |           |                 | Ĩ         |           | T         | F         | -         | 1           |                  |           |         |         | -          |                  |          |                  |                 | Ť       |         | V       |         |           |         |           |         |           |           |          | $\vdash$   | $\square$ | $\square$ |           | $\vdash$         |  |

|                              | CERAMIC PGA                  | PG84           |           |                 | •         |           |           | $\vdash$  | $\square$ | $\vdash$    | $\vdash$         | $\square$ |         |         |            | •                | ٠        | $\vdash$         |                 |         |         |         |         |           |         |           |         |           |           |          | $\vdash$   | $\vdash$  | $\vdash$  | $\vdash$  | $\left  \right $ |  |

|                              | CERAMIC QFP                  | CQ100          |           |                 |           |           |           | H         | $\vdash$  | $\vdash$    | $\vdash$         | $\square$ |         |         | •          |                  | •        | $\vdash$         |                 |         |         |         |         | $\square$ |         | $\square$ |         | $\square$ | $\vdash$  |          | $\vdash$   | $\vdash$  | $\vdash$  | $\vdash$  | $\vdash$         |  |

|                              | PLASTIC PQFP                 | PQ100          |           |                 |           |           |           | $\vdash$  | $\vdash$  | $\vdash$    | $\vdash$         | $\vdash$  |         |         |            |                  |          | $\vdash$         | -               |         |         |         |         |           |         |           |         |           | -         |          | ┢          | $\vdash$  | $\vdash$  | $\vdash$  | $\vdash$         |  |

| 100                          | PLASTICTQFP                  | TQ100          |           |                 |           |           |           | $\vdash$  | $\vdash$  | +-'         | $\vdash$         | $\vdash$  |         |         | •          |                  |          | $\left  \right $ | -               | -       | •       |         |         |           |         |           |         |           | $\vdash$  |          | ┢          | $\vdash$  | ┢         | $\vdash$  | ┝                |  |

| 100                          | PLASTIC TQFP<br>PLASTIC VQFP | VQ100          |           | $ \rightarrow $ |           | $\square$ |           | $\vdash$  |           | +           | $\vdash$         | $\vdash$  |         |         | $\vdash$   |                  |          | $\left  \right $ | -               |         |         |         |         |           |         |           |         |           | -         | $\vdash$ | -          | $\vdash$  | $\vdash$  | -         | $\vdash$         |  |

| -                            |                              |                |           |                 |           |           |           | $\vdash$  | •         |             | $\vdash$         | $\vdash$  |         |         |            |                  | •        | $\vdash$         | -               |         | •       |         |         |           |         |           |         |           |           | $\vdash$ | ┢          | $\vdash$  | +         | $\vdash$  | ┝                |  |

| 100                          | TOP BRZ. CQFP                | CB100          |           |                 |           |           |           | -         | +         | +-'         | $\mid \mid \mid$ | $\square$ |         |         | •          |                  |          | $\vdash$         | _               | -       | -       |         |         |           |         |           |         |           | $\vdash$  |          | ╞          | ╞         | $\vdash$  | ╞         | ┢                |  |

| 120                          |                              | PG120          |           |                 |           |           |           | -         | +-'       | ⊢'          | $\square$        | $\square$ |         |         |            | $\square$        | $\vdash$ | $\square$        | _               | -       | ٠       |         |         |           |         |           |         |           | $\vdash$  |          | ╞          | $\vdash$  | $\vdash$  | ╞         | ╞                |  |

| 132                          | PLASTIC PGA                  | PP132          |           |                 |           |           |           | -         | <u> </u>  | <u> </u> '  | $\square$        | $\square$ |         |         |            | $\square$        | ۲        | •                | _               | -       |         |         |         |           |         |           |         |           |           |          | $\vdash$   | $\vdash$  | $\vdash$  | ╞         | <u> </u>         |  |

|                              | CERAMIC PGA                  | PG132          |           |                 | •         |           |           | '         | <u> </u>  | ⊥_'         | $\square$        | $\square$ |         |         |            | $\square$        | ۲        |                  |                 |         |         |         |         |           |         |           |         |           |           |          | Ļ          | ╞         | $\vdash$  | Ļ         | <u> </u>         |  |

| 144                          | PLASTICTQFP                  | TQ144          |           |                 | •         |           |           |           |           | <b>♦</b>    | •                |           | ۲       | ٠       |            |                  | ۲        |                  |                 |         |         | ٠       | ۲       |           |         |           |         |           |           |          |            |           |           |           |                  |  |

|                              | CERAMIC PGA                  | PG144          |           |                 |           |           |           |           |           | $\perp$     |                  |           |         |         |            |                  |          | Ц                |                 |         |         |         |         |           |         |           |         |           |           |          |            |           |           | L         |                  |  |

| 156                          | CERAMIC PGA                  | PG156          |           |                 |           |           |           |           |           |             |                  |           |         |         |            |                  |          |                  |                 |         |         | ۲       | ٠       |           |         |           |         |           |           |          |            |           |           |           |                  |  |

| 160                          | PLASTIC PQFP                 | PQ160          |           |                 |           |           |           |           |           | $\bot'$     |                  |           |         |         |            |                  |          | ۲                | ۲               | ۲       |         | ♦       | ۲       | ♦         |         | ♦         |         |           |           |          |            |           |           |           |                  |  |

| 164                          | CERAMIC QFP                  | CQ164          |           |                 |           |           |           |           |           | [_'         |                  |           |         |         |            |                  |          |                  |                 |         |         |         |         |           |         |           |         |           | [         |          | [          | Γ_        | T_        | T_        | <u> </u>         |  |

| 104                          | TOP BRZ. CQFP                | CB164          |           |                 |           |           |           |           |           | []          |                  |           |         |         |            |                  |          | $\square$        | ۲               | ۲       |         |         |         |           |         |           |         |           |           |          |            | $\Box$    | $\Box$    | $\Box$    |                  |  |

| 475                          | PLASTIC PGA                  | PP175          |           |                 |           |           |           |           |           |             | $\square$        |           |         |         |            |                  |          |                  | ۲               | ۲       |         |         |         |           |         |           |         |           |           |          |            | $\square$ |           | Γ         |                  |  |

| 175                          |                              | PG175          |           |                 |           |           |           |           |           |             |                  |           |         |         |            |                  |          |                  | ۲               | ۲       |         |         |         |           |         |           |         |           |           |          | $\square$  | $\square$ | $\square$ |           | $\square$        |  |

| 176                          | PLASTICTQFP                  | TQ176          |           |                 |           |           |           |           | $\square$ |             |                  |           |         |         |            |                  |          |                  | •               | Ť       |         |         |         |           |         |           |         |           |           |          | $\square$  | $\square$ | $\square$ | $\square$ |                  |  |

| 184                          | CERAMIC PGA                  | PG184          |           |                 |           |           | Ì         | $\square$ | $\square$ | +           | $\square$        |           |         |         |            |                  |          |                  |                 |         |         |         |         |           |         |           |         |           |           |          | $\vdash$   | $\vdash$  | $\vdash$  | $\vdash$  | $\square$        |  |

| 191                          | CERAMIC PGA                  | PG191          |           |                 |           |           |           | $\square$ | $\vdash$  | $\square$   | $\vdash$         |           |         |         |            | $\vdash$         |          |                  |                 |         |         |         |         |           |         |           |         |           |           |          | $\vdash$   | $\square$ | $\vdash$  | $\vdash$  | $\vdash$         |  |

| 196                          | TOP BRZ. CQFP                | CB196          |           |                 |           |           |           | Ľ         | $\vdash$  | $\vdash$    | $\vdash$         | $\vdash$  |         |         | -          | $\left  \right $ |          | $\vdash$         |                 |         |         |         |         |           |         |           |         |           | $\vdash$  |          | $\vdash$   | $\vdash$  | $\vdash$  | $\vdash$  | $\left  \right $ |  |

| 100                          | PLASTIC PQFP                 | PQ208          |           |                 |           |           |           | Ľ         | $\vdash$  | $\vdash$    | $\vdash$         | $\vdash$  |         |         | $\vdash$   | $\vdash$         |          | $\vdash$         | ٠               |         |         |         |         |           |         |           |         |           | $\vdash$  |          | ┢          | $\vdash$  | $\vdash$  | $\vdash$  | $\vdash$         |  |

| 208                          | METAL MQFP                   | MQ208          |           | $\square$       |           |           |           | $\vdash$  | $\vdash$  | $\vdash$    | $\vdash$         | $\vdash$  |         |         | $\vdash$   | $\vdash$         |          | $\vdash$         | •               | -       |         | ▼       | •       | •         | •       | •         |         |           | $\vdash$  |          | ┢          | $\vdash$  | $\vdash$  | $\vdash$  | ┝                |  |

| 200                          | HI-PERFQFP                   | HQ208          |           |                 |           |           |           | Ł         | +         | $\vdash$    | $\vdash$         | $\vdash$  |         |         | $\vdash$   | $\left  \right $ |          | $\vdash$         | $\neg$          |         | -       |         |         |           |         |           |         |           |           | -        | $\vdash$   | +         | +         | +         | +                |  |

| 002                          | CERAMIC PGA                  | HQ208<br>PG223 |           |                 | P         |           |           | $\vdash$  | +-        | +-'         | $\vdash$         | $\vdash$  |         |         | -          | $\vdash$         |          | $\vdash$         | $\neg$          |         | -       |         |         |           |         |           |         |           | *         |          |            | +         | +         | +         |                  |  |

| 223                          |                              |                |           |                 | P         |           |           | $\vdash$  | +-        | +-'         | $\vdash$         | $\vdash$  |         |         | $\vdash$   | $\left  \right $ |          | $\vdash$         | $\neg$          | ٠       | -       |         |         |           |         |           | ٠       | •         | $\vdash$  |          | -          | $\vdash$  | +         | $\vdash$  | -                |  |

| 225                          |                              | BG225          |           |                 |           |           |           | $\vdash$  | +         | +-'         | $\vdash$         | $\vdash$  |         |         | -          | $\vdash$         |          | $\vdash$         | $\rightarrow$   |         | 4       |         |         |           | •       |           |         |           | -         |          | -          | $\vdash$  | +         | $\vdash$  |                  |  |

| - 22                         |                              | WB225          |           |                 |           |           |           |           | +         | <u> '</u>   | $\vdash$         | $\square$ |         |         |            | H                |          | Щ                | $ \rightarrow $ |         |         |         |         |           |         |           |         |           | $\vdash$  |          | $\vdash$   | $\vdash$  | $\vdash$  | $\vdash$  | –                |  |

| 228                          |                              | CB228          |           |                 |           |           |           | 4         | +         | <u> </u> _' | $\vdash$         | Щ         |         |         |            | [ ]              |          | $\square$        | $\neg$          |         |         |         |         |           |         |           |         |           | $\vdash$  |          | <u> </u>   | $\vdash$  | $\vdash$  | $\vdash$  | ⊢                |  |

| -                            | PLASTIC PQFP                 | PQ240          |           |                 |           |           |           | 4         | <u> </u>  | <u> </u> '  | $\square$        | Ц         |         |         |            | $\bigsqcup$      |          | Щ                |                 |         |         |         |         |           |         | ٠         | ٠       | ٠         |           |          |            | $\vdash$  | $\vdash$  | $\vdash$  | <u> </u>         |  |

| 240                          | METAL MQFP                   | MQ240          |           |                 |           |           |           |           | $\perp$   | <u> </u> '  | $\square$        | Ц         |         |         |            | Ц                |          | Ц                |                 |         |         |         |         |           |         |           |         |           |           |          |            |           |           |           |                  |  |

|                              | HI-PERFQFP                   | HQ240          |           |                 |           |           |           |           |           | <u></u>     |                  | Ц         |         |         |            |                  |          | Ц                |                 |         |         |         |         |           |         | ۲         | ۲       |           | *         |          |            |           |           |           |                  |  |

| 299                          | CERAMIC PGA                  | PG299          |           |                 |           |           |           |           |           | Ľ'          |                  | Ц         |         |         |            |                  |          | Ц                |                 |         |         |         |         |           |         |           |         |           | *         |          |            |           |           |           |                  |  |

| 304                          | HI-PERF.QFP                  | HQ304          |           |                 |           |           |           |           |           | ['          |                  |           |         |         |            |                  |          | ГЦ               |                 |         |         |         |         |           |         |           |         | ۲         | *         | *        |            | L         | L         | L         | Ľ                |  |

| 352                          | PLASTIC BGA                  | BG352          |           |                 |           |           |           |           |           | [_'         | $\left[ \right]$ |           |         |         | <b>[</b> _ | [ ]              |          | []               |                 |         |         |         |         |           |         |           |         |           | *         |          | <b>[</b> _ | Γ_        | Γ_        | Γ_        | Γ_               |  |

| 411                          | CERAMIC PGA                  | PG411          |           |                 |           |           |           |           |           | [ ]         |                  |           |         |         |            | $\square$        |          | $\square$        |                 |         |         |         |         |           |         |           |         |           |           | *        | *          | $\Box$    | $\square$ | $\Box$    |                  |  |

| 432                          | PLASTIC BGA                  | BG432          | $\square$ |                 | $\square$ | $\square$ | $\square$ |           |           |             |                  |           |         |         |            |                  |          |                  |                 |         |         |         |         |           |         |           |         |           | $\square$ |          |            | *         |           |           |                  |  |

| 499                          | CERAMIC PGA                  | PG499          |           | $\square$       | $\square$ | $\square$ |           |           |           |             | $\square$        |           |         |         |            |                  |          |                  |                 |         |         |         |         |           |         |           |         |           |           |          |            |           |           | *         |                  |  |

| 596                          |                              | BG596          |           |                 |           |           |           |           | $\square$ |             | $\square$        |           |         |         |            |                  |          |                  |                 |         |         |         |         |           |         |           |         |           |           |          | $\vdash$   | *         |           |           |                  |  |

| · ·                          | Product curren               | • • •          |           | na              | ~         |           |           | <br>      | -         |             | }=I              | No        |         | inc     |            |                  | icc      |                  | <br>مf ۱        |         |         |         |         |           |         |           |         |           |           | -        | L          | •         | •         | L.        |                  |  |

◆ = Product currently shipping or planned

New since last issue of XCELL

| PLASTICLCC         PC44         Image: Constraint of the cons                                          |      |               |       |         |         |         |        |        |   |   |   | 3F | <u></u> | JA | R | Y | 19 | 9 | 6_ |         |        |        |        |        |        |         |         |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-------|---------|---------|---------|--------|--------|---|---|---|----|---------|----|---|---|----|---|----|---------|--------|--------|--------|--------|--------|---------|---------|--------|

| 44       PLASTIC CVGP       VQ44       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PINS | TYPE          | CODE  | XC4005L | XC4010L | XC4013L | XC5202 | XC5204 |   |   |   |    |         |    |   |   |    |   |    | XC73144 | XC8100 | XC8101 | XC8103 | XC8106 | XC8109 | XC95108 | XC95216 | XC9536 |

| 44       PLASTIC VGFP       VQ44       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ◆       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●       ●                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | PLASTIC LCC   | PC44  |         |         |         |        |        |   |   |   | ۲  |         |    | • | ♦ |    |   |    |         | *      |        |        |        |        |         |         | ۵      |

| CERAMICLICC       WC44       WC44       Image: Constraint of the second seco                                                            |      | PLASTIC QFP   | PQ44  |         |         |         |        |        |   |   |   |    |         |    |   | • |    |   |    |         |        |        |        |        |        |         |         |        |

| 48       PLASTIC VORP       VQ64         64       PLASTIC VORP       VQ64         76       CERAMIC LCC       VC68         76       CERAMIC LCC       VC68         76       CERAMIC CCC       VC64         76       PLASTIC CCF       PC100         70       PLASTIC CCFP       PC100         70       PLASTIC VORP       PC100         70       PLASTIC VORP       PC100         7100       PLASTIC VORP       PC100         7120       CERAMIC PGA       PG12         7131       CERAMIC PGA       PG12         7141       PLASTIC VORP       PC160         7152       CERAMIC PGA       PG14         7164       PC144       PC144         7175       CERAMIC PGA       PG14         7176       CERAMIC PGA       PG14         7177       CERAMIC PGA       PG14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44   | PLASTIC VQFP  | VQ44  |         |         |         |        |        |   |   |   |    |         |    |   |   |    |   |    |         |        |        |        |        |        |         |         |        |

| 64       PLASTICUCGP       VG64         PLASTICLCC       PC68         68       CERAMICLCC       WC68         CERAMICLCC       WC64         PLASTICLCC       PC68         PLASTICLCC       PC64         CERAMICLCC       WC64         CERAMICLCC       WC64         CERAMICLCC       WC64         CERAMICLCC       WC64         CERAMICLCC       WC64         CERAMICLCC       WC64         CERAMICCAC       WC64         CERAMICCAC       WC64         PLASTICUCC       PC66         PLASTICYOPP       PO100         PLASTICYOPP       PO1100         PLASTICYOPP       PO1101         PLASTICYOPP       PO1114         PLASTICYOPP       PO1101         PLASTICYOPP       PO1101         PLASTICYOPP       PO1101         PLASTICYOPP       PO1101         PLASTICYOPP       PO1101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | CERAMIC LCC   | WC44  |         |         |         |        |        |   |   |   | ۲  |         |    | ♦ | ♦ |    |   |    |         |        |        |        |        |        |         |         | ٠      |