#### THE QUARTERLY JOURNAL FOR XILINX PROGRAMMABLE LOGIC USERS

The Programmable Logic Company<sup>SM</sup>

### Inside This Issue:

#### **GENERAL**

| Fawcett: PCI Compliance          | 2     |

|----------------------------------|-------|

| Guest Editorial: Chuck Fox on    |       |

| Developing New PLD Solutions     | 3     |

| New Xilinx Internet Web Site     | 6     |

| Financial Results                | 6     |

| Customer Success Story           | 7     |

| New Product Literature           | 8     |

| Upcoming Events                  | 8     |

| Xilinx Ireland Comes On-Line     | 9     |

| Training Class Supports XACTstep | 9     |

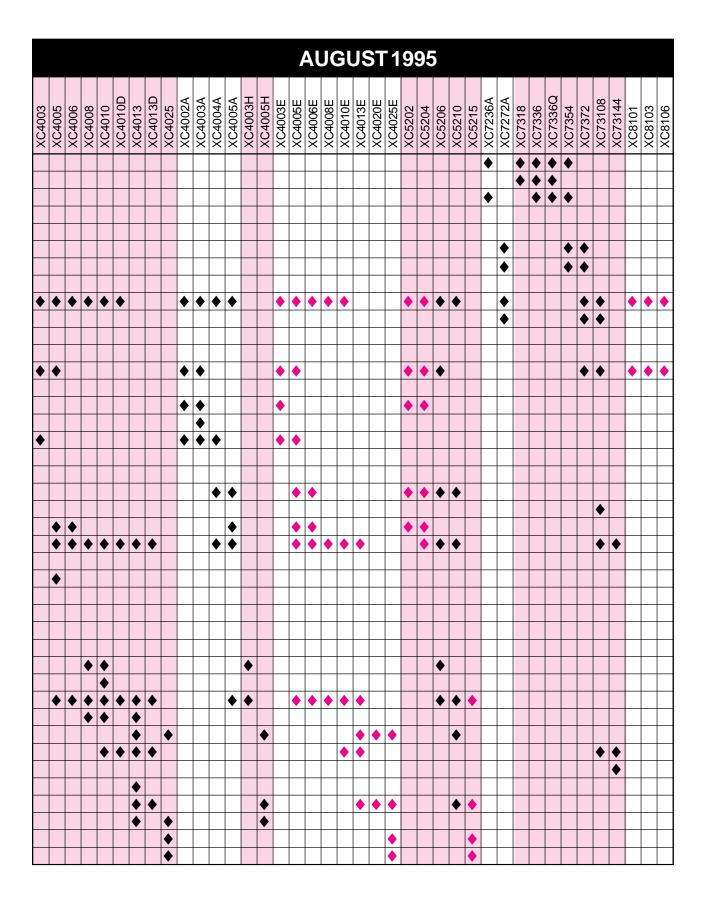

| Component Availability Chart     | 10-11 |

| Alliance Program Chart           | 12-13 |

| Alliance Contact Chart           | 13    |

| Development Systems Chart        | 14    |

| Programming Support Charts:      |       |

| XC7200, XC7300, XC1700           | 15-17 |

#### PRODUCTS

| New XC4000E Family            | 18-19 |

|-------------------------------|-------|

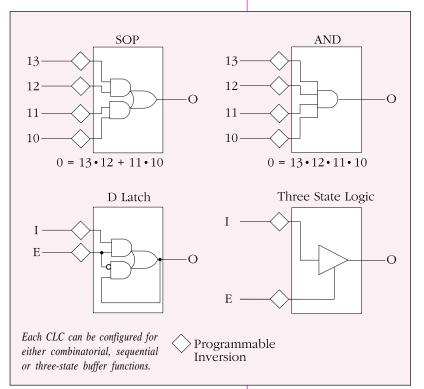

| XC8100 Enters Production      | 20-21 |

| XC6200 Architecture Announced | 22-23 |

#### **DEVELOPMENT SYSTEMS**

| Improved EPLD Synthesis Support | 25-26 |

|---------------------------------|-------|

| XACT step, Advanced System      | 26    |

#### HINTS & ISSUES

| HDL Synthesis Design Guide 27-29      |

|---------------------------------------|

| Overshoot and Undershoot 30           |

| Low-Pass Filtering of Noisy Inputs 30 |

| XC4000E:                              |

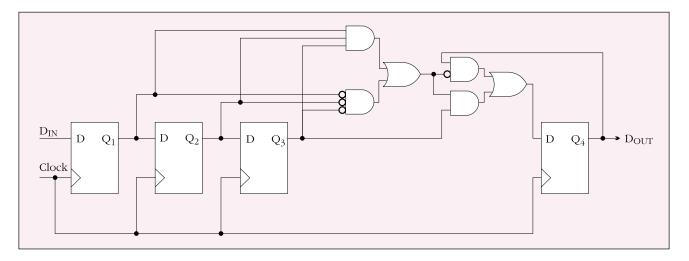

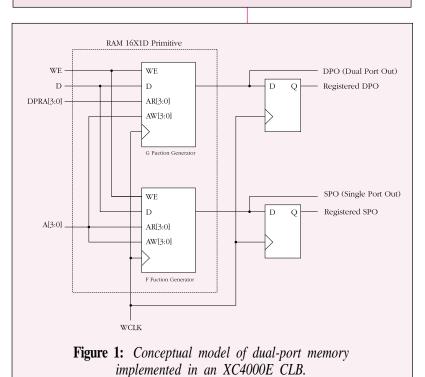

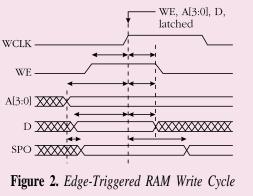

| Examining RAM Capabilities 31-33      |

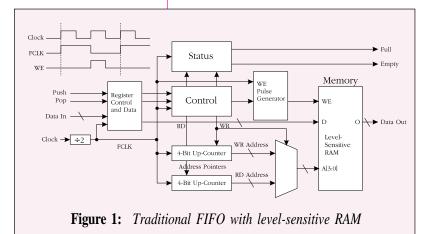

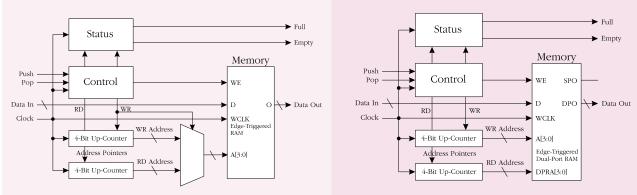

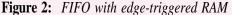

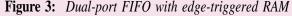

| Building FIFO Memories 34-35          |

| Mixing 3.3 Volt and 5 Volt Devices 35 |

| "Hold" is a Four-Letter Word 36       |

| Acquiring Application Notes           |

| and Design Files 37                   |

| Questions & Answers 38-39             |

| Technical Support Facilities 39       |

| 3Q95 Fax Response Form 40             |

|                                       |

# GENERALFEATURES

### **Ireland Facility On-Line**

Xilinx's new 100,000 square foot facility in Dublin, Ireland is now processing all European orders...

See Page 9

# PRODUCTINFORMATION

# Introducing three new FPGA Families!

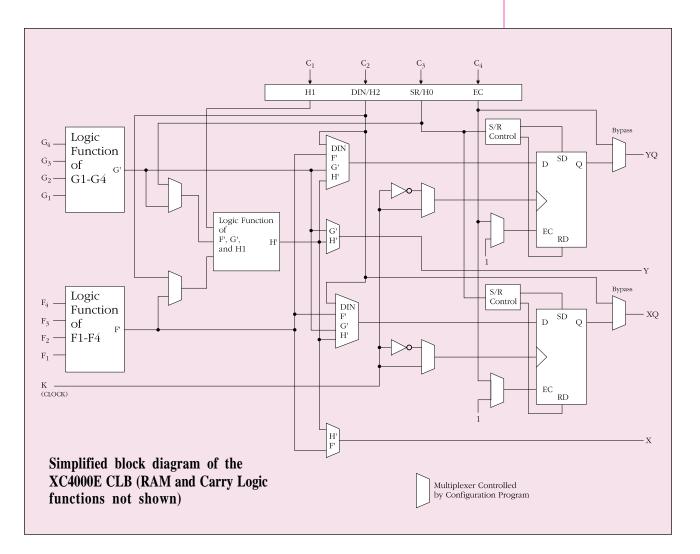

# **XC4000E** Family

With a myriad of new features, the XC4000E FPGA family increases performance over the existing XC4000 family by up to 50%... See Page 18

# XC8100 Family

The first Xilinx one-timeprogrammable FPGA family, based on MicroVia technology, enters production.

See Page 20

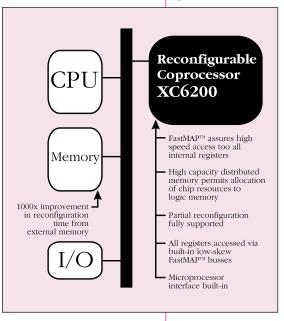

# **XC6200** Family

The new XC6200 SRAM-based FPGA architecture is the first FPGA specifically designed to implement reconfigurable coprocessors in embedded system applications. See Page 22

#### FROMTHEFAWCETT

•

•

•

# PCI Compliant $\neq$ PCI Suitable

By BRADLY FAWCETT  $\blacklozenge$  Editor

The rapid adoption and proliferation of the PCI (Peripheral Component Interconnect) bus has been one of the computer market's major success stories of the past year.

Originally defined by Intel, PCI has

become an industrywide standard controlled by a consortium — the PCI Special Interest Group, or PCI SIG. The highperformance PCI bus can handle the throughput demands of dataintensive applications such as multimedia and high-speed networking.

Full compliance to the PCI SIG specification is a must for systems and boards that will be sold in the general marketplace where interoperability among multiple vendors is required.

To achieve high throughput and ensure interoperability between a wide variety of boards and host systems, the PCI specification includes a strict definition of its electrical interface. IC components that can meet the performance, loading and drive requirements of this electrical interface are said to be "PCI-compliant." By submitting the appropriate paperwork, component suppliers that are members of the PCI SIG can have their compliant devices added to an "Integrators List" that is available to other PCI SIG members.

# Market Pressures and Marketing Tactics

PCI-related designs are a large potential market for high-density CPLDs and FPGAs. The flexibility of a programmable approach is attractive in a PC card market characterized by changing market needs and short product life cycles. These devices are, in fact, finding their way into many prototype and production PCI designs. Thus, programmable logic vendors are working hard to establish themselves as suppliers to this market. One tactic is to submit as many devices as possible for inclusion on the PCI SIG's Integrators List, and then, based on their inclusion on the list, advertise these devices as being "PCI Approved" (or a similar designation).

Designers of PCI boards and systems are advised to be leery of these claims. First, the PCI SIG does not guarantee the compliance of any device or offer any form of approval; submissions to the PCI SIG are strictly on the "honor system" and are not verified independently. (In fact, the component section of the Integrators List specifically states that functional testing is not required to be listed. The PCI SIG disclaims responsibility for any errors in the listings.) The Integrators List is

> *being* 'PCIcompliant' does not necessarily mean these devices are suitable for use in a PCI application."

considered confidential to PCI SIG members and is for their convenience only. Again, inclusion on the Integrators List does not constitute any endorsement or approval by the PCI SIG.

Continued on page 5

### XCELL

Please direct all inquiries, comments and submissions to:

Editor: Bradly Fawcett

#### Xilinx, Inc.

2100 Logic Drive San Jose, CA 95124 **Phone:** 408-879-5097 **FAX:** 408-879-4676 **E-Mail:** brad.fawcett@xilinx.com

©1995 Xilinx Inc. All rights reserved.

XCELL is published quarterly for customers of Xilinx, Inc. Xilinx, the Xilinx logo and XACT are registered trademarks; all XC-designated products, UIM, HardWire and XACT-Performance are trademarks; and "The Programmable Logic Company" is a service mark of Xilinx, Inc. All other trademarks are the property of their respective owners.

#### **GUESTEDITORIAL**

# Developing New PLD Solutions

by CHUCK FOX 🔶 Vice President, Product Marketing

By the end of 1995, Xilinx will have introduced more new programmable logic device family solutions in the last 18 months than in our prior ten-year history. Why so many? Why now? As with most semiconductor products, the answer to both questions stems from the convergence of technology and market needs.

#### **Technology and Markets**

First, there is the "push factor" of rapid advancements in IC fabrication technology. It took the industry nearly a decade to migrate from 2.0 micron to 1.0 micron technology. Yet, the move from 1.0 to 0.5 micron has taken less than five years (and 0.35 micron technology is only a year or so away). These shrinking IC geometries, along with larger wafer sizes, additional layers of metal interconnect, new software technologies and new packaging technologies have allowed dramatic increases in device density and performance. Equally dramatic price reductions have followed.

Advances in IC processing technology have accelerated the development of new programming structures. Xilinx is the only PLD company that is providing cost-effective and reliable SRAM, antifuse, EPROM and FLASH processes now available in volume production.

These technology shifts, of course, influence PLD architectural development. What conventional wisdom assumed was impossible yesterday may be feasible today. For example, the shift from two-layer to three-layer metal processes alters the "logic vs. routing" trade-offs in FPGA design (as evident in the new XC8100, XC5200, and XC6200 FPGA family architectures). Thus, advances in process technology lead to new programmable logic architectures.

Just as influential is the "pull factor" of increasingly competitive end-use markets. Today's electronic system market is characterized by global competition and changing industry standards, resulting in higherperformance products with shorter life cycles.

Design methodologies are changing; higher levels of design abstraction and automated tools are required to meet the twin challenges of increased complexity and decreased time-to-market.

#### **Inspiration** + Ability = New Architectures

Thus, our new product offerings reflect the goal of

every electronics design: leverage advancing technology to best match users' needs. In some cases, this takes the form of evolutionary improvements to current products, such as enhancing the popular XC4000 FPGA architecture to create the XC4000E family. In other cases, it involves new product development to take full advantage of new technologies or to address new markets; for example, the XC5200 architecture leverages 3-layer metal technology to lower FPGA costs, thereby expanding FPGA

Continued on the next page

•Xilinx is the only PLD company that is providing cost-effective and reliable SRAM, antifuse, EPROM and FLASH processes now available in volume production."

. . . . . . . . . . . . . . .

The high-performance XC7336Q is just one of the new products introduced by Xilinx in the first half of 1995.

#### **GUESTEDITORIAL**

#### Continued from the previous page

usage in high-volume applications.

Why so many PLD architectures? CPLDs and FPGAs are being used in an amazingly wide variety of logic applications, ranging from simple interface logic to reconfigurable computing arrays. While PLD use in communications, industrial and peripheral control applications continues to expand, increasing PLD capabilities and decreasing prices are opening up new markets in PC and consumer applications. Different applications have different needs. Different users have different preferences. No single technology or architecture can meet all those needs and desires.

The SRAM-based XC2000, XC3000A/ XC3100A, XC4000E and XC5200 architectures remain the best FPGA architectures for "glue logic" applications. Each has a slightly different mix of attributes. The XC3100A family offers the best raw speed,

•A broad product line supported by a powerful, unified suite of development tools gives the user the best of both worlds — the choice of the most-appropriate PLD architecture, and no need to purchase and learn a new set of design tools."

> the XC4000E provides the largest densities and feature set (including on-chip memory), and the XC5200 delivers the lowest cost per gate. We will continue to enhance these architectures and improve these product families. The new XC6200 FPGA architecture, with its built-in processor interface, targets a different type of application — reconfigurable coprocessing (although it will undoubtedly find its way into other applications as well). The XC8100 FPGAs are ideal for those applica

tions requiring "instant-on" operation, the increased security of a one-time-programmable solution, or a more "ASIC-like," synthesis-friendly design flow.

Some applications fit better with a CPLD-type architecture. The XC7300 family, featuring industry-leading performance, continues to expand with the recent additions of the XC73144 and XC7336Q. A revolutionary, new, in-system programmable architecture, based on flash memory technology, will be introduced later this year.

#### **Industry Leadership**

Why now? It has always been our corporate goal to be the leading supplier of programmable logic. Simply put, we want to fulfill all of our users' high-density programmable logic needs. As Xilinx and the programmable logic market grew in the late 1980s and early 1990s, we became the leading PLD supplier and could afford to make substantial investments in research and development. The new products appearing now are the result of years of development. As the largest and most successful supplier of programmable logic, we have the engineering resources to explore different approaches and support multiple development efforts. With the recent acquisition of FPGA-software-supplier NeoCAD, we are setting the standard for leading-edge development software to support multiple component families.

High-density PLDs are rapidly becoming a critical, strategic technology for leading electronic systems companies. A broad product line supported by a powerful, unified suite of development tools gives the user the best of both worlds the choice of the most-appropriate PLD architecture, and no need to purchase and learn a new set of design tools. We think this is crucial to being not only your programmable logic *supplier*, but also your programmable logic *partner*. ◆

#### **FROMTHE FAWCETT**

Continued from page 2

#### **Compliance No Simple Task**

Secondly, and more importantly, being "PCI-compliant" does not necessarily mean these devices are suitable for use in a PCI application. Electrical compliance only guarantees that the device meets the bare minimum electrical characteristics. It does not guarantee that the device has the logic capacity, functionality and overall speed to effectively implement a PCI interface design—the device may or may not be suitable for a real-world design.

For example, the PCI specification allows a 10 pF maximum load on a bus signal (except the clock signal, which is allowed a 12 pF maximum load), as well as a maximum trace length of 1.5 inches from the card edge connector to limit trace capacitance. Taken together, these two factors imply that each bus signal attaches to only one IC pin per board (that is, a signal coming from the connector can have only one destination).

Practically speaking, all the interface logic would need to be implemented in a single device in a fairly small package (such as a quad flat pack) so that all the pins can be close to the connector. A simple PCI interface typically requires about 100 I/O, about 4,000 usable gates, and well over 100 registers. The need for a single-chip solution eliminates a lot of the smaller PALs and CPLDs that have found their way on to the Integrators List and are advertised as "PCI-compliant" by their manufacturers.

The internal architectures of some devices do not easily meet the needs of PCI interface design. For example, many PCI bus signals are bidirectional and must be driven by three-state buffers. Some FPGA and CPLD architectures limit the number of different output enables that may be present on the device. Target interfaces require a minimum of four output enables; initiators require at least six. This is a bare minimum. It does not include the output enables needed for interrupts, controlling byte transactions, or connecting to the back-end logic. Realworld designs require several more output enables. Thus, devices with limited output enable capability are not practical for PCI designs.

#### **Beyond the Basics**

There are, of course, many other issues. Can the device deliver the needed performance to operate at any frequency from 0 to 33 MHz? Do the development tools make it easy to control circuit speed along the critical paths? The PCI bus has to attach to something — what are the requirements of the back-end interface? Compliant electrical characteristics are just the first step in selecting a programmable logic device for PCI interface design. Labeling a product as "PCI-compliant" does not ensure suitability for a particular design.

Xilinx does offer several devices that are both electrically compliant and architecturally suitable for PCI interface implementations. These include the XC3100A and new XC4000E FPGA families, as well as the higher-density members of the XC7300 EPLD family. Xilinx components have already been used in a number of successful PCI designs. In fact, the PCI SIG chose a Xilinx XC3100A FPGA for a board included in their BIOS compliance test kit.

For more information about programmable logic products for PCI designs, including application notes and reference designs, please contact us via E-mail at pci@xilinx.com or call your local Xilinx representative.

Copies of the PCI specification can be obtained from the PCI Special Interest Group, P.O. Box 14070, Portland, OR 97214 (tel: 800-433-5177). ◆

•Xilinx does offer several devices that are both electrically compliant and architecturally suitable."

> P.S. Our thanks to the thousands of engineers who joined us for the Programmable Logic Breakthrough '95 seminars this spring. We know your time is valuable and we appreciate your participation

Many new items have been added recently to the Xilinx webLINX site on the World Wide Web, including technical application notes, FPGA and EPLD data sheets, press releases, training schedules, financial news and stock quotations, and University Program news. An interactive, on-line technical support database and FTP site for file transfers are available as well. Most Xilinx Web documents are "published" using Adobe Acrobat<sup>™</sup>. Acrobat displays documents on the screen just as they would appear from a color printer. The Acrobat Reader is available free on the Internet., enabling anyone with Internet Web access to view and print high-quality Xilinx literature directly from the Web.

Look for future additions such as the Xilinx Annual Report, employment opportunity listings as well as current and previous issues of *XCELL*. Other possibilities include a search engine to permit quicker access to all the documents on a given topic and real-time order status. Your feedback is encouraged; if there is a document or feature you'd like to see on the Xilinx Web, please send an E-mail message to webmaster@xilinx.com.

The Xilinx home page on the World Wide Web can be accessed at http:// www.xilinx.com. ◆

#### **FINANCIAL RESULTS**

# **Record Revenue and Another Kachina Award**

Xilinx revenues rose to a record \$125.8 million in the first quarter of fiscal 1996 (ending July 1, 1995). This represents a 15 percent increase from the immediately preceding quarter, and a 67 percent increase from the same quarter last year.

Once again, revenue growth was driven by increasing demand for high-speed XC3100 and XC4000 family products. International sales constituted 36 percent of total revenue; sales from Japan showed the largest increase, benefiting from the strengthened yen.

Xilinx stock split 3-for-1 on August 11, 1995 for shareholders of record as of July 28. The stock split is indicative of the confidence of the Xilinx Board of Directors in the company's ability to maintain continued growth. The stock split will increase the total number of outstanding shares to 70 million. It is the first stock split since the company went public in 1990. Xilinx stock is traded on the NASDAQ exchange under stock symbol XLNX.

#### **Five Consecutive Kachinas**

In May, market research firm In-Stat Inc. named Xilinx as the Best Financially Managed IC Company for a record fifth consecutive year. The coveted Kachina Award was presented to Xilinx at In-Stat's annual Semiconductor Forum. (The Kachina Award is a statue carved by the Hopi Indians of Arizona. According to Hopi legend, the Kachina is a warrior who faces great difficulties and shows great strength.)

Separate awards are presented for IC companies that do and do not own their own fabrication facilities. The companies are ranked based on criteria such as operating income, net income, return on investment, inventory turnover and sales per employee. Xilinx beat out all other "fabless" companies, including Adaptec, Altera and Lattice Semiconductor. Xilinx has won this award each year since going public in June, 1990. No other semiconductor company, with or without a foundry, has received this award for more than two consecutive years.

# Videoconferencing with XC5000 FPGAs

VTEL Inc. designs and manufactures high-quality, multimedia videoconferencing systems. It is the leading provider of videoconferencing equipment for the remote education and medical industries.

The VTEL systems are based on architectures that employ multiple heterogeneous processor subsystems, interconnected and controlled using custom data paths and control logic. Xilinx FPGAs provide a cost-effective, adaptable solution for implementing this custom hardware, and have been used in several generations of VTEL systems.

VTEL's latest videoconferencing system uses XC5000 family FPGAs, making it one of the earliest adopters of this new FPGA family. The new design uses an XC5210 and an XC5206 device (in 240-pin and 160-pin PQFP packages, respectively) to implement specialized video and communication data pipelines and control logic. The FPGAs contain custom video processing control logic with multistage data pipelines to perform high-quality video format conversions and the adaptive overlay of video streams. Video is processed at near broadcast quality in both RGB and YUV formats.

The flexibility of the SRAM-based FPGAs facilitated the implementation of custom video merge processing in order to produce superior integration of multiple streams of live and control video. The FPGAs also were used to consolidate a large number of bus control, timing and communications signal routing, and test functions. If these functions had been implemented with PALs and/or discrete logic devices, the system would have required two to three times as many circuit boards, with the resulting increases in cost and power consumption.

Since the XC5000 development software was not yet available at the beginning of the design cycle, VTEL engineers took advantage of the Xilinx Unified Library and the footprint-compatibility of the XC4000 and XC5000 families. Initially, the logic targeted for the XC5210 and XC5206 devices was designed for an XC4010 and XC4006 FPGA, respectively. Logic capture, simulation and printed-circuit board layout were completed in this manner. The designs were captured and verified on a Sun workstation using the Viewlogic PowerView schematic editor and ViewSim simulator. Altogether, about six man-months of effort were required to enter, simulate and implement the designs.

Once the XC5000 library was available, the conversion to the XC5000 family parts went smoothly. After some floorplanning of the data path logic, the automatic tools of the XACT- system produced an implementation that exceeded the performance requirements of VTEL's application.

The compatibility between the XC4000 and XC5000 families was exploited again during prototyping and initial system test. The XC5210 FPGA was available when the first

Continued on the next page, see VIDEOCONFERENCING

### **New Product Literature**

Learn about the newest Xilinx products and services through our extensive library of product literature. The most recent pieces are listed below. To order or to obtain a complete list of all available literature, please contact your local Xilinx sales representative.

| TITLE                       | DESCRIPTION         | PARTNUMBER  |

|-----------------------------|---------------------|-------------|

| FPGAs                       |                     |             |

| XC4000E Overview            | Features & benefits | #0010257-01 |

| XC6200 Overview             | Features & benefits | #0010258-01 |

| XC8100 Overview             | Features & benefits | #0010254-01 |

| XC8100 Advanced Information | Technical Data      | #0010193-03 |

| EPLDs                       |                     |             |

| XC7300 Family Brochure      | Product Overview    | #0010253-01 |

#### **UPCOMING EVENTS**

Look for Xilinx technical papers and/or product exhibits at these upcoming industry forums. For further information about any of these conferences, please contact Kathleen Pizzo (Tel: 408-879-5377 FAX: 408-879-4676).

8th Annual IEEE ASIC Conference (ASIC '95) Sept. 18-22 Austin, Texas

**European Design Automation Conference (EURO-DAC '95)** Sept. 18-22 Brighton, United Kingdom

DSP '95

Oct. 18-20 Paris, France **Photonics East** Oct. 22-26 Philadelphia, Pennsylvania

**1995** International Conference on Signal Processing Applications and Technology and DSP World Exhibition (ICSPAT) Oct. 23-27 Boston, Massachusetts WESCON Nov. 7-9 San Francisco, California

International Integrated Circuits Conference Nov. 8-10 Shanghai, China

# Videoconferencing

#### Continued from page 7

prototype systems were built, but the XC5206 was not, so it was replaced by the pin-compatible XC4006.

The anticipated improved routing capabilities of the XC5000 architecture increased the effective usable capacity enough to allow the inclusion of additional test functions during the latter stages of product development. This additional functionality significantly enhanced board-level product testing capabilities.

VTEL design engineer Richard Glass noted, "Xilinx has provided VTEL with excellent FPGA support through several generations of system designs. VTEL especially values the ease of development and flexibility of the Xilinx FPGA products, which facilitates rapid development and allows incremental design improvement over product life cycles. By using FPGA technology, we have been able to adapt the subsystem designs to meet changing market requirements both during product development and in the field."

See page 37 for a listing of new application notes.

# Xilinx Ireland Comes On-Line

In keeping with the corporate goal of increasing international sales to half of total revenue, Xilinx has established a major new facility at the Citywest Business Campus in Dublin, Ireland. Construction of the 100,000 square foot manufacturing facility is scheduled to be completed late this year.

The new facility will be used to produce and distribute Xilinx products for Europe and other international markets. It is the company's first wholly-owned manufacturing facility outside of the United States. Besides providing additional capacity for a growing business, Xilinx Ireland provides closer access to European users, ultimately resulting in better service and faster response times.

The new Irish facility will replicate the activities of the company headquarters in San Jose, with the exception of field sales and marketing. Customer service is a key part of the Irish operation; all European orders are being received and processed in Dublin now; all international orders will be processed there by the end of the year.

After the manufacturing and customer service resources are in place, emphasis will be placed on system software testing and quality analysis. Eventually, IC and

software design groups will be established. This venture is expected to create more than 300 jobs.

Operations commenced in a temporary building at the Citywest site in April, starting with the processing of all European distributors' orders. The first product to ship from Ireland was delivered to an Italian distributor in mid-April. Xilinx Ireland is now processing all European and some Asian orders; production capacity will continue to rise throughout the year. The company is undertaking an intensive program to achieve ISO 9002 quality standards certification for the Dublin facility in 1996. ◆ When construction is finally complete late this year, Xilinx Ireland will contain 100,000 square feet of manufacturing and office space.

# Training Class Update Supports XACTstep, version 6

The Xilinx training courses are being kept up-todate with information about the latest products. The standard three-day training course will be updated for XACT*step*<sup>TM</sup> version 6 as well as the new XC5200 and XC4000E families as soon as the software begins production shipment. Our policy is to always base the course on the latest software versions available to our entire user base.

If you have a design starting now or have an immediate need for training, you should attend the current class. The instructor will be able to point out some of the key changes coming with the next release. Also, a one-day "update" class will be made available at the same time as the XACT*step* version production shipment. This class will be targeted at those who have used the previous version, or who have already attended training. The XC8100 family and its supporting software are also slated for production release this autumn. A class will be available at that time. For more information, contact your local sales office, or Xilinx Training at (408) 879-5090, (800) 231-3386x1, or e-mail to customer.training@xilinx.com.

- Product currently shipping or planned

- New since last issue of XCELL

|      | C                          | COM            | P      | 0      | Ν        | Ξ       | N      | Γ/     |        | Ά      |                                  | A       | B        |         |         | ٢Y                               | ζ(      | ; <del> </del> |         | R       | Т       |         |          |         |         |         |         |

|------|----------------------------|----------------|--------|--------|----------|---------|--------|--------|--------|--------|----------------------------------|---------|----------|---------|---------|----------------------------------|---------|----------------|---------|---------|---------|---------|----------|---------|---------|---------|---------|

| PINS | TYPE                       | CODE           | XC2064 | XC2018 | XC2064L  | XC2018L | XC3020 | XC3030 | XC3042 | XC3064 | XC3090                           | XC3020A | XC3030A  | XC3042A | XC3064A | XC3090A                          | XC3020L | XC3030L        | XC3042L | XC3064L | XC3090L | XC3120A | XC3130A  | XC3142A | XC3164A | XC3190A | XC3195A |

|      | PLASTIC LCC                | PC44           | ٠      | ٠      |          |         |        | ٠      |        |        |                                  |         | ٠        |         |         |                                  |         |                |         |         |         |         | ٠        |         |         |         |         |

| 44   | PLASTIC QFP                | PQ44           |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

|      | CERAMIC LCC                | WC44           |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

| 48   | PLASTIC DIP                | PD48           | ٠      |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

| 64   | PLASTIC VQFP               | VQ64           | •      | •      | <b>♦</b> | •       |        | •      |        |        |                                  | •       | <b>♦</b> |         |         |                                  |         | •              |         |         |         |         | <b>♦</b> |         |         |         |         |

|      | PLASTIC LCC                | PC68           | •      | •      | •        |         | •      | •      |        |        |                                  | •       | •        |         |         |                                  |         |                |         |         |         | •       | •        |         |         |         |         |

| 68   | CERAMIC LCC                | WC68           |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

|      | CERAMIC PGA                | PG68           | •      |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

|      | PLASTIC LCC<br>CERAMIC LCC | PC84<br>WC84   |        | •      | -        | ▼       | •      | •      | •      | •      | •                                | ▼       | ▼        | •       |         | ▼                                | •       | •              | ▼       | •       | •       | ▼       | •        | •       | •       |         |         |

| 84   | CERAMIC LCC                | PG84           |        |        |          |         |        |        |        |        |                                  |         |          | ♦       |         |                                  |         |                |         |         |         |         |          |         |         | _       | _       |

|      | CERAMIC PGA                | CQ100          |        | •      |          |         | ▼<br>▲ | •      |        |        |                                  | •       | •        | •       |         |                                  |         |                |         |         |         | •       | •        | •       |         |         |         |

|      | PLASTIC PQFP               | PQ100          |        |        |          |         | ▼<br>▲ | ٢      | ▼<br>▲ |        |                                  |         | ٢        | ٢       |         |                                  |         |                |         |         |         |         | ٢        |         |         |         |         |

| 100  | PLASTIC TQFP               | TQ100          |        | ٢      |          |         | •      | ▲      | ▲      |        |                                  | •       | •        | •       |         |                                  |         |                |         |         |         | •       | ♦        | •       |         |         |         |

|      | PLASTIC VQFP               | VQ100          |        | •      |          | ٠       |        | •      | •      |        |                                  |         | ۲        | ٠       |         |                                  |         | ۲              | ٢       |         |         |         | ♦        | ♦       |         |         |         |

|      | TOP BRZ. CQFP              | CB100          |        |        |          | •       | ٠      |        | ۲      |        |                                  | ۲       | •        | ♦       |         |                                  |         | •              | •       |         |         | ۲       | •        | ♦       |         |         |         |

| 120  | CERAMIC PGA                | PG120          |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

| 132  | PLASTIC PGA                | PP132          |        |        |          |         |        |        | ۲      | ۲      |                                  |         |          | ۲       | ۲       |                                  |         |                |         |         |         |         |          | ۲       | ۲       |         |         |

| 102  | CERAMIC PGA                | PG132          |        |        |          |         |        |        | ۲      | ۲      |                                  |         |          | ۲       | ♦       |                                  |         |                |         |         |         |         |          | ۲       | ۲       |         |         |

| 144  | PLASTIC TQFP               | TQ144          |        |        |          |         |        |        |        |        |                                  |         |          | ۲       | ♦       |                                  |         |                | ♦       | ♦       |         |         |          | ۲       | ۲       |         |         |

|      | CERAMIC PGA                | PG144          |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

| 156  | CERAMIC PGA                | PG156          |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

| 160  | PLASTIC PQFP               | PQ160          |        |        |          |         |        |        |        | ٠      | <b>♦</b>                         |         |          |         | •       | ٠                                |         |                |         |         |         |         |          |         | •       | •       | •       |

| 164  | CERAMIC QFP                | CQ164          |        |        |          |         |        |        |        |        | <ul> <li>♦</li> <li>▲</li> </ul> |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

|      | TOP BRZ. CQFP              | CB164          |        |        | -        |         |        |        |        |        | •                                |         |          |         |         | <ul> <li>♦</li> </ul>            |         |                |         |         |         |         |          |         |         |         |         |

| 175  | PLASTIC PGA<br>CERAMIC PGA | PP175          |        |        |          |         |        |        |        |        | <ul><li>▼</li><li>▲</li></ul>    |         |          |         |         | <ul> <li>▼</li> <li>▲</li> </ul> |         |                |         |         |         |         |          |         |         |         |         |

| 176  | PLASTIC TQFP               | PG175<br>TQ176 |        |        |          |         |        |        |        |        | •                                |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

| 184  | CERAMIC PGA                | PG184          |        |        |          |         |        |        |        |        |                                  |         |          |         |         | •                                |         |                |         |         | •       |         |          |         |         |         |         |

| 191  | CERAMIC PGA                | PG191          |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

| 196  | TOP BRZ. CQFP              | CB196          |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

|      | PLASTIC PQFP               | PQ208          |        |        |          |         |        |        |        |        | ٠                                |         |          |         |         | ٠                                |         |                |         |         |         |         |          |         |         |         |         |

| 208  | METAL MQFP                 | MQ208          |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

| 223  | CERAMIC PGA                | PG223          |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         | ۲       |

| 225  | PLASTIC BGA                | BG225          |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

|      | WINDOWED BGA               | WB225          |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

| 228  | TOP BRZ. CQFP              | CB228          |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

| 240  | PLASTIC PQFP               | PQ240          |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

|      | METAL MQFP                 | MQ240          |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

| 299  | CERAMIC PGA                | PG299          |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

| 304  | HI-PERF. QFP               | HQ304          |        |        |          |         |        |        |        |        |                                  |         |          |         |         |                                  |         |                |         |         |         |         |          |         |         |         |         |

### ALLIANCE PROGRAM - COMPANIES & PRODUCTS - SEPTEMBER 1995

| Company                               | PRODUCT NAME                                                                                      | VERSION                                              | FUNCTION                                                                                                                     | DESIGN KIT                                                                                                                                           | 2K/3K/4K<br>Support                                | XC5200<br>Support          | EPLD<br>Support      | Unified Lib.<br>Support                                                                                                                                      |

|---------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acugen                                | ATGEN<br>Sharpeye                                                                                 | 2.60<br>2.60                                         | Automatic Test Generation<br>Testability Analysis                                                                            | AALCA interface<br>AALCA interface                                                                                                                   | √<br>√                                             | Aug<br>Aug                 | <i>\</i><br><i>\</i> |                                                                                                                                                              |

| ALDEC/Susie-CAD                       | Active-Xilinx<br>Active-XIx-State                                                                 | 2.0<br>2.0                                           | Schematic Entry/Simulation<br>Schematic State Editor/                                                                        | Included<br>Included                                                                                                                                 | √<br>√                                             | \<br>\                     | \<br>\               | \<br>\                                                                                                                                                       |

|                                       | Active-XIx-Syn                                                                                    | 2.0                                                  | HDL Editor Simulation<br>Schematic State Editor/<br>HDL Editor Synthesis Sim.                                                | Included                                                                                                                                             | 1                                                  | 1                          | 1                    | 1                                                                                                                                                            |

| Aptix                                 | System Explorer<br>ASIC Explorer                                                                  | 2.1<br>2.3                                           | System Emulation<br>ASIC Emulation                                                                                           | Axess2.1<br>Axess2.3                                                                                                                                 | ✓<br>4K                                            | \<br>\                     |                      | 1                                                                                                                                                            |

| Cadence (Valid)                       |                                                                                                   |                                                      | \$<br>\$<br>\$<br>\$<br>\$<br>\$                                                                                             | Q4<br>Q4<br>Q4<br>Q4<br>Q4                                                                                                                           | \$ \$ \$ \$ \$<br>\$                               | \<br>\<br>\<br>\<br>\<br>\ |                      |                                                                                                                                                              |

| Capilano                              | DesignWorks                                                                                       | 3.1                                                  | Schematic Entry/Simulation                                                                                                   | XD-1                                                                                                                                                 | √                                                  |                            |                      |                                                                                                                                                              |

| Compass                               | Asic Navigator<br>QSim<br>X-Syn                                                                   |                                                      | Schematic Entry<br>Simulation<br>Synthesis                                                                                   | Xilinx Design Kit                                                                                                                                    | \$<br>\$<br>\$                                     | \$<br>\$                   |                      |                                                                                                                                                              |

| Data I/O                              | ABEL<br>Synario                                                                                   | 6.1<br>2.1                                           | Synthesis<br>Schematic Entry, Synthe-<br>sis and Simulation                                                                  | XEPLD Fitter<br>SYN-LCA<br>SYN-XEPLD                                                                                                                 | 1                                                  | Sep                        | <i>\</i><br><i>\</i> | √<br>√                                                                                                                                                       |

| Escalade                              | Design Book                                                                                       |                                                      | Design Entry                                                                                                                 |                                                                                                                                                      | ✓                                                  |                            |                      | 1                                                                                                                                                            |

| Exemplar Logic                        | Galileo                                                                                           | 3.04                                                 | Synthesis                                                                                                                    | Included                                                                                                                                             | 1                                                  | 1                          | 1                    | 1                                                                                                                                                            |

| Flynn Systems                         | FS-ATG                                                                                            | 2.6                                                  | Automatic Test Generation                                                                                                    | FS-High Density                                                                                                                                      | 1                                                  |                            |                      |                                                                                                                                                              |

| IBM-EDA                               | Boole-Dozer                                                                                       |                                                      | Synthesis                                                                                                                    |                                                                                                                                                      | 1                                                  |                            |                      |                                                                                                                                                              |

| IK Technology                         | G-DRAW<br>G-LOG                                                                                   | 5.0<br>4.03                                          | Schematic Entry<br>Simulation                                                                                                | GDL2XNF<br>XNF2GDL                                                                                                                                   | √<br>√                                             |                            |                      |                                                                                                                                                              |

| lkos                                  | Voyager                                                                                           | 2.10                                                 | Simulation                                                                                                                   | Xilinx Tool Kit                                                                                                                                      | ✓                                                  |                            |                      |                                                                                                                                                              |

| Incases                               | Theda                                                                                             | 2.0                                                  | Schematic Entry                                                                                                              | Xilinx Kit                                                                                                                                           | 1                                                  |                            |                      |                                                                                                                                                              |

| Intergraph                            | ACE Plus<br>AdvanSIM-1076<br>VeriBest Sim<br>Veribest DMM<br>VeriBest Syn<br>Synovation<br>PLDSyn | 12.2<br>12.0<br>14.0<br>14.0<br>14.0<br>12.2<br>12.0 | Schematic Entry<br>Simulation<br>Simulation<br>Design Flow Manager<br>Synthesis<br>Synthesis<br>Design entry, synthesis sim. | Xilinx FPGA Design Kit<br>Xilinx FPGA Design Kit<br>Xilinx FPGA Design Kit<br>Xilinx FPGA Design Kit<br>Xilinx FPGA Design Kit<br>SynLib<br>Included | 3K,4K<br>3K,4K<br>3K,4K<br>3K,4K<br>3K,4K<br>3K,4K | √<br>√<br>√                | 1                    | $\begin{array}{c} \checkmark \\ \checkmark $ |

| ISDATA                                | LOG/iC2<br>LOG/iC Classic                                                                         | 4.2<br>4.2                                           | Synthesis, simulation<br>Synthesis                                                                                           | Xilinx Mapper<br>LCA-PP                                                                                                                              | √<br>√                                             | 1                          | <i>\</i><br><i>\</i> | 1                                                                                                                                                            |

| IST                                   | ASYL+                                                                                             | 3.21                                                 | Synthesis                                                                                                                    | XNFinterface                                                                                                                                         | 1                                                  | 1                          | 1                    | 1                                                                                                                                                            |

| ПS                                    | XNF2LAS                                                                                           | 1a                                                   | Lasar model gen.                                                                                                             | XNF2LAS                                                                                                                                              | 1                                                  |                            |                      |                                                                                                                                                              |

| Logic Modeling<br>(Synopsys Division) | Smart Model<br>LM1200                                                                             |                                                      | Simulation Models<br>Hardware Modeler                                                                                        | In Smart Model Library<br>Xilinx Logic Module                                                                                                        | <i>\</i><br><i>\</i>                               |                            | <i>\</i><br><i>\</i> |                                                                                                                                                              |

| Logical Devices                       | CUPL                                                                                              | 4.5                                                  | Synthesis                                                                                                                    | Xilinx Fitter                                                                                                                                        | √                                                  |                            | 1                    |                                                                                                                                                              |

| Mentor Graphics                       | QuickSim II<br>Design Architect<br>Autologic                                                      | A.x_F<br>A.x_F<br>A.x_F                              | Simulation<br>Schematic Entry<br>Synthesis                                                                                   | Call Xilinx<br>Call Xilinx<br>Xilinx Synthesis Library                                                                                               | \<br>\<br>\                                        | \<br>\<br>\                | \<br>\<br>\          | \<br>\<br>\                                                                                                                                                  |

| MINC                                  | PLDesigner-XL                                                                                     | 3.3                                                  | Synthesis                                                                                                                    | Xilinx Design Module                                                                                                                                 | ✓                                                  |                            |                      |                                                                                                                                                              |

| Minelec                               | Ulticap                                                                                           | 1.32                                                 | Schematic Entry                                                                                                              | Xilinx Interface                                                                                                                                     | 2K,3K                                              |                            |                      |                                                                                                                                                              |

| OrCAD                                 | SDT386+<br>Capture<br>VST386+<br>Simulate<br>PLD 386+                                             | 1.2<br>6.0<br>1.2<br>6.0<br>2.0                      | Schematic Entry<br>Schematic Entry<br>Simulation<br>Simulation<br>Synthesis                                                  | Call Xilinx<br>Call Xilinx<br>Call Xilinx<br>Call Xilinx<br>Call OrCAD                                                                               | 1                                                  | XACT6<br>XACT6             | XACT6                | ХАСТ6                                                                                                                                                        |

| Protel                                | Advanced Schematic                                                                                | 2.2                                                  | Schematic Entry                                                                                                              | Xilinx interface                                                                                                                                     | 1                                                  |                            | 1                    |                                                                                                                                                              |

| Quad Design                           | Motive                                                                                            | 4.0                                                  | Timing Analysis                                                                                                              | XNF2MTV                                                                                                                                              | 1                                                  |                            |                      |                                                                                                                                                              |

| Simucad                               | Silos III                                                                                         | 95.100                                               | Simulation                                                                                                                   | Included                                                                                                                                             | 1                                                  |                            |                      | 1                                                                                                                                                            |

| Sophia Systems                        | Vanguard                                                                                          | 5.31                                                 | Schematic Entry                                                                                                              | Xilinx I/F Kit                                                                                                                                       | 1                                                  |                            | 1                    |                                                                                                                                                              |

| Synopsys                              | FPGA Compiler<br>Design Compiler<br>VSS                                                           | 3.3<br>3.3<br>3.3                                    | Synthesis<br>Synthesis<br>Simulation                                                                                         | Call Xilinx<br>Call Xilinx<br>Call Xilinx                                                                                                            | 3K,4K<br>✓<br>✓                                    | \<br>\<br>\                | \$<br>\$<br>\$       | \<br>\<br>\                                                                                                                                                  |

### ALLIANCE PROGRAM - COMPANIES & PRODUCTS - SEPTEMBER 1995 (con't)

| Company                   | PRODUCT NAME                         | VERSION            | FUNCTION                                   | DESIGN KIT                                | 2K/3K/4K<br>Support | XC5200<br>Support       | EPLD<br>Support | Unified Lib.<br>Support |

|---------------------------|--------------------------------------|--------------------|--------------------------------------------|-------------------------------------------|---------------------|-------------------------|-----------------|-------------------------|

| Synplicity                | Synplify<br>Synplify-Lite            | 2.5<br>2.5         | Synthesis<br>Synthesis                     | Included<br>Xilinx Mapper                 | 3K,4K<br>3K,4K      |                         |                 | √<br>√                  |

| Teradyne                  | Lasar                                | 6                  | Simulation                                 | Xilinx I/F Kit                            | ✓                   |                         |                 |                         |

| Tokyo Electron            | ViewCAD                              | 5.0502a            | FLDL to XNF translator                     | XNFGEN                                    | 1                   |                         |                 |                         |

| Topdown Design            | V-BAK                                | 1.1                | XNF to VHDL translator                     | XNF interface                             | ✓                   | 1                       |                 | 1                       |

| transEDA                  | TransPRO                             | 1.2                | Synthesis                                  | Xilinx Library                            | 1                   |                         |                 |                         |

| VEDA                      | Vulcan                               | 4.5                | Simulation                                 | Xilinx Tool Kit                           | 1                   |                         |                 |                         |

| Viewlogic                 | ProCapture<br>ProSim<br>ProSynthesis | 6.1<br>6.1<br>5.02 | Schematic Entry<br>Simulation<br>Synthesis | Call Xilinx<br>Call Xilinx<br>Call Xilinx | \$<br>\$<br>\$      | XACT6<br>XACT6<br>XACT6 | \<br>\<br>\     | √<br>√<br>√             |

| Viewpoint                 | VitalBridge<br>VeriLink              | 1.0<br>1.0         | Vital VHDL<br>Verilog lib. back-annotation | VHDL I/F kit<br>Verilog I/F kit           | √<br>√              |                         |                 |                         |

| Visual Software Solutions | StateCAD                             | 2.4                | State diagram                              | Xilinx fitter                             | 1                   |                         |                 |                         |

| Zycad                     | Paradigm XP<br>Paradigm RP           |                    | Gate-level simulation<br>Rapid prototyping |                                           | √<br>√              |                         |                 |                         |

### ALLIANCE PROGRAM - PLATFORMS & CONTACTS

|                           |                     |    | PLATI | FORM   |     |                 |

|---------------------------|---------------------|----|-------|--------|-----|-----------------|

| COMPANY                   | Contact Name        | PC | SUN   | RS6000 | HP7 | PHONE NUMBER    |

| Acugen                    | Peter de Bruyn Kops | 1  | 1     |        | 1   | 603-881-8821    |

| Aldec/Susie-CAD           | David Rinehart      | 1  |       |        |     | 702-293-2271    |

| Aptix Corporation         | Wolfgang Hoeflich   |    | 1     |        | 1   | 408-428-6200    |

| Cadence                   | Itzhak Shapira Jr.  |    | 1     | 1      | 1   | 408-428-5739    |

| Capilano Computing        | Chris Dewhurst      | 1  |       |        |     | 604-522-6200    |

| Compass Design            | Shahid Khan         |    | 1     |        | 1   | 408-433-4880    |

| Data I/O                  | Dave Kohlmeier      | 1  | 1     |        |     | 206-867-6802    |

| Escalade                  | Jerry Rau           |    | 1     | 1      |     | 408-481-1336    |

| Exemplar Logic            | Stan Ng             | 1  | 1     |        | 1   | 510-337-3700    |

| FlynnSystems              | Mike Jingozian      | 1  |       |        |     | 603-891-1111    |

| IBM-EDA                   | John Orfitelli      |    |       | 1      |     | 914-433-9073    |

| IKTechnology              | Hiroyuki Kataoka    |    |       |        | 1   | +81-3-3464-5551 |

| Ikos                      | Brad Roberts        |    | 1     |        | 1   | 408-366-8509    |

| Incases                   | Richard Collins     |    |       |        | 1   | 214-373-7344    |

| Intergraph Electronics    | Greg Akimoff        | 1  | 1     |        | 1   | 415-691-6541    |

| ISDATA                    | Ralph Remme         | ✓  | 1     |        | ✓   | +49-721-751087  |

| IST                       | Gabriele Saucier    | 1  | 1     |        | 1   | +33-76-70-51-00 |

| ITS                       | FrankMeunier        |    | 1     |        | 1   | 508-897-0028    |

| Logic Modeling            | Marnie McCollow     |    | 1     |        | 1   | 503-531-2412    |

| Logical Devices           | David Mot           | ✓  |       |        |     | 303-279-6868    |

| Mentor Graphics           | SamPicken           |    | 1     | 1      | 1   | 503-685-1298    |

| MINC                      | Lynne Dolan         | 1  | 1     |        | 1   | 719-590-1155    |

| Minelec (Belgium)         |                     | 1  |       |        |     | +32-02-4603175  |

| OrCAD                     | Troy Scott          | 1  |       |        |     | 503-671-9500    |

| Protel Technology         | Matthew Schwaiger   | 1  |       |        |     | 408-243-8143    |

| Quad Design Tech.         | Vern Potter         |    | 1     |        | 1   | 805-988-8250    |

| Simucad                   | Richard Jones       | 1  |       |        |     | 510-487-9700    |

| Sophia Systems            | BobArmstrong        | 1  | 1     |        | 1   | 408-943-9300    |

| Synopsys                  | Lynn Fiance         |    | 1     | 1      | 1   | 415-694-4102    |

| Synplicity                | Alisa Yaffa         | 1  | 1     |        | 1   | 415-961-4962    |

| Teradyne                  | MikeJew             |    | 1     |        | 1   | 617-422-3753    |

| Tokyo Electron            | Shige Ohtani        |    |       |        |     | +81-3-5561-7212 |

| TopDown                   | ArtPisani           | ✓  | 1     | 1      |     | 603-888-8811    |

| transEDA                  | JamesDouglas        |    | ✓     |        | ✓   | +44-1703-255118 |

| VEDA                      | GeorgeSher          |    | 1     |        | 1   | 408-496-4516    |

| ViewLogic                 | PreetVirk           | 1  | 1     | 1      | 1   | 508-480-0881    |

| Viewpoint International   | Ramesh Bhimarao     | 1  | 1     |        | 1   | 408-954-7370    |

| Visual Software Solutions | RickyEscoto         |    |       |        |     | 305-346-8890    |

| Zycad                     | David Allenbaugh    |    | 1     |        | 1   | 510-623-4451    |

|                                 |                                   |                           |                                    | PREVIOUS     | Curr         | ent Versi           | ON BY PL           | ATFORM             |                |

|---------------------------------|-----------------------------------|---------------------------|------------------------------------|--------------|--------------|---------------------|--------------------|--------------------|----------------|

| PRODUCT<br>CATEGORY             | PRODUCT<br>DESCRIPTION            | Product<br>Function       | XILINX PART<br>Number              | Ver.<br>Rel. | PC1<br>6.2   | <b>SN2</b><br>4.1.x | <b>AP1</b><br>10.4 | <b>HP7</b><br>9.01 | Last<br>Update |

| XILINX INDIVID                  | UAL PRODUCTS                      |                           |                                    |              |              |                     |                    |                    |                |

| CORE EPLD                       | XC7K SUPPORT                      | Core Implementation       | DS-550-xxx                         | 5.02         | 5.11         | 5.10                |                    | 5.10               | 01/95          |

| FLOORPLANNER <sup>4</sup>       | HI-DENSITY DES. KIT               | CORE IMPLEMENTATION       | ES-HD4K-SN2                        | N/A          |              | 5.10                |                    |                    | N/A            |

| Mentor <sup>2</sup>             | A.1-F                             | I/F AND LIBRARIES         | DS-344-xxx                         | 5.02         |              | 5.11                | 5.10               | 5.11               | 05/95          |

| OrCAD <sup>2</sup>              |                                   | I/F AND LIBRARIES         | DS-35-xxx                          | 5.00         | 5.10         |                     |                    |                    | 01/95          |

| SYNOPSYS <sup>2</sup>           |                                   | I/F AND LIBRARIES         | DS-401-xxx                         | 3.20         |              | 3.30                |                    | 3.30               | 06/95          |

| VIEWLOGIC <sup>2</sup>          | ProCapture                        | I/F AND LIBRARIES         | DS-390-xxx                         | 5.02         | 5.11         |                     |                    |                    | 05/95          |

| VIEWLOGIC <sup>2</sup>          | ProSim                            | I/F AND LIBRARIES         | DS-290-xxx                         | 5.02         | 5.11         |                     |                    |                    | 05/95          |

| VIEWLOGIC <sup>2</sup>          |                                   | I/F AND LIBRARIES         | DS-391-xxx                         | 5.10         | 5.11         | 5.11                |                    | 5.11               | 01/95          |

| XABEL <sup>2</sup>              |                                   | ENTRY, SIM, LIB, OPT.     | DS-371-xxx                         | 5.00         | 5.10         | 5.10                |                    |                    | 01/95          |

| X-BLOX <sup>1</sup>             |                                   | MODULE GENERATION & OPT.  | DS-380-xxx                         | 5.00         | 5.10         | 5.10                |                    | 5.10               | 01/95          |

| Verilog <sup>4</sup>            | 2K, 3K, 4K, 7K Lib.               | MODELS & XNF TRANS.       | ES-VERILOG-xxx                     |              |              | 1.00                |                    | 1.00               | N/A            |