# Viewlogic Interface Guide

Introduction

**Getting Started**

**Design Entry**

**Functional Simulation**

Implementing a Design

**Timing Simulation**

Design and Simulation Techniques

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A. Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CORE Generator, CoreGenerator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Foundation, HardWire, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, Select-RAM, Select-RAM+, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebLINX, XABEL, XACTstep, XACTstep Advanced, XACTstep Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479;

5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,777; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-1999 Xilinx, Inc. All Rights Reserved.

### **About This Manual**

This manual describes the Xilinx Viewlogic<sup>®</sup> Interface program, a tool used for interfacing Viewlogic's Workview Office<sup>®</sup> or Powerview<sup>®</sup> with the Xilinx tools to create FPGAs or CPLDs.

Before using this manual, you should be familiar with the operations that are common to all Xilinx software tools: how to bring up the system, select a tool for use, specify operations, and manage design data. These topics are covered in the *Development System Reference Guide*. Other publications you can consult for related information are the *Libraries Guide*, the *LogiBLOX Reference/User Guide*, the *Design Manager/Flow Engine Guide*, the *EPIC Design Editor Reference/User Guide*, and *The CPLD Schematic Design Flow*.

### **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this page. You can also directly access some of these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                          |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorial             | Tutorials covering Xilinx design flows, from design entry to verification and debugging http://support.xilinx.com/support/techsup/tutorials/index.htm                    |

| Answers<br>Database  | Current listing of solution records for the Xilinx software tools<br>Search this database using the search function at<br>http://support.xilinx.com/support/searchtd.htm |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches<br>http://support.xilinx.com/apps/appsweb.htm                                                           |

| Resource       | Description/URL                                                                                                                                                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Book      | Pages from <i>The Programmable Logic Data Book</i> , which describe device-specific information on Xilinx device characteristics, including readback, boundary scan, configuration, length count, and debugging http://support.xilinx.com/partinfo/databook.htm |

| Xcell Journals | Quarterly journals for Xilinx programmable logic users http://support.xilinx.com/xcell/xcell.htm                                                                                                                                                                |

| Tech Tips      | Latest news, design tips, and patch information on the Xilinx design environment http://support.xilinx.com/support/techsup/journals/index.htm                                                                                                                   |

### **Manual Contents**

This manual covers the following topics.

- The "Introduction" chapter describes the programs that comprise the Viewlogic interface and the Xilinx-Viewlogic design flow for FPGAs and CPLDs.

- The "Getting Started" chapter discusses how to configure your system to use Workview Office on a PC. It also discusses how to use the Xilinx interface with Powerview on workstations.

- The "Design Entry" chapter describes how to use ViewDraw to enter a schematic design. Not intending to document all the features of Workview Office, it discusses in detail the features needed for Xilinx designs.

- The "Functional Simulation" chapter describes how to prepare a simulation network for functional simulation within the Viewlogic simulation environment. It also describes how to load ViewTrace to view the simulation signals in a waveform format.

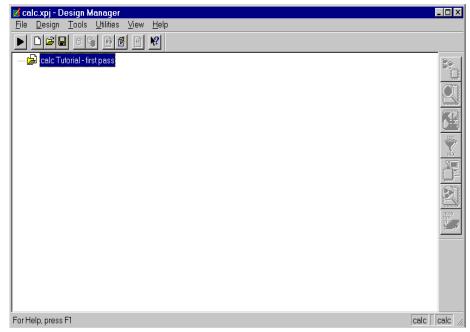

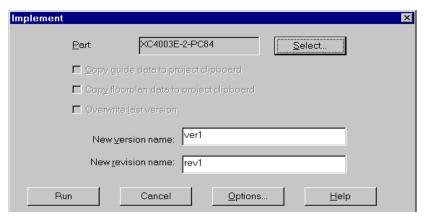

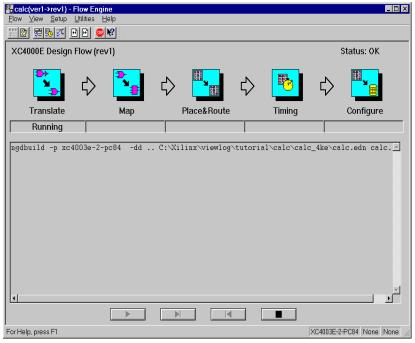

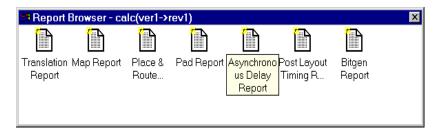

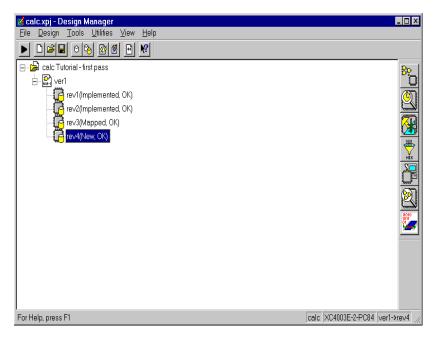

- The "Implementing a Design" chapter describes how to use the Design Manager and the Flow Engine to translate and implement your design.

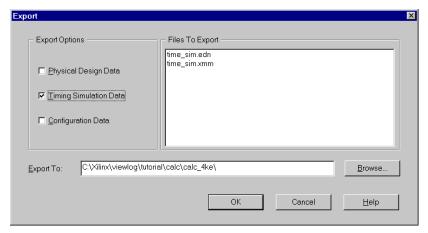

- The "Timing Simulation" chapter describes how to prepare a simulation network for timing simulation within the Viewlogic simulation environment. It also describes how to load ViewTrace to view the simulation signals in a waveform format.

The "Design and Simulation Techniques" chapter discusses aspects of schematic entry and simulation you need to know to use Workview Office and Powerview effectively.

### **Conventions**

This manual uses the following typographical and online document conventions. An example illustrates each typographical convention.

# **Typographical**

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

```

speed grade: -100

```

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

```

rpt_del_net=

```

Courier bold also indicates commands that you select from a menu.

```

\textbf{File} \rightarrow \textbf{Open}

```

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

```

edif2ngd design_name

```

References to other manuals

See the *Development System Reference Guide* for more information.

Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on | off}

```

A vertical bar " | " separates items in a list of choices.

```

lowpwr ={on | off}

```

A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

```

A horizontal ellipsis "..." indicates that an item can be repeated one or more times.

```

allow block block name loc1 loc2 . . . locn;

```

### **Online Document**

The following conventions are used for online documents.

- Red-underlined text indicates an interbook link, which is a crossreference to another book. Click the red-underlined text to open the specified cross-reference.

- Blue-underlined text indicates an intrabook link, which is a crossreference within a book. Click the blue-underlined text to open the specified cross-reference.

# Chapter 1

### Introduction

This chapter describes the programs that comprise the Viewlogic interface and the Xilinx-Viewlogic design flow for FPGAs and CPLDs. This chapter contains these sections.

- "Viewlogic Toolsets"

- "Viewlogic Programs"

- "Xilinx Device Support"

- "Following the Design Flow"

## **Viewlogic Toolsets**

The Viewlogic interface programs support both of Viewlogic's current systems, Workview Office and Powerview. However, this manual primarily discusses only Workview Office, the only Viewlogic software distributed by Xilinx.

### **Workview Office**

The Workview Office software runs on a Windows-based system.

This release supports Workview Office version 7.5 and later on Windows 95 and Windows NT 4.0.

### **Powerview**

The Powerview software runs on a workstation system with a graphic user interface.

This release supports Powerview V6.1 and later on SunOS $^{\text{TM}}$  V4.1.4, Solaris $^{\text{®}}$  V2.5, HP-UX $^{\text{®}}$  V10.2, and AIX $^{\text{®}}$  V4.1.5.

# **Viewlogic Programs**

This section briefly describes the Viewlogic programs used with Workview Office and Powerview.

### **ViewDraw**®

Viewlogic's schematic entry tool.

### **Digital Fusion**

Viewlogic's Integrated Simulation Environment tool that calls  $ViewSim^{\mathbb{B}}$  or Speedwave<sup>TM</sup> to run functional or timing simulations.

#### **ViewSim**

Viewlogic's gate-level simulator.

#### **Speedwave**

Viewlogic's VHDL simulator for Workview Office.

#### VWaves™

Viewlogic's waveform viewer and editor.

# Xilinx Device Support

The Viewlogic interface supports XC3000A/L, XC3100A, XC4000E/L/EX/XL/XLA/XLT/XV, XC5200, Spartan/XL, Virtex, and XC9500/XL/XV devices. XC9500/XL/XV are CPLD devices and the other families are FPGA devices.

# Following the Design Flow

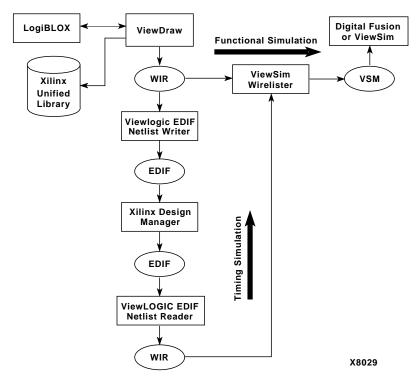

Creating FPGA and CPLD designs with Viewlogic tools involves the following steps.

- 1. Enter your design with the ViewDraw schematic editor, making sure that you observe the Xilinx design requirements noted in this manual.

- 2. Test the functionality of your design by creating a functional simulation network (VSM file) and loading it into Digital Fusion to simulate the design. You can use VWaves to view the waveforms generated by the simulation.

- 3. Implement your FPGA or CPLD design using Xilinx Design Manager.

- 4. Verify the timing of your design by creating a timing simulation network (VSM file) and loading it into Digital Fusion to simulate the design. You can use VWaves to view the waveforms generated by the simulation.

- 5. Download the design to the Xilinx device and verify the board.

The following figure shows the Xilinx-Viewlogic design flow.

Figure 1-1 Xilinx-VIEWlogic Flow

# Chapter 2

# **Getting Started**

This chapter discusses how to configure your system to use Workview Office on a PC. It also discusses how to use the Xilinx interface with Powerview on workstations. This chapter contains these sections.

- "Configuring for Workview Office"

- "Configuring for Powerview"

# **Configuring for Workview Office**

This manual provides instructions for Workview Office 7.5, including illustrations of that environment. However, you can use the Xilinx/Viewlogic interface programs with any current Viewlogic software, including Powerview 6.1.

### **Required Software**

To run Workview Office, you need the following versions of the development software.

- Workview Office release 7.5 or later

- Xilinx/Viewlogic Interface and Libraries version M1 or later

- Xilinx Development System Software version M1 or later

### Installing the Software

Before you can use the Workview Office software, you must set up your PC to use the Viewlogic and Xilinx Development System software.

- 1. Verify proper configuration of your system. Consult the Xilinx *Alliance Series 2.1i Installation Guide and Release Notes* for instructions about installing this software and setting up your machine to run the software.

- 2. Verify that your autoexec.bat file contains the following variables, assuming that you loaded the software noted in the previous step to the c:\wvoffice and c:\xilinx directories on your PC. If the software resides in different areas, modify the following Set statements according to the appropriate location. See the Xilinx Alliance Series 2.1i Installation Guide and Release Notes for additional information on system environment setup.

- The PATH variable sets the overall executable search path.

This variable must include the directories where the Work-view Office and Xilinx Development System software reside, as in the following example.

#### PATH=C:\XILINX\BIN\NT;C:\WVOFFICE;other\_paths

The PATH variable cannot include any previous version of either the Xilinx or Viewlogic software. Remove all paths to older software.

Xilinx and Workview Office software use the XILINX variable to locate data files. This variable must specify the directory where the Xilinx Development System resides, as in the following example.

#### SET XILINX=C:\XILINX

Set the WDIR variable for the data file search path for the Workview Office software as follows.

#### SET WDIR=C:\WVOFFICE\STANDARD

The LM\_LICENSE\_FILE variable directs the software to the license files. The location of these files do not matter as long as this variable points to the license files themselves, not just the directory where they reside. The first license file authorizes the Workview Office tools: the other authorizes the Xilinx tools(M1.4 and older versions). Xilinx M1.5 and later versions does not require a license.

The following syntax applies to Workview Office 7.31 and older versions only.

SET LM\_LICENSE\_FILE=C:\WVOFFICE\STAN-DARD\LICENSE.DAT,;C:\FLEXLM\LICENSE.DAT

Because the Workview Office 7.5 (and older versions) and the Xilinx M1 software use different versions of the FLEXIm software, you must specify the Workview Office license file first. Separate this path from the Xilinx license file by a comma followed by a semicolon (,;). For Workview Office 7.4 and newer versions, use only the semicolon as the delimiter.

Speedwave uses the VANTAGE\_VSS and VANTAGE\_CC variables for functional VHDL simulation. Only systems with extended licenses require these variables as shown in the following examples.

SET VANTAGE\_VSS=C:\WVOFFICE\V

SET VANTAGE CC=C:\WVOFFICE\MSVCNT\BIN\CL

3. After you install the Xilinx and Viewlogic software tools, you must copy two files from the Xilinx install directory to the Workview Office tree. You can find these two files, LIBS.LST and POWERVIE.INI, in the C:\XILINX\_PATH\VIEWLOG\DATA directory. In Windows Explorer, copy these to files to the STAN-DARD directory of the Workview Office tree (for example, C:\WVOFFICE\STANDARD), replacing the two files of the same names that currently exist there.

You must install these two files for a Xilinx-specific installation of Workview Office.

- libs.lst, a library definition that contains the updated listing for the M1 libraries.

- powervie.ini, a file that contains a string that tells Workview Office to use a Xilinx-restricted license.

### **Verifying Your Software Setup**

Before beginning a project, use the following steps to verify the correct software setup.

- 1. Verify the proper loading of Viewlogic and Xilinx software according to the instructions provided, and that your paths are set correctly.

- Customize the Workview Office Toolbar according to your preference. Click on the Workview Office Icon (farthest to the left) to see your customizing options. The Moveable Window Toolbar appears in the following figure.

Figure 2-1 Workview Office Toolbar

- 3. Click on the Workview Office icon located at the far left on the Workview Office Toolbar. A pull-down menu appears.

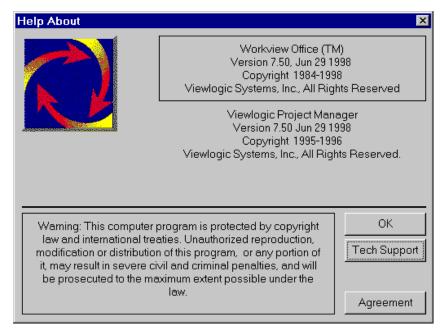

- 4. Click on About Workview Office...

The Workview Office "Help About" screen appears, as shown in the following figure.

Figure 2-2 Workview Office Help About Window

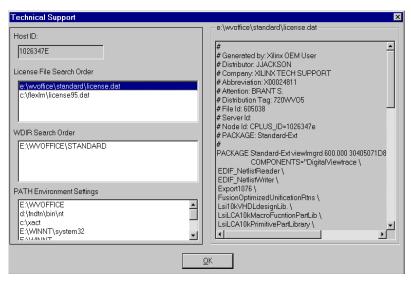

5. Click on the **Tech Support** button.

The Technical Support Box appears as shown in the next figure.

Figure 2-3 Technical Support Box

- 6. Verify that your Host ID number displays correctly. If you use a node-lock license, this number reads from the security key. If the key is missing, "unknown" appears in the box designated for the Host ID. Windows NT 4.0 sometimes requires the installation of a sentinel driver in order to display the security key. If your key is attached to the system and your Host ID appears as "unknown," please look for the solution located at http://support.xilinx.com/support/searchtd.htm

- 7. Directly below your Host ID number is the path you designate for the License File Search Order. Click on the following line.

#### C:\WVOFFICE\STANDARD\LICENSE.DAT

The license.dat file appears in the display window to the right.

- 8. Scroll down to the bottom of this window and verify that the Host ID number that appears near the lower-right corner matches the one in the upper-left corner.

- Verify that the WDIR Search Order displays C:\WVOF-FICE\STANDARD, and that the PATH Environment Settings display properly. If either of these two windows is empty, modify the autoexec.bat file accordingly.

**Note:** As previously stated, these environment settings assume that you installed the Workview Office software to C:\WVOFFICE. If this is not the case, you must change these settings.

10. After verifying all the settings, Click OK and the Technical Support window closes. Click OK in the Help About window and it closes.

You can now open an existing project or start a new project.

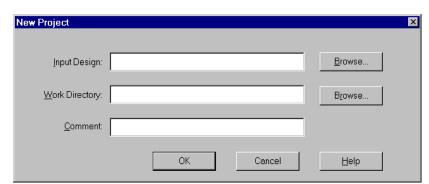

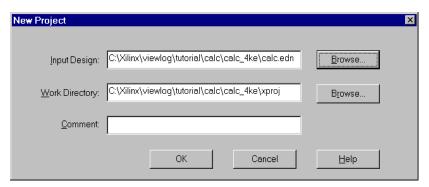

# **Creating a Project**

A project consists of a working directory that contains the sub-directories and data files for a given design. To create a project, select the libraries you need, arrange them in a particular search order, and save that scheme under the project directory. Saving this directory results in the creation of the following two files.

- *design*.vpj (Viewlogic project directory)

- viewdraw.ini (the initialization file)

The *design*.vpj file includes working directory and library information for your project. After you define your project libraries and set them up in the correct search order, saving the setup creates the file. This file can reside outside the project directory.

Project Manager creates the viewdraw.ini file automatically whenever you define or make changes to a project. This file contains library information as well as project settings. Do not modify the viewdraw.ini file directly. This file must reside in the project directory.

### **Setting Up Your Project Libraries**

This section provides information about specifying the library search order. Use the following table to determine which library to use for particular Xilinx family members.

Table 2-1 Xilinx Families and Libraries

| Family                                             | Library   |

|----------------------------------------------------|-----------|

| XC3000A, XC3000L, XC3100A                          | XC3000    |

| XC4000E, XC4000L                                   | XC4000E   |

| XC4000EX, XC4000XL, XC4000XLA, XC4000XLT, XC4000XV | XC4000X   |

| XC5200                                             | XC5200    |

| Spartan                                            | Spartan   |

| SpartanXL                                          | SpartanXL |

| Spartan2                                           | Spartan2  |

| Virtex                                             | Virtex    |

| XC9500, XC9500XL, and XC9500XV                     | XC9500    |

The XC4000EX library changed in M1.4. Any design using the XC4000EX/XL/XV family should now use the XC4000X library.

### Upgrading to M1.x for Existing M1.3 Designs

For existing M1.3 designs that use the XC4000EX library, you must make the following modifications when upgrading to M1.x. Taking these steps enables both the old (XC4000EX) and the new (XC4000X) aliases to refer to the new library.

- With M1.x software installed, select the XC4000EX/XL/XV library listing.

- 2. In the library search order window, select the XC4000X library.

- 3. Modify the alias to read XC4000EX.

- 4. Click on Add, (not Change).

- 5. Use the Move Up button to position this new library reference below the existing XC4000X library.

### **Creating the Library Search Order**

This section describes the steps for creating the library search order.

1. On the Workview Office Task Bar, click on the Project Manager icon.

The Viewlogic Project Manager window appears.

2. Define the project directory.

A prompt asks you to enter your project directory when you create a new project. To change your project directory, select Edit—Project Directory, then browse to the location.

3. Select Edit→Libraries from the pulldown menus.

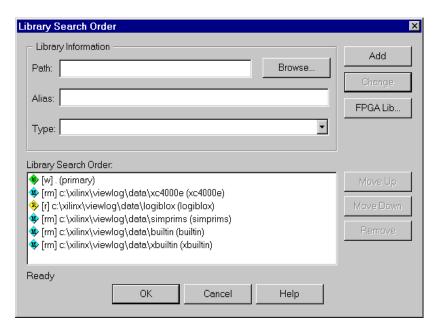

The Library Search Order dialog box appears.

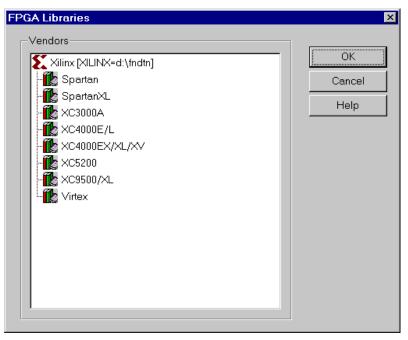

4. Click on the **FPGA Lib...** button in the Library Search Order dialog box.

The FPGA Libraries menu appears as shown in the following figure.

Figure 2-4 FPGA Libraries Menu

- 5. Choose a Xilinx family and click OK.

- 6. Add a Primary library for storing user-created symbols and schematics, and so you can apply the primary alias to all user-created symbols taken from this library. In the Library Information section of the Library Search Order window, create a new library with the following criteria.

- Path: .

- Alias: primary

- Type: writable

Click on Add after creating the library.

7. Make this new directory first in the search order, so select this directory and click on the Move Up button until the Primary library appears at the top. Click OK.

The Library Search Order window should look similar to the one in the next figure. This example shows the library search order for an XC4000E design.

Figure 2-5 Final Library Search Order

8. Add any other user-created libraries.

For each library, fill out the three fields in the Library Information section. Define the full path to the library, a unique alias, and the type, then click Add. Use the Move Up button to place these libraries between the primary library and the Xilinx family library.

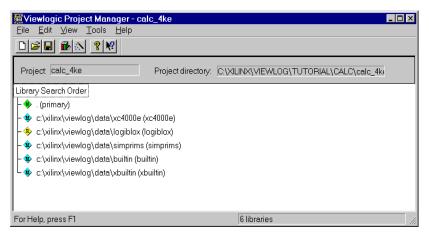

#### Click OK.

The Viewlogic Project Manager window appears with the libraries listed the same way you arranged them in the Library Search Order window, as shown in the following figure.

Figure 2-6 Viewlogic Project Manager

10. Select File→Save As and enter filename.vpj.

This saves all of the library and project information in the filename.vpj file and automatically places (or updates) the viewdraw.ini file in the project directory.

In summary, a valid Xilinx project requires a library search order that contains the following items (shown in the proper order).

- 1. Primary

- 2. User-created libraries (optional)

- 3. Family library (for example, XC4000E)

- 4. LogiBLOX (optional)

- 5. SimPrims

- 6. Builtin

- 7. Xbuiltin

To designate this as your current working project and begin working on this project in ViewDraw, open this file in the Viewlogic Project Manager. Close all other Viewlogic tools (such as ViewDraw and ViewSim) before changing projects.

### Setting Up To Use LogiBLOX

Using the LogiBLOX Module Selector can require a few additional setup steps, depending on which type of simulation model you want LogiBLOX to create. This section outlines these steps.

- Ensure that the Add LogiBLOX and Change LogiBLOX commands appear on the ViewDraw tools menu. If they do not, see the "Adding LogiBLOX Custom Commands to ViewDraw" section.

- 2. Ensure that your viewdraw.ini search order includes both the LogiBLOX library and the SimPrims library, each with the appropriate alias. See the "Creating the Library Search Order" section for details about this.

- Decide which type of simulation model you want LogiBLOX to create, behavioral VHDL or gate-level EDIF. See the "Choosing Between VHDL and EDIF Models" section.

- 4. If you want LogiBLOX to create VHDL models, you need to complete the following steps.

- a) Locate the Speedwave library that contains the LogiBLOX VHDL source provided by Xilinx. If your site has not analyzed this library, you need to run the Speedwave analyzer. See the "Analyzing the LogiBLOX VHDL Library" section.

- b) Create a Speedwave working library in your current project directory for analyzed LogiBLOX models. Define the Speedwave VHDL library search order to include this working library, the LogiBLOX VHDL library (described above) and the standard IEEE library. See the "Initializing the Project for Speedwave" section.

### Adding LogiBLOX Custom Commands to ViewDraw

You can add the following two custom Xilinx commands to the Tools menu in ViewDraw.

- Add LogiBLOX

- Change LogiBLOX

If these commands do not already appear on your ViewDraw **Tools** menu, you need to customize the Tools menu accordingly.

To customize the Tools menu, run the following from a command (MS-DOS) prompt.

#### custmenu xilinx\_path\viewlog\data\viewblox.txt

The custmenu program installs with Workview Office and uses the information in the viewblox.txt file (provided by Xilinx) to customize the ViewDraw Tools menu. ViewDraw cannot run when you execute the custmenu command.

Alternatively, you can customize the Tools menu directly in View-Draw, by following these steps.

- 1. Start the ViewDraw application.

- 2. Select Tools—Customize.

The Customize Tools Menu dialog appears.

3. Choose User Menu or Common Menu.

Adding the LogiBLOX commands to the Common menu allows all users of ViewDraw on that machine to see the commands. Adding the commands to the User menu makes them visible only when you run ViewDraw.

4. To add the Add LogiBLOX command, complete the fields as shown in the following table and click the Add button.

| In Field  | Enter Text    | Comments                                                                                                               |

|-----------|---------------|------------------------------------------------------------------------------------------------------------------------|

| Menu Text | &Add LogiBLOX | The & indicates that A is the keyboard equivalent for this menu item. You can choose a different mnemonic if you want. |

| Command   | viewblox.exe  | This executable resides in the same directory as all other Xilinx executables, found via your system path.             |

Table 2-2 Adding LogiBLOX

Table 2-2 Adding LogiBLOX

| In Field          | Enter Text | Comments                                                                                                                   |

|-------------------|------------|----------------------------------------------------------------------------------------------------------------------------|

| Arguments         | \$GUID     | This tells ViewDraw to pass a unique code to LogiBLOX, which uses this code to identify the invoking instance of ViewDraw. |

| Initial Directory |            | Leave the directory field blank. This indicates that the initial directory is the project directory.                       |

5. To add the Change Logiblox command, change the fields as shown in the next table and click the Add button.

Table 2-3 Changing LogiBLOX

| In Field          | Enter Text       | Comments                                                                                                                                                                                            |

|-------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Menu Text         | Change L&ogiBLOX | The & indicates that O is the keyboard equivalent for this menu item. You can choose a different mnemonic if you want.                                                                              |

| Command           | viewblox.exe     | This executable resides in the same directory as all other Xilinx executables, found via your system path.                                                                                          |

| Arguments         | \$GUID /modify   | This tells ViewDraw to pass a unique code to LogiBLOX, which uses this code to identify the invoking instance of ViewDraw. The modify option tells LogiBLOX that a Change command is being invoked. |

| Initial Directory |                  | Leave the directory field blank. This indicates that the initial directory is the project directory.                                                                                                |

6. Click the OK button to close the Customize dialog box.

### **Choosing Between VHDL and EDIF Models**

For functional simulation purposes, LogiBLOX can create either behavioral VHDL models or gate-level EDIF models. Which type you choose depends on your available VIEWlogic simulator, as described in this section.

To use VHDL models, you must have a license for the Speedwave simulation engine (also known as Vantage). This simulation flow takes advantage of the mixed gate-VHDL capability of Speedwave, modelling LogiBLOX modules in VHDL, the remainder of the schematic design in gates.

If you do not have Speedwave available, use LogiBLOX to create EDIF models. These gate-level models translate into VIEWlogic WIR files, usable by the standard Viewsim gate simulator.

VHDL model creation is faster than EDIF model creation in Logi-BLOX. Use VHDL models if your VIEWlogic environment supports it.

Specify the simulation model type in the LogiBLOX Setup dialog, as described in the "Adding LogiBLOX Components" section of the "Design Entry" chapter.

### **Analyzing the LogiBLOX VHDL Library**

The VHDL models created by LogiBLOX use some standard functions defined in the LogiBLOX VHDL library. Xilinx provides the VHDL source files for this library and you can find these in the standard Xilinx installation area. You need to analyze this library for Speedwave, making sure that analyzed library is available at the time you create individual LogiBLOX modules.

You need to analyze the LogiBLOX VHDL library only once, unless you upgrade your version of Speedwave or Xilinx software. Multiple projects can reference a single copy of the analyzed LogiBLOX library.

To analyze the LogiBLOX VHDL library for Speedwave, run the following Xilinx-provided batch file from a command (MS-DOS) prompt.

vaninit wvoffice\_path\v\pgm\libs

This creates the logiblox.lib Speedwave library directory under the specified *wvoffice\_path*\v\pgm\libs directory.

### Initializing the Project for Speedwave

LogiBLOX analyzes a VHDL simulation model into the current working Speedwave library after it creates the model. For this analysis to succeed, define the Speedwave VHDL library search order for the current project. The project requires a valid working library.

To create the working library and define the VHDL library search order, follow these steps.

- 1. Start the Digital Fusion or Speedwave application.

- 2. Choose File→Analyze VHDL Design.

- 3. After the HDL manager jumpstart wizard displays, click Next.

- 4. To use an existing VHDL library as your working library, click Yes, please use my existing library and browse for the library. Otherwise, click Next and your Library Path is set to your current Project Directory. Click Next again (if you used an existing library, skip to step 6).

- You can now add your source files to your newly created VHDL library. Browse for your VHDL files and add them to your source files. After making the addition(s), click Next.

- 6. The VHDL System Libraries displays. Select it by clicking on the checkbox to the left of each Library. Select IEEE.LIB, and LOGI-BLOX.LIB. If SYNOPSYS.LIB appears in the Available Libraries list, select it. (If you installed the Vantage Speedwave libraries with Workview Office, SYNOPSYS.LIB does not appear; you do not need it.) After you have made the selections, click Finish and the HDL Manager appears.

- The VHDL View should now have four libraries with check marks (three libraries if you use the Vantage Speedwave libraries). The VHDL User Library in this list is the working library.

- 8. Choose File→Save As to save the VHDL library search order for the current project.

- 9. Choose File→Exit to leave the HDL Manager; you can also exit from Digital Fusion at this point.

### **Setting Up Other Custom Menus**

There are additional custom Xilinx commands you can add to the Tools menu in ViewDraw.

- Write Xilinx EDIF

- Xilinx Functional Simulation

- Read Xilinx Timing EDIF

To customize the Tools menu with these commands, run the following from a command (MS-DOS) prompt.

- Windows 95

custmenu xilinx\_path\viewlog\data\xvdraw95.exe

- Windows NT

custmenu xilinx\_path\viewlog\data\xvdrawnt.exe

Alternatively, you can customize the Tools as explained in the "Adding LogiBLOX Custom Commands to ViewDraw" section. Complete the fields in Customize Tools Menu window as shown in the following tables.

Table 2-4 Adding Tools

| In Field  | Enter Text            | Comments                                                                                                                                 |

|-----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Menu Text | &Write Xilinx<br>EDIF | The & indicates that W is the keyboard equivalent for this menu item. You can choose a different mnemonic if you want.                   |

| Command   | cmd.exe               | This executable resides in the WINNT/system32 path of your Windows NT system. For Windows 95 system, change this command to command.exe. |

Table 2-4 Adding Tools

| In Field          | Enter Text                              | Comments                                                                                                                                                                       |

|-------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arguments         | edifneto -1<br>xilinx \$BLOCK-<br>NAMES | If the current schematic is called DESIGN.1, this command creates a DESIGN.EDN file readable by Xilinx M1 Design Manager. The -l xilinx option is required for Xilinx designs. |

| Initial Directory |                                         | Leave the directory field blank. This indicates that the initial directory is the project directory.                                                                           |

**Table 2-5 Changing Tools**

| In Field          | Enter Text                  | Comments                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Menu Text         | Read Xilinx<br>&Timing EDIF | The & indicates that T is the keyboard equivalent for this menu item. You can choose a different mnemonic if you want.                                                                                                                                                                                                                   |

| Command           | cmd.exe                     | This executable resides in the WINNT/<br>system32 path of your Windows NT<br>system. For Windows 95 system,<br>change this command to<br>command.exe.                                                                                                                                                                                    |

| Arguments         | edifneti<br>time_sim.edn    | This command reads in the Timing Simulation Data produced by the Xilinx M1 Core Technology tools.  TIME_SIM.1 writes into the project WIR directory, along with a number of XBA#.1 files. Follow this step with Tools → Create Digital  Netlist, filling in the Design Name field with TIME_SIM.1, to run a Viewlogic Timing Simulation. |

| Initial Directory |                             | Leave the directory field blank. This indicates that the initial directory is the project directory.                                                                                                                                                                                                                                     |

Table 2-6 Functional Simulation Tools

| In Field          | Enter Text                         | Comments                                                                                                               |

|-------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Menu Text         | Xilinx &Func-<br>tional Simulation | The & indicates that F is the keyboard equivalent for this menu item. You can choose a different mnemonic if you want. |

| Command           | vfuncsim.exe                       | This executable resides in the same directory as all other Xilinx executables, found via your system path.             |

| Arguments         | \$BLOCKNAME                        |                                                                                                                        |

| Initial Directory |                                    | Leave the directory field blank. This indicates that the initial directory is the project directory.                   |

VFUNCSIM.EXE runs five programs, EDIFNETO, NGDBUILD, NGD2EDIF, EDIFNETI, and VSM. Refer to the "Using Powerview to Create the Functional Simulation Netlist for Category A Designs" section of the "Functional Simulation" chapter for more information about the command lines used.

# **Configuring for Powerview**

This section contains information about the required Powerview software, installing the software, setting up your project libraries, and setting up to use LogiBLOX.

### **Required Software**

To run Powerview, you need the following versions of the development software.

- Powerview release 6.1 or later

- Xilinx/Viewlogic Interface and Libraries version M1 or later

- Xilinx Development System Software version M1 or later

### **Installing the Software**

The following instructions assume that you already installed and configured Powerview software. Please consult the Viewlogic documentation for details about installing and configuring Powerview.

- Install Xilinx's M1 Development System and the Xilinx-Viewlogic Interface Tools and Libraries. Ensure that your .cshrc or .login file sets the XILINX environment variable to point to the root of the Xilinx software tree and that your path contains the appropriate platform bin directory. Consult the Xilinx Alliance Release Document for instructions about setting up your machine to run the Xilinx software.

- Define the WDIR environment variable for Powerview in your .cshrc or .login file. To integrate Xilinx LogiBLOX with Powerview, you must add the following directory to the beginning of your WDIR variable (separated from the existing path by a colon).

```

$XILINX/viewlog/data/logiblox/standard

```

For example, if Powerview is in /tools/powerview, enter the following.

setenv WDIR \$XILINX/viewlog/data/logiblox/standard:/tools/powerview/standard

This command adds this Xilinx directory to the WDIR variable so that ViewDraw can locate the ViewScript customizations for LogiBLOX. You can place this directory anywhere in your WDIR search path, provided that the Xilinx directory is the first (or only) one that contains a vdrawus.vs file (this file contains customizations to ViewDraw). If you have other customizations in a vdrawus.vs file elsewhere in your WDIR search path, you can merge the Xilinx customizations into your existing vdrawus.vs file. Add the following line to the end of that file.

```

load( "logiblox.vs" );

```

### **Setting Up Your Project Libraries**

Powerview uses the viewdraw.ini file to set up the ViewDraw environment. You modify the viewdraw.ini file manually.

The viewdraw.ini file contains the path and directory search order for your libraries. You must keep a copy of the viewdraw.ini file in each project directory so you can customize the library search order for each project.

The library search order format allows you to specify an unlimited number of directories, with only one primary directory, as well as the library directories search order. The order of the list of directories at the end of the viewdraw.ini file determines the search order.

### Viewdraw.ini File Syntax

Use the following syntax when adding libraries to the viewdraw.ini file.

```

DIR [type] path (alias)

```

- Path is the full path specification of the library. Specifying a

period (.) as the path name for the primary ([p]) directory causes

ViewDraw to use the directory where the file resides as the base

directory for all new schematics, user-generated symbols,

netlists, and related simulation files.

- *Alias* is the library name associated with each component that you place in your schematic.

- *Type* indicates one of the following library directory formats.

- [p] denotes the primary or project directory. All symbols and schematics that you create are saved here.

- [w] indicates a read-write directory.

- [r] indicates a read-only directory.

- [m] indicates a library compressed into a megafile format. Megafiles are read-only by default.

### **Adding Xilinx Libraries**

Use the information in the "Xilinx Families and Libraries" table to determine which library to use for each particular Xilinx family member.

#### **Upgrading to M1.x for Existing M1.3 Designs**

For existing M1.3 designs that use the XC4000X library, you must make the following modifications when upgrading to M1.x. Taking these steps enables both the old (XC4000EX) and the new (XC4000X) aliases to refer to the new library.

- Follow the library setup instructions required for the XC4000X library.

- Duplicate the XC4000 library, modifying the alias to **xC4000EX**. Ensure both of the following lines exist in your viewdraw.ini.

```

DIR [m] /xilinx_path/viewlog/data/xc4000x (xc4000x)

DIR [m] /xilinx_path/viewlog/data/xc4000x(xc4000ex)

```

You cannot mix different family libraries in the same project directory. Specify libraries from exactly one Xilinx family for each project directory.

#### Adding SimPrims, Builtin, and Xbuiltin Libraries

The Xilinx Viewlogic library package includes the builtin library, a simplified version of the complete builtin library sold by Viewlogic. Use only the Xilinx-supplied builtin library (/xilinx\_path/viewlog/data/builtin) in any Xilinx project directory.

You must add the SimPrims, builtin, and xbuiltin libraries (the Viewlogic simulation model libraries) to the viewdraw.ini file.

You cannot use the SimPrims, builtin, or xbuiltin libraries to capture your design.

#### **Adding Library Aliases**

When specifying the library search order, you must also add a library alias to each library directory. A library alias is a name that identifies a specific library directory along with the parts that it contains. The alias distinguishes identically named components from different libraries. You must specify, in parenthesis, in the viewdraw.ini file the aliases for each Xilinx library for proper netlist translation.

#### **Specifying the Library Search Order**

Library directories should conform to the search order shown in the following table.

Table 2-7 Library Search Order

| Туре | Path                                | Alias     |

|------|-------------------------------------|-----------|

| p    | / project_directory                 | primary   |

| m    | /xilinx_path/viewlog/data/xc3000    | xc3000    |

| m    | /xilinx_path/viewlog/data/xc4000e   | xc4000e   |

| m    | /xilinx_path/viewlog/data/xc4000x   | xc4000x   |

| m    | /xilinx_path/viewlog/data/xc5200    | xc5200    |

| m    | /xilinx_path/viewlog/data/spartan   | spartan   |

| m    | /xilinx_path/viewlog/data/spartanxl | spartanxl |

| m    | /xilinx_path/viewlog/data/spartan2  | spartan2  |

| m    | /xilinx_path/viewlog/data/virtex    | virtex    |

| m    | /xilinx_path/viewlog/data/xc9000    | xc9000    |

| r    | /xilinx_path/viewlog/data/logiblox  | logiblox  |

| m    | /xilinx_path/viewlog/data/simprims  | simprims  |

| m    | /xilinx_path/viewlog/data/builtin   | builtin   |

| m    | /xilinx_path/viewlog/data/xbuiltin  | xbuiltin  |

Include the library alias names under the Library column. You must enter these aliases exactly as shown.

You can add user-defined libraries, but you must add them after the primary directory.

#### XC4000XL/XV Library Search Order Example

For a new XC4000XL/XV design on a workstation, ensure the library definition section looks like this.

```

DIR [p] .(primary)

DIR [m] /xilinx_path/viewlog/data/xc4000x (xc4000x)

DIR [r] /xilinx_path/viewlog/data/logiblox (logiblox)

DIR [m] /xilinx_path/viewlog/data/simprims (simprims)

DIR [m] /xilinx_path/viewlog/data/builtin (builtin)

DIR [m] /xilinx_path/viewlog/data/xbuiltin (xbuiltin)

```

### **Setting Up To Use LogiBLOX**

Using the LogiBLOX Module Selector requires a few additional setup steps, depending on which type of simulation model you want Logi-BLOX to create. This section outlines these steps.

**Note:** When you use LogiBLOX for the first time in a new project, it checks your setup, allowing you to correct any setup problems at that time. If you want LogiBLOX to do the setup for you, you need only review the "Choosing Between VHDL and EDIF Models" section.

- Ensure that your viewdraw.ini search order includes both the LogiBLOX library and the SimPrims library, each with the appropriate alias. See the "Specifying the Library Search Order" section for details about this.

- 2. Decide which type of simulation model you want LogiBLOX to create, either behavioral VHDL or gate-level EDIF. See the "Choosing Between VHDL and EDIF Models" section.

- 3. If you want LogiBLOX to create VHDL models, you need to complete the following steps.

- a) Locate the Vantage library that contains the LogiBLOX VHDL source provided by Xilinx. If this library has not already been analyzed at your site, you need to run the Vantage analyzer. Ensure your vsslib.ini file contains the path to the analyzed library. See the "Analyzing the LogiBLOX VHDL Library" section.

- b) Create a Vantage working library in your current project directory to contain analyzed LogiBLOX models. Your vsslib.ini file designates this as the working library. See the "Creating a Vantage Library for the Project" section.

- c) Create a vsslib.ini initialization file, required by LogiBLOX and by the Fusion simulator. See the "Creating the vsslib.ini Library List File" section.

#### **Choosing Between VHDL and EDIF Models**

For functional simulation purposes, LogiBLOX can create either behavioral VHDL models or gate-level EDIF models. Which type you choose depends on which VIEWlogic simulator you have available, as described in this section.

To use VHDL models, you must have a license for the FusionHDL or Fusion/Speedwave simulation engine (also known as Vantage). This simulation flow takes advantage of the mixed gate-VHDL capability of Fusion, modelling LogiBLOX modules in VHDL, the remainder of the schematic design modelled in gates.

If you do not have a Fusion/Speedwave license, use LogiBLOX to create EDIF models. These gate-level models translate into VIEW-logic WIR files, simulated by the standard Viewsim gate simulator.

Because VHDL model creation is faster that EDIF model creation in LogiBLOX, use VHDL models if your VIEWlogic environment supports it.

Specify the simulation model type in the LogiBLOX Setup dialog, as described in "Adding LogiBLOX Components" section of the "Design Entry" chapter.

#### Analyzing the LogiBLOX VHDL Library

The VHDL models created by LogiBLOX use some standard functions defined in the LogiBLOX VHDL library. Xilinx provides the VHDL source files for this library. Find these VHDL source files in the standard Xilinx installation area. You must analyze this library for Vantage. Make the analyzed library available at the time you create individual LogiBLOX modules.

You do not need to re-analyze the LogiBLOX library for every new project. However, a Vantage library is specific to the platform and operating system under which it was analyzed, so you must ensure that the library you use is correct for your environment.

To analyze the LogiBLOX VHDL library for Vantage, run the following command from the UNIX prompt.

#### vaninit parent\_directory

This Xilinx-provided script creates a new logiblox.lib Vantage library directory under the *parent\_directory* that you specify.

If you want to analyze the LogiBLOX library manually, follow these steps.

Ensure that the Vantage analysis tools are properly configured.

Define the VANTAGE\_VSS environment variable and place the Vantage analysis tools in the system path. Consult the VIEWlogic documentation for details about this.

- Change to the directory where you want to create the Vantage library for LogiBLOX. The Vantage tools create a directory called "logiblox.lib" below the current one. Run the remaining steps from this directory.

- 3. Run the following command to create a new Vantage library for the LogiBLOX VHDL source.

```

vanlibcreate logiblox.lib LOGIBLOX

```

The symbolic name of the new library is the last argument to this command, LOGIBLOX. Do not substitute any other name, as the LogiBLOX-generated VHDL models reference the library by this name.

Run the following commands to analyze the LogiBLOX VHDL source files.

```

analyze -src $XILINX/vhdl/src/logiblox/

mvlutil.vhd -lib logiblox.lib -libieee

analyze -src $XILINX/vhdl/src/logiblox/

mvlarith.vhd -lib logiblox.lib -libieee

analyze -src $XILINX/vhdl/src/logiblox/logiblox.vhd -lib logiblox.lib -libieee

```

Analyze the three VHDL source files in the order shown above.

Your vsslib.ini file for each project using LogiBlox specifies the Vantage library created here. You can find more information about the vsslib.ini file in the "Creating the vsslib.ini Library List File" section.

#### Creating a Vantage Library for the Project

LogiBLOX creates and then analyzes a VHDL simulation model into the current working Vantage library. Typically, you want this working library to reside under the VIEWlogic project directory. This section describes how to create a new Vantage library for this purpose. The following section describes how to designate this new library as the working library in vsslib.ini.

To create a new Vantage library under the project directory, move to the project directory and run the following command.

```

vanlibcreate logiview.lib LOGIVIEW

```

You can choose a different directory name and symbolic name for this library.

#### Creating the vsslib.ini Library List File

The vsslib.ini file tells the Vantage analysis tools (run from Logi-BLOX) where to find the current working library, the analyzed Logi-BLOX VHDL library, and the standard IEEE library.

The vsslib.ini file, a simple text file, lists the path to each Vantage library directory on a separate line. The first directory listed is considered the working library during analysis of LogiBLOX models. The order of directories is otherwise irrelevant.

The vsslib.ini file specifies the following directories.

- The Vantage library into which LogiBLOX models analyze. Make this the first directory listed in vsslib.ini because it is considered the working directory.

- 2. The analyzed version of the LogiBLOX VHDL library.

- 3. The standard IEEE library provided with the Vantage tools.

The following example shows a complete vsslib.ini file.

```

/proj/designs/memmap/logiview.lib

/proj/vanlibs/xilinx/logiblox.lib

/tools/powerview/standard/van_vss/pgm/libs/ieee.lib

```

In this example, *logiview.lib* is the working library.

# Chapter 3

# **Design Entry**

This chapter describes how to use ViewDraw to enter a schematic design. This chapter does not document all the features of Workview Office, but instead discusses in detail the tools you need for specific Xilinx features.

For more information about commands and tools in Workview Office, consult the online help files described in the "Obtaining Help" section.

This chapter contains these sections.

- "Invoking ViewDraw"

- "Opening an Existing Schematic"

- "Creating a New Schematic"

- · "Obtaining Help"

- "Working in ViewDraw"

- "Adding Components"

- "Adding LogiBLOX Components"

- "Changing Components"

- "Changing LogiBLOX Components"

- "Adding Nets"

- "Adding Buses"

- "Creating Custom Macros"

- "Creating Symbols (Macros)"

- · "Adding Labels"

- "Adding Attributes"

- "Saving Schematics"

- "Closing Schematics"

- "Converting a Design"

## **Invoking ViewDraw**

To start ViewDraw, follow this procedure.

- 1. Verify that a valid project exists in the Workview Office Project Manager.

- 2. From the Workview Office Toolbar, click on the ViewDraw button, shown in the next figure. ViewDraw opens.

# **Opening an Existing Schematic**

Use the following steps to open an existing schematic.

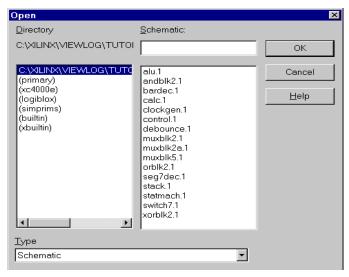

- To open an existing schematic, select File→Open in ViewDraw.

- Viewlogic allows a schematic to contain multiple sheets, saved as separate files to the project directory's sch directory. The extension of the file is the actual sheet number. For example, in a top-level schematic with two sheets, the sch directory contain *schematic*.1 and *schematic*.2 files.

- 2. To select the top-level schematic, select the primary library (or any other user-defined library) on the right side of the Open dialog box, shown in the following figure. You can either type the name directly in the Schematic field or click on the file in the design list box.

Figure 3-1 File Open Dialog Box

3. Click on **OK**. The selected schematic now appears.

## **Creating a New Schematic**

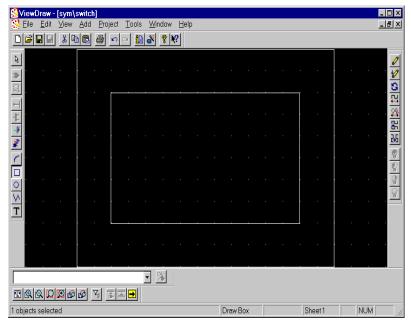

The following procedure demonstrates how to open and create schematics in ViewDraw.

- 1. Open a blank schematic window by clicking on File→New.

- 2. In the Name field, type in the name of the new schematic. Make sure that Schematic highlights in the Type field.

- 3. Click on OK. The blank schematic sheet now opens with the name of the new schematic at the top of the window, followed by a .1 extension.

### **Creating Schematics with Multiple Sheets**

When you create multiple-sheet designs, each sheet must have the same file name with extensions .1, .2, .3, and so forth. This convention applies to both top-level and lower-level schematics. The default sheet number is 1. To open a different sheet, type the schematic name and sheet number separated by a period in the Name field, or click on the file in the Designs list box. To view each sheet, use the Goto

Page icon from the View Toolbar or right mouse click and select GoTo Page.

### **Changing the ViewDraw Window Colors**

You can change the ViewDraw color settings to make it easier to view a schematic, choosing from a variety of available color schemes. In addition to these, Xilinx provides a special color scheme that provides optimal viewing of the Xilinx libraries in ViewDraw. If you want to change to this color palette, proceed with these steps.

- Select Project→Settings.

- 2. Click on the Color Palette tab.

- 3. Click the Import Scheme button.

- 4. In the Load Color Scheme dialog box that appears, navigate to the directory containing the Xilinx Development System, and then go to the viewlog\data subdirectory. Select the xilinx.scm file, and click Open.

- 5. Back in the Project Settings dialog box, the color scheme appears as Xilinx Library. Click on Apply to activate this new color palette. Click on OK to save the settings and close the Project Settings dialog box.

### **Changing ViewDraw Settings**

The Project Settings dialog box allows you to change various other aspects of the ViewDraw display and save these settings to the project's viewdraw.ini file.

- Select Project→Settings (if you closed it from the previous step).

- 2. Select any tab and make desired global changes.

- 3. To activate the new settings, click on Apply or OK. Apply keeps the Project Settings box open, OK closes it.

To find out the current settings of the key parameters without bringing up the dialog box, select Project—Status. ViewDraw opens a window displaying the settings.

Tools→Check Project gives an error stating that LogiBLOX symbols do not have an underlying schematic. You can ignore this

error safely, as an NGC netlist describing schematic functionality merges in later.

## **Obtaining Help**

You can obtain help about ViewDraw's commands and procedures by selecting commands on the Help menu or selecting the Help icon in the toolbar. In addition, the dialog boxes associated with some commands offer a Help button that you can click on to obtain context-sensitive help.

### Help from the Toolbar

To obtain help from the toolbar, follow these steps.

1. Click on the Help toolbar icon, shown in the following figure. Notice that your cursor now includes a question mark.

Select any icon or pull-down menu to get the information you need.

The ViewDraw Help screen appears showing the command you have selected. To go to the main ViewDraw Help window, select the Help Topics button.

#### Help from the Menu

To obtain help from the pull-down menu, select Help→ViewDraw Help Topics.

The main ViewDraw Help screen appears.

### **Help Topics**

From this main help window, you can search for help in three ways.

- Under the Contents tab, follow the books to chapters dealing with such topics as Getting Started, or Problem Solving.

- Under the Index tab, select a keyword from the list.

- Under the Find tab, enter a keyword from a complete list of keywords. Similar to the Index, this method takes longer to find information due to the greater number of keywords available.

# Working in ViewDraw

This section briefly discusses using mouse buttons, menus, keyboard commands, function keys, toolbar icons, and dialog boxes in View-Draw.

#### **Mouse Buttons**

Mouse buttons perform the following functions in ViewDraw.

- The left mouse button selects objects in ViewDraw. Use the Control key with the left mouse button to select multiple items.

- The right mouse button brings up a menu of common commands, like Properties, Add Component, Add Net, Delete, and Zoom. These commands refer to the selected items, or the schematic sheet itself if you selected nothing. The menu choices vary depending on the items selected.

#### **Menus**

ViewDraw offers eight menus. You can select menu commands with the mouse or the keyboard. With the mouse, click the left mouse button on the desired command. With the keyboard, press the Alt key and type the letter underlined in the command.

This document uses only the menu command in most situations. You can access most commands in a number of other ways, including keyboard hot keys or function keys, the command line, toolbar icons, and the right mouse button.

### **Keyboard Commands**

You can use a set of "hot keys" in place of the pull-down menu or the toolbar icon. The keyboard commands appear next to their equivalent command in the pull-down menus. For example, selecting File→Open displays the keyboard command Ctrl+O on the right side of the pull-down menu.

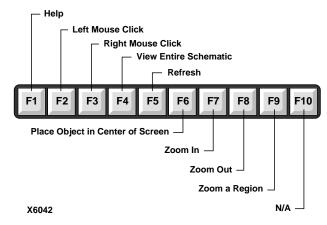

## **Function Keys**

You can use the function keys labeled F1, F2, F3, and so forth on your keyboard to invoke particular commands in the Workview Office tools. The next figure shows their assigned functions.

Figure 3-2 Function Keys

#### **Command Line**

You can enter certain commands via the command line, shown in the following figure. Open this toolbar from View—Command Line, and you can dock or float it like the other toolbars. To obtain the complete list of valid command line commands, select Help—ViewDraw Help Topics. Under the Index tab, select "Command Line Commands" and click on the Display button.

Figure 3-3 Command Line Toolbar

#### **Toolbar Icons**

Toolbar icons appear around the edges of ViewDraw. When you move the cursor over each icon, a description of its function appears in the status bar at the bottom of the ViewDraw screen. You can place these toolbars anywhere around the ViewDraw screen, or you can pull them off and leave them "floating." See the "Toolbar" figure, "View Toolbar" figure, "Object Toolbar" figure, and "Transform Toolbar" figure. You can turn them on or off from the View pull-down menu.

Figure 3-4 Toolbar

Figure 3-5 View Toolbar

Figure 3-6 Object Toolbar

Figure 3-7 Transform Toolbar

### **Dialog Boxes**

An ellipsis (...) following a ViewDraw menu command indicates that the command brings up a dialog box in which you can enter information and set options.

You can find the following common fields are common in many of the ViewDraw dialog boxes.

- OK closes the dialog box and implements the intended action according to the settings in the dialog box

- Cancel closes the dialog box without effecting any action

- Help gives you information about how to use the dialog box

## **Adding Components**

Follow these steps to place library components on your schematic.

To place a component on the schematic, select the Add→Component command or click on the Add Component toolbar icon, shown in the next illustration.

The Add Component dialog box appears, shown in the "Add Component Dialog Box" figure.

When you initially bring up the Add Component dialog box, ViewDraw displays the components found in the first library in the Directory field.

2. To view the available components in a library, select the library in the Directory list box.

The previous action updates the Components list box in the dialog box.

3. Using the down arrow in the scroll bar of the components list box, scroll down until you find the desired component.

**Note:** After selecting the components list box, you can jump to a component by typing the component's name.

4. Select the component.

Add Component Directory 5 1 <u>S</u>ymbol Close (xc4000e) and2.1 Help C:\XILINX\VIEWLOG\TUT acc16.1 • (primary) acc4.1 (xc4000e) acc8.1 (logiblox) add16.1 (simprims) a.dd4.1 (builtin) add8.1 (xbuiltin) adsu16.1 adsu4.1 adsu8.1 and2.1 and2b1.1 and2b2.1 and3.1 and3b1.1 and3b2.1

This highlights the component, updates the Symbol field, and an image of the component appears on the right.

Figure 3-8 Add Component Dialog Box

- 5. To place a component on the schematic, left click on the image of the component. Move the cursor into the schematic window and left click again to place the component.

- Make sure all user-defined blocks that you add to your design come from the Primary directory, not from the discrete path that describes your project directory. This ensures that each symbol in the design has a proper alias, reducing the risk of errors for programs like Altran that refer to these aliases.

- 6. Place as many components as desired, then click on the Close button to close the Add Component dialog box.

- Do not use Add—Component to select LogiBLOX components from the LogiBLOX library directly. The "Adding LogiBLOX Components" section describes how to add LogiBLOX modules to your design using the interactive LogiBLOX Module Selector.

## Adding LogiBLOX Components

This section describes how to add LogiBLOX components to your schematic design in ViewDraw. Refer to the *LogiBLOX Users Guide* for detailed information on creating modules with LogiBLOX.

Follow these steps to place a LogiBLOX component on your schematic.

Select the Tools→Add LogiBLOX command. If this command does not appear on the Tools menu, refer to the "Adding Logi-BLOX Custom Commands to ViewDraw" section of the "Getting Started" chapter.

**Note:** Powerview users choose Add—LogiBLOX to start LogiBLOX. If this command does not appear on the Add menu, refer to the "Configuring for Workview Office" section of the "Getting Started" chapter.

- When adding the first LogiBLOX component in a project, the LogiBLOX Setup dialog appears. Pay particular attention to the following two important settings for a ViewDraw schematic design.

- a) The Device Family setting must match the architecture library specified for this project (in the Project Manager or viewdraw.ini file).

- b) The Simulation Model setting (under the Options tab) must indicate the type of functional simulation model you want LogiBLOX to create, either behavioral VHDL or gatelevel EDIF. Refer to the "Choosing Between VHDL and EDIF Models" section of the "Getting Started" chapter for details.

Refer to the *LogiBLOX Users Guide* for information about the remaining LogiBLOX Setup options.

Click on OK to close the Setup dialog.

3. The LogiBLOX Module Selector dialog appears. Define the module type and parameters, and give the module a name.

**Note:** Because the corresponding ViewDraw symbol, also uses the module name, choose a name that conforms to the standard VIEW-logic naming restrictions.

- 4. Click on OK in the Module Selector dialog. This verifies module definition and generates a simulation model before the Module Selector disappears.

- LogiBLOX prepares the simulation model for use in the VIEWlogic environment (analyzing the VHDL model, or translating the EDIF model to WIR files).

- LogiBLOX generates a ViewDraw symbol and places the symbol on the current schematic sheet in move mode. You can then drop the LogiBLOX symbol in the proper location, as you would do with the Add—Component command.

The component created by LogiBLOX is represented by a symbol in your primary design directory. You can place this symbol on your schematic as many times as you like, either by copying the first instance, or by choosing the new symbol with the Add—Component command. If you want to change the definition of the LogiBLOX component, see the "Changing LogiBLOX Components" section.

# **Changing Components**

Rather than placing a new component, you can convert a placed component to another component. Use this method if you placed the wrong component and want to replace it with the correct component.

- Select the component(s) to change. If you select multiple items at on time, each of the instances changes to the one target component.

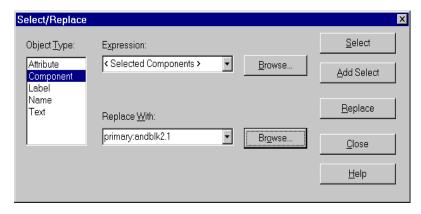

- Select the Edit→Replace command. The Find dialog box appears.

- In the Object Type box, select Component. The Expression window now shows "<Selected Components>."

- 4. Fill in the Replace With box with the component type you want. If you do not know the exact name of the component, click on <code>Browse...</code> to obtain the listing of all available components. This Replace With Component dialog box looks similar to the Add Component box, with one difference; after you select the component, click on <code>OK</code>. The Find Dialog Box appears as shown in the following figure.

Figure 3-9 Find Dialog Box

Click on Replace, then Close. This closes the Find dialog box and updates the schematic.

## **Changing LogiBLOX Components**

If you want to change the definition of a LogiBLOX component, follow these steps.

- 1. On your ViewDraw schematic, select the LogiBLOX component you want to modify. If more than one instance of this LogiBLOX component exists and you want to change them all, you can select any one of the instances.

- 2. Select the  $\mathtt{Tools} {\rightarrow} \mathtt{Change} \ \mathtt{LogibLox} \ \mathtt{command}.$

- Powerview Users choose Change→LogiBLOX.

- 3. The LogiBLOX Module Selector dialog appears with the selected module as the active one. Make the desired changes to the module definition.

- 4. If you want to overwrite the original module definition, you can simply click OK, without changing the module name. This action causes all instances of this module to change (including instances other than the selected one).

- Or, if you want to keep the original module definition, changing only the selected instance, enter a new module name before clicking OK. After the command completes, a new symbol replaces the selected symbol.

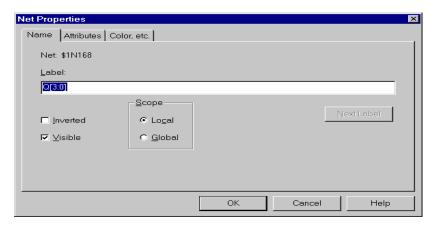

## **Adding Nets**

Nets and buses establish connectivity between pins on the same hierarchical level of a design. However, you do not need to physically connect nets on the schematic. If two dangling nets or buses in a single schematic share the same name, they are considered electrically connected. Labeling unconnected nets with the same name can make schematics easier to read, especially when dealing with common signals like clocks or resets. However, you must keep track of all signal names and make sure they match exactly.

**Note:** Net name association also applies to nets on different schematic sheets at the same level of hierarchy. For example, a net on design.1 named DATA0 connects electrically to another net on design.2 named DATA0.

Use the following procedure to add a net.

Select the Add→Net command. See the associated icon shown in the next figure.

- 2. Point the cursor at the point where the net starts, a point on a net, bus, or pin.

- Click and hold the left mouse button.

- 4. Click the right mouse button without releasing the left mouse button each time that you want the net to pivot.

- 5. Move the mouse to the desired end point of the net and release the left mouse button. Unlike the start point, you can place the end point somewhere other than on a net, bus, or pin.

## **Adding Buses**

You can draw a set of signals as a bus rather than as several separate wires. You do not have to connect a bus physically with the nets that make up the bus.

To add a bus, follow these steps.

Select the Add→Bus command. See the associated icon shown as follows.

- 2. Point the cursor at the point where the bus starts.

- 3. Click and hold the left mouse button to begin the bus.

- 4. Click the right mouse button without releasing the left mouse button each time that you want the bus to pivot.

- 5. Move the mouse to the desired end point of the bus and click the left mouse button. Unlike the start point, you can place the end point somewhere other than on a net, bus, or pin.

## **Creating Custom Macros**

A macro is any symbol defined by an underlying Viewlogic schematic. The Xilinx libraries contain several symbols that are macros. Macro schematics contain primitives and other macro symbols. When the software reads a schematic, it expands (flattens) the macro symbols into their underlying schematics. The components actually processed and reported by the software are the underlying primitives, referenced by their hierarchical instance names, after macro expansion.

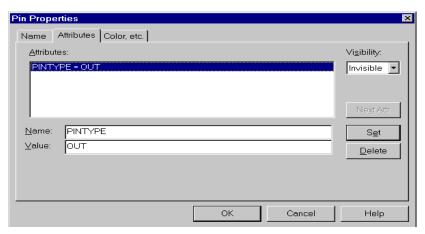

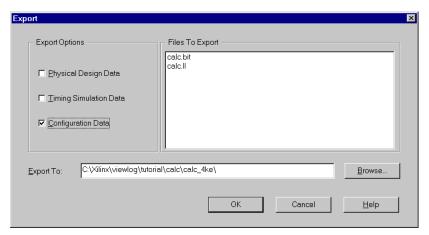

You can create your own custom macro symbols to use in your designs. The procedure for creating a custom macro is the same for CPLDs and FPGAs. You can create and store your custom macro symbols and their underlying schematics in your local project directory, or you can create a custom library directory to store your custom macros for use in multiple projects. See the "Design and Simulation Techniques" chapter for instructions on creating a custom library.