# CPLD Synthesis Design Guide

Getting Started with Synopsys for CPLDs

Designing with CPLDs

Compiling and Fitting a CPLD Design

Simulating your Design

**Library Component Specifications**

**Attributes**

Fitter Command and Option Summary

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A. Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CORE Generator, CoreGenerator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Foundation, HardWire, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, Select-RAM, Select-RAM+, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaBlock, VersaRing, Virtex, WebLINX, XABEL, XACTstep, XACTstep Advanced, XACTstep Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5.550.839: 5.550.843; 5.552,722; 5.553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479;

5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-1999 Xilinx, Inc. All Rights Reserved.

# **About This Manual**

This manual has been created to provide guidance in use of Synthesis Design for XC9500, XC9500XL, and XC9500XV CPLDs in the workstation environment. Practical examples in this manual apply to the Synopsys compiler and simulator.

# **Additional Resources**

For additional information, go to http://support.xilinx.com. Use the search function at the top of the support.xilinx.com page or click links that take you directly to online resources.

The following table provides information on tutorials and some of the resources you can access using the support.xilinx.com advanced Answers Search function.

| Resource            | Description/URL                                                                                                                                                                                                                                                 |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorial            | Tutorials covering Xilinx design flows, from design entry to verification and debugging http://support.xilinx.com/support/techsup/tutorials/index.htm                                                                                                           |

| Answers<br>Database | Current listing of solution records for the Xilinx software tools<br>Search this database using the search function at<br>http://support.xilinx.com/support/searchtd.htm                                                                                        |

| Application Notes   | Descriptions of device-specific design techniques and approaches http://support.xilinx.com/apps/appsweb.htm                                                                                                                                                     |

| Data Book           | Pages from <i>The Programmable Logic Data Book</i> , which describe device-specific information on Xilinx device characteristics, including readback, boundary scan, configuration, length count, and debugging http://support.xilinx.com/partinfo/databook.htm |

| Resource       | Description/URL                                                                                                                               |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Xcell Journals | Quarterly journals for Xilinx programmable logic users http://support.xilinx.com/xcell/xcell.htm                                              |

| Tech Tips      | Latest news, design tips, and patch information on the Xilinx design environment http://support.xilinx.com/support/techsup/journals/index.htm |

### **Manual Contents**

This manual covers the following topics.

- "Getting Started with Synopsys for CPLDs" chapter. This

chapter shows you how to prepare your setup files and verify

your installation. It also provides a design walk-through as an

overview of the basic steps for implementing Xilinx XC9000

CPLD designs using Synopsys.

- "Designing with CPLDs" chapter. This chapter discusses how to use design techniques, library cells and cpld command parameters to get the best performance from Xilinx XC9000 CPLDs.

- "Compiling and Fitting a CPLD Design" chapter. This chapter describes how to compile your design using the Synopsys Design Compiler shell (DC Shell).

- "Simulating Your Design" chapter. The Xilinx CPLD Synopsys

Interface supports both functional and timing simulation of

VHDL designs using the VSS simulator. This chapter shows you

how to prepare designs for simulation and how to use a test

bench.

- "Library Component Specifications" appendix lists library components used in CPLD designs.

- "Attributes" appendix lists attributes used in CPLD designs.

- "Fitter Command and Option Summary" appendix lists fitter options entered from the Design Manager, and lists fitter options entered on the cpld command line.

### **Conventions**

This manual uses the following typographical and online document conventions. An example illustrates each typographical convention.

# **Typographical**

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

```

speed grade: -100

```

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

```

rpt_del_net=

```

Courier bold also indicates commands that you select from a menu.

```

\mathtt{File} \to \mathtt{Open}

```

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

edif2ngd design\_name

· References to other manuals

See the *Development System Reference Guide* for more information.

Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

• Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on|off}

```

• A vertical bar " | " separates items in a list of choices.

```

lowpwr ={on|off}

```

A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

```

• A horizontal ellipsis "..." indicates that an item can be repeated one or more times.

```

allow block block_name loc1 loc2 . . . locn;

```

### **Online Document**

The following conventions are used for online documents.

- Red-underlined text indicates an interbook link, which is a crossreference to another book. Click the red-underlined text to open the specified cross-reference.

- Blue-underlined text indicates an intrabook link, which is a cross-reference within a book. Click the blue-underlined text to open the specified cross-reference.

# **Chapter 1**

# **Getting Started with Synopsys for CPLDs**

This chapter shows you how to prepare your Synopsys setup files and verify your installation. It also provides a design walk-through as an overview of the basic steps for implementing Xilinx XC9000/XL/XV CPLD designs using Synopsys. This chapter contains the following sections:

- "Workstation Environment"

- "Creating Synopsys Setup Files (Workstation)"

- "Analyzing the DesignWare and Simulation Libraries"

- "Verifying Your Installation (Workstation)"

- "Xilinx CPLD Design Flow"

- · "Design Example"

The remaining chapters in this manual provide additional detailed information on each step.

The design walk-through assumes that you have installed and configured the Xilinx software and libraries. For installation instructions, see the Release Document.

# **Workstation Environment**

Before running any software, you must make sure that your workstation environment is set up properly. The following are required to process Xilinx designs using the Synopsys interface:

1. Set the Xilinx environment variable to the Xilinx installation directory:

setenv XILINX xilinx\_path

2. Set the Synopsys environment variable to the Synopsys software directory:

```

setenv SYNOPSYS synopsys path

```

Add the following Xilinx executable directory to your path (in addition to all executable directories required by Synopsys software):

```

set path=( \

$XILINX/bin/platform \

$path)

```

where platform is sol (for Solaris) or hp (for Hewlett-Packard).

**Note:** In UNIX and DC Shell commands shown in this book, where text is too long to print on one line, the back-slash (\) character at the end of a line is used to indicate a continuation line. In actual usage, continuation line breaks are optional and may occur at any legal point in the command line.

# **Creating Synopsys Setup Files (Workstation)**

After you have installed the Xilinx software you must configure the Synopsys Design Compiler and VSS simulator setup files to access the XC9000 libraries. This section shows you how to configure the setup files and verify that your setup is working properly.

The setup files are typically located in each design directory where Xilinx CPLD designs are processed.

**Note:** You will find a sample setup file in \$XILINX/synopsys/examples/template.synopsys\_dc.setup\_9k. You can copy this file to your design directory and change the file name to .synopsys\_dc.setup.

### The Design Compiler Setup File

For XC9000 designs, your Design Compiler setup file (.synopsys\_dc.setup) must contain the following lines:

```

search path = { . \

Xilinx_path/synopsys/libraries/syn \

Synopsys_path/libraries/syn}

```

```

link_library = {xc9000.db}

target_library = {xc9000.db}

symbol_library = {xc9000.sdb}

compile_fix_multiple_port_nets = true

bus_naming_style = "%s<%d>"

bus_dimension_seperator_style = "><"

bus_inference_style = "%s<%d>"

edifout_netlist_only = true

edifout_write_properties_list= {INIT LOC PWR_MODE}

edifout_power_and_ground_representation = cell

edifout_mo_array = true

edifout_ground_name=GND

edifout_ground_pin_name=GROUND

edifout_power_name=VCC

edifout_power_pin_name=VCC

```

Where *Xilinx\_path* is the actual directory path where your Xilinx software is installed, and *Synopsys\_path* is the actual path where your Synopsys software is installed.

**Note:** You cannot use UNIX environment variables directly in the .synopsys\_dc.setup file, but you may use the dc\_shell variables, as shown in the template files.

# The VSS Simulator Setup File

For XC9000 designs, your VSS Simulator setup file, .synopsys\_vss.setup, must contain the following lines:

```

SIMPRIM: $XILINX/synopsys/libraries/sim/lib/simprims

TIMEBASE = NS

TIME RES FACTOR = 0.1

```

**Note:** You may use either the \$XILINX environment variable or the actual path specification in the .synopsys\_vss.setup file.

# **Analyzing the DesignWare and Simulation Libraries**

The Xilinx Synopsys Interface (XSI) provides simulation libraries supporting VSS. If you use VSS, you need to analyze the VHDL simulation models after you install the Xilinx Synopsys Interface and before you simulate your first Xilinx design. You must repeat these steps each time you install an update to your Synopsys software.

To analyze the VSS model files for Xilinx simulation, change your current directory to the simulation library source directory for the Xilinx SIMPRIMS library and run the analyze.csh script as follows:

```

cd $XILINX/synopsys/libraries/sim/src/simprims

./analyze.csh

```

The previous command analyzes the encrypted models for the SIMPRIMS library and places the output files into the \$XILINX/synopsys/libraries/sim/lib/simprims directory.

**Note:** The analyze.csh script attempts to create optimized models by using your system's C-compiler. If the vhdlan commands in the script encounter any difficulty accessing a C-compiler on your system, they will proceed by creating non-optimized models. The script may produce numerous warnings about this, but should complete successfully. The non-optimized models will produce the same results, but simulation run-time is typically longer.

# **Verifying Your Installation (Workstation)**

Before attempting to compile and fit a design, it is a good idea to verify that you have access to the installed software. A simple verification process is described below.

# **Verifying Synopsys Software Access**

To verify that your system is correctly configured to access the Synopsys software, enter the following UNIX commands:

```

which dc_shell

which vhdlan (if you are using the VSS simulator)

```

If you get a negative response for either command, (such as "no vhdlan in ...") this means that either the Synopsys software is not installed properly or that your system path is not set properly to include the Synopsys software directories. Refer to the Synopsys documentation for installation instructions.

### Verifying Xilinx Software Access

To verify that your system is correctly configured to access the Xilinx-supplied software, enter the following UNIX commands:

#### 1. which cpld

If **cpld** cannot be found, the Xilinx software is not installed or is not in your path.

#### 2. echo \$XILINX

This variable should also point to the Xilinx directory found in Step 1.

As a final verification that your Xilinx Synopsys interface is ready to use, we have provided a complete design example for you to run, which is described later in this chapter. To quickly verify Synopsys compilation, copy the sample design as described in step 1 and run scan.script as described in step 9.

# Xilinx CPLD Design Flow

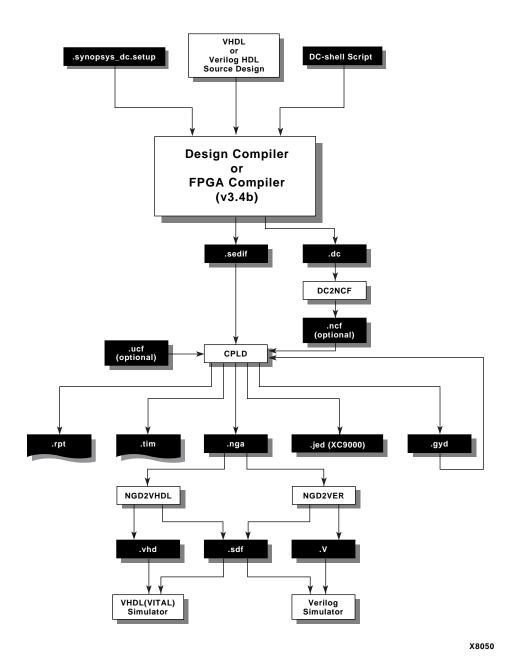

"Basic CPLD Design Flow" figure shows the basic design flow for creating CPLD designs. Each step is described in the following design example.

Figure 1-1 Basic CPLD Design Flow

# **Design Example**

The following design example is used to demonstrate the basic CPLD design flow. This design implements a counter with variable start and stop values which are loaded into registers from a data input bus. When the START input is asserted, the start value is loaded into the counter and the counter outputs are enabled. The counter outputs increment on each clock cycle until the counter value matches the stop value. The counter outputs are disabled on the next clock cycle. The design can be implemented in a Xilinx XC95108-7PC84 device.

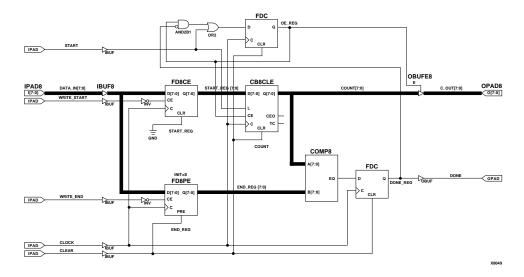

To help you understand the design, an equivalent schematic is shown in the "Schematic Representation - SCAN Design" figure.

Figure 1-2 Schematic Representation - SCAN Design

Both a VHDL and a Verilog HDL version of this design are provided with the software as an example.

The VHDL source file (scan.vhd) for the scan example design is shown below.

-----

```

-- Xilinx CPLD Synopsys VHDL Tutorial Design

-- File:

scan.vhd

-- Target Device: XC9536-5PC44

-- Author: Xilinx Corporation

Copyright (C) Xilinx Corporation

1994

All rights reserved

Requirements: Xilinx XACT Version

М1

(Alliance core and Synopsys

interface)

Synopsys: Design Compiler or FPGA

Compiler

v3.4b or later

_____

-- Standard library configuration --

Library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

entity scan is

port (CLOCK, CLEAR, START, WRITE_START, WRITE_END

: in std_logic;

DATA_IN : in std_logic_vector (7 downto 0);

C_OUT : out std_logic_vector (7 downto 0);

DONE : out std_logic);

end scan;

architecture behavioral of scan is

signal START_REG : std_logic_vector (7 downto 0);

signal END_REG : std_logic_vector (7 downto 0) :=

"11111111";

```

```

signal COUNT : std_logic_vector (7 downto 0) :=

"00000000";

signal OE_REG, DONE_REG : std_logic := '0';

-- Initial states used by behavioral simulation only.

begin

-- Starting value register.

process (CLOCK)

begin

if (CLOCK'event and CLOCK='1') then

if (WRITE_START = '0') then

START_REG <= DATA_IN;

end if;

end if;

end process;

Ending value register with asynchronous preload.

process (CLEAR, CLOCK)

begin

if (CLEAR = '1') then

END_REG <= "11111111";</pre>

elsif (CLOCK'event and CLOCK='1') then

if (WRITE_END = '0') then

END_REG <= DATA_IN;</pre>

end if;

end if;

end process;

-- DONE flag and OE-control registers with

asynchronous clear.

process (CLEAR, CLOCK)

begin

```

```

if (CLEAR = '1') then

DONE_REG <= '0';

OE_REG <= '0';

elsif (CLOCK'event and CLOCK='1') then

Registered equality comparator:

if (COUNT = END_REG) then

DONE_REG <= '1';</pre>

else

DONE_REG <= '0';

end if;

OE-control register:

if (START = '1') then

OE_REG <= '1';

elsif (DONE_REG = '1') then

OE_REG <= '0';

end if;

end if;

end process;

-- Counter with asynchronous clear and parallel load.

process (CLEAR, CLOCK)

begin

if (CLEAR = '1') then

COUNT <= "00000000";

elsif (CLOCK'event and CLOCK='1') then

if (START = '1') then

COUNT <= START_REG;

elsif (OE_REG = '1') then

COUNT <= COUNT + 1;

```

```

end if;

end if;

end process;

-- Three-state counter outputs.

C_OUT <= COUNT when (OE_REG = '1')

else "ZZZZZZZZZ";

DONE <= DONE_REG;

end behavioral;</pre>

```

### **Design Entry**

Typically you will enter your design in Synopsys VHDL/HDL form by using a text editor. However, all required source, setup, and test bench files for this design example have already been entered for you. The VHDL design files are contained in the \$XILINX/synopsys/tutorial/cpld/vhdl directory, and the Verilog HDL design files are in \$XILINX/synopsys/tutorial/cpld/verilog.

#### Step1 - Create a Design Directory

Create a local copy of the scan tutorial directory as follows:

- Change your current working directory to a local, writable location in which you will place the scan working directory.

- Copy the entire VHDL or Verilog directory tree from the installed tutorial area into your current directory, for example:

```

cp -r $XILINX/synopsys/tutorial/cpld/vhdl .

or

cp -r $XILINX/synopsys/tutorial/cpld/verilog .

```

Change your current directory to the new working directory as follows:

```

cd vhdl

or

cd verilog

```

If you need more information on design entry see the Synopsys Design Compiler manuals.

#### **Functional Simulation**

Functional simulation verifies the logic of your design. This will save you time by catching logic errors early in the development cycle. This section describes the simulation flow for the VHDL System Simulator (VSS). If you are not using VSS, skip this section and continue with step 9.

You must analyze your source design file and test bench before simulation.

#### Step 2 - Analyze Your Design

Analyze the scan design by entering the following Synopsys command on the UNIX command line:

```

vhdlan scan.vhd

```

You will see the analyzer version number and a copyright notice. If the analysis works properly you will be returned to the UNIX prompt with no error messages displayed.

#### Step 3 - Analyze Your Test Bench

For this example a test bench is provided (scan\_tb.vhd). At the end of this file, a configuration named CFG\_SCAN\_TB is declared.

Analyze the test bench for scan by entering the following Synopsys command on the UNIX command line:

```

vhdlan scan tb.vhd

```

Again, you will see the analyzer version number and a copyright notice. If the analysis works properly you will be returned to the UNIX prompt with no error messages displayed.

The test bench for the scan design example (scan\_tb.vhd) is shown below:

```

-- Xilinx CPLD Synopsys VHDL Tutorial Design Test

Bench

-- File: scan tb.vhd

```

```

-- Target Device: XC9536-5PC44

-- Author: Xilinx Corporation

Copyright (C) Xilinx Corporation

1994

All rights reserved

-- Requirements: Xilinx XACT Version M1

(Alliance core and Synopsys

interface)

Synopsys: VSS simulator v3.4b-vital

or later

library IEEE;

use IEEE.std_logic_1164.all;

use STD.Textio.all;

entity scan_tb is

end scan_tb;

architecture test of scan_tb is

constant tCW : time := 25 ns;

component scan

port (CLOCK, CLEAR, START, WRITE_START,

WRITE_END: in std_logic;

DATA_IN: in std_logic_vector (7 downto 0);

C_OUT: out std_logic_vector (7 downto 0);

DONE: out std_logic);

end component;

```

```

signal CLOCK, CLEAR, START, WRITE_START, WRITE_END:

std_logic;

signal DATA_IN: std_logic_vector (7 downto 0);

signal C_OUT: std_logic_vector (7 downto 0);

signal DONE: std_logic;

begin

UUT: scan

port map (CLOCK, CLEAR, START, WRITE_START,

WRITE_END,

DATA_IN, C_OUT, DONE);

DRIVER: process

begin

CLOCK <= '0';

CLEAR <= '1';

START <= '0';

WRITE_START <= '1';</pre>

WRITE_END <= '1';</pre>

DATA_IN <= "00000000";

wait for 200 ns;

CLEAR <= '0';

wait for tCW;

CLOCK <= '1';

wait for tCW;

CLOCK <= '0';

DATA_IN <= "01111101";

WRITE_START <= '0';

wait for tCW;

```

```

CLOCK <= '1';

wait for tCW;

CLOCK <= '0';

DATA_IN <= "10000001";

WRITE_START <= '1';</pre>

WRITE_END <= '0';</pre>

wait for tCW;

CLOCK <= '1';

wait for tCW;

CLOCK <= '0';

DATA_IN <= "00000000";

WRITE_END <= '1';</pre>

START <= '1';

wait for tCW;

CLOCK <= '1';

wait for tCW;

for I in 1 to 6 loop

CLOCK <= '0';

START <= '0';

wait for tCW;

CLOCK <= '1';

wait for tCW;

end loop;

CLOCK <= '0';

START <= '1';

wait for tCW;

CLOCK <= '1';

```

```

wait for tCW;

CLOCK <= '0';

START <= '0';

wait for tCW;

CLOCK <= '1';

wait for tCW;

CLOCK <= '0';

CLEAR <= '1';

wait for tCW;

CLOCK <= '1';

wait for tCW;

CLOCK <= '0';

CLEAR <= '0';

wait for tCW;

wait;

end process;

end test;

configuration CFG_SCAN_TB of scan_tb is

for test

end for;

end CFG_SCAN_TB;

```

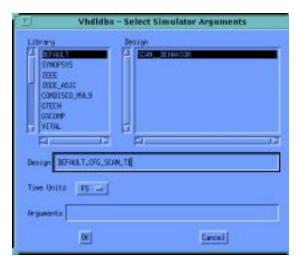

### Step 4 - Invoke the Simulator

Invoke the simulator by entering the following Synopsys command on the UNIX command line:

```

vhdldbx &

```

You will see the following window for selecting the analyzed configurations:

Figure 1-3 VHDLDBX Window

#### Step 5 - Select the Design

Select CFG\_SCAN\_TB from the menu. This brings up the Synopsys VHDL Debugger window.

#### Step 6 - Trace Signals

Click in the lower section of the Synopsys VHDL Debugger window and enter the following command:

```

trace *'signal

```

This command selects all signals at the test bench level for display and brings up the Dynamic Waveform Viewer (Waves).

#### Step 7 - Run the Simulation

Click the **RUN** button in the Debugger window to run the simulation waveform specified in the test bench. A trace display appears.

#### Step 8 - Return to UNIX

Return to the UNIX environment by selecting EXECUTE-QUIT from the VHDL Debugger menu.

If you need more information on functional simulation see the "Simulating Your Design" chapter.

### Synthesizing Your Design (Compiling)

Synthesizing your design converts the VHDL or Verilog HDL source text into a netlist that is composed of logic primitives. The netlist is in a form that can be read by the Xilinx fitter.

**Note:** This design example demonstrates the compilation flow using dc\_shell commands. You could instead use the Synopsys Design Analyzer GUI, but this is not shown in this book.

#### Step 9 - Enter the DC Shell Environment

Enter the Synopsys DC Shell environment by entering the following Synopsys command on the UNIX command line:

```

dc_shell

```

You will see the DC Shell license information and command-line prompt. Verify that the software version is v3.1 or newer.

**Note:** The commands required to compile the scan design example are shown in the following steps 10 through 16. These commands are also contained in compiler script files. The appropriate commands for either the Design Compiler orthe FPGA Compiler are contained in scan.script which you can run by entering the following Synopsys command:

```

include scan.script

```

If you choose to use these compiler scripts, go to step 17 when compilation is complete.

Unless otherwise specified, the commands in steps 10-16 are the same for both FPGA Compiler and Design Compiler. Unless otherwise specified, these commands are the same for either the VHDL or Verilog HDL version of the scan design.

#### Step 10 - Analyze Your Source Design

Read and analyze your VHDL source design file by entering the following Synopsys command:

```

analyze -format vhdl scan.vhd

```

For Verilog HDL source design, enter the following command:

```

analyze -format verilog scan.v

```

The warning messages you may see during this step are normal. The VHDL source file contains initial signal values that are used only for functional simulation and these values are ignored during synthesis. Actual register initial states are set using attributes as shown in step 13.

#### Step 11 - Elaborate Your Design

To build the design based on your analyzed VHDL file, entering the following Synopsys command:

```

elaborate scan

```

This command displays each register and 3-state buffer encountered in your design.

#### Step 12 - Synthesize Your Design

To synthesize an implementation of your design based on cells in the XC9000 technology library enter the following Synopsys command:

```

compile -map_effort low

```

The mapping effort is set to LOW to save compilation time because the synthesizer does not perform any speed or area optimization for CPLD designs; optimization is performed by the CPLD fitter.

#### Step 13 - Specify Initial Register States

In this design we want the counter, the OE\_REG and DONE flip-flop to be initialized to zero. We also want the END\_REG register to initialize to all ones to prevent the comparator from detecting a false DONE condition. The initial states of the remaining flip-flops are not critical for this design.

By default, all registers in an XC9500 or XC9500XL devices are initialized to zero when powered up, so we need not specify any dc\_shell directives for the counter, OE\_REG or DONE. To specify the all-ones initial state of the END\_REG register, enter the following Synopsys command:

set\_attribute END\_REG\* init S -type string

**Note:** The init attribute may be attached to either the flip-flop cells or their output nets in the design.

#### **Step 14 - Specify Timing Constraints**

We want to constrain clock period for this design to be no more than 12 ns. Enter the following Synopsys timing constraint:

```

create_clock CLOCK -period 12

```

#### Step 15 - Use a Global Clock Input Port

We want the CLOCK input for this design to be assigned to one of the global clock input pins (GCLK) of the device. Normally, the CPLD fitter would do this automatically whenever possible. To explicitly assign a global clock, enter the following Synopsys shell command:

```

set_pad_type -exact BUFG CLOCK

```

#### Step 16 - Place I/O Buffer Cells

To place I/O buffer cells on all top-level ports in the design, enter the following Synopsys commands:

```

set_port_is_pad "*"

insert_pads

```

#### **Step 17 - Flatten the Design**

Any hierarchy in the design must be flattened before attributes can be written into the netlist. Enter the following Synopsys shell command to flatten the design:

```

ungroup -all -flatten

```

#### Step 18 - Output the Netlist

The design database is now complete and ready to be output in netlist form.

Write an EDIF-formatted netlist by entering the following Synopsys command:

```

write -format edif -output scan.sedif

```

#### **Step 19 - Output Timing Constraints**

The timing constraint entered in step 14 is written into a separate DC\_shell script file which is later read by the Xilinx implementation software. Enter the following Synopsys shell command to write the timing constraint file:

write\_script > scan.dc

#### Step 20 - Exit DC Shell

Exit DC Shell by entering the following Synopsys command:

exit

You are returned to the UNIX prompt.

#### **Step 21 - Translate Timing Constraints File**

The DC\_shell script file containing your timing constraints written in Step 19 must be translated into a Xilinx constraint file, scan.ncf. At the Unix prompt, enter the following command to run the translator:

dc2ncf scan.dc

If you need more information on compiling your design, see the "Compiling Your Design" chapter.

The synthesizer creates a gate-level design with no physical device information; the physical layout of the device is done in the fitter step. No speed or area estimates are provided by the XC9000 synthesis library. Therefore do not attempt to create a timing report or perform estimated timing simulation at this time.

# **Fitting Your Design**

The CPLD fitter translates your logical design file (scan.sedif) into a physical device layout, and performs all device-specific logic optimization.

**Note:** This design example demonstrates the fitter flow using cpld command-line entry. You could instead use the Xilinx Design Manager GUI to process your design. This is explained in chapters 2 and 3 of this guide.

#### Step 22 - Fit Your Design

To fit your design into an XC9000 device, enter the following on the UNIX command line:

```

cpld scan

```

To fit the design into an XC9500XL device, enter the following command:

```

cpld -p 9500xl scan

```

The fitter displays a series of progress messages and a resource summary that shows how well your design fits into the target device.

When the fitter is finished, and assuming there are no errors, you need only to examine the fitter report file, scan.rpt. If you wish, you can also examine the static timing report file, scan.tim.

If you need more information on fitting, see the "Fitting Your Design" chapter.

### **Timing Simulation**

Timing simulation uses the actual device delays based on the physical layout of your design after fitting.

#### Step 23 - Prepare A Timing Simulation File

The cpld command produces a timing simulation database file (scan.nga) each time the design is successfully implemented. To translate the .nga file for simulation using VSS or other VITAL simulator, enter the following command at the UNIX prompt:

```

ngd2vhdl -w scan scan_time

```

The ngd2vhd1 command produces a VITAL-compliant structural VHDL file (scan\_time.vhd) and an SDF-formatted timing back-annotation file (scan\_time.sdf).

To translate the .nga file for simulation using a Verilog simulator, enter the following command:

```

ngd2ver -w scan scan_time

```

The ngd2ver command produces a structural Verilog file (scan\_time.v) and an SDF-formatted timing book annotation file (scan\_time.sdf).

**Note:** The remainder of this tutorial describes the procedure for performing timing simulation using the VSS simulator. If you are not using the VSS simulator, skip the remainder of this tutorial.

#### Step 24 - Analyze Your Implemented Design

Analyze the implemented design produced by the Xilinx ngd2vhd1 command by entering the following Synopsys command on the UNIX command line:

```

vhdlan scan_time.vhd

```

You will see the analyzer version number and a copyright notice. If the analysis works properly you will be returned to the UNIX prompt with no error messages displayed.

#### Step 25 - Analyze Your Test Bench

Analyze the simulation test bench by entering the following Synopsys command on the UNIX command line:

```

vhdlan scan_tb.vhd

```

Again, you will see the analyzer version number and a copyright notice. If the analysis works properly you will be returned to the UNIX prompt with no error messages displayed.

#### Step 26 - Invoke the VSS Simulator

Invoke the Synopsys VSS simulator by entering the following Synopsys command on the UNIX command line:

```

vhdldbx -sdf_top \

/SCAN_TB/UUT -sdf scan_time.sdf CFG_SCAN_TB &

```

This will open the simulator window. The <code>-sdf</code> parameter specifies the timing back-annotation file produced by <code>ngd2vhd1</code>. The <code>-sdf\_top</code> parameter specifies the level in the test bench hierarchy at which the back annotation information will be applied, which is the "UUT" instance of the scan test bench.

#### Step 27 - Open the Waveform Viewer

Use the **TRACE** command to specify the same signals used during functional simulation in step 6. Enter the following command on the VHDL Debugger command line:

trace \*'signal

This opens the Dynamic Waveform Viewer window.

### Step 28 - Run the Simulation

Run the simulation by clicking the RUN button in the lower section of the Synopsys VHDL Debugger window.

This will run the timing simulation test bench and display the simulation trace of your design.

#### Step 29 - Return to UNIX

Return to the UNIX environment by selecting **EXECUTE-QUIT** from the simulator menu.

If you need more information on timing simulation, see the "Simulating Your Design" chapter.

# **Chapter 2**

# **Designing with CPLDs**

This chapter discusses how to control various device features and get the best performance from Xilinx XC9500, XC9500XL, and XC9500XV CPLDs. You can control aspects of design implementation at these points:

- in your VHDL or Verilog HDL source design

- using dc\_shell commands or Design Analyzer commands

- · using FPGA Express implementation options

- using cpld command-line parameters or the Xilinx Design Manager templates

For more information on synthesis library cells, see the "Library Component Specifications" appendix. For more information on attributes, see the "Attributes" appendix. For more information on CPLD commands, see chapter 3, *Compiling and Fitting your Designs*.

This chapter describes how you can control the aspects of design implementation. It contains the following sections:

- "Target Device Selection"

- "Special I/O Ports"

- "Controlling Register Initial State"

- "Controlling Power Consumption"

- "Controlling Output Slew Rate"

- "Controlling the Pinout"

- "Controlling Logic Optimization"

- "Controlling Timing Paths"

- "XC9500 Local Feedback"

# **Target Device Selection**

You must always select a target family, such as XC9500 or XC9500XL. By default, the fitter will automatically select a device within that family for you, choosing, in general, the smallest part that will satisfy the needs and constraints of your design. Otherwise, you can select a specific device, package, speed, or any valid combination.

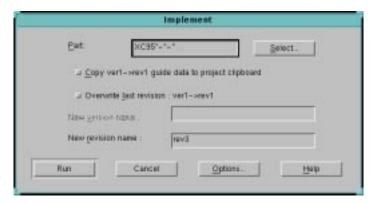

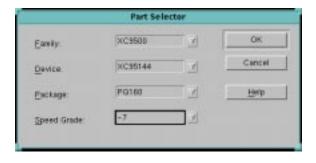

# **Selecting a Part from the Design Manager**

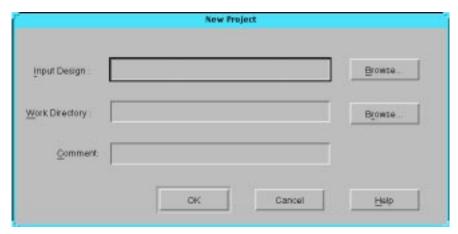

You can select the target device family and, optionally, a specific device, package and speed from the Design Manager. To bring up the Design Implementation Dialog Box select:

$extsf{Design}

ightarrow extsf{Implement}$

Figure 2-1 Design Implementation Dialog Box

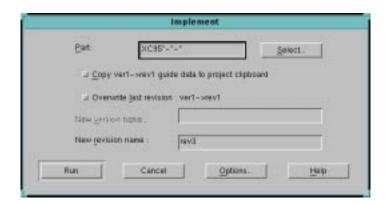

Click once on the Select button to get the Part Selector Dialog Box.

Figure 2-2 Part Selector

The part selector allows you to select from CPLD families, devices, packages and speed grades.

#### Family

This option allows you to select from a list of Xilinx families. Click once on the down arrow adjacent to this option box to display available families. If you select the XC9500 family, the device, package and speed boxes will all be set to All. Once you have selected a family you can select a device from within that family, or you can leave any or all of the remaining boxes set to All.

#### Device

This option allows you to select a specific CPLD device from the family selected on line one. Click once on the down arrow adjacent to this option box to list the devices for the Family selected above. Once you have selected a device, only packages and speed grades available for that device will appear in the Package and Speed Grade option lines below.

If you are only interested in selecting the fastest device available, leave this option on All and select the Speed Grade only.

#### Package

This line allows you to select from available packages. If you have already selected a device, the option line will only display packages that are available for that device.

#### Speed Grade

This option allows you to select from available speed grades. If you have already select a device from the <code>Device</code> option box, only the speed grades available for that device will be displayed when you click on the down arrow. However, if speed is your primary consideration, leave the <code>Device</code> option box on <code>All</code> and select your <code>Speed</code> <code>Grade</code> only. If you select a speed grade and then try to select a device which does not support that speed <code>grade</code>, the <code>Speed</code> <code>Grade</code> option box will revert to <code>All</code>.

#### Command Line Device Selection

You can optionally specify a target device on the cpld command line when you run the fitter. The format of the part-type parameter on the cpld command line is:

cpld -p part\_type design\_name

where

-p part\_type — specifies the target device type or set of devices from which to choose (default is automatic device selection from the XC9500 family); where part\_type can be:

9500 = any XC9500 family device (auto selection)

9500xl = any XC9500XL family device (auto selection)

9500xv = any XC9500XV family device (auto selection)

"95ddd[xl][-ss][-pppp]" — where 95ddd is the device code (such as 95108), ss is the speed grade, pppp is the package code (such as PQ160), and an asterisk (\*) can be used as a wildcard string (quotes required around part\_type when asterisk is used).

You may specify either a unique device code, a range of eligible devices or an entire CPLD family from which the fitter will automatically choose. The fitter will, in general, automatically select the smallest device and package that will fit the design, and the fastest speed grade of the resulting device.

To specify a range of devices, you can use an asterisk (\*) as a wildcard character. You may also specify an enumerated list of devices, separated by commas. If you use the asterisk character or an enumerated list in the cpld command, you must enclose the parameter string in quotes. If you use an asterisk in the part code field, your string must begin with a "9" (for XC9500). If you want to select from the XC9500XL family, the letters "XL" must appear in the part string; if you want to select from the XC9500XV family, the letters "XV" must appear in the part string; otherwise the fitter selects only from the XC9500 family. If you use a comma-separated list, all devices must be from the same CPLD family (either all XC9500, all XC9500XL, or all XC9500XV, but not mixed). For example, the following are valid parttype parameter specifications:

```

cpld -p 95108-10-PC84 design1

cpld -p "95108-*-PC84" design1

cpld -p "95**XL-*-PX84" design1

cpld -p "95108-10-PC84,95108-7-PQ*" design1

```

If you leave the speed grade unspecified, the fitter will always choose the fastest available speed grade for the selected device.

Refer to the Release Document for a list of CPLD device codes supported by the current version of the fitter software.

# Special I/O Ports

Ordinarily, you need only to declare ports in your top-level entity to represent all the I/O pins on the CPLD device. The Synopsys set\_port\_is\_pad and insert\_pads commands automatically infer IBUF, OBUF, OBUFE and IOBUFE cells from XC9000 library to represent the I/O ports in the netlist.

The following sections describe special global control pins on CPLD devices that can be used for register clocking, tristate control and register set/reset, instead of ordinary IBUF inputs. Unless otherwise specified, the fitter automatically allocates these special global pins, if possible, when input ports in your design are used to perform these control functions.

# **Clock Inputs**

To use a device input as a clock source, you can simply refer to a toplevel input port as the clock condition in a process. For example:

```

entity xyz is

port (CLOCK:in std_logic; ...

...

process (CLOCK)

begin

if (CLOCK'event and CLOCK='1') then

```

The fitter automatically uses one of the global clock pins (GCK for XC9000) whenever possible.

For XC9000 devices, a global clock input signal may perform negative-edge clocking. For example:

```

process (CLOCK)

begin

if (CLOCK'event and CLOCK='0') then

```

The same clock input may even be used both as both positive-edged and negative-edged to clock different processes on opposite edges of the clock signal. Global clock inputs may also be used as ordinary input signals to other logic elsewhere in the design.

If an input port signal passes through any logic function (other than an inverter) before it is used as a clock by any flip-flop, the input will not be routed to any flip-flops in the design using the global clock path. Instead, that clock signal will be routed through the logic array.

There are a limited number of global clock pins on each CPLD device (consult the device data sheet). If you need to explicitly control the use of global clock pins, you can specify the set\_pad\_type command in your dc\_shell script with the parameter "-exact BUFG," and reference an input port of your design. For example:

```

set_pad_type -exact BUFG clock1

```

**Note:** The cell name BUFG must be upper case. The **set\_pad\_type** command must be executed before the **insert\_pads** command.

The global clock pins provide much shorter clock-to-output delays than clocks routed through the logic array. Routing a clock through the logic array also uses up one extra p-term for each flip-flop.

If you want to prevent the fitter from automatically using the global clock pins, go to the Implementation Options template of the Design Manager and remove the check mark from Use Global Clock(s) as follows:

- 1. Design → Implement

- Press the Options softkey.

- 3. Select Edit Template

- 4. Select the Basic tab.

- 5. Remove the check mark from Use Global Clock(s).

Using command line you can also prevent the fitter from automatically using the global clock pins. To do this, specify the "-nogck" parameter on the cpld command line as follows:

2-6

```

cpld -nogck design_name

```

If -nogck is specified, input ports used as clocks will pass through the array. You can still use the set\_pad\_type command to explicitly specify global clock inputs.

If you use an internal signal as a clock, it will be routed to the flipflops through the logic array.

## **Output Enable Signals**

To use a device input to control tristate device outputs, you can simply refer to a top-level input port signal as a tristate condition in your design. For example:

```

entity xyz is

port (ENABLE:in std_logic; ...

...

0 <= 0_VALUE when (ENABLE='1') else `Z';</pre>

```

The fitter automatically uses one of the global tristate control pins (GTS for XC9000) whenever possible.

For XC9000 devices, a global tristate control input signal may perform an active-low output-enable. For example:

```

Q <= Q_VALUE when (ENABLE='0') else `Z';

```

The same tristate control input may even be used both active-high and active-low to enable alternate groups of device outputs. Global tristate control inputs may also be used as ordinary input signals to other logic elsewhere in the design.

If an input port signal passes through any logic function (other than an inverter) before it is used as an output enable by any output port, the input will not be routed to device output drivers in the design using the global tristate control path. Instead, the output enable signal will be routed through the logic array.

There are a limited number of global tristate control pins on each CPLD device (consult the device data sheet). If you need to explicitly control the use of global tristate control pins, you can specify the set\_pad\_type command in your dc\_shell script with the parameter "-exact BUFGTS", and reference an input port of your design. For example:

```

set_pad_type -exact BUFGTS enable1

```

**Note:** The cell name BUFGTS must be upper case. The **set\_pad\_type** command must be executed before the **insert pads** command.

The global tristate control pins provide much shorter input-tooutput-enable delays than tristate controls routed through the logic array. Routing a tristate control signal through the logic array also uses up one extra p-term for each output.

If you want to prevent the fitter from automatically using the global tristate control pins, go to Implementation Options template of the Design Manager and remove the check mark from Use Global Output Enable.

- 1. Design  $\rightarrow$  Implement

- 2. Press the Options softkey.

- 3. Select Edit Template

- 4. Select the Basic tab.

- 5. Remove the check mark from Use Global Output Enable(s).

Using the command line, if you want to prevent the fitter from automatically using the global tristate control pins, specify the -nogts parameter on the cpld command line as follows:

```

cpld -nogts design_name

```

If -nogts is specified, input ports used for tristate control will pass through the array. You can still use the set\_pad\_type command to explicitly specify global tristate control inputs.

If you use an internal signal as an output enable, it will be routed to the outputs through the logic array.

# **Asynchronous Clear and Preset**

To use a device input as an asynchronous clear or preset source, you can simply refer to a top-level input port as the set or reset condition in a clocked process. For example:

```

entity xyz is

port (CLOCK, RESET : in std_logic; ...

process (CLOCK, RESET)

```

```

begin

if (RESET='1') then Q <= `0';

elsif (CLOCK'event and CLOCK='1') then</pre>

```

For XC9000 designs, the fitter automatically uses the global set/reset pin (GSR) whenever possible. A global set/reset input signal may also perform active-low clear or preset. For example:

```

process (CLOCK, PRESET)

begin

if (PRESET='0') then Q <= `1';

elsif (CLOCK'event and CLOCK='1') then</pre>

```

A global set/reset inputs may also be used as an ordinary input signal to other logic elsewhere in the design.

If an input port signal passes through any logic function (other than an inverter) before it is used as an asynchronous clear or preset on any flip-flop, the input will not be routed to any flip-flops in the design using the global set/reset path. Instead, the clear/preset signal will be routed through the logic array. Routing a clear or preset through the logic array uses up one extra p-term for each flip-flop.

There is only one global set/reset pin on each XC9000 device. If you need to explicitly control the use of the global set/reset pin, you can specify the set\_pad\_type command in your dc\_shell script with the parameter "-exact BUFGSR" and reference an input port of your design. For example:

```

set_pad_type -exact BUFGSR reset1

```

**Note:** The cell name BUFGSR must be upper case. The set\_pad\_type command must be executed before the insert pads command.

If you use an internal signal as a set or reset, it will always be routed through the logic array.

**Note:** If a flip-flop has both a clear and preset condition and you assert both the clear and preset concurrently, its Q-output is unpredictable. This is because the fitter may arbitrarily invert the logic stored in a flip-flop to achieve better logic optimization. Individual clear and preset operations still produce the correct final logic state as dictated by the user design. Functional simulation does not accurately predict the ultimate behavior of the chip when clear and preset

are asserted concurrently. Timing simulation, however, is performed after logic optimization and behaves exactly as the chip will when programmed.

#### **Clock Enable**

If you express a synchronous clock-enable condition in a clocked process, and FDCE\_X or FDPE\_X primitive will be inferred from the XC9000 library. For example:

```

process (CLOCK)

begin

if (CLOCK'event and CLOCK='1') then

if (CLOCK EN='1') then O<=D;</pre>

```

These FDCE\_X or FDPE\_X primitives are always expanded into an ordinary D-type flip-flop with its Q-feedback multiplexed into its D-input.

FDCE\_X is an edge-triggered D-type flip-flop with asynchronous clear and clock enable. The synthesizer uses this component for all functions that require D-type registers with clock-enable, provided no asysnchronous preset condition is specified. FDCE\_X is not intended to be instantiated into any design.

FDCE is also an edge-triggered D-type flip-flop primitive with clear and clock enable. But, FDCE is never inferred. Users must explicitly instantiate it or explicitly replace an FDCE\_X cell that is inferred in the design. For XC9500XL and XC9500XV devices, the FDCE unconditionally uses the clock-enable product-term of the macrocell to implement the CE input. For XC9500 devices, FDCE is always expanded into a simple D-type flip-flop with its Q-feedback multiplexed into its D-input, just like the FDCE\_X cell.

FDPE\_X is an edge-triggered D-type flip-flop with asynchronous preset and clock enable. The synthesizer uses this component for all functions that require D-type registers with preset and clock-enable. FDPE\_X is not intended to be instantiated into any design.

FDPE is also an edge-triggered D-type flip-flop primitive with preset and clock enable. But, FDPE is never inferred. Users must explicitly instantiate it or explicitly replace an FDPE\_X cell that is inferred into the design. For XC9500XL and XC9500XV devices, the FDPE unconditionally uses the clock-enable product-term of the macrocell to

implement the CE input. For XC9500 devices, FDPE is always expanded into a simple D-type flip-flop with its Q-feedback multiplexed into its D-input, just like the FDPE\_X cell..

If you use FDCE or FDPE cells and target an XC9500XL or XC9500XV device, you may find that the logic connected to the clock enable input in some designs may not get optimized into the same macrocell as the flip-flop. The XC9500XL or XC9500XV macrocell contains only a single product-term to implement clock enable input logic. The CPLD fitter does not attempt transform your clock enable input logic onto the D-input of the flip-flop if it cannot be completely implemented using the clock enable p-term. In general, only primary inputs (device input pins or macrocell feedbacks), their complements or positive-logic AND-gate functions of primary inputs or their complements can be completely implemented using the p-term. If you connect a more complex logic function to the clock enable input of an FDCE or FDPE cell and it does not get completely implemented on the clock enable p-term, your design may incur extra macrocell resources and combinational macrocell feedback delays.

# **Controlling Register Initial State**

All registers in a CPLD device are initialized when the device is powered up. The initial state (preload value) of each register is programmable.

Registers in XC9000 macrocells have both asynchronous clear and asynchronous preset controls available. The initial power-on states of CPLD macrocell registers can be selected regardless of whether the register is asynchronously cleared of preset during operation.

Unless otherwise specified in your design, each register in an XC9000 device will initialize to the zero (reset) state at power-up.

#### **Initial State Attribute**

You can specify the preload states of selected register cells in your design by setting the initial state attribute in dc\_shell as follows:

```

set_attribute register_cell init state -type string

where:

```

register\_cell is the name (or set of names) of register cell(s) in your design, or the names of register output nets. state is either R (reset to 0) or S (set to 1).

For example, to specify an initial state of "1" for the register named QOUT\_reg, enter the following:

```

set_attribute QOUT_reg init S -type string

```

The initial state attribute is ignored if it is applied to any cell in your design that is not a flip-flop.

# **Controlling Power Consumption**

The power consumption of each macrocell in an CPLD device is programmable. The standard (default) setting consumes more power and produces shorter propagation delay. The low-power setting reduces power consumption for less speed-critical paths.

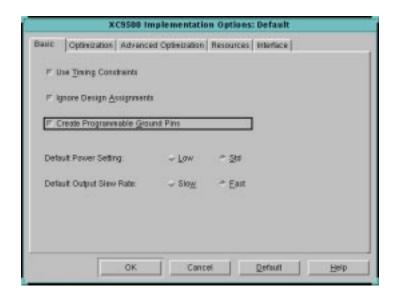

By default, all macrocells in the design will operate in standard power mode. You can change the global power setting to use the low power mode throughout the design by selecting Low on the Default Power Setting in the Implementation Options template in the Design Manager:

- 1. Design  $\rightarrow$  Implement

- 2. Press the Options softkey.

- 3. Select Edit Template

- 4. Select the Basic tab.

- 5. Select the Low option adjacent to Macrocell Power Setting.

When you run the fitter your design will be implemented with the low power setting.

To specify low power when using the Unix command line, use the "lowpwr" parameter with the cpld command as follows:

```

cpld -lowpwr design_name

```

You can also instruct the fitter to automatically reduce the macrocell power for paths that do not require standard power to meet timing constraints. In the Design Manager, check Timing Driven. On the Unix command line, specify the -autopwrslew parameter on the cpld command line:

```

cpld -autopwrslew design_name

```

# **Controlling Output Slew Rate**

For XC9000 devices each output is programmable to operate either at full speed or with limited slew rate. Limiting the slew rate reduces output switching surges in the device. Slew rate control becomes important when your design uses a large number of outputs or you have transmission lines on your board which are sensitive to fast edge rates.

By default, the CPLD fitter will apply a fast slew rate to all outputs. If you want to limit the slew rate of a device output to decrease its switching speed, use the "set\_pad\_type" command in dc\_shell. Enter the following in dc\_shell:

```

set_pad_type -slewrate HIGH port_list

```

where *port\_list* is a list of output ports that are to operate with slow output slew rate.

If you need to explicitly set an output to use fast slew rate, enter the following in dc\_shell:

```

set_pad_type -slewrate NONE port_list

```

**Note:** The **set\_pad\_type** command must be executed before the **insert pads** command in dc shell.

By default, the fitter uses Fast for slew rate for all output drivers. To change the default to slow slew rate in the Design Manager:

- 1. Design  $\rightarrow$  Implement

- 2. Press the Options softkey.

- 3. Select Edit Template

- 4. Select the Basic tab.

- Place a check mark in Slow box adjacent to Default Output Slew Rate.

To specify default slow slew-rate from the UNIX command line, use the parameter -slowslew in the cpld command:

```

cpld -slowslew design_name

```

The fitter also has an option whereby it will automatically apply **Slow** slew rate to each output unless that would cause any propagation delay to that pin to fail to meet a timing specification.

To enable slew-rate optimization in the Design Manager, go to the Implementation Options template and check the Fast box on the Default Output Slew Rate line.

To enable automatic slew rate control from the Unix command line, use the parameter -autoslewpwr when executing the cpld command.

cpld -autoslewpwr design\_name

# **Controlling the Pinout**

When you first run the fitter before your pinout is committed, the software automatically selects pin locations for your I/O signals. Pin locations are selected which will give you the greatest flexibility to iterate your design without having to move any of the pins. Each time the fitter successfully implements your design, it creates a guide file (<code>design\_name.gyd</code>), which contains all the resulting pinout information. After you commit your pinout, subsequent design iterations cause the guide file to be read by the fitter and your committed pinout will be preserved.

We strongly recommend that you allow the software to automatically generate your initial pinout. Attempting to select your own initial pin preferences reduces the ability of the fitter to implement your design successfully the first time. It further reduces the amount of logic changes you could make after locking your pinout.

# **Pin Locking**

If you have successfully fit a design into an CPLD device and you build a prototype containing the device, you will probably want to "lock" the pinout.

- 1. In the Design Manager, select an existing design revision that was successfully run through the Fit step (typically, your most recent revision).

- Select Design →Lock Pins. The pinout saved in the selected revision (stored in design\_name.gyd) is translated into pin location (LOC) constraints and written into a user constraint file (design\_name.ucf).

- 3. Select View Lock Pins Report in the dialog box to make sure no pin assignment conflicts were found.

When ready, run the fitter (Design → Implement). The previous pinout information will be read from the UCF file and used in the new design revision.

If you want to tell the fitter to directly read the guide file (design\_name.gyd) on the Unix command line, you should specify the "pinlock" option with the cpld command as follows:

```

cpld -pinlock design_name

```

The -pinlock parameter tells the fitter to read and obey the pinout from the guide file that was saved the last time the fitter completed.

The fitter will not move any of the pins contained in the guide file, even if it prevents the design from successfully mapping.

Whenever you specify a guide file (pin locking), the fitter automatically uses the same device and package as previously used, unless you override it with a different specific device and/or package.

The pin locations stored in the guide file are specified based on the top-level port names in your design. If you change the name of any of your ports, the corresponding pin will no longer be constrained to the location stored in the guide file.

When you iterate your design while your pins are locked, you are free to delete existing ports and/or add new ports. The fitter will automatically select the best locations for any new ports you add, after placing all the existing ports constrained by the guide file.

**Note:** If you iterate your design and your pinout is not yet committed (you haven't built a prototype containing the device), you should not specify the pinlock option. Instead, allow the software to redefine the pinout of your modified design. This will continue to give you the greatest flexibility to iterate your design again after you commit your pinout.

## Pin Assignment

You can assign explicit locations for pins in your design using the LOC attribute in dc\_shell. Enter the following in dc\_shell:

```

set_attribute port LOC pin_name -type string where port is the name of the port being assigned.

```

For example, to place the "start" input port on pin 23:

#### set\_attribute start LOC p23 -type string

For PC, PQ and VQ type packages, the *pin\_name* takes the form "Pnn" where *nn* is a number. For example, for the PC84 package, the valid range for *pin\_name* is P1 through P84. For grid array type packages (PG and BG), the *pin\_name* takes the form "rc", where r is the row letter and c is the column number.

You can also specify pin locations interactively using the Constraints Editor tool invoked from the Design Manager.

When your design contains LOC attributes, you should specify the target device type in the Design Manager Part Selector menu or using the cpld command's -p parameter (see Target Device Selection in this Chapter). The LOC attributes are typically not compatible when retargeting a design between different package types, device types or device families.

The LOC attributes are unconditional in that the software will not attempt to relocate a pin if it cannot achieve the specified assignment. If you specify a set of LOC attributes that the fitter cannot satisfy, the fitter will terminate with an error.

The LOC attributes override the pin assignments in the guide file if you specify the pinlock option. This allows you to make explicit changes to your committed pinout. If you override the guide file using LOC attributes, the software will issue a warning.

If your objective is to preserve a previously created pinout, we recommend you use the pinlock feature instead of creating a set of LOC attributes with the existing pin locations. The guide file saved from the previous design implementation contains additional information to help the fitter to successfully fit your modified design.

If you used LOC attributes when compiling your netlist but you want to temporarily allow the fitter automatically assign all I/O pins, place a check in the Ignore Design Assignments box in the Basic tab of the Implementation Options template:

- 1. Design  $\rightarrow$  Implement

- Press the Options softkey.

- Select Edit Template

- 4. Select the Basic tab.

Remove the check mark next to Use Design Location Constraints.

To temporarily allow the fitter automatically assign all I/O pins when using the Unix command line, you can specify the -ignoreloc parameter on the cpld command:

```

cpld -ignoreloc design_name

```

The -ignoreloc option allows you to temporarily ignore all the LOC attributes in your netlist. This is useful if you want to test how your design fits a different target device without re-compiling your design.

## **Prohibiting the Use of Device Pins**

Prohibit I/O Locations allows you to reserve device pins for later use, or simply prevent them from being used at all. For instance, if you anticipate design changes in the future and want to set traces on your printed circuit board now, you can use this feature to prevent the fitter from using pins associated with those traces. Then, when you decide to use the traces, you can use the LOC attribute to assign those pins to new input/output buffers you place in your design.

In the Constraints Editor, **Prohibit I/O Locations** prevents all selected I/O pins from being used by the design. This dialog can be entered using a dialog box provided in the **Ports** tab.

# **Pin Assignment Precautions**

You can apply the LOC attribute to as many ports in your design as you like. However, each pin assignment further constrains the software making it more difficult for the fitter to automatically allocate logic and I/O resources for the remaining I/O signals in your design.

When you manually assign output and I/O pins, you force the software to place associated logic functions into specific macrocells and specific function blocks. If the associated logic does not exceed the available function block resources (macrocells, product terms, and FastCONNECT inputs), the logic is mapped into the macrocell and the design will route in the FastCONNECT.

It is usually best to allow the fitter to automatically assign most or all of the pins based on the most efficient placement of logic in the device. The fitter automatically establishes a pinout which best

allows for future design iterations without pin relocation. Any manual pin assignments you make in your design may not allow as much tolerance for changes in the logic associated with those pins, and in the logic physically mapped to nearby locations in the device.

If you are assigning pin locations to ports used as clocks, asynchronous set/reset, or output enable in your design, you should assign them to the GCK, GSR and GTS pins on the device if you want to take advantage of these global resources. The fitter will still automatically assign other clock, set/reset and output enable inputs to remaining GCK, GSR and GTS pins if available.

# **Controlling Logic Optimization**

When you create combinational logic functions, the software attempts to collapse as much of the logic as possible into the smallest number of CPLD macrocells. Combinational logic optimization performed by the synthesis tool are generally not essential to the efficiency or performance of the resulting CPLD implementation. The CPLD fitter automatically performs all essential optimizations.

Any combinational logic function bounded between device I/O pins and flip-flops is subject to complete or partial collapsing. Collapsing the logic improves the speed of the logic path and can also reduce the amount of logic resources (macrocells, p-terms and FastCONNECT inputs) required to implement the function.

The process of collapsing logic into other logic functions is called "logic optimization".

# **Multilevel Logic Optimization**

Multilevel Logic Optimization seeks to simplify the total number of logic expressions in a design, and then collapse the logic in order to meet user objectives such as density, speed and timespecs. This optimization targets CPLD architecture, making it possible to collapse to the macrocell limits, reduce levels of logic, and minimize the total number of pterms.

Multilevel Logic Optimization extracts combinational logic from your design. Combinational logic includes:

- register-to-register logic

- path-to-register logic

- register-to-path logic

- path-to-path logic

Multilevel Logic Optimization operates on combinational logic according to the following rules:

- 1. If timespecs are set, the program will optimize for speed to meet timespecs.

- If timespecs are not set, the program will optimize either for speed or density, depending on the user setting of Timing Optimization.

- a) If Timing Optimization is turned on, the combinational logic will be mapped for speed.

- b) If Timing Optimization is turned off, the combinational logic will be mapped for density. The goal of optimization will then be to reduce the total number of pterms.

- 3. Logic marked with the attribute **NOREDUCE** will not be extracted or optimized.

#### **Setting Multilevel Logic Optimization**

Multilevel Logic Optimization can be set from the Advanced tab of the Implementation Options template of the Design Manager as follows:

- 1. Design  $\rightarrow$  Implement

- 2. Press the Options softkey.

- 3. Select Edit Template

- 4. Select the Advanced tab.

- Place a check in the Use Multilevel Logic Optimization box.

Multilevel Logic Optimization will operate when you run the fitter.

If you wish to disable multilevel logic optimization when running a design from the cpld command, use the option -nomlopt. If you do not specify this option, the fitter automatically uses multilevel logic optimization.

#### **Collapsing Product Term Limit**

When a larger combinational logic function consisting of several levels of AND-OR logic is completely collapsed (flattened), the number of product terms required to implement the function may grow considerably. By default, the fitter limits the number of p-terms used as a result of collapsing to 20 when using the Optimize Speed template, or 90 when using the Optimize Density template. If the collapsing of a logic level results in a logic function consisting of more p-terms than the limit (after Boolean reduction), then the collapsing of that logic level is not performed and the function will be implemented using two or more levels of AND-OR logic.

**Note:** The fitter will not exceed the collapsing p-term limit even if a timing constraint applied to a path cannot be met.

When the Timing Optimization option is off, as it is in the Optimize Density template, the fitter only performs collapsing on a node if the total number of p-terms used after collapsing would be less than the total number of p-terms used by the combined functions before collapsing.

The overall extent to which logic is collapsed throughout an XC9000 design can be controlled from the Advanced Optimization tab of the Implementation Options template.

- 1. Design  $\rightarrow$  Implement

- 2. Press the Options softkey.

- 3. Select Edit Template

- 4. Select the Advanced tab.

- 5. Place a value in the Collapsing Pterm Limit box, or use the up and down arrows to raise or shrink the Pterm limit. The allowable range is between 2 and 90.

To change the Pterm limit from Unix, use the "-pterms" parameter on the cpld command line:

```

cpld -pterms nn design_name

```

where *nn* is the maximum allowable number of p-terms that can be used to implement a logic function after collapsing. The allowable range for the pterms parameter is between 2 and 90.

If you find that the path delay of a larger, multi-level logic function in an XC9000 design is not satisfactory, try increasing the pterms parameter to allow the larger functions to be flattened further. For example, you may try increasing the p-term limit to 35 when rerunning the fitter, as shown:

```

cpld -pterms 35 design1

```

The fitter report (<code>design\_name.rpt</code>) indicates the number of p-terms used for each logic function. You should see these numbers increase as you raise the pterms limit, until the design is fully flattened. At the same time, you'll see the internal combinational nodes eliminated until none remain.

## **Preventing Collapsing of a Logic Node**

Flattening typically increases the overall amount of p-term resources required to implement the design. Some designs which fit the target device initially may fail to fit if flattened too much. Other designs can be flattened completely and still fit. If you cannot increase the cpld pterms parameter enough to sufficiently flatten a critical path and still fit the target device, you may try applying logic optimization control at specific nodes in your design.

A special cell is provided in the XC9000 libraries, named KEEP, which is used to apply a logic optimization constraint to any signal passed through it. The KEEP cell has one input port named I and one output port named O (letter O). By instantiating a KEEP cell and passing through it a signal in the middle of a combinational logic function, you can prevent that signal from being collapsed. That is, you prevent the cell that drives the signal from being collapsed forward into any of its fanouts. The KEEP cell is instantiated as follows:

```

label: KEEP port map (O => outgoing_signal, I =>

incoming_signal);

```

In the following example, a KEEP cell is used to prevent the logic for an address decoder from being collapsed into the select input of a 16bit multiplexer:

```