# CX20152

## Dual 16 bit, 88 kHz, Multiplexed D/A

#### Description

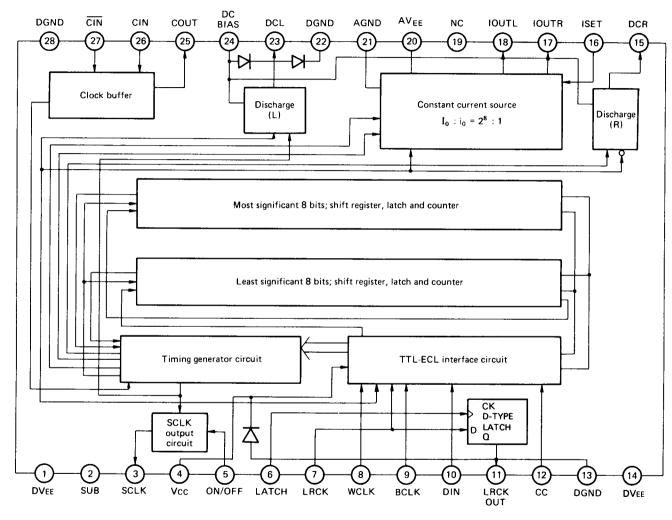

CX20152 is a 16-bit D/A converter IC for PCM audio. It uses an integration system consisting of the following circuits.

- Clock signal generator

- TTL-ECL interface circuit

- Discharge drive circuit

- Analog switch drive circuit

- 1/4 frequency divider output circuit

By adding an integrator, analog switch and low pass filter externally to the IC, analog signal is reproduced from the 16-bit digital data.

#### Features

• Conversion frequency

88.2kHz

Serial data input

• Low distortion factor

0.003% (typ.)

#### Structure

Bopolar Sillicon Monolithic IC

#### **Absolute Maximum Rating**

| <ul> <li>Supply voltage</li> </ul>              | VCC to VEE | 12            | ٧  |

|-------------------------------------------------|------------|---------------|----|

| <ul> <li>Operating temperature</li> </ul>       | Topr       | -20 to +75    | °C |

| Storage temperature                             | Tstg       | -55 to $+150$ | °C |

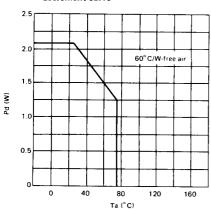

| <ul> <li>Allowable power dissipation</li> </ul> | PD         | 2.1           | W  |

#### **Recommended Operating Conditions**

| Supply voltage | Vcc | 5 ±0.25  | ٧ |

|----------------|-----|----------|---|

|                | VFF | -5 ±0.25 | V |

#

Evaluation Board Available - CX20152PCB

#### Pin Description

| No. | Symbol   | Description                                     |

|-----|----------|-------------------------------------------------|

| 1   | DVEE     | Digital VEE: -5V                                |

| 2   | SUB      | IC substrate: Be sure to connect to Pin 1.      |

| 3   | SCLK     | System clock output pin                         |

| 4   | Vcc      | Digital Vcc: +5V                                |

| 5   | ON/OFF   | Pin to determine the system clock on/off        |

| 6   | LATCH    | Clock pin of D type latch                       |

| 7   | LRCK     | LRCK input pin                                  |

| 8   | WCLK     | WCLK input pin                                  |

| 9   | BCLK     | BCLK input pin                                  |

| 10  | DIN      | DIN (data input pin): MSB first                 |

| 11  | LRCK OUT | LRCK output pin                                 |

| 12  | СС       | CC input pin                                    |

| 13  | DGND     | Digital ground                                  |

| 14  | DVEE     | Digital VEE: -5V                                |

| 15  | DCR      | Right channel discharge drive signal output pin |

| 16  | ISET     | Integration current setting pin                 |

| 17  | IOUTR    | Right channel current output pin                |

| 18  | IOUTL    | Left channel current output pin                 |

| 19  | NC       | No connection                                   |

| 20  | AVEE     | Analog VEE                                      |

| 21  | AGND     | Analog GND                                      |

| 22  | DGND     | Digital GND                                     |

| 23  | DCL      | Left channel discharge drive signal output pin  |

| 24  | DC BIAS  | Discharge circuit bias pin                      |

| 25  | COUT     | Clock generator output pin                      |

| 26  | CIN      | Clock generator positive input pin              |

| 27  | ČIŃ      | Clock generator negative input pin              |

| 28  | DGND     | Digital GND                                     |

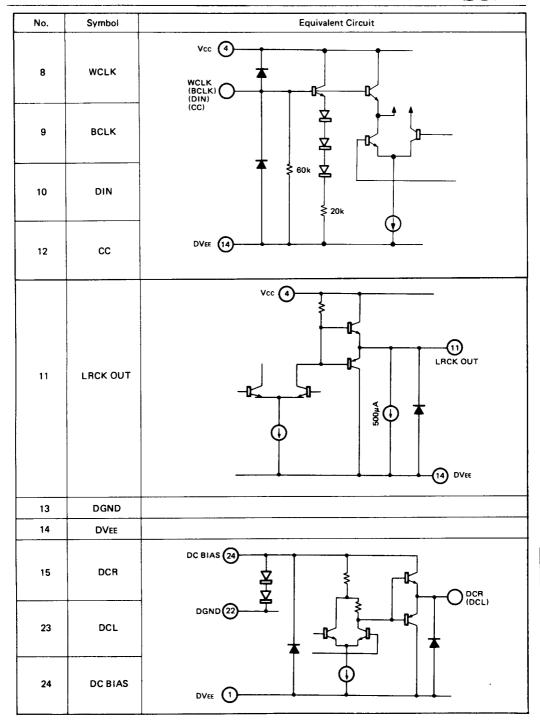

#### **CX20152 Input/Output Pin Equivalent Circuits**

| No. | Symbol | Equivalent Circuits                        |

|-----|--------|--------------------------------------------|

| 1   | DVEE   |                                            |

| 2   | SUB    |                                            |

| 3   | SCLK   | VCC 4  S S S S S S S S S S S S S S S S S S |

| 4   | Vcc    |                                            |

| 5   | ON/OFF | ON/OFF 5  470  50k  70k  10k  10k  10k     |

| 6   | LATCH  | LATCH (LRCK)                               |

| 7   | LRCK   | DVEE 14                                    |

| No. | Symbol | Equivalent Circuits               |

|-----|--------|-----------------------------------|

| 22  | DGND   |                                   |

| 16  | ISET   | 21) AGND   SET 16   2k   20) AVEE |

| 17  | IOUTR  | AGND (21)                         |

| 18  | IOUTL  | AVEE (22)                         |

| 19  | NC     |                                   |

| 20  | AVEE   |                                   |

| 21  | AGND   |                                   |

| 25  | СОПТ   | 28) DGND CIN(26) COUT             |

| 26  | CIN    | CIN (27)<br>4.9k ₹ ₹4.9k          |

| 27  | CIN    | DVEE                              |

| 28  | DGND   |                                   |

#### **Electrical Characteristics**

$\{Ta = 25^{\circ}C, V_{EE} = -5.0V, V_{CC} = 5.0V\}$

|                                             |            |                                                                                          | -, - 22 |       | ,     |      |

|---------------------------------------------|------------|------------------------------------------------------------------------------------------|---------|-------|-------|------|

| ltem                                        | Symbol     | Conditions                                                                               | Min.    | Тур.  | Max.  | Unit |

| Circuit current                             | lee        | 1, 2, 14, 20 Pins 4, 5 = 5V                                                              | -125    | -95   |       | mΑ   |

| Circuit current                             | lcc1       | Pin 5 = 5V<br>(6, 7, 8, 9, 10, 12, GND)                                                  |         | 12.6  | 15.5  | mΑ   |

| Circuit current                             | lcc2       | Pin 5 = 0V<br>(6, 7, 8, 9, 10, 12, GND)                                                  |         | 5.9   | 10.0  | mA   |

| Input threshold voltage                     | Vтн        | 6, 7, 8, 9, 10, 12                                                                       |         | 2.1   |       | V    |

| High level input voltage                    | Vн         | 6, 7, 8, 9, 10, 12                                                                       | 2.9     |       |       | ٧    |

| Low level input voltage                     | VIL        | 6, 7, 8, 9, 10, 12                                                                       |         |       | 0.9   | ٧    |

| High level input current 1                  | İH-1       | 5 V <sub>IH</sub> = 5V                                                                   |         | 0.7   | 1.3   | mΑ   |

| High level input current 2                  | hH2        | 6, 7, 8, 9, 10, 12 VIH = 5V                                                              |         | 250   | 550   | μΑ   |

| Low level input current 1                   | HL1        | 5 VIH = OV                                                                               |         | 0.35  | 0.8   | mΑ   |

| Low level input current 2                   | laL2       | 6, 7, 8, 9, 10, 12 VIL = OV                                                              |         | 120   | 550   | μΑ   |

| High level output voltage                   | VLRCKH     | With Pin 7 at 4.5V, set I <sub>OH</sub> = -100μA and input a clock of 0V-5V-0V to Pin 6. | 2.7     | 4.2   |       | ٧    |

| Low level output voltage                    | VLRCKL     | With Pin 7 at 0V, set I <sub>OL</sub> = 100µA and input a clock of 0V-5V-0V to Pin 6.    |         | -3.1  | -2.7  | ٧    |

| SCLK output, high level                     | Vsclkh     | 3 IoH = -10μA                                                                            | 3.4     | 4.2   |       | V    |

| SCLK output, low level                      | VSCLKL     | 3 $IoL = 400\mu A$                                                                       |         | 0.5   | 1.6   | V    |

| Discharge circuit power dissipation current | IDCBIAS    | 24 VDCBIAS = OV                                                                          |         | 1.9   | 2.5   | mA   |

| Discharge circuit high level output voltage | Vocн       | 15, 23 Pin 24 voltage = 1.3V<br>Load current = 1.2mA                                     | 0       | 0.4   | 0.65  | ٧    |

| Discharge circuit low level output voltage  | VDCL       | 15, 23 Pin 24 voltage = 1.3V<br>Load current = 1.2mA                                     |         | -4.2  | -3.4  | ٧    |

| SET current                                 | İSET       | 16                                                                                       |         | 0.5   | 1.0   | mΑ   |

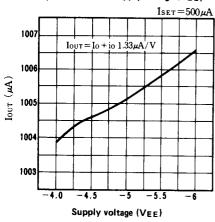

| IOUT output current                         | Іоит       | 17, 18 Pins 17, 18: Voltage = 0V Pin 16: ISET = 500μA (lout = lo + io)                   |         | 2.008 |       | mA   |

| Clock input bias voltage                    | Vcin       | 26, 27                                                                                   |         | -1.3  |       | ٧    |

| Clock high level output voltage             | Vсон       | 25                                                                                       |         | -0.8  |       | ٧    |

| Clock low level output voltage              | VcoL       | 25                                                                                       |         | -1.6  |       | ٧    |

| Current output pin leakage                  | lo<br>LEAK | 17, 18 Pins 17, 18: Voltage = 0V when the current output is off.                         |         |       | 1.5   | μΔ   |

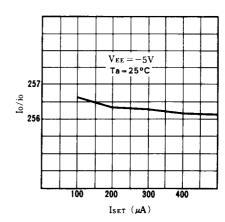

| Current ratio                               | lo/io      | 17, 18 Pin 16: ISET = 500µA                                                              | 255.0   | 256.0 | 257.5 | -    |

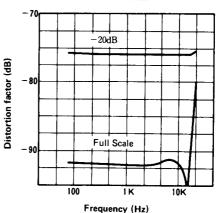

| District for                                | THD1       | Both right and left; OdB (full scale) when reproduced.                                   |         | 0.003 | 0.005 | %    |

| Distortion factor                           | THD2       | Both right and left; -20dB when reproduced.                                              |         | 0.02  | 0.025 | %    |

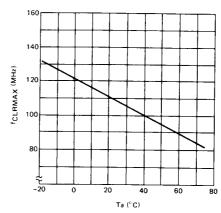

| Operation clock frequency                   | fcLK1      | Both self-drive & external-drive Ta = -20 ~ +70° C                                       |         | 68    | 80    | МН   |

| Operation clock frequency                   | fCLK2      | Both self-drive & external-drive Ta = -20 ~ +75°C                                        |         | 68    | 75    | мн   |

#### **Description of Conversion Operation**

#### (1) Data pickup (BCLK, DIN, WCLK, LRCK)

Data consist of 16-bit serial signals in 2's complement. They are transmitted into the IC sequentially from the MSB in synchornization with the rise edge of the bit clock (BCLK). (The BCLK delay will change the data. The falling edge changes the data.)

When the word clock (WCLK) is changed from high level to low level at the 17th BCLK, the 16-bit data is transferred from the shift register to the latch with the decay signal. When CX20152 is used in the stereo mode, other-channel data are transmitted from the 17th BCLK.

In the stereo mode, the Rch data is picked up when LRCK is at a low level and the Lch data is picked up when LRCK is at a high level. IOUTL and DCL operate only when LRCK is at a low level, and IOUTR and DCR operate only when LRCK is at a high level.

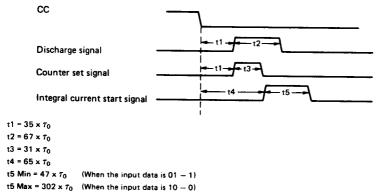

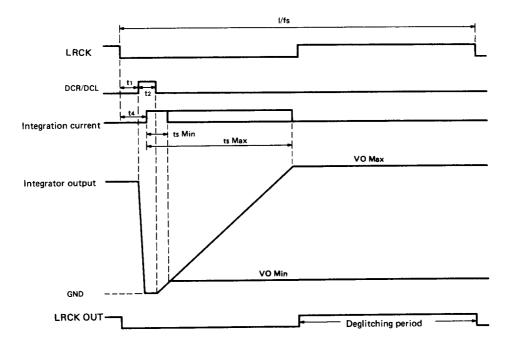

#### (2) Conversion operation (CC, LRCK, CIN, IOUTL, IOUTR, DCL, DCR)

When more than 3 clocks are fed from the clock input (CIN) with the conversion command (CC) at a high level, all the internal timing circuits are reset.

After the resetting, the internal timing circuit starts operation when a clock is input from CIN with CC at a low level. From this operation, three signals, Discharge, Counter set and Integral current Start, are generated. Timing of these signals is determined as follows by the clock interval  $\tau_0$  and its quantity.

The counter set signal is used to set the data input in the latch to the counter but does not output externally.

The discharge signal is output from DCL and DCR and controlled by LRCK. It is output from DCL when LRCK is at a low level and from DCR when LRCK is at a high level.

The integral current start signal starts the upper current lo and lower current io flowing. The counter starts counting from the preset value simultaneously when the discharge signal is off, counts 11 offsets after the end of the counting and outputs a signal to stop the integration current. The value  $t_5$  is varied between 0 to 255 by the input data value preset to the counter.

Therefore, the time before the end of the integration after the low level has been set, i.e. the conversion time, requires the maximum  $\{t_4 + t_5 \text{ Max} = 367 \times \tau_0\}$  seconds.

The integration current of IOUTL is output, as with the discharge signal, when LRCK is at a low level; IOUTR is output when LRCK is at a high level.

#### (3) The relation between sampling frequency fs and clock

The maximum and minimum values of the integration voltage output, VO Max and VO Min, are expressed as follows.

$$V_{O \text{ Max}} = \frac{I_0}{C} * \tau_o^* 267 + \frac{I_0}{C} * \tau_o^* 266$$

(t<sub>4</sub>+t<sub>5</sub> Max)

Vo Min =

$$\frac{I_0}{C} * \tau_o^* 12 + \frac{i_0}{C} * \tau_o^* 11$$

(t<sub>4</sub>+t<sub>5</sub> Min)

where  $f_{CLK}$  is a clock frequency and au is a period.

The integration voltage is held by the capacitor C in the integrator when the current is switched off. This voltage is used as D/A conversion output during the deglitching period T which is given according to the settling time of the deglitching circuit.

The relation between the conversion frequency f<sub>s</sub> and the clock frequency FCLK is given as below assuming that the conversion time and deglitching period are equivalent:

$$fs = \frac{f_{CLK}}{2 \times (t_4 + t_{5 \text{ Max}})} = \frac{f_{CLK}}{734}$$

where fs = 44.1 kHz results in 32.4 MHz of fclk

It is, however, recommendable to specify  $f_s$  as the follow for the practical use because a settling time of 0.5 to 1.0  $\mu s$  is required for the integrator after the current for  $t_s$  disappears:

$$fs = \frac{fCLK}{2(t_4 + t_5 Max + 1.0(\mu s)) + T}$$

#### (4) Integration current setting (ISET, IOUTL, IOUTR)

Integration current is determined by a constant current value input through the ISET pin, which is given as below:

IOUTL (R) =

$$i_0 + i_0 = (4 + \frac{1}{64})$$

ISET

where i<sub>0</sub> and I<sub>0</sub> are integration currents corresponded to the ILSB and 28 LSB, respectively.

If  $D_0$  and  $D_{15}$  are specified as MSB and LSB, respectively, integrator output voltage  $V_0$  is given by the following equation:

$$V_0 = \frac{I_0}{C} (D_0 * 2^7 + \overline{D}, * 2^7 + \dots + \overline{D}_7 * 2^0 + 12) \tau_0$$

$$+ \frac{I_0}{C} (\overline{D_8} * 2^7 + \overline{D_9} * 2^6 + \dots + \overline{D_{15}} * 2^0 + 11) \tau_0$$

where ISET = 500  $\mu$ A,  $\tau = \frac{1}{35 \text{ (MHz)}}$  = 28.6 (ns) and C=2000 pF result in the maximum output voltage Vo Max

of the integrator when any of a value from 10 to 0 is given as an input data. Based on the relations below,

$$i_0 = \frac{1}{64} * ISET$$

Vo Max is calculated as the follow:

Vo Max =

$$\frac{2.0 \times 10^{-3}}{2000 \times 10^{-12}} *267*28.6 \times 10^{-9}$$

+  $\frac{400*10^{-6}/64}{2000 \times 10^{-12}} *266*28.6 \times 10^{-9}$

= 7.67 (V)

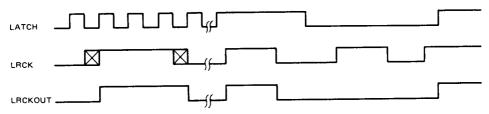

#### (5) LRCK OUT operation (LATCH, LRCK, LRCK OUT)

The LRCK OUT is a drive output for the analog switch IC (equivalent to MC14053B) to clip the output converted by CX20152 and the integrator so that the converted output can be a PAM wave. If the PAM wave has a jitter, a conversion error results. To absorb this jitter, a D-type latch is built-in and the LATCH input is used as its clock. The D-type latch sets the output state in synchronization with the rise of the clock(LATCH) and the logic high.

Timing of LATCH, LRCK and LRCKOUT

In the high-speed conversion (with sampling frequency of 88.2kHz), the clock frequency is as high as about 70MHz. This will affect the delay time of the analog switch IC. The delay time possibly becomes equal to t<sub>1</sub>. Then, the last part of the PAM wave overlasps on the discharge time for CX20152 causing a considerable conversion error. In such a case, LRCK level can be fed through by keeping LATCH at a high level.

#### (6) Clock input/output Pin (COUT, CIN and CIN)

The clock buffer consists of a circuit equivalent to a general-purpose ECL logic circuit, with its input pin biased with an internal bias circuit (= -1.3V). The output amplitude level is 0.8V.

#### (7) Bias Pin (DVEE, SUB, DGND, VCC, AVEE, AGND and DC BIAS)

SUB denotes the IC substrate and its voltage potential should be common to that of DVEE . The standard value of DVEE and AVEE is -5.0V.

$V_{CC}$  is the power supply for the interface circuit from a CMOS or TTL level to the internal ECL logic. Its standard value is +5V.

DC BIAS is the bias circuit of the discharge signal output circuit. As it requires about 2.5mA as its standard current, supply current should be  $2.5mA + \alpha$ . This pin voltage is biased to 2Vf and the value of  $\alpha$  is determined as follows.

To maintain the pin voltage at 2Vf ( $\approx$  1.4V), about 0.5 mA of current is required. Additionally, the maximum current flowing through the load resistor R<sub>L</sub> attached to DCR (Pin 15) and DCL (Pin 23) is obtained from the following equation.

$$1/R_L \times (V_{DCH} + |DV_{EE}|) \times 2$$

, where  $R_L = 4.7$ kohm, VDCH = 0.4V and DVEE =  $-5$ V

Hence,  $\alpha = 0.5 + 1.15 = 1.65$  (mA)

Therefore, the total current will be 4.32mA.

We recommend 5mA with R<sub>L</sub> at 4.7 k $\Omega$ .

#### (8) System clock output pin, ON/OFF (SCKL, ON/OFF)

SCLK is the output pin of the 1/4 frequency divider of the oscillation circuit's master clock frequency. The frequency outputs when the ON/OFF pin is supplied with 5V (Vcc) and stops when the ON/OFF pin is supplied with 0V or set to open.

As its output amplitude is 2V and too low to be connected directly to a TTL or CMOS, be sure to amplify before connection.

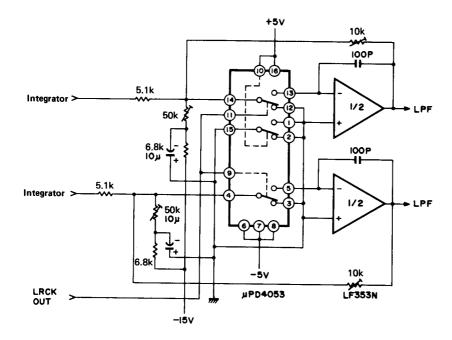

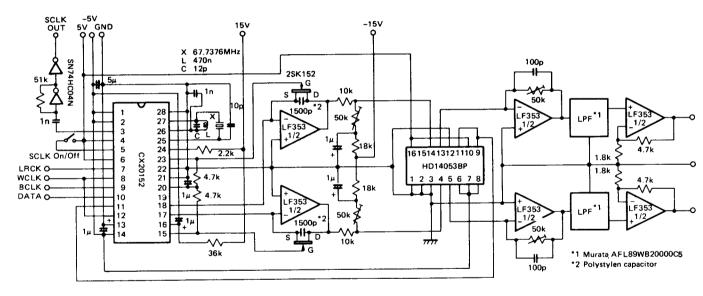

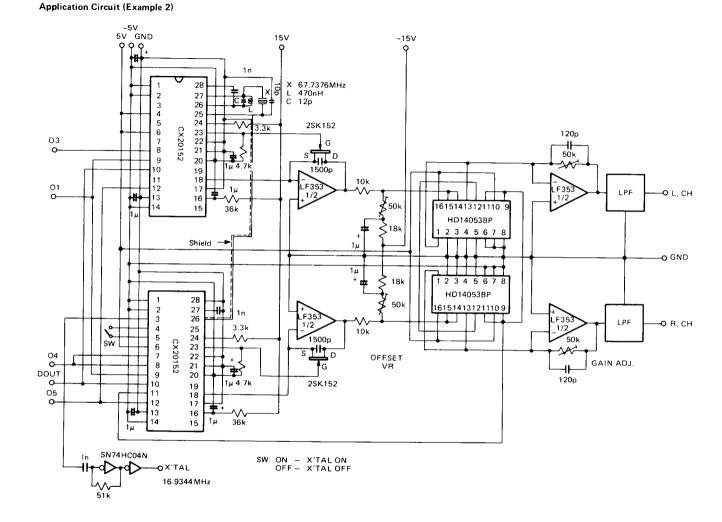

#### Application Circuit for Operating Deglitcher in Sample/Hold Type

CX20152

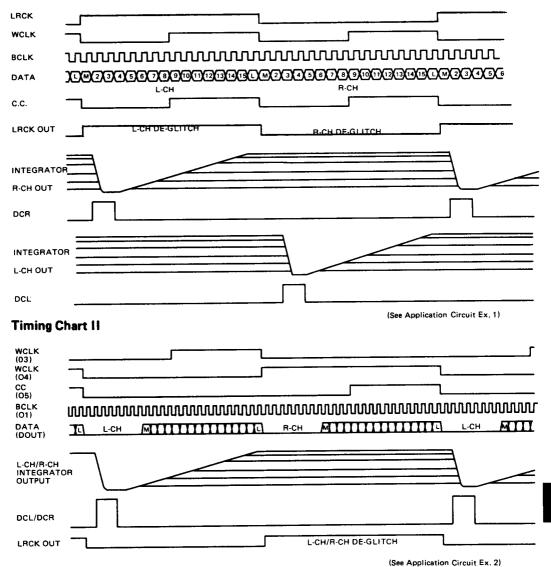

#### **Timing Chart**

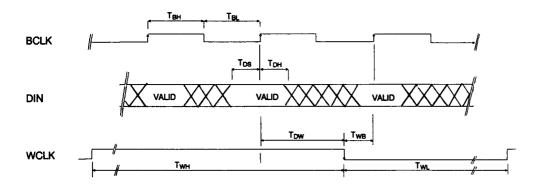

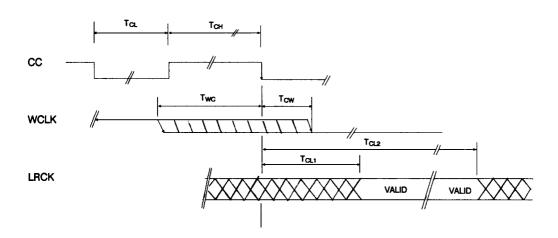

## **Detailed Timing Chart**

| Твн              | BCLK "H" Pulse width             | min = 100ns                                                   |

|------------------|----------------------------------|---------------------------------------------------------------|

| TBL              | BCLK "L" Pulse width             | min = 100ns                                                   |

| TDS              | DIN Set-up time                  | min = 50ns                                                    |

| TDH              | DIN Hold Time                    | min = 50ns                                                    |

| Tow              | from DINto WCLK                  | min = 150ns                                                   |

| TwB              | from WCLKto BCLK                 | min = 50ns                                                    |

| Тwн              | WCLK "H" Pulse Width             | min = 100ns                                                   |

| TwL              | WCLK "L" Pulse Width             | min = 100ns                                                   |

| TCH              | CC "H" Pulse width               | min = 4xrM                                                    |

| TCL              | CC "L" Pulse width               | min = 102χτ <sub>M</sub>                                      |

| Twc              | from WCLKto CC                   | max = T <sub>CL</sub> + T <sub>CH</sub> - 70 x τ <sub>M</sub> |

| Tcw              | from CC to WCLK                  | max = 30 x τ M                                                |

| T <sub>CL1</sub> | from CC to LRCK "Invalid→ Valid" | max=34 x TM - TA - TB/2                                       |

| T <sub>CL2</sub> | from CC to LRCK "Valid→ Invalid" | min = 367×τ <sub>M</sub>                                      |

|                  |                                  |                                                               |

$\tau$  M = 1/fMCLK

$\tau$  A = Delay time produced by external analog switch

$\tau$  B = 1/fBCLK

## Maximum allowable power dissipation decrement curve

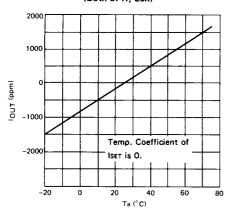

lout temperarure characteristics (Io + io)

(Both of R, Lch)

Output current vs. Supply voltage (VEE)

## Maximum clock frequency temperature characteristics

lo/io vs. ISET

Distortion factor