CMOS LSI

LC78681E

# SANYO

# Digital Signal Processor for

**Compact Disc Players**

# Overview

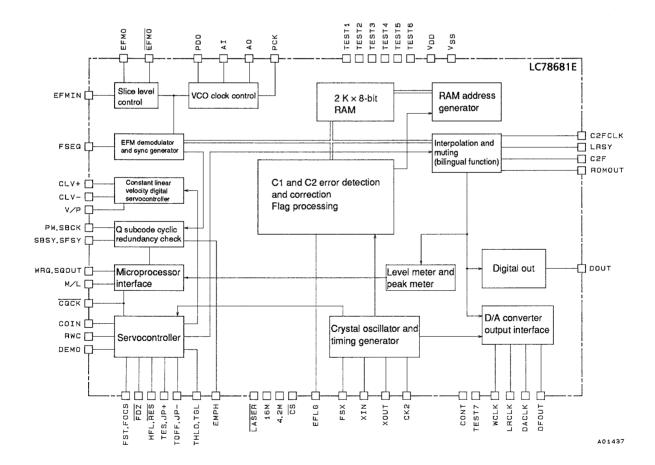

The LC78681E is a CMOS LSI providing digital signal processing (DSP) and servo control for compact disc players and other audio devices, including laser disc players and equipment using compact disc video (CD-V) and compact disc interactive (CD-I) formats. Functions include the demodulation of EFM (eight-to-fourteen modulation) signals from optical pickups, deinterleaving, detection and correction of error signals, and signal processing for digital filters as well as other features that can help reduce player cost. The LC78681E also processes commands from the microprocessor for the servo system. Direct interface is also possible with the Sanyo LC7883K and LC78835, which are serial input D/A converters with on-chip digital filters.

# **Functions**

- HF signals that are input are sliced at an accurate level, converted to EFM signals, and undergo phase-comparison with VCO for PLL playback at an average of 4.3218 MHz.

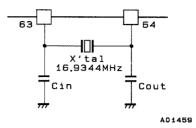

- Through external connection of a 16.9344 MHz crystal oscillator, all required timing signals can be generated on-chip, including the standard clock.

- Frame phase difference signals made from the playback clock and the reference clock can control the speed of the disc motor.

- Performs detection, protection, and interleaving of frame synchronization signals, ensuring stable data reading.

- Demodulates EFM signals and performs conversion to 8-bit symbol data.

- Separates subcodes from EFM demodulation signals for output to an external microprocessor.

- After CRC checking, Q subcode signals are output to the microprocessor by the serial I/O interface (LSB-first

output selectable).

- On-chip RAM performs buffering for EFM demodulation signals, as well as absorbing up to  $\pm 4$  frames of jitter due to fluctuations in the speed of disc rotation.

- Performs unscrambling and deinterleaving for rearranging the EFM demodulation signals into the specified sequence.

- Performs detection and correction of error signals, as well as error flag processing (double C1 and double C2 error correction system).

- Compares the results of the C1 flag and the C2 check to set the C2 flag, and performs signal interpolation and previous-value hold according to the C2 flag. The interpolator uses 4-interpolation, where 0 volt down is performed when the C2 flag is set four times in a row.

- Performs functions such as track jump, focus start, disc motor start and stop, muting on and off, and track count when the appropriate command is input from the microprocessor (8-bit serial input).

- Features on-chip digital out.

- Can perform the desired track counting. High-speed access is possible.

- Uses zero cross-muting.

- Fully supports double-speed dubbing.

- Supports all types of D/A conversion.

- Features on-chip digital level meter and peak meter functions.

- Supports bilingual function.

# Features

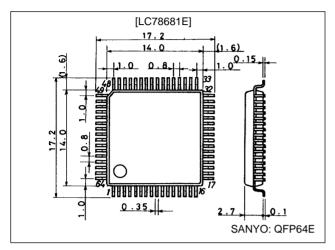

- Compact and space-saving 64-pin QFP package

- Silicon-gate CMOS design (low power dissipation)

- Single 5 V power supply (suitable for portable sets)

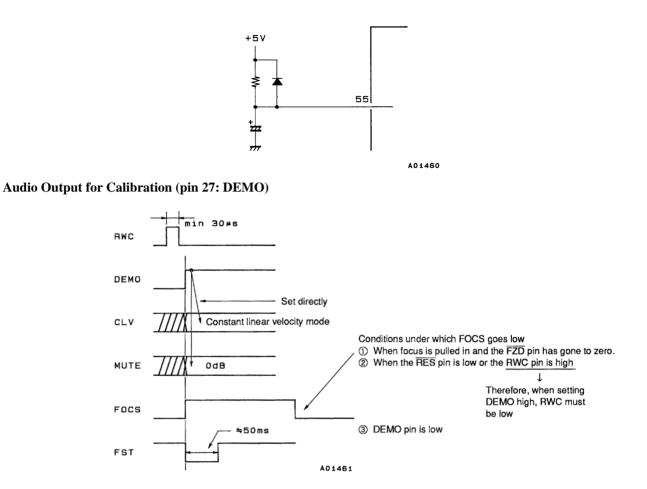

- DEMO pin for improved operability in adjustment

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

# **Package Dimensions**

unit: mm

#### 3159-QFP64E

# **Equivalent Circuit**

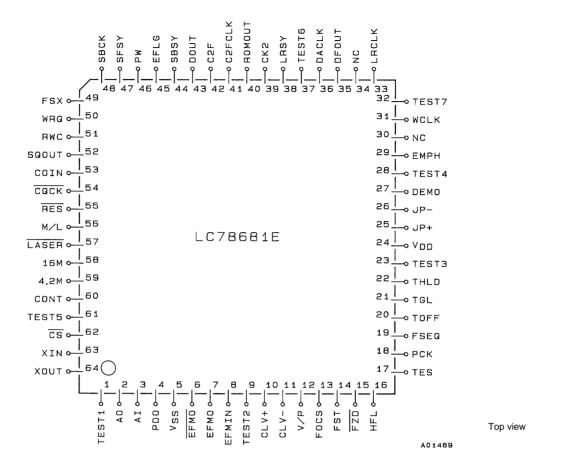

#### **Pin Assignment**

# Specifications Absolute Maximum Ratings at Ta = 25°C, $V_{SS}$ = 0 V

| Parameter                   | Symbol               | Conditions | Ratings                          | Unit |

|-----------------------------|----------------------|------------|----------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max  |            | V <sub>SS</sub> – 0.3 to 7       | V    |

| Maximum input voltage       | V <sub>IN</sub> max  |            | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ | V    |

| Maximum output voltage      | V <sub>OUT</sub> max |            | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ | V    |

| Allowable power dissipation | Pd max               |            | 300                              | mW   |

| Operating temperature       | Topr                 |            | -30 to +75                       | °C   |

| Storage temperature         | Tstg                 |            | -40 to +125                      | °C   |

# Allowable Operating Ranges at Ta = 25°C, $V_{SS}$ = 0 V

|                              |                     |                                                      |                     | Ratings |                     |      |

|------------------------------|---------------------|------------------------------------------------------|---------------------|---------|---------------------|------|

| Parameter                    | Symbol              | Conditions                                           | min                 | typ     | max                 | Unit |

| Supply voltage               | V <sub>DD</sub>     | V <sub>DD</sub>                                      | 4.5                 |         | 5.5                 | V    |

|                              | V <sub>IH</sub> (1) | TEST1 to 5, AI, FZD, HFL, DEMO, M/L,<br>RES          | 0.7 V <sub>DD</sub> |         | V <sub>DD</sub>     | V    |

| Input high level voltage     | V <sub>IH</sub> (2) | SBCK, RWC, COIN, $\overline{CQCK}$ , $\overline{CS}$ | 2.2                 |         | V <sub>DD</sub>     | V    |

|                              | V <sub>IH</sub> (3) | EFMIN                                                | 0.6 V <sub>DD</sub> |         | V <sub>DD</sub>     | V    |

|                              | V <sub>IH</sub> (4) | TES                                                  | 0.8 V <sub>DD</sub> |         | V <sub>DD</sub>     | V    |

|                              | V <sub>IL</sub> (1) | TEST1 to 5, AI, FZD, HFL, DEMO, M/L,<br>RES          | V <sub>SS</sub>     |         | 0.3 V <sub>DD</sub> | v    |

| Input low level voltage      | V <sub>IL</sub> (2) | SBCK, RWC, COIN, CQCK, CS                            | V <sub>SS</sub>     |         | 0.8                 | V    |

|                              | V <sub>IL</sub> (3) | EFMIN                                                | V <sub>SS</sub>     |         | 0.4 V <sub>DD</sub> | V    |

|                              | V <sub>IL</sub> (4) | TES                                                  | V <sub>SS</sub>     |         | 0.2 V <sub>DD</sub> | V    |

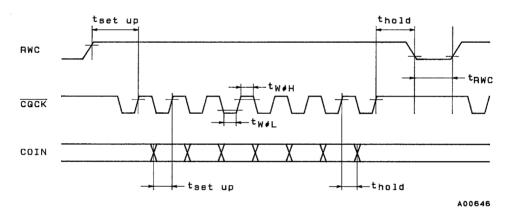

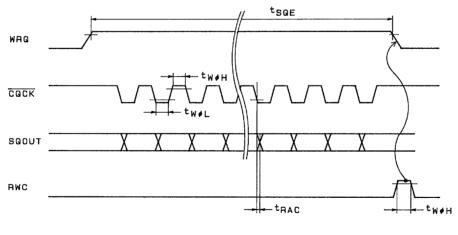

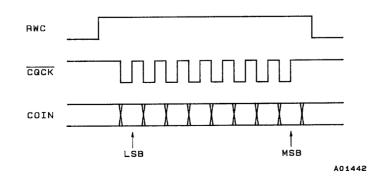

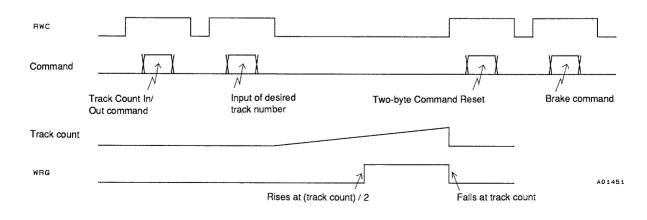

| Data setup time              | t set up            | COIN, RWC: Figure 1                                  | 400                 |         |                     | ns   |

| Data hold time               | t hold              | RWC: Figure 1                                        | 400                 |         |                     | ns   |

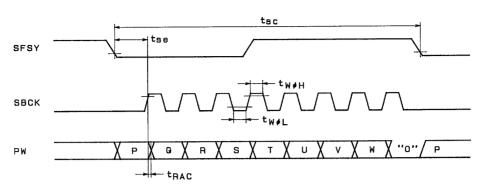

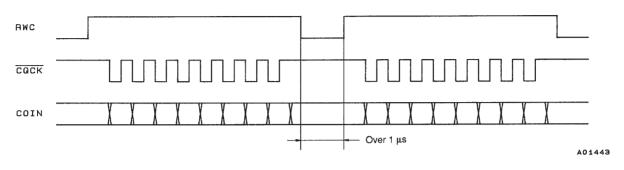

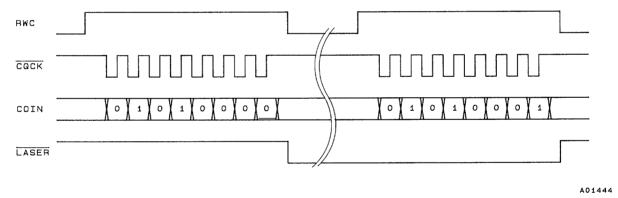

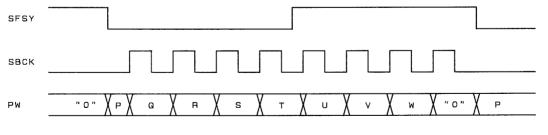

| High level clock pulse width | t <sub>WøH</sub>    | SBCK, CQCK: Figures 1, 2 and 3                       | 400                 |         |                     | ns   |

| Low level clock pulse width  | t <sub>WøL</sub>    | CQCK, SBCK: Figures 1, 2 and 3                       | 400                 |         |                     | ns   |

| Data read access time        | t <sub>RAC</sub>    | Figures 2 and 3                                      | 0                   |         | 400                 | ns   |

| Command output time          | t <sub>RWC</sub>    | RWC: Figure 1                                        | 1000                |         |                     | ns   |

| Sub-Q read enable time       | t <sub>SQE</sub>    | Figure 2, no RWC signal                              |                     | 11.2    |                     | ms   |

| Subcode read cycle           | t sc                | Figure 3                                             |                     | 136     |                     | μs   |

| Subcode read enable          | t se                | Figure 3                                             | 400                 |         |                     | ns   |

| Crystal oscillator frequency | fX'tal              | X <sub>IN</sub> , X <sub>OUT</sub>                   |                     | 16.9344 |                     | MHz  |

| 0                            | f op (1)            | AI                                                   | 2.0                 |         | 20                  | MHz  |

| Operating frequency range    | f op (2)            | EFMIN: V <sub>IN</sub> ≥ 1 Vpp                       |                     |         | 10                  | MHz  |

# Electrical Characteristics at Ta = 25°C, $V_{SS}$ = 0 V, $V_{DD}$ = 5 V

|                           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ratings               |     |     | 11-14 |

|---------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----|-------|

| Parameter                 | Symbol              | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | min                   | typ | max | Unit  |

| Current drain             | I <sub>DD</sub>     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                       | 17  | 30  | mA    |

|                           | I <sub>IH</sub> (1) | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                       |     | 5   | μA    |

| Input high level current  | I <sub>IH</sub> (2) | TEST1 to 5, DEMO, $\overline{CS}$ :<br>V <sub>IN</sub> = V <sub>DD</sub> = 5.5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25                    |     | 75  | μA    |

| Input low level current   | I <sub>IL</sub> (1) | $\begin{tabular}{l} \hline AI, EFMIN, FZD, TES, SBCK, COIN, \\ \hline CQCK, RES, HFL, RWC, M/L: V_{IN} = V_{SS} \end{tabular}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -5                    |     |     | μA    |

|                           | V <sub>OH</sub> (1) | AO, PDO, EFMO, $\overline{EFMO}$ , CLV <sup>+</sup> , CLV <sup>-</sup> ,<br>FOCS, FSEQ, PCK, TOFF, TGL, THLD,<br>JP <sup>+</sup> , JP <sup>-</sup> , EMPH, EFLG, FSX, V/P:<br>$I_{OH} = -1 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>DD</sub> – 1   |     |     | v     |

| Output high lovel veltage | V <sub>OH</sub> (2) | DOUT: I <sub>OH</sub> = -12 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>DD</sub> – 0.5 |     |     | V     |

| Output high level voltage | V <sub>OH</sub> (3) | $\label{eq:laster} \hline $$ LASER, SQOUT, 16M, 4.2M, CONT, $$ WCLK, TEST7, LRCLK, WRQ, C2F, $$ DFOUT, DACLK, SFSY, LRSY, SBSY, $$ CK2, PW, ROMOUT, C2FCLK: $$ I_{OH} = -0.5 $$ mA $$ The second se$ | V <sub>DD</sub> – 1   |     |     | v     |

Continued on next page.

Continued from preceding page.

|                            |                      | Quertal Quertitions                                                                                                                                      | Ratings |     |      |      |

|----------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|------|

| Parameter                  | Symbol               | Conditions                                                                                                                                               | min     | typ | max  | Unit |

|                            | V <sub>OL</sub> (1)  | AO, PDO, EFMO, $\overline{EFMO}$ , CLV+, CLV-,<br>FOCS, FSEQ, PCK, TOFF, TGL, THLD,<br>JP+, JP-, EMPH, EFLG, FSX, V/P:<br>$I_{OL} = 1 \text{ mA}$        |         |     | 1    | v    |

|                            | V <sub>OL</sub> (2)  | DOUT: I <sub>OL</sub> = 12 mA                                                                                                                            |         |     | 0.5  | V    |

| Output low level voltage   | V <sub>OL</sub> (3)  | LASER, SQOUT, 16M, 4.2M, CONT,<br>WCLK, TEST7, LRCLK, WRQ, DFOUT,<br>DACLK, SFSY, CK2, PW, ROMOUT,<br>C2FCLK, C2F, LRSY, SBSY:<br>I <sub>OL</sub> = 2 mA |         |     | 0.4  | v    |

|                            | V <sub>OL</sub> (4)  | FST: I <sub>OL</sub> = 5 mA                                                                                                                              |         |     | 0.75 | V    |

|                            | I <sub>OFF</sub> (1) | PDO, FST: V <sub>OH</sub> = V <sub>DD</sub>                                                                                                              |         |     | 5    | μA   |

| Output off leakage current | I <sub>OFF</sub> (2) | PDO, FST: V <sub>OL</sub> = V <sub>SS</sub>                                                                                                              | -5      |     |      | μA   |

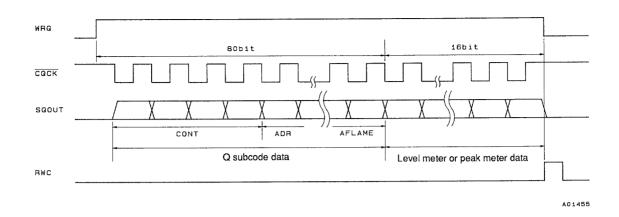

Figure 1 Command Input

A01439

Figure 2 Subcode Q Output

# LC78681E

A01629

# Figure 3 Subcode Output

# **Pin Description**

| No. | Name            | I/O | Description                                                                                                                                                                                   |

|-----|-----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | TEST1           | I   | LSI test input. Normally unconnected.                                                                                                                                                         |

| 2   | AO              | 0   |                                                                                                                                                                                               |

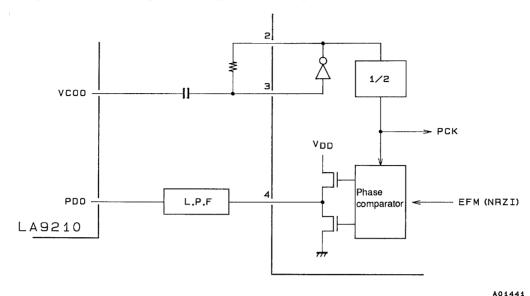

| 3   | AI              | I   | LPin for input of the on-chip VCO output from the LA9210 (8.6436 MHz). Phase detector output (PDO) is phased output with the EFM signal, set so that frequency is raised by positive voltage. |

| 4   | PDO             | 0   | ouput with the LT M signal, set so that nequency is raised by positive voltage.                                                                                                               |

| 5   | V <sub>SS</sub> | _   | GND                                                                                                                                                                                           |

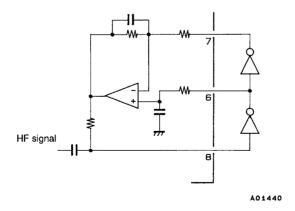

| 6   | EFMO            | 0   |                                                                                                                                                                                               |

| 7   | EFMO            | 0   | Inputs 1 to 2 V <sub>PP</sub> HF signal to EFMIN. Complementary EFM signal output is made from EFMO and EFMO via the amplitude limiter. These are used for slice level control.               |

| 8   | EFMIN           | I   |                                                                                                                                                                                               |

| 9   | TEST2           | I   | LSI test input. Normally unconnected.                                                                                                                                                         |

| 10  | CLV+            | 0   |                                                                                                                                                                                               |

| 11  | CLV-            | 0   | Disc motor control outputs.                                                                                                                                                                   |

| 12  | V/P             | 0   | Output is high with constant linear velocity rough servo, and low during phase control                                                                                                        |

| 13  | FOCS            | 0   |                                                                                                                                                                                               |

| 14  | FST             | 0   | Focus servo is switched off when FOCS is high. Lens is lowered by FST and raised gradually when FOCS is high.<br>Generation of FZD resets FOCS. Used for focus servo control.                 |

| 15  | FZD             | I   | Generation of F2D resets FOCS. Used for focus servo control.                                                                                                                                  |

| 16  | HFL             | I   | Generates kick pulse, JP+, or JP- according to track jump command. Jumps the specified number of tracks (1, 2, 4,                                                                             |

| 17  | TES             | I   | 16, 32, 64, or 128).                                                                                                                                                                          |

| 18  | PCK             | 0   | 4.3218 MHz PCK monitor output.                                                                                                                                                                |

| 19  | FSEQ            | 0   | High when SYNC (true frame sync) detected from the EFM signal matches SYNC from counter (interleaving frame sync). (Single-frame latch output.)                                               |

| 20  | TOFF            | 0   |                                                                                                                                                                                               |

| 21  | TGL             | 0   | Generates kick pulse, JP+, or JP <sup>-</sup> according to track jump command. Jumps the specified number of tracks (1, 2, 4, 16, 32, 64, or 128).                                            |

| 22  | THLD            | 0   | 10, 52, 04, 01 120).                                                                                                                                                                          |

| 23  | TEST3           | I   | LSI test input. Normally unconnected.                                                                                                                                                         |

| 24  | V <sub>DD</sub> | —   | +5 V                                                                                                                                                                                          |

| 25  | JP+             | 0   | Generates kick pulse, JP+, or JP- according to track jump command. Jumps the specified number of tracks (1, 2, 4,                                                                             |

| 26  | JP-             | 0   | 16, 32, 64, or 128).                                                                                                                                                                          |

| 27  | DEMO            | I   | Sound generation function for set adjustment.                                                                                                                                                 |

| 28  | TEST4           | I   | LSI test input. Normally unconnected.                                                                                                                                                         |

| 29  | EMPH            | 0   | Deemphasis required when high.                                                                                                                                                                |

| 30  | NC              |     | Not connected.                                                                                                                                                                                |

| 31  | WCLK            | 0   | Signal output to D/A converter. Outputs latch signal and signals for left-right switching and sample holding.                                                                                 |

| 32  | TEST7           | 0   | LSI test input. Normally unconnected.                                                                                                                                                         |

| 33  | LRCLK           | 0   | Signal output to D/A converter. Outputs latch signal and signals for left-right switching and sample holding.                                                                                 |

| 34  | NC              |     | Not connected.                                                                                                                                                                                |

| 35  | DFOUT           | 0   | Signal output to D/A convertor. Outputs latebailand and signals for left right quitabing and comple holding                                                                                   |

| 36  | DACLK           | 0   | Signal output to D/A converter. Outputs latch signal and signals for left-right switching and sample holding.                                                                                 |

| 37  | TEST6           | 0   | LSI test input. Normally unconnected.                                                                                                                                                         |

Continued on next page.

Continued from preceding page.

| No. | Name             | I/O | Description                                                                                                                                                                                                      |

|-----|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38  | LRSY             | 0   |                                                                                                                                                                                                                  |

| 39  | CK2              | 0   |                                                                                                                                                                                                                  |

| 40  | ROMOUT           | 0   | For output of CD-ROM interface signals.                                                                                                                                                                          |

| 41  | C2FCLK           | 0   |                                                                                                                                                                                                                  |

| 42  | C2F              | 0   |                                                                                                                                                                                                                  |

| 43  | DOUT             | 0   | Digital OUT output                                                                                                                                                                                               |

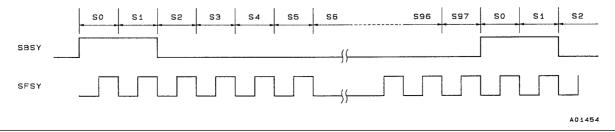

| 44  | SBSY             | 0   | Subcode block synchronization output                                                                                                                                                                             |

| 45  | EFLG             | 0   | C1 and C2 single and double error correction flag.                                                                                                                                                               |

| 46  | PW               | 0   |                                                                                                                                                                                                                  |

| 47  | SFSY             | 0   | SFSY is subcode frame synchronization signal. P, Q, R, S, T, U, V, and W subcodes are read out by sending clock eight times to SBCK.                                                                             |

| 48  | SBCK             | I   |                                                                                                                                                                                                                  |

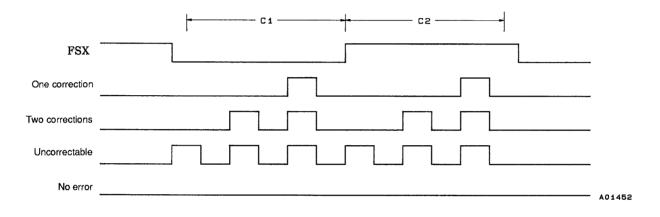

| 49  | FSX              | 0   | 7.35 kHz synchronization signal output                                                                                                                                                                           |

| 50  | WRQ              | 0   |                                                                                                                                                                                                                  |

| 51  | RWC              | I   | WRQ goes high when Q subcode data passes the CRC check. Through external connection and sending of CQCK,                                                                                                         |

| 52  | SQOUT            | 0   | data is read from SQOUT. Set MSB-first/LSB-first to low when data in LSB-first format is desired.<br>Command is generated by sending output synchronized with CQCK command data after setting microprocessor RWC |

| 53  | COIN             | I   | to high.                                                                                                                                                                                                         |

| 54  | CQCK             | I   |                                                                                                                                                                                                                  |

| 55  | RES              | I   | Set to low at powerup.                                                                                                                                                                                           |

| 56  | M/L              | I   | Same as for pins 50 to 54.                                                                                                                                                                                       |

| 57  | LASER            | 0   | Permits control via serial control from the microprocessor.                                                                                                                                                      |

| 58  | 16 M             | 0   | 16.9344 MHz output pin                                                                                                                                                                                           |

| 59  | 4.2 M            | 0   | 4.2336 MHz output pin.                                                                                                                                                                                           |

| 60  | CONT             | 0   | Permits control via serial control from the microprocessor.                                                                                                                                                      |

| 61  | TEST5            | I   | LSI test input. Normally unconnected.                                                                                                                                                                            |

| 62  | CS               | I   | Chip select pin. The LC78681 is active when this pin is low (on-chip pull-down resistor).                                                                                                                        |

| 63  | X <sub>IN</sub>  | I   | 16.9344 MHz crystal oscillator connection pins.                                                                                                                                                                  |

| 64  | X <sub>OUT</sub> | 0   |                                                                                                                                                                                                                  |

# **Functional Description**

#### HF Signal Input Circuit (pin 8: EFMIN, pin 7: EFMO and pin 6: EFMO)

An EFM signal (NRZ) sliced at the optimum level is obtained when the HF signal is input on EFMIN.

#### PLL Clock Regeneration Circuit (pin 4: PDO, pin 3: AI, and pin 2: AO)

A PLL comprising a VCO can be made with an LA9210. Output from the PDO pin goes positive when the VCO phase is lagging.

#### VCO Half-Frequency Clock (pin 18: PCK)

This pin monitors a signal generated by dividing the VCO frequency by two. This signal has an average frequency of 4.3218 MHz.

#### Frame Synchronization Detector Monitor (pin 19: FSEQ)

FSEQ is latched high for one frame when the frame sync (true synchronization signal) recovered from the EFM signal matches the sync timing generated by an internal counter.

## Servo Command Function (pin 51: RWC, pin 53: COIN, pin 54: CQCK and pin 62: CS)

Commands can be input by setting RWC high and issuing the command synchronized to the  $\overline{CQCK}$  clock from COIN.

Focus start Track jump Mute control 1-byte commands Disc motor control Other control commands Track count

2-byte command

1. 1-byte Commands

#### 2. 2-byte Commands

The commands are executed on the falling edge of RWC.

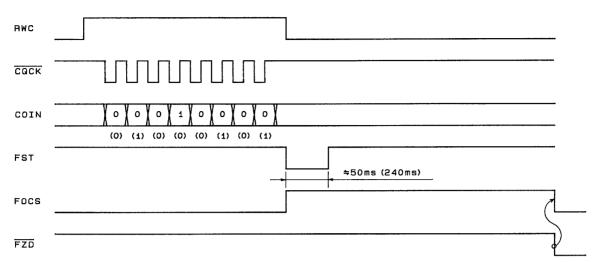

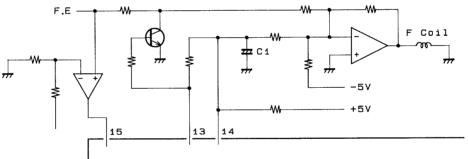

#### Focus Servocontroller (pin 13: FOCS, pin 14: FST, pin 15: FZD and pin 57: LASER)

| MSB     | LSB     | Command        | RES = low |

|---------|---------|----------------|-----------|

| 0 0 0 0 | 1 0 0 0 | FOCUS START #1 |           |

| 1 0 1 0 | 0 0 1 0 | FOCUS START #2 |           |

| 0 0 0 0 | 1 0 1 0 | LASER ON       |           |

| 1 0 0 0 | 1 0 1 0 | LASER OFF      | 0         |

| 0 0 0 0 | 0 0 0 0 | NOTHING        |           |

1. Laser Control

2. Focus Start

When a Focus Start command (either 1 or 2) is issued, the pickup lens is first lowered as C1 discharges through FST and then raised gradually as C1 is recharged by FOCS.  $\overrightarrow{FZD}$  goes low when the focal point is reached, and FOCS is reset and the focus servocontroller turned on when this signal is received.

After issuing this command, the microprocessor checks the DRF signal from the LA9210 to verify that focus has been reached, and advances to the next step. If C1 recharges fully before focus has been reached, the Focus Start command should be reissued to repeat operation of the focus servocontroller.

#### LC78681E

Note: If for Focus Start 2, the value in parentheses is in effect only when FST is low (unlike Focus Start 1).

A01445

Notes: 1. The falling edge of  $\overline{FZD}$  is not accepted when FST is low.

- 2. After a Focus Start command has been issued, the focus servocontroller is reinitialized when RWC goes high. For this reason, a new command should not be issued until the S-curve for the focus coil drive has been completed.

- 3. If focus cannot be reached (i.e., the FZD signal does not go low), the FOCS signal remains high and the lens remains raised. In this case, the Nothing command should be issued to reinitialize the servocontroller.

- 4. When the  $\overline{\text{RES}}$  pin is set low,  $\overline{\text{LASER}}$  is directly set high.

- 5. Focus start using the DEMO pin is in mode 1.

A01445

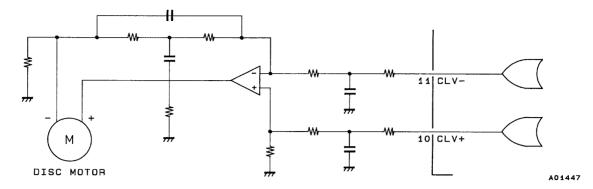

#### Constant Linear Velocity Servocontroller (pin 10: CLV+, pin 11: CLV- and pin 12: V/P)

| MSB     | LSB     | Command                       | RES = low |

|---------|---------|-------------------------------|-----------|

| 0 0 0 0 | 0 1 0 0 | DISC MOTOR START (accelerate) |           |

| 0 0 0 0 | 0 1 0 1 | DISC MOTOR CLV (CLV)          |           |

| 0 0 0 0 | 0 1 1 0 | DISC MOTOR BRAKE (decelerate) |           |

| 0 0 0 0 | 0 1 1 1 | DISC MOTOR STOP (stop)        | 0         |

The disc motor accelerates when  $CLV^+$  is high and decelerates when  $CLV^-$  is high. These outputs are selected by the motor mode commands issued by the microprocessor (accelerate, decelerate, CLV, or stop). The  $CLV^+$  and  $CLV^-$  outputs for each mode are shown in the following table.

| Mode       | CLV+ | CLV- |

|------------|------|------|

| Accelerate | High | Low  |

| Decelerate | Low  | High |

| CLV        | *    | *    |

| Stop       | Low  | Low  |

- Note: \* For constant linear velocity servo control commands, the TOFF pin is low only in the CLV mode; otherwise it is high. Control of the TOFF pin by command is effective only in the CLV mode.

- 1. CLV Mode

- In the CLV (constant linear velocity) mode, the LC78681E detects disc speed from the HF signal and switches the internal DSP mode to perform various types of control for maintaining the correct linear velocity. The pulse-width modulation cycle is 7.35 kHz, and the 1/64 duty cycle is 1.114 s. V/P outputs high during rough servo and low during phase control.

| Internal mode                   | CLV+ | CLV- | V/P  |

|---------------------------------|------|------|------|

| Rough servo (velocity too low)  | High | Low  | High |

| Rough servo (velocity too high) | Low  | High | High |

| Phase control (PLCK locked)     | PWM  | PWM  | Low  |

#### 2. CLV Control Gain Switching

| MSB     | LSB     | Command     | RES = low |

|---------|---------|-------------|-----------|

| 1 0 1 0 | 1 0 0 0 | DISC 8 set  |           |

| 1 0 1 0 | 1 0 0 1 | DISC 12 set | 0         |

CLV control gain during rough switching for 8-cm discs can be set at 8.5 dB lower than for 12-cm discs.

#### 3. Internal Brake Mode

| MSB     | LSB     | Command                | RES = low |

|---------|---------|------------------------|-----------|

| 1 1 0 0 | 0 1 0 1 | Internal brake on      |           |

| 1 1 0 0 | 0 1 0 0 | Internal brake off     | 0         |

| 1 0 1 0 | 0 0 1 1 | Internal brake control |           |

- The internal brake mode is enabled when an Internal Brake On command (C5H) is input. Executing a Brake command (06H) in this mode allows the deceleration of the disk to be monitored at the WRQ pin.

- In this mode, the EFM signal density per frame can be counted to determine the status of disc deceleration. When there are fewer than four EFM signals, CLV<sup>-</sup> falls to low, and the WRQ pin simultaneously goes high to indicate that brakes is completed. The microprocessor issues a Stop command when it senses that the WRQ pin is high, thereby completing the stopping of the disc.

| EFM signal  |    |        |

|-------------|----|--------|

| 06H command | nd |        |

| CLV+        |    |        |

| CLV-        |    |        |

| WRQ .       |    |        |

|             |    | A01448 |

- Notes: 1. When EFM signal noise results in errors in deceleration state determination, it may be advantageous to use the internal brake control command (A3H) to change the EFM signal count from four to eight.

- 2. If focus is lost during execution of an internal brake command, it is necessary to first refocus and then input the internal brake command again.

- 3. Due to the possibility of state determination errors due to the EFM signal playback state (e.g., damaged disk or access in progress) we recommend that this product be used in conjunction with a microprocessor.

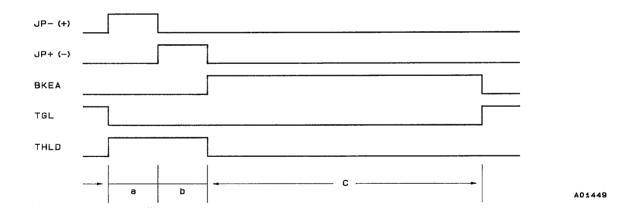

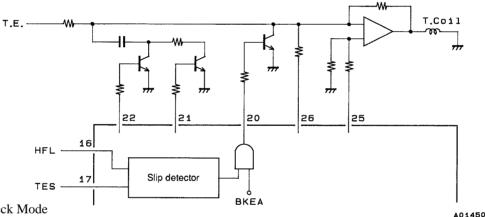

#### Track Jump Circuit (pin 16: HFL, pin 17: TES, pin 20: TOFF, pin 21: TGL, pin 22: THLD, pin 25: JP<sup>+</sup> and pin 26: JP<sup>-</sup>)

1. Internal Track Count

The following two modes are available.

| MSB     | LSB     | Command                                               | RES = low |

|---------|---------|-------------------------------------------------------|-----------|

| 0 0 1 0 | 0 0 1 0 | New track count (combination of TES and HFL)          | 0         |

| 0 0 1 0 | 0 0 1 1 | Standard track count (direct count of the TES signal) |           |

The standard track count uses the TES signal without modification as the internal track count clock. In order to reduce counting errors due to noise on the rising and falling edges of the TES signal, the new track counter suppresses this noise through combination with the HFL signal, enabling an accurate track count. However, if the HFL signal is lost because of foreign matter or scratching on the disk, no track count pulse may be generated. For this reason, caution is required when using this mode.

#### 2. Track Jump Commands

| MSB LSB         | Command             | RES = low |

|-----------------|---------------------|-----------|

| 1 0 1 0 0 0 0 0 | Standard track jump | 0         |

| 1 0 1 0 0 0 1   | New track jump      |           |

| 0 0 0 1 0 0 1   | 1 TRACK JUMP IN #1  |           |

| 0 0 0 1 0 0 1 0 | 1 TRACK JUMP IN #2  |           |

| 0 0 1 1 0 0 0 1 | 1 TRACK JUMP IN #3  |           |

| 0 0 0 1 0 0 0 0 | 2 TRACK JUMP IN     |           |

| 0 0 0 1 0 0 1 1 | 4 TRACK JUMP IN     |           |

| 0 0 0 1 0 1 0 0 | 16 TRACK JUMP IN    |           |

| 0 0 1 1 0 0 0 0 | 32 TRACK JUMP IN    |           |

| 0 0 0 1 0 1 0 1 | 64 TRACK JUMP IN    |           |

| 0 0 0 1 0 1 1 1 | 128 TRACK JUMP IN   |           |

| 0 0 0 1 1 0 0 1 | 1 TRACK JUMP OUT #1 |           |

| 0 0 0 1 1 0 1 0 | 1 TRACK JUMP OUT #2 |           |

| 0 0 1 1 1 0 0 1 | 1 TRACK JUMP OUT #3 |           |

| 0 0 0 1 1 0 0 0 | 2 TRACK JUMP OUT    |           |

| 0 0 0 1 1 0 1 1 | 4 TRACK JUMP OUT    |           |

| 0 0 0 1 1 1 0 0 | 16 TRACK JUMP OUT   |           |

| 0 0 1 1 1 0 0 0 | 32 TRACK JUMP OUT   |           |

| 0 0 0 1 1 1 0 1 | 64 TRACK JUMP OUT   |           |

| 0 0 0 1 1 1 1 1 | 128 TRACK JUMP OUT  |           |

| 0 0 0 1 0 1 1 0 | 256 TRACK CHECK     |           |

| 0 0 0 0 1 1 1 1 | TOFF                |           |

| 1 0 0 0 1 1 1 1 | TON                 | 0         |

| 1 0 0 0 1 1 0 0 | TRACK JUMP BRAKE    |           |

When a track jump command is issued to the servocontroller, an acceleration pulse is generated (a period), followed by a deceleration pulse (b period) and braking (c period), completing the specified jump. TES and HFL input during braking detects the direction of beam slippage, and the portion of the TE signal that compensates for slippage is cut off by TOFF, which, together with boosting of the servo gain by TGL, supplements the destination track for the jump.

Note: Of the disc motor control outputs, the TOFF pin is low in the CLV mode, and high in the Start Stop, and Brake modes. TOFF can also be independently switched on or off by the microprocessor. However, disc motor control is enabled only in the CLV mode.

#### 3. Track Jump Modes

The relationship between acceleration pulses, deceleration pulses, and brake periods is shown in the following table.

| Command                  | Standard track jump mode                           |                        |                | New track jump mode                               |               |                |

|--------------------------|----------------------------------------------------|------------------------|----------------|---------------------------------------------------|---------------|----------------|

| Commanu                  | а                                                  | b                      | С              | а                                                 | b             | С              |

| 1 TRACK JUMP IN (OUT) #1 | 233 µs                                             | 233 µs                 | 24 ms          | 233 µs                                            | 233 µs        | 24 ms          |

| 1 TRACK JUMP IN (OUT) #2 | 0.5-track jump                                     | 233 µs                 | 24 ms          | 0.5-track jump                                    | a period      | 24 ms          |

| 1 TRACK JUMP IN (OUT) #3 | 0.5-track jump                                     | 233 µs                 | Does not occur | 0.5-track jump                                    | a period      | Does not occur |

| 2 TRACK JUMP IN (OUT)    | Ther                                               | e are no a, b, or c pe | riods.         | 1-track jump                                      | a period      | Does not occur |

| 4 TRACK JUMP IN (OUT)    | 2-track jump                                       | 466 µs                 | 24 ms          | 2-track jump                                      | a period      | 24 ms          |

| 16 TRACK JUMP IN (OUT)   | 9-track jump                                       | 7-track jump           | 24 ms          | 9-track jump                                      | a period      | 24 ms          |

| 32 TRACK JUMP IN (OUT)   | 18-track jump                                      | 14-track jump          | 24 ms          | 18-track jump                                     | 14-track jump | 24 ms          |

| 64 TRACK JUMP IN (OUT)   | 36-track jump                                      | 28-track jump          | 24 ms          | 36-track jump                                     | 28-track jump | 24 ms          |

| 128 TRACK JUMP IN (OUT)  | 72-track jump                                      | 56-track jump          | 24 ms          | 72-track jump                                     | 56-track jump | 24 ms          |

| 256 TRACK CHECK          | TOFF goes high aft<br>jumped. The a and<br>output. |                        | 24 ms          | TOFF goes high af<br>jumped. The a and<br>output. |               | 24 ms          |

| TRACK JUMP BRAKE         | There are no a or b                                | periods.               | 24 ms          | There are no a or b                               | periods.      | 24 ms          |

Notes: 1. The actuator drive signals are not generated for the 256-track Check. Instead issuance of a feed motor signal is required because the TES signal is in the track-count mode and the tracking servocontroller is off.

2. The servocontroller register is automatically reset after one a, b, and c track jump sequence.

3. When a new track jump command is issued while a previous command is still being processed, the new command is executed immediately.

4. Track Check Mode

| MSB       | LSB   | Command              | RES = low |

|-----------|-------|----------------------|-----------|

| 1 1 1 1 0 | 0 0 0 | Track Count In       |           |

| 1 1 1 1 1 | 0 0 0 | Track Count Out      |           |

| 1 1 1 1 1 | 1 1 1 | 2-byte COMMAND RESET | 0         |

A Track Count In or Track Count Out command followed by a binary number between 16 and 256 can be used to start track counting for the specified number of tracks.

- Notes: 1. The fall of RWC when the desired number of tracks is input in binary format starts the track count.

- 2. During track counting, TOFF is high and the tracking servocontroller is turned off. For this reason, issuance of a feed motor signal is required.

- 3. The Track Count In and Track Count Out commands cause the WRQ signal to change from the Q subcode standby monitor when normal to the track count monitor. WRQ goes high at half the track count and low again at the end of the count. The microprocessor monitors WRQ to detect track count completion.

- 4. When a 2-byte Command Reset command is not issued, the track count starts again. For example, to advance 20,000 tracks, the microprocessor can set the track count number to 200 and wait 100 WRQ pulses.

- 5. The Brake command is used to bring the pickup to the track when counting is finished.

#### Error Flag Output (pin 45: EFLG and pin 49: FSX)

The 7.35 kHz FSX frame synchronization signal is divided down from the reference clock. The status of error correction in each frame is output on EFLG, as shown in the figure, where the number of high pulses in each FSX period indicates the quality of the replay signal.

#### P, Q, and R through W Subcode Output Circuit (pin 46: PW, pin 44: SBSY, pin 47: SFSY and pin 48: SBCK)

PW is the subcode signal output pin. The falling edge of SFSY starts the 136  $\mu$ s period during which SBCK is clocked eight times, allowing all codes — P, Q, and R through W — to be read. The signals appearing at the PW pin change with the rising edge of SBCK. When SBCK is static, the P code is input to PW. SFSY is the signal output for each subcode frame, and the rising edge of this signal indicates standby status for output of the subcode symbols (P through W). Subcode data P if output simultaneously with the falling edge of this signal.

A01453

SBSY is output for each subcode block. It is high during the S0 and S1 synchronization cycles. Its falling edge indicates the end of synchronization and the start of EIAJ-format data within the subcode block.

## Q Subcode Output Circuit (pin 50: WRQ, pin 51: RWC, pin 52: SQOUT, pin 54: CQCK, pin 56: M/L and pin 62: CS)

| MSB           | LSB | Command      | RES = low |

|---------------|-----|--------------|-----------|

| 0 0 0 0 1 0 0 | 0 1 | ADDRESS FREE |           |

| 1 0 0 0 1 0 0 | 0 1 | ADDRESS 1    | 0         |

Q subcode data can be read from the SQOUT pin by clocking the  $\overline{CQCK}$  pin.

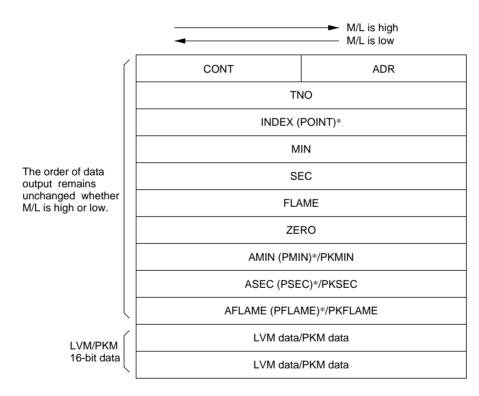

Of the 8-bit subcode data, the Q signal is effective for operations such as song access and display. WRQ is high only when the block CRC is correct and the address in the Q subcode format is 1\*. When the microprocessor senses that WRQ is high and issues  $\overline{CQCK}$ , data can be read from SQOUT in the sequence indicated below. When  $\overline{CQCK}$  is activated, the DSP disables internal register updating. When the microprocessor finishes reading data, it briefly sets RWC high to reenable data updating and resets WRC low.  $\overline{CQCK}$  should start to oscillate in the 11.2 ms period during which WRQ is high. Data can be read in LSB-first format when M/L is low and in MSB-first format when it is high.

Note: \* This condition is ignored when the Address Free command is issued. (The Address Free command is used in CD-V applications.)

Note: \* Items in parentheses are for the disc lead-in area.

- Notes: 1. The WRQ pin normally indicates Q subcode standby status, but provides different information during the Track Count mode or internal braking. (See the sections on track counting and internal braking.)

- 2. The LC78681E is active when  $\overline{CS}$  is low, with output from SQOUT. SQOUT is in the high-impedance state when the  $\overline{CS}$  pin is high.

#### Reading Level Meter (LVM) and Peak Meter (PKM) Data

| MSB     | LSB     | Command             | $\overline{RES} = low$ |

|---------|---------|---------------------|------------------------|

| 0 0 1 0 | 1 0 1 1 | PKM set (LVM reset) |                        |

| 0 0 1 0 | 1 1 0 0 | LVM set (PKM reset) | 0                      |

| 0 0 1 0 | 1 1 0 1 | PKM mask set        |                        |

| 0 0 1 0 | 1 1 1 0 | PKM mask reset      | 0                      |

#### 1. Level Meter (LVM)

- The Level Meter mode is enabled by inputting the Level Meter Set command (2CH).

- Level meter data is 16 bits, and is composed of 15 bits of absolute-value data and an MSB indicating left-right polarity. Data is for the left channel when the MSB is high and for the right channel when low.

- Level meter data is appended at the end of 80 bits of Q subcode data, and can be read from the SQOUT pin by clocking the  $\overrightarrow{CQCK}$  pin 96 times. The left and right channels are swapped each time that level meter data is read. The left and right channels are independent, and the highest value read for each of the channels is held.

- 2. Peak Meter (PKM)

- The Peak Meter mode is enabled by inputting the Peak Meter Set command (2BH).

- Peak meter data is 16 bits, and is composed of 15 bits of absolute-value data and an MSB fixed at 0. The maximum value is detected with no regard for right or left channel.

- Peak meter data is read in a manner similar to that for level meter data. However, data is not updated by further reading.

- The absolute time for Q subcode data when in the Peak Meter mode is issued while holding the absolute time (ATIME) that is detected after generation of the maximum value. (Relative time is normal operation.)

- Issuing a Peak Meter Mask Set command causes values larger than the maximum value already in memory to be ignored, even when this command is issued in the Peak Meter mode. This is canceled by the Peak Meter Mask Reset command (used in peak searches for songs in memory).

#### **Mute Control Circuit**

| MSB     | LSB     | Command     | RES = low |

|---------|---------|-------------|-----------|

| 0 0 0 0 | 0 0 0 1 | Mute 0 dB   |           |

| 0 0 0 0 | 0 0 1 0 | Mute –12 dB |           |

| 0 0 0 0 | 0 0 1 1 | Mute ∞ dB   | 0         |

Volume can be reduced by 12 dB (MUTE -12 dB) or muted fully (MUTE  $\infty$  dB) by issuing the commands shown above. Muting switches at zero crossings to prevent switching noise on the audio output. A zero crossing is judged to be any data where the upper seven bits are all 1 or all 0.

#### **Bilingual Function**

| MSB     | LSB     | Command  | RES = low |

|---------|---------|----------|-----------|

| 0 0 1 0 | 1 0 0 0 | STO CONT | 0         |

| 0 0 1 0 | 1 0 0 1 | Lch CONT |           |

| 0 0 1 0 | 1 0 1 0 | Rch CONT |           |

- The left and right channels are output to the left and right channels when reset or when the Stereo command (28H) is issued.

- Left channel data is output to both the left and right channels when the Left Channel Set command (29H) is issued.

- Right channel data is output to both the left and right channels when the Right Channel Set command (2AH) is issued.

#### Deemphasis Control (pin 29: EMPH)

The preemphasis on/off bit in the Q subcode data is output on EMPH. Deemphasis is required when EMPH is high.

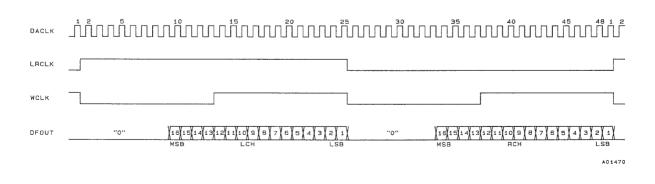

#### D/A Converter Interface (pin 31: WCLK, pin 33: LRCLK, pin 35: DFOUT and pin 36: DACLK)

D/A converter data is output in MSB-first format from DFOUT, in synchronization with the falling edge of DACLK.

| MSB LSB         | Command                  | RES = low |

|-----------------|--------------------------|-----------|

| 1 0 0 0 1 0 0 0 | CD-ROM XA                |           |

| 1 0 0 0 1 0 1 1 | CONT and CD-ROM XA Reset | 0         |

Issuing the CD-ROM XA command causes data which does not undergo interpolation or muting control to be output on DFOUT (when CD-ROM XA is supported). Because the Reset command for CD-ROM XA is common with the CONT reset on pin 60, caution is required.

• LC78681 D/A Converter Interface

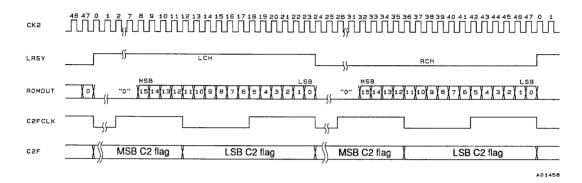

#### Output for CD-ROM (pin 39: CK2, pin 37: LRSY, pin 40: ROMOUT: pin 42: C2F and pin 41: C2FCLK)

Data from the ROMOUT pin which is synchronized with the LRSY signal is output in MSB-first format. Because this data has not been processed by either the interpolation, previous-value hold, or digital filtering circuits, it is suitable for CD-ROM IC input. CK2 is a 2.1168 MHz clock, and data is output on its rising edge. C2F flags 8-bit units of data, and is synchronized to C2FCLK.

#### LC8951 and LC78681 Interface

#### Digital Audio Out Circuit (pin 43: DOUT)

This is the output pin for the digital audio interface, with output in EIAJ format. The signal is output after interpolation and muting. This output pin has a built-in driver, and can drive a transistor directly.

| MSB     | LSB     | Command  | RES = low |

|---------|---------|----------|-----------|

| 0 1 0 0 | 0 0 1 0 | DOUT ON  | 0         |

| 0 1 0 0 | 0 0 1 1 | DOUT OFF |           |

| 0 1 0 0 | 0 0 0 0 | UBIT ON  | 0         |

| 0 1 0 0 | 0 0 0 1 | UBIT OFF |           |

- The digital out pin can be fixed low by issuing the DOUT OFF command.

- The UBIT data in the DOUT data can be fixed at 0 by issuing the UBIT OFF command.

#### Control Pin (pin 60: CONT)

| MSB     | LSB     | Command                  | RES = low |

|---------|---------|--------------------------|-----------|

| 0 0 0 0 | 1 1 1 0 | CONT set                 | Low       |

| 1 0 0 0 | 1 0 1 1 | CONT and CD-ROM XA Reset | 0         |

The CONT pin can be set high by issuing the CONT Set command.

#### Crystal Oscillator (pin 63: X<sub>IN</sub> and pin 64: X<sub>OUT</sub>)

| MSB     | LSB     | Command           | RES = low |

|---------|---------|-------------------|-----------|

| 1 0 0 0 | 1 1 1 0 | OSC ON            | 0         |

| 1 0 0 0 | 1 1 0 1 | OSC OFF           |           |

| 1 1 0 0 | 0 0 0 1 | Double-speed mode |           |

| 1 1 0 0 | 0 0 1 0 | Normal mode       | 0         |

| 0 1 1 0 | 0 0 0 0 | VCO 8 M           | 0         |

| 0 1 1 0 | 0 0 0 1 | VCO 16 M          |           |

A clock to serve as a time base can be obtained by connecting a 16.9344 MHz crystal to  $X_{IN}$  and  $X_{OUT}$ . The OSC OFF command stops oscillation of the crystal and the VCO. The double-speed mode can also be enabled through the use of commands. The relationship between the crystal and VCO is shown below.

| VCO playback speed              | Mode 8M           |                   | Mode 16M          |                   |

|---------------------------------|-------------------|-------------------|-------------------|-------------------|

|                                 | Normal speed mode | Double speed mode | Normal speed mode | Double speed mode |

| After reset                     | 0                 | _                 | _                 | _                 |

| Al pin external input (8M VCO)  | 8.6436 MHz        |                   |                   |                   |

| AI pin external input (17M VCO) |                   |                   | 17.2872 MHz       | 17.2872 MHz       |

| Al pin external input (LA9210)  | 8.6436 MHz        | 17.2872 MHz       |                   |                   |

| PCK monitor output              | 4.3218 MHz        | 8.6436 MHz        | 4.3218 MHz        | 8.6436 MHz        |

Recommended crystal oscillator constants

| Manufacturer            | Oscillator            | Cin/Cout                   |

|-------------------------|-----------------------|----------------------------|

| CITIZEN WATCH CO., LTD. | CSA-309 (16.9344 MHz) | 6 pF to 10 pF (Cin = Cout) |

#### 4.2M and 16M Pins (pin 59: 4.2M and pin 58: 16M)

Buffered 16.9344 MHz output from an externally connected 16.9344 MHz crystal is output from 16 M. It is also divided by four to generate a 4.2336 MHz clock that is output on 4.2 M. When the OSC OFF command has been issued, these outputs are held either high or low. The same frequency is generated in both normal and double-speed modes.

#### Reset Circuit (pin 55: RES)

This pin should momentarily be held low after power-on. This is set to  $-\infty$  dB for muting or to STOP for the disc motor.

| Constant linear velocity servo | START        | STOP         | BRAKE                                   | CLV |

|--------------------------------|--------------|--------------|-----------------------------------------|-----|

| Muting control                 | 0 dB         | -12 db       | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |     |

| Q subcode address conditions   | Address 1    | Address free |                                         |     |

| Laser control                  | ON (low)     | OFF (hig     | Jh)                                     |     |

| CONT                           | High         | Low          |                                         |     |

| OSC                            | ON           | OFF          |                                         |     |

| Track jump mode                | Standard New |              |                                         |     |

| Track count mode               | Standard     | New          |                                         |     |

The states shown above in boxes are set directly when  $\overline{\text{RES}}$  is low.

Setting this pin high sets muting to 0 dB and the disc motor to constant linear velocity, even when the microprocessor issues no command, and activates focusing. Because this also makes the  $\overrightarrow{LASER}$  pin active, EFM signals and audio output can be obtained without the microprocessor as long as the mechanism and servo are hooked up correctly.

#### Other Pins (pin 1: TEST1, pin 9: TEST2, pin 23: TEST4, pin 61: TEST5, pin 37: TEST6 and pin 32: TEST7)

These are test pins for the internal circuitry of the LC78681E. TEST1 through TEST5 have internal pull-down resistors. The test inputs can be left open during normal operation.

## **Description of Block Operation**

#### 1. RAM Address Control

The LC78681E incorporates an 8-bit  $\times$  2-kbyte RAM buffer, allowing address control to be used to remove from the EFM demodulation data such timing variations, or jitter, that are caused by variations in disc motor speed. The buffer can absorb up to ±4 frames of jitter. The buffer controller constantly monitors buffer free space and adjusts the CLV servocontroller divider ratio to keep the data write address in the middle of the buffer (i.e., at zero). If the ±4-frame limit is exceeded, the write address is forced to ±0, and the output is muted for 128 frames because the resulting error cannot be handled by normal error processing algorithms.

| Position   | Division ratio or processing |                |

|------------|------------------------------|----------------|

| -4 or less | Force to ±0                  |                |

| -3         | 589                          |                |

| -2         | 589                          | Increase ratio |

| -1         | 589                          |                |

| ±0         | 588                          | Standard ratio |

| +1         | 587                          |                |

| +2         | 587                          | Decrease ratio |

| +3         | 587                          |                |

| +4 or more | Force to ±0                  |                |

#### C1 and C2 Error Correction

After EFM demodulation, data is written to the internal RAM, jitter is absorbed, and the processing described below is carried out under uniform timing according to the crystal clock. First, the C1 stage involves error detection and correction, determination of the C1 flags, and writing to the C1 flag register. Next, the C2 stage involves error detection and correction, determination of the C2 flags, and writing to the internal RAM.

| C1 flag          | Error correction and flag processing |            |

|------------------|--------------------------------------|------------|

| No errors        | No correction required               | Flag reset |

| 1 error          | Correction                           | Flag reset |