## μ**PD78356**

## **16-BIT SINGLE-CHIP MICROCONTROLLER**

## HARDWARE

μ**PD78355** μ**PD78356** μ**PD78P356**

## **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

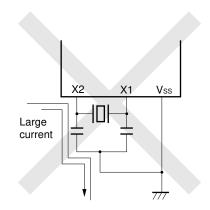

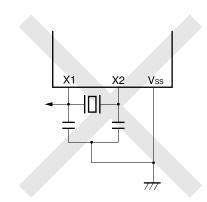

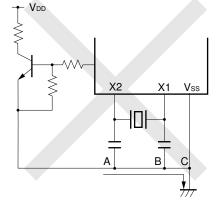

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

## **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

QTOP is a trademark of NEC Corporation. MS-DOS and Windows are trademarks of Microsoft Corporation. PC/AT and PC DOS are trademarks of IBM Corporation. SPARCstation is a trademark of SPARC International, Inc. SunOS is a trademark of Sun-Microsystems, Inc. HP9000 Series 700 and HP-UX are trademarks of Hewlett-Packard Company. NEWS and NEWS-OS are trademarks of SONY Corporation. TRON is an abbreviation of The Real-time Operating System Nucleus. ITRON is an abbreviation of Industrial TRON.

Phase-out/Discontinued

The export of these products from Japan is regulated by the Japanese government. The export of some or all of these products may be prohibited without governmental license. To export or re-export some or all of these products from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

License not needed : µPD78355/(A)/(A1)/(A2), 78P356KP-S The customer must judge the need for license : µPD78356/(A)/(A1)/(A2), 78P356GC-7EA, 78P356GD-5BB/(A)/(A1)/(A2)

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customer must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard:Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices in "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact NEC Sales Representative in advance.

Anti-radioactive design is not implemented in this product.

## Major Revisions in This Edition

| Page          | Description                                                                                                                          |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Throughout    | "The following products are under development" -> changed to "already developed" $\mu$ PD78355, 78356, 78P356, 78356 (A), 78P356 (A) |

| p. 83, 84     | CHAPTER 5 PORT FUNCTIONS<br>Addition of description of the external 8-bit bus to 5.2.3 (4) Port 9                                    |

| p. 231, 232   | CHAPTER 10 ASYNCHRONOUS SERIAL INTERFACE<br>Addition of 10.7 Transmitting/Receiving Data Using the Macro<br>Service                  |

| p. 469 to 471 | APPENDIX B TOOLS<br>Addition of description when using the integrated debugger                                                       |

The mark  $\bigstar$  shows major revised points.

## PREFACE

| Users:        | This manual is for engineers who intend to subseries for application program develop. The related products are $\mu$ PD78356 subs                                     | oment.                                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|               | <ul> <li>Standard products : μPD78355, 78356</li> <li>Special products : μPD78355 (A)<sup>Note</sup>, 78356 (A1)<sup>Note</sup>, 78356 (A2)<sup>Note</sup></li> </ul> |                                                                                                            |

|               | Note Under development                                                                                                                                                |                                                                                                            |

| Purpose:      | The purpose of this manual is to help use of the $\mu$ PD78356 subseries as listed belo                                                                               |                                                                                                            |

| Organization: | The $\mu$ PD78356 subseries manual consists and instruction.                                                                                                          | of two volumes, hardware (this manual)                                                                     |

|               | Hardware<br>Pin functions<br>Internal peripheral hardware<br>Interrupt<br>Instruction set list                                                                        | Instruction<br>CPU functions<br>Addressing<br>Instruction set list<br>Detailed explanation of instructions |

|               |                                                                                                                                                                       |                                                                                                            |

#### - CAUTIONS -

Cautions on the use of the  $\mu$  PD78356 subseries are summarized in CHAPTER 22. Read them before using the product.

For the up-to-the-minute information about this product, please contact an NEC representative.

Guidance:

Before using this manual, the user should have a general knowledge of the electronics, logical circuit, and microcontroller fields.

#### - To readers using this manual for the products other than $\mu$ PD78356

-> When there is no functional difference in the products, the manual describes only the  $\mu$ PD78356, and its descriptions are applicable to the products other than  $\mu$ PD78356 subseries.

The description of PROM is for both a one-time PROM and EPROM.

Examples in this manual are described assuming that they are used for the "Standard" quality grade of ordinary electronic equipment. If you want to apply these examples to use which requires "Special" quality grade, consider the quality grade of parts and circuits to be actually used.

| • | To check the details of a register if you know the name of the register: |

|---|--------------------------------------------------------------------------|

|   | -> Look it up in APPENDIX C.                                             |

- To understand the details of functions which you want to use: -> Look it up in APPENDIX D.

- To understand details of the instruction functions in the μPD78356 subseries:

See the separate μPD78356 User's Manual Instruction (IEU-853)<sup>Note</sup>.

- To understand the general functions of the  $\mu$ PD78356 subseries: -> Read the entire manual in the order of the table of contents.

- To know the electrical specifications in the μPD78356 subseries:

-> Refer to the Data Sheet in the separate volume.

- To know application examples of each function:

Refer to the separate Application Note.

**Note** This document number is that of Japanese version.

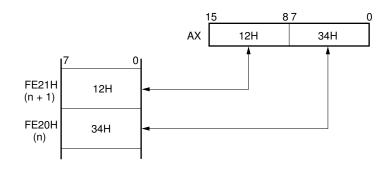

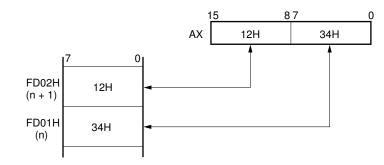

| Data weight        | : | Higher digits on the left side                      |

|--------------------|---|-----------------------------------------------------|

|                    |   | Lower digits on the right side                      |

| Active low         | : | xxxx (Pins and signal names are overscored)         |

| Memory map address | : | Low-order address on the upper side                 |

|                    |   | High-order address on the lower side                |

| Note               | : | Explanation of the indicated part of the text       |

| Caution            | : | Information requesting the user's special attention |

| Remark             | : | Supplementary information                           |

| Numeric value      | : | Binary xxxxB or xxxx                                |

|                    |   | Decimal xxxx                                        |

|                    |   | Hexadecimal xxxxH                                   |

Legend:

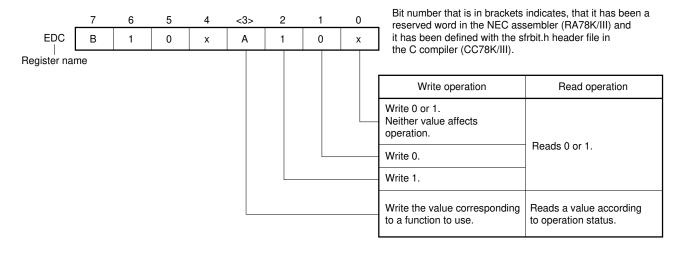

### **Register format:**

## Never write a combination of codes marked "Setting prohibited" in the register formats in the text.

Be careful when handling characters that are easily confused:

- 0 (zero), O (uppercase of o)

- 1 (one), I (lowercase of L), I (uppercase of i)

#### Related documents:

### Documents related to device

| Document Nam                                | е          | Document No.         |                      |

|---------------------------------------------|------------|----------------------|----------------------|

|                                             |            | English              | Japanese             |

| µPD78355, 78356 Data Sh                     | eet        | To be published soon | U10155J              |

| µPD78P356 Data Sheet                        |            | To be published soon | U10325J              |

| µPD78355 (A), 78356 (A) [                   | Data Sheet | Planned              | To be published soon |

| $\mu$ PD78P356 (A) Data Shee                | t          | Planned              | To be published soon |

| µPD78356 User's Manual                      | Hardware   | This manual          | U10669J              |

| Instructions                                |            | IEU-1395             | IEU-853              |

| µPD78356<br>Special Function Register Table |            | IEM-1214             | IEM-5576             |

| µPD78352A Instruction Set                   |            | —                    | IEM-5543             |

### • Documents related to development tools

| Document Nam             | e        | Docum    | ent No.  |

|--------------------------|----------|----------|----------|

|                          |          | English  | Japanese |

| IE-78350-R               | Hardware | EEU-1366 | EEU-754  |

| User's Manual            | Software | EEU-1376 | EEU-753  |

| IE-784000-R User's Manua | l        | EEU-1534 | EEU-5004 |

| IE-78355-R-EM1 User's Ma | anual    | EEU-1423 | EEU-866  |

| EP-78355GC-R User's Mai  | nual     | EEU-1508 | EEU-963  |

| EP-78355GD-R User's Mai  | nual     | EEU-1509 | EEU-964  |

Caution The above related documents are subject to change without notice. For design purpose, etc., be sure to use the latest documents.

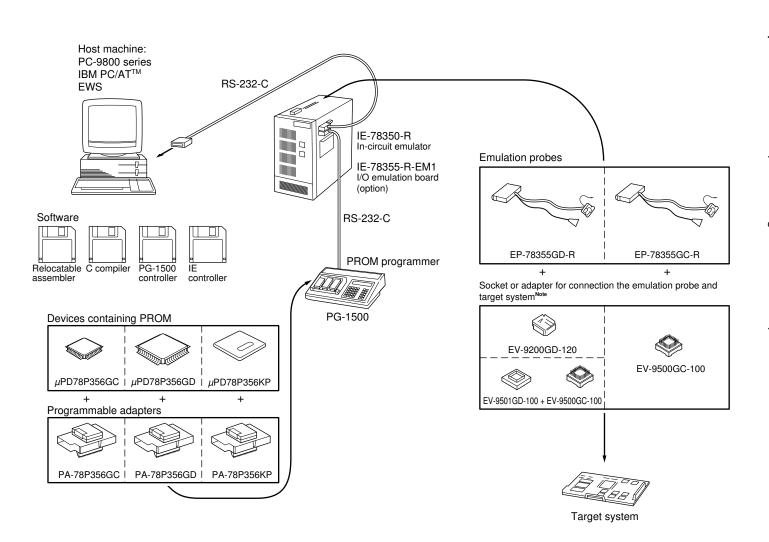

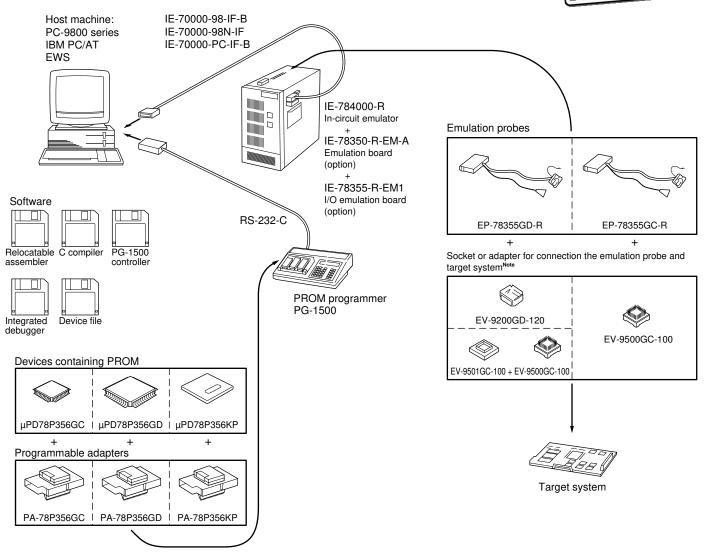

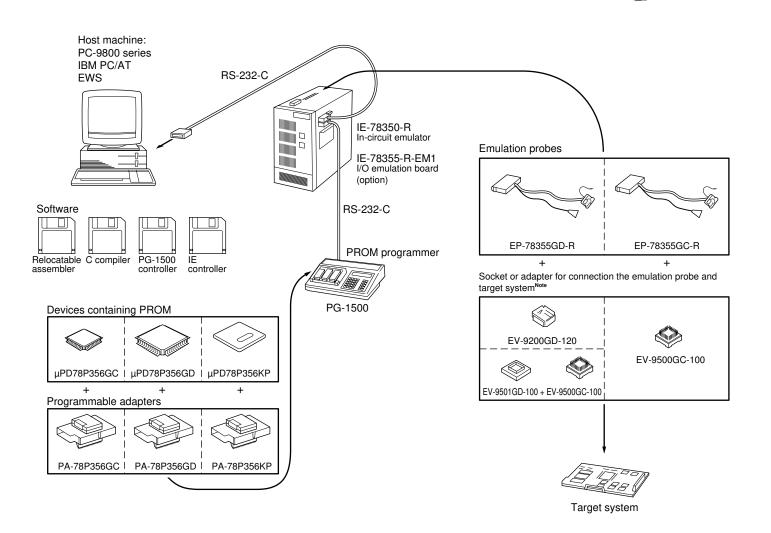

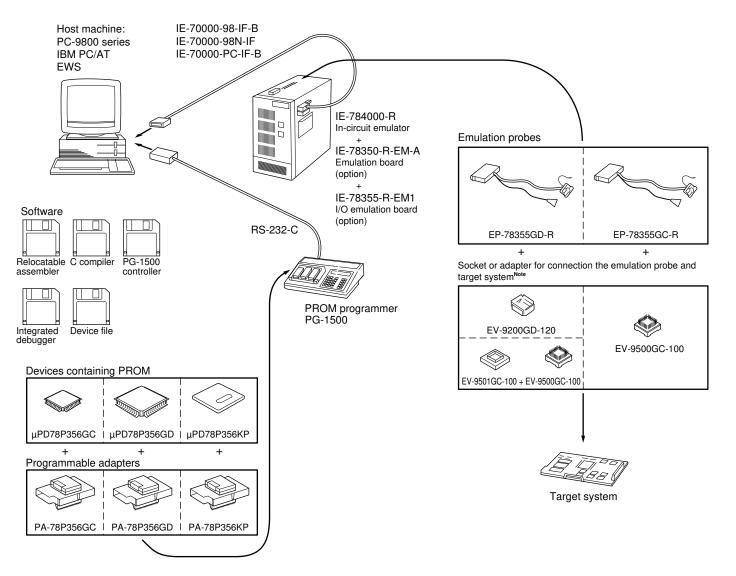

**Note** The conversion socket or the conversion adapter is supplied with the emulation probe.

Remarks 1. The PG-1500 can be directly connected to the host machine via the RS-232-C interface.2. In this figure, the distribution media for software is represented by 3.5-inch floppy disks.

2. In this figure, the host machines are represented by desk-top personal computers.

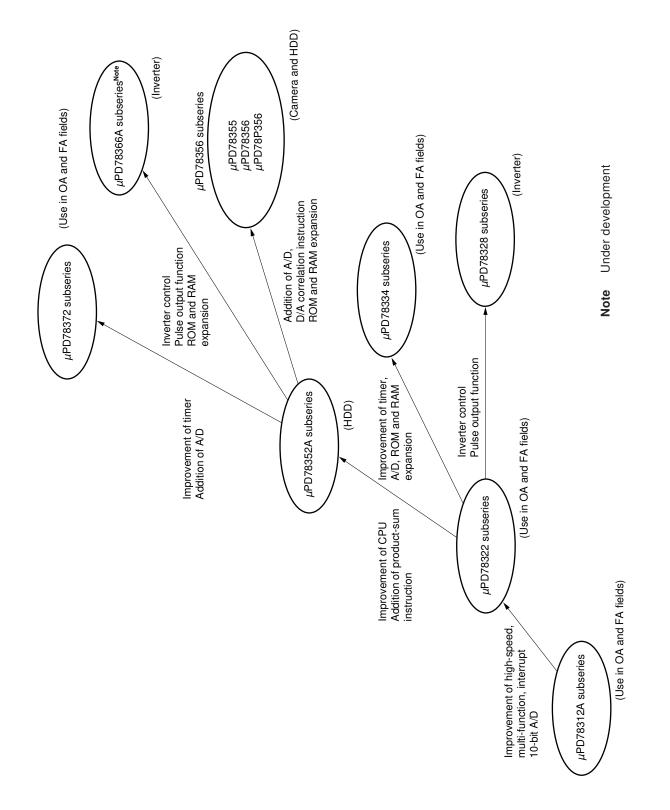

## Development of 78K/III series products

## CONTENTS

| CHAPTE | R 1 GENERAL                                                                                     | 1        |

|--------|-------------------------------------------------------------------------------------------------|----------|

| 1.1    | Features                                                                                        | 2        |

| 1.2    | Applications                                                                                    | 3        |

| 1.3    | Ordering Information and Quality Grade                                                          | 3        |

|        | 1.3.1 Standard products                                                                         | 3        |

|        | 1.3.2 Special products                                                                          | 4        |

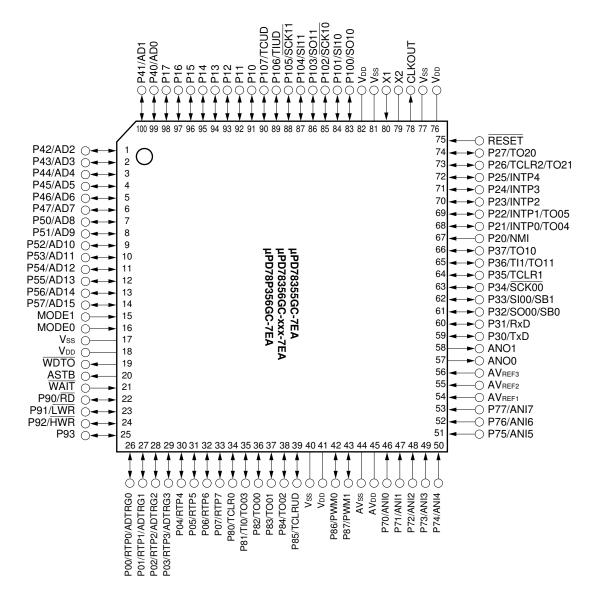

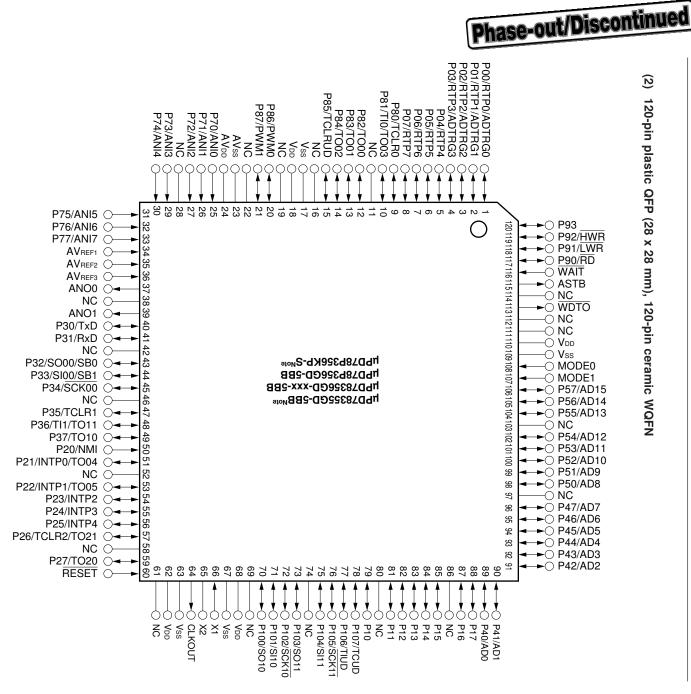

| 1.4    | Pin Configuration (Top View)                                                                    | 5        |

|        | 1.4.1 μPD78355 normal operation mode                                                            | 5        |

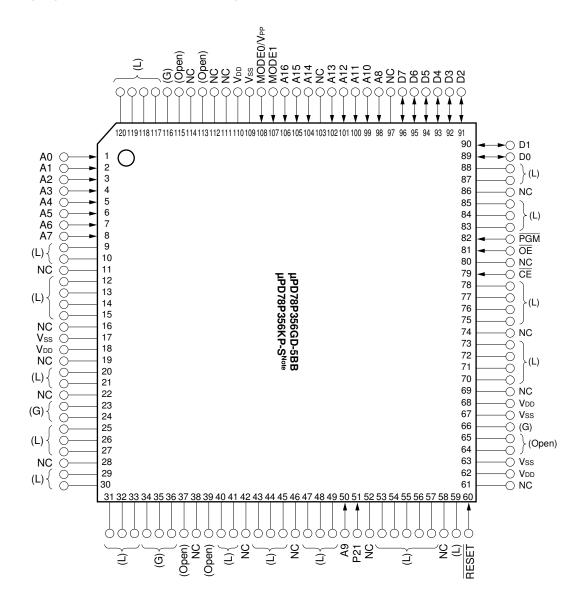

|        | 1.4.2 PROM programming mode (only $\mu$ PD78P356: MODE0/V <sub>PP</sub> = +5 V,                 |          |

|        | MODE1 = G, P21 = G, RESET = G)                                                                  | 8        |

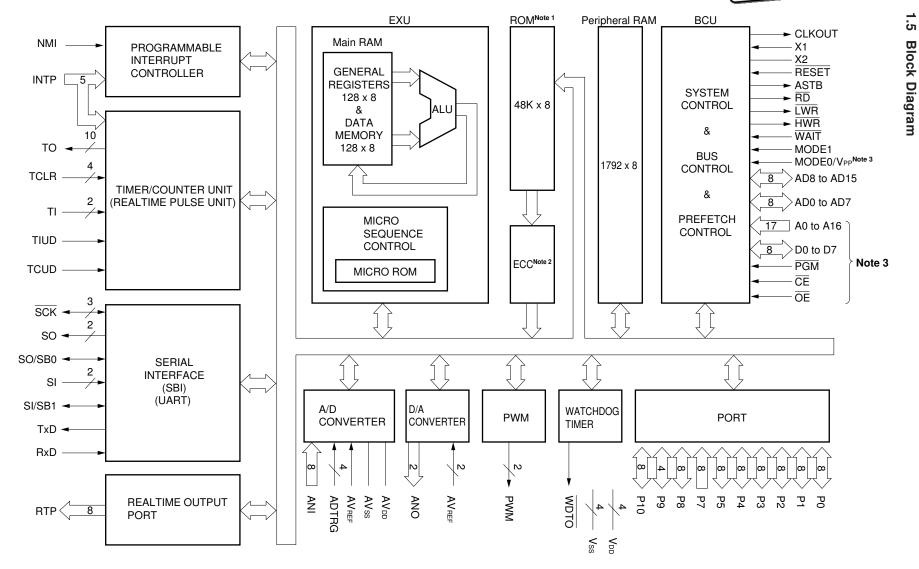

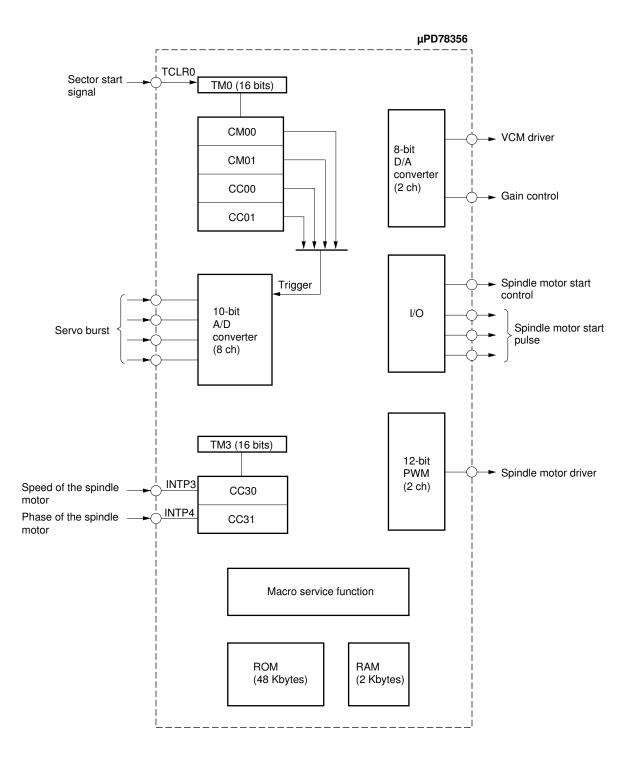

| 1.5    | Block Diagram                                                                                   | 10       |

| 1.6    | Function Overview                                                                               | 11       |

| 1.7    | Differences between the $\mu$ PD78355, $\mu$ PD78356, and $\mu$ PD78P356                        | 12       |

| 1.8    | Example of System Configuration                                                                 | 13       |

|        |                                                                                                 |          |

| CHAPTE | R 2 PIN FUNCTIONS                                                                               | 15       |

| 2.1    | List of Pin Functions                                                                           | 15       |

|        | 2.1.1 Normal operating mode                                                                     | 15       |

|        | 2.1.2 PROM programming mode                                                                     |          |

|        | (only for the $\mu$ PD78P356: MODE0/VPP = H, MODE1 = L, P21 = L, $\overline{\text{RESET}}$ = L) | 20       |

| 2.2    | Pin Functions                                                                                   | 21       |

|        | 2.2.1 Normal operation mode                                                                     | 21       |

|        | 2.2.2 PROM programming mode (only for the $\mu$ PD78P356)                                       | 31       |

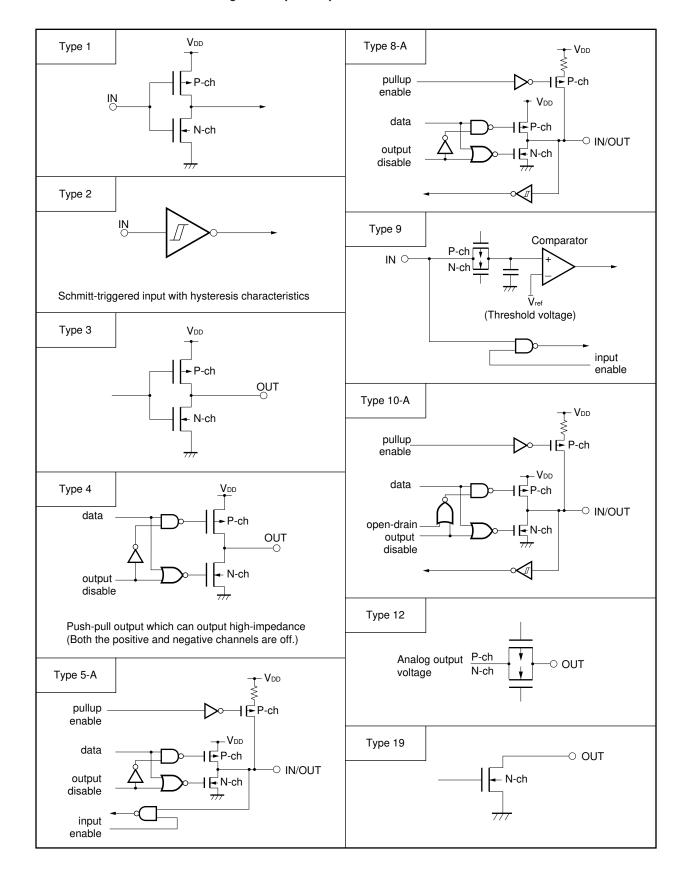

| 2.3    | Input/Output Circuits and Connection of Unused Pins                                             | 32       |

|        |                                                                                                 |          |

| CHAPTE | R 3 CPU ARCHITECTURE                                                                            | 35       |

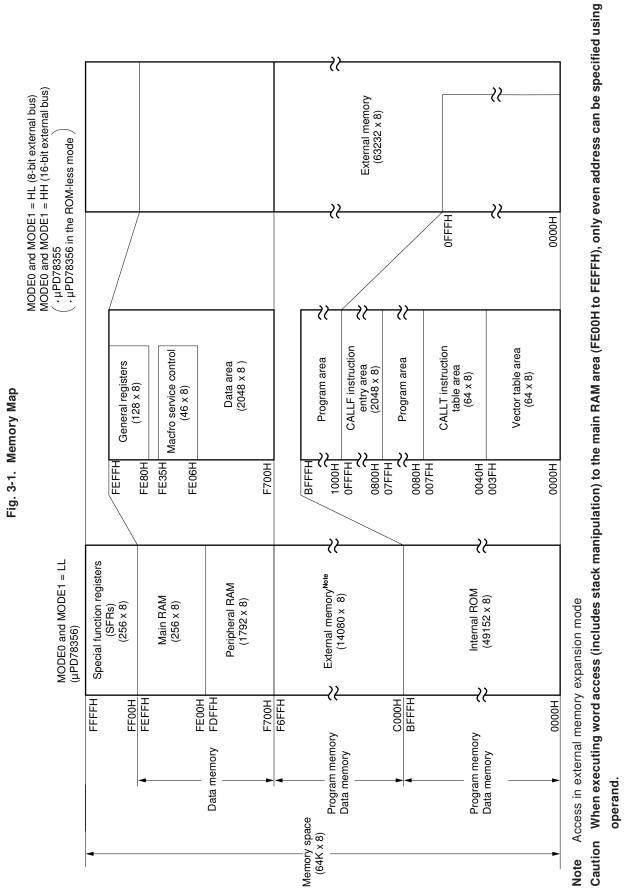

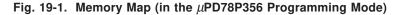

| 3.1    | Memory Space                                                                                    | 35       |

|        | 3.1.1 Vector table area                                                                         | 37       |

|        | 3.1.2 CALLT instruction table area                                                              | 38       |

|        | 3.1.3 CALLF instruction entry area                                                              | 38       |

|        | 3.1.4 Internal RAM area                                                                         | 38       |

|        | 3.1.5 Special function register area                                                            | 43       |

|        | 3.1.6 External memory area                                                                      | 43       |

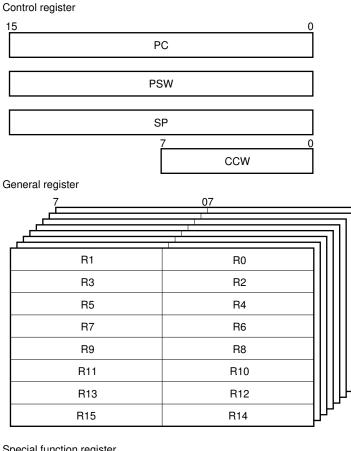

| 3.2    | Processor Registers                                                                             | 44       |

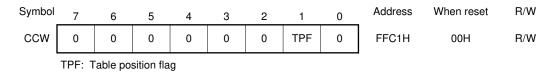

|        | 3.2.1 Control registers                                                                         | 45       |

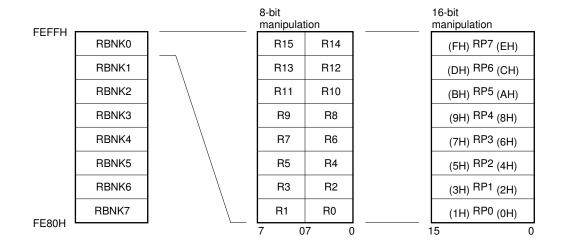

|        | 3.2.2 General registers                                                                         | 51       |

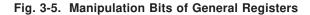

|        | 3.2.3 Special function registers (SFRs)                                                         | 53       |

| 3.3    | Data Memory Addressing                                                                          | 61       |

|        | 3.3.1 General-register addressing                                                               | 62       |

|        | 3.3.2 Short direct addressing                                                                   | 63       |

|        | 3.3.3 Special function register (SFR) addressing                                                | 63       |

| CHADTE | R 4 SUMMARY OF BLOCK FUNCTION                                                                   | 65       |

| 4.1    | Execution Unit                                                                                  | 65<br>65 |

| 4.1    | Bus Control Unit                                                                                | 65       |

| 7.6    |                                                                                                 |          |

|    | 4.3   | Progra                | m Memory and Data Memory                                 | 65                |  |  |  |

|----|-------|-----------------------|----------------------------------------------------------|-------------------|--|--|--|

|    | 4.4   | Ports                 |                                                          |                   |  |  |  |

|    | 4.5   | Real-Time Pulse Unit  |                                                          |                   |  |  |  |

|    | 4.6   | Real-Time Output Port |                                                          |                   |  |  |  |

|    | 4.7   | A/D Converter         |                                                          |                   |  |  |  |

|    | 4.8   | D/A Converter         |                                                          |                   |  |  |  |

|    | 4.9   | Serial                | Interfaces                                               | 67                |  |  |  |

|    | 4.10  | PWM C                 | Dutput Unit                                              | 67                |  |  |  |

|    | 4.11  | Watch                 | dog Timer                                                | 67                |  |  |  |

|    | 4.12  | Interru               | pt Controller                                            | 67                |  |  |  |

| ~  |       |                       |                                                          |                   |  |  |  |

| CH |       |                       | RT FUNCTIONS                                             | 69                |  |  |  |

|    | 5.1   |                       | are Configuration                                        | 69<br>77          |  |  |  |

|    | 5.2   |                       | ons of the Ports                                         | 77                |  |  |  |

|    |       | 5.2.1                 | I/O port functions and alternate functions               | 78                |  |  |  |

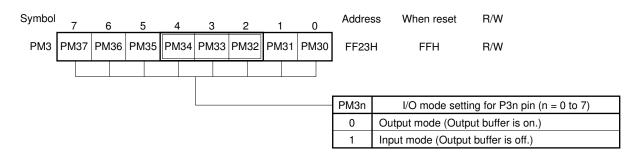

|    |       | 5.2.2                 | I/O mode setting                                         | 79                |  |  |  |

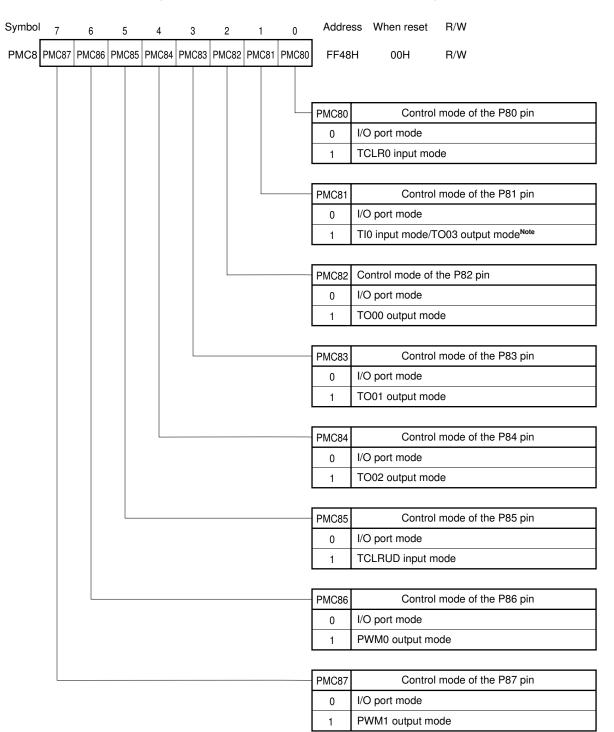

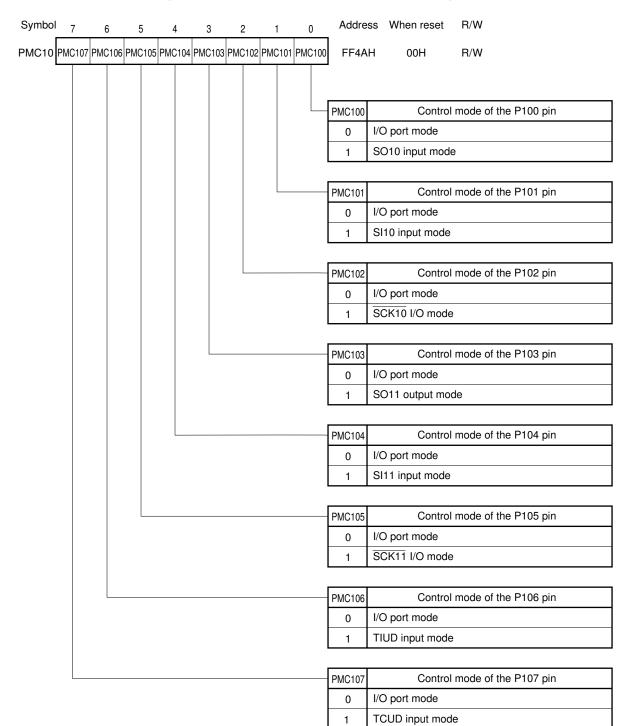

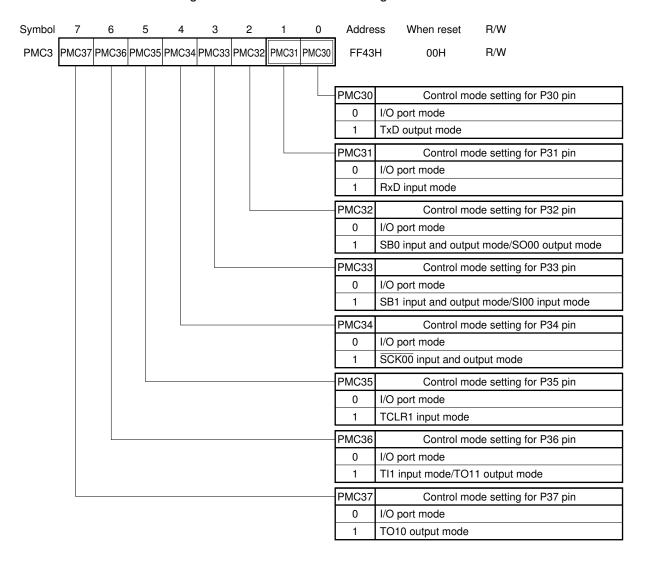

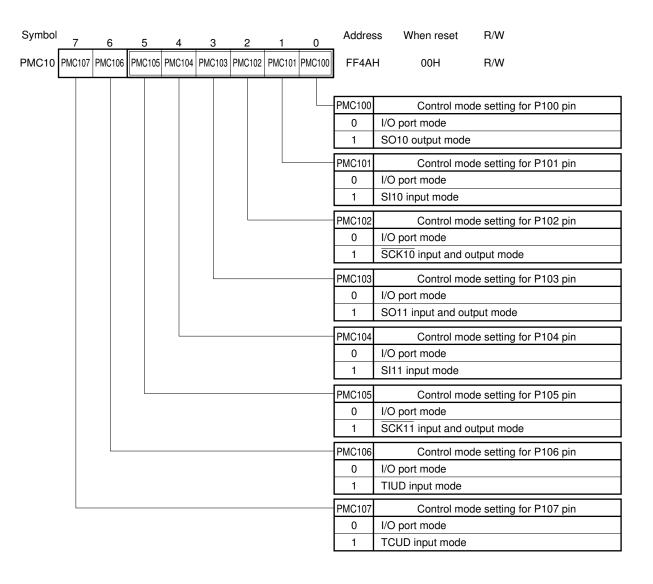

|    |       | 5.2.3                 | Control mode setting                                     | 82                |  |  |  |

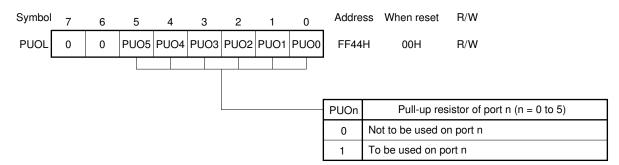

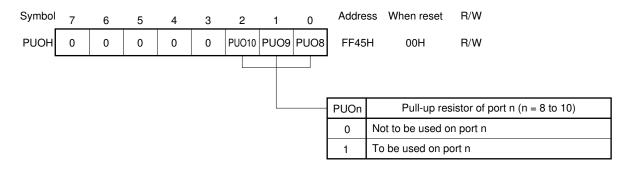

|    |       | 5.2.4                 | Pull-up resistor specification                           | 90                |  |  |  |

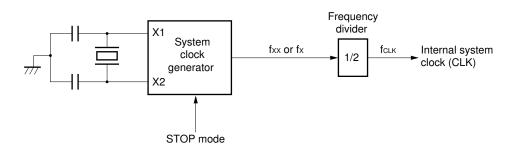

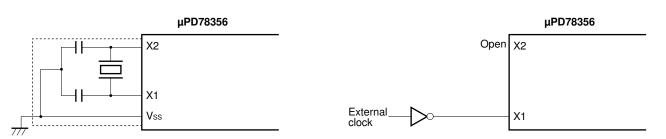

| СН | APTER | 6 CLC                 | OCK GENERATOR                                            | 93                |  |  |  |

|    |       |                       |                                                          |                   |  |  |  |

| CH |       |                       | AL-TIME PULSE UNIT (RPU)                                 | 97                |  |  |  |

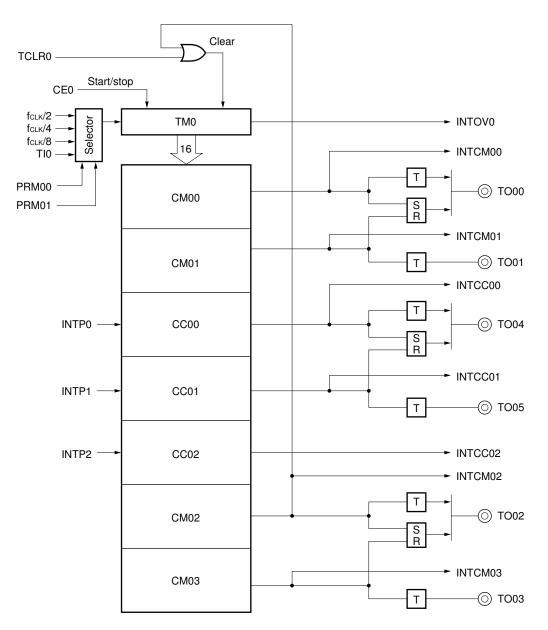

|    | 7.1   | •                     | uration                                                  | 98                |  |  |  |

|    |       | 7.1.1                 | TM0                                                      | 102               |  |  |  |

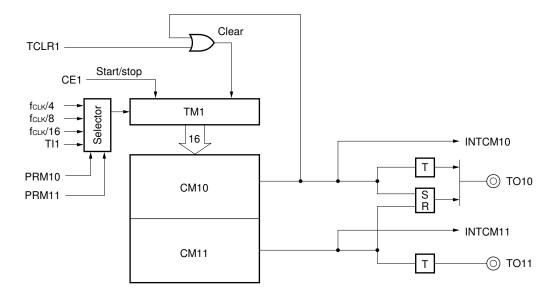

|    |       | 7.1.2                 | TM1                                                      | 102               |  |  |  |

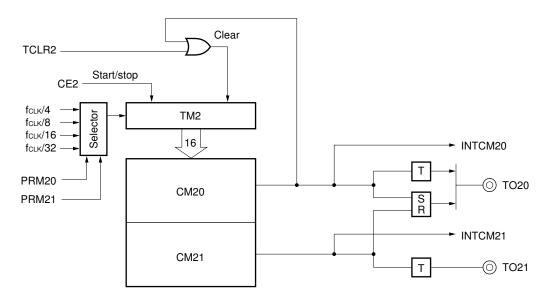

|    |       | 7.1.3                 | TM2                                                      | 102               |  |  |  |

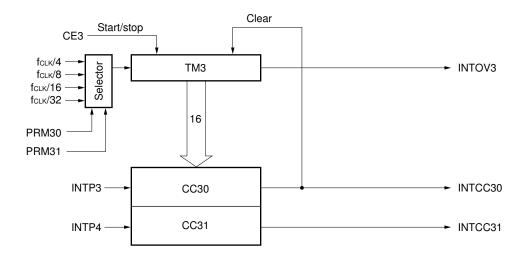

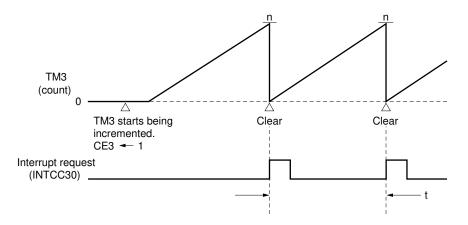

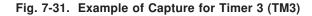

|    |       | 7.1.4                 | TM3                                                      | 103               |  |  |  |

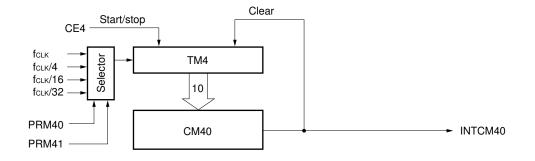

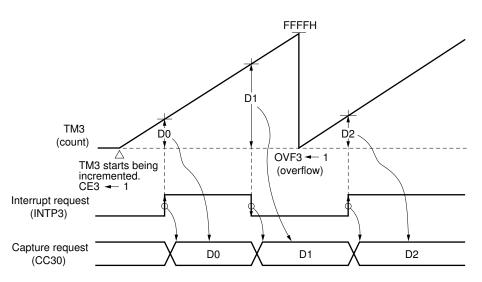

|    |       | 7.1.5<br>7.1.6        | TM4                                                      | 103               |  |  |  |

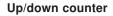

|    |       |                       | UDC                                                      | 103               |  |  |  |

|    |       | 7.1.7                 | Compare registers                                        | 104               |  |  |  |

|    | 7.2   | 7.1.8                 | Capture/compare registers (CC00 to CC02, CC30, and CC31) | 105<br><b>106</b> |  |  |  |

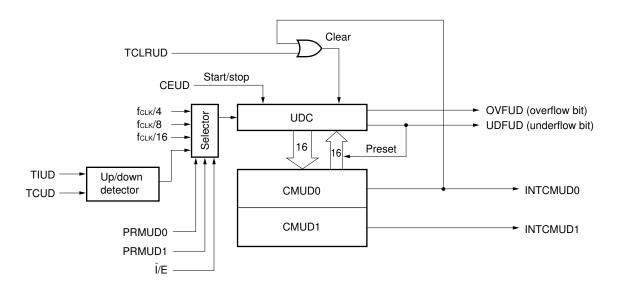

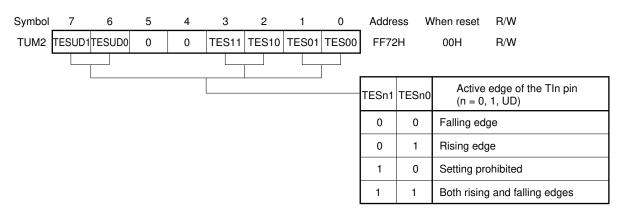

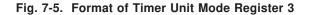

|    | 1.2   | 7.2.1                 | Timer unit mode registers (TUM0 to TUM3)                 | 106               |  |  |  |

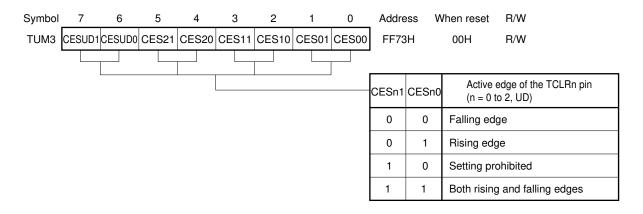

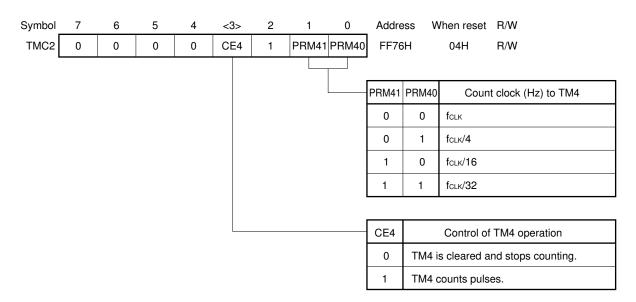

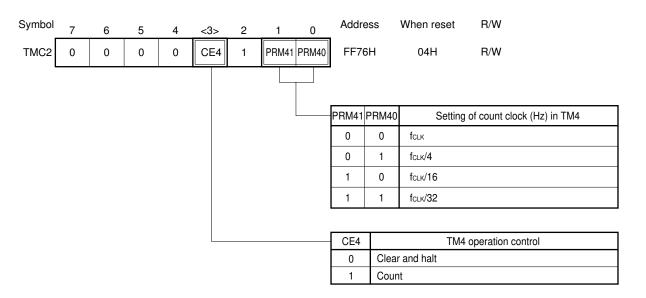

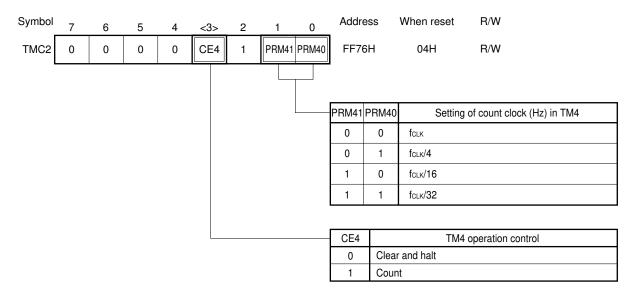

|    |       | 7.2.1                 | Timer Control Registers (TMC0 to TMC2 and the UDCC)      | 100               |  |  |  |

|    |       | 7.2.2                 | Timer output control registers (TOC0 to TOC2)            | 114               |  |  |  |

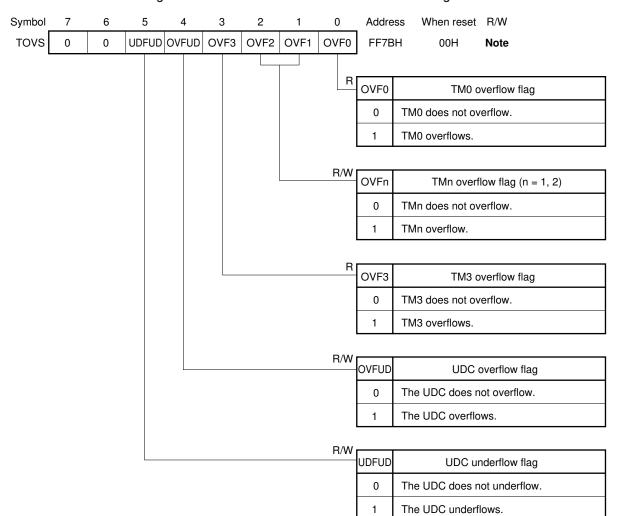

|    |       | 7.2.4                 | Timer overflow status register (TOVS)                    | 119               |  |  |  |

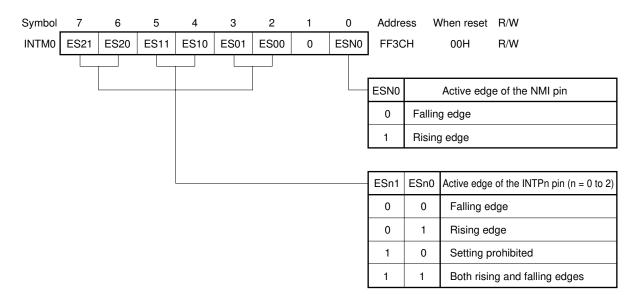

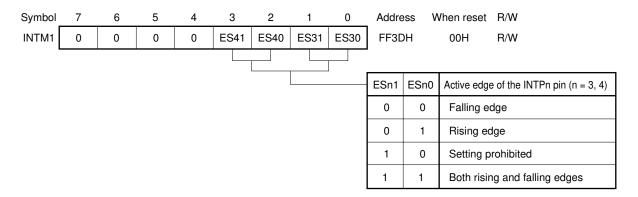

|    |       | 7.2.4                 | External interrupt mode registers (INTM0 and INTM1)      | 121               |  |  |  |

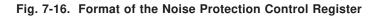

|    |       | 7.2.6                 | Noise protection control register (NPC)                  | 123               |  |  |  |

|    | 7.3   |                       | ion                                                      | 124               |  |  |  |

|    | 110   | 7.3.1                 | Timer 0 (TM0)                                            | 124               |  |  |  |

|    |       | 7.3.2                 | Timer 1 (TM1)                                            | 130               |  |  |  |

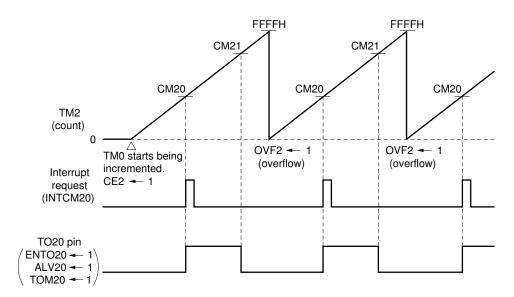

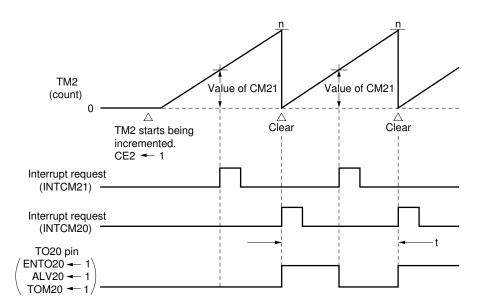

|    |       | 7.3.3                 | Timer 2 (TM2)                                            | 134               |  |  |  |

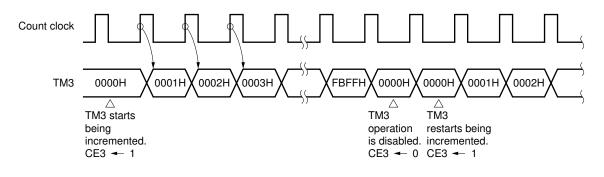

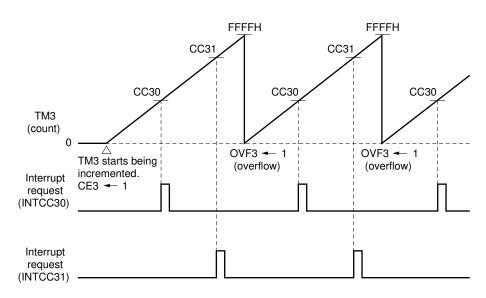

|    |       | 7.3.4                 | Timer 3 (TM3)                                            | 138               |  |  |  |

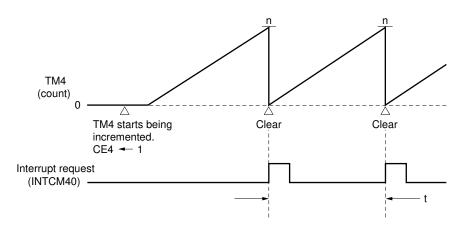

|    |       | 7.3.5                 | Timer 4 (TM4)                                            | 142               |  |  |  |

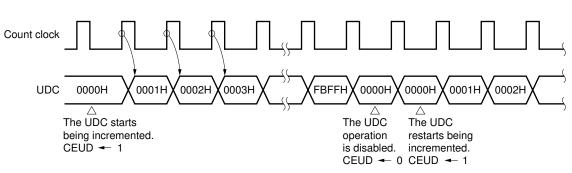

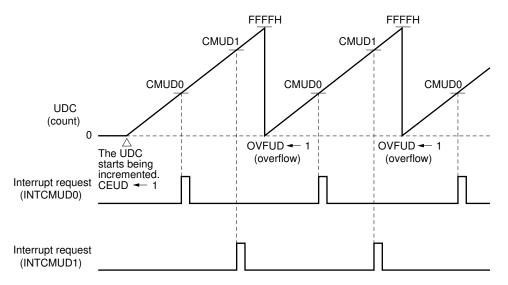

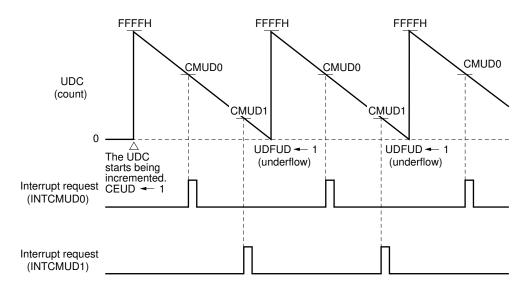

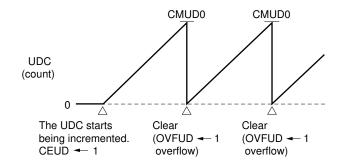

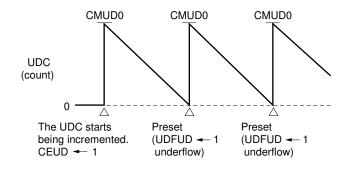

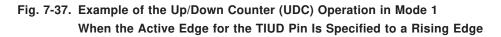

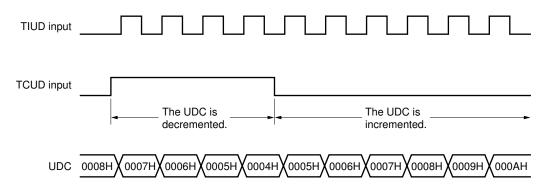

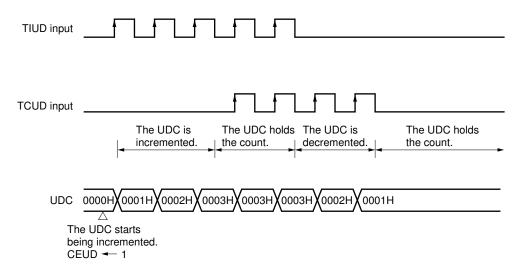

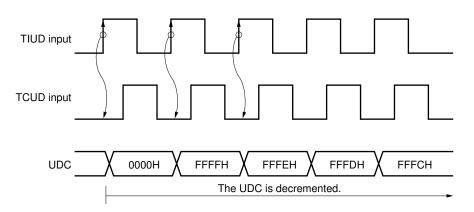

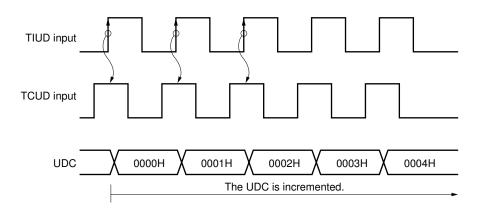

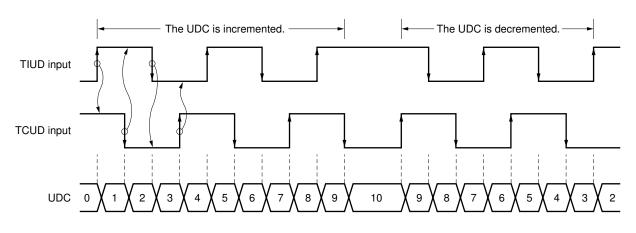

|    |       | 7.3.6                 | Up/down counter (UDC)                                    | 144               |  |  |  |

|    | 7.4   |                       | Output Function                                          | 152               |  |  |  |

|    | 7.5   |                       | ime Output Function                                      | 155               |  |  |  |

|    |       |                       | •                                                        |                   |  |  |  |

|              | 7.5.1            | Configuration                                                                    | 155 |

|--------------|------------------|----------------------------------------------------------------------------------|-----|

|              | 7.5.2            | Control registers                                                                | 156 |

|              | 7.5.3            | Operation                                                                        | 158 |

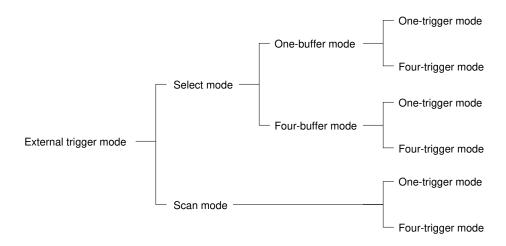

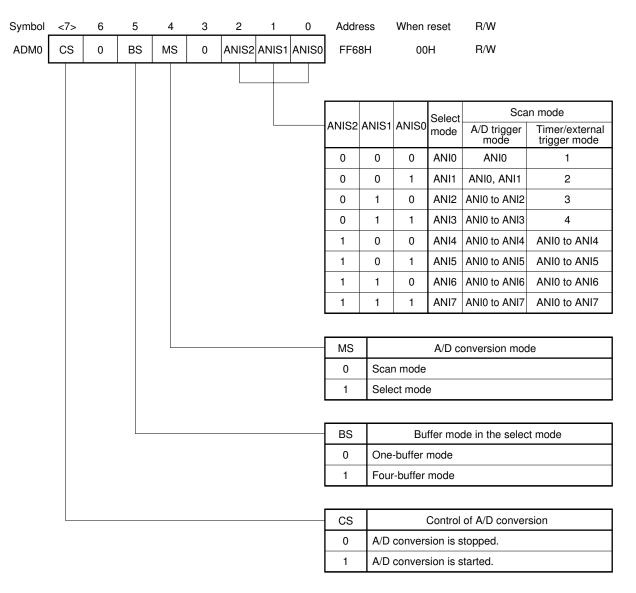

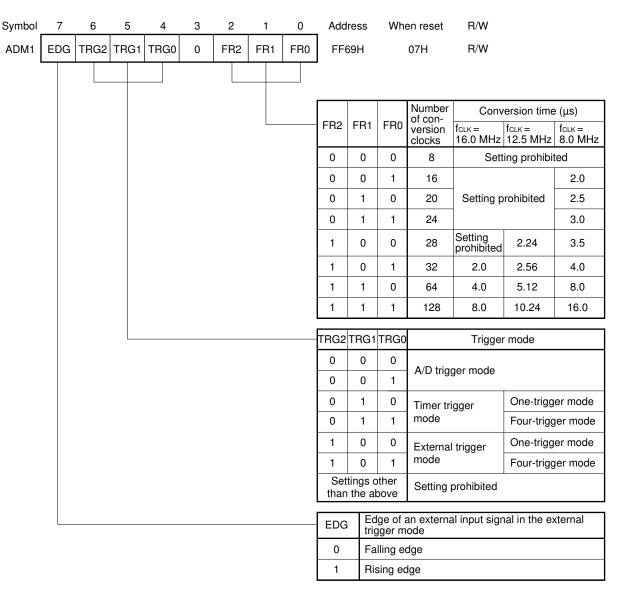

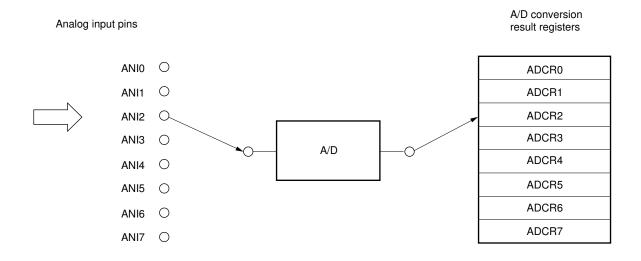

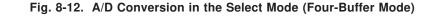

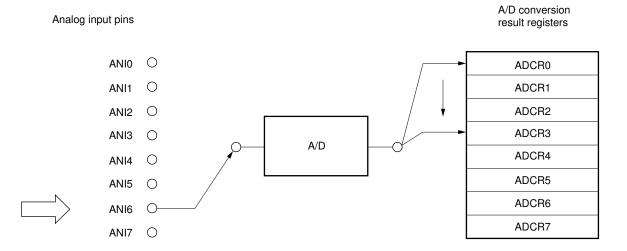

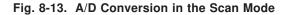

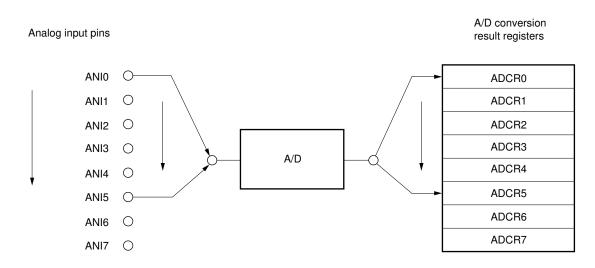

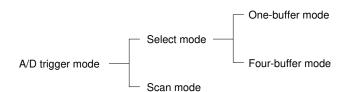

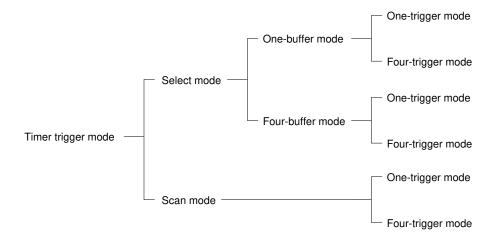

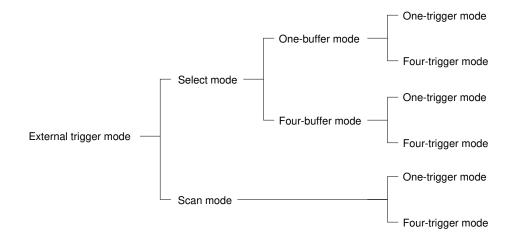

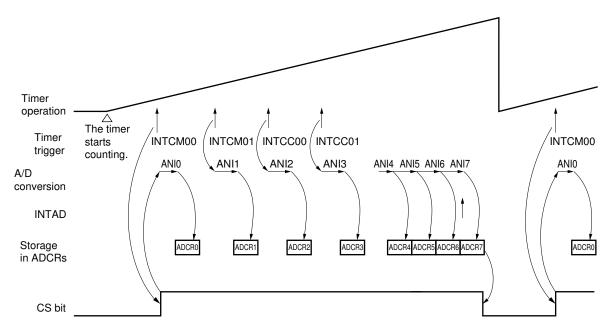

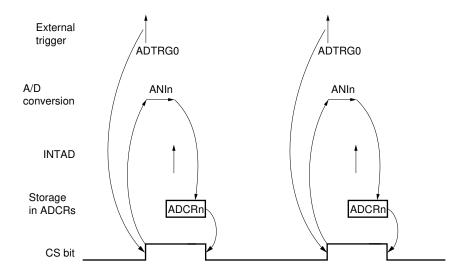

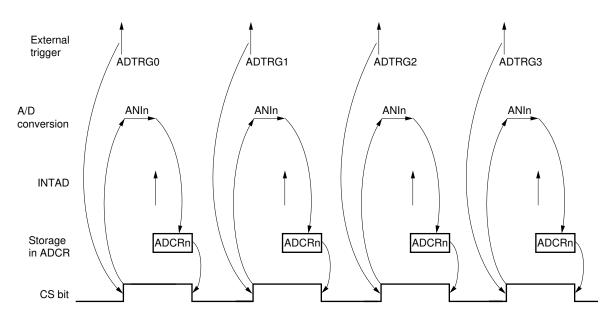

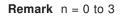

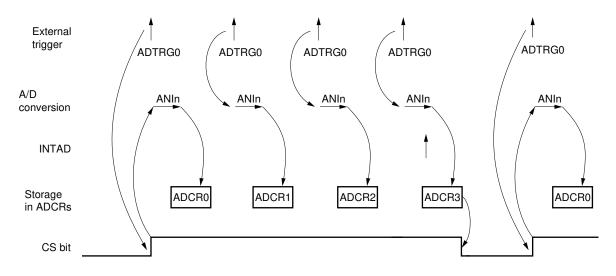

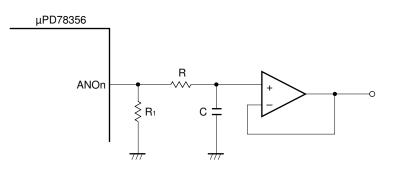

| CHAPTE       | R8 A/D           | CONVERTER                                                                        | 159 |

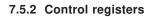

| 8.1          |                  | juration                                                                         |     |

| 8.2          |                  | onverter Mode Register 0 (ADM0)                                                  |     |

| 8.3          |                  | onverter Mode Register 1 (ADM1)                                                  |     |

| 8.4          |                  | onversion Result Registers (ADCRs)                                               |     |

| 8.5          |                  | tion                                                                             |     |

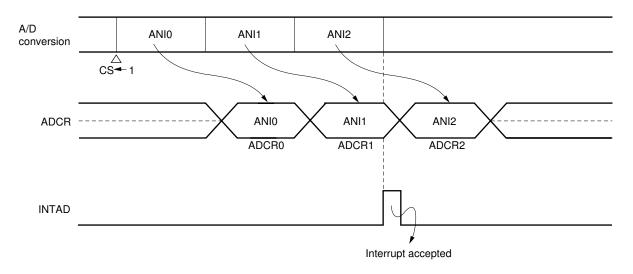

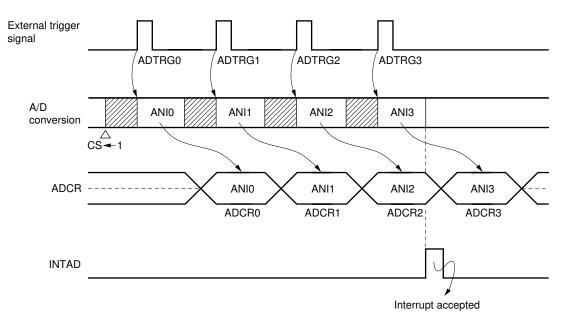

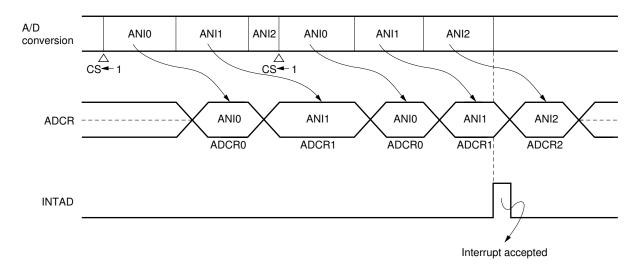

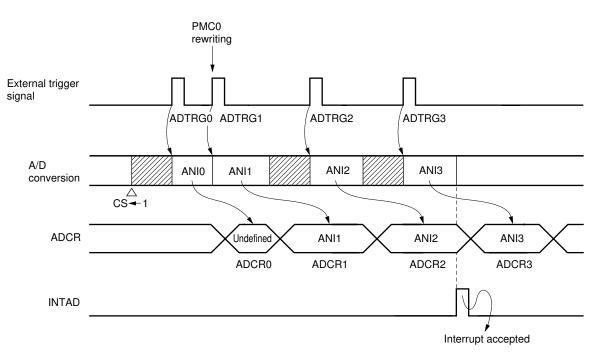

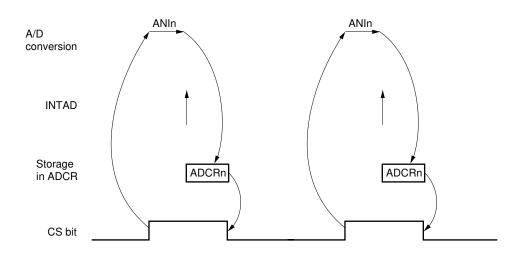

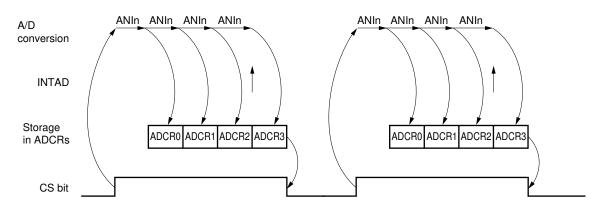

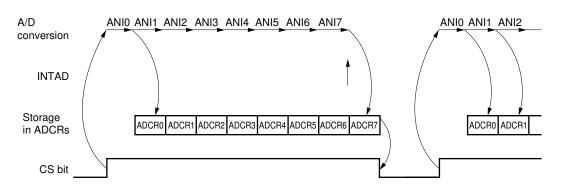

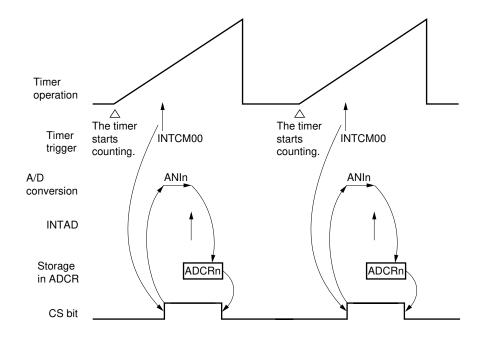

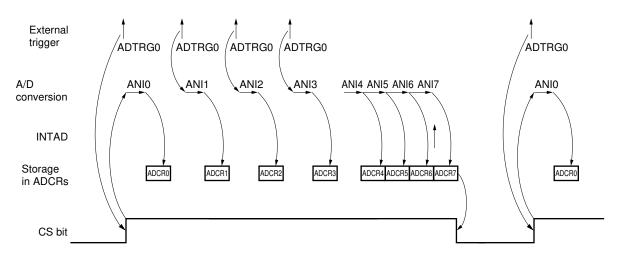

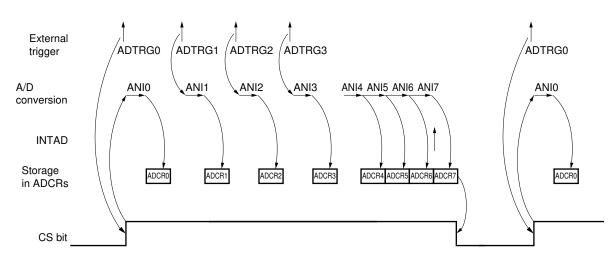

| 0.5          | 8.5.1            | Basic operation of the A/D converter                                             |     |

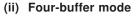

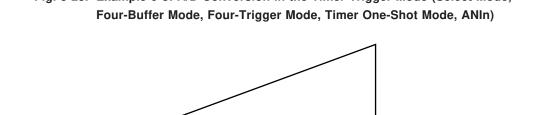

|              | 8.5.2            | Operating mode for the A/D converter                                             |     |

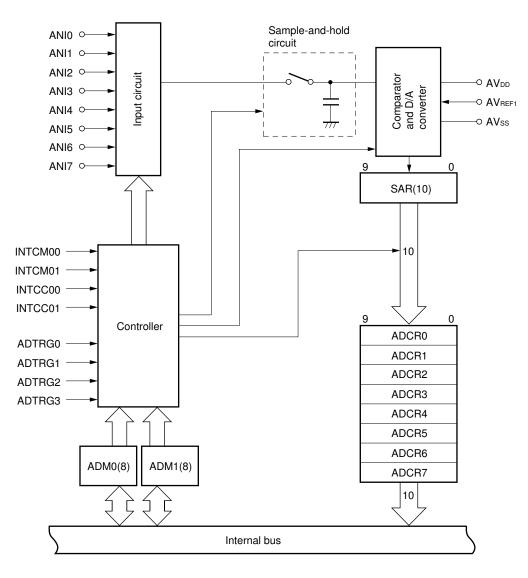

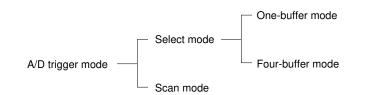

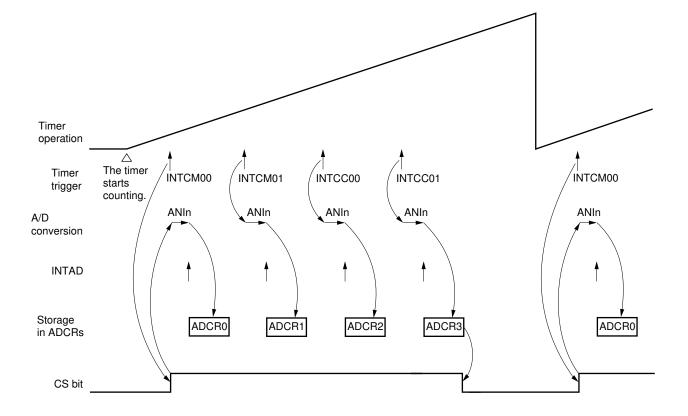

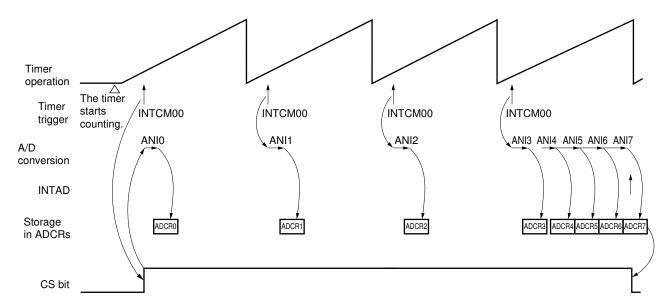

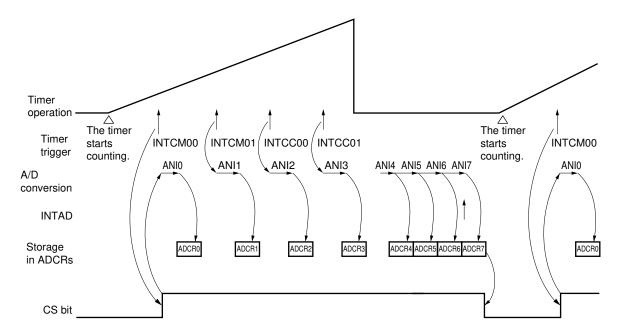

|              | 8.5.3            | Trigger modes for the A/D converter                                              |     |

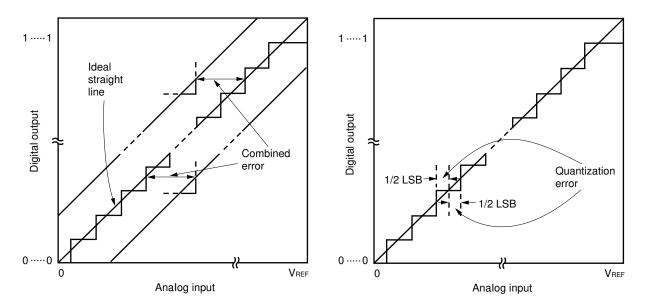

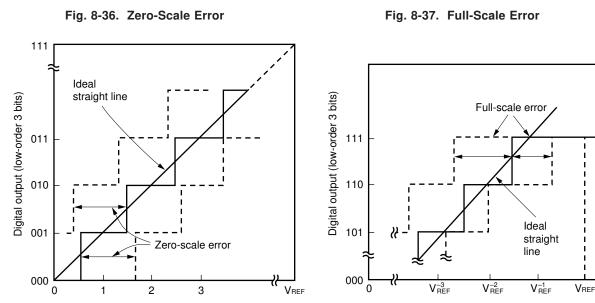

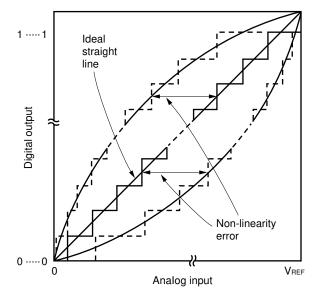

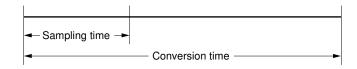

| 8.6          |                  | ary for A/D Converter Characteristics Graphs                                     |     |

|              |                  |                                                                                  |     |

|              |                  |                                                                                  |     |

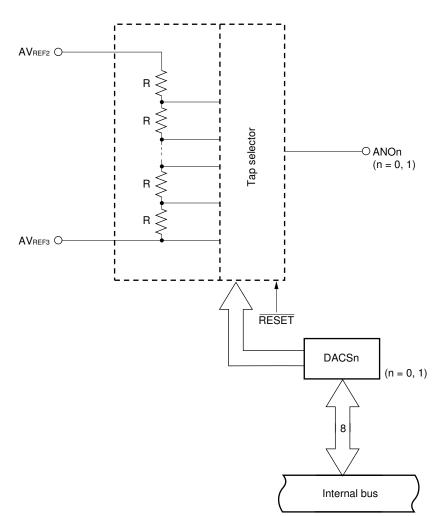

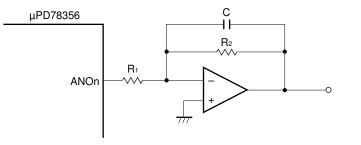

| 9.1          | -                | juration                                                                         |     |

| 9.2          | •                | tion of the D/A Converters<br>ons                                                |     |

| 9.3          | Cautio           | ns                                                                               | 211 |

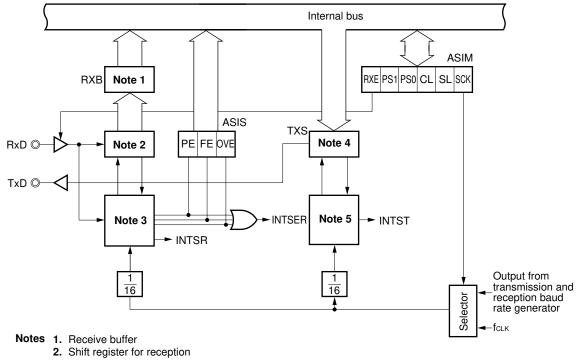

| СНАРТЕ       | R 10 AS          | SYNCHRONOUS SERIAL INTERFACE                                                     | 213 |

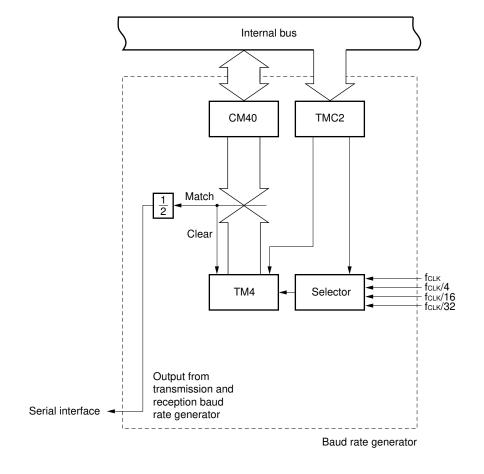

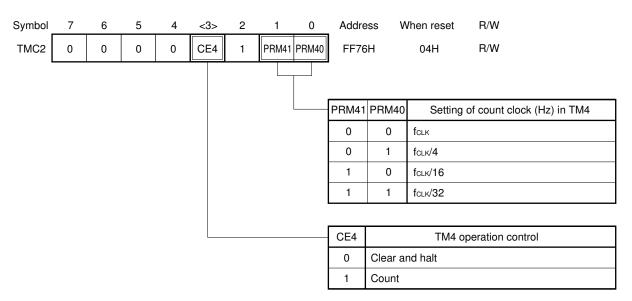

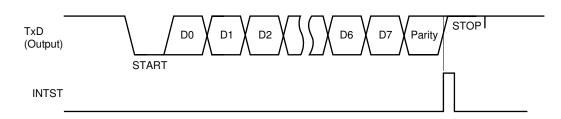

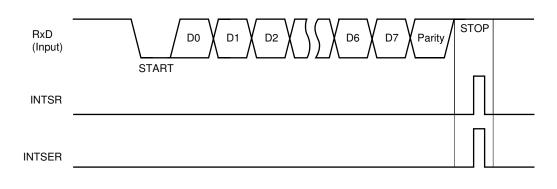

| 10.1         | Config           | juration of Asynchronous Serial Interface                                        | 214 |

| 10.2         | Setting          | g Pins for Serial Transmission                                                   | 216 |

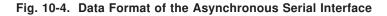

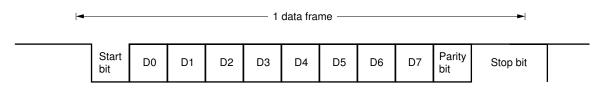

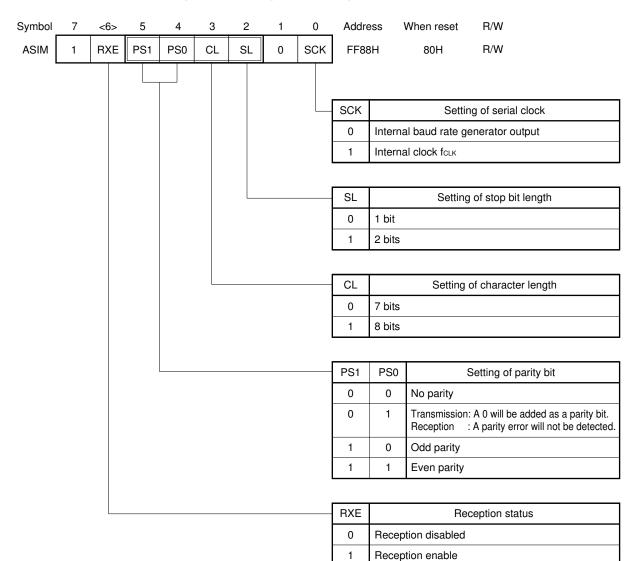

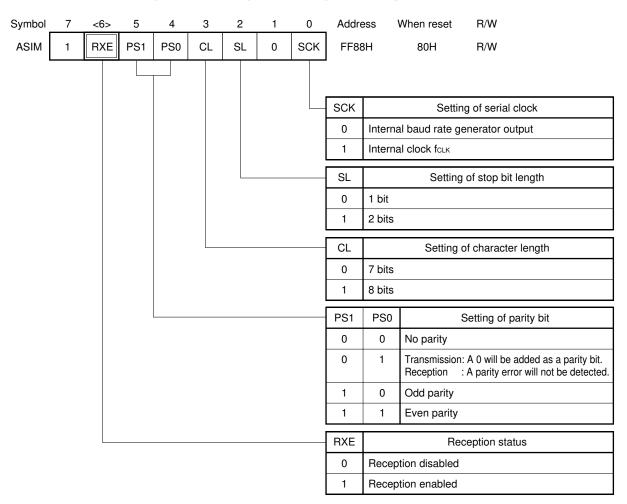

| 10.3         | Setting          | g Data Format                                                                    | 218 |

| 10.4         | Setting          | g Baud Rate                                                                      | 220 |

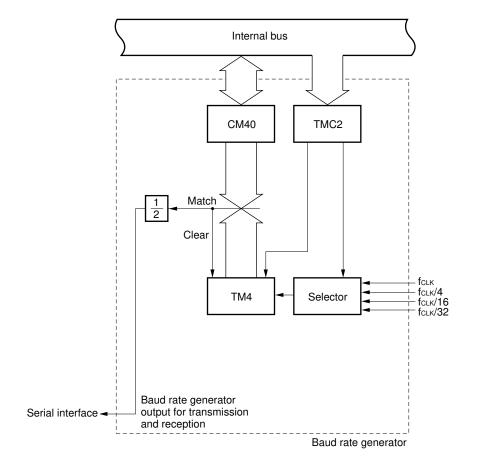

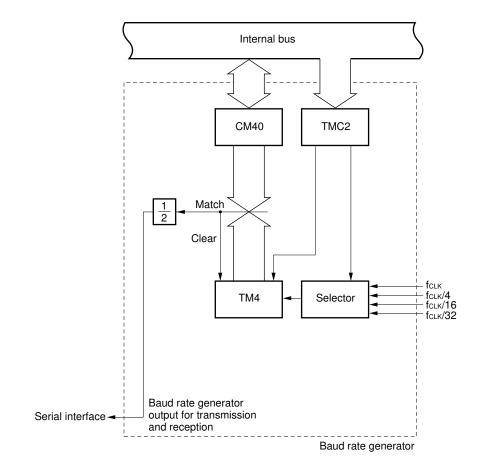

|              | 10.4.1           | Configuration of baud rate generator                                             | 222 |

|              | 10.4.2           | Setting a desired baud rate                                                      | 224 |

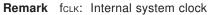

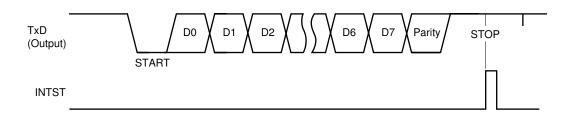

| 10.5         | Transr           | mitting Data                                                                     | 227 |

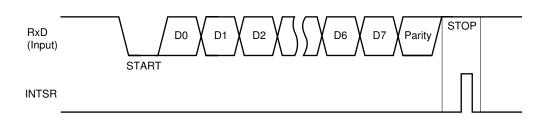

| 10.6         | Receiv           | /ing Data                                                                        | 229 |

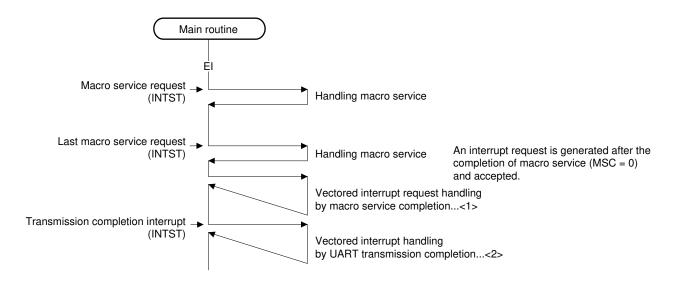

| 10.7         | Trans            | mitting/Receiving Data Using the Macro Service                                   | 231 |

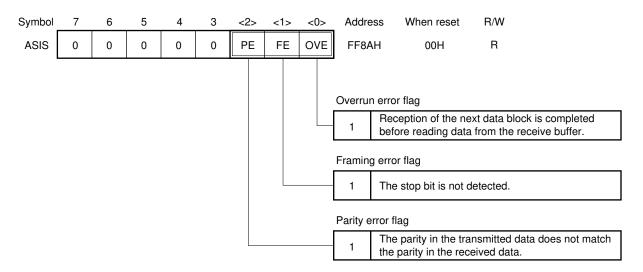

| 10.8         | Handli           | ing Reception Error                                                              | 233 |

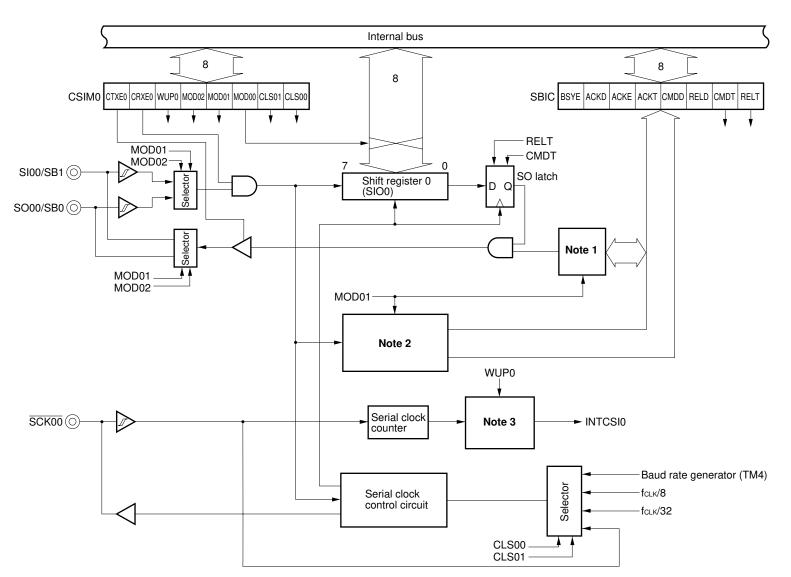

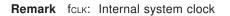

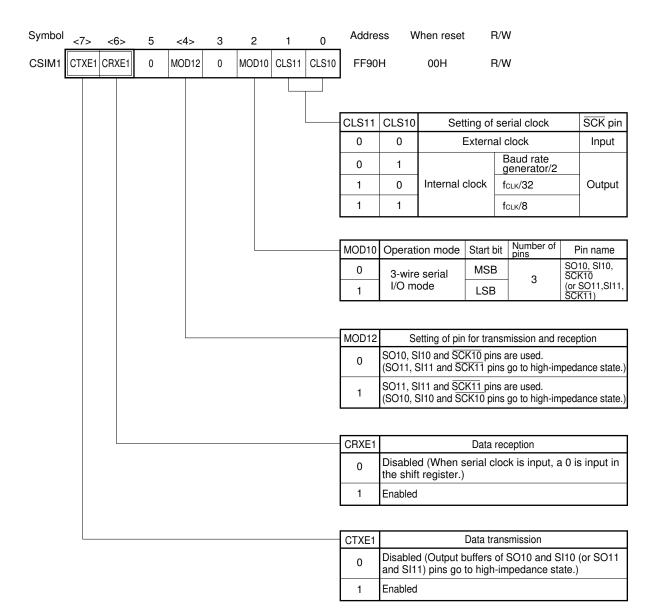

| СНАРТЕ       |                  | LOCK SYNCHRONOUS SERIAL INTERFACE                                                | 235 |

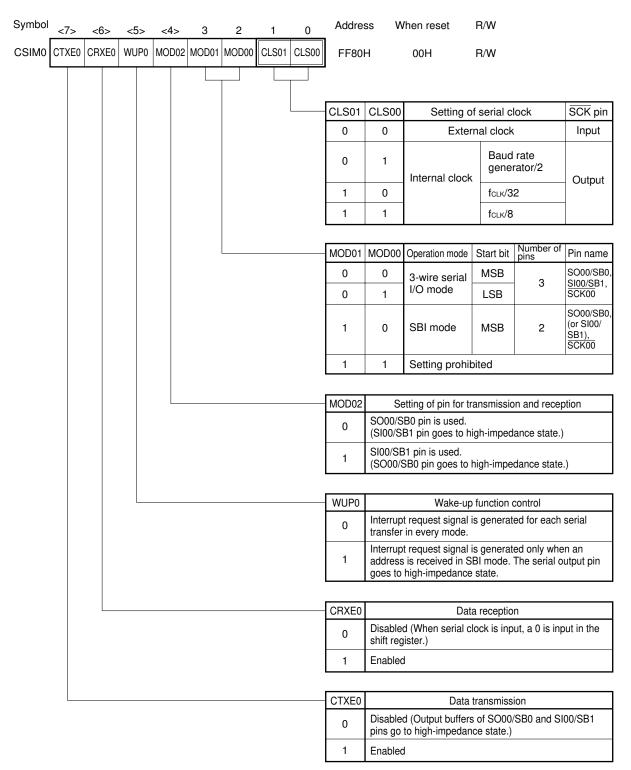

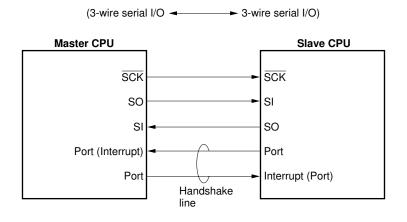

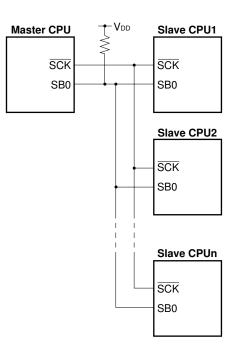

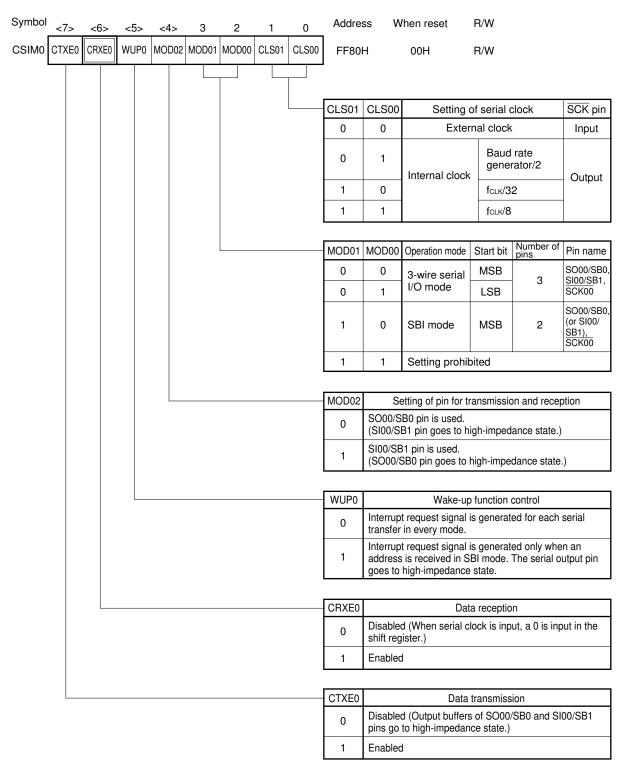

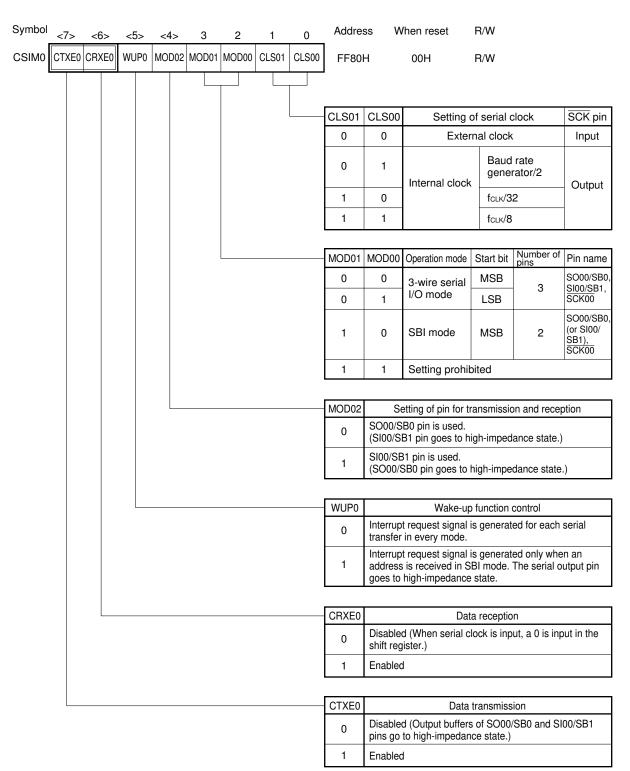

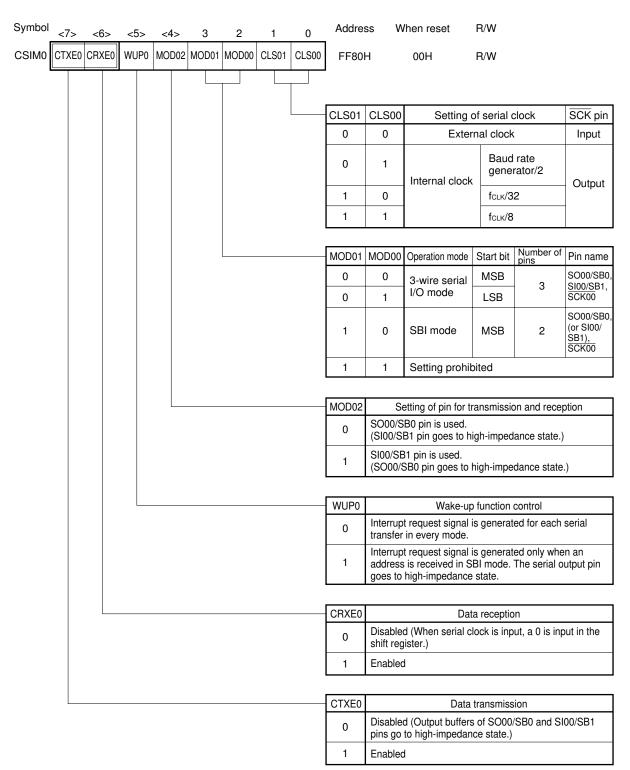

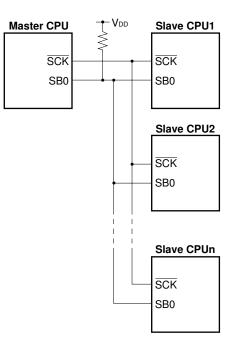

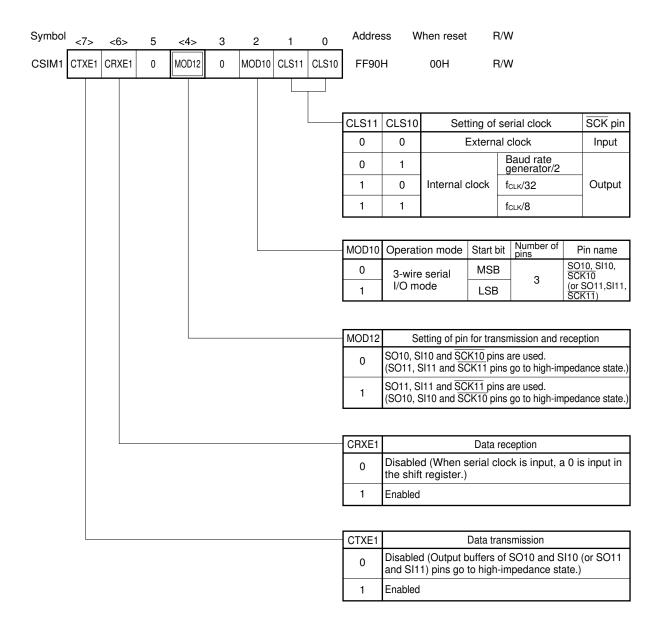

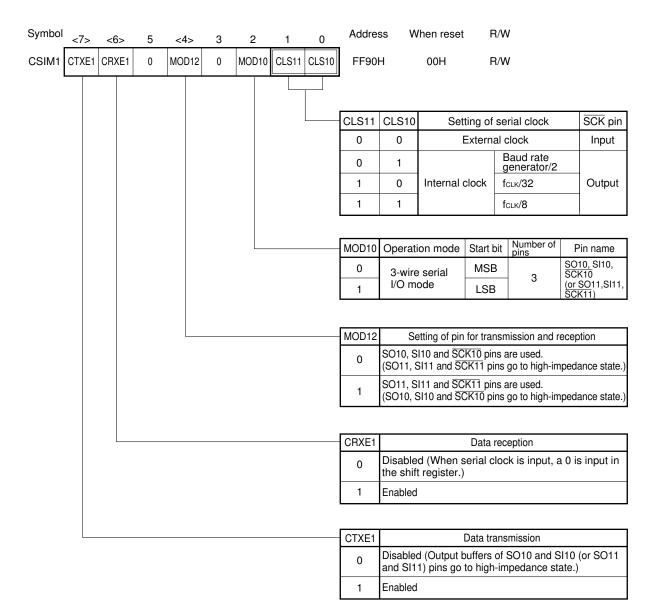

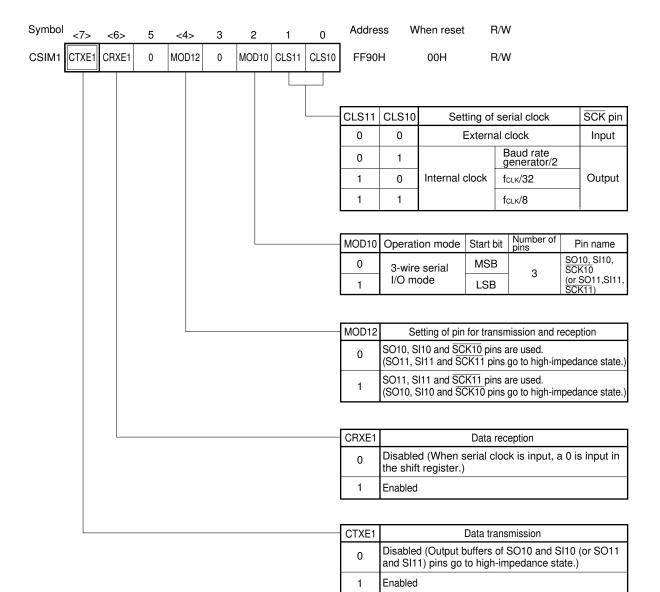

| 11.1         |                  | juration of Clock Synchronous Serial Interface                                   |     |

| 11.2         | -                | g Pins for Serial Transmission                                                   |     |

| 11.2         |                  | g Baud Rate                                                                      |     |

| 11.5         |                  |                                                                                  |     |

|              | 11.3.1<br>11.3.2 | Configuration of baud rate generator<br>Setting a desired baud rate              |     |

| 11 /         | -                | -                                                                                |     |

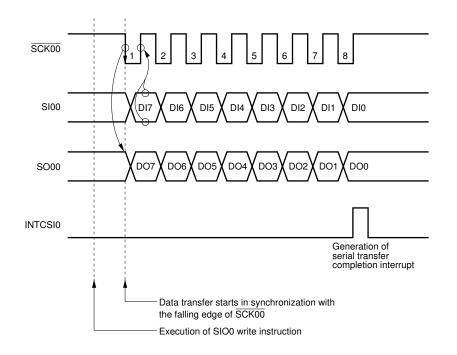

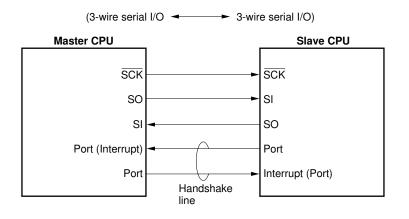

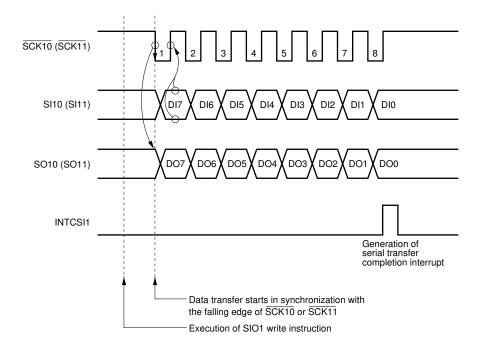

| 11.4<br>11.5 |                  | peration Modes of Clock Synchronous Serial Interface<br>g 3-Wire Serial I/O Mode |     |

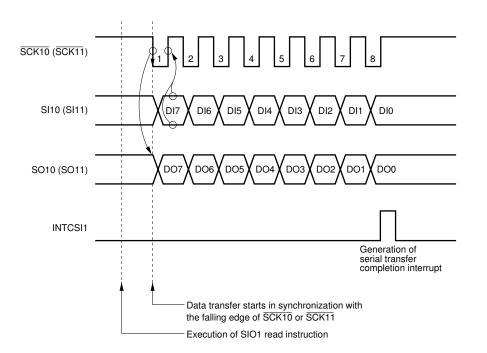

| 11.5         | 11.5.1           | -                                                                                |     |

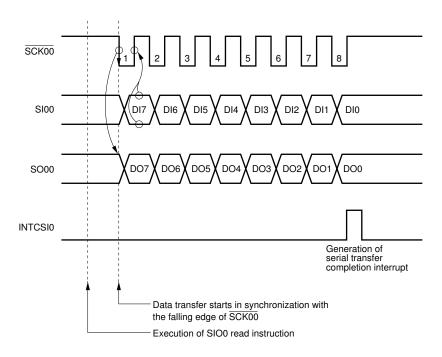

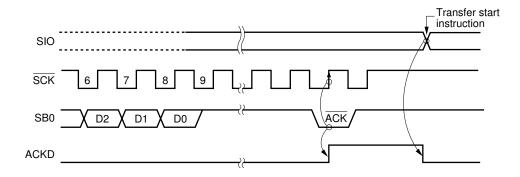

|              |                  | Transmitting data in 3-wire serial I/O mode                                      |     |

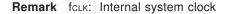

|              | 11.5.2           | Receiving data in 3-wire serial I/O mode                                         |     |

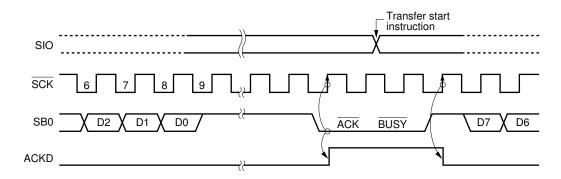

|              | 11.5.3           | Transmitting and receiving data in 3-wire serial I/O mode                        |     |

| 14.0         | 11.5.4           | Action taken when shift operation is not in phase with serial clock              |     |

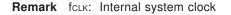

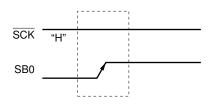

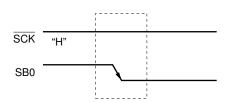

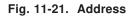

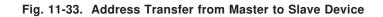

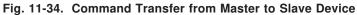

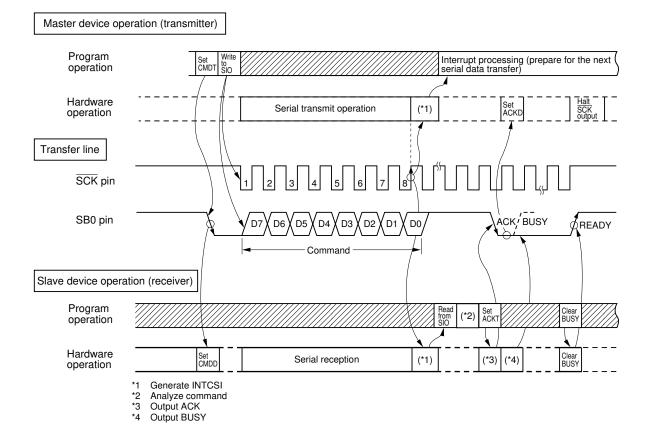

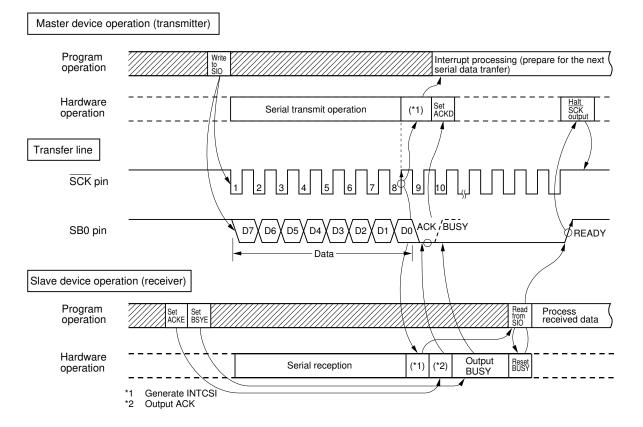

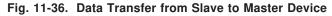

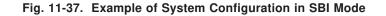

| 11.6         |                  | g SBI Mode                                                                       |     |

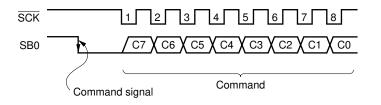

|              | 11.6.1           | SBI data format                                                                  |     |

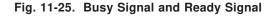

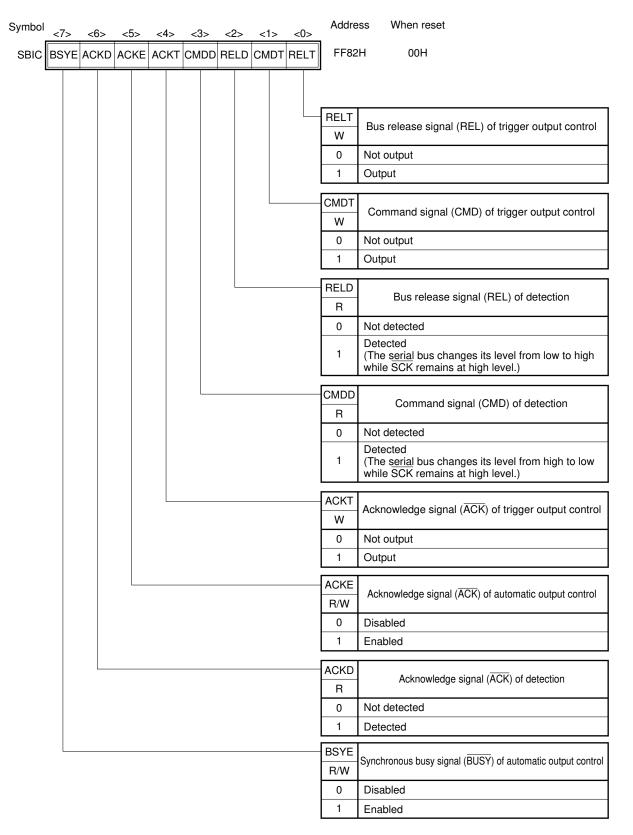

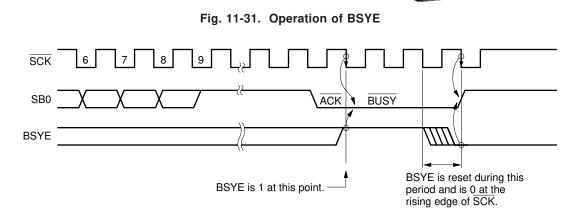

|              | 11.6.2           | Controlling and detecting the serial bus status                                  |     |

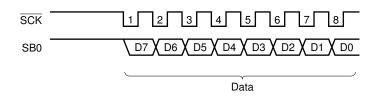

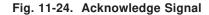

|              | 11.6.3           | Transmitting and receiving data in SBI mode                                      |     |

|              | 11.6.4           | Activating operation only when an address is received                            |     |

| CHA | PTER                                                   | 12 CL                                                                                                                                                                                                                                   | OCK SYNCHRONOUS SERIAL INTERFACE                                                                                                                                   |                                                                                                                                                                                                                            |

|-----|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                        | (W                                                                                                                                                                                                                                      | TH PIN SWITCHING FUNCTION)                                                                                                                                         | 279                                                                                                                                                                                                                        |

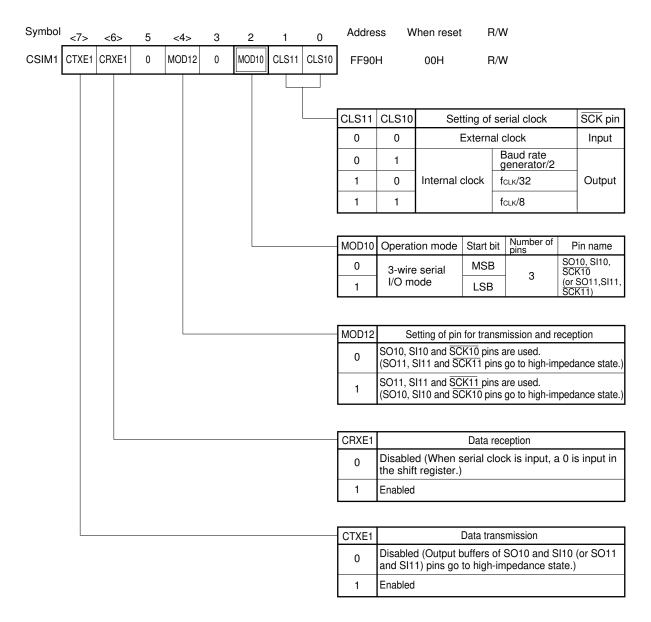

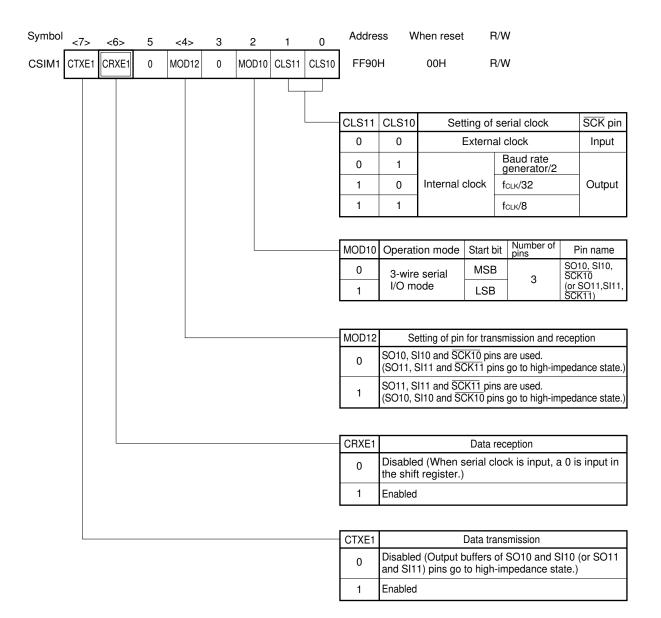

|     | 12.1                                                   | Config                                                                                                                                                                                                                                  | uration of Clock Synchronous Serial Interface                                                                                                                      |                                                                                                                                                                                                                            |

|     |                                                        | (with F                                                                                                                                                                                                                                 | Pin Switching Function)                                                                                                                                            | 280                                                                                                                                                                                                                        |

|     | 12.2                                                   | Setting                                                                                                                                                                                                                                 | Pins for Serial Transmission                                                                                                                                       | 282                                                                                                                                                                                                                        |

|     | 12.3                                                   | Switch                                                                                                                                                                                                                                  | ing Pins in 3-Wire Serial I/O Mode                                                                                                                                 | 284                                                                                                                                                                                                                        |

|     | 12.4                                                   | Setting                                                                                                                                                                                                                                 | g Baud Rate                                                                                                                                                        | 286                                                                                                                                                                                                                        |

|     |                                                        | 12.4.1                                                                                                                                                                                                                                  | Configuration of baud rate generator                                                                                                                               | 288                                                                                                                                                                                                                        |

|     |                                                        | 12.4.2                                                                                                                                                                                                                                  | Setting a desired baud rate                                                                                                                                        | 290                                                                                                                                                                                                                        |

|     | 12.5                                                   | Operat                                                                                                                                                                                                                                  | ion Mode of Clock Synchronous Serial Interface                                                                                                                     |                                                                                                                                                                                                                            |

|     |                                                        | (with F                                                                                                                                                                                                                                 | Pin Switching Function)                                                                                                                                            | 292                                                                                                                                                                                                                        |

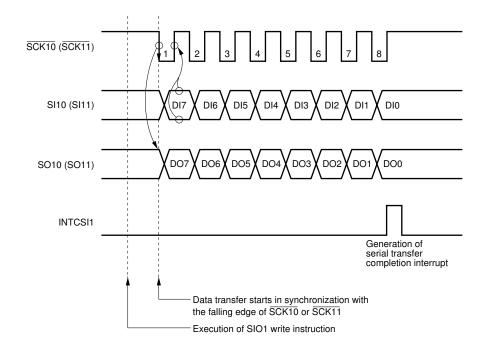

|     | 12.6                                                   | Selecti                                                                                                                                                                                                                                 | ing Start Bit for 3-Wire Serial I/O Mode Transmission                                                                                                              | 293                                                                                                                                                                                                                        |

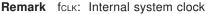

|     |                                                        | 12.6.1                                                                                                                                                                                                                                  | Transmitting data in 3-wire serial I/O mode                                                                                                                        | 295                                                                                                                                                                                                                        |

|     |                                                        | 12.6.2                                                                                                                                                                                                                                  | Receiving data in 3-wire serial I/O mode                                                                                                                           | 297                                                                                                                                                                                                                        |

|     |                                                        | 12.6.3                                                                                                                                                                                                                                  | Transmitting and receiving data in 3-wire serial I/O mode                                                                                                          | 299                                                                                                                                                                                                                        |

|     |                                                        | 12.6.4                                                                                                                                                                                                                                  | Action taken when shift operation is not in phase with serial clock                                                                                                | 302                                                                                                                                                                                                                        |

|     |                                                        |                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                                                                                                                                                                                                            |

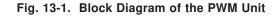

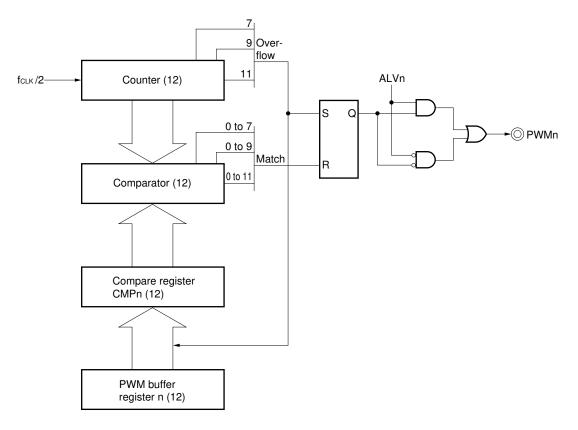

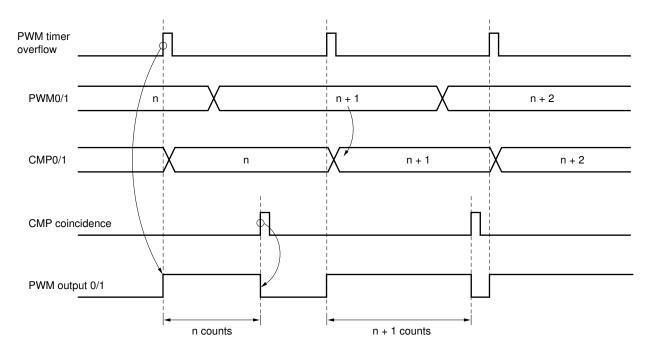

| СНА | PTER                                                   | 13 PV                                                                                                                                                                                                                                   | VM SIGNAL OUTPUT FUNCTION                                                                                                                                          | 303                                                                                                                                                                                                                        |

|     | 13.1                                                   | Config                                                                                                                                                                                                                                  | uration                                                                                                                                                            | 303                                                                                                                                                                                                                        |

|     | 13.2                                                   | Contro                                                                                                                                                                                                                                  | I Register                                                                                                                                                         | 304                                                                                                                                                                                                                        |

|     |                                                        | 13.2.1                                                                                                                                                                                                                                  | PWM control register (PWMC)                                                                                                                                        | 304                                                                                                                                                                                                                        |

|     |                                                        | 13.2.2                                                                                                                                                                                                                                  | PWM buffer registers (PWM0 and PWM1)                                                                                                                               | 304                                                                                                                                                                                                                        |

|     |                                                        | 13.2.3                                                                                                                                                                                                                                  | Compare registers (CMP0 and CMP1)                                                                                                                                  | 304                                                                                                                                                                                                                        |

|     | 10.0                                                   | 0                                                                                                                                                                                                                                       |                                                                                                                                                                    | 305                                                                                                                                                                                                                        |

|     | 13.3                                                   | Operat                                                                                                                                                                                                                                  | ion                                                                                                                                                                | 305                                                                                                                                                                                                                        |

|     | 13.3                                                   | Operat                                                                                                                                                                                                                                  | 10n                                                                                                                                                                | 305                                                                                                                                                                                                                        |

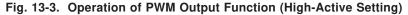

|     |                                                        | •                                                                                                                                                                                                                                       | ATCHDOG TIMER                                                                                                                                                      | 305                                                                                                                                                                                                                        |

| СНА |                                                        | 14 W/                                                                                                                                                                                                                                   |                                                                                                                                                                    |                                                                                                                                                                                                                            |

| СНА | PTER                                                   | ·<br>14 W/<br>Config                                                                                                                                                                                                                    | ATCHDOG TIMER                                                                                                                                                      | 307                                                                                                                                                                                                                        |

| СНА | PTER<br>14.1                                           | ·<br>14 W/<br>Config<br>Watch                                                                                                                                                                                                           | ATCHDOG TIMER                                                                                                                                                      | 307<br>307                                                                                                                                                                                                                 |

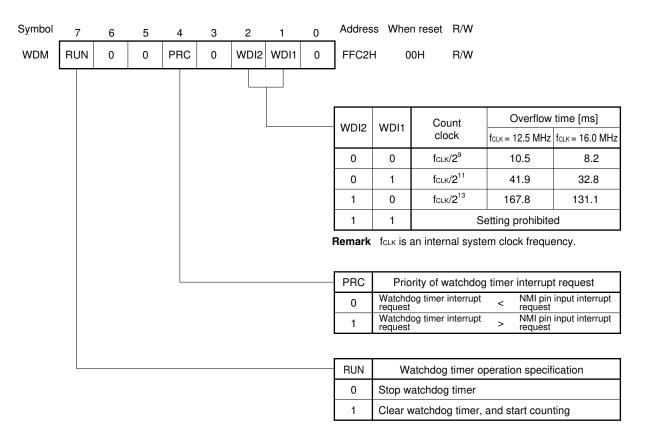

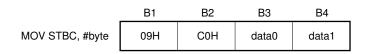

| СНА | PTER<br>14.1<br>14.2                                   | 14 W<br>Config<br>Watch<br>Watch                                                                                                                                                                                                        | ATCHDOG TIMER<br>uration<br>dog Timer Mode Register (WDM)                                                                                                          | 307<br>307<br>308                                                                                                                                                                                                          |

| СНА | PTER<br>14.1<br>14.2<br>14.3<br>14.4                   | Config<br>Watche<br>Watche<br>Examp                                                                                                                                                                                                     | ATCHDOG TIMER<br>uration<br>dog Timer Mode Register (WDM)<br>dog Timer Output Pin<br>le of Application                                                             | 307<br>307<br>308<br>310                                                                                                                                                                                                   |

| СНА | PTER<br>14.1<br>14.2<br>14.3<br>14.4                   | Config<br>Watche<br>Watche<br>Examp                                                                                                                                                                                                     | ATCHDOG TIMER<br>uration<br>dog Timer Mode Register (WDM)<br>dog Timer Output Pin                                                                                  | 307<br>307<br>308<br>310                                                                                                                                                                                                   |

| СНА | PTER<br>14.1<br>14.2<br>14.3<br>14.4<br>PTER           | Config<br>Watche<br>Watche<br>Examp                                                                                                                                                                                                     | ATCHDOG TIMER<br>uration<br>dog Timer Mode Register (WDM)<br>dog Timer Output Pin<br>le of Application                                                             | 307<br>307<br>308<br>310<br>310                                                                                                                                                                                            |

| СНА | PTER<br>14.1<br>14.2<br>14.3<br>14.4<br>PTER           | Config<br>Watche<br>Watche<br>Examp                                                                                                                                                                                                     | ATCHDOG TIMER<br>uration<br>dog Timer Mode Register (WDM)<br>dog Timer Output Pin<br>le of Application                                                             | 307<br>307<br>308<br>310<br>310<br>311                                                                                                                                                                                     |

| СНА | PTER<br>14.1<br>14.2<br>14.3<br>14.4<br>PTER           | 14 W/<br>Config<br>Watch<br>Watch<br>Examp<br>15 IN<br>Interru                                                                                                                                                                          | ATCHDOG TIMER<br>uration<br>dog Timer Mode Register (WDM)<br>dog Timer Output Pin<br>ble of Application<br>TERRUPT FUNCTION<br>pt Requests                         | 307<br>307<br>308<br>310<br>310<br>311<br>311                                                                                                                                                                              |

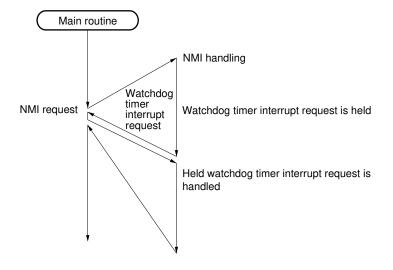

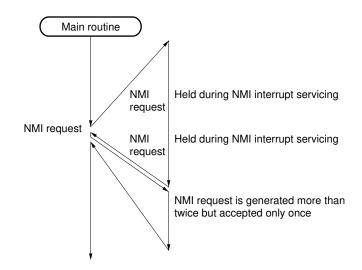

| СНА | PTER<br>14.1<br>14.2<br>14.3<br>14.4<br>PTER           | Config<br>Watche<br>Watche<br>Examp<br>15.1.1                                                                                                                                                                                           | ATCHDOG TIMER<br>uration<br>dog Timer Mode Register (WDM)<br>dog Timer Output Pin<br>de of Application<br>TERRUPT FUNCTION<br>pt Requests<br>Nonmaskable interrupt | 307<br>307<br>308<br>310<br>310<br>311<br>311<br>314                                                                                                                                                                       |

| СНА | PTER<br>14.1<br>14.2<br>14.3<br>14.4<br>PTER           | A 14 W/<br>Config<br>Watche<br>Examp<br>A 15 IN<br>Interru<br>15.1.1<br>15.1.2                                                                                                                                                          | ATCHDOG TIMER<br>uration                                                                                                                                           | 307<br>308<br>310<br>310<br>311<br>314<br>314<br>314                                                                                                                                                                       |

| СНА | PTER<br>14.1<br>14.2<br>14.3<br>14.4<br>PTER           | <b>14 W/</b><br><b>Config</b><br><b>Watch</b><br><b>Watch</b><br><b>Examp</b><br><b>15 IN</b><br><b>Interru</b><br>15.1.1<br>15.1.2<br>15.1.3<br>15.1.4                                                                                 | ATCHDOG TIMERuration                                                                                                                                               | 307<br>307<br>308<br>310<br>310<br>311<br>314<br>314<br>314<br>315                                                                                                                                                         |

| СНА | APTER<br>14.1<br>14.2<br>14.3<br>14.4<br>APTER<br>15.1 | <b>14 W/</b><br><b>Config</b><br><b>Watch</b><br><b>Watch</b><br><b>Examp</b><br><b>15 IN</b><br><b>Interru</b><br>15.1.1<br>15.1.2<br>15.1.3<br>15.1.4                                                                                 | ATCHDOG TIMER                                                                                                                                                      | 307<br>308<br>310<br>310<br>311<br>311<br>314<br>314<br>314<br>315<br>315                                                                                                                                                  |

| СНА | APTER<br>14.1<br>14.2<br>14.3<br>14.4<br>APTER<br>15.1 | <b>14 W/</b><br><b>Config</b><br><b>Watch</b><br><b>Examp</b><br><b>15 IN</b><br><b>Interru</b><br>15.1.1<br>15.1.2<br>15.1.3<br>15.1.4<br><b>Interru</b>                                                                               | ATCHDOG TIMERuration                                                                                                                                               | 307<br>308<br>310<br>310<br>311<br>314<br>314<br>314<br>314<br>315<br>315<br>315                                                                                                                                           |

| СНА | APTER<br>14.1<br>14.2<br>14.3<br>14.4<br>APTER<br>15.1 | <b>14 W/</b><br><b>Config</b><br><b>Watch</b><br><b>Examp</b><br><b>15 IN</b><br><b>Interru</b><br>15.1.1<br>15.1.2<br>15.1.3<br>15.1.4<br><b>Interru</b><br>15.2.1                                                                     | ATCHDOG TIMER<br>uration                                                                                                                                           | 307<br>308<br>310<br>310<br>311<br>314<br>314<br>314<br>315<br>315<br>316<br>316                                                                                                                                           |

| СНА | APTER<br>14.1<br>14.2<br>14.3<br>14.4<br>APTER<br>15.1 | <b>14 W/</b><br><b>Config</b><br><b>Watch</b><br><b>Examp</b><br><b>15 IN</b><br><b>Interru</b><br>15.1.1<br>15.1.2<br>15.1.3<br>15.1.4<br><b>Interru</b><br>15.2.1<br>15.2.2<br>15.2.3                                                 | ATCHDOG TIMER<br>uration                                                                                                                                           | 307<br>308<br>310<br>310<br>311<br>314<br>314<br>314<br>315<br>315<br>316<br>316<br>316                                                                                                                                    |

| СНА | APTER<br>14.1<br>14.2<br>14.3<br>14.4<br>APTER<br>15.1 | <b>14 W/</b><br><b>Config</b><br><b>Watch</b><br><b>Examp</b><br><b>15 IN</b><br><b>Interru</b><br>15.1.1<br>15.1.2<br>15.1.3<br>15.1.4<br><b>Interru</b><br>15.2.1<br>15.2.2<br>15.2.3                                                 | ATCHDOG TIMER                                                                                                                                                      | <ul> <li>307</li> <li>308</li> <li>310</li> <li>310</li> <li>311</li> <li>314</li> <li>314</li> <li>315</li> <li>316</li> <li>316</li> <li>316</li> <li>316</li> <li>316</li> <li>316</li> <li>316</li> </ul>              |

| СНА | APTER<br>14.1<br>14.2<br>14.3<br>14.4<br>APTER<br>15.1 | <b>14 W/</b><br><b>Config</b><br><b>Watch</b><br><b>Examp</b><br><b>15 IN</b><br><b>Interru</b><br>15.1.1<br>15.1.2<br>15.1.3<br>15.1.4<br><b>Interru</b><br>15.2.1<br>15.2.2<br>15.2.3<br><b>Interru</b>                               | ATCHDOG TIMER                                                                                                                                                      | <ul> <li>307</li> <li>308</li> <li>310</li> <li>310</li> <li>311</li> <li>314</li> <li>314</li> <li>315</li> <li>316</li> <li>316</li> <li>316</li> <li>316</li> <li>316</li> <li>316</li> <li>316</li> <li>317</li> </ul> |

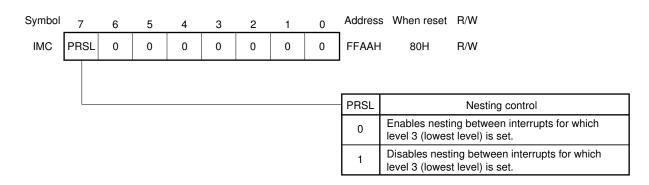

| СНА | APTER<br>14.1<br>14.2<br>14.3<br>14.4<br>APTER<br>15.1 | <b>14 W/</b><br><b>Config</b><br><b>Watch</b><br><b>Watch</b><br><b>Examp</b><br><b>15 IN</b><br><b>Interru</b><br>15.1.1<br>15.1.2<br>15.1.3<br>15.1.4<br><b>Interru</b><br>15.2.1<br>15.2.2<br>15.2.3<br><b>Interru</b><br>15.3.1     | ATCHDOG TIMER                                                                                                                                                      | <ul> <li>307</li> <li>308</li> <li>310</li> <li>310</li> <li>311</li> <li>314</li> <li>314</li> <li>315</li> <li>316</li> <li>316</li> <li>316</li> <li>316</li> <li>316</li> <li>317</li> <li>319</li> </ul>              |

| СНА | APTER<br>14.1<br>14.2<br>14.3<br>14.4<br>APTER<br>15.1 | <b>14 W/</b><br><b>Config</b><br><b>Watch</b><br><b>Examp</b><br><b>15 IN</b><br><b>Interru</b><br>15.1.1<br>15.1.2<br>15.1.3<br>15.1.4<br><b>Interru</b><br>15.2.1<br>15.2.2<br>15.2.3<br><b>Interru</b><br>15.3.1<br>15.3.2           | ATCHDOG TIMER                                                                                                                                                      | 307<br>308<br>310<br>310<br>311<br>314<br>314<br>314<br>315<br>316<br>316<br>316<br>316<br>316<br>316<br>317<br>319<br>324                                                                                                 |

| СНА | APTER<br>14.1<br>14.2<br>14.3<br>14.4<br>APTER<br>15.1 | <b>14 W/</b><br><b>Config</b><br><b>Watch</b><br><b>Examp</b><br><b>15 IN</b><br><b>Interru</b><br>15.1.1<br>15.1.2<br>15.1.3<br>15.1.4<br><b>Interru</b><br>15.2.1<br>15.2.2<br>15.2.3<br><b>Interru</b><br>15.3.1<br>15.3.2<br>15.3.3 | ATCHDOG TIMER                                                                                                                                                      | 307<br>308<br>310<br>310<br>311<br>314<br>314<br>315<br>315<br>316<br>316<br>316<br>316<br>316<br>317<br>319<br>324<br>326                                                                                                 |

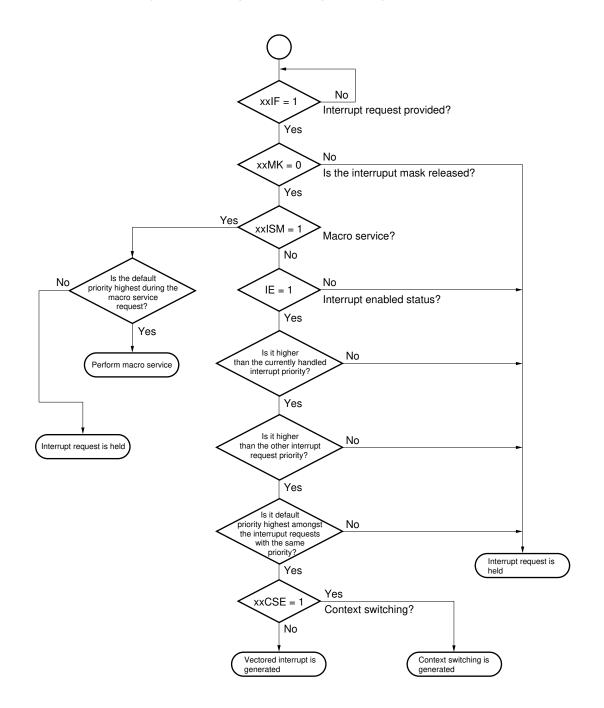

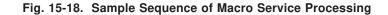

|          | 15.5  | Maskable Interrupt Acknowledgement                                                     | 333 |

|----------|-------|----------------------------------------------------------------------------------------|-----|

|          |       | 15.5.1 Vectored interrupt                                                              | 335 |

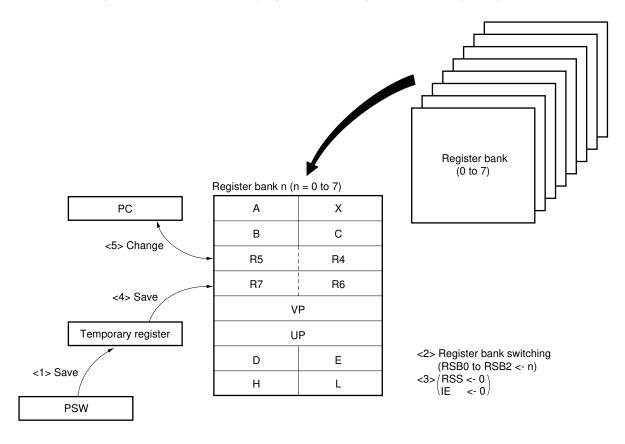

|          |       | 15.5.2 Context switching                                                               | 335 |

|          |       | 15.5.3 Maskable interrupt priority                                                     | 337 |

|          | 15.6  | Software Interrupt Acknowledgement                                                     | 343 |

|          |       | 15.6.1 Software interrupt acknowledgement by the BRK instruction                       | 343 |

|          |       | 15.6.2 Software interrupt (context switching) acknowledgement by the BRKCS instruction | 343 |

|          | 15.7  | Op-code Trap Interrupt Acknowledgement                                                 | 346 |

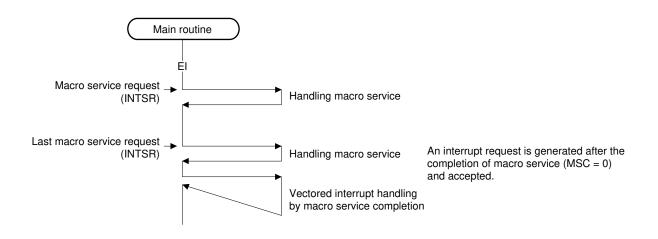

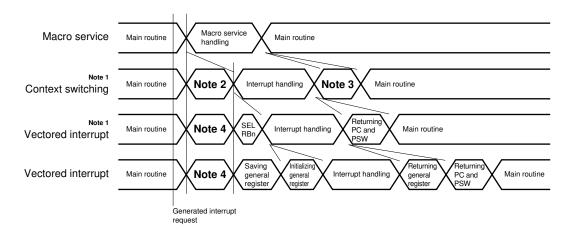

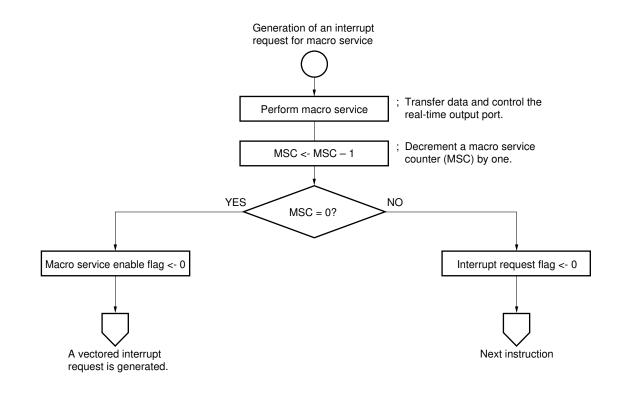

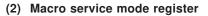

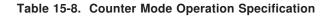

|          | 15.8  | Macro Service Function                                                                 | 347 |

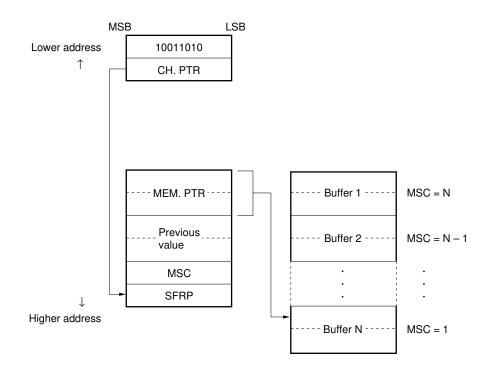

|          |       | 15.8.1 Macro service overview                                                          | 347 |

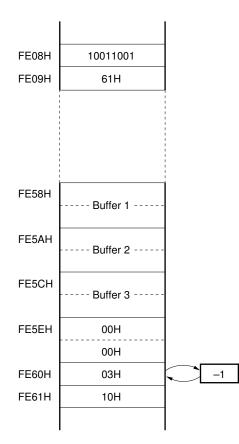

|          |       | 15.8.2 Basic operation of macro service                                                | 350 |

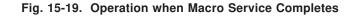

|          |       | 15.8.3 Macro service completion                                                        | 352 |

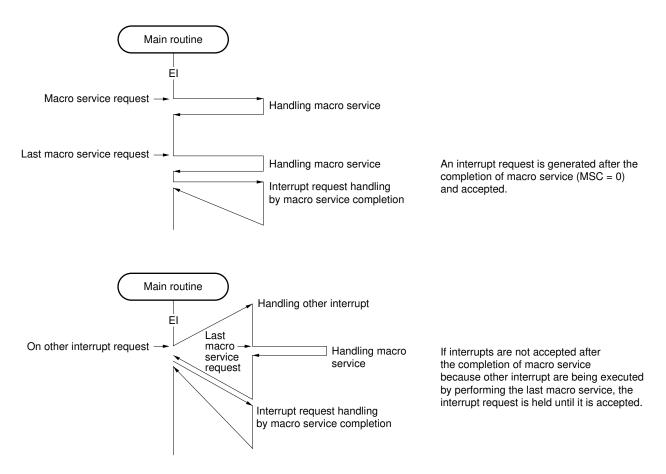

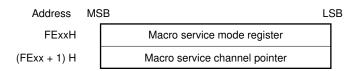

|          |       | 15.8.4 Macro service control register                                                  | 353 |

|          |       | 15.8.5 Macro service mode                                                              | 355 |

|          |       | 15.8.6 Macro service operation                                                         | 355 |

|          | 15.9  | When Interrupt Requests and Macro Service are Held Temporarily                         | 364 |

|          | 15.10 | Instructions Which are Stopped Temporarily in Interrupts and Macro Services            | 367 |

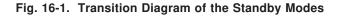

| СН       | APTER | 16 STANDBY FUNCTION                                                                    | 369 |

| -        | 16.1  | Function Overview                                                                      | 369 |

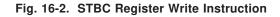

|          | 16.2  | Standby Control Register (STBC)                                                        | 370 |

|          | 16.3  | Operation                                                                              | 372 |

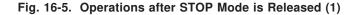

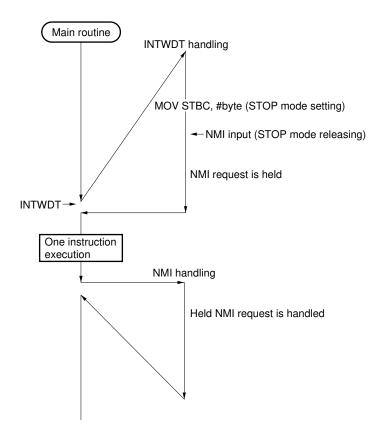

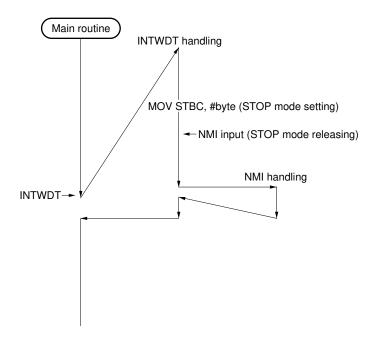

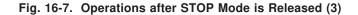

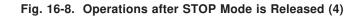

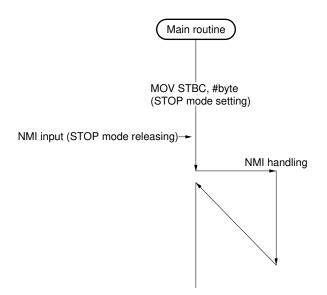

|          |       | 16.3.1 HALT mode                                                                       | 372 |

|          |       | 16.3.2 STOP mode                                                                       | 375 |

|          |       |                                                                                        |     |

| CH       | APTER | 17 RESET FUNCTION                                                                      | 385 |

| СН       | APTER | 18 BUS INTERFACE FUNCTION                                                              | 389 |

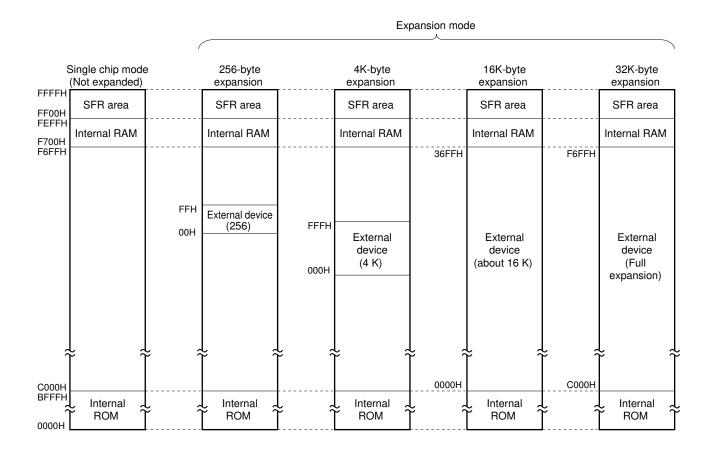

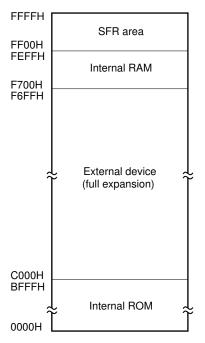

|          | 18.1  | External Device Expansion Function for the $\mu$ PD78356                               | 389 |

|          | 18.2  | Access to External Devices by the $\mu$ PD78355                                        | 393 |

|          | 18.3  | Control Registers                                                                      | 394 |

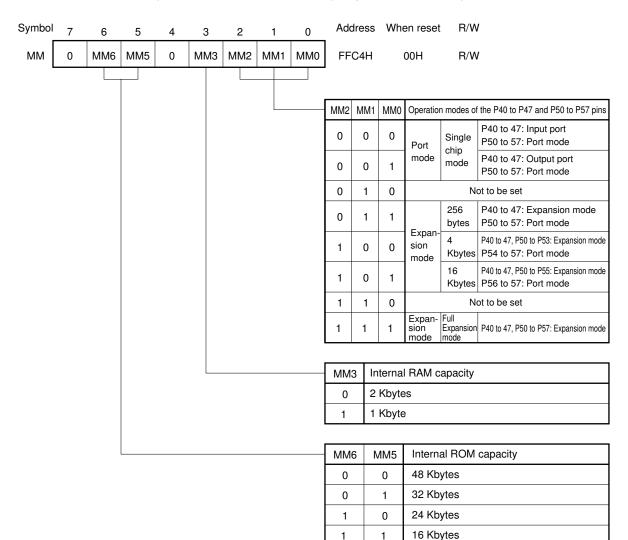

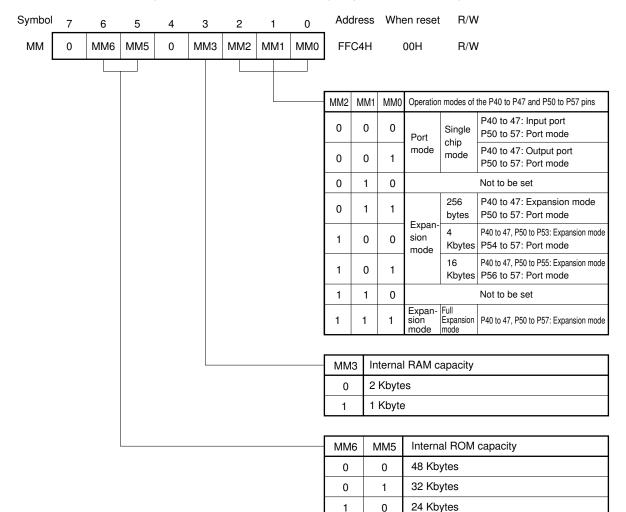

|          |       | 18.3.1 Memory expansion mode register                                                  | 394 |

|          |       | 18.3.2 Programmable wait control register                                              | 396 |

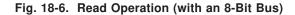

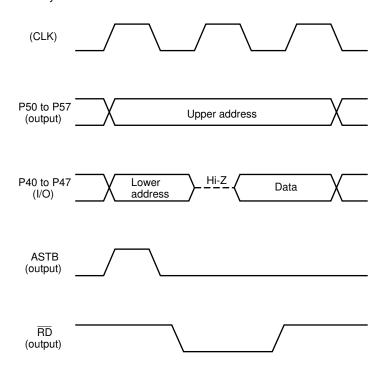

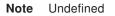

|          | 18.4  | Bus Timing                                                                             | 399 |

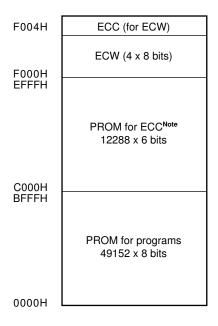

| СН       |       | 19 PROGRAMMING FOR THE $\mu$ PD78P356                                                  | 403 |

| <b>.</b> | 19.1  | Operating Mode                                                                         | 404 |

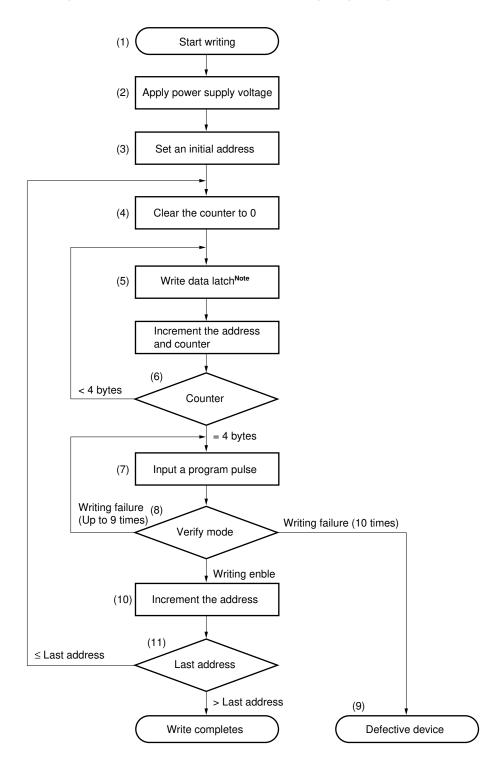

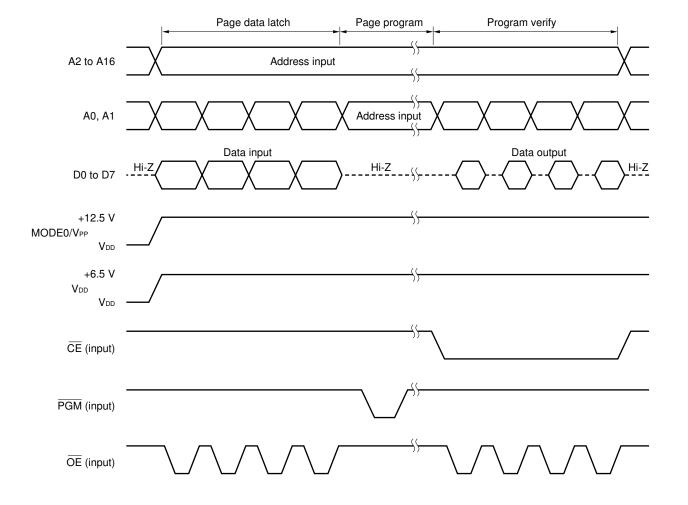

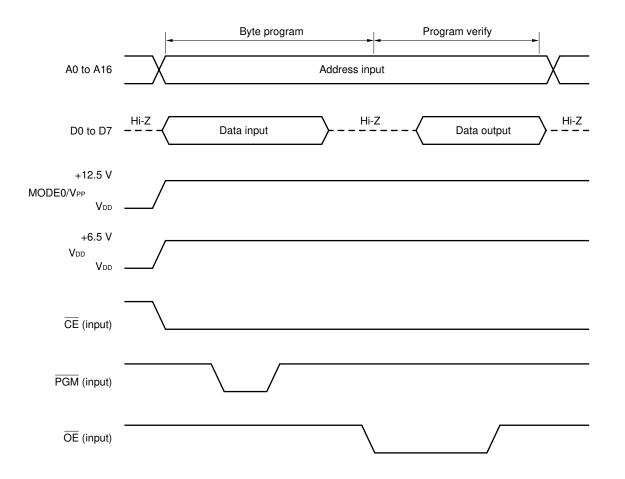

|          | 19.2  | Procedure for Writing on PROM (Page Program Mode)                                      | 405 |

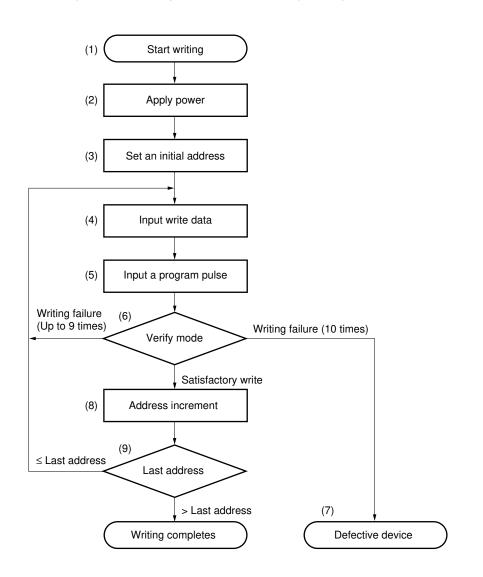

|          | 19.3  | Procedure for Writing Data into PROM (Byte Program Mode)                               | 408 |

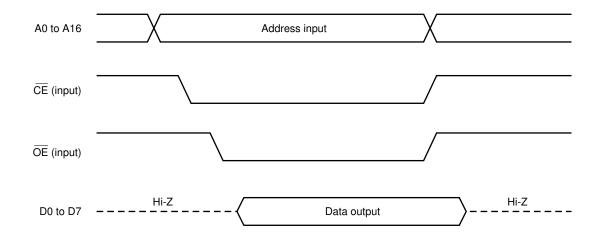

|          | 19.4  | Procedure for Reading from PROM                                                        | 411 |

|          | 19.5  | Erasure Characteristics (µPD78P356KP Only)                                             | 412 |

|          | 19.6  | Protective Film Covering the Erasure Window ( $\mu$ PD78P356KP Only)                   | 412 |

|          | 19.7  | Screening of One-Time PROM Version Devices                                             | 412 |

| <b>.</b> |       |                                                                                        |     |

| CH       |       | 20 INSTRUCTION SET                                                                     | 413 |

|          | 20.1  | Operand Identifier and Description                                                     | 413 |

|         | 20.2         | Legend                                                                    | 416        |

|---------|--------------|---------------------------------------------------------------------------|------------|

|         | 20.3         | Notational Symbols in Flag Operation Field                                | 417        |

|         | 20.4         | Differences between the $\mu$ PD78356 and $\mu$ PD78352A Instruction Sets | 417        |

|         | 20.5         | Operations of Basic Instructions                                          | 418        |

|         |              |                                                                           |            |

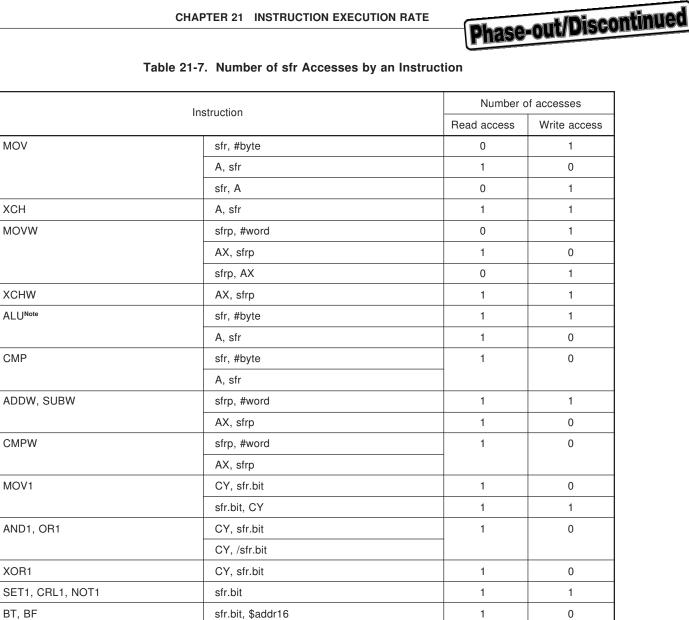

| CH      | APTER        | 21 INSTRUCTION EXECUTION RATE                                             | 435        |

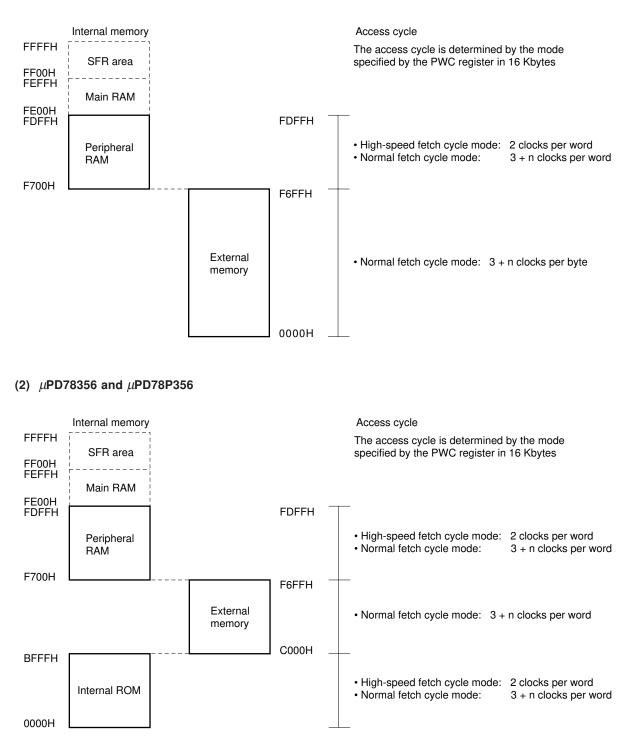

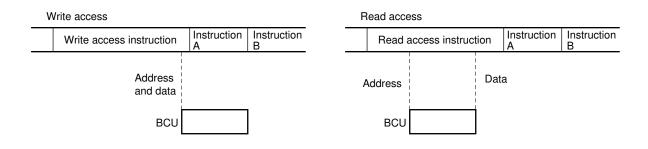

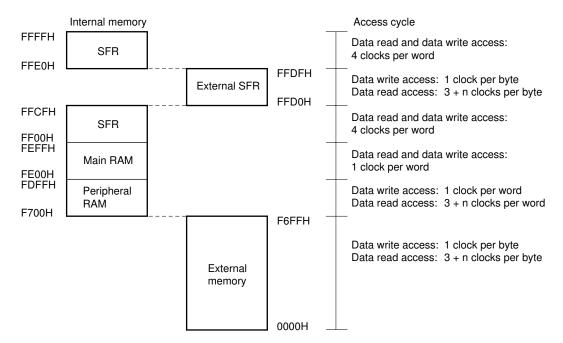

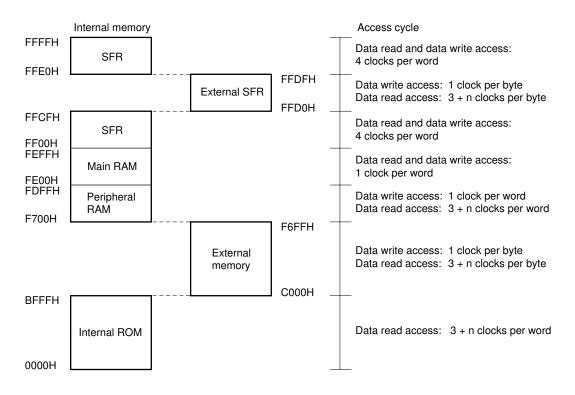

|         | 21.1         | Memory Space and Access Speed                                             | 435        |

|         |              | 21.1.1 Main RAM and peripheral RAM                                        | 435        |

|         |              | 21.1.2 Memory access                                                      | 435        |

|         | 21.2         | Interrupt Execution Rate                                                  | 443        |

|         | 21.3         | Calculating the Number of Execution Clocks                                | 444        |

| <u></u> |              | 22 CAUTIONS                                                               | 440        |

| СП      | 22.1         | Cautions for Chapter 2                                                    | 449<br>449 |

|         | 22.1         | •                                                                         |            |

|         | 22.2         | Cautions for Chapter 3                                                    | 449<br>450 |

|         | 22.3<br>22.4 | Cautions for Chapter 5                                                    | 450        |

|         |              | Cautions for Chapter 6                                                    | 451        |

|         | 22.5         | Cautions for Chapter 7                                                    | 451        |

|         | 22.6         | Cautions for Chapter 8                                                    | 453        |

|         | 22.7         | Cautions for Chapter 9                                                    | 454        |

|         | 22.8         | Cautions for Chapter 10                                                   | 455        |

|         | 22.9         | Cautions for Chapter 11                                                   | 456        |

|         |              | Cautions for Chapter 12                                                   | 456        |

|         |              | Cautions for Chapter 13                                                   | 456        |

|         |              | Cautions for Chapter 14                                                   | 456        |

|         |              | Cautions for Chapter 15                                                   | 457        |

|         |              | Cautions for Chapter 16                                                   | 459        |

|         |              | Cautions for Chapter 17                                                   | 459        |

|         |              | Cautions for Chapter 18                                                   | 459        |

|         | 22.17        | Cautions for Chapter 21                                                   | 460        |

| AP      | PENDI        | X A DIFFERENCES BETWEEN THE $\mu$ PD78356 AND $\mu$ PD78334               | 461        |

| AP      |              | K B TOOLS                                                                 | 465        |

|         | B.1          | Development Tools                                                         | 465        |

|         | B.2          | Embedded Software                                                         | 472        |

|         |              |                                                                           |            |

| AP      | PENDIX       | C REGISTER INDEX                                                          | 475        |

|         | C.1          | Register Name Index (Alphabetic Order)                                    | 475        |

|         | C.2          | Register Symbol Index (Alphabetic Order)                                  | 479        |

| AP      | PENDI        | X D FUNCTION INDEX                                                        | 483        |

|         |              |                                                                           |            |

| AP      | PENDI        | K E REVISION HISTORY                                                      | 489        |

## LIST OF FIGURES (1/7)

| Fig. No. | Title                                            | Page |

|----------|--------------------------------------------------|------|

| 2-1.     | Input/Output Circuits of Each Pin                | 34   |

| 3-1.     | Memory Map                                       | 36   |

| 3-2.     | Register Configuration                           | 44   |

| 3-3.     | Format of Program Status Word                    | 46   |

| 3-4.     | Format of CPU Control Word                       | 50   |

| 3-5.     | Manipulation Bits of General Registers           | 51   |

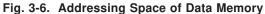

| 3-6.     | Addressing Space of Data Memory                  | 61   |

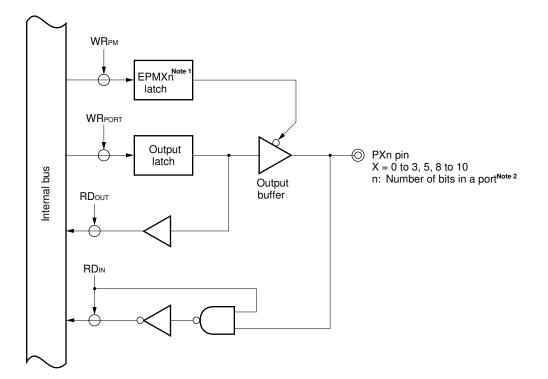

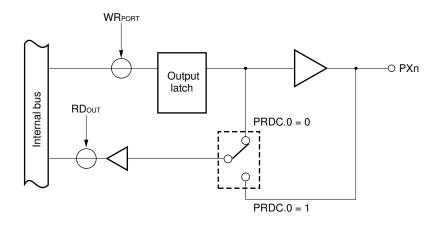

| 5-1.     | Basic I/O Port Configuration                     | 70   |

| 5-2.     | Port Specified as an Output Port                 | 71   |

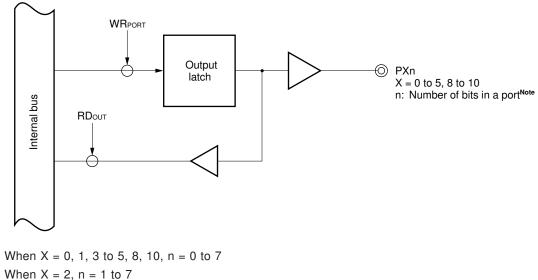

| 5-3.     | Port Specified as an Input Port                  | 72   |

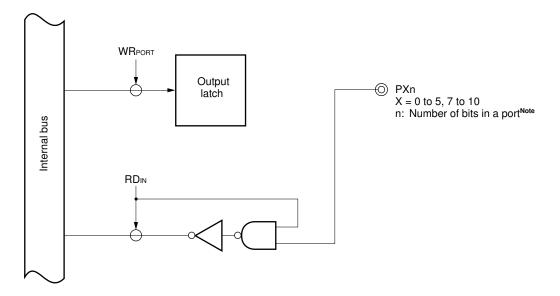

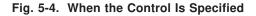

| 5-4.     | When the Control Is Specified                    | 73   |

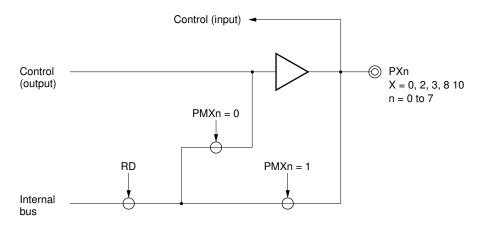

| 5-5.     | Port Read Control Register Format                | 74   |

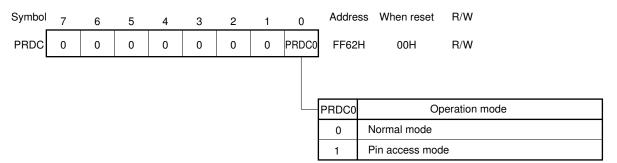

| 5-6.     | Control (Output Port Specified)                  | 75   |

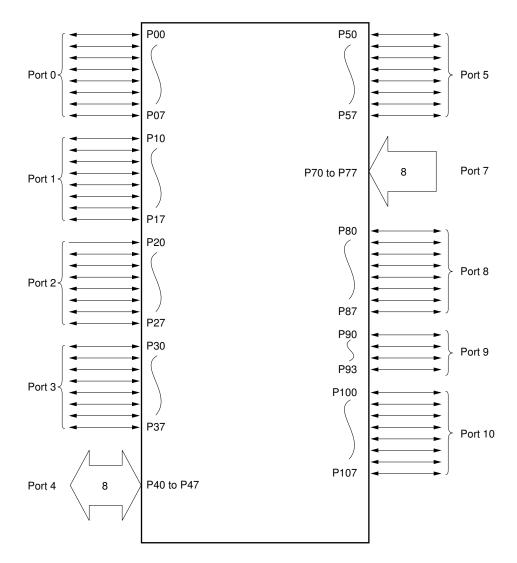

| 5-7.     | Port Configuration                               | 77   |

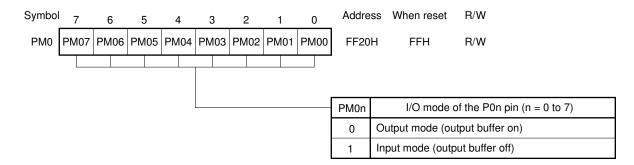

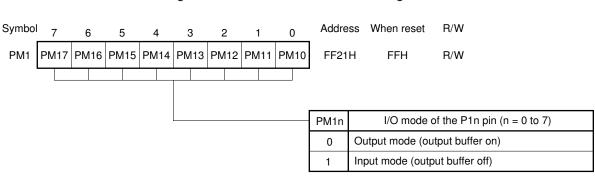

| 5-8.     | Format of the Port 0 Mode Register               | 79   |

| 5-9.     | Format of the Port 1 Mode Register               | 79   |

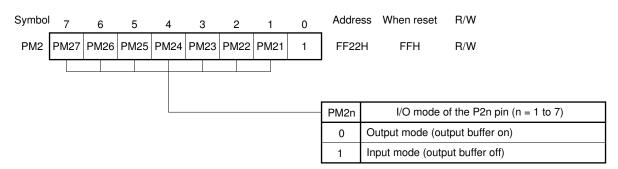

| 5-10.    | Format of the Port 2 Mode Register               | 80   |

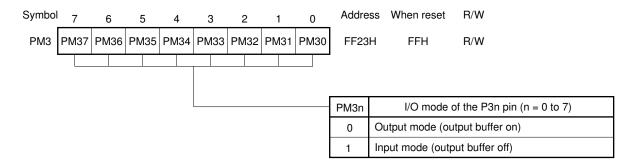

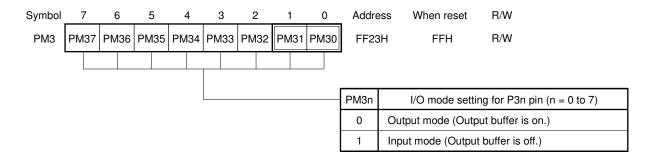

| 5-11.    | Format of the Port 3 Mode Register               | 80   |

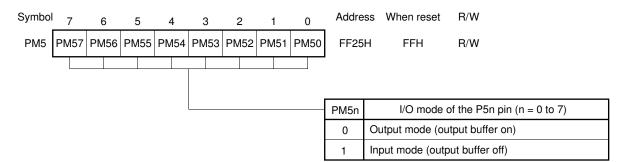

| 5-12.    | Format of the Port 5 Mode Register               | 80   |

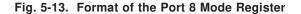

| 5-13.    | Format of the Port 8 Mode Register               | 80   |

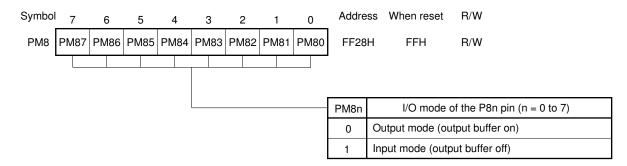

| 5-14.    | Format of the Port 9 Mode Register               | 81   |

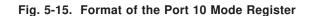

| 5-15.    | Format of the Port 10 Mode Register              | 81   |

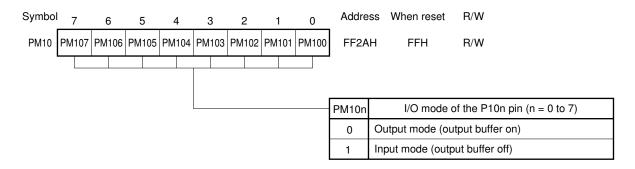

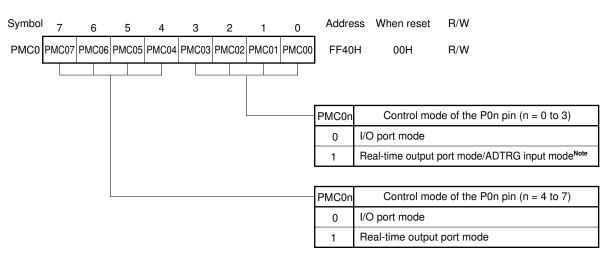

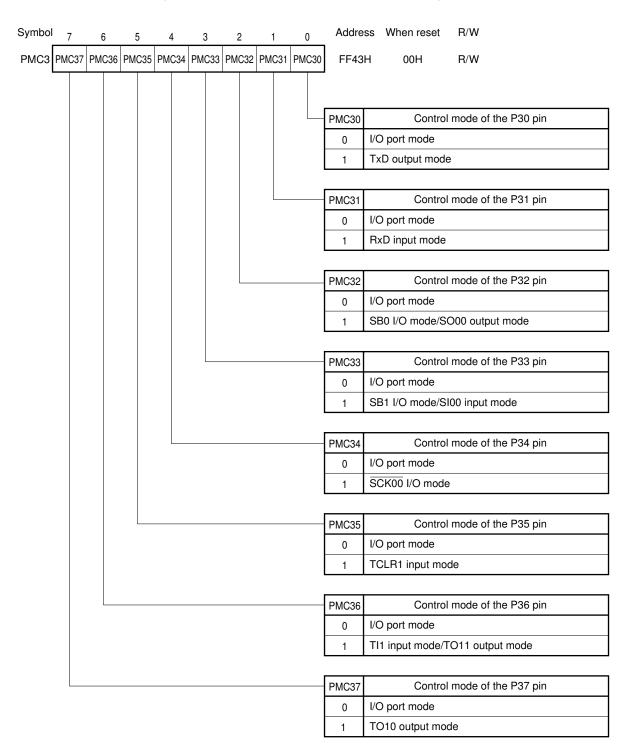

| 5-16.    | Format of the Port 0 Mode Control Register       | 84   |