# D ■ 6427525 0039265 T76 ■ NECE µPD78352 Family (µPD78350/352A/P352) 16-/8-Bit, K-Series Microcontrollers With Real-Time Output Ports

September 1993

## Description

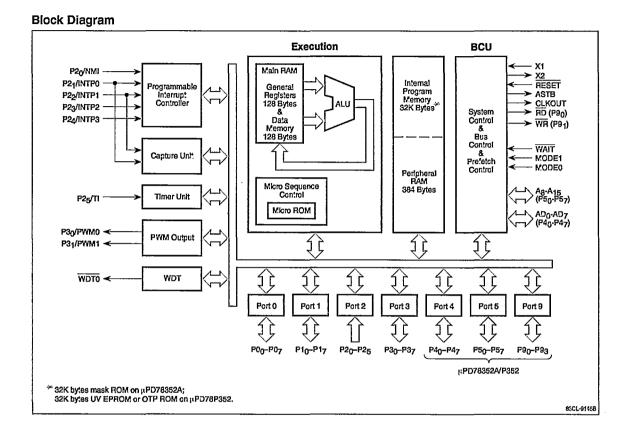

The  $\mu$ PD78350,  $\mu$ PD78352A, and  $\mu$ PD78P352 are members of the K-Series<sup>®</sup> of microcontrollers. These 16-/8bit microcontrollers—with a minimum instruction time of 125 ns at 32 MHz (160 ns at 25 MHz for the  $\mu$ PD78350)—are designed for high-speed, real-time process control. They feature a 16-bit CPU, an 8-bit external data bus, eight banks of main registers, an advanced interrupt handling facility, and a powerful set of memory-mapped on-chip peripherals. A 16-bit multiply and accumulate instruction provides hardware convolution capability. On-board memory includes 640 bytes of RAM, 32K bytes of mask ROM in the  $\mu$ PD78352A, and 32K bytes of UV EPROM or one-time programmable (OTP) ROM in the  $\mu$ PD78P352.

The advanced interrupt handling facility has four levels of programmable hardware-priority control and three methods of servicing interrupt requests, including vectoring, hardware context switching, and macro service. The macro service facility reduces the CPU overhead involved in servicing peripheral interrupts by transferring data between the memory-mapped special function registers (SFRs) and memory without the use of time consuming interrupt service routines. In addition, the macro service facility can be used to perform certain CPU functions, such as event counting and math-oriented data alterations.

The combination of high-speed hardware convolution capability and context switching, eight register banks, and the macro service facility makes these devices ideal for applications in the hard-disk drive and tape drive markets as well as the automotive and industrial control/robotics markets.

K-Series is a registered trademark of NEC Electronics Inc.

## Features

- □ Complete single-chip microcontroller

- -16-bit ALU

- 640 bytes of RAM

- 32K bytes of mask ROM (µPD78352A)

- 32K bytes of UV EPROM or OTP ROM (µPD78P352)

- □ Powerful instruction set

- 16-bit unsigned and signed multiply

- 16-bit unsigned divide

- 16-bit multiply and accumulate instruction

- 1-bit and 8-bit logic instructions

- String instructions

- Minimum instruction time

- --- 160 ns at 25 MHz (µPD78350) --- 125 ns at 32 MHz (µPD78352A/P352)

- 5-byte instruction prefetch queue

- □ Memory expansion

67E D

- 8085 bus-compatible

- -64K-byte address space

- Large I/O capacity

Up to 30 I/O port lines (µPD78350)

Up to 50 I/O port lines (µPD78352A/P352)

- Memory-mapped, on-chip peripherals (special function registers)

- Timer/counter unit

- 16-bit free-running timer: Two 16-bit capture registers; Two external interrupt/capture lines

- 16-bit timer/event counter: One 16-bit compare register; One external event counter line

- 16-bit interval timer: One 16-bit compare register

- Two 8-bit precision pulse-width modulated (PWM) output lines

- Programmable priority interrupt controller (four levels)

- Three methods of interrupt service

- Vectored interrupts

- Context switching with hardware register bank switch

- Macro service mode with choice of five different functions

- Watchdog timer with dedicated output

- STOP and HALT standby functions

- Single 5-volt power supply

67E D 🗰 6427525 0039266 902 🖬 NECE

# µPD78352 Family

NEC

#### Ordering Information

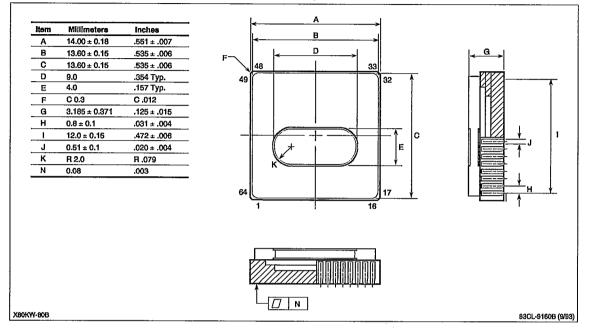

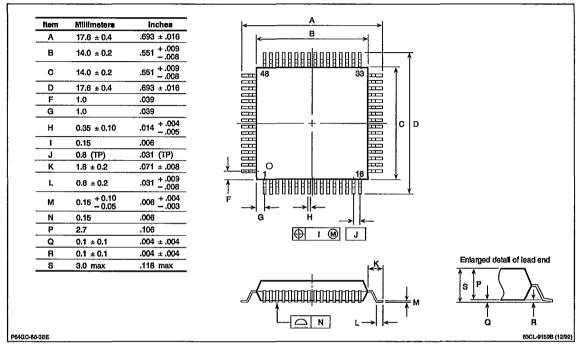

| Part Number       | ROM          | Package                             | Package Drawing<br>P64GC-80-3BE |  |

|-------------------|--------------|-------------------------------------|---------------------------------|--|

| µPD78350GC-3BE    | ROMIess      | 64-pin plastic QFP (3.0-mm height)  |                                 |  |

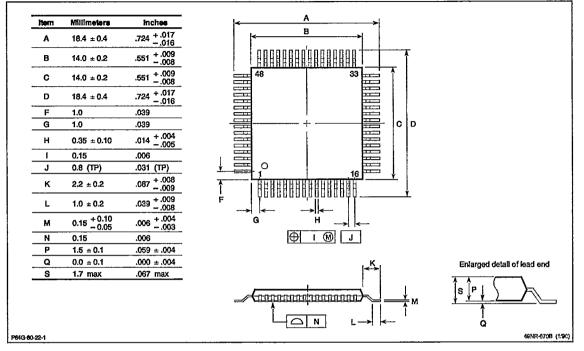

| µPD78352AG-xxx-22 | 32K mask ROM | 64-pin plastic QFP ( 1.7-mm height) | P64G-80-22-1                    |  |

| µPD78P352G-22     | 32K OTP ROM  | -                                   |                                 |  |

| μPD78P352KK       | 32K UV EPROM | 64-pin ceramic LCC with window      | X80KW-80B                       |  |

xxx indicates ROM code suffix.

#### **Pin Configurations**

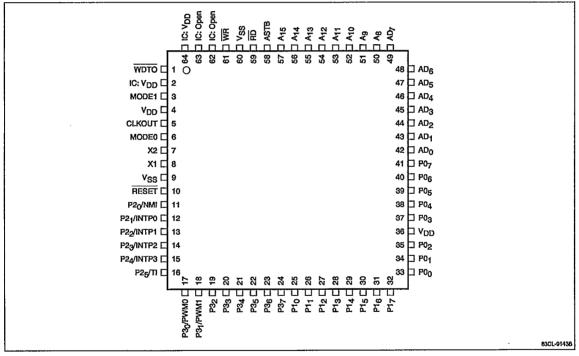

#### 64-Pin Plastic QFP (µPD78350)

### Pin Configurations (cont)

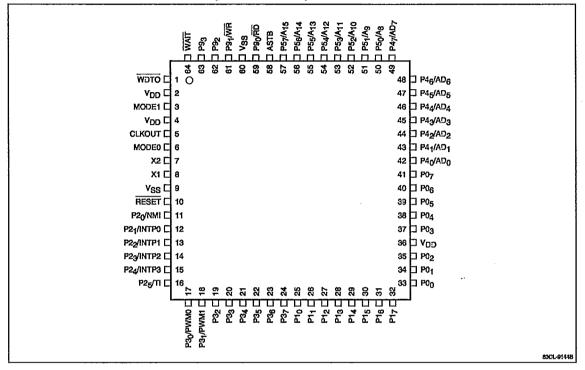

#### 64-Pin Plastic QFP and Ceramic LCC (µPD78352A/P352)

## Pin Functions; Normal Operating Mode

| Symbol                             | Function                                                                                                                                                                                                                  | Alternate Symbol                  | Alternate Function                                            |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------|

| P0 <sub>0</sub> - P0 <sub>7</sub>  | Port 0; 8-bit, bit-selectable I/O port                                                                                                                                                                                    |                                   |                                                               |

| P10 - P17                          | Port 1; 8-bit, bit-selectable I/O port                                                                                                                                                                                    |                                   |                                                               |

| P20                                | Port 2; 6-bit input port                                                                                                                                                                                                  | NMI                               | External nonmaskable interrupt                                |

| P21<br>P22<br>P23<br>P24           |                                                                                                                                                                                                                           | INTPO<br>INTP1<br>INTP2<br>INTP3  | Maskable external interrupts                                  |

| P25                                |                                                                                                                                                                                                                           | TI                                | External input for timer 1                                    |

| P3 <sub>0</sub><br>P3 <sub>1</sub> | Port 3; 8-bit, bit-selectable I/O port                                                                                                                                                                                    | PWM0<br>PWM1                      | Pulse-width modulated outputs                                 |

| P3 <sub>2</sub> - P3 <sub>7</sub>  |                                                                                                                                                                                                                           |                                   |                                                               |

| P4 <sub>0</sub> - P4 <sub>7</sub>  | Port 4; byte-selectable I/O port (µPD78352A/<br>P352)                                                                                                                                                                     | AD <sub>0</sub> - AD <sub>7</sub> | Low-order 8 bits of the multiplexed external address/data bus |

| P5 <sub>0</sub> - P5 <sub>7</sub>  | Port 5; bit-selectable I/O port (µPD78352A/P352)                                                                                                                                                                          | A <sub>8</sub> - A <sub>15</sub>  | High-order 8 bits of the external address bus                 |

| P90                                | Port 9; 4-bit, bit-selectable I/O port                                                                                                                                                                                    | RD                                | External read strobe output                                   |

| P9 <sub>1</sub>                    | (µPD78352A/P352). For 78350, P9 <sub>0</sub> functions as RD and P9 <sub>1</sub> functions as WR signals only. P9 <sub>2</sub>                                                                                            | WR                                | External write strobe output                                  |

| P9 <sub>2</sub><br>P9 <sub>3</sub> | and $P9_3$ are not provided for 78350.                                                                                                                                                                                    |                                   | Internally connected; must be left open<br>(μPD78350).        |

| ASTB                               | Address strobe output; used to latch address for external memory.                                                                                                                                                         |                                   |                                                               |

| CLKOUT                             | Output of the system clock                                                                                                                                                                                                | -                                 |                                                               |

| IC                                 | Internally connected; must be left open.                                                                                                                                                                                  | -                                 |                                                               |

| MODE0                              | Connect to V <sub>DD</sub> for µPD78350 and µPD78P352<br>in programing mode. Connect to V <sub>SS</sub> for normal<br>operation of µPD78352A/P352.<br>The level of this pin cannot be changed during<br>normal operation. | -                                 |                                                               |

| MODE1                              | Always connect to V <sub>SS</sub> . The level of this pin cannot be changed during normal operation.                                                                                                                      | •                                 |                                                               |

| RESET                              | External system reset input                                                                                                                                                                                               | •                                 |                                                               |

| WAIT                               | A low-level input adds wait states to the<br>external bus cycle; used by very-slow memory<br>and/or peripherals (only for 78352A/P352).                                                                                   | -                                 |                                                               |

| WDTO                               | Open-drain output from the watchdog timer                                                                                                                                                                                 | -                                 |                                                               |

| X1                                 | Crystal connection or external clock input                                                                                                                                                                                | -                                 |                                                               |

| X2                                 | Crystal connection or open for external clock                                                                                                                                                                             | -                                 |                                                               |

| V <sub>DD</sub>                    | +5-volt power input                                                                                                                                                                                                       | -                                 |                                                               |

| V <sub>SS</sub>                    | Ground                                                                                                                                                                                                                    | -                                 |                                                               |

. .....

----

# µPD78352 Family

# NEC

## FUNCTIONAL DESCRIPTION

## **Central Processing Unit**

The central processing unit (CPU) of the  $\mu$ PD78352 family features 16-bit arithmetic including 16 x 16-bit multiply, both unsigned and signed, and 32 x 16-bit unsigned divide (producing a 32-bit quotient and a 16-bit remainder). The signed multiply executes in 1.12  $\mu$ s and the divide in 3.44  $\mu$ s at 25 MHz (0.875 and 2.69  $\mu$ s, respectively, for  $\mu$ PD78352A/P352 at 32 MHz).

Also, a multiply-and-accumulate instruction, "MACW n," performs a signed multiply on factors from a pair of tables and sums the results in the 32-bit register AXDE. The total execution time for 10 terms is 17.2  $\mu$ s at 25 MHz for the  $\mu$ PD78350 and 13.44  $\mu$ s at 32 MHz for the  $\mu$ PD78352A/P352.

A CALLT vector table and a CALLF area decrease the number of bytes in the call instructions for commonly used subroutines. A 1-byte call instruction can access up to 32 subroutines through their addresses in the CALLT vector table. A 2-byte call instruction can access any routine beginning in a specific CALLF area.

The internal system clock ( $f_{CLK}$ ) is generated by dividing the oscillator frequency by 2. Therefore, at the maximum oscillator frequency of 25 MHz for the  $\mu$ PD78350, the clock is 12.5 MHz. Since instructions execute in two or more cycles, the minimum instruction time is 160 ns. For the  $\mu$ PD78352A/P352 running at 32 MHz, the clock is 16 MHz and the minimum instruction time is 125 ns.

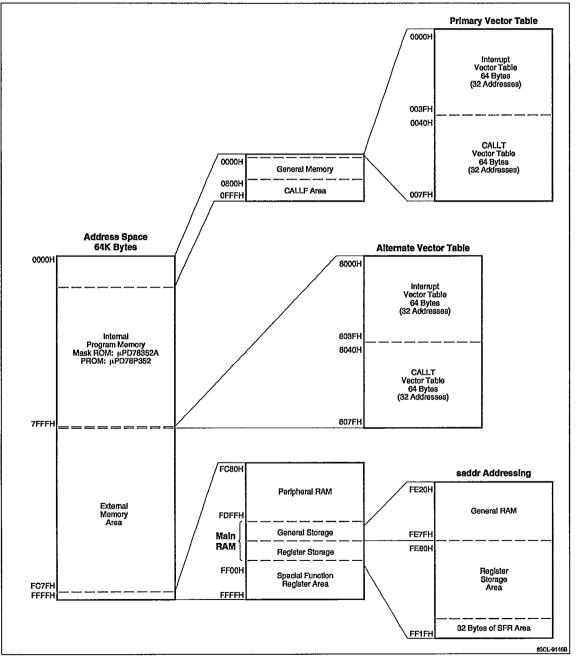

## **Internal RAM**

The  $\mu$ PD78352 family has total of 640 bytes of internal RAM. The upper 256-byte area (FE00H-FEFFH) features high-speed access of one or two internal system clocks per word of data depending on the addressing mode and is known as "Main RAM." The remainder (FC80H-FDFFH) is accessed at the same speed as external memory (1 byte per three internal system clocks) and is known as "Peripheral RAM." The general register banks and the macro service control words are stored in Main RAM. The remainder of Main RAM and any unused register bank locations are available for general storage.

#### Main RAM Access Speed

| Access Mode     | Internal System Clocks (f <sub>CLK</sub> ) |

|-----------------|--------------------------------------------|

| Memory access   | 2                                          |

| Saddr access    | 1                                          |

| Register access | 1                                          |

## Internal Program Memory

The  $\mu$ PD78352A contains 32K bytes of mask ROM;  $\mu$ PD78P352 contains 32K bytes of UV EPROM or onetime programmable ROM. Instructions are fetched from this program memory at a maximum rate of 1 byte every two internal system clocks. The  $\mu$ PD78350 does not have internal program memory.

### **External Memory**

The  $\mu$ PD78352 family has a 64K-byte address space. The  $\mu$ PD78352A/P352 can access 0, 256, 4K, 16K, or 32K bytes of external memory in the area from 8000H to FDFFH. External memory can be either ROM, RAM, or peripheral as required. The  $\mu$ PD78352A/P352 has an 8-bit wide external data bus and a 16-bit wide external address bus. The low-order 8 bits of the address bus are multiplexed to provide the 8-bit data bus at I/O port 4.

High-order address bits are taken from port 5 as required. Address latch, read, and write strobes are also provided. In the  $\mu$ PD78352A/P352, the memory mode register (MM) controls the size of the external memory It can be programmed to use 0, 4, 6, or 8 bits from port 5 for the high-order address. Any remaining port 5 bits can be used for I/O.

The  $\mu$ PD78350 does not have ports 4 and 5. It has eight dedicated high-order address lines and eight dedicated address/data lines. All memory below address FC80H must be external, and the MM register is not used.

The programmable wait control register (PWC) allows the programmer to specify one or two additional wait states if they are required for slow-speed memory or external peripheral devices. These wait states for internal and external memory are specified independently in 16K-blocks. If additional wait states are required, an external WAIT pin is provided.

In addition, by using the AW0 and AW1 bits of the PWC register, the width of the ASTB signal can be increased by one cycle to allow more precharge time for dynamic RAMs or more address decoding time. This address wait signal can be enabled in 32K-byte blocks. See figure 1.

#### Figure 1. Programmed Wait Control Register

| 15                   |           |   |         |           |           |                | 8    | 7           |         |             |      |          |         |       | 0           |

|----------------------|-----------|---|---------|-----------|-----------|----------------|------|-------------|---------|-------------|------|----------|---------|-------|-------------|

| AW1                  | AW0       | 0 | 0       | 0         | 0         | 0              | 0    | PWC7        | PWC6    | PWC5        | PWC4 | PWC3     | PWC2    | PWC1  | PWC0        |

| 16K Mem              | ory Block | : | Wait Co | ontrol Re | egister l | Bits           | Wait | States      | Data Ac | cess Cl     | ocks | Fetch Cy | cle Mod | e Fet | ch Cloci    |

| 0000H-3F             | FFH       |   | PWC     | 1, PWC0   |           | 00<br>01<br>10 |      | 0<br>1<br>2 |         | 3<br>4<br>5 |      | No       | rmal    |       | 3<br>4<br>5 |

|                      |           |   |         |           |           | 11             |      | 0           |         | 4           |      | High-    | speed   |       | 2           |

| 4000H-7F             | FFH       |   | PWC     | 3, PWC2   |           | 00<br>01<br>10 |      | 0<br>1<br>2 |         | 3<br>4<br>5 |      | No       | rmal    |       | 3<br>4<br>5 |

|                      |           |   |         |           |           | 11             |      | 0           |         | 4           |      | High-    | speed   |       | 2           |

| 3000H-BF             | FFH       |   | PWC     | 5, PWC4   |           | 00<br>01<br>10 |      | 0<br>1<br>2 |         | 3<br>4<br>5 |      | No       | rmal    |       | 3<br>4<br>5 |

|                      |           |   |         |           | Ī         | 11             | -    |             |         | N/A         |      | N        | I/A     |       | N/A         |

| C000H-FC<br>*FFD0H-F |           |   | PWC     | 7, PWC6   |           | 00<br>01<br>10 |      | 0<br>1<br>2 |         | 3<br>4<br>5 |      | No       | rmal    |       | 3<br>4<br>5 |

|                      |           |   |         |           |           | 11             | -    | -           |         | N/A         |      | N        | I/A     |       | N/A         |

| FC80H-FI             | OFFH      |   | PWC     | 7, PWC6   |           | 00<br>01<br>10 |      | 0<br>0<br>0 |         | 3<br>3<br>3 |      | No       | rmal    |       | 3<br>3<br>3 |

|                      |           |   |         |           |           | 11             | -    | _           |         | N/A         |      | N        | I/A     |       | N/A         |

\* Data in the SFR external access area, FFD0H-FFDFH, cannot be fetched.

| 32K Memory Block | Wait Control Register Bit | Address Wait |          |

|------------------|---------------------------|--------------|----------|

| 0000H-7FFFH      | AW0                       | 0            | Disabled |

|                  |                           | 1            | Enabled  |

| 8000H-FC7FH      | AW1                       | 0            | Disabled |

|                  |                           | 1            | Enabled  |

# N E C ELECTRONICS INC

## 67E D 🖬 6427525 0039272 106 MINECE

NFC

# µPD78352 Family

## **Program Fetch**

The  $\mu$ PD78352 family devices allow opcode fetch in the area between 0000H and FDFFH; they contain a 5-byte instruction prefetch queue.The bus control unit can fetch an instruction byte from memory during cycles in which the execution unit is not using the memory bus. If the instruction byte is fetched from on-chip memory, two internal system clocks are required for each byte, and the queue can hold 5 bytes. If the instruction is fetched from external memory, three internal system clocks are required for each byte, and the queue can hold 5 bytes. If the instruction is fetched from external memory, three internal system clocks are required for each byte, and the queue can hold 3 bytes. For programs located in internal memory, the PWC register also can be programmed to allow 1 byte to be fetched every two, three, four, or five internal system clocks.

### **CPU Control Registers**

**Program Counter.** The program counter is a 16-bit register that holds the address of the next instruction to be executed. After reset line goes high, the program counter is loaded with the address stored in locations 0000H and 0001H.

**Stack Pointer.** The stack pointer is a 16-bit register that holds the address of the last item pushed onto the stack. It is decremented before new data is pushed onto the stack and incremented after data is popped off the stack.

**CPU Control Word.** The CPU control word (CCW) selects the origin of the interrupt vector and CALLT tables. If the TPF bit (bit 1) is zero, the origin is 0000H; if the TPF bit is one, the origin is 8000H. The CCW is a special function register located at address FFC1H. The addresses of the vectors for the RESET input, operation-code trap, and BRK instruction are fixed at 0000H, 003CH, and 003EH, respectively, and are not altered by the TPF bit.

**Program Status Word.** The program status word (PSW) is a 16-bit register containing flags that are set or reset depending on the results of an instruction. This register can be written to or read from 8 bits at a time. The high-order 8 bits are called the PSWH and the low-order 8 bits are called the PSWL. The individual flags can also be manipulated on a bit-by-bit basis. The assignment of PSW bits follows.

|                                                        | 7    | 6                                                  | 5                                                                 | 4                                                                                        | 3                                                          | 2                                               | 1                                      | 0  |

|--------------------------------------------------------|------|----------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------|----------------------------------------|----|

| PSWH [                                                 | UF   | RBS2                                               | RBS1                                                              | RBS0                                                                                     | 0                                                          | 0                                               | 0                                      | 0  |

|                                                        | 7    | 6                                                  | 5                                                                 | 4                                                                                        | 3                                                          | 2                                               | 1                                      | 0  |

| PSWL [                                                 | S    | z                                                  | RSS                                                               | AC                                                                                       | IE                                                         | P/V                                             | 0                                      | CY |

| UF<br>RBS2-1<br>S<br>Z<br>RSS<br>AC<br>IE<br>P/V<br>CY | 7BS0 | Acti<br>Sigr<br>Zerc<br>Reg<br>Aux<br>Inte<br>Pari | n flag (<br>b flag )<br>ister s<br>iliary (<br>rrupt e<br>ty or a | ister b<br>(1 if las<br>(1 if las<br>set sele<br>carry f<br>enable<br>arithme<br>(or 1-b | st resu<br>st resu<br>action<br>lag (c<br>.flag<br>etic ov | ult was<br>ult was<br>flag<br>arry o<br>verflow | s nega<br>s zero)<br>ut of 3<br>v flag | ,  |

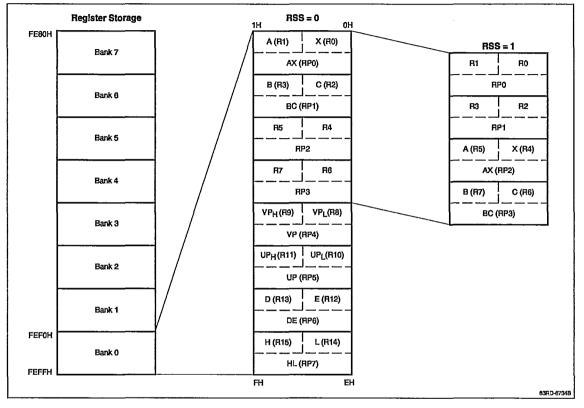

#### **General Registers**

There are sixteen 8-bit general registers, which can also be paired to function as 16-bit registers. A complete set of 16 registers is mapped into each of eight program-selectable register banks stored in Main RAM. Three bits in the PSW specify the active register bank.

Registers have functional names (like A, X, B, C for 8-bit registers and AX, BC for 16-bit registers) and absolute names (like R1, R0, R3, R2 for 8-bit registers and RP0, RP1 for 16-bit registers). Each instruction determines whether a register is referred to by functional or absolute name and whether it is 8 or 16 bits.

Two possible relationships may exist between the absolute and functional names of the first four register pairs. The RSS bit in the PSW determines which of these is active at any time. The effect is that the accumulator and counter registers can be saved, and a new set can be specified by toggling the RSS bit. Figure 2 illustrates the general register configuration.

# µPD78352 Family

Figure 2. General Registers

## Addressing

The  $\mu$ PD78352 family features 1-byte addressing of both the special function registers and the portion of on-chip RAM from FE20H to FEFFH. The 1-byte sfr addressing accesses the entire SFR area, while the 1-byte saddr addressing accesses the first 32 bytes of the SFR area and 224 bytes of the Main RAM.

The 16-bit SFRs and words of memory in these areas can be addressed by 1-byte saddrp addressing, which is valid for even addresses only. Since many instructions use 1-byte addressing, access to these locations is almost as fast and as versatile as access to the general registers. There are nine addressing modes for data in main memory: direct, register, register indirect with autoincrement or autodecrement, saddr, saddr indirect, SFR, based, indexed, and based indexed. There are also 8-bit and 16-bit immediate operands. Figure 3 is the memory map of the  $\mu$ PD78352 family. N E C ELECTRONICS INC 67E D 6427525 0039274 TA9 MECF

EC

# µPD78352 Family

10

# µPD78352 Family

### **Special Function Registers**

The input/output ports, timers, capture and compare registers, and mode and control registers for both the peripherals and the CPU are collectively known as special function registers. They are all memorymapped between FF00H and FFFFH and can be accessed either by main memory addressing or by 1-byte SFR addressing. All can be read under program control, and most can also be written. They are either 8 or 16 bits, as required, and many of the 8-bit registers are capable of single-bit access as well.

Locations FFD0H through FFDFH are known as the external access area. Registers in external circuitry, interfaced and mapped to these addresses, can be addressed with SFR addressing. Table 1 lists the special function registers.

### Table 1. Special Function Registers

|             |                                    |        |     | Acc | ess Units ( | Bits) |                   |  |

|-------------|------------------------------------|--------|-----|-----|-------------|-------|-------------------|--|

| Address     | Register (SFR)                     | Symbol | R/W | 1   | 8           | 16    | State After Reset |  |

| FF00H       | Port 0                             | P0     | R/W | х   | x           | _     | Undefined         |  |

| FF01H       | Port 1                             | P1     | R/W | x   | x           |       | Undefined         |  |

| FF02H       | Port 2                             | P2     | R   | x   | x           | _     | Undefined         |  |

| FF03H       | Port 3                             | P3     | R/W | x   | x           | _     | Undefined         |  |

| FF04H       | Port 4 (Note 1)                    | P4     | R/W | x   | x           | _     | Undefined         |  |

| FF05H       | Port 5 (Note 1)                    | P5     | R/W | x   | x           | _     | Undefined         |  |

| FF09H       | Port 9 (Note 1)                    | P9     | R/W | x   | x           | _     | Undefined         |  |

| FF10H-FF11H | Compare register 00                | CT00   | R/W |     | _           | x     | Undefined         |  |

| FF12H-FF13H | Compare register 01                | CT01   | R/W | _   | _           | x     | Undefined         |  |

| FF14H-FF15H | Compare register 10                | CM10   | R/W | _   | -           | x     | Undefined         |  |

| FF1EH-FF1FH | Compare register 20                | CM20   | R/W | _   |             | ×     | Undefined         |  |

| FF20H       | Port 0 mode register               | PMO    | R/W | x   | x           |       | FFH               |  |

| FF21H       | Port 1 mode register               | PM1    | R/W | x   | x           |       | FFH               |  |

| FF23H       | Port 3 mode register               | PM3    | R/W | x   | x           |       | FFH               |  |

| FF25H       | Port 5 mode register (Note 1)      | PM5    | R/W | x   | x           |       | FFH               |  |

| FF29H       | Port 9 mode register (Note 1)      | PM9    | R/W | x   | x           |       | xFH               |  |

| FF30H-FF31H | Timer register 0                   | TMO    | R   | _   | _           | x     | 00H               |  |

| FF32H-FF33H | Timer register 1                   | TM1    | R   |     | -           | x     | 00H               |  |

| FF34H-FF35H | Timer register 2                   | TM2    | R   | _   | _           | x     | 00H               |  |

| FF38H       | Timer control register 0           | TMCO   | R/W | x   | x           |       | 00H               |  |

| FF39H       | Timer control register 1           | TMC1   | R/W | x   | x           |       | 00H               |  |

| FF3CH       | External interrupt mode register 0 | INTMO  | R/W | x   | x           |       | 00H               |  |

| FF3DH       | External interrupt mode register 1 | INTM1  | R/W | x   | x           |       | 00H               |  |

| FF43H       | Port 3 mode control register 0     | PMC3   | R/W | x   | x           |       | 00H               |  |

| FF62H       | Port read control register         | PRDC   | R/W | x   | x           |       | 00H               |  |

| FF64H       | PWM control register               | PWMC   | R/W | x   | x           |       | 00H               |  |

| FF66H       | PWM buffer register 0              | PWM0   | R/W | x   | x           |       | Undefined         |  |

| FF6EH       | PWM buffer register 1              | PWM1   | R/W | x   | x           | _     | Undefined         |  |

| FFA8H       | In-service priority register       | ISPR   | R   | x   | x           |       | OOH               |  |

| FFAAH       | Interrupt mode control register    | IMC    | R/W | x   | x           |       | 80H               |  |

| FFACH       | Interrupt mask flag register       | MKL    | R/W | x   | x           |       | <b>7</b> FH       |  |

|             |                                    |        |     |     |             |       |                   |  |

## Table 1. Special Function Registers (cont)

|             |                                       |        |     | Acce | ss Units ( | (Bits) |                   |

|-------------|---------------------------------------|--------|-----|------|------------|--------|-------------------|

| Address     | Register (SFR)                        | Symbol | R/W | 1.   | 8          | 16     | State After Reset |

| FFACH-FFADH | Interrupt mask flag register (Note 2) | МК     | R/W |      | -          | х      | xx7FH             |

| FFCOH       | Standby control register (Note 3)     | STBC   | R/W |      | x          |        | 0000 x000B        |

| FFC1H       | CPU control word                      | CCW    | R/W | x    | x          |        | 00H               |

| FFC2H       | Watchdog timer mode register (Note 3) | WDM    | R/W | _    | x          | _      | 00H               |

| FFC4H       | Memory expansion mode register        | MM     | R/W | x    | x          | -      | 00H               |

| FFC6H-FFC7H | Programmable wait control register    | PWC    | R/W | _    |            | x      | COAAH             |

| FFD0H-FFDFH | External access area                  | _      | R/W | x    | x          |        | Undefined         |

| FFEOH       | Interrupt control register (INTOV)    | OVIC   | R/W | x    | x          |        | 43H               |

| FFE1H       | Interrupt control register (INTPO)    | PICO   | R/W | x    | x          | _      | 43H               |

| FFE2H       | Interrupt control register (INTP1)    | PIC1   | R/W | x    | x          | _      | 43H               |

| FFE3H       | Interrupt control register (INTCM10)  | CMIC10 | R/W | х    | x          |        | 43H               |

| FFE4H       | Interrupt control register (INTCM20)  | CMIC20 | R/W | x    | x          |        | 43H               |

| FFE5H       | Interrupt control register (INTP2)    | PIC2   | R/W | x    | x          |        | 43H               |

| FFE6H       | Interrupt control register (INTP3)    | PIC3   | R/W | x    | x          | _      | 43H               |

67F D

Notes:

(1) µPD78352A/P352 only.

(2) Used only when a word is accessed by an instruction with the sfrp operand. (3) These are protected registers, which can be written by a special instruction only.

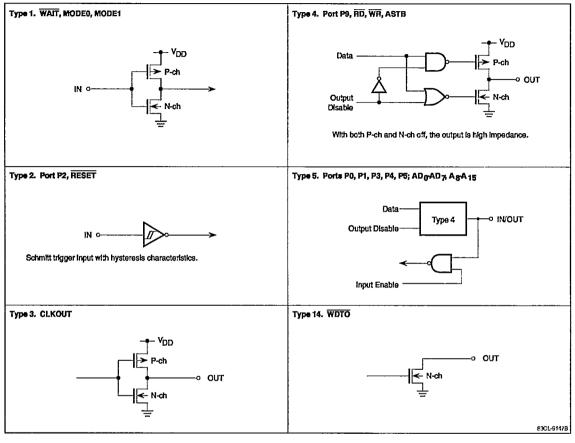

### Input/Output Ports

The  $\mu$ PD78350 has four I/O ports providing a total of 30 I/O lines. The  $\mu$ PD78352A/P352 have an additional three I/O ports for a total of 50 I/O lines.

Ports P0, P1, and P3 are 8-bit input/output ports and P2 is a 6-bit input port. All the bits in P0, P1, and P3 can be individually selected for either input or output using port mode registers PM0, PM1, and PM3. Bits P3<sub>0</sub> and P3<sub>1</sub> can also be programmed for use as PWM outputs PWM0 and PWM1 by using port 3 mode control register PMC3.

Port P2 functions only in the control mode as input pins for the NMI signal, the INTP0 to INTP3 interrupt signals, and the external count clock for timer 1 (TI). However, any masked interrupt automatically becomes an input line and the state of all the pins can be read by the program using a read instruction to port 2. Each pin of P2 can be programmed for rising, falling, or both rising and falling edge detection.

The output level of the P0, P1, and P3 I/O pins can be tested to determine whether they agree with the contents of the output latch. When the low-order bit of port read control register PRDC is set to 1, the output level of the I/O pins can be read with the port still in the output mode. These data values can be compared with the data known to be in the output latch to determine if the port is functioning correctly. Figure 4 shows the structure of each port pin.

# µPD78352 Family

Figure 4. I/O Circuits

NEC

The three additional input/output ports in the  $\mu$ PD78352A/P352 are ports P4, P5, and P9. These ports are available if external memory or memory-mapped external circuitry is not being used. Port 4 is shared with the low-order address/data bus (AD<sub>0</sub> to AD<sub>7</sub>) and is byte-selectable for input or output. Port 5 is shared with the high-order address bus (A<sub>8</sub> to A<sub>15</sub>). Depending on the amount of external memory used, either 8, 6, 4, or 0 bits are available for bit-selectable I/O. Port 9 is a 4-bit, bit-selectable I/O port. Two of its pins are shared with the read and write strobes.

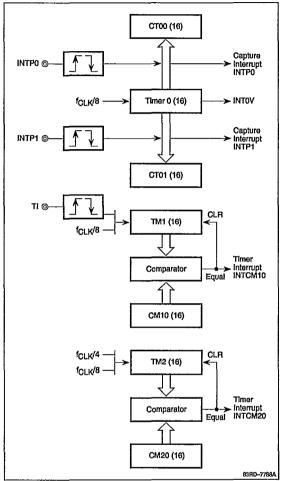

### Timers

The  $\mu$ PD78352 family has three 16-bit timers. Two of them count only the internal system clock; the third counts either the internal system clock or external events. Refer to the block diagram, figure 5.

Timer 0 is a 16-bit, free-running counter that counts the internal system clock ( $f_{CLK}/8$ ) and generates an interrupt request (INTOV) when it overflows. It also has two associated capture registers, CT00 and CT01. The timer value can be captured in synchronization with external interrupt lines INTP0 and INTP1, respectively. These lines can be programmed to trigger interrupts as well.

Timer 1 is a 16-bit counter serving as an interval timer or an event counter. It can count either the internal system clock ( $f_{CLK}$ /8) or external events sensed on the TI line. It has an associated comparator register, CM10. When the counter contents match the CM10 contents, the counter is cleared to 0, and an interrupt request (INTCM10) is generated. The counter continues to count until disabled by software.

Timer 2 is a 16-bit counter that serves as an interval timer. It can be programmed to count the internal system clock ( $f_{CLK}/4$  or  $f_{CLK}/8$ ). It also has an associated comparator register, CM20. When the counter contents match the CM20 contents, the counter is cleared to 0 and an interrupt request (INTCM20) is generated. The counter continues to count until disabled by software.

#### Figure 5. Timers Block Diagram

N E C ELECTRONICS INC

# **µPD78352** Family

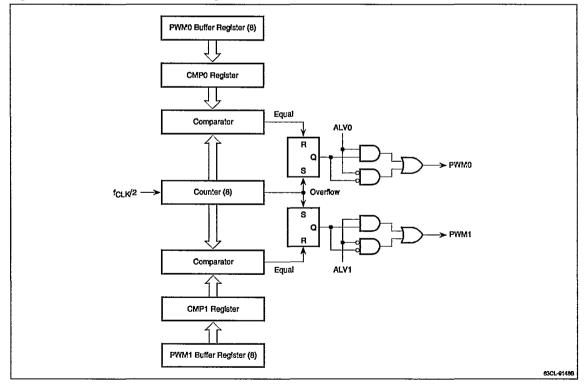

## **Pulse-Width Modulated Outputs**

The µPD78352 family has two high-speed, pulse-width modulated (PWM) outputs. A single 8-bit, free-running counter counts the internal system clock for k/2 and serves both outputs. For the µPD78350 running at 25 MHz ( $f_{CLK} = 12.5$  MHz), the resolution is 160 ns and the repetition rate is 24.4 kHz. For the µPD78352A/P352 running at 32 MHz (f<sub>CLK</sub> = 16 MHz), the resolution is 125 ns and the repetition rate is 31.25 kHz.

The polarity of each output can be selected under program control. Whenever the counter overflows, the CMP0 and CMP1 registers are loaded from their respective PWM buffer registers and each output becomes active. When the counter value matches the value in the associated compare register, that output goes inactive, The two PWM outputs, PWM0 and PWM1, share pins with port 3 bits 0 and 1, respectively.

Figure 6. Pulse-Width Modulated Outputs

67E D

# µPD78352 Family

#### Interrupts

The  $\mu$ PD78352 family has seven maskable hardware interrupt sources: four external and three internal. The four external maskable interrupts share pins with port 2. Two of them, INTP0 and INTP1, can also be used to trigger capture events in registers CT00 and CT01

associated with timer 0. In addition, there are two nonmaskable interrupts, three software interrupts, and reset. The software interrupts, generated by the BRK or BRKCS instruction and the operation code trap, are not maskable. See table 2.

| Table 2 | Interrupt | Sources |

|---------|-----------|---------|

|         | monape    | 0000000 |

| Type of     | Default       | Signal  |                            |          | Macro Service | Vector  | Address |

|-------------|---------------|---------|----------------------------|----------|---------------|---------|---------|

| Request     | Priority      | Name    | Source                     | Location | Control Word  | TPF = 0 | TPF = 1 |

| Software    |               | —       | Operation code trap        | CPU      | _             | 003     | зсн     |

|             | _             | _       | BRK instruction            | CPU      | _             | 00:     | 3EH     |

|             | $\rightarrow$ |         | BRKCS instruction (Note 1) | CPU      | —             | -       | _       |

| Nonmaskable |               | NMI     | NMI input pin              | External |               | 0002H   | 8002H   |

|             |               | INTWDT  | Watchdog timer overflow    | Internal |               | 0004H   | 8004H   |

| Maskable    | 0             | INTOV   | Timer 0 overflow           | Internal | FE06H         | 0006H   | 8006H   |

|             | 1             | INTPO   | INTPO pin                  | External | FE08H         | 0008H   | 8008H   |

|             | 2             | INTP1   | INTP1 pin                  | External | FEOAH         | 000AH   | 800AH   |

|             | 3             | INTCM10 | CM10 coincidence           | Internal | FE0CH         | 000CH   | 800CH   |

|             | 4             | INTCM20 | CM20 coincidence           | Internal | FEOEH         | 000EH   | 800EH   |

|             | 5             | INTP2   | INTP2 pin                  | External | FE10H         | 0010H   | 8010H   |

|             | 6             | INTP3   | INTP3 pin                  | External | FE12H         | 0012H   | 8012H   |

| Reset       | _             | RESET   | RESET pin                  | External | _             |         | 0000H   |

Note:

(1) Initiates context switch

## Interrupt Servicing

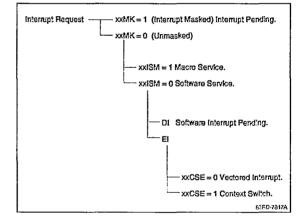

The  $\mu$ PD78352 family provides four levels of programmable hardware priority control and three different methods of handling maskable interrupt requests: standard vectoring, context switching, and macro service. The programmer can choose the priority and mode of servicing each maskable interrupt by using the interrupt control registers.

#### **Interrupt Control Registers**

The  $\mu$ PD78352 family has 10 interrupt control registers. Each maskable interrupt request has its own control register, which includes bits to specify interrupt request, interrupt mask, macro service enable, context switch enable, and priority. Priorities range from 0 (highest) to 3. See figure 7.

There is also a mask flag register, MKL, with a bit for each maskable interrupt. Since each interrupt has two mask bits, the masking of the interrupt is the "or" function of those two bits. Interrupt mode control register IMC can be used to enable or disable nesting of interrupts set to the lowest priority level (level 3). Inservice priority register ISPR is used by the hardware to hold the priority level of the interrupt request currently being serviced. It is manipulated by hardware only, but it can be read by software.

Finally, the IE bit of the program status word also is used to control the interrupts. If the IE bit is 0, all maskable interrupts, but not macro service, are disabled. The IE bit can be set or cleared by the El or DI instruction, respectively, or by direct writing to the PSW. The IE bit is cleared each time an interrupt is accepted.

# µPD78352 Family

### Figure 7. Interrupt Control Register (xxlCx)

| 7      | 6      | 5       | 4       |

|--------|--------|---------|---------|

| xxlFxx | ххМКхх | xxISMxx | xxCSExx |

| 3      | 2      | 1       | 0       |

| 0      | 0      | xxPRx1  | xxPRx0  |

| xxlFxx  |        | Interrupt Request Flag                                 |

|---------|--------|--------------------------------------------------------|

| 0<br>1  |        | No interrupt request<br>Interrupt request received     |

| xxMKxx  |        | Interrupt Mask Flag                                    |

| 0<br>1  |        | Interrupt request enabled<br>Interrupt will be pending |

| xxISMxx |        | Macro Service Enable                                   |

| 0<br>1  |        | Software service<br>Macro service                      |

| XXCSEXX |        | Context Switch Enable                                  |

| 0<br>1  |        | Vector service<br>Context switch                       |

| xxPRx1  | xxPRx0 | Priority Specification                                 |

| 0       | 0      | Priority 0 (highest)                                   |

| 0       | 1      | Priority 1                                             |

| 1       | 0      | Priority 2                                             |

| 1       | 1      | Priority 3                                             |

## Interrupt Priority

The two nonmaskable interrupts, NMI and INTWDT, have priority over all others. Their priority relative to each other is under program control.

Four hardware-controlled priority levels are available for the maskable interrupts. Any one of the four levels can be assigned by software to each of the maskable interrupt lines. Interrupt requests of a priority higher that the processor's current priority level are accepted; requests of the same or lower priority are held pending until the processor's priority state is lowered by a return instruction from the current service routine.

By setting the PRSL bit of the IMC register to zero, it is possible to specify in software that level 3 interrupts (the lowest level) can be accepted when the processor is operating at level 3. This nesting within a level applies to level 3 only.

Interrupt requests programmed to be handled by macro service have priority over all software interrupt service regardless of the assigned priority level, and macro service requests are accepted even when the interrupt enable bit in the PSW is set to the disable state. See figure 8.

The "Default Priorities" listed in table 2 are fixed by hardware; they are effective only when it is necessary to choose between two interrupt requests of the same software-assigned priority. For example, the default priorities would be used after the completion of a high-priority routine if two interrupts of the same lower priority were pending.

Software interrupts, the BRK and BRKCS instructions, and the operation code trap are executed regardless of the processor's priority level and the state of the IE bit. They do not alter the processor's priority level.

Figure 8. Interrupt Service Sequence

## Vectored Interrupt

When vectored interrupt is specified for a given interrupt request, (1) the program status word and the program counter are saved on the stack, (2) the processor's priority is raised to that specified for the interrupt, (3) the IE bit in the PSW is set to zero, and (4) the routine whose address is in the interrupt vector table is entered. At completion of the service routine, the RETI instruction (or RETB instruction for software interrupts) reverses the process, and the  $\mu$ PD78352 family device resumes the interrupted routine.

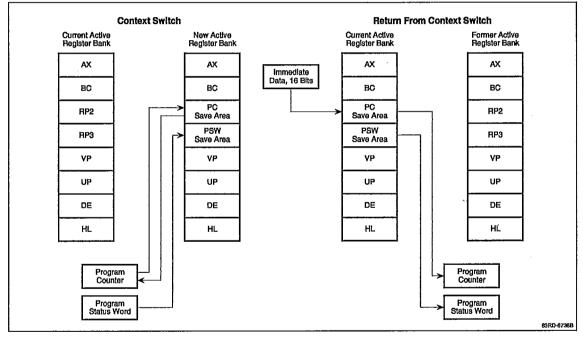

#### **Context Switch**

When context switching (figure 9) is specified for a given interrupt, the active register bank is changed to the register bank specified by the three low-order bits of the word in the interrupt vector table. The program counter is loaded from RP2 of the new register bank,

67E D 🗰 6427525 0039282 055 MINECE

# µPD78352 Family

the old program counter and program status word are saved in RP2 and RP3 of the new register bank, and the IE bit in the PSW is set to zero.

At completion of the service routine, the RETCS instruction for routines entered from hardware requests, or the RETCSB instruction for routines entered from the BRKCS instruction, reverse the process. The old program counter and program status word are restored from RP2 and RP3 of the new register bank. The entry address of the service routine, which must be specified in the 16-bit immediate operand of these return instructions, is stored again in RP2.

#### Macro Service

When macro service is specified for a given interrupt, the macro service hardware temporarily stops the executing program and transfers data between the special function register area and the memory space. Control is then returned to the executing program, providing a completely transparent method of interrupt service. Macro service significantly improves response time and makes it unnecessary to save any registers.

For each request on the interrupt line, one operation is performed, and an 8-bit counter is decremented. When

the counter reaches 0, a software service routine is entered according to its specified priority. Either vectored interrupt or context switch can be specified for entry to this routine, which is known as the macro service completion routine.

Macro service is provided for all of the maskable interrupt requests, and each has a specific macro service control word stored in Main RAM. The function to be performed is specified in the control word.

The  $\mu$ PD78352 family provides five different macro service functions.

N E C ELECTRONICS INC

Described

# 67E D 🖿 6427525 0039283 T91 MINECE

# NEC

# µPD78352 Family

| Function | Description                                                                                                                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EVTCNT   | Event counter. Counts up to 256 events<br>by incrementing or decrementing the<br>macro service counter. When the counter<br>reaches 00H, the software service<br>routine is entered.                    |

| BLKTRS   | Block transfer. Transfers a byte or word<br>of data in either direction between a<br>specified special function register and a<br>buffer in Main RAM (FExx).                                            |

| BLKTRS-P | Block transfer with memory pointer.<br>Transfers a byte or word of data in either<br>direction between a specified special<br>function register and a buffer anywhere<br>in the 64K-byte address space. |

| DTADIF   | Data difference. Stores the difference between the current value of a specified                                                                                                                         |

between the current value of a specified 16-bit special function register and its previous value in a word buffer in Main RAM (FExx).

DTADIF-P Data difference with memory pointer. Stores the difference between the current value of a specified 16-bit special function register and its previous value in a word buffer anywhere in the 64K-byte address space.

## **Standby Modes**

The standby modes, HALT and STOP, reduce power consumption when CPU action is not required. In HALT mode, the CPU is stopped but the system clock continues to run. The HALT mode is released by any unmasked interrupt, an external NMI, or an external reset pulse. In STOP mode, both the CPU and the system clock are stopped, further minimizing power consumption. The STOP mode is released by either an external reset pulse or an external NMI. The HALT and STOP modes are entered by programming the standby control register STBC. This register is a protected location and can be written to only by a special instruction. If the third and fourth bytes of the instruction are not complements of each other, the data is not written and an operation code trap interrupt occurs.

## Watchdog Timer

The watchdog timer protects against inadvertent program loops. A nonmaskable interrupt occurs if the timer is not reset by the program before it overflows. At the same time, the watchdog timer output pin, WDTO, goes active low for a period of 32 system clocks. The WDTO can be connected to the RESET pin or used to control external circuitry. Three program-selectable intervals are available: 10.5, 41.9, and 167.8 ms at 25 MHz; 8.2, 32.8, and 131.1 ms at 32 MHz.

Once started, the timer can be stopped only by an external reset. Watchdog timer mode register WDM is used to select the time interval, to set the relative priority of the watchdog timer interrupt and NMI, and to clear the timer. This register is a protected location and can be written to only by a special instruction. If the third and fourth bytes of the instruction are not complements of each other, the data is not written and an operation code trap interrupt occurs.

#### **External Reset**

The  $\mu$ PD78352 family is reset by taking the RESET pin low. The reset circuit contains a noise filter to protect against spurious system resets caused by noise. On power-up, the RESET pin must remain low until the power supply reaches its operating voltage and the oscillator has stabilized. During reset, the program counter is loaded with the address contained in the reset vector table (addresses 0000H, 0001H); program execution starts at that address upon the RESET pin going high. While RESET is low, all external lines except WDTO, CLKOUT, V<sub>SS</sub>, V<sub>DD</sub>, X1, and X2 are in the high-impedance state.

## **ELECTRICAL SPECIFICATIONS**

Note: Specifications are preliminary for µPD78352A and final for µPD78350/P352.

# Absolute Maximum Ratings

| Supply voltage, V <sub>DD</sub>                                                                                          | –0.5 to +7.0 V                                     |

|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Supply voltage, V <sub>PP</sub>                                                                                          | -0.5 to +13.5 V                                    |

| Input voltage, V <sub>1</sub><br>Except P2 <sub>0</sub> /NMI (A9) of µPD78P352<br>P2 <sub>0</sub> /NMI (A9) of µPD78P352 | –0.5 to V <sub>DD</sub> + 0.5 V<br>–0.5 to +13.5 V |

| Output voltage, V <sub>O</sub>                                                                                           | -0.5 to V <sub>DD</sub> + 0.5 V                    |

| Output current, low; l <sub>OL</sub><br>Each output pin<br>Total                                                         | 4.0 mA<br>100 mA                                   |

| Output current, high; i <sub>OH</sub><br>Each output pin<br>Total                                                        | –1.0 mA<br>–20 mA                                  |

| Operating temperature, T <sub>OPT</sub>                                                                                  | -10 to +70°C                                       |

| Storage temperature, T <sub>STG</sub>                                                                                    | -65 to +150°C                                      |

Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under DC and AC characteristics.

## **Oscillator Conditions**

$T_A = -10$  to 70°C;  $V_{DD} = +5 V \pm 10\%$

| Parameter                 | Symbol         | Max | Unit | Conditions                    |

|---------------------------|----------------|-----|------|-------------------------------|

| Input pin<br>capacitance  | C <sub>I</sub> | 20  | pF   | f = 1 MHz;<br>unmeasured pins |

| Output pin<br>capacitance | Co             | 20  | pF   | returned to 0 V               |

| I/O pin<br>capacitance    | с <sub>ю</sub> | 20  | pF   | -                             |

|                              |                                            |                                     | μPD7 | 78350 | μPD78352A/P352 |     |      |

|------------------------------|--------------------------------------------|-------------------------------------|------|-------|----------------|-----|------|

| Oscillator                   | Parameter                                  | Symbol                              | Min  | Max   | Min            | Max | Unit |

| Ceramic resonator or crystal | resonator or crystal Oscillation frequency | fxx                                 | 8    | 25    | 8              | 32  | MHz  |

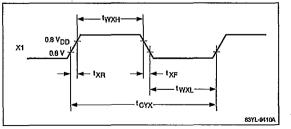

| External clock               | X1 input frequency                         | fx                                  | 8    | 25    | 8              | 32  | MHz  |

|                              | X1 clock cycle time                        | tcyx                                | 40   | 125   | 31.25          | 125 | ns   |

|                              | X1 input rise/fall time                    | t <sub>XR</sub> , t <sub>XF</sub>   | 0    | 10    | 0              | 10  | ns   |

|                              | X1 input high/low level width              | <sup>t</sup> WXH <sup>, t</sup> WXL | 15   | 60    | 10             | 60  | ns   |

67E D

## External Clock

#### **DC Characteristics**

$T_A = -10 \text{ to } +70^{\circ}\text{C}; V_{DD} = +5.0 \text{ V} \pm 10\%; V_{SS} = 0 \text{ V}$

| Parameter                      | Symbol           | Min                   | Тур | Max  | Unit | Conditions                                               |

|--------------------------------|------------------|-----------------------|-----|------|------|----------------------------------------------------------|

| Input voltage, low             | VIL              | 0                     |     | 0.8  | v    | · · · · · · · · · · · · · · · · · · ·                    |

| Input voltage, high            | V <sub>IH1</sub> | 2.2                   |     |      | V    | (Note 1)                                                 |

|                                | V <sub>IH2</sub> | 0.8 V <sub>DD</sub>   |     |      | v    | (Note 2)                                                 |

| Output voltage, low            | VOL              |                       |     | 0.45 | V    | I <sub>OL</sub> = 2.0 mA                                 |

| Output voltage, high           | V <sub>OH</sub>  | V <sub>DD</sub> – 1.0 |     |      | v    | $I_{OH} = -400 \mu A$                                    |

| Input leakage current          | <sup>ي</sup> ر   |                       |     | ±10  | μA   | $V_{l} = 0$ to $V_{DD}$                                  |

| Output leakage current         | ILO              |                       |     | ±10  | μA   | $V_{O} = 0$ to $V_{DD}$                                  |

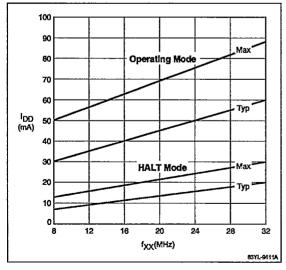

| V <sub>DD</sub> supply current | I <sub>DD1</sub> |                       | 50  | 90   | mA   | Operating mode, µPD78350                                 |

|                                |                  |                       | 60  | 87   | mA   | Operating mode, $\mu$ PD78352A; f <sub>XX</sub> = 32 MHz |

|                                |                  |                       | 80  | 120  | mA   | Operating mode, $\mu$ PD78P352; f <sub>XX</sub> = 32 MHz |

|                                | IDD2             |                       | 25  | 40   | mA   | HALT mode, $\mu$ PD78350; f <sub>XX</sub> = 25 MHz       |

|                                |                  |                       | 20  | 30   | mA   | HALT mode, $\mu$ PD78352A; f <sub>XX</sub> = 32 MHz      |

|                                |                  |                       | 35  | 50   | mA   | HALT mode, $\mu$ PD78P352; f <sub>XX</sub> = 32 MHz      |

| Data retention voltage         | VDDDR            | 2.5                   |     |      | ۷    | STOP mode                                                |

| Data retention current         | RDCO             |                       | 2   | 10   | μA   | STOP mode; V <sub>DDDR</sub> = 2.5 V                     |

|                                |                  |                       | 10  | 50   | μA   | STOP mode; V <sub>DDDR</sub> = 5.0 V ±10%                |

#### Notes:

(1) All except pins in Note 2.

(2) Pins RESET, X1, X2, INTPn, NMI, and TI.

## Power Consumption, 78352A

67E D

■ 6427525 0039286 7TO ■ NECE

# µPD78352 Family

# NEC

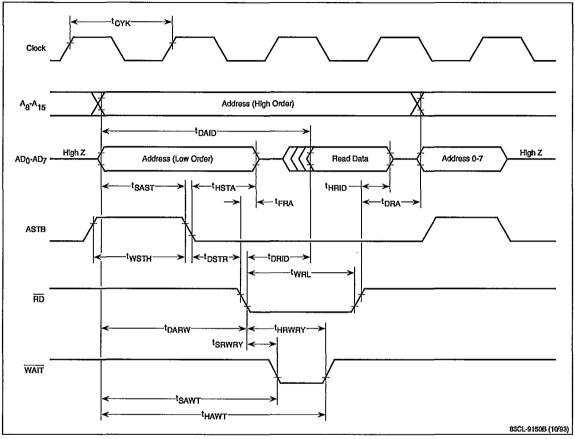

#### **AC Characteristics**

$T_A = -10 \text{ to } + 70^{\circ}\text{C}; V_{DD} = +5.0 \text{ V} \pm 10\%; V_{SS} = 0 \text{ V}$

|                                   |                                       |     | 78350<br>25 MHz |      | 52A/P352<br>32 MHz |      |                                      |

|-----------------------------------|---------------------------------------|-----|-----------------|------|--------------------|------|--------------------------------------|

| Parameter                         | Symbol                                | Min | Max             | Min  | Max                | Unit | Conditions                           |

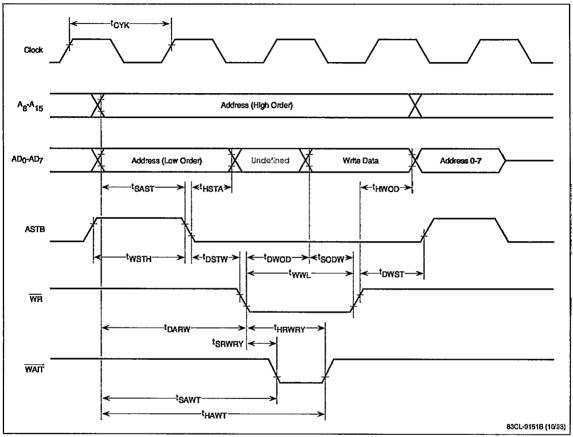

| External Memory Read/Write        | Operation                             |     |                 |      |                    |      |                                      |

| System clock cycle time (Note 1)  | tCYK                                  | 80  | 250             | 62.5 | 250                | ns   | C <sub>L</sub> = 50 pF               |

| Address setup time to ASTB I      | t <sub>sast</sub>                     | 16  |                 | 7    |                    | ns   | C <sub>L</sub> = 100 pF (Note 2)     |

| Address hold after ASTB ↓         | t <sub>HSTA</sub>                     | 26  |                 | 11   |                    | ns   | C <sub>L</sub> = 100 pF              |

| RD I to address floating          | t <sub>FRA</sub>                      |     | 0               |      | 0                  | ns   | C <sub>L</sub> = 100 pF              |

| Address to data input valid       | t <sub>DAID</sub>                     |     | 144             |      | 100                | ns   | C <sub>L</sub> = 100 pF (Notes 2, 3) |

| RD I to data input valid          | t <sub>DRID</sub>                     |     | 76              |      | 49                 | ns   | C <sub>L</sub> = 100 pF (Note 3)     |

| ASTB↓to RD↓delay time             | t <sub>DSTR</sub>                     | 24  |                 | 15   |                    | ns   | C <sub>L</sub> = 100 pF              |

| Data hold time from RD †          | t <sub>HRID</sub>                     | 0   |                 | 0    |                    | ns   | C <sub>L</sub> = 100 pF              |

| RD f to address active            | t <sub>DRA</sub>                      | 26  |                 | 25   |                    | ns   | C <sub>L</sub> = 100 pF              |

| RD width low                      | t <sub>WRL</sub>                      | 90  |                 | 63   |                    | ns   | C <sub>L</sub> = 100 pF (Note 3)     |

| ASTB width, high                  | twsth                                 | 23  |                 | 14   |                    | ns   | C <sub>L</sub> = 100 pF (Note 2)     |

| VR to data output                 | tDWOD                                 |     | 29              |      | 21                 | ns   | C <sub>L</sub> = 100 pF              |

| ASTB↓to ₩R↓delay                  | t <sub>DSTW</sub>                     | 24  |                 | 15   |                    | ns   | C <sub>L</sub> = 100 pF              |

| Data setup time to WR †           | tSODW                                 | 75  |                 | 57   |                    | ns   | C <sub>L</sub> = 100 pF (Note 3)     |

| Data hold time after WR †         | <sup>t</sup> HWOD                     | 8   |                 | 8    |                    | ns   | C <sub>L</sub> = 100 pF              |

| WR width, low                     | twwL                                  | 90  |                 | 57   |                    | ns   | C <sub>L</sub> = 100 pF (Note 3)     |

| VAIT setup time from address      | <sup>t</sup> SAWT                     |     |                 |      | 107                | ns   | C <sub>L</sub> = 100 pF (Note 2, 4)  |

| WAIT setup time from RD I or WR I | tsrwry                                |     | -               |      | 37                 | ns   | C <sub>L</sub> = 100 pF (Note 4)     |

| WAIT hold time from address       | <sup>t</sup> HAWT                     | -   |                 | 149  |                    | កទ   | C <sub>L</sub> = 100 pF (Note 2, 4)  |

| WAIT hold time from RD I or WR I  | tHRWRY                                |     |                 | 80   |                    | ns   | C <sub>L</sub> = 100 pF (Note 4)     |

| ASTB t delay time from WR t       | tDWST                                 | 110 |                 | 78   |                    | ns   | _C <sub>L</sub> = 100 pF             |

| Address to RD I or WR I delay     | tDARW                                 | 89  |                 |      | 69                 | ns   | C <sub>L</sub> = 100 pF              |

| Other Operations                  |                                       |     |                 |      |                    |      |                                      |

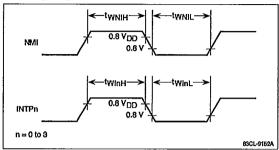

| NMI high/low level width          | twnih<br>twniL                        | 2.5 | <del></del>     | 2.0  |                    | μs   |                                      |

| NTP0 high/low level width         | twich, twici                          | 640 |                 | 500  |                    | ns   | -                                    |

| NTP1 high/low level width         | twitth, twitt.                        | 640 |                 | 500  |                    | ns   | -                                    |

| NTP2 high/low level width         | <sup>t</sup> W12H <sup>, t</sup> W12L | 640 |                 | 500  |                    | ns   | _                                    |

| NTP3 high/low level width         | twish, twisiL                         | 640 |                 | 500  |                    | nŝ   | -                                    |

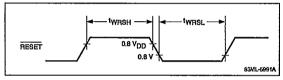

| RESET high/low level width        | twrsh, twrsL                          | 2.5 |                 | 2.0  |                    | μs   | -                                    |

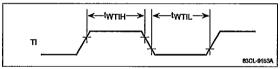

| 'l high/low level width           | twrih, twriL                          | 640 |                 | 500  |                    | ns   |                                      |

#### Notes:

(1)  $t_{CYK}$  equals twice the period of the crystal or external clock input.

(3) No wait states

(4) One external wait state and one internal wait state

# µPD78352 Family

### Timing Dependent on t<sub>CYK</sub>

N E C ELECTRONICS INC

| Symbol             | Calculation Formula                         | Min/Max | Unit |

|--------------------|---------------------------------------------|---------|------|

| tSAST              | (0.5 + a)T - 24                             | Min     | ns   |

| t <sub>HSTA</sub>  | 0.5T – 14<br>0.5T – 20 (Note 1)             | Min     | ns   |

| twsth              | (0.5 + a)T - 17                             | Min     | ns   |

| t <sub>DSTR</sub>  | 0.5T 16                                     | Min     | ns   |

| t <sub>WRL</sub>   | (1.5 + n)T - 30                             | Min     | ns   |

| tDAID              | (2.5 + a + n)T - 56                         | Max     | ns   |

| t <sub>DRID</sub>  | (1.5 + n)T – 44                             | Мах     | ns   |

| t <sub>DRA</sub>   | 0.5T – 14<br>0.5T – 6 (Note 1)              | Min     | ns   |

| tDSTW              | 0.5T – 16                                   | Min     | ns   |

| t <sub>WWL</sub>   | (1.5 + n)T − 30<br>(1.5 + n)T − 36 (Note 1) | Min     | ns   |

| tDWOD              | 0.5T - 10                                   | Max     | ns   |

| t <sub>SODW</sub>  | (1 + n)T – 5                                | Min     | ns   |

| tSAWT              | (a + n)T - 18 (Note 1)                      | Max     | ns   |

| t <sub>HAWT</sub>  | (0.5 + a + n)T-7 (Note 1)                   | Min     | ns   |

| tSRWRY             | (n – 1)T – 25 (Note 1)                      | Max     | ns   |

| t <sub>HRWRY</sub> | (n - 0.5)T - 14 (Note 1)                    | Min     | ns   |

| <sup>t</sup> DARW  | (a + 1)T+9<br>(a +1 )T+7 (Note 1)           | Max     | ns   |

| tDWST              | 1.5T – 10<br>1.5T – 15 (Note 1)             | Min     | ns   |

| twюн               | 8T                                          | Min     | П\$  |

| twici              | 8T                                          | Min     | ns   |

| twith              | 8T                                          | Min     | ns   |

| twiiL              | 8T                                          | Min     | ns   |

| twizh              | 8T                                          | Min     | ns   |

| twi2L              | 8T                                          | Min     | ns   |

| twish              | 8T                                          | Min     | ns   |

| t <sub>WI3L</sub>  | 8T                                          | Min     | ns   |

| twri <del>ll</del> | 8T                                          | Min     | ns   |

| twril.             | 8T                                          | Min     | ns   |

| -                  |                                             |         |      |

#### Notes:

(1) 78352A/P352 only

(2)  $T = t_{CYK}$  (ns)

- (3) When an address wait is inserted, the value of letter "a" is 1. Otherwise, it is 0.

- (4) Letter "n" is the number of wait cycles specified by the external wait pin WAIT and the PWC register.

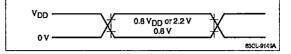

#### **AC Timing Test Points**

\_

N E C ELECTRONICS INC 67E D 🖬 6427525 0039288 573 🖬 NECE

# µPD78352 Family

NI EC

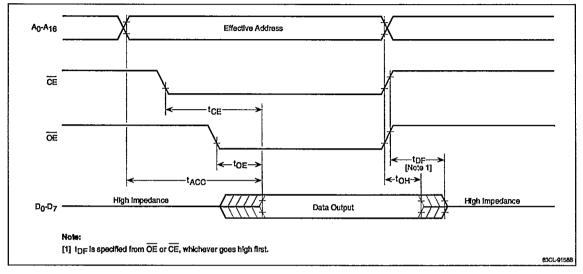

## **Timing Waveforms**

## **Read Operation**

# µPD78352 Family

**Timing Waveforms (cont)**

## Write Operation

67E D

# NEC

# µPD78352 Family

## Timing Waveforms (cont)

#### Interrupt Input

#### Reset Input

#### TI Input

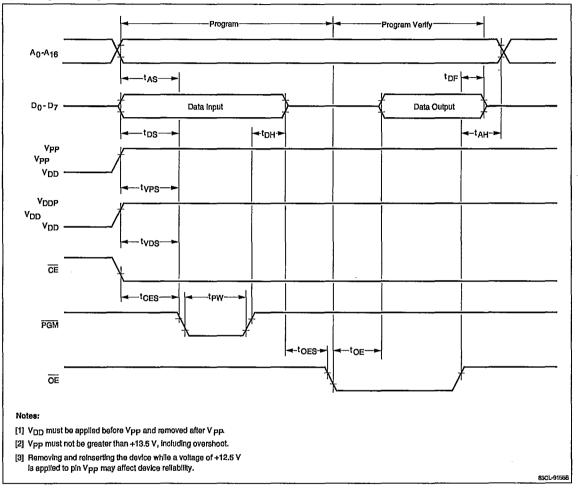

#### Table 4. Operation Modes For Programming

#### RESET PGM MODE1 P21 CE OE D<sub>0</sub> - D<sub>7</sub> Mode MODE0/Vpp VDD Page data latch L L L н L н +12.5 V +6.5 V Data input L L L н н L +12.5 V +6,5 V High impedance Page program Byte program L L L L Н L +12.5 V +6.5 V Data input L L L L L Program verify н +12.5 V +6.5 V Data output Program inhibit L L L Х L L +12.5 V +6.5 V High impedance Х н н L L L L L н +5.0 V +5.0 V Data output Read Ouput disable L L L L н х +5.0 V +5.0 V High impedance L н х х Standby L L +5.0 V +5.0 V High impedance

X can be either H or L.

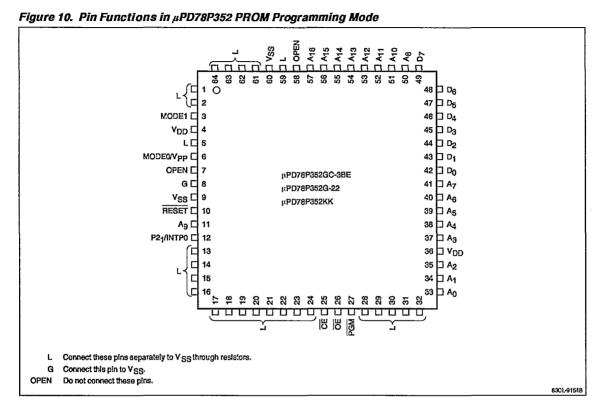

## **PROM PROGRAMMING**

The PROM in the  $\mu$ PD78P352 is one-time programmable (OTP) or ultraviolet erasable (UV EPROM). The 32,758 x 8-bit PROM has the programming characteristics of an NEC  $\mu$ PD27C1001A, including both page and byte programming modes. The MODE0/V<sub>PP</sub>, MODE1, P2<sub>1</sub>, and RESET pins are used to place the  $\mu$ PD78P352 into the PROM programming mode. Table 3 shows the functions of the  $\mu$ PD78P352 pins in normal operating mode and PROM programming mode.

🔲 6427525 0039290 121 🔳 NECE

| Normal Operating<br>Mode                                                                                     | Programming Mode                                                                                                                                        |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P0 <sub>0</sub> - P0 <sub>7</sub> , P5 <sub>0</sub> , P2 <sub>0</sub> ,<br>P5 <sub>1</sub> - P5 <sub>7</sub> | A <sub>0</sub> - A <sub>16</sub>                                                                                                                        |  |  |  |  |

| P4 <sub>0</sub> - P4 <sub>7</sub>                                                                            | D <sub>0</sub> - D <sub>7</sub>                                                                                                                         |  |  |  |  |

| P12                                                                                                          | PGM                                                                                                                                                     |  |  |  |  |

| P1 <sub>1</sub>                                                                                              | CE                                                                                                                                                      |  |  |  |  |

| P1 <sub>0</sub>                                                                                              | ŌĒ                                                                                                                                                      |  |  |  |  |

| MODE0/Vpp                                                                                                    | MODE0/VPP                                                                                                                                               |  |  |  |  |

| MODE1, P2 <sub>1</sub> ,<br>RESET                                                                            | MODE1, P2 <sub>1</sub> ,<br>RESET                                                                                                                       |  |  |  |  |

|                                                                                                              | Normal Operating<br>Mode        P00 - P07, P50, P20,<br>P51 - P57        P40 - P47        P12        P11        P10        MODE0/Vpp        MODE1, P21, |  |  |  |  |

#### Table 3. Pin Functions During PROM Programming

## **PROM Programming Mode**

When +6.5 V is applied to the V<sub>DD</sub> pin and +12.5 V to the MODE0/V<sub>PP</sub> pin, the  $\mu$ PD78P352 enters the PROM programming mode. Operation in this mode is determined by the setting of CE, OE, and PGM pins as indicated in table 4.

## PROM Byte Programming Procedure

Data can be written to the PROM one byte at a time by the following procedure.

- (1) Set the pins not used for programming as indicated in figure 10. Set MODE0/ $V_{PP}$  and  $V_{DD}$  pins to +5 V and MODE1, P2<sub>1</sub>, and RESET pins to 0 V. The  $\overline{CE}$ ,  $\overline{OE}$ , and  $\overline{PGM}$  pins should be high.

- (2) Supply +6.5 V to V<sub>DD</sub> pin and +12.5 V to MODE0/ V<sub>PP</sub> pin. Set CE pin low and OE pin high.

- (3) Provide initial address to pins A<sub>0</sub> A<sub>16</sub>.

- (4) Provide write data.

- (5) Input a 0.1-ms program pulse (active low) to PGM pin.

- (6) Use verify mode (pulse OE low) to test data. If data has been written, proceed to step 8; if not, repeat steps 4–6. If data cannot be written in 10 attempts, go to step 7.

- (7) Classify PROM as defective and cease write operation.

- (8) Increment address.

- (9) Repeat steps 4-8 until last address is programmed.

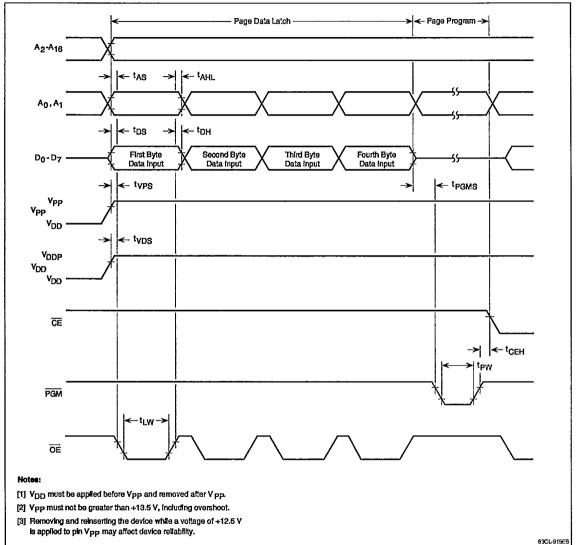

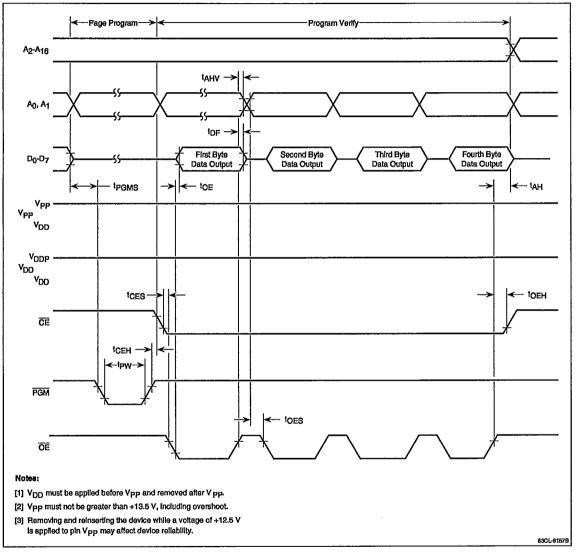

## **PROM Page Programming Procedure**

Data can be written to the PROM four bytes at a time (page programming) by the following procedure.

- (1) Set the pins not used for programming as indicated in figure 10. Set MODE0/ $V_{PP}$  and  $V_{DD}$  pins to +5 V and MODE1, P2<sub>1</sub>, and RESET pins to 0 V. The  $\overline{CE}$ ,  $\overline{OE}$ , and  $\overline{PGM}$  pins should be high.

- (2) Supply +6.5 V to V<sub>DD</sub> pin and +12.5 V to MODE0/ V<sub>PP</sub> pin. Set CE pin low.

- (3) Provide initial page address to pins A<sub>0</sub> A<sub>16</sub>.

- (4) Provide first byte of data and latch it into PROM by pulsing OE low. Continue incrementing address and latching in data until four bytes have been loaded.

- (5) Input a 0.1-ms program pulse (active low) to PGM pin. Data bus D<sub>0</sub> - D<sub>7</sub> is in a high-impedance state.

- (6) Use verify mode (pulse OE low four times) to test four bytes of data. If all four bytes of data have been written, proceed to step 8; if not, repeat steps 4–6. If data cannot be written in 10 attempts, go to step 7.

- (7) Classify PROM as defective and cease write operation.

- (8) Increment address.