# μPD7831xA/78P31xA 16-/8-Bit, Single-Chip CMOS Microcomputers, Real-Time Control Oriented

#### Description

The µPD7831xA family of microcomputers is designed for use in process control. They perform all the usual process control functions and are particularly well-suited for driving stepping motors and dc motors in servo loops. The processors include on-chip memory, timers, input/output registers, and a powerful interrupt handling facility. The µPD78310A/312A is constructed of high-speed CMOS circuitry and operates from a single +5-volt power supply.

The input frequency (maximum 12 MHz) is derived from an external crystal or an external oscillator. The internal processor clock is two-phase, and thus machine states are executed at a rate of 6 MHz. The shortest instructions require three states, making the minimum time 500 ns. The CPU contains a three-byte instruction prefetch queue, which allows a subsequent instruction to be fetched during execution of an instruction that does not reference memory.

Program memory is 8K bytes of mask-programmable ROM ( $\mu$ PD78312A only), and data memory is 256 bytes of static RAM. The  $\mu$ PD78310A is the ROMless version.  $\mu$ PD78P312A is a prototyping chip for  $\mu$ PD78312A. It has an on-chip 8K EPROM instead of a mask ROM.

#### **Features**

- Complete single-chip microcomputer

- 16-bit ALU

- 8K ROM (µPD78312A only)

- 256 bytes RAM

- 1-bit and 8-bit logic

- Instruction prefetch queue

- 16-bit unsigned multiply and divide

- String instructions

- Memory expansion

- -- 8085A bus-compatible

- Total 64K address space

- Large I/O capacity: up to 32 I/O port lines

- □ Extensive timer/counter system

- Two 16-bit up/down counters

- Quadrature counting

- Two 16-bit timers

- Free-running counter with two 16-bit capture

- registers

- Pulse-width modulated outputs

- Timebase counter

- □ Four-channel 8-bit A/D converter

- □ Two 4-bit real-time output ports

- Two nonmaskable interrupts

- Eight hardware priority interrupt levels

- Macroservice facility for interrupts gives the effect of eight DMA channels

- Bidirectional serial port

- Either UART or interface mode

- Dedicated baud rate generator

- Watchdog timer

- Refresh output for pseudostatic RAM

- Programmable HALT and STOP modes

- One-byte call instruction

- On-chip clock generator

- CMOS silicon gate technology

- □ +5-volt power supply

#### Ordering Information

| Part Number          | Package                                            | ROM       |

|----------------------|----------------------------------------------------|-----------|

| μPD78310ACW          | 64-pin plastic shrink DIP                          | ROMless   |

| μPD78310AGF-3BE /    | 64-pin plastic QFP                                 | •         |

| μPD78310AGQ-36       | 64-pin plastic QUIP                                | -         |

| μPD78310AL           | 68-pin plastic PLCC                                | -         |

| μPD78312ACW-xxx      | 64-pin plastic shrink DIP                          | Mask ROM  |

| μPD78312AGF-xxx-3BE  | 64-pin plastic QFP                                 | •         |

| μPD78312AGQ-xxx-36 - | 64-pin plastic QUIP                                | -         |

| μPD78312AL-xxx       | 68-pin plastic PLCC                                | •         |

| μPD78P312ACW         | 64-pin plastic shrink DIP                          | OTP EPROM |

| μPD78P312AGF-3BE     | 64-pin plastic QFP                                 | •         |

| μPD78P312AGQ-36 <    | 64-pin plastic QUIP                                | •         |

| μPD78P312AL          | 68-pin plastic PLCC                                | •         |

| μPD78P312ADW         | 64-pin ceramic shrink<br>DIP with window (350 mil) | EPROM     |

| μPD78P312AR          | 64-pin ceramic QUIP<br>with window                 | •         |

Notes: xxx is the ROM code number.

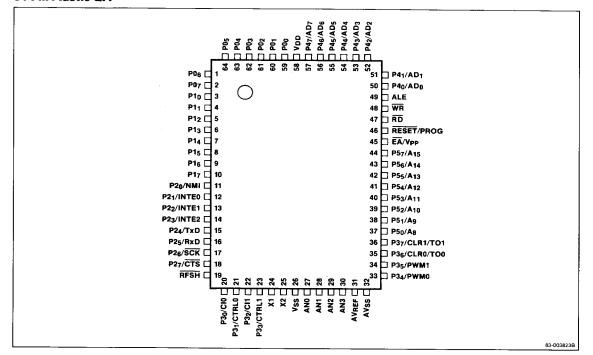

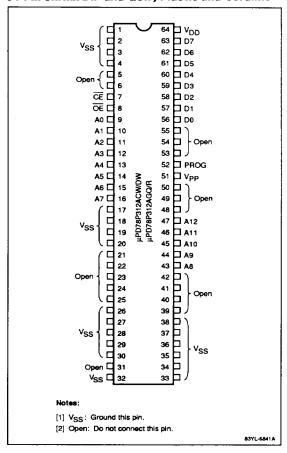

# Pin Configurations

#### 64-Pin Shrink DIP and QUIP, Plastic and Ceramic

| 04-FIII ƏIII IIIK DIF | and t | auir, rii |             | 0 4110 001                       |            |

|-----------------------|-------|-----------|-------------|----------------------------------|------------|

|                       |       |           | _           |                                  |            |

| P0₀ ☐                 | 1     |           | ъ,          | VDD                              |            |

| P01 🗖                 | 2     | 6         | ъb          | P47/AD7                          |            |

| P02 ☐                 | 3     | 6         | ъþо         | P46/AD6                          |            |

| P03 □                 | 4     | 6         | ıþı         | P45/AD5                          |            |

| P04 □                 | 5     | 6         | þ           | P44/AD4                          |            |

| P05 □                 | 6     | 5         | Þ           | P43/AD3                          |            |

| P0 <sub>6</sub> □     | 7     | 5         | ıþ۰         | P42/AD2                          |            |

| P07 🗆                 | 8     | 5         | ı طِ ر      | P41/AD1                          |            |

| P10 □                 | 9     | 5         | ı طِ ءَ     | P4 <sub>0</sub> /AD <sub>0</sub> |            |

| P11 □                 | 10    | 5         | <b>5</b> þ. | ALE                              |            |

| P12 □                 | 11    | 5-        | ۱þ          | WR                               |            |

| P13 □                 | 12    | 5         |             | RD                               |            |

| P14 □                 | 13    | 5         |             | RESET/PROG                       |            |

| P15 □                 | 14    | 5         | ıÞ          | EA/Vpp                           |            |

| P16 □                 | 15    | 5         | ۰Þ          | P57/A15                          |            |

| P17 🗆                 | 16    | 4         | 9 Þ         | P56/A14                          |            |

| P20/NMI □             | 17    | 4         | ₽ Þ         | P55/A13                          |            |

| P21/INTE0             | 18    | 4         | 7 Þ         | P54/A12                          |            |

| P22/INTE1 □           | 19    | 4         | ۶Þ          | P53/A11                          |            |

| P23/INTE2 □           | 20    | 4         | ۶Þ          | P52/A10                          |            |

| P24/TxD □             | 21    | 4         | <b>⁴</b> Þ  | P5 <sub>1</sub> /A <sub>9</sub>  |            |

| P25/RxD □             | 22    |           |             | P5 <sub>0</sub> /A <sub>8</sub>  |            |

| P26/SCK □             | 23    |           |             | P37/CLR1/TO                      |            |

| P27/CTS □             | 24    | 4         | · [         | P36/CLR0/TO                      | 0          |

| RFSH [                | 25    |           | 1_          | P35/PWM1                         |            |

| P3g/C10 [             | ı     |           |             | P34/PWM0                         |            |

| P31/CTRL0             | 27    |           |             | AVSS                             |            |

| P32/CI1               |       |           |             | AVREF                            |            |

| P33/CTRL1             | 29    |           | 62          | AN3                              |            |

| X1 🗆                  | 1     |           | 5 P         | AN2                              |            |

| X2 C                  |       |           | 4Ε          | AN1                              |            |

| Vss C                 | 32    | 3         | 3           | AN0                              |            |

|                       |       |           |             |                                  | 83-003822A |

|                       |       |           |             | ****                             |            |

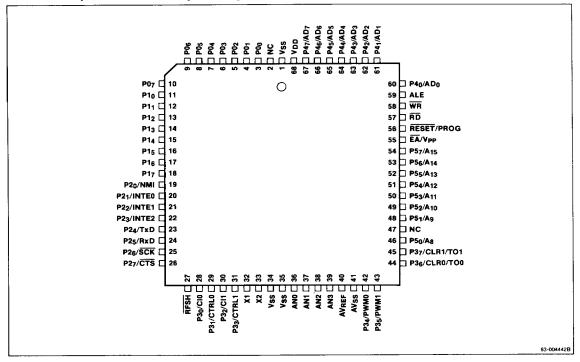

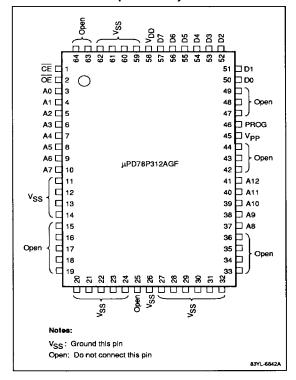

# Pin Configurations (cont)

#### 64-Pin Plastic QFP

#### Pin Configurations (cont)

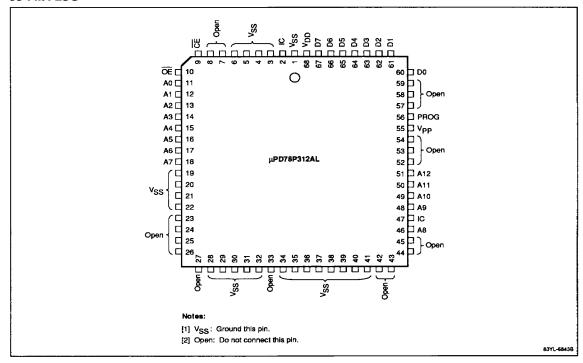

#### 68-Pin PLCC (Plastic Leaded Chip Carrier)

#### Pin Identification

| Symbol                                                             | Function                                           |

|--------------------------------------------------------------------|----------------------------------------------------|

| AN0-AN3                                                            | A/D converter inputs                               |

| ALE                                                                | Address latch enable output                        |

| EA/V <sub>PP</sub>                                                 | External access control input; programming voltage |

| P0 <sub>7</sub> -P0 <sub>0</sub>                                   | I/O port 0                                         |

| P1 <sub>7</sub> -P1 <sub>0</sub>                                   | I/O port 1                                         |

| P2 <sub>0</sub> /NMI                                               | Nonmaskable interrupt input                        |

| P2 <sub>1</sub> -P2 <sub>3</sub> /<br>INTE0-INTE2                  | Maskable interrupt inputs                          |

| P2 <sub>4</sub> /TxD                                               | I/O port 2; serial transmit output                 |

| P2 <sub>5</sub> /R xD                                              | I/O port 2; serial receive input                   |

| P2 <sub>6</sub> /SCK                                               | I/O port 2; serial clock output                    |

| P2 <sub>7</sub> /CTS                                               | I/O port 2; clear to send input                    |

| P3 <sub>0</sub> /CIO                                               | Up/down counter 0 input                            |

| P3 <sub>1</sub> /CTRL0                                             | Up/down counter 0 control input                    |

| P3 <sub>2</sub> /Cl1                                               | Up/down counter 1 input                            |

| P3 <sub>3</sub> /CTRL1                                             | Up/down counter 1 control input                    |

| P3 <sub>4</sub> /PWM0                                              | I/O port 3; pulse width modulated output 0         |

| P3 <sub>5</sub> /PWM1                                              | I/O port 3; pulse width modulated output 1         |

| P3 <sub>6</sub> /CLR0/TO0                                          | I/O port 3; counter 0 clear input; timer 0 output  |

| P3 <sub>7</sub> /CLR1/TO1                                          | I/O port 3; counter 1 clear input; timer 1 output  |

| P4 <sub>7</sub> -P4 <sub>0</sub> /AD <sub>7</sub> -AD <sub>0</sub> | I/O port 4; external address; data bus             |

| P5 <sub>7</sub> -P5 <sub>0</sub> /A <sub>15</sub> -A <sub>8</sub>  | I/O port 5; high address byte output               |

| RD                                                                 | Read strobe output                                 |

| RESET/PROG                                                         | External reset input; PROM programming mode        |

| RFSH                                                               | Refresh output                                     |

| WR                                                                 | Write strobe output                                |

| X1                                                                 | External crystal or external clock input           |

| X2                                                                 | External crystal                                   |

| AV <sub>REF</sub>                                                  | A/D reference voltage                              |

| AV <sub>SS</sub>                                                   | Analog ground                                      |

| $V_{DD}$                                                           | Power supply                                       |

| V <sub>SS</sub>                                                    | Power return                                       |

#### **PIN FUNCTIONS**

#### ANO-AN3 (A/D Converter Inputs)

AN0-AN3 are the four program selectable input channels for the A/D converter.

#### ALE (Address Latch Enable)

ALE is the address latch enable. It is to be used by external circuitry to latch the low-order 8 address bits during the first part of a read or write cycle.

#### EA/Vpp

On  $\mu$ PD78312A, a low on  $\overline{EA}$  enables use of external memory in place of on-chip ROM. The  $\overline{EA}$  pin must be low on  $\mu$ PD78310A. On the  $\mu$ PD78P312A, this pin is used for programming voltage. In normal operation, it must be connected to  $V_{DD}$ .

#### P07-P00 (Port 0)

Port 0 consists of 8 bits, individually programmable for input/output or two 4-bit real-time (timer controlled) output ports.

#### P17-P10 (Port 1)

Port 1 consists of 8 bits, individually programmable for input/output.

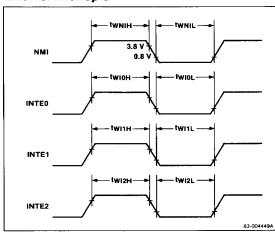

# P2<sub>0</sub>/NMI (Port 2; Nonmaskable Interrupt)

Port P2<sub>0</sub> is dedicated to NMI, the nonmaskable external interrupt request.

# P2<sub>1</sub>-P2<sub>3</sub>/INTE0-INTE2 (Port 2; Maskable Interrupts)

Ports P2<sub>1</sub>-P2<sub>3</sub> are dedicated to INTE0, INTE1, and INTE2, the maskable external interrupt requests.

#### P2<sub>4</sub>/TxD (Port 2; Serial Transmit)

P2<sub>4</sub> is an I/O port bit or the transmitted serial data output.

#### P25/RxD (Port 2; Serial Receive)

P25 is an I/O port bit or the received serial data input.

# P26/SCK (Port 2; Serial Clock)

P26 is an I/O port bit or the serial shift clock output.

#### P2<sub>7</sub>/CTS (Port 2: Clear to Send)

P2<sub>7</sub> is an I/O port bit or clear-to-send input (external serial transmission control) in the asynchronous communication mode. In the serial I/O interface mode, it becomes the serial receive clock I/O pin.

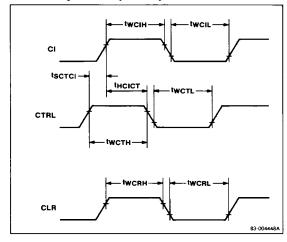

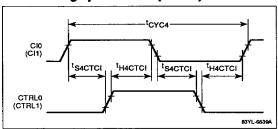

#### P3<sub>0</sub>/CI0 (Port 3; Counter 0)

Port P3<sub>0</sub> is dedicated to C10, the external count input for up/down counter 0.

#### P3<sub>1</sub>/CTRL0 (Port 3; Counter 0 Control)

Port P3<sub>0</sub> is dedicated to CTRL0, the external control input for up/down counter 0.

#### P3<sub>2</sub>/Cl1 (Port 3; Counter 1)

Port P3<sub>2</sub> is dedicated to CI1, the external count input for up/down counter 1.

# P3<sub>3</sub>/CTRL1 (Port 3; Counter 1 Control)

Port P3<sub>3</sub> is dedicated to CTRL1, the external control input for up/down counter 1.

#### P3<sub>4</sub>/PWM0 (Port 3; Pulse Width 0)

$P3_4$  is an I/O port bit or the pulse-width modulated output o

# P35/PWM1 (Port 3; Pulse Width 1)

P3<sub>5</sub> is an I/O port bit or the pulse-width modulated output

#### P36/CLR0/T00 (Port 3; Counter 0 Clear; Timer 0)

P36 is an I/O port bit, or the clear input for up/down counter 0, or the timer 0 flip-flop output.

#### P37/CLR1/TO1 (Port 3; Counter 1 Clear; Timer 1)

P3<sub>7</sub> is an I/O port bit, or the clear input for up/down counter 1, or the timer 1 flip-flop output.

# P4<sub>0</sub>-P4<sub>7</sub>/AD<sub>0</sub>-AD<sub>7</sub> (Port 4; External Address/Data Bus)

Port 4 consists of 8 bits, programmable as a unit for input or output, or as the multiplexed address/data bus if external memory or external interface circuitry is used. The port is controlled by the memory mapping register. If the EA pin is low, port 4 is always an address/data bus.

# P5<sub>0</sub>-P5<sub>7</sub>/A<sub>8</sub>-A<sub>15</sub> (Port 5; High-Address Byte)

Port 5 consists of 8 bits, individually programmable for input or output, or the high-order address bits for external memory. Under control of the memory mask register, bits P5<sub>3</sub>-P5<sub>0</sub> are used for 4K memory expansion, bits P5<sub>5</sub>-P5<sub>0</sub> for 16K memory expansion, or bits P5<sub>7</sub>-P5<sub>0</sub> for 56K memory expansion. If the EA pin is low, port 5 is always the high-order address bus.

#### RD (Read Strobe)

RD is the read strobe output. It is to be used by external memory (or data registers) to place data on the I/O bus during a read operation.

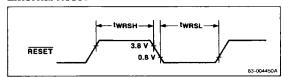

#### **RESET/PROG**

This pin is used for the external reset input. A low level sets all registers to their specified reset values. During programming of the  $\mu$ PD78P312A, this pin is used to place the device into PROM programming mode.

#### RFSH (Refresh)

RFSH is the refresh pulse output to be used for external pseudostatic DRAM.

#### WR (Write Strobe)

WR is the write strobe output. It is to be used by external memory (or data registers) to latch data from the I/O bus during a write operation.

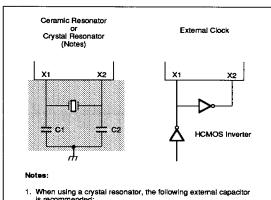

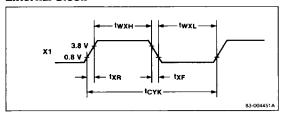

#### X1, X2 (External Crystal or Clock input)

X1 and X2 are the external oscillator inputs or the connections for an external crystal. If an external clock is used, it is connected to X1 and its inverse is connected to X2. The system clock frequency is half the input frequency.

#### AV<sub>REF</sub> (A/D Reference Voltage)

AV<sub>REF</sub> is the reference voltage input for the A/D converter.

#### AV<sub>SS</sub> (Analog Ground)

AVSS is the analog ground pin.

#### V<sub>DD</sub> (Power Supply)

V<sub>DD</sub> is the positive power supply input.

#### V<sub>SS</sub> (Power Return)

V<sub>SS</sub> is the power supply return, normally ground.

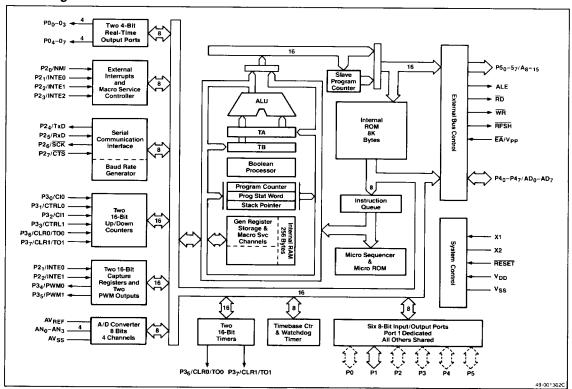

#### **Block Diagram**

#### **FUNCTIONAL DESCRIPTION**

On-chip features designed to facilitate process control include two 16-bit timers, quadrature counting, two 16-bit up/down counters, two pulse-width modulated outputs, a free-running counter with two capture registers, two 4-bit real-time (timer-controlled) output ports, an 8-bit A/D converter with four input channels, a timebase counter to generate widely spaced interrupts, and a watchdog timer to guard against infinite program loops.

In addition, a serial I/O port can be used in either an interface mode or an asynchronous communication mode. HALT and STOP modes are provided to conserve power at times when CPU action is not required.

All I/O, timer, and control registers are defined as special function registers and assigned addresses in the top 256 bytes of memory. The special function registers may be operated on directly by many of the arithmetic, logic, and move instructions of the CPU. Table 1 describes the registers.

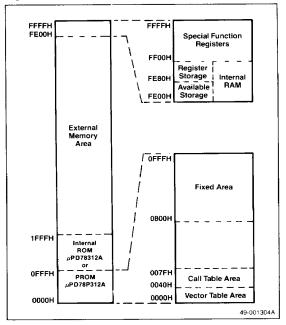

#### Addressing

The  $\mu$ PD783101xA features 1-byte addressing of the special function registers and 1-byte addressing of the internal RAM. There are nine modes of addressing main memory, including autoincrement, autodecrement, indexing, and double indexing. There are 8- and 16-bit immediate operands.

Figure 1. Memory Map

# **External Memory**

External memory (figure 1) is supported by I/O port 4, an 8-bit multiplexed address/data bus. The memory mapping register controls the size of external memory as well as the number of additional wait states. High-order address bits are taken from I/O port 5 as required. No bits are required for 256 bytes of external memory; bits P5<sub>3</sub>-P5<sub>0</sub> are used for 4K bytes, P5<sub>5</sub>-P5<sub>0</sub> for 16K bytes, and P5<sub>7</sub>-P5<sub>0</sub> for 56K bytes. Any remaining port 5 bits are available for I/O.

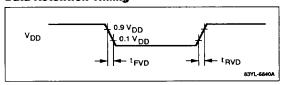

#### Refresh

The  $\mu$ PD7831xA has a refresh signal for use with the pseudostatic RAM. The refresh cycle can be set to one of four intervals ranging from 2.67 to 21.3  $\mu$ s. The refresh is timed to follow a read or write operation so that there is no interference.

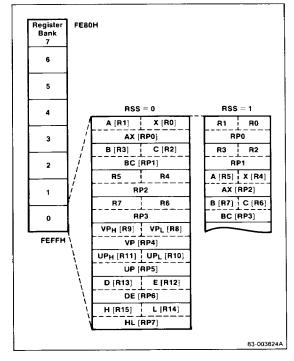

Figure 2. Register Designation and Storage

#### General Registers

The CPU has sixteen 8-bit registers (figure 2) that can also be used in pairs to function as 16-bit registers. A complete set of 16 general registers is mapped into each of 8 program-selectable register banks stored in RAM. Three bits in the PSW specify which of the register banks is active at any given time. Each register bank has two program-selectable accumulators.

The general registers of the  $\mu$ PD7831xA have both absolute and functinal names. AX is the functional name for the accumulator. Setting the RSS bit in the PSW to 1 transfers the AX and BC registers from their normal RP0 and RP1 positions to RP2 and RP3 as shown in figure 2. This adds considerable programming flexibility.

#### **Program Status Word**

Following is the program status word format.

| 0  | RB <sub>2</sub> | RB <sub>1</sub> | RB <sub>0</sub> | 0  | 0   | ΙE  | 0  |

|----|-----------------|-----------------|-----------------|----|-----|-----|----|

| 15 |                 |                 |                 |    |     |     | 8  |

| S  | Z               | RSS             | AC              | UF | P/V | SUB | CY |

|    |                 |                 |                 |    |     |     |    |

RB<sub>2</sub>-RB<sub>0</sub> Active register bank number

IE Interrupt enable

S Sign (1 if last result was negative)

Z Zero (1 if last result was zero)

RSS Register set select

AC Auxiliary carry (carry out of 3rd bit)

UF User flag

P/V Parity or arithmetic overflow SUB Subtract (1 if last operation was

subtract)

CY Carry

# Input/Output

All ports may be used for either latched output or high-impedance input. All ports except port 4 are bit-programmable for input or output. Port 0 is used for real-time or normal I/O. Port 1 is used for normal I/O. The low nibble of ports 2 and 3 is always used for control and the high nibble for control or normal I/O. Port 4 is used for the external address/data bus or byte-programmable I/O. Port 5 is used for the high bits of the external address or for normal I/O.

# Real-Time Output Port

The real-time output port shares pins with I/O port 0. The high and low nibbles are treated separately or together. Data is transferred from a buffer to the port latches on either a timer or software command.

#### Serial Port

The serial port can operate in UART or interface mode with the baud rate and byte format under program control. The serial port also includes a dedicated baud rate generator.

# **Pulse-Width Modulated Outputs**

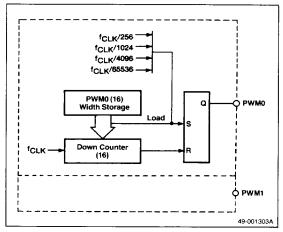

The two independent pulse-width modulated outputs are controlled by two 16-bit modulus registers and counters. There are four programmable repetition rates ranging from 91.6 Hz to 23.4 MHz. Figure 3 shows one of these outputs.

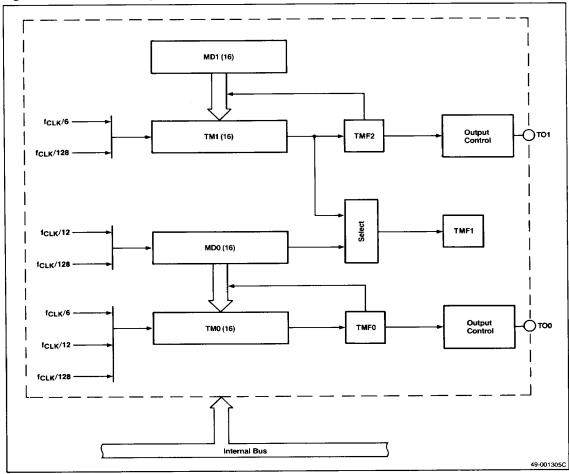

#### **Timers**

The µPD7831xA has two 16-bit timers. The inputs to these timers may be the internal clock divided by 6 or by 128. Each timer has an associated modulus register to store the timer count. The timer counts down to zero, sets a flag, reloads from the modulus register, and then counts down again. The timer flags can be used under program control to generate interrupt requests and/or a square-wave output. TM0 also functions optionally as two one-shot timers.

Figure 4 is a diagram of the interval timers.

There is a free-running counter that counts the internal clock divided by 4 or by 16. The counter has two 16-bit capture registers. Capture is triggered by an external interrupt request or by the up/down counter clock.

The timebase counter generates a signal at one of four intervals ranging from 170  $\mu$ s to 175 ms. The signal can be used to generate an interrupt request and/or an up/down counter capture.

Figure 3. Pulse-Width Modulated Output

Figure 4. Timer Block Diagram

#### **Up/Down Counters**

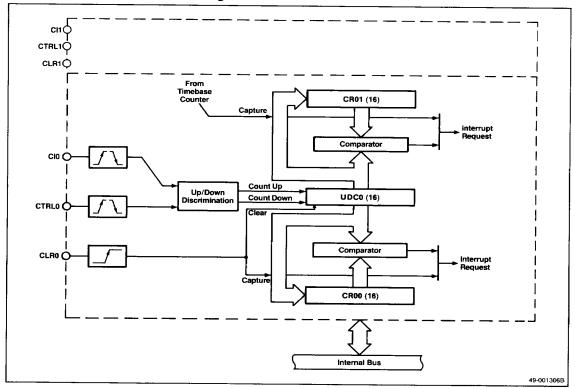

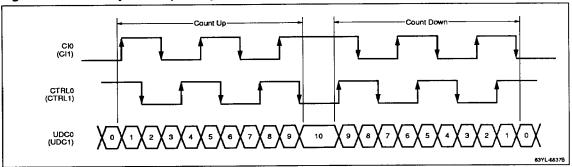

The  $\mu$ PD7831xA has two 16-bit up/down counters, each of which has two capture/compare registers. There are three modes of operation: compare and interrupt, capture on external command, and capture on timebase counter command. There are five sources of counts: the internal clock divided by 3, the external clock, external independent up and down inputs, external clock with direction control, and external clock with automatic up/down discrimination. Figure 5 shows an up/down counter.

Figure 5. Up/Down Counter Block Diagram

# **Quadrature Counting**

The two up/down counters, UDC0 and UDC1, have an optional quadrature counting mode, which is activated by specifying mode 4 in the counter unit input mode register, CUIM. It is designed to count the output of a two-phase pulsed optical shaft angle encoder. The input for phase A is the CIO (or CI1) pin, and the input for phase B is the CTRL0 (or CTRL1) pin. The counter UDC0 (or UDC1) is incremented or decremented at both positive and negative transitions of both input signals. Whether it is incremented or decremented is dependent upon the relative phase of the two signals as illustrated in figure 6.

Figure 6. Counter Operation (Mode 4)

#### **Standby Modes**

HALT and STOP modes conserve power when CPU action is not required. In HALT mode, the CPU stops and the clock continues to run. Maskable interrupts can restart the CPU.

In STOP mode, the CPU and clock are both stopped. A RESET pulse or the nonmaskable external interrupt is required to restart them. There is also the option of slowing the system clock by a factor of four. The standby control register controls the standby modes and is a protected location written to only by a special instruction.

#### Watchdog Timer

The watchdog timer protects against inadvertent program loops. A nonmaskable interrupt occurs if the timer is not reset before a timeout occurs. There are four program-selectable intervals ranging from 5.5 to 349.3 ms. The watchdog timer can be disabled by software. The watchdog timer mode register controls the watchdog timer and is a protected location written to only by a special instruction.

#### A/D Converter

The A/D converter has four input channels and can operate in either scan or select mode. The A/D converter performs 8-bit successive approximation conversions, has a 30- $\mu$ s conversion time, and is triggered either internally or externally. The A/D converter includes an on-chip sample and hold amplifier.

#### Interrupts

There are two nonmaskable interrupt sources: the external nonmaskable interrupt and the watchdog timer. Their relative priorities are software selectable.

7-14

There are eight hardware priority interrupt levels, level 0 having the highest priority and level 7 the lowest. The 15 maskable interrupt sources (table 2) are divided into five groups, and each group can, under program control, be assigned to any one of the priority levels.

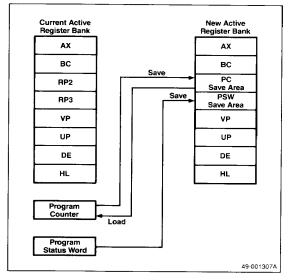

Interrupts may be serviced by routines entered either by vectoring or by context switching. Context switching automatically saves all the general registers, the program status word, and the program counter. Figure 7 illustrates the mechanism of context switching.

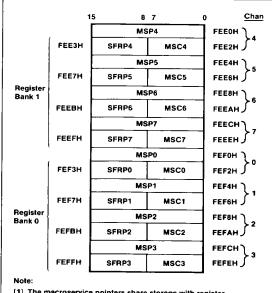

Finally, an optional macroservice function transfers data between any one special function register and memory without program intervention.

#### Macroservice

The macroservice controller can be programmed to perform word or byte transfers. It can transfer data from a special function register to memory or from memory to a special function register. Transfer events are triggered by interrupt requests and take place without software intervention.

There are eight macroservice channels; channel control information is stored in RAM. This information (figure 8) consists of a 16-bit memory address (optionally incremented at each transfer), and 8-bit special function register designator, and an 8-bit transfer counter (decremented at each transfer). When the count equals 0, a context switch or vectored interrupt occurs.

Figure 7. Hardware Context Switching

Figure 8. Macroservice Pointer Addresses

- [1] The macroservice pointers share storage with register banks 0 and 1.

- [2] MSP = Memory address pointer SFRP = Special function register pointer MSC = Transfer counter

83-003825A

Table 1. Special Function Registers

| Address        | Function                      | Mnemor         | ilc  | Read/Write   | 16-Bit Transfer | Reset State |

|----------------|-------------------------------|----------------|------|--------------|-----------------|-------------|

| FF00H          | I/O port 0                    | P0             |      | R/W          | No              | Undefined   |

| FF01H          | I/O port 1                    | P1             |      | R/W          | No              | Undefined   |

| FF02H          | I/O port 2                    | P2             |      | R/W (Note 1) | No              | Undefined   |

| FF03H          | I/O port 3                    | P3             |      | R/W (Note 1) | No              | Undefined   |

| FF04H          | I/O port 4                    | P4             |      | R/W          | No              | Undefined   |

| FF05H          | I/O port 5                    | P5             |      | R/W          | No              | Undefined   |

| FF08H<br>FF09H | Capture/compare register 00   | CR00L<br>CR00H | CR00 | R/W          | Yes             | Undefined   |

| FF0AH<br>FF08H | Capture/compare register 01   | CR01L<br>CR01H | CR01 | R/W          | Yes             | Undefined   |

| FF0CH<br>FF0DH | Capture/compare register 10   | CR10L<br>CR10H | CR10 | R/W          | Yes             | Undefined   |

| FFOEH<br>FFOFH | Capture/compare register 11   | CR11L<br>CR11H | CR11 | R/W          | Yes             | Undefined   |

| FF10H<br>F11H  | Capture register 0 (from FRC) | CPTOL<br>CPTOH | СРТО | R/W          | Yes             | Undefined   |

| FF12H<br>FF13H | Capture register 1 (from FRC) | CPT1L<br>CPT1H | CPT1 | R/W          | Yes             | Undefined   |

Table 1. Special Function Registers (cont)

| Address        | Function                               | Mnemoni        | c    | Read/Write   | 16-Bit Transfer | Reset State     |

|----------------|----------------------------------------|----------------|------|--------------|-----------------|-----------------|

| FF14H<br>FF15H | PWM register 0 (duration)              | PWM0L<br>PWM0H | PWM0 | R/W          | Yes             | Undefined       |

| FF16H<br>FF17H | PWM register 1 (duration)              | PWM1L<br>PWM1H | PWM1 | R/W          | Yes             | Undefined       |

| FF1CH<br>FF1DH | Presettable up/down counter 0          | UD COL         | UDC0 | R/W          | Yes             | Undefined       |

| FF1EH<br>FF1FH | Presettable up/down counter 1          | UDC1L<br>UDC1H | UDC1 | R/W          | Yes             | Undefined       |

| FF20H          | Port 0 mode register                   | PM0            |      | R/W          | No              | FFH             |

| FF21H          | Port 1 mode register                   | PM1            |      | R/W          | No              | FFH             |

| FF22H          | Port 2 mode register                   | PM2            |      | R/W (Note 1) | No              | FFH             |

| FF23H          | Port 3 mode register                   | РМЗ            |      | R/W (Note 1) | No              | FFH             |

| FF25H          | Port 5 mode register                   | PM5            |      | R/W          | No              | FFH             |

| FF32H          | Port 2 mode control register           | PMC2           |      | R/W          | No              | <b>O</b> FH     |

| FF33H          | Port 3 mode control register           | РМСЗ           |      | R/W          | No              | 0FH             |

| FF38H          | Real-time output port control register | RTPC           |      | R/W          | No              | 08H             |

| FF3AH<br>FF3BH | Port 0 buffer register (Note 2)        | POL POH        |      | R/W          | No              | Undefined       |

| FF40H          | Memory expansion mode register         | ММ             |      | R/W          | No              | 30H             |

| FF41H          | Refresh mode register                  | RFM            |      | R/W          | No              | 10H             |

| FF42H          | Watchdog timer mode register           | WDM            |      | R/W          | No              | 00H             |

| FF44H          | Standby control register               | STBC           |      | R/W          | No              | 2nH<br>(Note 3) |

| FF46H          | Timebase mode register                 | ТВМ            |      | R/W          | No              | 00H             |

| FF48H          | External interrupt mode register       | INTM           |      | R/W          | No              | 00H             |

| FF4AH          | In-service priority register           | ISPR           |      | R            | No              | 00H             |

| FF4EH          | CPU control word                       | ccw            |      | R/W          | No              | 00H             |

| FF50H          | Serial communication mode register     | SCM            |      | R/W          | No              | 00Н             |

| FF52H          | Serial communication control register  | scc            |      | R/W          | No              | 00H             |

| FF53H          | Baud rate generator                    | BRG            |      | FI/W         | No              | 00Н             |

| FF56H          | Serial communication receive buffer    | RXB            |      | R            | No              | Undefined       |

| FF57H          | Serial communication transmit buffer   | TXB            |      | W            | No              | Undefined       |

| FF60H          | Free-running counter control register  | FRCC           |      | R/W          | No              | 00H             |

Table 1. Special Function Registers (cont)

| Address           | Function                                               | Mnemonic         | Read/Write | 16-Bit Transfer | Reset State |

|-------------------|--------------------------------------------------------|------------------|------------|-----------------|-------------|

| FF64H             | Capture mode register                                  | СРТМ             | R/W        | No              | 00Н         |

| FF66H             | PWM mode register                                      | PWMM             | R/W        | No              | 00H         |

| FF68H             | A/D converter mode register                            | ADM              | R/W        | No              | 00H         |

| FF6AH             | A/D converter result register                          | ADCR             | R          | No              | Undefined   |

| FF70H             | Count unit input mode register                         | CUIM             | R/W        | No              | 00Н         |

| FF72H             | Up/down counter control register 0                     | UDCC0            | R/W        | No              | 00Н         |

| FF74H             | Capture/compare control register                       | CRC              | R/W        | No              | 00Н         |

| FF7AH             | Up/down counter control register 1                     | UDCC1            | R/W        | No              | <b>00</b> H |

| FF80H             | Timer 0 control register                               | TMC0             | R/W        | No              | 00H         |

| FF82H             | Timer 1 control register                               | TMC1             | R/W        | No              | 00Н         |

| F F88H<br>F F89H  | Timer 0                                                | TMOL TMO<br>TMOH | R/W        | Yes             | Undefined   |

| FF8AH<br>FF8BH    | Modulus/timer register 0                               | MDOL MDO<br>MDOH | R/W        | Yes             | Undefined   |

| FF8CH<br>FF8DH    | Timer 1                                                | TM1L TM1<br>TM1H | R/W        | Yes             | Undefined   |

| FF8EH<br>FF8FH    | Modulus register 1                                     | MD1L MD1<br>TM1H | R/W        | Yes             | Undefined   |

| FFB0H to<br>FFBFH | External area (Note 4)                                 |                  | ·          |                 | •           |

| FFC0H             | CRF00 interrupt control<br>Up/down counter 0           | CRIC00           | R/W        | No              | 47H         |

| FFC1H             | CRF00 macroservice control Up/down counter 0           | CRMS00           | R/W        | No              | Undefined   |

| FFC2H             | CRF01 interrupt control Up/down counter 0              | CRIC01           | R/W        | No              | 47H         |

| FFC4H             | CRF10 Interrupt control Up/down counter 1              | CRIC10           | R/W        | No              | 47H         |

| FFC5H             | CRF10 macroservice control Up/down counter 1           | CRMS10           | R/W        | No              | Undefined   |

| FFC6H             | CRF11 interrupt control Up/down counter 1              | CRIC11           | R/W        | No              | 47H         |

| FFC8H             | EXIFO interrupt control External interrupt INTE0       | EXIC0            | R/W        | No              | 47H         |

| FFC9H             | EXIFO macroservice control<br>External interrupt INTEO | EXMS0            | R/W        | No              | Undefined   |

| FFCAH             | EXIF1 interrupt control External interrupt INTE1       | EXIC1            | R/W        | No              | 47H         |

| FFCBH             | EXIF1 macroservice control External interrupt INTE1    | EXMS1            | R/W        | No              | Undefined   |

| FFCCH             | EXIF2 interrupt control External interrupt INTE2       | EXIC2            | R/W        | No              | 47H         |

# µPD7831xA/78P31xA

Table 1. Special Function Registers (cont)

| Address | Function                                               | Mnemonic | Read/Write | 16-Bit Transfer | Reset State |

|---------|--------------------------------------------------------|----------|------------|-----------------|-------------|

| FFCDH   | EXIF2 macroservice control<br>External interrupt INTE2 | EXMS2    | R/W        | No              | Undefined   |

| FFCEH   | TMF0 interrupt control<br>Timer flag                   | TMIC0    | R/W        | No<br>          | 47H         |

| FFCFH   | TMF0 macroservice control<br>Timer flag                | TMMS0    | R/W        | No              | Undefined   |

| FFD0H   | TMF1 interrupt control<br>Timer flag                   | TMIC1    | R/W        | No              | 47H         |

| FFD1H   | TMF1 macroservice control<br>Timer flag                | TMMS1    | R/W        | No              | Undefined   |

| FFD2H   | TMF2 interrupt control<br>Timer flag                   | TMIC2    | R/W        | No              | 47H         |

| FFD3H   | TMF2 macroservice control<br>Timer flag                | TMMS2    | R/W        | No              | Undefined   |

| FFDAH   | Receive error interrupt control<br>Serial port         | SEIC     | R/W        | No              | 47H         |

| FFDCH   | Receive interrupt control<br>Serial port               | SRIC     | R/W        | No              | 47H         |

| FFDDH   | Receive macroservice control<br>Serial port            | SRMS     | R/W        | No              | Undefined   |

| FFDEH   | Transmit interrupt control<br>Serial port              | STIC     | R/W        | No              | 47H         |

| FFDFH   | Transmit macroservice control<br>Serial port           | STMS     | R/W        | No              | Undefined   |

| FFE0H   | A/D converter interrupt control                        | ADIC     | R/W        | No              | 47H         |

| FFE1H   | A/D converter macroservice control                     | ADMS     | R/W        | No              | Undefined   |

| FFE2H   | Timebase counter interrupt control                     | TBIC     | R/W        | No              | 47H         |

#### Notes:

- (1) Bits 0-3 of port 2 and of port 3 are read-only.

- (2) POH and POL are 4-bit buffer registers used to store data to be loaded into the high and low nibbles of the real-time output (P0). The high order 4 bits of POH and the low order 4 bits of POL are used.

- (3) Bit 3 of the STBC is not affected by RESET (n = 0 or 8).

- (4) External registers interfaced with these addresses can be accessed by special function register addressing.

Table 2. Interrupt Sources and Vector Addresses

| Nonmaskable Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        | Default Priority | Mnemonic | Interrupt Source               | Macroservice | Vector |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------|----------|--------------------------------|--------------|--------|

| No   No   Maskable interrupts   O   CRF00   Up/down counter 0   Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Software               | <del>-</del>     | BRK      | Break instruction              | No           | 003EH  |

| Maskable interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Nonmaskable Interrupts |                  | NMI      | External nonmaskable interrupt | No           | 0002H  |

| 1         CRF01         Up/down counter 0         No           2         CRF10         Up/down counter 1         Yes           3         CRF11         Up/down counter 1         No           4         EXIF0         External interrupt 0         Yes           5         EXIF1         External interrupt 1         Yes           6         EXIF2         External interrupt 2         Yes           7         TMF0         Timer flag 0         Yes           8         TMF1         Timer flag 1         Yes           9         TMF2         Timer flag 2         Yes           10         SEF         Serial port error         No           11         SRF         Serial port receive buffer         Yes           12         STF         Serial port transmit buffer         Yes           13         ADF         A/D converter done flag         Yes           14         TBF         Timebase counter flag         No |                        | _                | WDT      | Watchdog timer                 | No           | 000AH  |

| 2         CRF 10         Up/down counter 1         Yes           3         CRF 11         Up/down counter 1         No           4         EXIF0         External interrupt 0         Yes           5         EXIF1         External interrupt 1         Yes           6         EXIF2         External interrupt 2         Yes           7         TMF0         Timer flag 0         Yes           8         TMF1         Timer flag 1         Yes           9         TMF2         Timer flag 2         Yes           10         SEF         Serial port error         No           11         SRF         Serial port receive buffer         Yes           12         STF         Serial port transmit buffer         Yes           13         ADF         A/D converter done flag         Yes           14         TBF         Timebase counter flag         No                                                              | Maskable interrupts    | 0                | CRF00    | Up/down counter 0              | Yes          | 001AH  |

| 3   CRF11   Up/down counter 1   No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        | 1                | CRF01    | Up/down counter 0              | No           | 001 CH |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        | 2                | CRF 10   | Up/down counter 1              | Yes          | 001 EH |

| 5         EXIF1         External interrupt 1         Yes           6         EXIF2         External interrupt 2         Yes           7         TMF0         Timer flag 0         Yes           8         TMF1         Timer flag 1         Yes           9         TMF2         Timer flag 2         Yes           10         SEF         Serial port error         No           11         SRF         Serial port receive buffer         Yes           12         STF         Serial port transmit buffer         Yes           13         ADF         A/D converter done flag         Yes           14         TBF         Timebase counter flag         No                                                                                                                                                                                                                                                                  |                        | 3                | CRF11    | Up/down counter 1              | No           | 0020H  |

| 6         EXIF2         External interrupt 2         Yes           7         TMF0         Timer flag 0         Yes           8         TMF1         Timer flag 1         Yes           9         TMF2         Timer flag 2         Yes           10         SEF         Serial port error         No           11         SRF         Serial port receive buffer         Yes           12         STF         Serial port transmit buffer         Yes           13         ADF         A/D converter done flag         Yes           14         TBF         Timebase counter flag         No                                                                                                                                                                                                                                                                                                                                     |                        | 4                | EXIF0    | External interrupt 0           | Yes          | 0004H  |

| 7         TMF0         Timer flag 0         Yes           8         TMF1         Timer flag 1         Yes           9         TMF2         Timer flag 2         Yes           10         SEF         Serial port error         No           11         SRF         Serial port receive buffer         Yes           12         STF         Serial port transmit buffer         Yes           13         ADF         A/D converter done flag         Yes           14         TBF         Timebase counter flag         No                                                                                                                                                                                                                                                                                                                                                                                                        |                        | 5                | EXIF1    | External interrupt 1           | Yes          | 0006H  |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        | 6                | EXIF2    | External interrupt 2           | Yes          | 0008H  |

| 9         TMF2         Timer flag 2         Yes           10         SEF         Serial port error         No           11         SRF         Serial port receive buffer         Yes           12         STF         Serial port transmit buffer         Yes           13         ADF         A/D converter done flag         Yes           14         TBF         Timebase counter flag         No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                        | 7                | TMF0     | Timer flag 0                   | Yes          | 000EH  |

| 10   SEF   Serial port error   No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        | 8                | TMF1     | Timer flag 1                   | Yes          | 0010H  |

| 11 SRF Serial port receive buffer Yes  12 STF Serial port transmit buffer Yes  13 ADF A/D converter done flag Yes  14 TBF Timebase counter flag No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        | 9                | TMF2     | Timer flag 2                   | Yes          | 0012H  |

| 12 STF Serial port transmit buffer Yes 13 ADF A/D converter done flag Yes 14 TBF Timebase counter flag No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        | 10               | SEF      | Serial port error              | No           | 0022H  |

| 13 ADF A/D converter done flag Yes  14 TBF Timebase counter flag No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        | 11               | SRF      | Serial port receive buffer     | Yes          | 0024H  |

| 14 TBF Timebase counter flag No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                        | 12               | STF      | Serial port transmit buffer    | Yes          | 0026H  |

| Page 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        | 13               | ADF      | A/D converter done flag        | Yes          | 0028H  |

| Reset — RESET External reset line —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        | 14               | TBF      | Timebase counter flag          | No           | 000CH  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Reset                  | _                | RESET    | External reset line            | _            | 0000H  |

#### **ELECTRICAL SPECIFICATIONS**

# Absolute Maximum Ratings $T_A + 25^{\circ}C$

Power supply voltage V<sub>DD</sub> -0.5 to +7.0 V Reference voltage, AVREF -0.5 V to V<sub>DD</sub> +0.3 V Power supply return, AVSS -0.5 to +0.5 V Input voltage, V<sub>I1</sub>  $-0.5 \text{ to } + V_{DD} + 0.5$ (except RESET of µPD78P312A) input voltage, V<sub>I2</sub> (RESET of μPD78P312A only) -0.5 to +13.5 V Output voltage, VO -0.5 to V<sub>DD</sub> +0.5 V Output current, low; IOL (single pin) 4 mA Output current, low; IOL; total, 100 mA all output pins (µPD78312/310A) Output current, low; IOL; total, 60 mA all output pins (aPD78P312A) Output current, high; IOH (single pin) -1 mA Output current, high; IOH; total, -25 mA all output pins (µPD78312/310A)

| Output current, high; I <sub>OH</sub> ; total,<br>all output pins (μPD78P312A) | –15 mA         |

|--------------------------------------------------------------------------------|----------------|

| Operating temperature, T <sub>OPT</sub>                                        | -10 to +70 ℃   |

| Storage temperature, T <sub>STG</sub>                                          | -65 to +150 °C |

Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage.

# **Operating Frequency**

| Oscillator Frequency f <sub>XX</sub> | TA           | V <sub>DD</sub> |

|--------------------------------------|--------------|-----------------|

| 4 MHz ≤ f <sub>XX</sub> ≤ 12 MHz     | -10 to +70°C | +5.0 V 10%      |

#### Capacitance

$T_A = +25^{\circ}C; V_{DD} = V_{SS} = 0 \text{ V}$

| Parameter          | Symbol          | Max | Unit | Conditions                  |

|--------------------|-----------------|-----|------|-----------------------------|

| Input capacitance  | CI              | 10  | pF   | f = 1 MHz;                  |

| Output capacitance | Со              | 20  | pF   | unmeasured<br>pins returned |

| I/O capacitance    | C <sub>IO</sub> | 20  | pF   | to 0 V.                     |

# **DC Characteristics**

$T_A = -10 \text{ to } +70^{\circ}\text{C}; V_{DD} = +5.0 \text{ V } \pm 5\%; V_{SS} = 0 \text{ V}$

| Parameter                      | Symbol            | Min                | Тур | Max             | Unit | Conditions                                           |

|--------------------------------|-------------------|--------------------|-----|-----------------|------|------------------------------------------------------|

| Input low voltage              | V <sub>IL1</sub>  | 0                  |     | 8.0             | ٧    | Except EA on μPD78310A/312A                          |

|                                | V <sub>IL2</sub>  | 0                  |     | 0.5             | ٧    | EA on (μPD78310A/312A only)                          |

| Input high voltage             | V <sub>IH1</sub>  | 2.2                |     | V <sub>DD</sub> | ٧    | Except P2 <sub>0</sub> /NMI, X1, X2, RESET           |

|                                | V <sub>IH2</sub>  | 3.8                |     | V <sub>DD</sub> | ٧    | P2 <sub>0</sub> /NMI X1, X2, RESET                   |

| Output low voltage             | V <sub>OL</sub>   |                    |     | 0.45            | ٧    | I <sub>OL</sub> = 2.0 mA                             |

| Output high voltage            | V <sub>OH</sub>   | V <sub>DD</sub> -1 | -   |                 | ٧    | I <sub>OH</sub> = -1 mA                              |

| Input current                  | Ц                 |                    |     | ±10             | μA   | $P2_0/NMI$ , RESET $V_1 = 0.45 \text{ V to } V_{DD}$ |

| Input leakage current          | ILI               | ******             |     | ±10             | μA   |                                                      |

| input/output leakage current   | ILO               |                    |     | ±10             | μА   |                                                      |

| AV <sub>REF</sub> current      | Al <sub>REF</sub> |                    | 1.5 | 5               | mA   | f <sub>CLK</sub> = 6 MHz                             |

| V <sub>DD</sub> supply current | I <sub>DD1</sub>  |                    | 30  | 60              | mA   | Operating mode; f <sub>CLK</sub> = 6 MHz             |

|                                | l <sub>DD2</sub>  |                    | 5   | 15              | mA   | Halt mode; f <sub>CLK</sub> = 6 MHz                  |

| Data retention voltage         | V <sub>DDDR</sub> | 2.5                |     |                 | ٧    | Stop mode                                            |

| Stop mode supply current       | IDDDR             |                    | 3   | 15              | μА   | Stop mode; V <sub>DDDR</sub> = 2.5 V                 |

|                                |                   |                    | 10  | 50              | μА   | Stop mode; V <sub>DDDR</sub> = 5.0 V ±10%            |

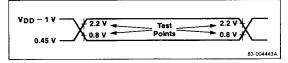

# AC Characteristics

$T_A = -10 \text{ to } +70^{\circ}\text{C}; V_{DD} = +5.0 \text{ V} \pm 10\%; V_{SS} = 0 \text{ V}$

| Parameter                         | Symbol             | Min | Тур | Max  | Unit | Conditions          |

|-----------------------------------|--------------------|-----|-----|------|------|---------------------|

| Read/Write Operation              |                    |     |     |      |      |                     |

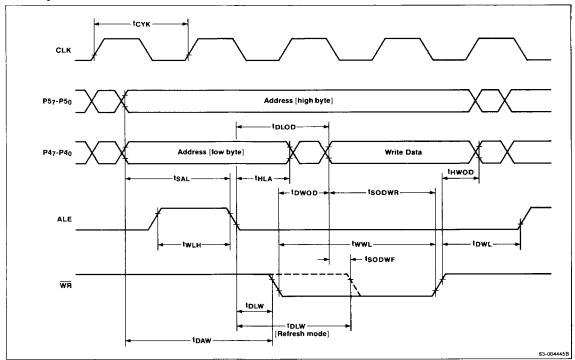

| System clock cycle time           | †CYK               | 166 |     | 2000 | ns   | (Note 1)            |

| Address setup time to ALE↓        | t <sub>SAL</sub>   | 150 |     |      | ns   |                     |

| Address hold time after ALE↓      | thLA               | 30  |     |      | ns   | (Note 4)            |

| Address to RD ↓ delay time        | <sup>t</sup> DAR   | 230 |     | •    | ns   |                     |

| RD ↓ to address floating          | t <sub>FRA</sub>   |     |     | 0    | ns   |                     |

| Address to data input             | <sup>‡</sup> DAID  |     |     | 410  | ns   |                     |

| ALE ↓ to data input               | <sup>†</sup> DLID  |     |     | 230  | ns   |                     |

| RD ↓ to data input                | t <sub>DRID</sub>  |     |     | 180  | ns   |                     |

| ALE ↓ to RD ↓ delay time          | t <sub>DLR</sub>   | 60  |     |      | ns   |                     |

| Data hold time after RD ↑         | <sup>t</sup> HRID  | 0   |     |      | ns   |                     |

| RD ↑ to address active            | t <sub>DRA</sub>   | 50  |     |      | ns   |                     |

| RD ↑ to ALE ↑ delay time          | t <sub>DRL</sub>   | 100 |     |      | ns   |                     |

| RD width low                      | twaL               | 200 |     |      | ns   |                     |

| ALE width high                    | t <sub>WLH</sub>   | 120 |     |      | ns   |                     |

| Address to WR ↓ delay time        | t <sub>DAW</sub>   | 300 |     |      | ns   |                     |

| ALE ↓ to data output              | t <sub>D LOD</sub> |     |     | 190  | ns   |                     |

| WR ↓ to data output               | <sup>t</sup> DWOD  |     |     | 100  | ns   |                     |

| ALE ↓ to WR ↓ delay time (Note 2) | t <sub>DLW</sub>   | 30  |     |      | ns   |                     |

|                                   |                    | 110 |     |      | ns   | During refresh mode |

| Data setup time to WR ↑           | tsopwr             | 150 |     |      | ns   |                     |

| AC Characteristics (cont) | AC | Characteristics | (cont) |

|---------------------------|----|-----------------|--------|

|---------------------------|----|-----------------|--------|

| Parameter                                                                         | Symbol                      | Min                         | Тур                                 | Max               | Unit             | Conditions                                                                          |

|-----------------------------------------------------------------------------------|-----------------------------|-----------------------------|-------------------------------------|-------------------|------------------|-------------------------------------------------------------------------------------|

| Read/Write Operation (cont)                                                       |                             |                             |                                     |                   |                  |                                                                                     |

| Data setup time to WR ↓ (Note 3)                                                  | t <sub>SODWF</sub>          | 30                          |                                     |                   | ns               | During refresh mode                                                                 |

| Data hold time to WR ↑                                                            | t-HWOD                      | 20                          |                                     |                   | ns               | (Note 4)                                                                            |

| WR ↑ to ALE ↑ delay time                                                          | <sup>‡</sup> DWL            | 110                         |                                     |                   | ns               |                                                                                     |

| WR width low                                                                      | \$wwL                       | 200                         |                                     |                   | ns               |                                                                                     |

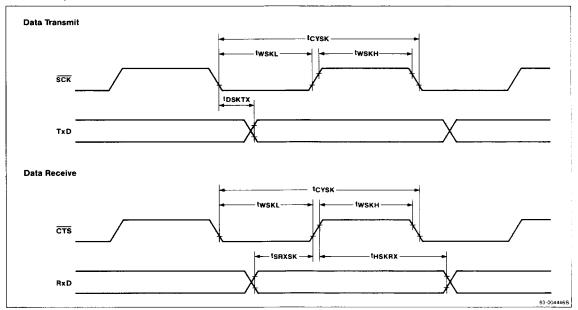

| Serial Port                                                                       |                             |                             |                                     |                   | ·                |                                                                                     |

| Serial clock cycle time                                                           | tcysk                       | 1.33                        |                                     |                   | μѕ               | SCK output (Note 5)                                                                 |

|                                                                                   |                             | 1.33                        |                                     |                   | μs               | CTS output (Note 6)                                                                 |

|                                                                                   |                             | 1                           |                                     |                   | μS               | CTS input (Note 7)                                                                  |

| Serial clock low level width                                                      | twskl.                      | 580                         |                                     |                   | ns               | SCK output (Note 5)                                                                 |

|                                                                                   |                             | 580                         |                                     |                   | ns               | CTS output (Note 6)                                                                 |

|                                                                                   |                             | 420                         |                                     |                   | ns               | CTS input (Note 7)                                                                  |

| Serial clock high level width                                                     | †wskh                       | 580                         |                                     |                   | ns               | SCK output (Note 5)                                                                 |

|                                                                                   |                             | 580                         | <del></del>                         |                   | ns               | CTS output (Note 6)                                                                 |

|                                                                                   |                             | 420                         |                                     |                   | ns               | CTS input (Note 7)                                                                  |

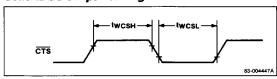

| CTS high, low level                                                               | twcsh,                      | 3                           | -                                   |                   | <sup>‡</sup> CYK | Asynchronous mode                                                                   |

| RxD setup time to CTS ↑                                                           | <sup>t</sup> SRXSK          | 80                          |                                     |                   | ns               | **                                                                                  |

| RxD hold time after CTS ↑                                                         | HSKRX                       | 80                          |                                     |                   | ns               | ******                                                                              |

| SCK ↓ to TxD delay time                                                           | <sup>‡</sup> DSKTX          |                             |                                     | 210               | ns               |                                                                                     |

| <b>A/D Converter</b><br>T <sub>A</sub> = -10°C to +70°C; V <sub>DD</sub> = +5 V : | ±10%; AV <sub>REF</sub> = 4 | .0 V to V <sub>DD</sub> ; A | N <sub>SS</sub> = V <sub>SS</sub> = | = 0 V             |                  |                                                                                     |

| Resolution                                                                        |                             | 8                           |                                     |                   | Bit              |                                                                                     |

| Full scale error                                                                  |                             |                             |                                     | 0.4               | %                | t <sub>CYK</sub> = 166 to 500 ns                                                    |

| Quantization error                                                                |                             |                             |                                     | ±1/2              | LSB              |                                                                                     |

| Conversion time                                                                   | †CONV                       | 180                         |                                     |                   | †CYK             | t <sub>CYK</sub> = 166 to 250 ns                                                    |

|                                                                                   |                             | 120                         |                                     |                   | <sup>‡</sup> CYK | t <sub>CYK</sub> = 250 to 500 ns                                                    |