# NCR 53C700/53C700-66 SCSI I/O Processor

Data Manual

The product(s) described in this publication is a licensed product of NCR Corporation.

TolerANT and SCSI SCRIPTS are registered trademarks of NCR Corporation.

It is the policy of NCR Corporation to improve products as new technology, components, software, and firmware become available. NCR Corporation, therefore, reserves the right to change specifications without notice.

NCR products are not intended for use in life-support appliances, devices, or systems. Use of an NCR product in such applications without the written consent of the appropriate NCR officer is prohibited.

For information on updates to this or other NCR products, contact the NCR Microelectronic Products Division electronic bulletin board at (719) 596-1649.

Copyright ©1993 By NCR Corporation Dayton, Ohio U.S.A. All Rights Reserved Printed in U.S.A.

### **Preface**

#### **SCSI Specifications**

This manual assumes some prior knowledge of current and proposed SCSI standards. For background information, please contact:

#### **ANSI**

11 West 42nd Street New York, NY 10036 (212) 642-4900 Ask for document number X3.131-1986 (SCSI-1)

#### **Global Engineering Documents**

2805 McGaw Irvine, CA 92714 (800)-854-7179 or (714) 261-1455 Ask for document number X3.131-199X (SCSI-2)

#### **ENDL Publications**

14426 Black Walnut Court Saratoga, CA 95070 (408) 867-6642 Document names: SCSI Bench Reference, SCSI Encyclopedia

#### Prentice Hall

Englewood Cliffs, NJ 07632 (201) 767-5937

Ask for document number ISBN 0-13-796855-8, SCSI: Understanding the Small Computer System Interface

į

#### NCR Microelectronic Products Division Electronic Bulletin Board

(719) 596-1649

#### The SCSI Electronic Bulletin Board

(719) 574-0424

## Revision Record

| Page No. | Date  | Remarks                                                             |

|----------|-------|---------------------------------------------------------------------|

| n/a      | 10/89 | Revision 2.3, Draft                                                 |

| n/a      | 12/89 | Revision 2.4, Draft                                                 |

| n/a      | 2/90  | Revision 2.5, Draft                                                 |

| n/a      | 1/92  | Revision 3.0, Preliminary, Added the NCR 53C700-66 and NCR TolerANT |

| 7-1      | 2/92  | Added Input Leakage-SCSI RST electrical specification               |

| n/a      | 11/92 | Revision 4.0, Final, Reformatted to new standard                    |

# Table of Contents

| Preface                                                                             | i   |

|-------------------------------------------------------------------------------------|-----|

| Chapter One Introduction                                                            |     |

| General Description                                                                 | 1-1 |

| SIOP Features Summary                                                               | 1-1 |

| Chapter Two Functional Description                                                  |     |

| SCSI Core                                                                           |     |

| DMA Core                                                                            |     |

| SCSI SCRIPTS Processor                                                              |     |

| SIOP Data Paths                                                                     |     |

| How the SIOP Transfers16 or 32-Bit Data                                             |     |

| 16-Bit Data Transfers for Bus Master Read and Write Cycles 80286 Mode or 80386 Mode |     |

| 80286 Mode 16-Bit Data Transfers                                                    |     |

| 80386 Mode 16-Bit Data Transfers                                                    |     |

| 32-Bit Data Transfers                                                               |     |

| 80486/80386 Mode                                                                    |     |

| How the SIOP Fetches Instructions                                                   |     |

| How to Transfer Data as a Bus Master                                                |     |

| Interrupts                                                                          | 2-8 |

Chapter Three

Signal Descriptions

## Chapter Four Registers

| Reg | rister Descriptions                                                   | .4-3 |

|-----|-----------------------------------------------------------------------|------|

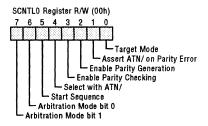

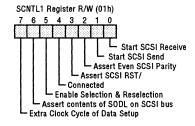

|     | SCSI Control 0 (SCNTL0), Address 00 Read/Write                        | .4-3 |

|     | SCSI Control 1 (SCNTL1), Address 01 Read/Write                        |      |

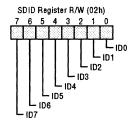

|     | SCSI Destination ID (SDID), Address 02 Read/Write                     | .4-8 |

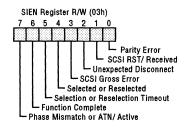

|     | SCSI Interrupt Enable (SIEN), Address 03 Read/Write                   | .4-8 |

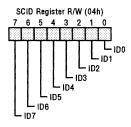

|     | SCSI Chip ID (SCID), Address 04 Read/Write                            | 4-10 |

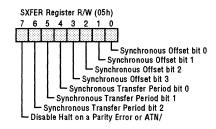

|     | SCSI Transfer (SXFER), Address 05 Read/Write                          | 4-11 |

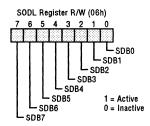

|     | SCSI Output Data Latch (SODL), Address 06 Read/Write                  | 4-13 |

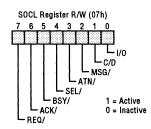

|     | SCSI Output Control Latch (SOCL), Address 07 Read/Write               | 4-14 |

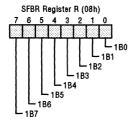

|     | SCSI First Byte Received (SFBR), Address 08 Read Only                 | 4-14 |

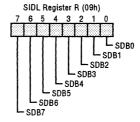

|     | SCSI Input Data Latch (SIDL), Address 09 Read Only                    | 4-15 |

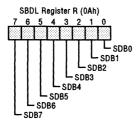

|     | SCSI Bus Data Lines (SBDL), Address 0A Read Only                      | 4-15 |

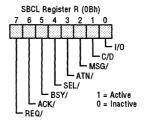

|     | SCSI Bus Control Lines (SBCL), Address 0B Read 53C700, Read/Write -66 | 4-16 |

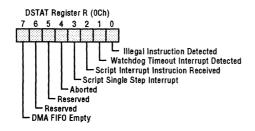

|     | DMA Status (DSTAT), Address 0C Read Only                              |      |

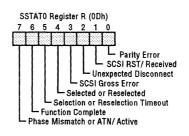

|     | SCSI Status 0 (SSTAT0), Address 0D Read Only                          | 4-18 |

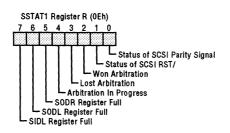

|     | SCSI Status 1 (SSTAT1), Address 0E Read Only                          | 4-20 |

|     | SCSI Status 2 (SSTAT2), Address 0F Read Only                          | 4-21 |

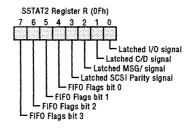

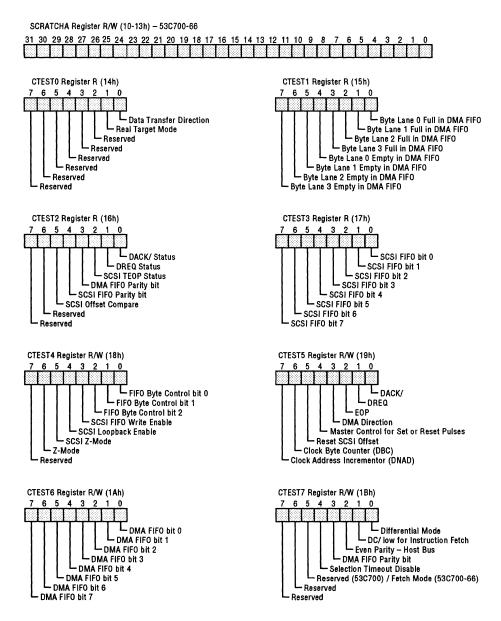

|     | Scratch A (SCRATCHA), Address 10-13 Read/Write                        | 4-22 |

|     | Chip Test 0 (CTEST0), Address 14 Read Only                            | 4-22 |

|     | Chip Test 1 (CTEST1), Address 15 Read Only                            | 4-23 |

|     | Chip Test 2 (CTEST2), Address 16 Read Only                            | 4-23 |

|     | Chip Test 3 (CTEST3), Address 17 Read Only                            | 4-24 |

|     | Chip Test 4 (CTEST4), Address 18 Read/Write                           | 4-25 |

|     | Chip Test 5 (CTEST5), Address 19 Read/Write                           | 4-26 |

|     | Chip Test 6 (CTEST6), Address 1A Read/Write                           | 4-27 |

|     | Chip Test 7 (CTEST7), Address 1B Read/Write                           | 4-28 |

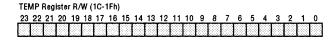

|     | Temporary Stack (TEMP), Address 1C-1F Read/Write                      | 4-29 |

|     | DMA FIFO (DFIFO), Address 20 Read/Write                               | 4-29 |

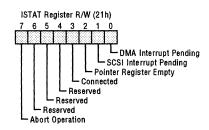

|     | Interrupt Status (ISTAT), Address 21 Read/Write                       | 4-31 |

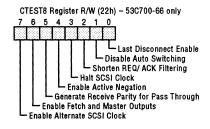

|     | Chip Test 8 (CTEST8), Address 22 Read/Write                           | 4-33 |

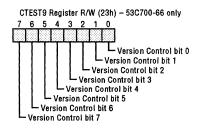

|     | Chip Test 9 (CTEST9), Address 23 Read Only                            | 4-34 |

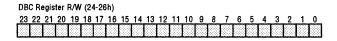

|     | DMA Byte Counter (DBC), Address 24-26 Read/Write                      | 4-34 |

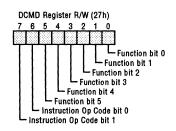

|     | DMA Command (DCMD), Address 27 Read/Write                             | 4-35 |

|     | DMA Next Address for Data (DNAD), Address 28-2B Read/Write            | 4-35 |

|     | DMA SCRIPTS Pointer (DSP), Address 2C-2F Read/Write                   | 4-36 |

|     | DMA SCRIPTS Pointer Save (DSPS), Address 30-33 Read/Write             | 4-36 |

|     | DMA Mode (DMODE), Address 34 Read/Write                               | 4-37 |

|     | DMA Interrupt Enable (DIEN), Register 39 Read/Write                   |      |

|     | DMA Watchdog Timer (DWT), Address 3A Read/Write                       |      |

|     | DMA Control (DCNTL), Address 3B Read/Write                            |      |

|     | Scratch B (SCRATCHB), Address 3C-3F Read/Write                        | 4-41 |

### Chapter Five Command Set

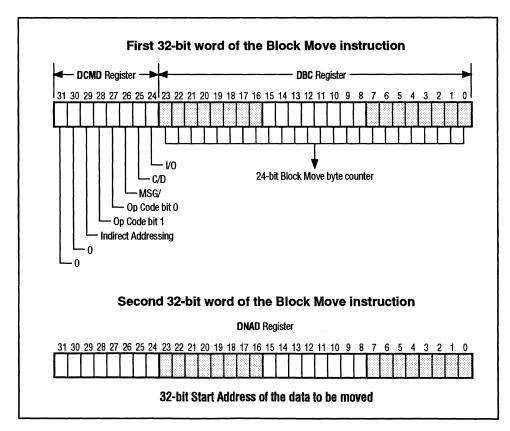

| Block Move Instructions                          | 5-1  |

|--------------------------------------------------|------|

| Indirect Addressing Field (Bit 29)               | 5-2  |

| Opcode Field (Bits 28, 27)                       |      |

| Phase Field (Bits 26-24, MSG, C/D, & I/O)        |      |

| Transfer Counter Field (Bits 23-0, DBC register) |      |

| Start Address Field (Bits 31-0, DNAD register)   |      |

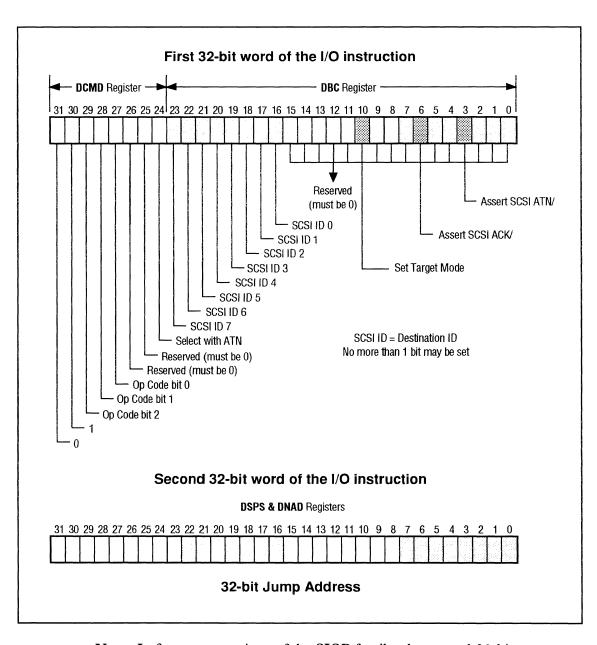

| I/O Instructions                                 | 5-5  |

| Opcode Field (Bits 29, 28, 27)                   | 5-6  |

| Select with ATN/ Field (Bit 24)                  |      |

| SCSI Destination ID Field (Bits 23-16)           |      |

| SET Target Role (Bit 9)                          |      |

| Assert ACK/ (Bit 6) & Assert ATN/ (Bit 3) Fields |      |

| Jump Address Field                               |      |

| jump radices ricid                               |      |

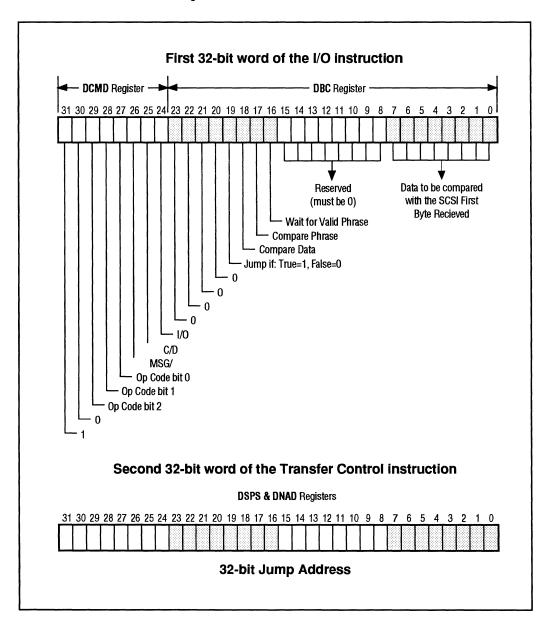

| Transfer Control Instructions                    | 5-9  |

| Opcode Field (Bits 29, 28, 27)                   | 5-10 |

| Phase Field (Bits 26, 25, 24)                    |      |

| Jump if True/False Field (Bit 19)                |      |

| Compare Data (Bit 18)                            |      |

| Compare Phase Field (Bit 17)                     |      |

| Compare Data Field (Bit 16)                      |      |

| Mask for Compare Data (Bits 15-8)                |      |

| Data to be Compared Field (Bits 7-0)             |      |

| Jump Address Field (Bits 31-0, DNAD register)    |      |

| Chapter Six                                      |      |

| How to Use the 53C700/53C700-66                  |      |

| How to Start the SIOP in the SCSI SCRIPTS Mode   | 6-1  |

| How to Execute Normal SCRIPTS                    | 6-1  |

| How to Execute Single-Step SCRIPTS               |      |

| Steps Necessary to Start SCRIPTS                 |      |

| How to Test the SIOP in the Loopback Mode        |      |

| How to Implement Parity Options                  |      |

| How to Control Parity                            |      |

| What Parity Errors and Interrupts Occur?         |      |

| How to Test the DMA FIFO                         |      |

|                                                                                   | 6-9    |

|-----------------------------------------------------------------------------------|--------|

| How to Abort an Operation                                                         |        |

| How to Disconnect the SIOP                                                        | 6-13   |

| How to Select a Target                                                            |        |

| How to Reselect an Initiator                                                      | 6-14   |

| How to Respond to Multiple SCSI IDs                                               | 6-15   |

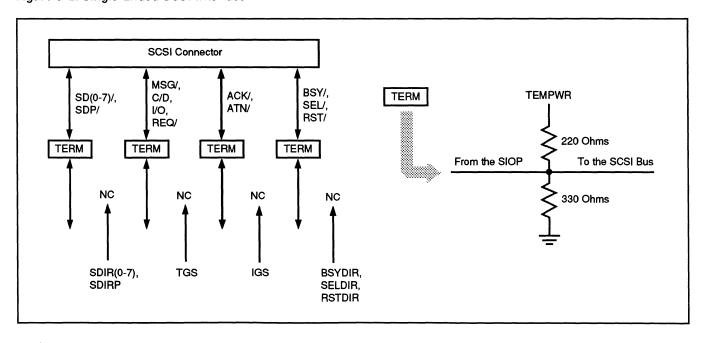

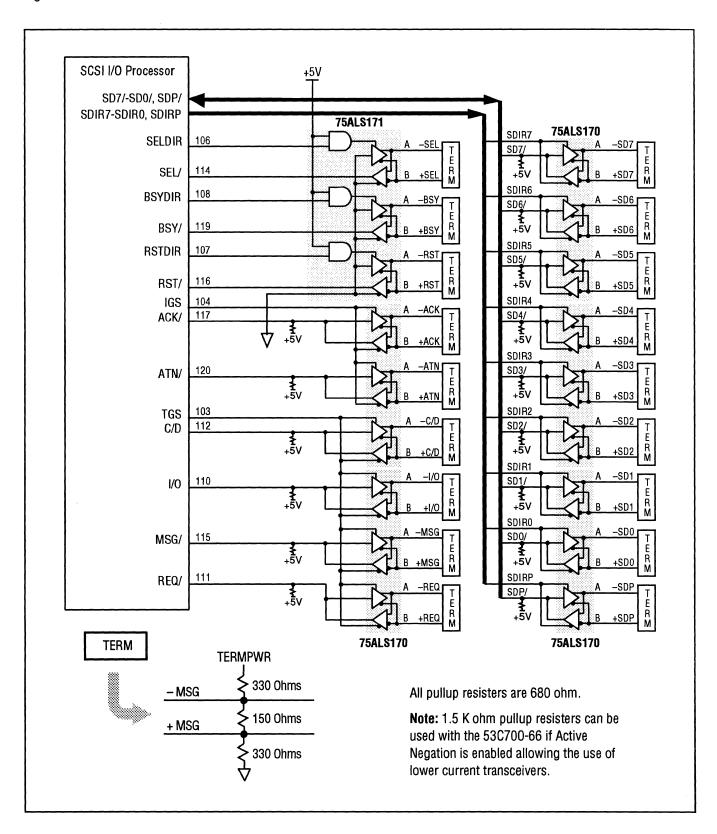

| How to Use Single-Ended SCSI Interface                                            | 6-16   |

| How to use Differential SCSI Interface                                            | 6-18   |

| How to Terminate the SIOP Device                                                  | 6-18   |

| Chapter Seven Electrical Specifications                                           |        |

| DC Characteristics                                                                | 7-1    |

| NCR TolerANT Active Negation Technology Electrical Characteristics (53C700-66 Onl | ly)7-5 |

| AC Electrical Characteristics                                                     | 7-9    |

|                                                                                   | 7-10   |

Appendix A

Register Summary

Appendix B

Mechanical Drawing

Appendix C

SCSI Engineering Notes

Appendix D

53C700 vs 53C700-66 Differences

# Chapter One Introduction

## General Description

The NCR 53C700 SCSI I/O Processor (SIOP) is the industry's first intelligent host adapter on a chip. The 53C700 chip is a powerful, next generation solution for high-performance host-to-peripheral interfacing. The 53C700 can be integrated directly on the motherboard or externally adapted to EISA, Micro Channel™, or other buses.

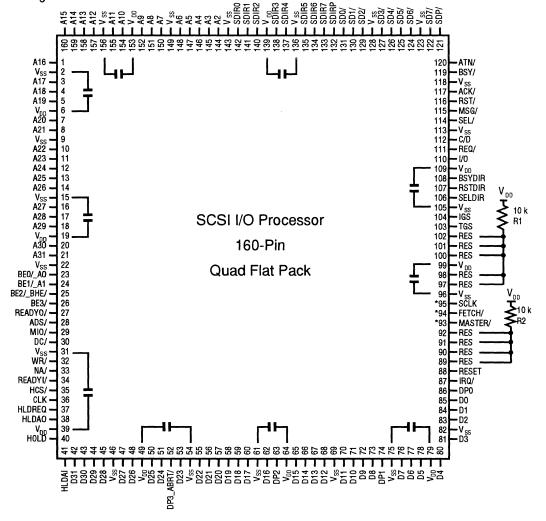

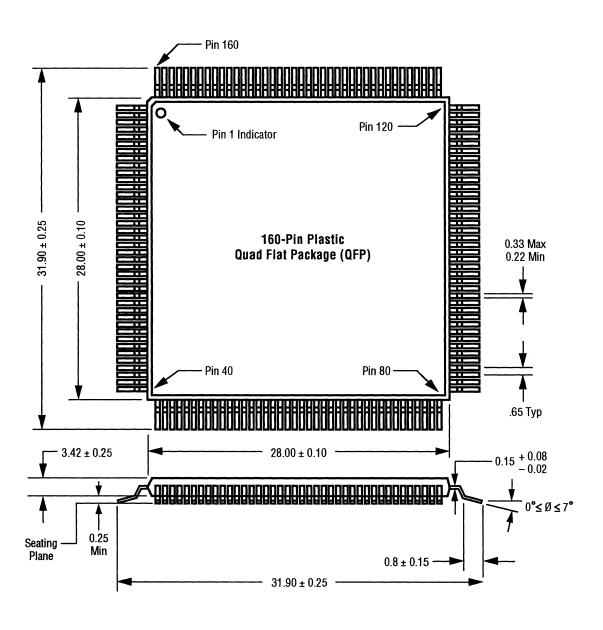

The 53C700 is available as either a 50 MHz chip (labeled and called the 53C700) or a 66 MHz chip (labeled and called the 53C700-66). The 53C700 and the 53C700-66 are both packaged as a 160-pin Quad Flat Pack (QFP). In this manual, when differences exist between the two chips they will be called by their names, but when they are functionally equivalent they will be referred to by SIOP.

### **SIOP Features Summary**

- Supports 25 and 33 MHz 80386 and 80486 memory bus speeds

- Supports 32-bit word data bursts with variable burst lengths

- Unique interrupt status reporting

- High-speed asynchronous/synchronous SCSI bus transfers

- High performance CMOS technology

- Supports variable block size & scatter/gather data transfers

- Minimizes SCSI I/O start latency

- Performs complex bus sequences without interrupts

- Memory transfers up to 47 MB/s for the 53C700 and up to 62 MB/s for the 53C700-66

- Single + 5 V supply

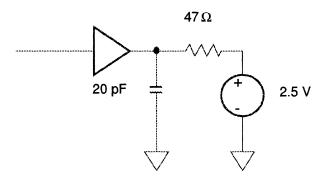

- Active negation of SCSI Data, Parity, REQ and ACK signals with NCR's TolerANT technology improves rise times and Fast SCSI transfer rates in both single-ended and differential modes

# NCR TolerANT<sup>TM</sup> Active Negation Technology

TolerANT is an NCR trade marked term referring to NCR's SCSI transceiver technology. NCR's TolerANT (Active Negation Technology) allows optional active negation of SCSI signals during information transfer phases. More specifically, TolerANT refers to NCR's Active Negation Technology in SCSI drivers and to the conditioning of input signal in SCSI receivers. This feature is only in the 53C700-66 chip. Following is a summary of the TolerANT features and benefits in the 53C700-66 chip.

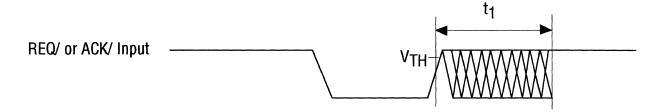

- Filters high frequency noise on SCSI signal inputs due to bus reflections or voltage transients on VTERM

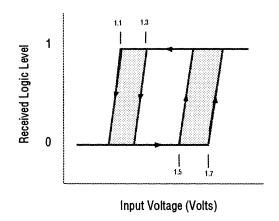

- Wide hysteresis Schmitt triggers with optimal threshold points

- Fast SCSI-2 performance on both singleended and differential cables

- Better high level noise margin on SCSI outputs

- Reduced data double clocking problems

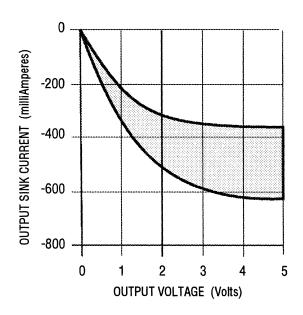

- Controlled slew rate and controlled  $V_{OH}/I_{OH}$

- Compatible with ALT-2 termination, i.e. no terminator overload

- Low power dissipation in terminator

- Glitchless SCSI outputs on power up/down

- No current leakage from SCSI bus when powered down

- Active Negation

TolerANT provides improved data integrity in poor cabling environments. NCR SCSI devices are tolerant of cabling environments in which other devices would be subject to data corruption. Active negation is some times called active deassertion.

Active negation is enabled by setting the EAN bit (bit 4) in the CTEST8 register. It can be used in both single-ended and differential mode. TolerANT is compatible with both the Alternative One and Alternative Two termination schemes proposed by the American National Standards Institute.

Active negation causes the SCSI REQ, ACK, data, and parity signals to be actively pulled up to approximately three volts by internal transistors on each pin. The benefits of this technology include reduced noise when the signal is going high (deasserted), increased performance due to balanced duty cycles, and improved Fast SCSI transfer rates.

### Benefit Summary

#### **Performance**

- Supports 25 and 33 MHz 80386 or 80486 memory bus speeds

- Supports variable block size & scatter/gather data transfers

- Supports 32-bit word data bursts with variable burst lengths

- Minimizes SCSI I/O start latency Only 500 ns to begin compared to 2-8 ms

- Performs complex bus sequences without interrupts including restore data pointers

- Unique interrupt status reporting Reduces ISR overhead

- High-speed asynchronous/synchronous SCSI bus transfers

53C700/53C700-66 = 5.0 MB/s asynchronous 53C700 = 6.25 MB/s synchronous 53C700-66 = 10 MB/s synchronous

Memory transfers in excess of 50 MB/s

#### Integration

- Full 32-bit DMA bus master

- High performance SCSI core

- Integrated SCRIPTS processor

- Allows intelligent Host adapter performance on a mother board

#### Ease of Use

- · Reduces SCSI development effort

- Emulates existing intelligent host adapters

- Easily adapted to the SCSI Common Access Method (CAM)

- Preserves existing software

- Development tools and SCSI SCRIPTS provided

- All interrupts are maskable and pollable

#### Flexibility

- High level programmer's interface (SCSI SCRIPTS)

- Allows tailored SCSI sequences to be executed from main memory

- Flexible sequences to tune I/O performance or to adapt to unique SCSI devices

- Accommodates changes in the logical I/O interface definition

- Low level programmability (register oriented)

- \* 80286, 80386SX, 80386 or 80486 support

- Externally adaptable to EISA, MCA, and other system buses

- Supports changes from initiator to target roles dynamically

#### Reliability

- · 2 K volts ESD protection SCSI signals

- Typical 350 mV SCSI bus hysteresis

- Protection against bus reflections due to impedance mismatches

- Controlled bus assertion times (reduces RFI, improves reliability, and eases FCC certification)

- Latch-up protection greater than 100 mA

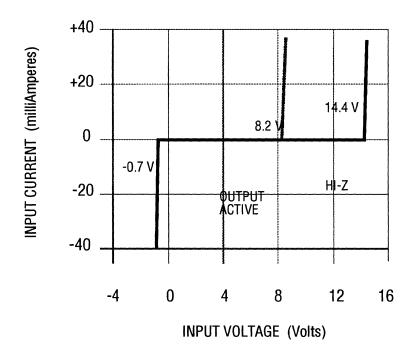

- Voltage feed-through protection (minimum leakage current through SCSI pads)

- · 20% of signals are power and ground

- Ground plane isolation of I/O pads and chip logic

#### **Testability**

- All SCSI signals accessible through programmed I/O

- SCSI loopback diagnostics

- Self-selection capability

- SCSI bus signal continuity checking

Figure 1-2. NCR 53C700/53C700-66 Block Diagram

|  |  |  | la<br>La        |

|--|--|--|-----------------|

|  |  |  | F               |

|  |  |  | -               |

|  |  |  | -               |

|  |  |  | Z = \           |

|  |  |  | V. 2            |

|  |  |  |                 |

|  |  |  |                 |

|  |  |  |                 |

|  |  |  | r-              |

|  |  |  | 1<br>105        |

|  |  |  | 1               |

|  |  |  | L               |

|  |  |  |                 |

|  |  |  | r               |

|  |  |  | L               |

|  |  |  | _               |

|  |  |  | l <sub>ma</sub> |

|  |  |  | f               |

|  |  |  | F               |

|  |  |  | _               |

|  |  |  | ŗ               |

|  |  |  | 2               |

|  |  |  | !"              |

|  |  |  |                 |

|  |  |  |                 |

|  |  |  | × /             |

|  |  |  |                 |

|  |  |  |                 |

|  |  |  | f               |

|  |  |  | _               |

|  |  |  |                 |

|  |  |  | _               |

|  |  |  |                 |

|  |  |  | ſ               |

|  |  |  | Ĺ               |

|  |  |  |                 |

|  |  |  | r               |

|  |  |  | Į.              |

|  |  |  | ſ               |

|  |  |  | · ·             |

|  |  |  |                 |

|  |  |  | ſ               |

|  |  |  | ĺ               |

|  |  |  |                 |

|  |  |  | ı               |

|  |  |  |                 |

|  |  |  |                 |

|  |  |  |                 |

|  |  |  |                 |

|  |  |  |                 |

|  |  |  |                 |

|  |  |  |                 |

# Chapter Two Functional Description

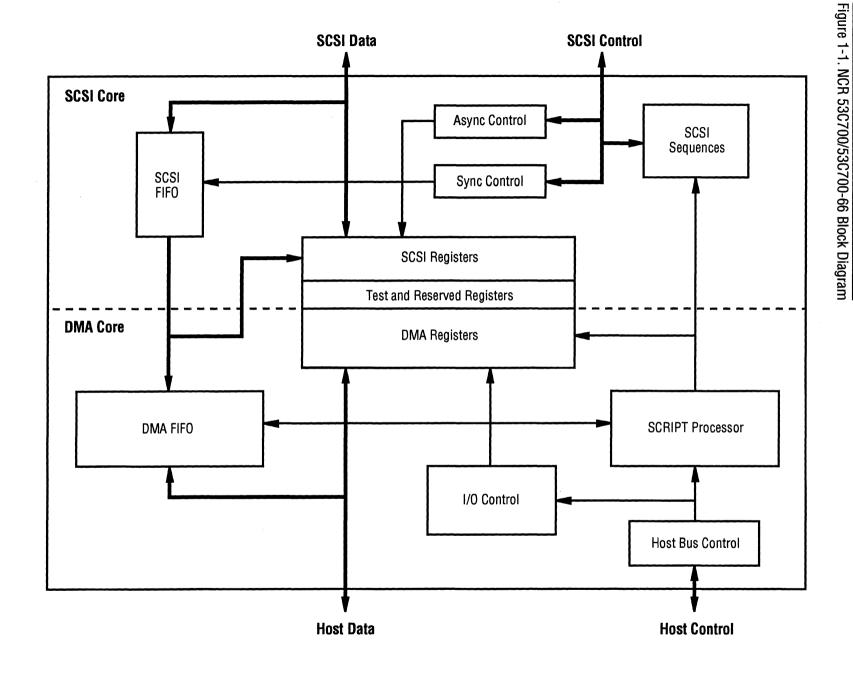

The NCR 53C700 SCSI I/O Processor (SIOP) is the first intelligent SCSI Host adapter on a chip. A high-performance SCSI core and an intelligent 32-bit bus master DMA controller have been integrated with a SCSI SCRIPTS Processor™ to accommodate the flexibility requirements of not only SCSI-1, but SCSI-2, and eventually SCSI-3. This flexibility is supported while solving the protocol performance problems that have plagued both intelligent and non-intelligent adapter designs (See the SCSI I/O Processor Block Diagrams in Figures 1-1 and 1-2). The 53C700-66 contains the same structure as the 53C700 plus added features.

**SCSI** Core

The SCSI core is designed to allow simple migration to SCSI-2 wide bus and enhanced synchronous transfer rate requirements. The 53C700 offers synchronous transfers up to 6.25 MB/s with asynchronous transfers up to 5 MB/s. The 53C700-66 offers synchronous transfers up to 10 MB/s with asynchronous transfers up to 5 MB/s. The programmable SCSI interface makes it easy to "fine tune" the system for specific mass storage requirements or SCSI-2 requirements.

The SCSI core offers low level register access or a high level control interface. Like first generation SCSI devices, the SIOP SCSI core can be accessed as a register oriented device. The ability to sample and/or assert any signal on the SCSI bus can be used in error recovery and diagnostic procedures. Loopback diagnostics are also sup-

ported. The SCSI core may perform a self-selection and operate as both an initiator and a target. The 53C700 can test the SCSI pins for physical connection to the board or the SCSI bus.

Unlike previous generation devices, the SCSI core can be controlled by the SCRIPTS Processor through a high level logical interface. Commands controlling the SCSI core are fetched out of the main Host memory. These commands instruct the SCSI core to select, reselect, disconnect, wait for a disconnect, transfer information, change bus phases and in general, implement all aspects of the SCSI protocol.

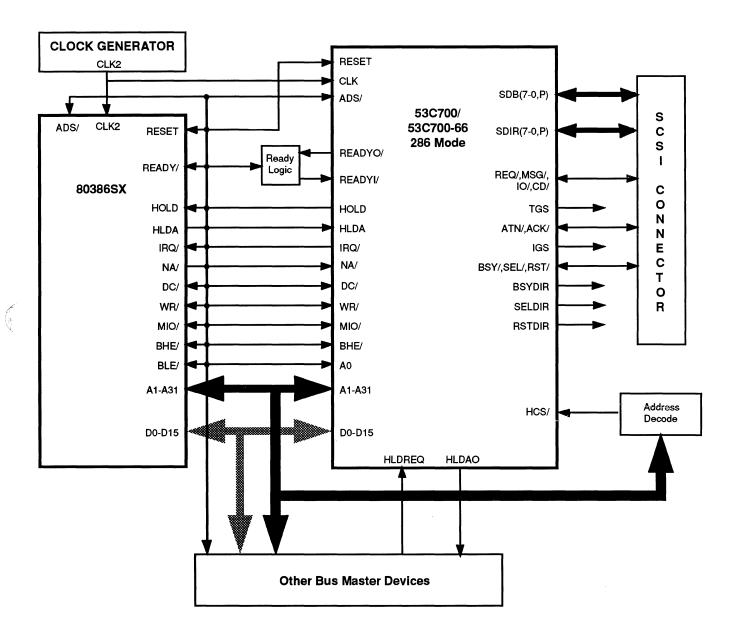

#### **DMA** Core

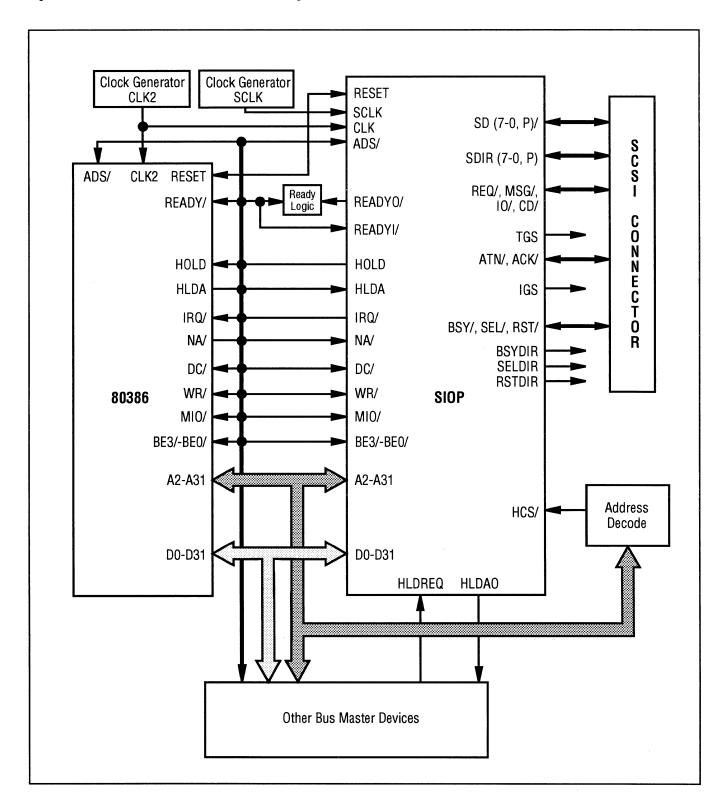

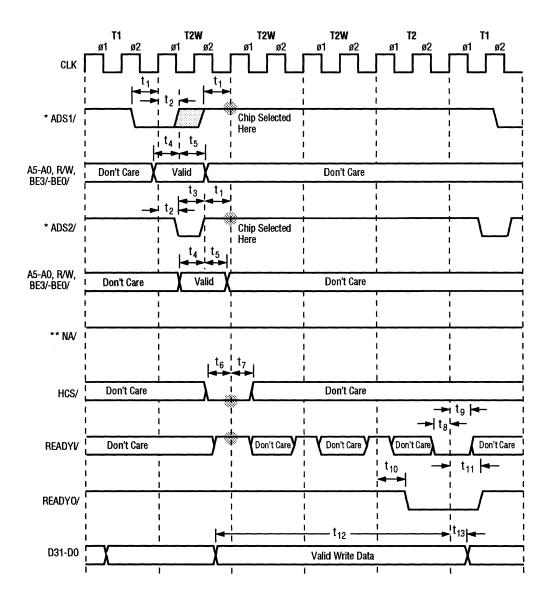

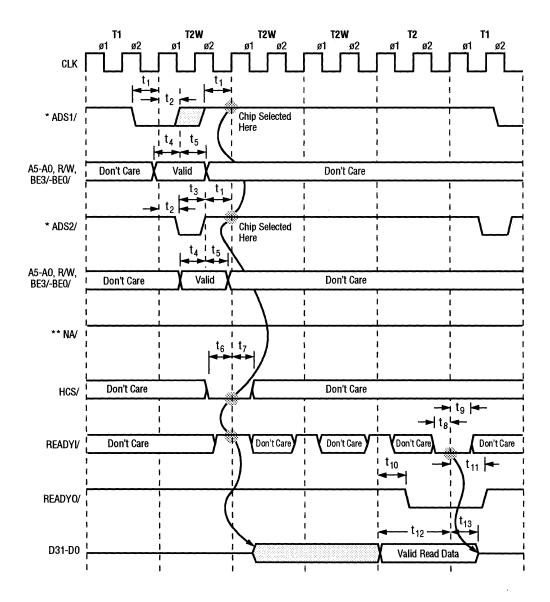

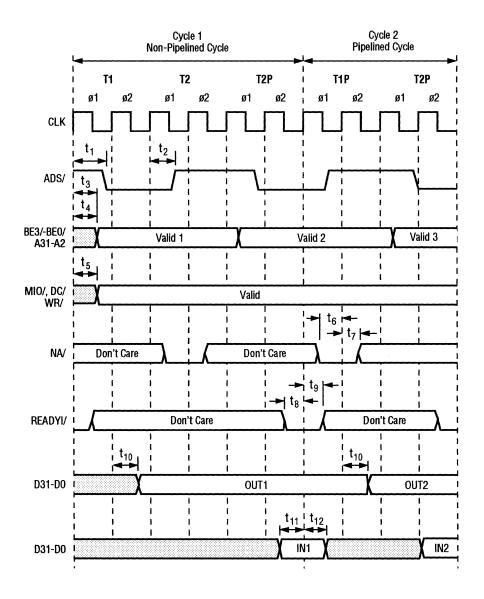

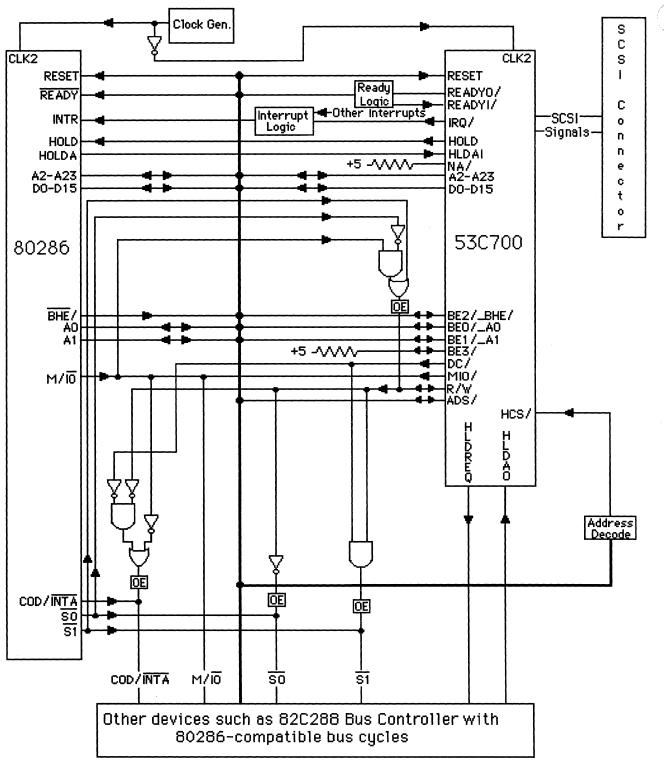

The DMA core is a bus master DMA device that attaches easily to the 80286, 80386, 80386SX, and 80486 processors. The 53C700 supports 25 MHz 80386/80486 (the 53C700-66 supports 33 MHz 80386/80486) bus timings and may be externally adapted to other system buses such as EISA, Micro Channel or attached through a "bus gasket" to a 680X0 device.

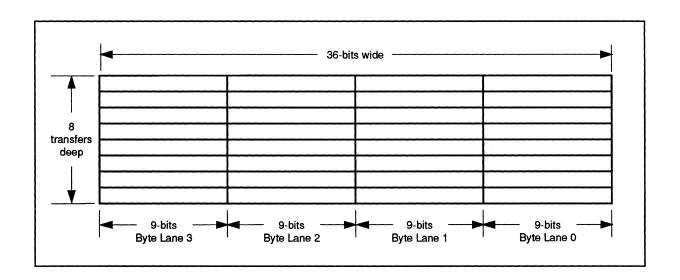

The SIOP supports 16 or 32-bit memory and automatically supports misaligned DMA transfers. As with the 80386/80486, data bus enables are provided for each byte lane. A 32-byte FIFO allows the SIOP to support two, four, or eight (16 or 32-bit) words to be burst across the memory bus interface providing memory transfer rates up to 47 MB/s for the 53C700 and 62 MB/sec for the 53C700-66.

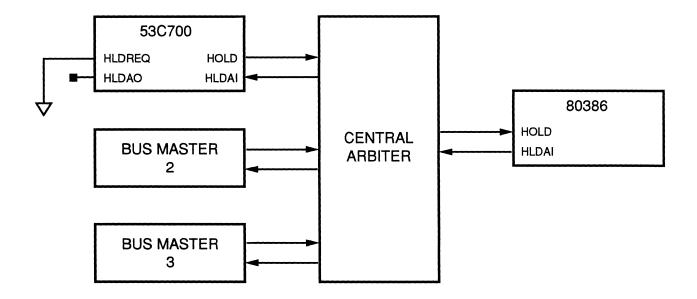

The DMA core is tightly coupled to the SCSI core through the SCRIPTS processor which supports uninterrupted scatter/gather memory operations. A flexible arbitration scheme allows either daisy-chained or "ORed" memory bus request implementations.

#### SCSI SCRIPTSTM Processor

The SCSI SCRIPTS Processor is a 2 MIPS processor that allows both DMA and SCSI instructions to be fetched from Host memory. Algorithms written in SCSI SCRIPTS can control the actions of the SCSI and DMA cores and are executed from 16 or 32-bit system memory. Complex SCSI bus sequences are executed independently of the Host CPU.

The SCRIPTS Processor can begin a SCSI I/O operation in 500 ns. This compares to 2-8 ms required for traditional intelligent Host adapters. The SCRIPTS Processor offers performance and customized algorithms. Design your own algorithms to tune SCSI bus performance, to adjust to

new bus device types (i.e. scanners, communication gateways, etc.), or to incorporate changes in the SCSI-2/3 logical bus definitions without sacrificing I/O performance.

SCSI SCRIPTS are independent of the CPU and system bus in use. Therefore, scripts for an EISA implementation of an 80386 can be identical to the scripts for an 80386SX Micro Channel implementation.

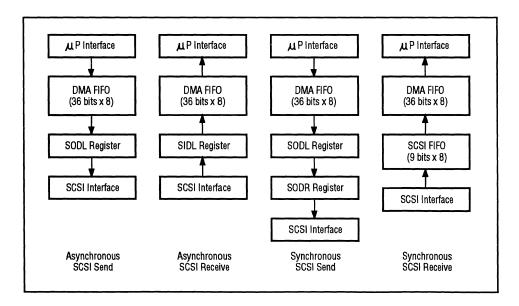

#### SIOP Data Paths

The data paths through the SIOP are dependent on two things.

- Is data being moved in or out of the chip

- Is SCSI data being sent asynchronously or synchronously.

Figure 2-1 shows how data is moved to or from the SCSI bus in each of the four modes.

To determine if any bytes remain in the data path when the chip halts any operation, take the following steps.

#### Asynchronous SCSI Send – Initiator and Target Operation

- 1. Use the algorithm described in the DFIFO register description to determine if any bytes are left in the DMA FIFO.

- Read the SSTAT1 register and examine bit 5

to determine if any bytes are left in the SODL

register. If bit 5 equals 1, then there is a byte

in the SODL register and add one to the

number of bytes left.

#### Synchronous SCSI Send – Initiator and Target Operation

- 1. Use the algorithm described in the DFIFO register description to determine if any bytes are left in the DMA FIFO.

- 2. Read the SSTAT1 register and test bit 5 to determine if any bytes are left in the SODL register. If bit 5 equals 1, then there is one byte in the SODL register, therefore, add one to the number of bytes left.

- 3. Read the SSTAT1 register and test bit 6 to determine if any bytes are remaining in the SODR register. If bit 6 equals 1, then there is one byte in the SODR register, therefore, add one to the number of bytes left.

#### Asynchronous SCSI Receive – Initiator and Target Operation

- 1. Use the algorithm described in the DFIFO register description to determine if any bytes are left in the DMA FIFO.

- 2. Read the SSTAT1 register and test bit 7 to determine if any bytes are left in the SIDL register. If bit 7 equals 1, then there is one byte in the SIDL register, therefore, add one to the number of bytes left.

#### Synchronous SCSI Receive – Initiator and Target Operation

1. Use the algorithm described in the DFIFO register description to determine if any bytes are left in the DMA FIFO.

2. Read the SSTAT2 register and test bits 7-4 (the binary representation of the number of valid bytes in the SCSI FIFO) to determine if any bytes are left in the SCSI FIFO.

# How the SIOP Transfers 16 or 32-Bit Data

The SIOP can transfer data 16-bits or 32-bits per transfer. The two bits controlling how data is transferred are summarized below. These two bits do not determine how SCSI SCRIPTS are fetched. The Scripts-16 bit in the DCNTL register controls whether SCSI SCRIPTS are loaded 16-bits per transfer or 32-bits per transfer.

Table 2-1. Block Move Transfer Bit Descriptions

| BW16 | 286M | Description                                                                                     |

|------|------|-------------------------------------------------------------------------------------------------|

| 0    | 0    | 32-bit data transfers, SIOP asserts and expects 80486/80386 signals                             |

| X    | 1    | 16-bit data transfers, (slave & master mode) SIOP asserts and expects 80286 signals             |

| 1    | 0    | 16-bit data transfers, (master mode data transfers only) SIOP asserts and expects 80386 signals |

| Key: | BW16 | = Bus Width 16-bit in the DMODE register                                                        |

|      | 286M | = 80286 Mode bit in the DMODE register                                                          |

|      | X    | = Don't Care                                                                                    |

| T 1  |      | 1 1 0700                                                                                        |

In bus master mode, the SIOP optimizes moving data to an odd-byte boundary address.

### 16-Bit Data Transfers for Bus Master Read and Write Cycles 80286 Mode or 80386 Mode

The starting address for each Block Move instruction is specified in the second 32-bit word of the instruction. That address is stored in the DNAD register. If starting at an odd address, then the first Block Move operation is a 1-byte transfer on D15-D8, DP1. Each successive transfer is a word transfer to an even address on D15-D0, DP1-DP0. If the SIOP has one byte left to transfer to complete a Block Move instruction, then that byte will be transferred to an even address on D7-D0, DP0.

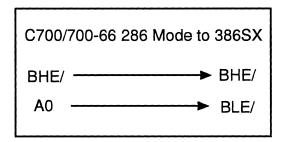

#### 80286 Mode 16-Bit Data Transfers

Table 2-2. 80286 Mode 16-Bit Data Transfers (DMODE register, bit 4 = 1)

| Address<br>(DNAD register)        | BHE/ | <b>A</b> 0 | D15-8 | D7-0 |

|-----------------------------------|------|------------|-------|------|

| Even byte transfers (address + 0) | 1    | 0          | -     | xx   |

| Odd byte transfers (address + 1)  | 0    | 1          | уу    | -    |

| Even word transfers (address + 0) | 0    | 0          | уу    | xx   |

Table 2-3. Address, Data, and Byte Enables for 16-Bit Bus

| уу   | XX         |                            |

|------|------------|----------------------------|

| 15—8 | 70         | Address (longword aligned) |

| BHE/ | <b>A</b> 0 |                            |

#### 80386 Mode 16-Bit Data Transfers

Table 2-4. 80486/80386 Mode 16-Bit Data Transfers (DMODE register bit 4 = 0, bit 5 = 1)

|                            |      | First Cycle |      |      |       | Second Cycle |      |      |      |      |        |       |

|----------------------------|------|-------------|------|------|-------|--------------|------|------|------|------|--------|-------|

| Address<br>(DNAD register) | BE3/ | BE2/        | BE1/ | BEO/ | D15-8 | D7-0         | BE3/ | BE2/ | BE1/ | BEO/ | D15-D8 | D7-D0 |

| 8-Bit Transfer             | 's   |             |      |      |       |              |      |      |      |      |        |       |

| Address + 0                | 1    | 1           | 1    | 0    | -     | ww           | _    | none | -    | -    | -      | -     |

| Address + 1                | 1    | 1           | 0    | 1    | xx    | -            | _    | none | -    | _    | -      | -     |

| Address + 2                | 1    | 0           | 1    | 1    | -     | уу           | -    | none | -    | -    | -      | _     |

| Address + 3                | 0    | 1           | 1    | 1    | ZZ    | -            | -    | none | _    | -    | -      | -     |

| 16-Bit Transfe             | ers  |             |      |      |       |              |      |      |      |      |        |       |

| Address + 0                | 1    | 1           | 0    | 0    | xx    | ww           | _    | none | -    | -    | -      | -     |

| Address + 1                | 1    | 0           | 0    | 1    | xx    | -            | 1    | 0    | 1    | 1    | -      | уу    |

| Address + 2                | 0    | 0           | 1    | 1    | ZZ    | уу           | _    | none | -    | -    | -      | -     |

| 24-Bit Transfe             | ers  |             |      |      |       |              |      |      |      |      |        |       |

| Address + 0                | 1    | 0           | 0    | 0    | xx    | ww           | 1    | 0    | 1    | 1    | -      | уу    |

| Address + 1                | 0    | 0           | 0    | 1    | xx    | -            | 0    | 0    | 1    | 1    | ZZ     | уу    |

| 32-Bit Transfe             | ers  |             |      |      |       |              |      |      |      |      |        |       |

| Address + 0                | 0    | 0           | 0    | 0    | xx    | ww           | 0    | 0    | 1    | 1    | ZZ     | уу    |

Table 2-5. Address, Data Bus and Byte Enables for 32-Bit Bus

| _ | ZZ   | уу    | XX   | ww   |                            |

|---|------|-------|------|------|----------------------------|

|   | 3124 | 23—16 | 158  | 70   | Address (longword aligned) |

|   | BE3/ | BE2/  | BE1/ | BE0/ |                            |

Note: 80386 mode 16-bit data transfers are implemented the same as Intel's 80386 microprocessor.

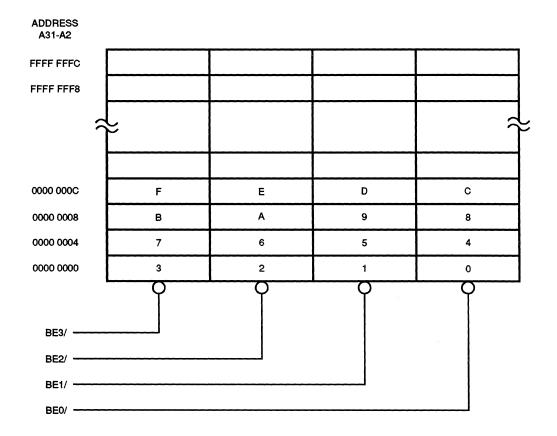

#### 32-Bit Data Transfers

The starting address for each Block Move instruction is specified in the second 32-bit word of the instruction stored in the DNAD register.

If bit 0 = 1, and the Byte Counter Value stored in the DBC register is greater than three, then the first Block Move operation involves a 3-byte transfer on D31-D8, DP3-DP1 with BE3/, BE2/, and BE1/ all driven active. Each successive transfer will occur on D31-D0, DP3-DP0 with BE3/-BE0/ all driven active.

If the SIOP has two-bytes to transfer in order to complete a Block Move instruction, then those bytes will be transferred on D15-D0, DP1-DP0 with BE1/ and BE0/ driven active.

If the SIOP has one-byte to transfer in order to complete a Block Move instruction, then that byte will be transferred on D7-D0, DP0 with BE0/driven active.

If the SIOP has three-bytes to transfer to complete a Block Move instruction, those bytes will be transferred on D23-D0, DP2-DP0 with BE2/, BE1/, and BE0/ driven active.

#### 80486/80386 Mode

Table 2-6. 32-Bit Data Transfers in 80486/80386 Mode

|             | BE<br>3/ | BE<br>2/ | BE<br>1/ | BE<br>0/ |  |

|-------------|----------|----------|----------|----------|--|

| Address + 0 | 0        | 0        | 0        | 0        |  |

| Address + 1 | 0        | 0        | 0        | 1        |  |

| Address + 2 | 0        | 0        | 1        | 1        |  |

| Address + 3 | 0        | 1        | 1        | 1        |  |

**Key:** BE3/-BE0/ 0 = asserted 1 = deasserted Address longword boundary aligned

# How the SIOP Fetches Instructions

Write the address containing the first SCSI SCRIPTS to the DSP register to start the SIOP instruction fetch process. After the first SCSI SCRIPTS address is written to the DSP register, the SIOP continues to fetch and execute instructions by reading them from system memory.

SCSI SCRIPTS are not required to reside in system memory because by decoding a certain address space, they could reside in a PROM. Only store SCSI SCRIPTS in a memory-mapped address because the SIOP does not fetch instructions out of I/O-mapped address space. Each SCSI SCRIPTS instruction consists of two 32-bit words. Load SCSI SCRIPTS instructions in one of two ways: by fetching two 32-bit words or by fetching four 16-bit words.

If SCSI SCRIPTS are to be loaded 16-bits per transfer, write the "SCRIPTS Loaded in 16-Bit Mode" bit in the DCNTL register to 1. The DC/control signal can be driven high or low depending on the status of the "DC/Output Low for Instruction Fetch" bit in the CTEST7 register. If this bit is 1, then the DC/ signal will be low during instruction fetch cycles. Allowing the DC/ signal to be driven low during instruction fetches allows the system designer to choose whether SCSI SCRIPTS instructions should reside in cacheable or alternate memory space.

If this bit is 0, then the DC/ signal will be high during instruction fetch cycles. Usually only control (DC/ low) resides in the cache memory and data information (DC/ high) does not.

### How To Transfer Data as a Bus Master

When the SIOP becomes bus master, it takes over control of the system bus and can transfer data in a variety of ways. The SIOP can transfer data to I/O addresses, memory addresses, or a fixed ad-

dress. The following three bits determine the width and type of data transfer that will occur once the SIOP assumes bus mastership and is ready to transfer data.

Table 2-7. SIOP Bus Master Data Transfer Descriptions

| BW16 | IOM | FAM | Transfer Description                                                              |  |

|------|-----|-----|-----------------------------------------------------------------------------------|--|

| 0    | 0   | 0   | 32-bit transfers to a memory address which is incremented after each transfer     |  |

| 0    | 0   | 1   | 32-bit transfers to a memory address which is not incremented after each transfer |  |

| 0    | 1   | 0   | 32-bit transfers to an I/O address which is incremented after each transfer       |  |

| 0    | 1   | 1   | 32-bit transfers to an I/Oaddress which is not incremented after each transfer    |  |

| 1    | 0   | 0   | 16-bit transfers to a memory address which is incremented after each transfer     |  |

| 1    | 0   | 1   | 16-bit transfers to a memory address which is not incremented after each transfer |  |

| 1    | 1   | 0   | 16-bit transfers to an I/O address which is incremented after each transfer       |  |

| 1    | 1   | 1   | 16-bit transfers to an I/O address which is not incremented after each transfer   |  |

**Key:** BW16 = Bus Width 16-bit in the DMODE register

IOM = I/O or Memory Mapped bit in the DMODE register

FAM = Fixed Address Mode bit in the DMODE register

#### Interrupts

#### Polling vs. Hardware Interrupts

The external microprocessor can be informed of an interrupt condition by polling or hardware interrupts. Polling means that the microprocessor must continually loop and read a register until it detects a bit set that indicates an interrupt. This method is the fastest, but it wastes CPU time that could be used by other system tasks. The preferred method of detecting interrupts in most systems is hardware interrupts. In this case, the 53C7X0 will assert the Interrupt Request (IRQ/) line that will interrupt the microprocessor, causing the microprocessor to execute an interrupt service routine. A hybrid approach would use hardware for long waits, and use polling for short waits.

#### Registers

The five registers in the 53C7X0 that are used for detecting or defining interrupts are the ISTAT (register 0x21), the SSTAT0 (register 0x0D), the DSTAT (register 0x0C), the SIEN (register 0x03), and the DIEN (register 0x39).

The ISTAT is the only register than can be accessed as a slave during SCRIPTS operation, therefore it is the register that is polled when polled interrupts are used. It is also the first register that should be read when the IRQ/ pin has been asserted in association with a hardware interrupt. If the SIP bit in the ISTAT register is set, then a SCSI-type interrupt has occurred and the SSTATO register should be read. If the DIP bit in the ISTAT register is set, then a DMA-type interrupt has occurred and the DSTAT register should be read. SCSI-type and DMA-type interrupts may occur simultaneously, so in some cases both SIP and DIP may be set.

The SSTAT0 register contains the SCSI-type interrupt bits. Reading this register will determine which condition or conditions caused the SCSI-type interrupt, and will clear that SCSI interrupt condition. If the 53C7X0 is receiving data from the SCSI bus and a fatal interrupt condition

occurs, the 53C7X0 will attempt to send the contents of the DMA FIFO to memory before generating the interrupt. If the 53C7X0 is sending data to the SCSI bus and a fatal SCSI interrupt condition occurs, data could be left in the DMA FIFO. Because of this the DFE bit in DSTAT should be checked. If this bit is clear, set the CLF (Clear DMA and SCSI FIFOs) bit before continuing.

The DSTAT register contains the DMA-type interrupt bits. Reading this register will determine which condition or conditions caused the DMAtype interrupt, and will clear that DMA interrupt condition. Bit 7 in DSTAT, DFE (DMA FIFO Empty), is purely a status bit; it will not generate an interrupt under any circumstances and will not be cleared when read. DMA interrupts will flush neither the DMA nor SCSI FIFOs before generating the interrupt, so the DFE bit in the DSTAT register should be checked after any DMA interrupt. If the DFE bit is clear, then the FIFOs must be cleared by setting the CLF (Clear DMA and SCSI FIFOs) bit, or flushed by setting the FLF (Flush DMA FIFO) bit. The CLF bit is bit 6 in the DFIFO register on the 53C700 and 53C700-66, bit 2 in CTEST8 in the 53C710, and bit 2 in CTEST3 in the 53C720. The FLF bit is bit 7 in the DFIFO register in the 53C700 and 53C700-66, bit 3 in CTEST8 in the 53C710, and bit 3 in CTEST3 in the 53C720.

The SIEN register is the interrupt enable register for the SCSI interrupts in SSTAT0.

The DIEN register is the interrupt enable register for DMA interrupts in DSTAT.

#### Fatal vs. Non-Fatal Interrupts

A fatal interrupt, as the name implies, always causes SCRIPTS to stop running. A non-fatal interrupt will cause SCRIPTS to stop running only if it is not masked. Masking will be discussed later in this engineering note. All DMA interrupts (indicated by the DIP bit in ISTAT and one or more bits in DSTAT being set) are fatal.

Some SCSI interrupts (indicated by the SIP bit in the ISTAT and one or more bits in SSTAT0 being set) are non-fatal. When the chip is operating in Initiator mode, only the CMP (Function Complete) and SEL (Selected or Reselected) interrupts are non-fatal. When operating in Target mode CMP, SEL, and M/A (Target mode: ATN/ active) are non-fatal. Refer to the description for the DHP (Disable Halt on a Parity Error or ATN/ active (Target Mode Only)) bit in the SXFER register to configure the chip's behavior when the ATN/ interrupt is enabled during Target mode operation.

The reason for non-fatal interrupts is to prevent SCRIPTS from stopping when an interrupt occurs that does not require service from the CPU. This prevents an interrupt when arbitration is complete (CMP set), when the 53C7X0 has been selected or reselected (SEL set), or when the initiator has asserted ATN (target mode: ATN/ active). These interrupts are not needed for events that occur during high-level SCRIPTS operation.

#### Masking

Masking an interrupt means disabling or ignoring that interrupt. Interrupts can be masked by clearing bits in the SIEN (for SCSI interrupts) register or DIEN (for DMA interrupts) register. How the chip will respond to masked interrupts depends on: whether polling or hardware interrupts are being used; whether the interrupt is fatal or non-fatal; and whether the chip is operating in Initiator or Target mode.

If a non-fatal interrupt is masked and that condition occurs, SCRIPTS will not stop, the appropriate bit in the SSTATO will still be set, the SIP bit in the ISTAT will not be set, and the IRQ/ pin will not be asserted. See the section on non-fatal vs. fatal interrupts for a list of the non-fatal interrupts.

If a fatal interrupt is masked and that condition occurs, then SCRIPTS will still stop, the appropriate bit in the DSTAT or SSTAT0 register will be set, the SIP or DIP bits in the ISTAT will be set, and the IRQ/ pin will not be asserted.

When the chip is initialized, enable <u>all</u> fatal interrupts if you are using hardware interrupts. If a fatal interrupt is disabled and that interrupt condition occurs, SCRIPTS will halt and the system will never know it unless it times out and checks the ISTAT after a certain period of inactivity.

If you are polling the ISTAT instead of using hardware interrupts, then masking a fatal interrupt will make no difference since the SIP and DIP bits in the ISTAT inform the system of interrupts, not the IRQ/ pin.

Masking an interrupt after IRQ/ is asserted will not cause IRQ/ to be deasserted.

#### **Stacked Interrupts**

The 53C7X0 has the ability to stack interrupts if they occur one after the other. If the SIP or DIP bits in the ISTAT register are set (first level), then there is already at least one pending interrupt and any future interrupts will be stacked in extra registers behind the SSTAT0 and DSTAT registers (second level). When two interrupts have occurred and the two levels of the stack are full, any further interrupts will set additional bits in the extra registers behind SSTAT0 and DSTAT. When the first level of interrupts are cleared, all the interrupts that came in afterward will move into the SSTAT0 and DSTAT. After the first interrupt is cleared by reading the appropriate register, the IRQ/ pin will be deasserted for a set time as published in the product Data Manual; the stacked interrupt(s) will move into the SSTAT0 or DSTAT; and the IRQ/ pin will be asserted once again.

Since a masked non-fatal interrupt will not set the SIP or DIP bits, interrupt stacking will not occur as a result of a masked, non-fatal interrupt. A masked, non-fatal interrupt will still post the interrupt in SSTAT0 but will not assert the IRQ/pin. Since no interrupt is generated, future interrupts will move right into the SSTAT0

instead of being stacked behind another interrupt. When another condition occurs that generates an interrupt, the bit corresponding to the earlier masked non-fatal interrupt will still be set.

A related situation to interrupt stacking is when two interrupts occur simultaneously. Since stacking does not occur until the SIP or DIP bits are set, there is a small timing window in which multiple interrupts can occur but will not be stacked. These could be multiple SCSI interrupts (SIP set), multiple DMA interrupts (DIP set), or multiple SCSI and multiple DMA interrupts (both SIP and DIP set).

As previously mentioned, DMA interrupts will not attempt to flush the FIFOs before generating the interrupt. It is important to set either the CLF (Clear DMA and SCSI FIFOs) bit or the FLF (Flush DMA FIFO) bit if a DMA interrupt occurs and the DFE (DMA FIFO Empty) bit is not set. This is because any future SCSI interrupts will not be posted until the DMA FIFO is clear of data. These 'locked out' SCSI interrupts will be posted as soon as the DMA FIFO is empty.

#### Halting in an Orderly Fashion

When an interrupt occurs, the 53C7X0 will attempt to halt in an orderly fashion.

- If in the middle of an instruction fetch, the fetch will be completed, except in the case of a Bus Fault or Watchdog Timeout. Execution will not begin, but the DSP will point to the next instruction since it is updated when the current Script is fetched.

- If the DMA direction is a write to memory and a SCSI interrupt occurs, the 53C7X0 will attempt to flush the DMA FIFO to memory before halting. Under any other circumstances only the current cycle will be completed before halting, so the DFE bit in DSTAT should be checked to see if any data remains in the DMA FIFO.

- SCSI REQ/ACK handshakes that have begun will be completed before halting.

- The 53C7X0 will attempt to clean up any outstanding synchronous offset before halting.

- In the case of Transfer Control Instructions, once instruction execution begins it will continue to completion before halting.

- If the instruction is a JUMP/CALL WHEN <phase>, the DSP will be updated to the transfer address before halting.

- All other instructions may halt before completion.

#### Sample Interrupt Service Routine

The following is a sample of an interrupt service routine for the 53C7X0. It can be repeated if polling is used, or should be called when the IRQ/pin is asserted if hardware interrupts are used.

- 1. Read ISTAT

- 2. If only the SIP bit is set, read SSTAT0 to clear the SCSI interrupt condition and get the SCSI interrupt status. The bits in the SSTAT0 tell which SCSI interrupt(s) occurred and determine what action is required to service the interrupt(s).

- 3. If only the DIP bit is set, read the DSTAT to clear the interrupt condition and get the DMA interrupt status. The bits in the DSTAT will tell which DMA interrupt(s) occurred and determine what action is required to service the interrupt(s).

- 4. If both the SIP and DIP bits are set, read SSTAT0 and DSTAT as a word to clear the SCSI and DMA interrupt condition and get the interrupt status. If using 8-bit reads of the SSTAT0 and DSTAT registers to clear interrupts, insert 10 CLKs on the 53C700 and 53C700-66, and 12 CLKs on the 53C710 between the consecutive reads to ensure that the interrupts clear properly. Both the SCSI and DMA interrupt conditions should be handled before leaving the ISR. It is recom-

- mended that the DMA interrupt be serviced before the SCSI interrupt because a serious DMA interrupt condition could influence how the SCSI interrupt is acted upon.

- 5. When using polled interrupts, go back to step 1 before leaving the interrupt service routine, in case any stacked interrupts moved in when the first interrupt was cleared. When using hardware interrupts, the IRQ/ pin will be asserted again if there are any stacked interrupts. This should cause the system to reenter the interrupt service routine.

# Chapter Three Signal Descriptions

There are two groups of signals: Host interface signals and SCSI interface signals. The NCR 53C700 SIOP will be referred to as the SIOP throughout this document. A slash ("/") indicates an active-low signal. An underscore ("\_") indicates a dual-function pin. An ("I") for Input, an ("O") for Output, and ("I/O") for Input and Output signal. Note: All unused inputs or bi-directional signals that could become an input should be tied high or low but must never be left floating. This applies to any CMOS device.

<sup>\*</sup> If unused, pins should be connected to a 10 K pullup resistor

Table 3-1. Host Interface Signals

| Symbol    | Pin#                                                                       | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|----------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A(31-2)   | 21-20, 18-16, 14-10,<br>8-7, 5-3, 160-157,<br>155-154, 152-150,<br>148-144 | I/O  | Host Address Bus – Tri-state, active-high. These signals provide physical memory addresses or I/O port addresses dependent on the MIO/ signal state. The 80386/80486 drives the address lines in slave mode and the SIOP drives the address lines in master mode. In 80286 mode, the A(31-24) signals are driven to the value in the DNAD register to be used for the upper address signals for memory paging. The address outputs are synchronized with the CLK signal. During data transfer in slave mode to/from the SIOP's registers, use A(5-2) in 80386/80486 mode, and A(5-0) in 80286 mode.          |

| D(31-0)   | 42-45, 47-48, 50-51, 53, 55-60, 62, 65-68, 70-73, 76-78, 80-81, 83-85      | I/O  | Host Data Bus – Tri-state, active-high. These signals provide the data path between the 80486/80386/80286 and the SIOP. Data can be transferred on 32-bit or 16-bit buses. This is controlled by bits 4 and 5 in the DMODE register. The DMODE register should not be changed while DMA is active. Data outputs are synchronized with the CLK signal.                                                                                                                                                                                                                                                        |

| DP3_ABRT/ | 52                                                                         | I/O  | Host Data Parity for byte lane 3 or Abort – Tri-state, active-low. This signal can be used as the parity bit for D31-D24. When not using the pass parity option, use this signal as an Abort Transfer pin. To enable this signal as an ABRT/ signal, parity generation must be enabled (bit 2, the SCNTL0 register). When ABRT/ is asserted, the DMA transfer is aborted. The ABRT input is asynchronous and requires a 40 ns pulse width. When this signal is a parity signal, its output is synchronized with the CLK signal.                                                                              |

| DP(2-0)   | 63, 74, 86                                                                 | I/O  | Host Data Parity Bits – Tri-state, active-high. These signals are the parity bits for the Host data bus, D(23-0). DP2 is the parity signal for data bits D(23-16), DP1 is the parity signal for data bits D(15-8), and DP0 is the parity signal for data bits D(7-0). The SIOP supports both even and odd parity on the Host data bus. Host bus even/odd parity is programmed through bit 2 of the CTEST7 register. When the SIOP is configured for parity generation (bit 2, the SCNTLO register), these signals are placed in a high-impedance state. Parity outputs are synchronized with the CLK signal. |

Table 3-1. Host Interface Signals (Continued)

| Symbol    | Pin# | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BE3/      | 26   | I/O  | Byte Enable, BE3/ – Tri-state, active-low. This signal enables data transfer in the D(31-24) data byte lane. It is driven by the Host when the SIOP is in slave mode and driven by the SIOP during a DMA transfer. In 286 mode, this signal is not defined and should be pulled high. Bit 4 of the DMODE register determines whether the chip operates in 286 mode or 386/486 mode. The output is synchronized with the CLK signal. |

| BE2/_BHE/ | 25   | I/O  | Byte Enable, BE2/ or Byte High Enable/ – Tri-state, active-low. In 386/486 mode, this signal enables data transfers on the D(23-16) data byte lane. In 286 mode, it distinguishes between 8-bit and 16-bit data transfers. Bit 4 of the DMODE register determines whether the chip operates in 286 or 386 mode. The output is synchronized with the CLK signal.                                                                     |

| BE1/_A1   | 24   | I/O  | Byte Enable, BE1/ or Address, A1 – Tri-state, active-low. In 386/486 mode, this signal enables data transfer in the D(15-8) data byte lane. In 286 mode, this pin is active-high, address line A1, and should be connected to A1 of the 80286.  Bit 4 of the DMODE register determines whether the chip operates in 286 or 386/486 mode. The output is synchronized with the CLK signal.                                            |

| BEO/_A0   | 23   | I/O  | Byte Enable, BE0/ or Address, A0 – Tri-state, active-low. In 386 mode, this signal enables data transfers on the D(7-0) data byte lane. In 286 mode, this signal is tri-state, active-high and used as address line A0, connected to the A0 pin of the 286. Bit 4 of the DMODE register determines whether the chip is operating in 286 or 386 mode. The output is synchronized with the CLK signal.                                |

| W_R/      | 32   | I/O  | Write or Read/ – Tri-state. This signal defines the type of bus cycle being performed. When the SIOP is in slave mode, high is a write to the chip and low is a read from the chip. When the SIOP is in master mode, high is a write to the system bus and low is a read from the system bus. The output is synchronized with the CLK signal.                                                                                       |

Table 3-1. Host Interface Signals (Continued)

| Symbol  | Pin# | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC/     | 30   | O    | Data Control Output – Tri-state. This signal defines the type of bus cycle being performed. A high signal indicates data is on the bus. A low signal indicates that the bus contains control information. In master mode this signal can be driven to either state when the SIOP is performing an instruction fetch operation. The assertion or deassertion of this signal during instruction fetch operations is controlled through bit 1 in the CTEST7 register. The output is synchronized with the CLK signal.                                                                                                                             |

| MIO/    | 29   | O    | Memory Input/Output – Tri-state. This signal defines the type of bus cycle being performed. When high, transfer is to a memory address. When low, transfer is to an I/O address. The output is synchronized with the CLK signal.                                                                                                                                                                                                                                                                                                                                                                                                               |

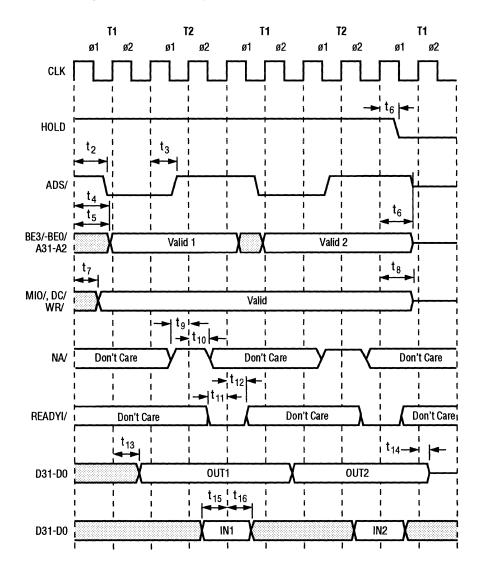

| ADS/    | 28   | I/O  | Address Status – Tri-state, active-low. ADS/ indicates that address and control signals are valid and stable. In slave mode, this signal is driven by the 286/386/486. In master mode, it is driven by the SIOP. The output is synchronized with the CLK signal.                                                                                                                                                                                                                                                                                                                                                                               |

| NA/     | 33   | I    | Next Address Request – Active-low. When the SIOP is in master mode, NA/ indicates that the system is requesting address pipelining. During address pipelining, address and status signals for the next bus cycles are driven during the current cycle. An active signal indicates that the system is ready to accept new values of BE3/, BE2/, BHE/, BE1/A1, BE0/A0, A31-A2, WR/, DC/, and MIO/. It is monitored only when in master mode. This signal should not be driven active during a slave access to the SIOP.                                                                                                                          |

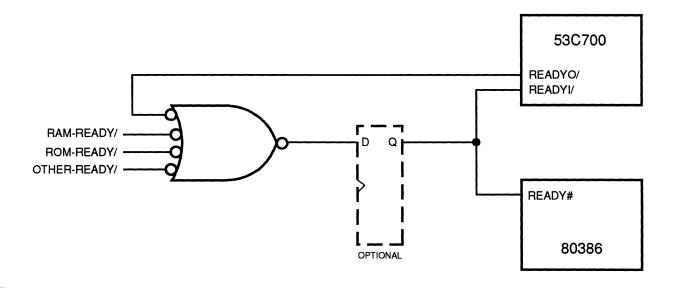

| READYI/ | 34   | I    | Ready Transfer Acknowledge – Active-low. In master mode, READYI/ indicates that the slave device is ready to transfer data. When READYI/ is active during a read cycle, the SIOP latches the input data and terminates the cycle. If READYI/ is active during a write cycle, the SIOP terminates the bus cycle. In slave mode, when data is read from the SIOP, this signal is monitored by the SIOP to determine when to stop driving the data bus. This allows wait states for both read's and writes in slave mode to be inserted to extend the bus cycle if needed. The 53C700 always needs a READYI/ to terminate a read or write signal. |

Table 3-1. Host Interface Signals (Continued)

| Symbol  | Pin# | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READYO/ | 27   | O    | Ready Output Signal – Active-low, totem-pole. When the SIOP is in slave mode, it asserts READYO/ to acknowledge the completion of a bus cycle. A 53C700 slave read or write cycle is a minimum of 5t states or 10 clock periods. It is not used in master mode. The output is synchronized with the CLK signal.                                                                                               |

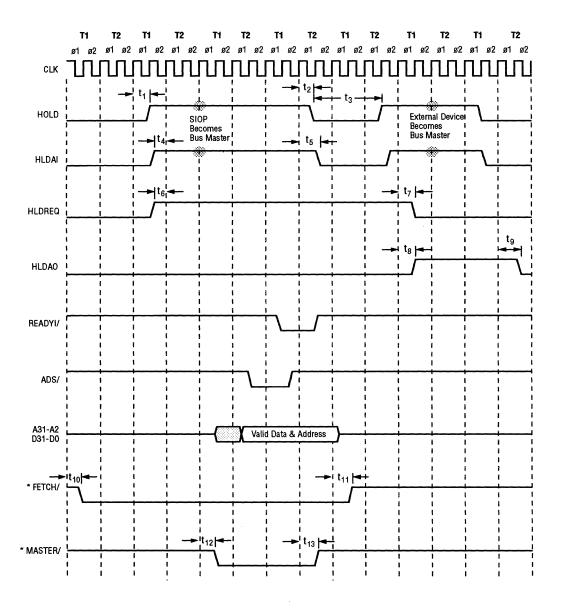

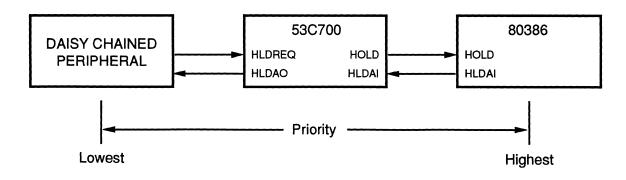

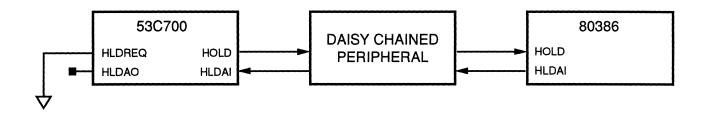

| HOLD    | 40   | O    | Hold Request Output – Active-high, totem-pole. This output only signal is asserted when the SIOP needs access to the host system bus while performing a DMA transfer. If the HLDREQ input signal is asserted, this signal is asserted to allow another bus master device to gain control of the system bus using a daisy-chaining* scheme. The output is synchronized with the CLK signal.                    |

| HLDREQ  | 37   | I    | Bus Hold Request Input – Active-high. This signal indicates that another bus master device requests use of the host bus. It allows the system to incorporate a daisy-chaining* technique for handling system bus requests for use. If another bus master device requests the bus at the same time as the SIOP, the SIOP has priority. The signal can be asserted asynchronously by another bus master device. |

| HLDAI   | 41   | I    | Bus Hold Acknowledge In – Active-high. This signal is asserted by the Host CPU to indicate that it has given up the system bus. This signal is passed through to the HLDAO pin unless the SIOP requires use of the bus.                                                                                                                                                                                       |

| HLDAO   | 38   | O    | Bus Hold Acknowledge Out – Active-high, totem-pole. This signal is a copy of HLDAI, unless the SIOP assumes bus mastership and uses the system bus. If HLDAI is active and the SIOP does not need to use the system bus, then this signal is asserted. The output is synchronized with the CLK signal.                                                                                                        |

<sup>\*</sup> See 80386/80486 Interface in Section 6 for more information on HOLD/HLDA schemes.

Table 3-1. Host Interface Signals (Continued)

| Symbol   | Pin# | Туре | Description                                                                                                                                                                                                                                                                                                     |

|----------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

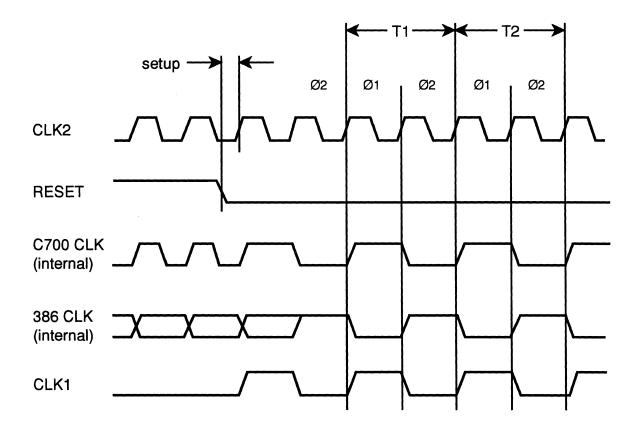

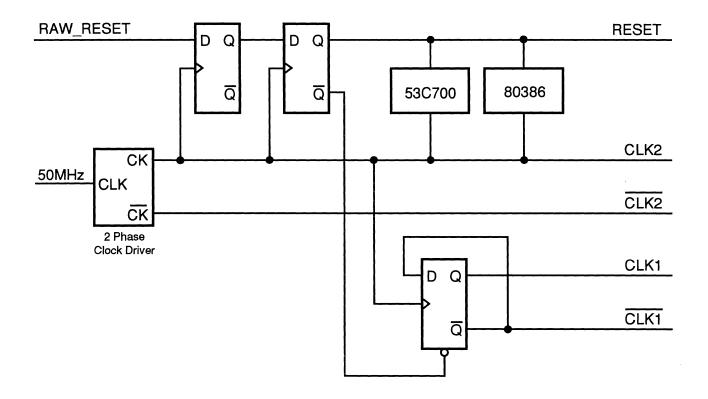

| RESET    | 88   | I    | Hardware Reset – Active-high. When asserted, all registers are set to the default values as described in the register sections. The signal is connected to the 80386 RESET line. This signal also defines the Ø1 and Ø2 clock phases.                                                                           |

| IRQ/     | 87   | O    | Interrupt Request – Active-low, open drain. This signal is asserted in response to an interrupt condition or when a SCSI SCRIPTS interrupt instruction is issued. This signal has an internal pull-up resistor. The output is synchronized with the CLK signal.                                                 |

| HCS/     | 35   | I    | Host Chip Select – Active-low. This signal is generated by external address decoding to allow the SIOP's registers to be memory or I/O mapped.                                                                                                                                                                  |

| CLK      | 36   | I    | Square Wave Clock – provides the fundamental timing for the system bus and for the SIOP chip. It should be the same signal as the CLK2 input of the 80386. The CLK signal input frequency should range from 16.67 MHz to 50 MHz for the 53C700 and up to 66 MHz for the 53C700-66 with a 40% to 60% duty cycle. |

| MASTER/* | 93*  | O    | Master Status – 8 mA, tristate, output. Driven low when the 53C700-66 becomes bus master. This feature is enabled by bit 6 of CTEST8.                                                                                                                                                                           |

| FETCH/*  | 94*  | O    | Fetch Opcode – 8 mA, tristate, output. Indicates that the next bus request will be for an opcode fetch. This feature is enabled by bit 6 of CTEST8.                                                                                                                                                             |

| SCLK*    | 95*  | I    | SCSI Clock – SCLK may be used to derive all SCSI related timings. Normal operation is to derive all SCSI timings from CLK (pin 36). The speed of this clock will be determined by the application's requirements. This feature is enabled by bit 7 of CTEST8.                                                   |

<sup>\*</sup> Pins 93, 94, and 95 are 53C700-66 features. Any pin(s) not used or in the 53C700, connect them to a 10 K pull up resistor.

Table 3-2. SCSI Interface Signals

| Symbol            | Pin#                         | Туре | Description                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD(7-0)/,<br>SDP/ | 122, 124-127<br>129-131, 121 | I/O  | SCSI Data/ and SCSI Data Parity/ - 48 mA, open drain, active-low.                                                                                                                                                                                                                                                                                                      |

| SDIR(7-0)         | 133-135, 137-138<br>140-142  | 0    | SCSI Data Direction – Active-high. In differential mode, these signals control the direction of external differential pair transceivers for the SD(7-0)/ signals. When this signal is high, the direction is from the SIOP to the SCSI bus. When it is low, the direction is from the SCSI bus to the SIOP. These signals are always valid, even in single-ended mode. |

| SDIRP             | 132                          | O    | SCSI Parity Direction – Active-high. In differential mode this signal controls the direction of an external differential pair transceiver for the SDP/ signal. When the signal is high signals move from the SIOP to the SCSI bus. When it is low, signals move from the SCSI bus to the SIOP. The signal is always valid, even in single-ended mode.                  |

| ATN/              | 120                          | I/O  | SCSI Attention – 48 mA, open drain. The initiator asserts this signal to indicate to the target that a message out phase is desired. The signal can be directly connected to the single-ended SCSI ATN line. In differential mode, the IGS output controls the direction of this signal.                                                                               |

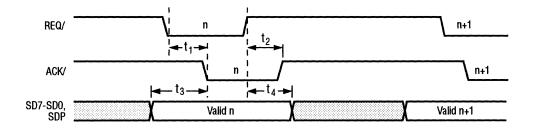

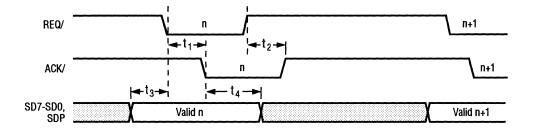

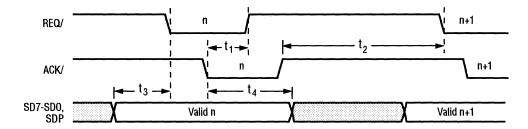

| REQ/              | 111                          | I/O  | SCSI Data Transfer Request – 48 mA, open drain, active-low. This signal is asserted by the target requesting a data transfer. When this signal is active, the MSG/, C/D, and I/O phase lines are valid. This signal can be directly connected to the single-ended SCSI REQ line. In differential mode, the TGS output controls the direction of this signal.           |

| ACK/              | 117                          | I/O  | SCSI Acknowledge – 48 mA open drain, active-low. This signal is asserted by the initiator in response to the REQ/ signal to acknowledge a data transfer. It can be directly connected to the single-ended SCSI ACK line. In differential mode, the IGS output controls the direction of this signal.                                                                   |

Table 3-2. SCSI Interface Signals (Continued)

| Symbol | Pin# | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSG/   | 115  | I/O  | SCSI Message Phase Signal – 48 mA, open drain. The target asserts this signal with the I/O and C/D signals to determine the information transfer phase. This signal can be directly connected to the single-ended SCSI MSG line. In differential mode, the TGS output controls the direction of this signal.                                                                                                         |

| I/O    | 110  | I/O  | SCSI Input-Output Phase – 48 mA, open drain. This signal is asserted with the MSG/ and C/D signals by the target to determine the information transfer phase. Input (asserted) and output (deasserted) transfers are always made with respect to the initiator. This signal can be directly connected to the single-ended SCSI I/O line. In differential mode, the TGS output controls the direction of this signal. |

| C/D    | 112  | I/O  | SCSI Control-Data Phase – 48 mA, open drain. This signal is asserted with the MSG/ and I/O signals by the target to determine the information transfer phase. This signal can be directly connected to the single-ended SCSI C/D line. In differential mode, the TGS output controls the direction of this signal.                                                                                                   |

Table 3-3. SCSI Phases

| MSG/ | C/D | 1/0 | SCSI Phase                   |

|------|-----|-----|------------------------------|

| 0    | 0   | 0   | Data-Out                     |

| 0    | 0   | 1   | Data-In                      |

| 0    | 1   | 0   | Command                      |

| 0    | 1   | 1   | Status                       |

| 1    | 0   | 0   | Reserved for future standard |

| 1    | 0   | 1   | Reserved for future standard |

| 1    | 1   | 0   | Message-Out                  |

| 1    | 1   | 1   | Message-In                   |

Key: "0" not asserted, "1" asserted

Table 3-2. SCSI Interface Signals (Continued)

| Symbol | Pin# | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSY/   | 119  | I/O  | SCSI Busy – 48 mA open drain, active-low. This signal is asserted when the SCSI bus is busy. When a device wants to arbitrate to use the SCSI bus, it is driven active. Once the arbitration and selection phases are complete, the target drives this signal active. This signal can be connected directly to the single-ended SCSY BSY/ line. In differential mode, this signal is an input only and the BSYDIR signal asserts BSY/ on the SCSI bus. |

| RST/   | 116  | I/O  | SCSI Reset – 48 mA open drain, active-low. This signal is asserted to perform a SCSI bus reset. It can be directly connected to the single-ended SCSI RST line. In differential mode, it is an input only and the RSTDIR signal is used to assert RST/ on the SCSI bus. When the reset SCSI bus bit in the SCNTL1 register is set to 1, the RST/ signal is asserted and remains asserted until this bit is reset to 0.                                 |

| SEL    | 114  | I/O  | SCSI Select – 48 mA open drain, active-low. This signal is asserted to select or reselect another SCSI device. This signal can be directly connected to the single-ended SEL line. In differential mode, it is an input only and the SELDIR signal asserts SEL/ on the SCSI bus.                                                                                                                                                                       |

| BSYDIR | 108  | O    | SCSI Busy/Direction – This signal controls the assertion of the SCSI BSY/ signal in differential mode. Connect it to the driver enable of the differential pair transceiver. When this signal is high, BSY/ is asserted on the SCSI bus. When it is low, the differential pair drive is disabled. The SCSI termination resistors will deassert BSY/ by pulling it high. This signal is always valid even in single-ended mode.                         |

| RSTDIR | 107  | O    | SCSI Reset/Direction – This signal controls the assertion of the SCSI RST/ signal in differential mode. Connect it to the drive enable of the differential pair transceiver. When this signal is high, RST/ is asserted on the SCSI bus. When it is low, the differential pair driver is disabled. The SCSI termination resistors will then deassert RST/ by pulling RST/ high. This signal is always valid, even in single-ended mode.                |

Table 3-2. SCSI Interface Signals (Continued)

| Symbol | Pin# | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

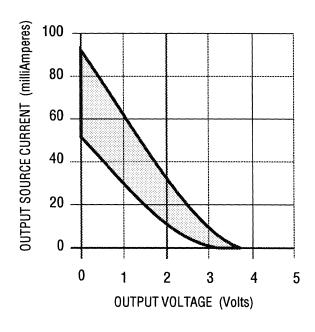

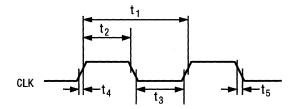

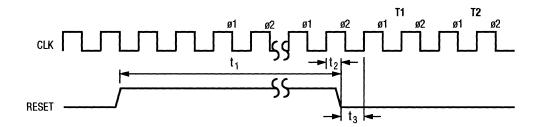

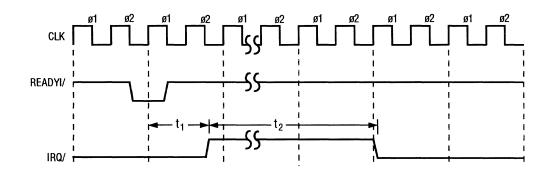

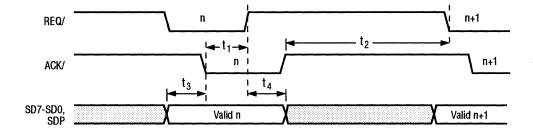

|--------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|