## **Functional Description and** Specifications of the PCM16C02 PC Card **Interface Device in Rev 3 DMA Mode**

- DMA INTERFACE PIN DESCRIPTION AND BLOCK DIAGRAM

- ATTRIBUTE MEMORY MAP

- HOST-SIDE DMA REGISTER (0x3FA)

- FUNCTION CONFIGURATION OPTION REGISTER 1 (0x1040)

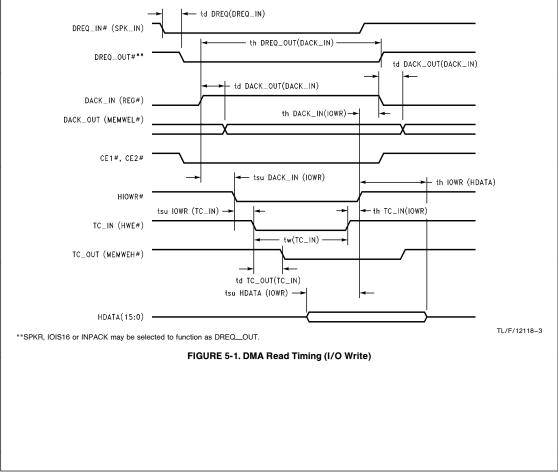

- DMA READ TIMING DIAGRAM AND SPECIFICATIONS

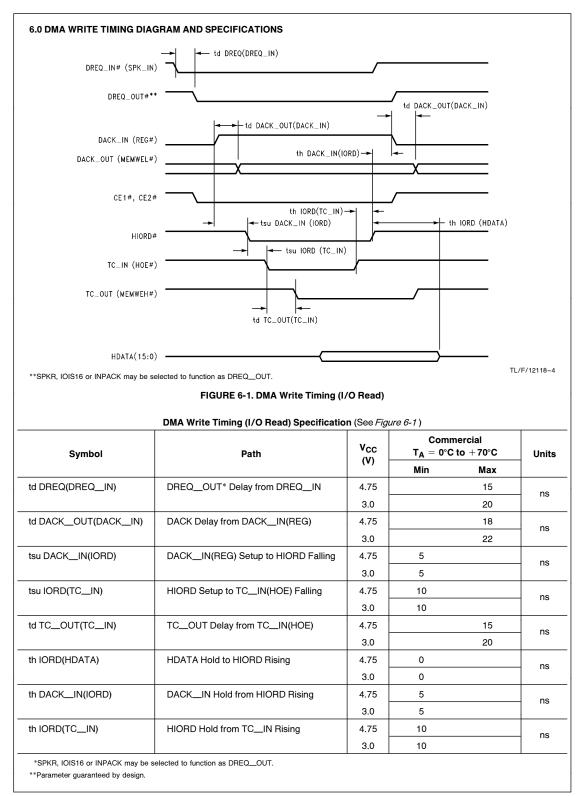

- DMA WRITE TIMING DIAGRAM AND SPECIFICATIONS

- OVERVIEW

This note provides the functional description and details of register settings necessary to configure Function 1 of the PCM16C02 to support the DMA extension to the PC Card Standard, February 1995 (i.e, Rev 3 DMA Mode). Also, National Semiconductor Application Note 998 Raymond Beahm August 1995

included in this note are performance specifications necessary for DMA designs. Note, the implementation of a specific PC Card design using DMA is outside of the scope of this note.

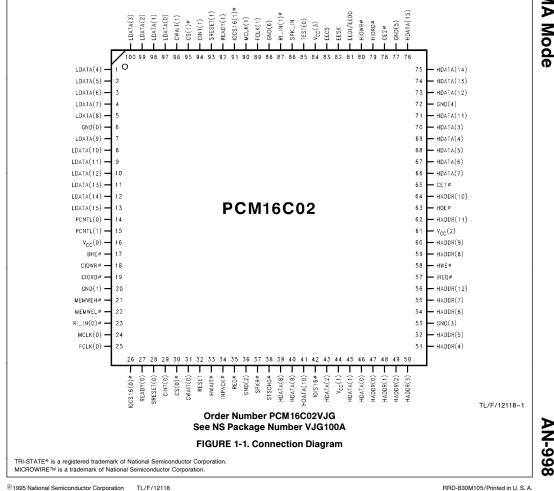

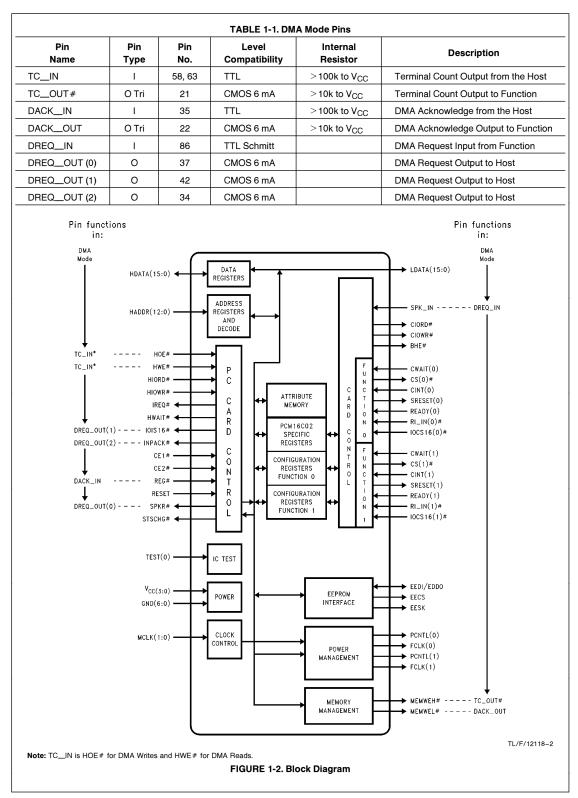

#### **1.0 DMA INTERFACE PIN DESCRIPTION**

During DMA Mode, nine device pins for Function 1 are configured to support the PC Card Standard DMA interface. Two of the nine device pins support the TC\_IN pin of the PC Card Standard DMA interface. The HOE# pin is configured as TC\_IN during DMA Writes, and the HWE# pin is configured as TC\_IN during DMA Reads.

Refer to the Connection Diagram in Figure 1-1 and the Block Diagram in Figure 1-2 while reviewing the DMA Mode Pins described in Table 1-1.

RRD-B30M105/Printed in U. S. A

|                                          | BLE 2-1. Attribute Memory Ma | ٢             | 1        |

|------------------------------------------|------------------------------|---------------|----------|

| Register Description                     | Register Type                | Address (Hex) | EEPRON   |

| Card Information Structure               | PC Card CIS                  | 0x000-0x03E2  | Yes      |

| Pin Polarity Register                    | PCM16C02 Specific            | 0x03E4        | Yes      |

| PMGR and Clock Register                  | PCM16C02 Specific            | 0x03E6        | Yes      |

| CTERM0 Register                          | PCM16C02 Specific            | 0x03E8        | Yes      |

| CTERM1 Register                          | PCM16C02 Specific            | 0x03EA        | Yes      |

| Reserved for Future Use Registers        | PCM16C02 Specific            | 0x03EC-0x03EE | Yes      |

| Miscellaneous Register                   | PCM16C02 Specific            | 0x03F0        | Yes      |

| Reserved for Future Use Registers        | PCM16C02 Specific            | 0x03F2-0x03F4 | Yes      |

| Wait State Timer Registers               | PCM16C02 Specific            | 0x03F6        | Yes      |

| NAND Flash (NM29N16) Config Register     | PCM16C02 Specific            | 0x03F8        | Yes      |

| Host-Side DMA Register                   | PCM16C02 Specific            | 0x03FA        | Yes      |

| Watchdog Timer Register                  | PCM16C02 Specific            | 0x03FC        | Yes      |

| Reserved for Future Use Registers        | PCM16C02 Specific            | 0x03FE        | Yes      |

| Card Information Structure               | PC Card CIS                  | 0x0400-0x07FE | Optional |

| ID Register                              | PCM16C02 Specific            | 0x1000        | No       |

| EEPROM Control Register                  | PCM16C02 Specific            | 0x1002        | No       |

| EEPROM Security Register                 | PCM16C02 Specific            | 0x1004        | No       |

| Reserved for Future Use Registers        | PCM16C02 Specific            | 0x1006-0x101E | No       |

| Function 0 Configuration Option Register | PC Card                      | 0x1020        | No       |

| Function 0 Configuration Status Register | PC Card                      | 0x1022        | No       |

| Function 0 Pin Replacement Register      | PC Card                      | 0x1024        | No       |

| Unused                                   | PC Card                      | 0x1026        | No       |

| Function 0 I/O Event Register            | PC Card                      | 0x1028        | No       |

| Function 0 Base A Register               | PC Card Extension            | 0x102A        | No       |

| Function 0 Base B Register               | PC Card Extension            | 0x102C        | No       |

| Unused                                   | PC Card Extension            | 0x102E-0x1030 | No       |

| Function 0 Limit Register                | PC Card Extension            | 0x1032        | No       |

| Reserved for Future Use Registers        | PC Card Extension            | 0x1034-0x103E | No       |

| Function 1 Configuration Option Register | PC Card                      | 0x1040        | No       |

| Function 1 Configuration Status Register | PC Card                      | 0x1042        | No       |

| Function 1 Pin Replacement Register      | PC Card                      | 0x1044        | No       |

| Unused                                   | PC Card                      | 0x1046        | No       |

| Function 1 I/O Event Register            | PC Card                      | 0x1048        | No       |

### 3.0 HOST-SIDE DMA REGISTER (0x3FA)

If enabled for DMA mode, the PCM16C02 will properly meet all of the PC Card Standard requirements for DMA operation including the generation of DACK and TC signals to the card function, and the passing of DREQ from the function to the host.

| D7-D6 | D5          | D4          | D3      | D2        | D1        | D0  |

|-------|-------------|-------------|---------|-----------|-----------|-----|

| RFU   | Dreq_sel(1) | Dreq_sel(0) | TC_ppol | Dack_ppol | Dreq_ppol | RFU |

Dreq\_sel—Selects which host-side output will become Dreq\_out when configured for DMA mode.

| lf: | Dreq_sel(1) | Dreq_sel(0) | Dreq_out is: |

|-----|-------------|-------------|--------------|

|     | 0           | 0           | Spkr         |

|     | 0           | 1           | IOIS16       |

|     | 1           | 0           | Inpack       |

|     | 1           | 1           | Reserved     |

**TC\_ppol**—Sets the polarity for the TC output in DMA mode. If set to zero (0), TC will go low when HOE# or HWE# are asserted (low) with REG# de-asserted (high). If set to one (1), TC will go high when HOE# or HWE# are asserted (low) with REG# de-asserted (high). Default value for TC\_ppol is zero.

5.0 DMA READ TIMING DIAGRAM AND SPECIFICATIONS

**Dack\_ppol**—Sets the polarity for the DACK output in DMA mode. If set to zero (0), DACK will go low when HIORD# or HIOWR# are asserted (low) with REG# de-asserted (high). If set to one (1), DACK will go high when HIORD# or HIOWR# are asserted (low) with REG# de-asserted (high). Default value for Dack\_ppol is zero.

**Dreq\_ppol**—sets the polarity for the DREQ\_OUT output in DMA mode. If set to zero (0), DREQ\_OUT will go low when DREQ\_IN is taken (low). If set to one (1), DREQ\_ OUT will go high when DREQ\_IN is taken (low). Default value for Dreq\_ppol is zero.

# 4.0 FUNCTION CONFIGURATION OPTION REGISTER 1 (0x1040)

| D7    | D6      | D5-D0                        |

|-------|---------|------------------------------|

| SREST | LevIREQ | Function Configuration Index |

DMA\_EN(D4) (For Function 1 ONLY)—If set to a one (1), function 1 is configured for DMA mode. If set to zero (0), function 1 is configured for normal I/O mode (default state).

Thus Function 1 can be configured as either a standard I/O or DMA interface, however Function 0 cannot be configured as a DMA interface. Note, Function 0 can be configured as either a standard I/O or NAND Flash (NM29N16) interface.

4

| Symbol               | Path                                | V <sub>CC</sub><br>(V) | Commercial<br>T <sub>A</sub> = 0°C to +70°C |     | Units |

|----------------------|-------------------------------------|------------------------|---------------------------------------------|-----|-------|

|                      |                                     |                        | Min                                         | Max |       |

| td DREQ(DREQ_IN)     | DREQ_OUT* Delay from DREQ_IN        | 4.75                   |                                             | 15  | ns    |

|                      |                                     | 3.0                    |                                             | 20  | 113   |

| td DACK_OUT(DACK_IN) | DACK_OUT Delay from DACK_IN(REG)    | 4.75                   |                                             | 18  | ns    |

|                      |                                     | 3.0                    |                                             | 22  | 110   |

| tsu DACK_IN(IOWR)    | DACK_IN(REG) Setup to HIOWR Falling | 4.75                   | 5                                           |     | ns    |

|                      |                                     | 3.0                    | 5                                           |     | 113   |

| tsu IOWR(TC_IN)      | HIOWR Setup to TC_IN(HWE) Falling   | 4.75                   | 10                                          |     | ns    |

|                      |                                     | 3.0                    | 10                                          |     | 113   |

| td TC_OUT(TC_IN)     | TC_OUT Delay from TC_IN(HWE)        | 4.75                   |                                             | 15  | ns    |

|                      |                                     | 3.0                    |                                             | 20  | 110   |

| tsu HDATA(IOWR)      | HDATA Setup to HIOWR Rising         | 4.75                   | 100                                         |     | ns    |

|                      |                                     | 3.0                    | 100                                         |     | 110   |

| th IOWR(HDATA)       | HDATA Hold from HIOWR Rising        | 4.75                   | 30                                          |     | ns    |

|                      |                                     | 3.0                    | 30                                          |     | 113   |

| th TC_IN(IOWR)       | HIOWR Hold from TC_IN Rising        | 4.75                   | 10                                          |     | ns    |

|                      |                                     | 3.0                    | 10                                          |     | 110   |

| tw (TC_IN)           | TC_IN Pulse Width                   | 4.75                   | 40                                          |     | ns    |

|                      |                                     | 3.0                    | 40                                          |     |       |

| th DREQ_OUT(DACK_IN) | DREQ_OUT Hold from DACK_IN Rising   | 4.75                   | 0                                           |     | ns    |

|                      |                                     | 3.0                    | 0                                           |     | 10    |

| th DACK_IN(IOWR)     | DACK_IN Hold from HIOWR Rising      | 4.75                   | 5                                           |     | ns    |

|                      |                                     | 3.0                    | 5                                           |     |       |

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| National Semiconductor<br>Corporation<br>Arlington, TX 76017<br>Tel: 1(800) 272-9959<br>Fax: 1(800) 737-7018 National Semiconductor<br>Europe   National Semiconductor<br>Europe Fax: (+49) 0-180-530 85 86<br>Email: cniwge@itewm2.nsc.com   Deutsch Tel: (+49) 0-180-532 78 82<br>Français Tel: (+49) 0-180-532 78 82<br>Français Tel: (+49) 0-180-532 78 56<br>Italiano Tel: (+49) 0-180-532 78 56 | National Semiconductor<br>Hong Kong Ltd.<br>13th Floor, Straight Block,<br>Ocean Centre, 5 Canton Rd.<br>Tsimshatsui, Kowloon<br>Hong Kong<br>Tel: (852) 2736-9960<br>Fax: (852) 2736-9960 | National Semiconductor<br>Japan Ltd.<br>Tel: 81-043-299-2309<br>Fax: 81-043-299-2408 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.