# **ANSI FDDI TP-PMD and** 802.3 100BASE-TX Signaling with the **DP83223A TWISTER**

National Semiconductor Application Note 965 **Todd Vafiades** September 1994

## **1.0 INTRODUCTION**

The American National Standards Institution has ratified a specification for 125 Mbps signaling over 100  $\Omega$  Category-5 Unshielded Twisted Pair cable or  $150\Omega$  Type-1 Shielded Twisted Pair cable. This specification was generated to support the FDDI Twisted Pair PMD option to enable FDDI signaling over lengths of up to 100 Meters of Twisted Pair cabling. The intent was to assist in the expedient deployment of FDDI by enabling connection to the desktop via existing office cabling.

The advent of Fast Ethernet also called for a Twisted Pair PMD alternative which could support 125 Mbps operation over Category-5 UTP or Type-1 STP cabling. The IEEE 802.3 committee adopted the specification known as 100BASE-TX which, like FDDI TP-PMD, is also based on single pair transmission and reception of the 125 Mbps bit stream. Due to the physical and electrical commonalities between the 100BASE-TX and FDDI TP-PMD implementations, the 100BASE-TX specification was modeled after the FDDI TP-PMD standard. This resulted in nearly identical specifications for both protocols.

The differences between the two specifications are basically limited to the various unshielded and shielded connector pin assignments. All remaining aspects of the two specifications are identical.

The National Semiconductor DP83223A TWISTER transceiver is designed to be compliant with both the ANSI FDDI TP-PMD and IEEE 802.3 100BASE-TX twisted pair specifications. This application note will assist in the understanding and use of the DP83223A transceiver device for both the FDDI TP-PMD and 100BASE-TX protocols.

© 1995 National Semiconductor Corporation TL/F/12306 RRD-B30M75/Printed in U. S. A

## 2.0 OVERVIEW

The subjects covered in this application note include a comparison between FDDI TP-PMD and 100BASE-TX specifications, connection diagram, PMD schematics and circuit details, layout considerations, and magnetics. Additionally, appendices covering a bill of materials for a typical UTP design and common mode termination references are included.

The basic signaling method and media types are outlined as follows. The transmitting and receiving nodes must effectively couple the serial bit stream to and from the twisted pair media. This transmission must be compliant with the AOI (Active Output Interface), the AII (Active Input Interface) as well as the twisted pair Channel Characteristics as defined in both the FDDI TP-PMD and 100BASE-TX specifications. More specifically, the specifications define the differential signal encoding, signal decoding and media types as:

- ENCODE = 2V pk-pk differential MLT-3

- DECODE = Receive end Equalization

- MEDIA = Up to 100M of  $100\Omega$  Category 5 Unshielded Twisted pair or  $150\Omega$  Shielded Twisted Pair

Note: Media types should conform to the EIA/TIA 574 for STP and EIA/TIA 568, TSB-36 for UTP specifications

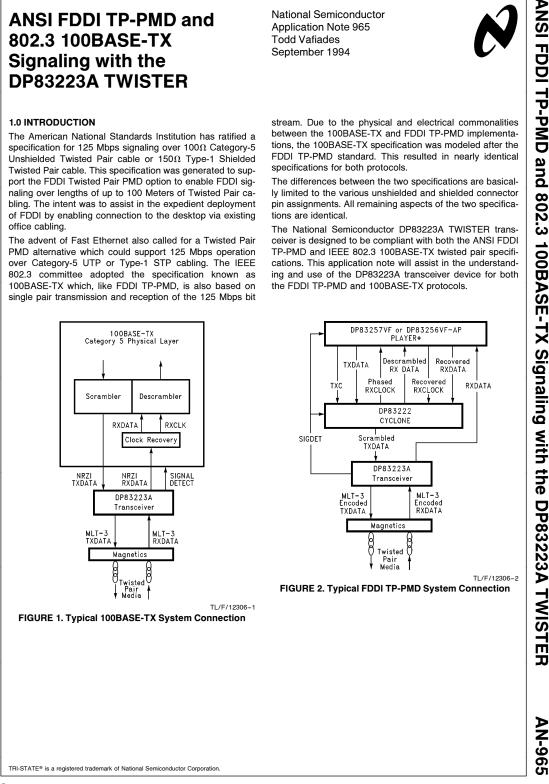

The DP83223A TWISTER allows for a simple, cost-effective design while requiring minimal board space. The system connection diagrams in *Figures 1* and *2* illustrate the general placement and interconnection of the PMD relative to the Physical Layer and twisted pair cabling.

# 3.0 FDDI TP-PMD VS. 100BASE-TX

This section highlights the implementation differences between FDDI TP-PMD and 100BASE-TX. The single outstanding difference lies in the media connector pin assignment.

#### 3.1 Unshielded Media Connector Pin Assignments

The pin assignment for the FDDI TP-PMD unshielded twisted pair RJ45-8 jack connector is given as:

| FDDI TP-PMD   | Pin                 |  |

|---------------|---------------------|--|

| Transmit pair | 1 (TX+) and 2 (TX-) |  |

| Unused pair   | 3 and 6             |  |

| Unused pair   | 4 and 5             |  |

| Receive pair  | 7 (RX+) and 8 (RX–) |  |

The pin assignment for the 100BASE-TX unshielded twisted pair RJ45-8 jack connector is given as:

| 100BASE-TX    | Pin                 |

|---------------|---------------------|

| Transmit pair | 1 (TX+) and 2 (TX-) |

| Receive pair  | 3 (RX+) and 6 (RX-) |

| Unused pair   | 4 and 5             |

| Unused pair   | 7 and 8             |

## 3.2 Shielded Media Connector Pin Assignments

The pin assignment for the FDDI TP-PMD and 100BASE-TX are identical. The shielded twisted pair DB-9 receptacle connector is given as:

| FDDI TP-PMD & 100BASE -TX | Pin                 |  |

|---------------------------|---------------------|--|

| Transmit pair             | 5 (TX+) and 9 (TX-) |  |

| Receive pair              | 1 (RX+) and 6 (RX-) |  |

| Unused pins               | 2,3,4,7,8           |  |

| Ground to chassis         | Shield              |  |

## 4.0 PMD SCHEMATIC EXAMPLE

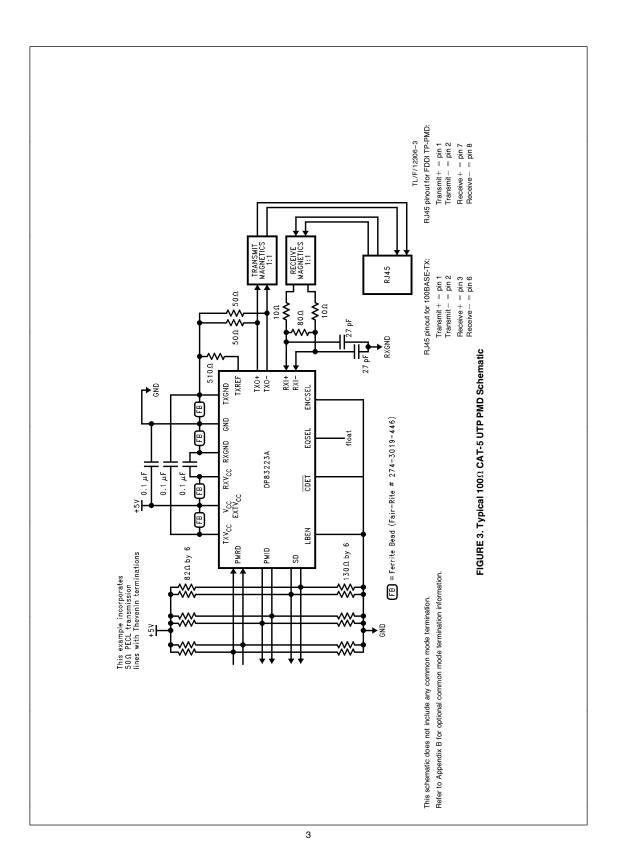

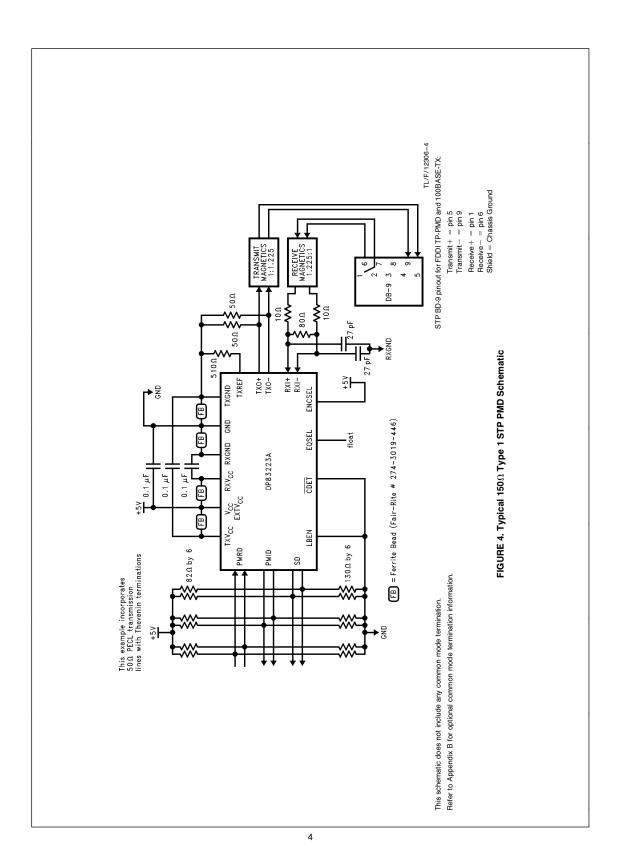

The schematic examples given in *Figures 3* and 4 provide detailed 100 $\Omega$  UTP and 150 $\Omega$  STP designs respectively which may be integrated directly onto a motherboard. With only minor modifications, these designs may be used to create an ORM (Optical Replacement Module). Refer to section 4.1.1.2 for further information concerning ORM applications.

# 4.1 Circuit Details

The schematics given in *Figures 3* and 4 contain several common functional parameters. The important differences between an STP and UTP implementation are also described. The following subsections attempt to clarify the designs, providing a more thorough understanding.

## 4.1.1 PECL Terminations

All PECL (Pseudo ECL) signals interfacing the Physical Layer with the PMD require appropriate terminations. These signals include PMRD $\pm$ , PMID $\pm$  and SD $\pm$ . There are important options to be considered when choosing the best termination scheme for a given implementation. There are also additional design guidelines available for reference which can be found in the F100K ECL Logic Databook and Design Guide published by National Semiconductor.

#### 4.1.1.1 Cost vs. Power

Several factors must be considered when choosing a PECL termination scheme for a given implementation.

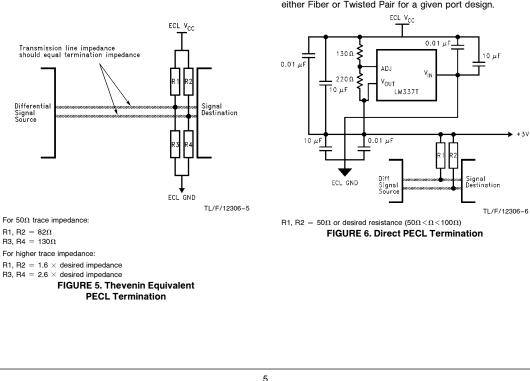

To reduce complexity and minimize costs, a Thevenin equivalent PECL termination approach which requires only two resistors per PECL signal should be considered. For a  $50\Omega$  transmission line impedance, the Thevenin equivalent consists of an  $82\Omega$  resistor from the signal to the +5V ECL supply and a  $130\Omega$  resistor from the signal to the ECL Ground return. This equivalent termination should be placed as close to the end of the transmission line(s) as possible (refer to *Figure 5*). The choice of the Thevenin equivalent termination is best suited for single-port design such as an end-station adapter card where quite often, only the three differential pairs listed in 4.1.1 require high speed PECL termination.

Note that each differential pair of Thevenin terminations draws approximately 30 mA of additional current from the +5V supply. For an 8-port hub consisting typically of up to 24 PECL interfaces, as much as 3.6W of additional power is required just to support the Thevenin termination scheme.

For a multi-port implementation such as a hub or switch configuration, power requirements may mandate a lower power termination technique. In this case, a dedicated rail supporting direct 50 termination is a good alternative to the Thevenin equivalent as it requires approximately half the power. *Figure 6* illustrates the use of the National Semiconductor LM337T Adjustable Voltage Regulator which provides a +3V supply (V<sub>CC</sub> minus 2V) for +5V PECL termination.

For further power conservation, the designer may optionally choose a microstrip transmission line with a higher characteristic impedance. Since all PECL interfaces to the DP83223A TWISTER are differential, the small change in output logic levels caused by a shift in termination current is minimal. More than sufficient differential logic margins will be maintained for termination impedances up to  $100\Omega$ . In addition, the higher characteristic impedance and higher termination resistance will result in slightly longer risetimes which the designer must keep in mind when choosing transmission line distances and component placement. In brief, the shorter the transmission line and the more controlled its characteristic impedance, the better the signal transfer. The choice of higher transmission line impedances and terminations is viable for either Thevenin or Direct termination techniques.

### 4.1.1.2 ORM vs. Direct Integration

The implementation of choice may be an ORM (Optical Replacement Module) instead of direct integration. The most obvious benefit of an ORM is the inherent flexibility in use of either Fiber or Twisted Pair for a given port design.

The selection of an ORM requires that the implementor understand two important factors in their design and use. Since an ORM is intended as a direct replacement for an Optical Data Link module, it is necessary to place the ECL termination on the Motherboard and not on the ORM to guarantee compatibility. It is also important for the implementor to be aware that the SD- (Signal Detect compliment) signal has been omitted from some 9-pin LCF implementations. The cost vs. power factors discussed in section 4.1.1.1 are valid for ORM implementations as well as direct integration.

## 4.1.2 Twisted Pair Forward Termination

Given a differential transmit amplitude of 2V pk-pk, a standard 1:1 isolation transformer at the receive input provides for optimized adaptive equalization performance for CAT-5 implementations. For compliancy to the STP specification and to maintain matched impedance to the 150 $\Omega$  characteristic impedance, 1:1.225 turns ratio is required for the transmit magnetics and the reverse, 1.225:1, is required for the receive magnetics. Using these step-up and step-down transformers for 150 $\Omega$  applications allows the use of the same components and component values for termination and noise filtering that are employed for 100 $\Omega$  applications.

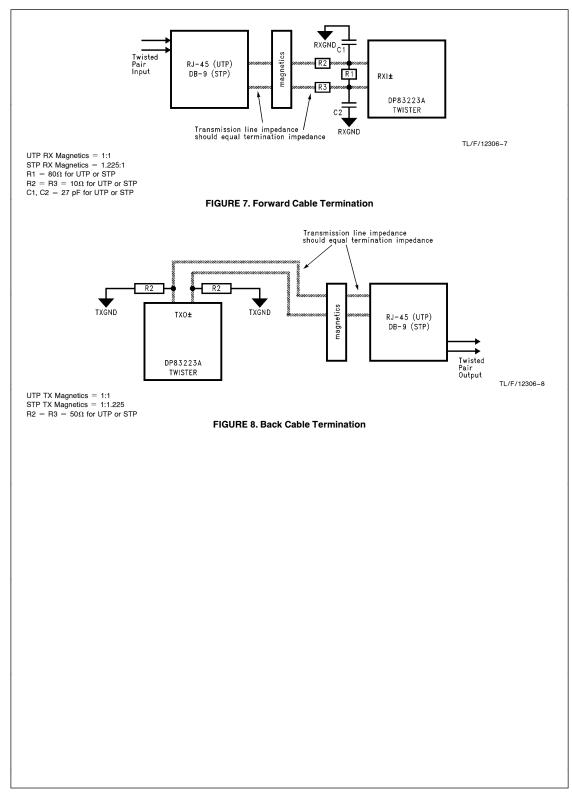

Figure 7 illustrates suggested placement and values for the forward cable termination. Important aspects of the forward termination are highlighted here.

The voltage divider formed by R1, R2 and R3 is an important implementation requirement. For MLT-3 operation, the DP83223A TWISTER transceiver's receive input reference is set to 1.5V. Because the transmit amplitude is specified at 2.0V, some signal attenuation is required. This attenuation is accomplished by two factors. First, insertion loss due to the receive magnetics is typically on the order of approximately 0.7 dB. This reduces the amplitude of the incoming signal by about 100 mV. Second, the remaining attenuation is accomplished by a simple resistive voltage divider placed at the RXI $\pm$  inputs. The receive signal, already reduced by the insertion loss of the receive magnetics, is further attenuated by 20% by R1, R2, and R3 before reaching the RXI $\pm$  inputs (*Figure 7*). Therefore, the combination of the insertion loss and receive attenuation circuit reduces the voltage to approximately 1.5V which ensures appropriate signal transfer and optimal adaptive equalization. Adjusting the ratio of the voltage divider can help to optimize the adaptive equalization by precisely compensating for the inherent insertion loss of a given choice of magnetics.

It is important that the serial combination of R1, R2 and R3 must equal  $100\Omega$  which is required for proper forward termination of the transmission line.

Because the voltage divider attenuates any noise along with the received signal, the Signal-to-Noise ratio is not decreased. Additionally, by incorporating the two bandwidth limiting capacitors as shown in *Figure 7,* increased immunity to differential and common mode noise is achieved.

## 4.1.3 Twisted Pair Back Termination

*Figure 8* illustrates the suggested implementation for the twisted pair back termination required for a balanced system impedance. It is suggested that the TXGND (Transmit Ground) of the DP83223A TWISTER be used as the return for the back termination of either UTP or STP cable types.

## 4.1.4 Transmit Amplitude

The TXREF pin of the DP83223A TWISTER offers amplitude adjustment of the transmitted signal onto the media. Assuming the use of 1:1 transformers for UTP applications and 1:1.225 transformers for STP applications, the equation for selecting the appropriate resistor value (R<sub>REF</sub>) for a desired V<sub>OUT</sub> is given as:

$$\mathsf{R}_{\mathsf{REF}} = \frac{10.24 \times 100\Omega}{\mathsf{V}_{\mathsf{OUT}}}$$

where:

> R<sub>REF</sub> is the TX amplitude reference resistor in  $\Omega$

> Z\_{CABLE} is the effective characteristic differential impedance of the twisted pair cable in  $\Omega$

$> V_{OUT}$  is the differential peak-peak output voltage in V

> 5.12 is related to the reference scaling factor

Please refer to Figure 4 for proper connection of  $\mathsf{R}_{\mathsf{REF}}$  to the TXREF pin.

| Signal             | Pin No. | Description                              | Туре                     |  |

|--------------------|---------|------------------------------------------|--------------------------|--|

| V <sub>CC</sub>    | 13, 26  | V <sub>CC</sub>                          | Supply                   |  |

| GND                | 14, 22  | GND                                      | Supply                   |  |

| RXV <sub>CC</sub>  | 4, 27   | Receive V <sub>CC</sub>                  | Supply                   |  |

| RXGND              | 3, 28   | Receive GND                              | Supply                   |  |

| TXV <sub>CC</sub>  | 5, 11   | Transmit V <sub>CC</sub>                 | Supply                   |  |

| TXGND              | 7, 10   | Transmit GND                             | Supply                   |  |

| EXTV <sub>CC</sub> | 23      | External V <sub>CC</sub>                 | Supply                   |  |

| RXI±               | 2, 1    | Receive Data Inputs                      | Differential Voltage In  |  |

| PMID±              | 25, 24  | Physical Media Indicate Data             | ECL Out                  |  |

| $PMRD\pm$          | 15, 16  | Physical Media Request Data ECL In       |                          |  |

| TXO±               | 9, 8    | Transmit Data Outputs                    | Differential Current Out |  |

| SD±                | 20, 21  | Signal Detect Outputs                    | ECL Out                  |  |

| TXREF              | 6       | Transmit Amplitude Reference Current Out |                          |  |

| ENCSEL             | 12      | Encode Select Input                      | CMOS In                  |  |

| LBEN               | 19      | Loopback Enable CMOS In                  |                          |  |

| EQSEL              | 17      | Equalization Select 3-Level Select       |                          |  |

| OE                 | 18      | Output Enable Bar                        | CMOS Schmitt Trig In     |  |

## **6.0 FUNCTIONAL TRUTH TABLES**

The DP83223A TWISTER incorporates a high degree of functional flexibility. The following subsections provide the logical truth tables for various functional options.

## 6.1 Output Enable

| ŌE | тхо         | PMID+/-    |

|----|-------------|------------|

| 0  | Follow PMRD | Follow RXI |

| 1  | TRI-STATE®  | Static     |

## 6.2 Equalization Select

| EQSEL | Mode        |

|-------|-------------|

| <1.5V | Full EQ     |

| Float | Adaptive EQ |

| >3.0V | EQ Off      |

EQSEL should be allowed to float for 155 Mb/s ATM applications.

# 6.3 Encode Select

| ENCSEL | Mode   |

|--------|--------|

| 0      | MLT-3  |

| 1      | Binary |

ENCSEL should be tied to a CMOS logic high level for 155 Mb/s ATM applications.

#### 6.4 Loopback Select

| LBEN | Mode     |  |

|------|----------|--|

| 0    | Normal   |  |

| 1    | Loopback |  |

The Loopback Function is intended for board diagnostics. In Loopback mode, the ECL signal applied to the PMRD inputs will appear at the PMID outputs regardless of the signal present at the RXI inputs.

The LBEN pin should be tied to a CMOS logic level for normal 155 Mb/s ATM applications.

## 7.0 LAYOUT CONSIDERATIONS

Careful circuit layout is essential for meeting EMC/EMI requirements as well as ensuring robust overall performance. The following subsections examine power and ground issues, shielding suggestions and example PMD layouts.

It is important to note that the suggestions provided in this section will not, in and of themselves, guarantee compliance to specific EMC/EMI standards.

# 7.1 Power and Ground Layout

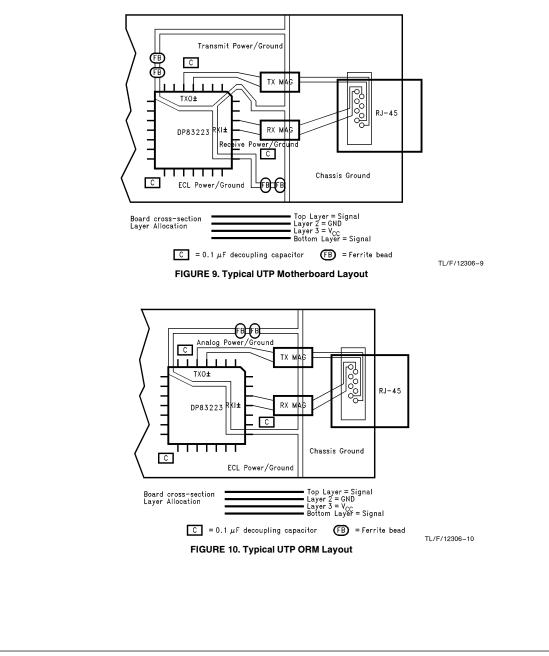

Many high frequency board designs take advantage of multiple layer topologies. Multiple board layers can be used to provide good impedance control of transmission line signal traces, increased noise margins to crosstalk and enhanced supply noise decoupling. While power and ground plane separation can be achieved on adjacent layers, additional separation can be achieved on a given single layer as well. These single layer plane separations are commonly referred to as islands. The use of islands can be beneficial in effectively separating two or more sensitive, unique power or ground planes within a given design. The example given in *Figure 9* illustrates a desirable separation of three different power and ground planes for use with the DP83223A TWISTER. Note that Ferrite beads are used to bridge the Islands allowing for very low loss DC interconnect while providing good attenuation for AC coupled noise at critical frequencies. This design is recommended only for implementations which provide sufficient board area for creating islands of significant size. Creating islands for very small layout areas such as the  $1" \times 1.5"$  9-pin LCF foot

print require an alternate design. When islands become too small they begin to loose their planar properties. *Figure 10* illustrates an alternative layout recommendation for very small area implementations such as the 9-pin ORM.

## 7.2 Shielding

Physical shielding can help to decrease radiated emissions. The use of shielded RJ45 (UTP) or DB-9 (STP) connectors is good practice. The shields of these connectors are commonly connected directly to chassis ground of the system.

# 8.0 MAGNETICS

Effective system performance requires transmit and receive transformers for coupling the differential signal to and from the twisted pair cabling. Due to the commonalities between the FDDI TP-PMD and 100BASE-TX specifications, the same magnetics will perform equally well for both technologies. National Semiconductor has worked with several magnetics companies to create designs and product for test and use with the DP83223A TWISTER. The following subsections examine the requirements for transmit and receive magnetics. The transmit and receive magnetics, as available from various vendors, may be physically separate components or a single module containing both components. The transformer center taps may optionally be used for common mode termination. Refer to Appendix B for further information.

## 8.1 Transmit Magnetics

The diagram in Figure 11 illustrates the basic design for the transmit magnetics suggested for use with the DP83223A TWISTER.

# 8.2 Receive Magnetics

The diagram in Figure 12 illustrates the basic design for the receive magnetics suggested for use with the DP83223A TWISTER.

> from transceive

from

8.3 Magnetics Manufacturers

Please contact your preferred magnetics vendor for the latest product information and part numbers. Bel Fuse, Inc. 5362 W. 78th St. Indianapolis, IN 46268-4147 (317) 876-0044 Coilcraft, Inc. 1102 Silver Lake Rd. Cary, Illinois 60013 (708) 639-6400 Filmag (a Technitrol Company) 9445 Farnham Street San Diego, CA 92123 (619) 569-6577 Nano Pulse Industries 440 Nibus St. Brea, CA 92622 (714) 529-2600 Pulse Engineering P.O. box 12235 San Diego, CA 92112 (619) 674-8100 Valor Electronics, Inc. 9715 Business Park Ave. San Diego, CA 92131 (619) 537-2619 or (619) 537-2631 signal direction 1:1 isolation transformer for UTP 1:1.225 isolation step-up transformer for STP edia minimum total OCL > 350  $\mu$ H TL/F/12306-11 **FIGURE 11. Transmit Magnetics** signal direction 1:1 isolation transformer for UTP 1.225:1 isolation step-down transformer for STP TL/F/12306-12 **FIGURE 12. Receive Magnetics**

# APPENDIX A

# **BILL OF MATERIALS**

The following B.O.M. contains all components necessary to complete the UTP motherboard design example given in section 4.0.

## ICs:

National Semiconductor DP83223A TWISTER (1)

## **PECL Termination Resistors:**

82Ω ¼wt 5% (6) 130Ω ¼wt 5% (6)

## Cable Termination and TXREF Resistors

## **Decoupling Capacitors:**

0.1 μF 16V 5% (3)

**Optional Bandwidth Limiting Capacitors** 27 pF 16V 1% (2)

Ferrites: Fair-Rite # 274-3019-446/7 (4)

## Magnetics:

Contact magnetics vendor of choice

#### Connectors:

Shielded PC-mount RJ45-8 (1)

## APPENDIX B

#### COMMON MODE TERMINATION

The effects of common mode termination have been shown, in some cases, to help increase margins to both EMI radiation and susceptibility. However, it should be noted that careful PMD circuit design and shielding practices will have a significant effect on EMC related performance.

Common mode termination has been the subject of much testing and discussion throughout various Network Standards meetings. An annex to the FDDI TWISTED PAIR PHYSICAL LAYER MEDIUM DEPENDENT (TP-PMD) ANSI Standard defines the use for and gives examples of common mode termination. To obtain a copy of the ANSI FDDI TP-PMD Standard, contact Global Engineering in Englewood, CO. Tel 1-800-854-7179

## REFERENCES

1. National Semiconductor DP83223A device specification. 2. FDDI TWISTED PAIR PHYSICAL LAYER MEDIUM DE-PENDENT (TP-PMD) Working Draft Proposed American National Standard Rev 2.1 dated 2/94

3. EIA/TIA 574, 568A, and TSB-36 specifications

4. IEEE 100BASE-TX specification

**AN-965**

# LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.  A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| Ø | National Semiconductor<br>Corporation<br>2900 Semiconductor Drive<br>P.O. Box 58000<br>Santa Clara, CA 95052-8090<br>Tei: 1(800) 272-9959<br>TWX: (910) 339-9240 | National Semiconductor<br>GmbH<br>Livry-Gargan-Str. 10<br>D-82256 Fixstenfeldbruck<br>Germany<br>Tel: (61-41) 35-0<br>Telex: 527649<br>Fax: (81-41) 35-1 | National Semiconductor<br>Japan Ltd.<br>Sumitomo Chemical<br>Engineering Center<br>Bldg. 7F<br>1-7-1, Nakase, Mihama-Ku<br>Chiba-City,<br>Ciba Prefecture 261<br>Tel: (043) 299-2300 | National Semiconductor<br>Hong Kong Ltd.<br>13th Floor, Straight Block,<br>Ocean Centre, 5 Canton Rd.<br>Tsimshatsui, Kowloon<br>Hong Kong<br>Tei: (852) 2737-1600<br>Fax: (852) 2736-9960 | National Semiconductores<br>Do Brazil Ltda.<br>Rue Deputado Lacorda Franco<br>120-3A<br>Sao Paulo-SP<br>Brazil 05418-000<br>Tel: (55-11) 212-5066<br>Telex: 391-1131931 NSBR BR<br>Fax: (55-11) 212-1181 | National Semiconductor<br>(Australia) Pty, Ltd.<br>Building 16<br>Business Park Drive<br>Monash Business Park<br>Nottinghill, Melbourne<br>Victoria 3168 Australia<br>Tel: (3) 558-9998<br>Fax: (3) 558-9998 |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                                                                  |                                                                                                                                                          | Fax: (043) 299-2500                                                                                                                                                                  |                                                                                                                                                                                            | 1 dx. (60 11) 212 1101                                                                                                                                                                                   | 1 44. (6) 666 6666                                                                                                                                                                                           |

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.