# PCI IDE Application Note

National Semiconductor Application Note 963 Lakhdar Iguelmamen Hans Wang September 1994

## **ERRATA**

## Description

The current BIOS (AMI, Award) will take Read/Write action towards the "Base Address Register" when it detects the PCI device through the "PCI configuration space" during power-on self-test. Different makers of BIOS will assign different values to the "Base Address Register". However, none of these values can be used as the default value of the legacy IDE HDD device. Which means that the "IDE port I/O space" resident on the chip has been redirected by the BIOS, and the system would not be able to communicate with the IDE device.

The outcome is "System could not boot through IDE HDD". National provides hardware and software solutions and both of them will not have any impact on system performance.

## **Software Solution**

- · BIOS needs to be changed

- · No changes to software drivers

- · No extra glue logic

Typically, BIOS use the "Sub-class code (01h) and program interface register (00h)" to detect whether the attached device is legacy IDE controller chip or not. Currently different BIOS venders remap IDE's Base Address Register to different address shown in the next table.

National Semiconductor is working with AMI, Award, and Phoenix to get BIOS modified to fix this anomaly.

Here are the required address changes for AMI and Award BIOS.

We suggest that the BIOS venders make the following changes once the Legacy-mode IDE is detected.

- a. Keep the "Base Address Register" untouched.

- Write the default address for channel 0 and channel 1 back to the "Base Address Register" once the "Legacy IDE" is detected.

#### Overview

The hardware patch solution is designed to fix the problem of existing demo boards' incompatibility with existing BIOS. This solution uses a GAL to fix the problem and works with existing BIOS without any power-on procedures. But it requires software changes to run on/off the hardware patch.

## **Hardware Patch Solution**

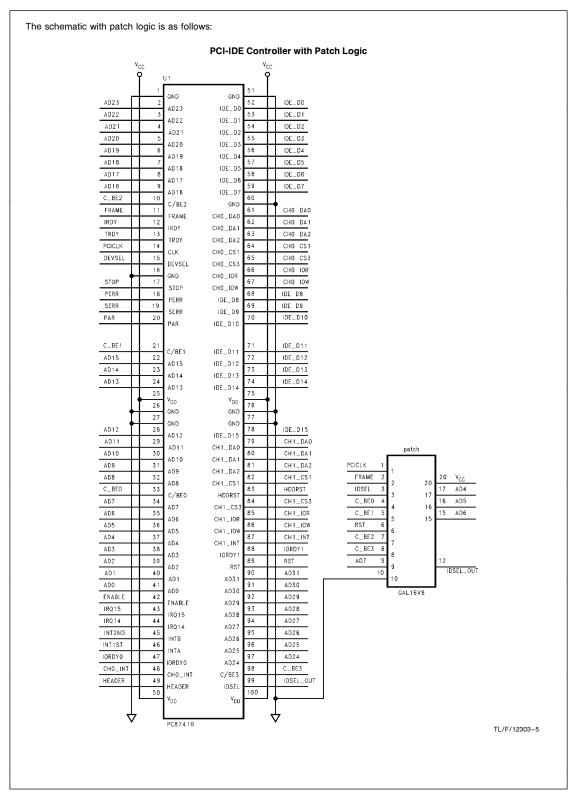

This document describes how to modify the existing demo board and what software drivers changes are required to turn on/off the software patch.

## **Hardware Patch**

- Requires a PAL

- No BIOS change required

- Wire the following signals to the GAL socket

| Pin #  | Connect                               |

|--------|---------------------------------------|

| 1      | PCI CLK                               |

| 2      | FRAME#                                |

| 3      | IDSEL (from the PCI local bus)        |

| 4      | CBE0#                                 |

| 5      | CBE1#                                 |

| 6      | RST#                                  |

| 7      | CBE2#                                 |

| 8      | CBE3#                                 |

| 9      | AD7                                   |

| 10     | GND                                   |

| 11, 20 | V <sub>CC</sub>                       |

| 12     | IDSEL_OUT (pin-99 or PC87410 "IDSEL") |

| 15     | AD6                                   |

| 16     | AD5                                   |

| 17     | AD4                                   |

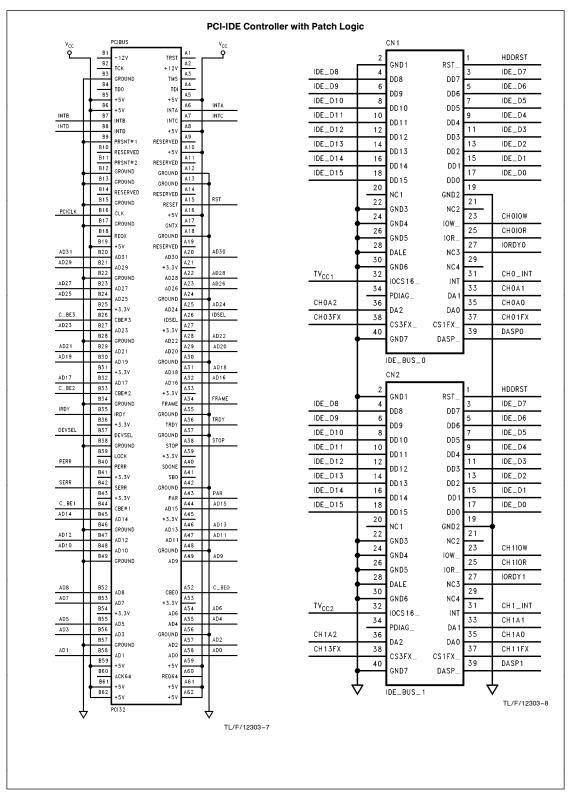

For more details, please refer to the schematic of PCI-IDE controller with patch logic.

| Address<br>Register  | Default<br>Value | AMI<br>BIOS | Award<br>BIOS (a) | Award<br>BIOS (b) |

|----------------------|------------------|-------------|-------------------|-------------------|

| Reg. 0<br>(10h-13h)  | 00 00 01 F1      | 00 00 FC F9 | 00 00 D0 01       | 00 00 50 01       |

| Reg. 1<br>(140h-17h) | 00 00 03 F5      | 00 00 FC F5 | 00 00 D1 01       | 00 00 51 01       |

| Reg. 2<br>(18h-1Bh)  | 00 00 01 71      | 00 00 FC F9 | 00 00 D2 01       | 00 00 52 01       |

| Reg. 3<br>(1Ch-1Fh)  | 00 00 01 75      | 00 00 FC F9 | 00 00 D2 01       | 00 00 53 01       |

Award: a.) version: 4.50 date code: 002194 Pentium-S b.) version: 4.50 date code: 122793 Pentium

## **PATCH LOGIC**

The following is the patch logic for PC87410 PCI-IDE controller with National's OPAL format. The PAL device could be either G16V8 or P16R4. See attached schematics with Patch Logic.

```

begin header

end header

begin definitions

device gal 16v8;

input clk=1, frame=2, idsel=3, cbe0=4, cbel=5, reset=6, cbe2=7, cbe3=8, ad7=9,

AD6=15, AD5=16, AD4=17;

output (com) idsel_out=12;

feedback st=13, st1=14;

end definitions

CLK FRAME IDSEL CBEO CBE1 RESET

ST ST1 IDSEL_OUT

Begin Equations

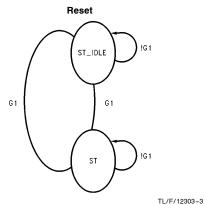

gl = !frame * idsel * cbe3 * !cbe2 * cbel * !cbe0 * ad7;

st := reset * ( st * !gl + !st * gl);

{st.re = reset;}

st.c = clk;

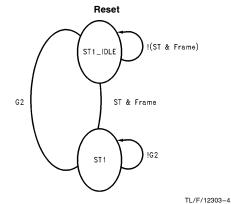

g2 = frame * !st;

stl := reset * ( stl * !g2 + !stl * st * frame);

{stl.re = reset;}

stl.c = clk;

idsel_out = idsel * (stl + ad7 + ad6 + ad5 + !ad4);

End Equations

```

## State Machine: Bubble Diagrams for PCI\_GAL.OPL

# **BILL OF MATERIAL**

## a. Active Devices

| Item | Quantity | Reference | Remarks and Part No        |

|------|----------|-----------|----------------------------|

| 1    | 1        | U1        | PC87410 PDI-IDE Controller |

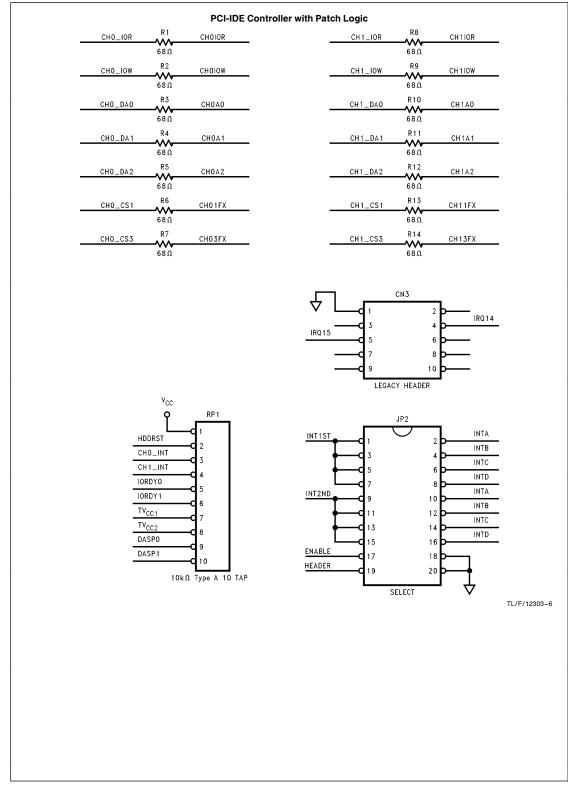

## b. Passive Devices

| Item | Quantity | Reference | Remarks and Part No         |

|------|----------|-----------|-----------------------------|

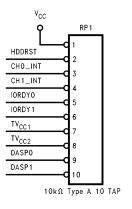

| 2    | 1        | R1        | 10 k $\Omega$ Type A 10 TAP |

|      |          |           | (resister pack)             |

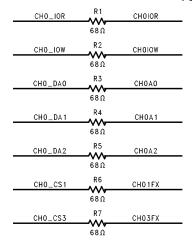

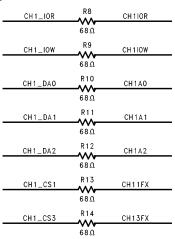

| 3    | 14       | R1 R14    | $68\Omega$                  |

| 4    | 2        | R15/R16   | $270\Omega$                 |

| 5    | 1        | R17       | $560\Omega$                 |

## c. Connector

| Item | Quantity | Reference | Remarks and Part No |        |

|------|----------|-----------|---------------------|--------|

| 6    | 1        | CN1       | IDE Channel 0       | 2 x 20 |

| 7    | 1        | CN2       | IDE Channel 1       | 2 x 20 |

| 8    | 1        | JP1       | To LED              | 2      |

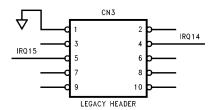

| 9    | 1        | CN3       | Legacy Header       | 2 x 5  |

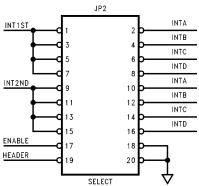

| 10   | 1        | JP2       | Selector for        |        |

|      |          |           | INTA and INTB       | 2 x 10 |

6

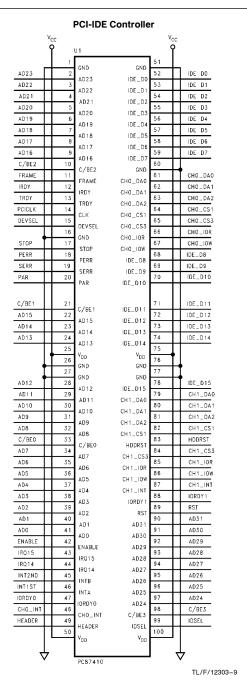

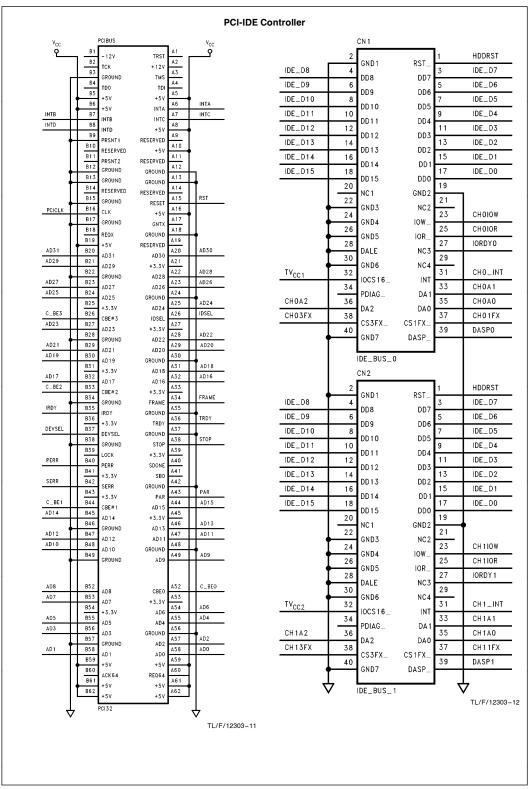

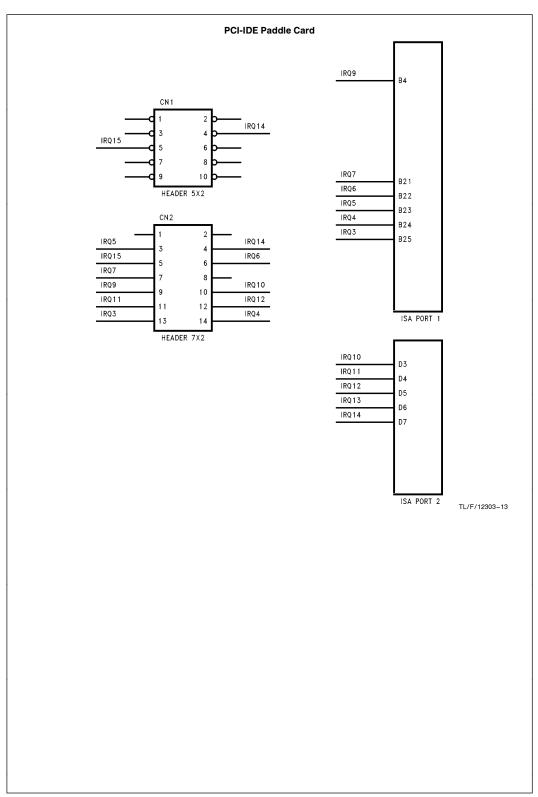

# SCHEMATICS

# **PCI-IDE Controller**

TL/F/12303-10

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**AN-963**

N C 25 P

National Semiconductor Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tei: 1(800) 272-9959 TWX: (910) 339-9240 National Semiconductor GmbH Livry-Gargan-Str. 10 D-82256 Fürstenfeldbruck Germany Tel: (81-41) 35-0 Telex: 527649 Fax: (81-41) 35-1 National Semiconductor Japan Ltd. Sumitomo Chemical Engineering Center Bldg. 7F 1-7-1, Nakase, Mihama-Ku Chiba-City, Ciba Prefecture 261 Tel: (043) 299-2500 Fax: (043) 299-2500

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductores Do Brazil Ltda. Rue Deputado Lacorda Franco 120-3A Sao Paulo-SP Brazil 05418-000 Teli: (55-11) 212-5066 Telex: 391-1131931 NSBR BR Fax: (55-11) 212-1181 National Semiconductor (Australia) Pty, Ltd. Building 16 Business Park Drive Monash Business Park Nottinghill, Melbourne Victoria 3168 Australia Tel: (3) 558-9999 Fax: (3) 558-9998