# The Operation of the FIFO in the DP8390, DP83901, DP83902 and DP83905

## **1.0 INTRODUCTION**

To accommodate the different rates at which data comes from (or goes to) the network and goes to (or comes from) the system memory, the NIC contains a 16-byte FIFO for buffering data between the bus and the media. The FIFO threshold is programmable, allowing filling (or emptying) the FIFO with different burst lengths. When the FIFO has filled to its programmed threshold, the local DMA channel transfers these bytes or words into local memory. It is crucial that the local DMA is given access to the bus within a minimum bus latency time, otherwise a FIFO underrun (or overrun) occurs. During transmission the DMA writes data into the FIFO and the Transmit Serializer reads data from the FIFO and transmist it. During reception the Receive Deserializer writes data into the FIFO and the DMA reads data from the FIFO.

### 2.0 FIFO THRESHOLD

The DMA transfers between the FIFO and memory occur in bursts beginning when the FIFO threshold is reached. The threshold takes on different meanings during transmission and reception. During reception the FIFO threshold refers to the number of bytes in the FIFO. During transmission the FIFO threshold refers to the number of empty bytes in the FIFO threshold refers to the number of empty bytes in the FIFO. The size of the FIFO (16) - # bytes in FIFO. Bits FTO and FT1 in the Data Configuration Register set the FIFO threshold to 2 bytes, 4 bytes, 8 bytes, or 12 bytes (1 word, 2 words, 4 words, or 6 words).

National Semiconductor Application Note 886 Bonnie Wilson Bill Lee June 1993

The threshold for the first burst is different than subsequent thresholds as discussed in detail in Sections 3.0 and 4.0. The values in Tables I and II are derived from the timing diagrams in Section 6.0. The first threshold refers to the state of the FIFO at point B in the timing diagrams, and the threshold refers to the state of the FIFO at point D. The discussion below refers to the threshold, not the first threshold.

The FIFO logic operates differently in reception and transmission. During reception in byte mode, a threshold is indicated when approximately the n + 14th bit has entered the FIFO; thus, with an 8-byte threshold, the NIC issues Bus Request (BREQ) when the FIFO contains 9 bytes and 6 bits. For reception in word mode, BREQ is generated when approximately n + 22 bits have entered the FIFO; thus with a 2-word threshold, BREQ is issued when the 54th bit has entered the FIFO. Refer to Table I for the exact receive thresholds for each case.

During transmission in byte mode, a threshold is indicated when approximately the n + 12th bit has entered the FIFO; thus with an 8-byte threshold, the NIC issues BREQ when the FIFO contains 9 bytes and 4 bits. For transmission in word mode, BREQ is generated when approximately n + 29 bits have entered the FIFO. Thus, with a 4-word threshold (equivalent to an 8-byte threshold), BREQ is issued when the 96th bit has entered the FIFO. Refer to Table II for the exact transmit thresholds for each case.

| TABLE I. Receive Packet Thresholds |                  |                  |  |  |  |  |  |

|------------------------------------|------------------|------------------|--|--|--|--|--|

| Receive Packet Cases               | First Threshold  | Threshold        |  |  |  |  |  |

| Word Mode, 1 Word Threshold        | 4 Words, 11 bits | 2 Words, 5 bits  |  |  |  |  |  |

| Word Mode, 2 Word Threshold        | 4 Words, 10 bits | 3 Words, 6 bits  |  |  |  |  |  |

| Word Mode, 4 Word Threshold        | 5 Words, 7 bits  | 5 Words, 5 bits  |  |  |  |  |  |

| Word Mode, 6 Word Threshold        | 6 Words, 8 bits  | 6 Words, 6 bits  |  |  |  |  |  |

| Byte Mode, 2 Byte Threshold        | 9 Bytes, 2 bits  | 3 Bytes, 4 bits  |  |  |  |  |  |

| Byte Mode, 4 Byte Threshold #1     | 9 Bytes, 2 bits  | 5 Bytes, 6 bits  |  |  |  |  |  |

| Byte Mode, 4 Byte Threshold #2     | 9 Bytes, 6 bits  | 5 Bytes, 6 bits  |  |  |  |  |  |

| Byte Mode, 8 Byte Threshold        | 10 Bytes         | 9 Bytes, 6 bits  |  |  |  |  |  |

| Byte Mode, 12 Byte Threshold       | 13 Bytes, 7 bits | 13 Bytes, 5 bits |  |  |  |  |  |

## TABLE I. Receive Packet Thresholds

**AN-88**

© 1995 National Semiconductor Corporation TL/F/11819

RRD-B30M75/Printed in U. S. A

| Transmit Packet Cases        | First Threshold  | Threshold                                  |

|------------------------------|------------------|--------------------------------------------|

| Word Mode, 1 Word Threshold  | 6 Words          | 3 Words, 12 bits                           |

| Word Mode, 2 Word Threshold  | 4 Words, 3 bits  | 3 Words, 13 bits                           |

| Word Mode, 4 Word Threshold  | 5 Words, 13 bits | 5 Words, 13 bits                           |

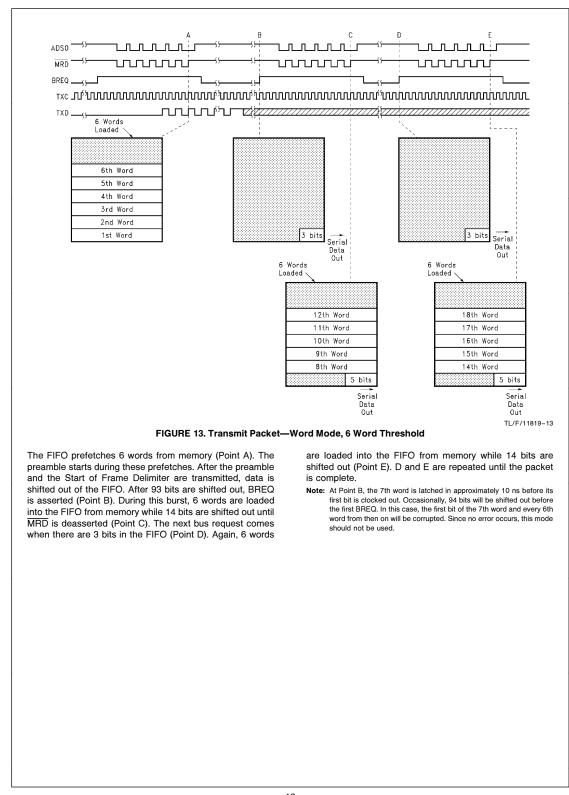

| Word Mode, 6 Word Threshold  | 7 Words, 13 bits | 7 Words, 13 bits                           |

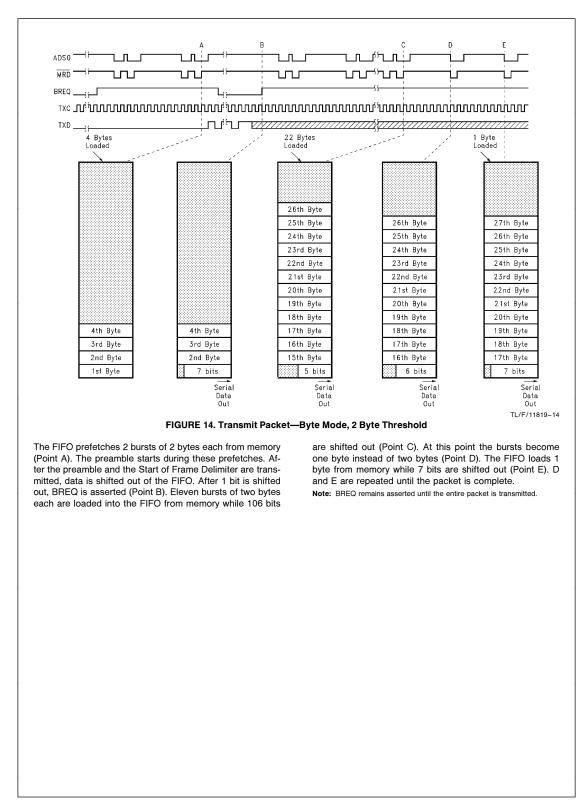

| Byte Mode, 2 Byte Threshold  | 12 Words, 1 bit  | (See Timing Diagram,<br><i>Figure 14</i> ) |

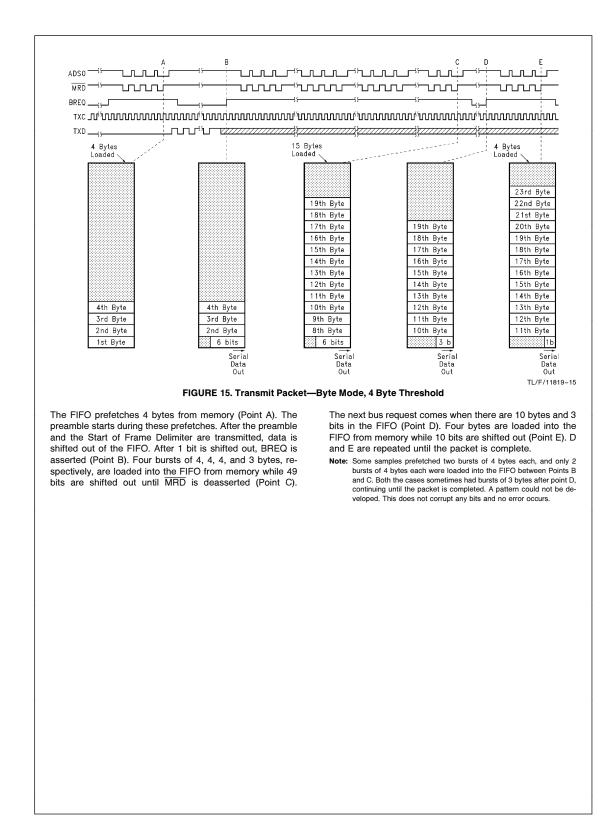

| Byte Mode, 4 Byte Threshold  | 12 Bytes, 1 bit  | 5 Bytes, 5 bits                            |

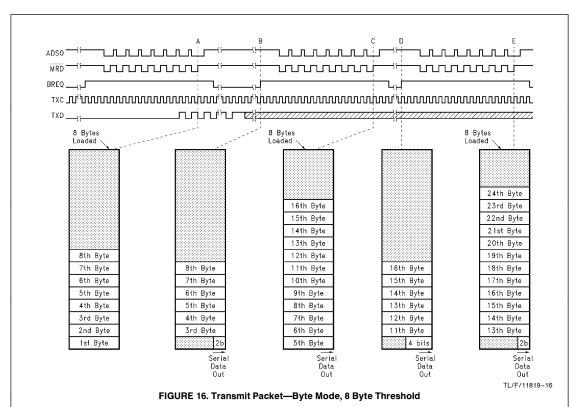

| Byte Mode, 8 Byte Threshold  | 9 Bytes, 6 bits  | 9 Bytes, 4 bits                            |

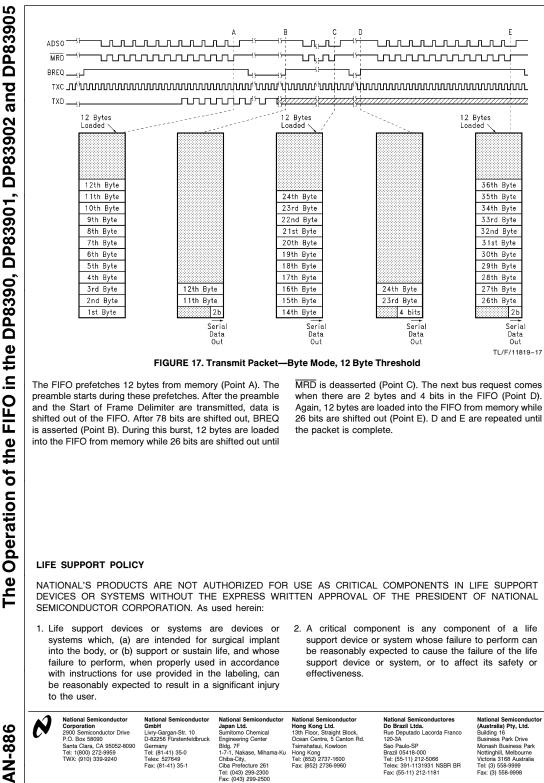

| Byte Mode, 12 Byte Threshold | 13 Bytes, 6 bits | 13 Bytes, 4 bits                           |

## 3.0 FIFO OPERATION DURING RECEIVE

At the beginning of reception, the NIC stores the entire Address field of each incoming packet in the FIFO to determine whether the packet matches its Physical Address Registers or maps to one of its Multicast Registers. Therefore, the first local DMA transfer does not occur until after 8 bytes (4 words) have accumulated in the FIFO, regardless of the value of the threshold. This affects the bus latencies at 2 byte, 4 byte, 1 word, and 2 word thresholds during the first receive BREQ. Thus the threshold for the first burst that is loaded into memory differs from the remaining threshold values. Refer to Table I for the exact threshold values.

## **4.0 FIFO OPERATION DURING TRANSMIT**

Before transmitting, the NIC performs a prefetch from memory to load the FIFO. The number of bytes prefetched is the programmed FIFO threshold, except for 1 byte, 1 word, and 2 word thresholds which prefetch 4 bytes, 2 words, and 4 words respectively. The next BREQ is not issued until after the NIC actually begins transmitting data, i.e., after Preamble and SFD. The threshold for the first burst that is loaded from memory following the prefetched data often differs from the remaining threshold values. Refer to Table II for the exact threshold values.

## 5.0 FIFO UNDERRUNS AND OVERRUNS

To assure that there is no overwriting of data, the FIFO logic flags an overrun if it becomes full before bus acknowledge is returned. To assure that there is no lost data, the FIFO flags an underrun if it becomes empty before bus acknowledge is returned. There are two causes which produce overruns and underruns:

- 1. The bus latency is so long that the FIFO has filled (or emptied) before the local DMA has serviced the FIFO.

- The bus latency or bus data rate has slowed the throughput of the local DMA to a point where it is slower than the network data rate (10 Mb/s). This second condition is also dependent upon DMA clock and data width (byte wide or word wide).

The worst case condition ultimately limits the overall bus latency that the NIC can tolerate.

## 6.0 TIMING DIAGRAMS

The following pages contain detailed timing diagrams and descriptions of every possible receive and transmit mode transfer. The descriptions are of 2, 4, 8, and 12 byte transfers (on an 8-bit Novell board) and 1, 2, 4, and 6 word transfers (on a 16-bit Novell board). For each transfer, the bus clock runs at 20.0 MHz. Tables III and IV summarize the information found in the receive and transmit transfer diagrams respectively.

| Receive Packet<br>Cases<br>(Point A to B)                                                                    |                                               | D to<br>erted                                                                                           | rted to MWR<br>Deasserted                                             |                                                                                                    | MWR<br>Deasserted to<br>BREQ Asserted<br>(Point C to D) | BREQ Asserted<br>to MWR<br>Deasserted<br>(Point D to E)       |                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

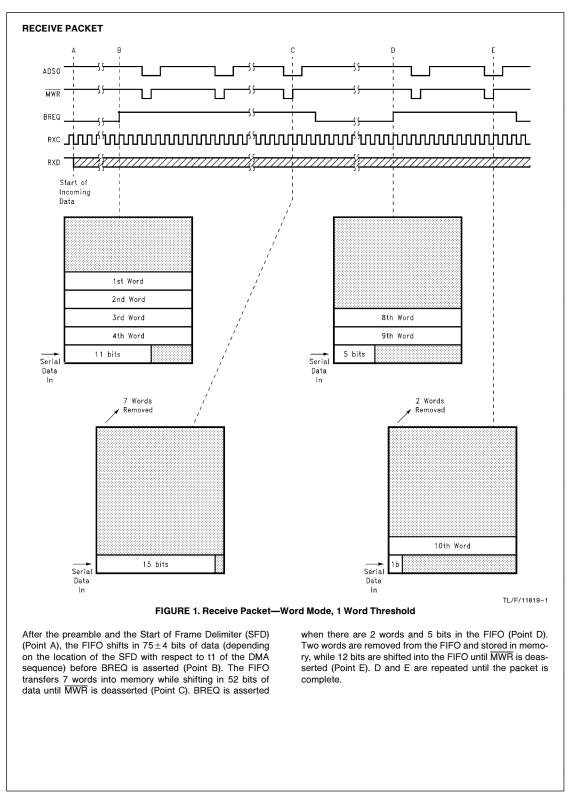

| Word Mode<br>1 Word Threshold                                                                                | d                                             | $75\pm4$ bits Sr                                                                                        | nifted In                                                             | 7 Words Rem<br>52 bits Shifte                                                                      |                                                         | 22 bits Shifted In                                            | 2 Words Removed<br>12 bits Shifted In                                                                                                           |

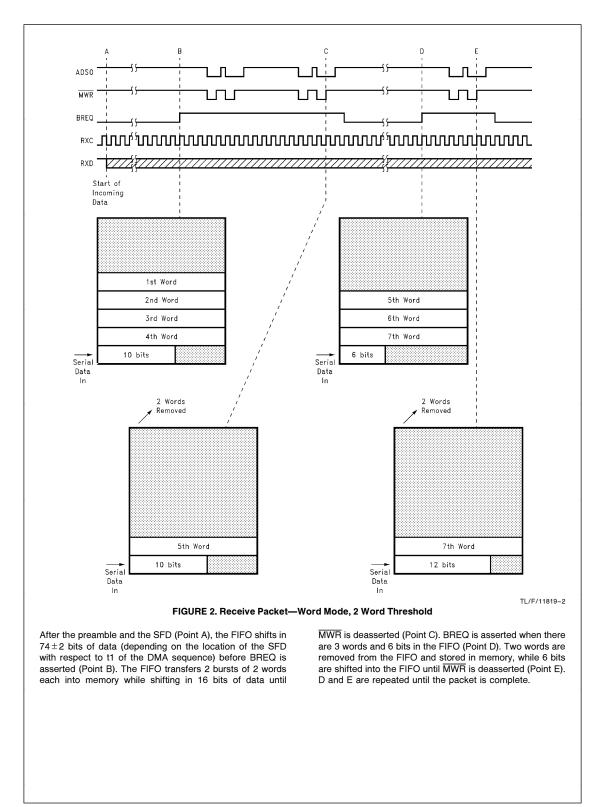

| Word Mode<br>2 Word Threshold                                                                                | d                                             | 74 $\pm$ 2 bits Shifted In                                                                              |                                                                       | ed In 4 Words Removed<br>16 bits Shifted In                                                        |                                                         | 28 bits Shifted In                                            | 2 Words Removed<br>6 bits Shifted In                                                                                                            |

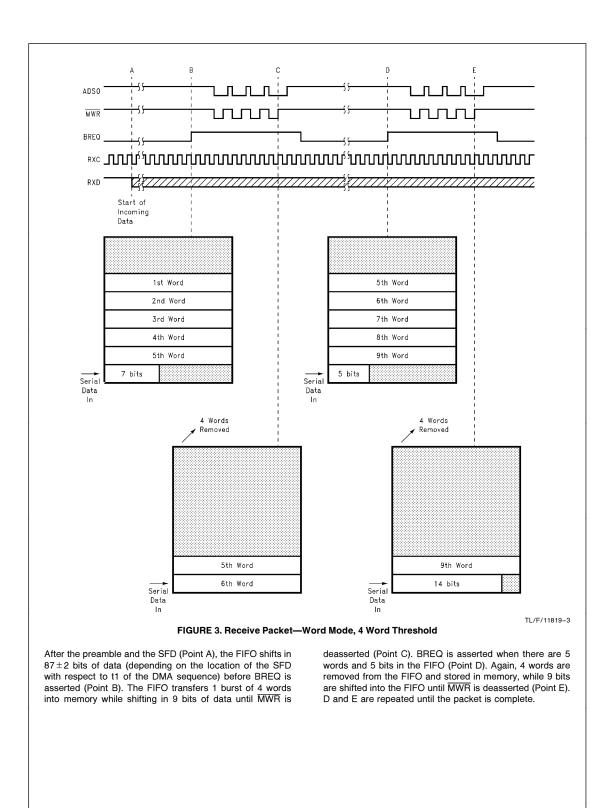

| Word Mode<br>4 Word Threshold                                                                                | d                                             | 87±2 bits Sh                                                                                            | ifted In 4 Words Remove<br>9 bits Shifted                             |                                                                                                    |                                                         | 53 bits Shifted In                                            | 4 Words Removed<br>9 bits Shifted In                                                                                                            |

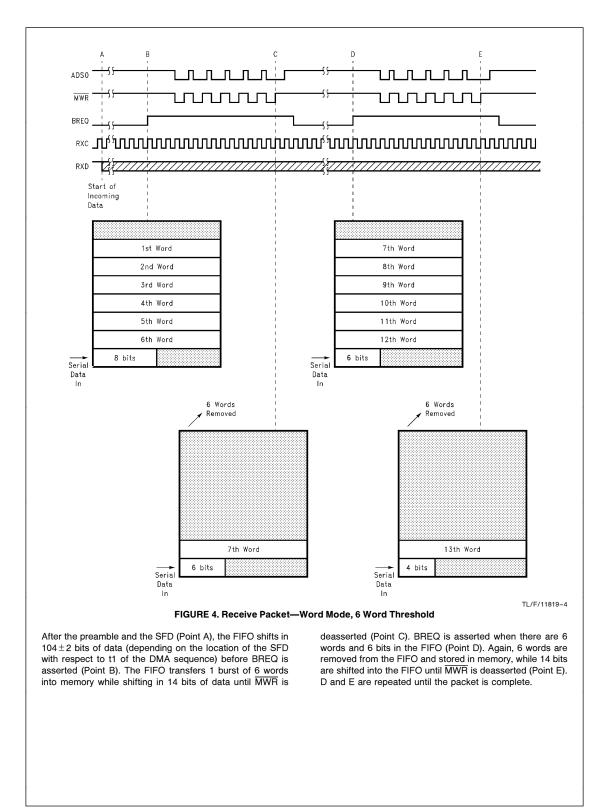

| Word Mode<br>6 Word Threshold                                                                                | d                                             | 104 $\pm$ 2 bits S                                                                                      | hifted In                                                             | 6 Words Rem<br>14 bits Shifte                                                                      |                                                         | 80 bits Shifted In                                            | 6 Words Removed<br>14 bits Shifted In                                                                                                           |

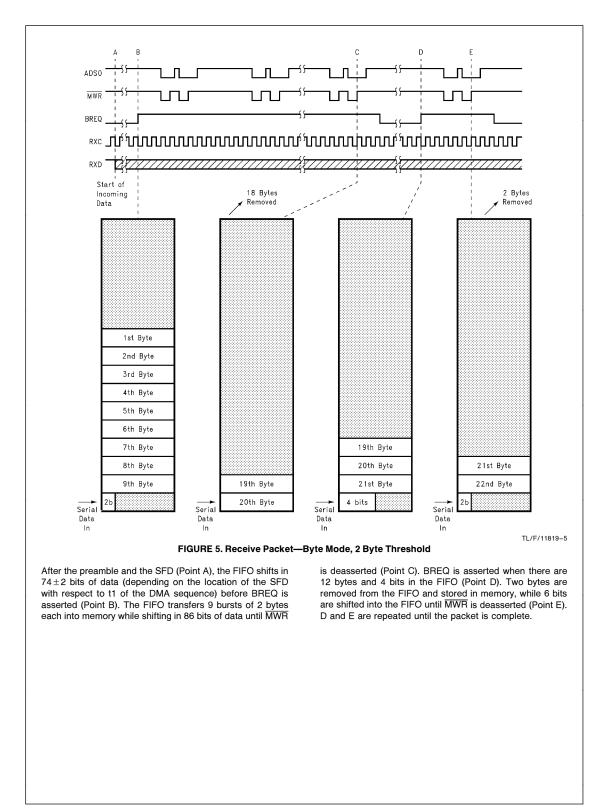

| Byte Mode<br>2 Byte Threshold                                                                                | -                                             |                                                                                                         | ifted In 18 Bytes Remove<br>86 bits Shifted Ir                        |                                                                                                    |                                                         | 12 bits Shifted In                                            | 2 Bytes Removed<br>6 bits Shifted In                                                                                                            |

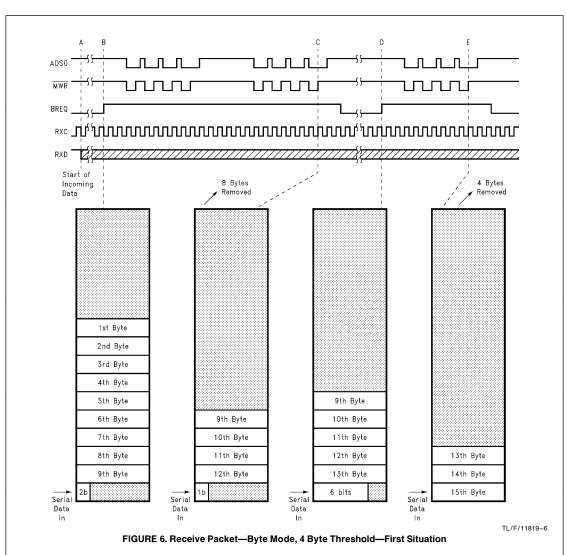

| Byte Mode<br>4 Byte Threshold 7                                                                              | ⊭1                                            | $74\pm1$ bit Sh                                                                                         | ifted In                                                              | 8 Bytes Remo<br>23 bits Shifte                                                                     |                                                         | 21 bits Shifted In                                            | 4 Bytes Removed<br>10 bits Shifted In                                                                                                           |

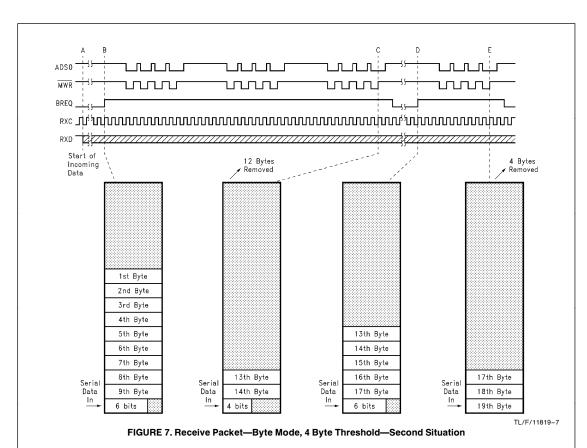

| Byte Mode<br>4 Byte Threshold 7                                                                              | ⊭2                                            | $78\pm1$ bit Sh                                                                                         | ifted In                                                              | 12 Bytes Rem<br>38 bits Shifte                                                                     |                                                         | 26 bits Shifted In                                            | 4 Bytes Removed<br>10 bits Shifted In                                                                                                           |

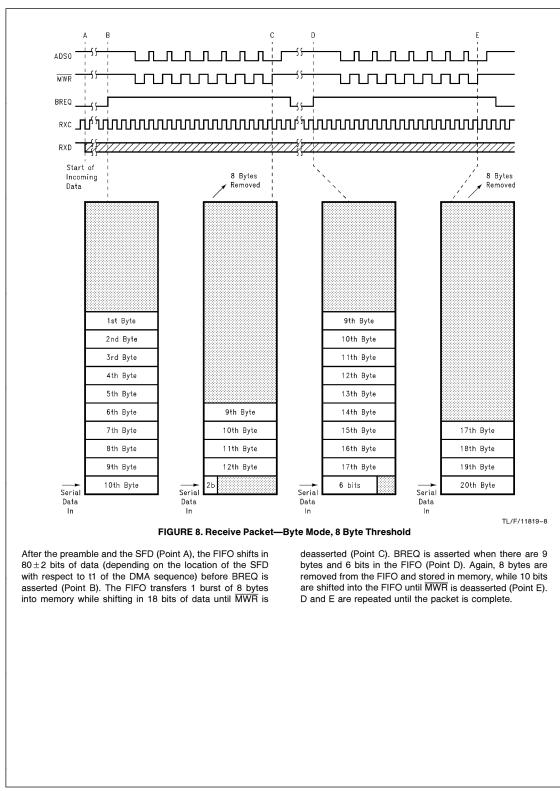

| Byte Mode<br>8 Byte Threshold                                                                                | 1                                             | 80±2 bits Sh                                                                                            | nifted In                                                             | 8 Bytes Remo<br>18 bits Shifte                                                                     |                                                         | 44 bits Shifted In                                            | 8 Bytes Removed<br>18 bits Shifted In                                                                                                           |

| Byte Mode<br>12 Byte Threshol                                                                                | d                                             | $111 \pm 2$ bits S                                                                                      | hifted In                                                             | 12 Bytes Rem<br>26 bits Shifte                                                                     |                                                         | 68 bits Shifted In                                            | 12 Bytes Removed<br>26 bits Shifted In                                                                                                          |

|                                                                                                              |                                               |                                                                                                         | TABLE IV                                                              | . Transmit Packe                                                                                   | t Trans                                                 | fers                                                          |                                                                                                                                                 |

| Transmit Packet<br>Cases                                                                                     |                                               | nitial Loading<br>to BREQ<br>Asserted<br>Point A to B)                                                  | t<br>De                                                               | Q Asserted<br>to MRD<br>asserted<br>int B to C)                                                    | В                                                       | MRD<br>Deasserted to<br>REQ Asserted<br>(Point C to D)        | BREQ Asserted<br>to MRD<br>Deasserted<br>(Point D to E)                                                                                         |

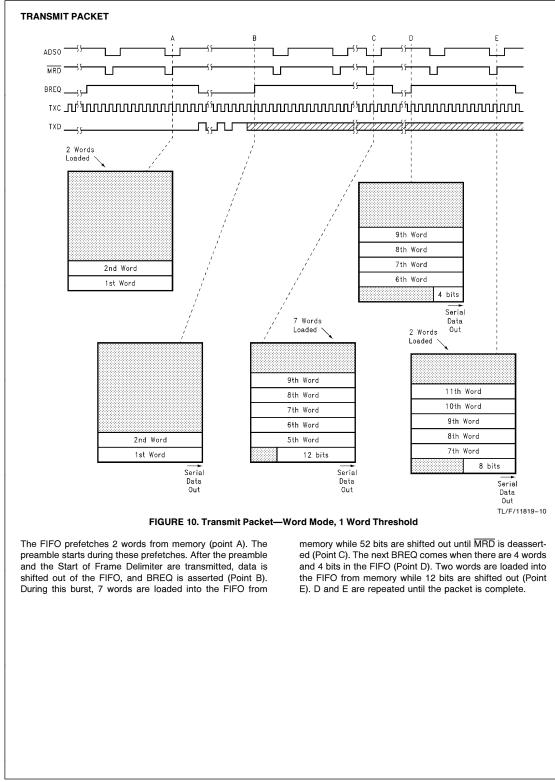

| Word Mode<br>1 Word Threshold                                                                                |                                               | Words Loaded<br>bits Shifted Out                                                                        |                                                                       | ords Loaded<br>s Shifted Out                                                                       | 24                                                      | bits Shifted Out                                              | 2 Words Loaded<br>12 bits Shifted Out                                                                                                           |

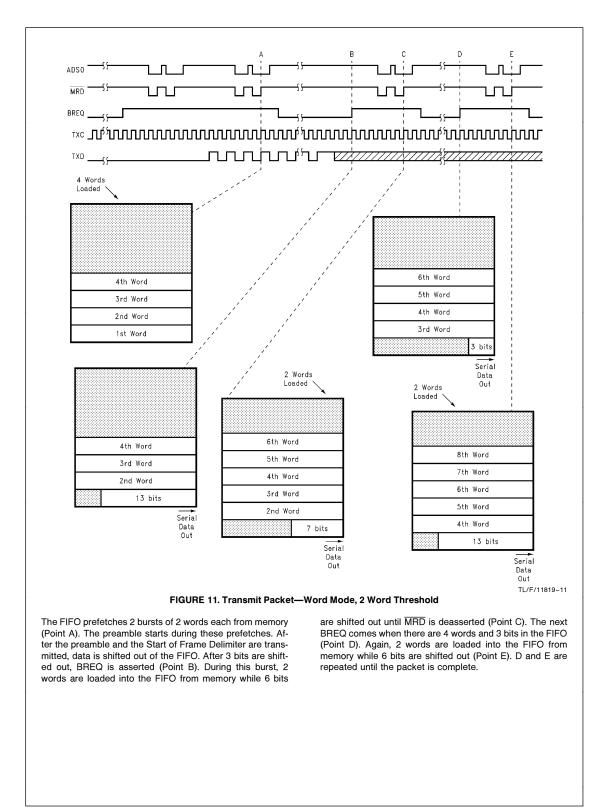

| Word Mode                                                                                                    |                                               | Words Loaded<br>bits Shifted Out                                                                        |                                                                       | ords Loaded<br>Shifted Out                                                                         | 20                                                      | bits Shifted Out                                              | 2 Words Loaded<br>6 bits Shifted Out                                                                                                            |

| 2 Word Threshold                                                                                             |                                               |                                                                                                         |                                                                       |                                                                                                    |                                                         |                                                               |                                                                                                                                                 |

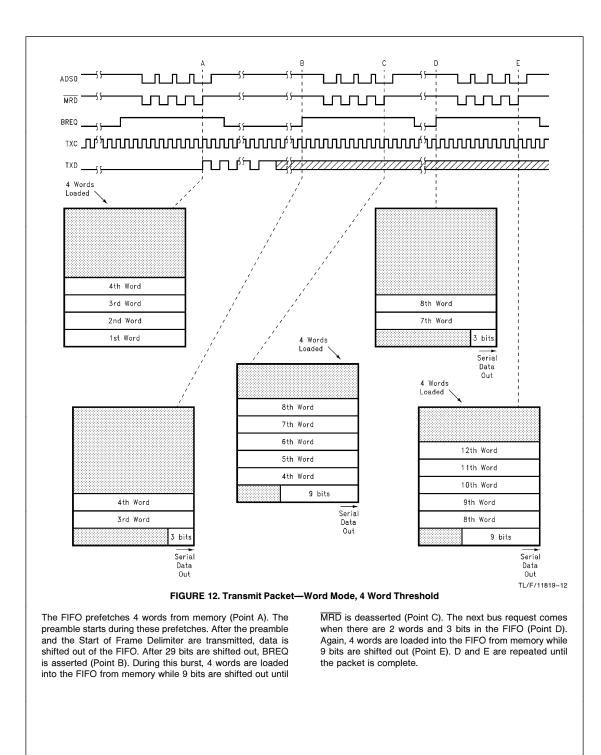

| 2 Word Threshold<br>Word Mode<br>4 Word Threshold                                                            |                                               | Words Loaded<br>bits Shifted Out                                                                        |                                                                       | ords Loaded<br>s Shifted Out                                                                       | 54                                                      | bits Shifted Out                                              | 4 Words Loaded<br>9 bits Shifted in                                                                                                             |

| Word Mode                                                                                                    | 29  <br>6 \                                   |                                                                                                         | 14 bits<br>6 Wc                                                       |                                                                                                    |                                                         | bits Shifted Out                                              | 4 Words Loaded                                                                                                                                  |

| Word Mode<br>4 Word Threshold<br>Word Mode                                                                   | 29<br>6 \<br>93<br>4                          | bits Shifted Out<br>Words Loaded                                                                        | 14 bits<br>6 Wc<br>14 bi<br>(Refer to                                 | s Shifted Out<br>ords Loaded                                                                       | 82                                                      |                                                               | 4 Words Loaded<br>9 bits Shifted in<br>6 Words Loaded<br>14 bits Shifted in                                                                     |

| Word Mode<br>4 Word Threshold<br>Word Mode<br>6 Word Threshold<br>Byte Mode                                  | 29<br>6<br>93<br>4<br>1<br>4                  | bits Shifted Out<br>Words Loaded<br>bits Shifted Out<br>Bytes Loaded                                    | 14 bits<br>6 Wc<br>14 bi<br>(Refer to<br><i>Fi</i><br>15 By           | s Shifted Out<br>ords Loaded<br>ts Shifted in<br>Timing Diagram                                    | 82<br>(Refe                                             | bits Shifted Out                                              | 4 Words Loaded<br>9 bits Shifted in<br>6 Words Loaded<br>14 bits Shifted in<br>(Refer to Timing Diagra                                          |

| Word Mode<br>4 Word Threshold<br>Word Mode<br>6 Word Threshold<br>Byte Mode<br>2 Byte Threshold<br>Byte Mode | 29<br>6 \<br>93<br>4<br>1<br>1<br>4<br>1<br>8 | bits Shifted Out<br>Words Loaded<br>bits Shifted Out<br>Bytes Loaded<br>bit Shifted Out<br>Bytes Loaded | 14 bits<br>6 Wc<br>14 bi<br>(Refer to<br><i>Fi</i><br>49 bits<br>8 By | s Shifted Out<br>ords Loaded<br>ts Shifted in<br>Timing Diagram<br><i>gure 14</i> )<br>rtes Loaded | 82<br>(Refe                                             | bits Shifted Out<br>r to Timing Diagram<br><i>Figure 14</i> ) | 4 Words Loaded<br>9 bits Shifted in<br>6 Words Loaded<br>14 bits Shifted in<br>(Refer to Timing Diagram<br><i>Figure 14</i> )<br>4 Bytes Loaded |

After the preamble and the SFD (Point A), the FIFO shifts in  $74\pm1$  bit of data (depending on the location of the SFD with respect to t1 of the DMA sequence) before BREQ is asserted (Point B). The FIFO transfers 2 bursts of 4 bytes each into memory while shifting in 23 bits of data until

MWR is deasserted (Point C). BREQ is asserted when there are 5 bytes and 6 bits in the FIFO (Point D). Four bytes are removed from the FIFO and stored in memory, while 10 bits are shifted into the FIFO until MWR is deasserted (Point E). D and E are repeated until the packet is complete.

After the preamble and the SFD (Point A), the FIFO shifts in  $78\pm1$  bit of data (depending on the location of the SFD with respect to 11 of the DMA sequence) before BREQ is asserted (Point B). The FIFO transfers 3 bursts of 4 bytes each into memory while shifting in 38 bits of data until

MWR is deasserted (Point C). BREQ is asserted when there are 5 bytes and 6 bits in the FIFO (Point D). Four bytes are removed from the FIFO and stored in memory, while 10 bits are shifted into the FIFO until MWR is deasserted (Point E). D and E are repeated until the packet is complete.

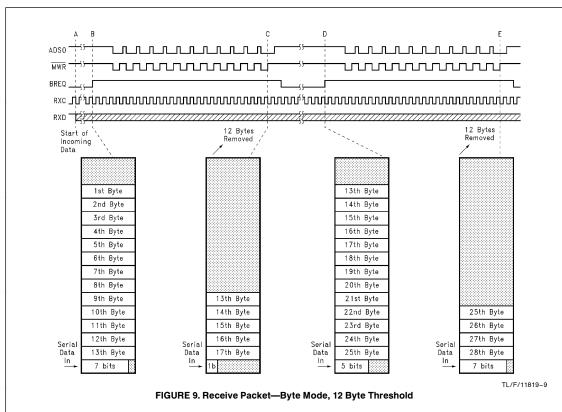

After the preamble and the SFD (Point A), the FIFO shifts in  $111\pm 2$  bits of data (depending on the location of the SFD with respect to t1 of the DMA sequence) before BREQ is asserted (Point B). The FIFO transfers 1 burst of 12 bytes into memory while shifting in 26 bits of data until  $\overline{\rm MWR}$  is

deasserted (Point C). BREQ is asserted when there are 13 bytes and 5 bits in the FIFO (Point D). Again, 12 bytes are removed from the FIFO and stored in memory, while 26 bits are shifted into the FIFO until MWR is deasserted (Point E). D and E are repeated until the packet is complete.

The FIFO prefetches 8 bytes from memory (Point A). The preamble starts during these prefetches. After the preamble and the Start of Frame Delimiter are transmitted, data is shifted out of the FIFO. After 22 bits are shifted out, BREQ is asserted (Point B). During this burst, 8 bytes are loaded

into the FIFO from memory while 18 bits are shifted out until

$\overline{\text{MRD}}$  is deasserted (Point C). The next bus request comes when there are 6 bytes and 4 bits in the FIFO (Point D). Again, 8 bytes are loaded into the FIFO from memory while 18 bits are shifted out (Point E). D and E are repeated until the packet is complete.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications