# Programming the NS32FX200 for Use with a Contact Image Sensor (CIS) Scanner

National Semiconductor Application Note 821 Varda Karpati April 1992

### INTRODUCTION

The NS32FX200 is a highly integrated system chip designed especially for a FAX voice application based on a National Semiconductor NS32FX161, NS32FX164 or NS32FV16 embedded processor. The NS32FX200 provides a complete video (scanner) solution.

The main features of the scanner controller are:

- Programmable generation of synchronization signals for CIS or Charge Coupled Device (CCD) scanners

- Two on-chip Digital-to Analog Convertors (DAC) for shading correction, dithering and Gamma correction

- Automatic writing of scanned bitmap to memory via a DMA channel

- Support for line scan times of 2.5 ms, 5 ms, 10 ms and 20 ms

- Support for external image enhancement

The NS32FX200 system chip supports a wide range of CIS scanners. This application note uses the scanner input signals of the Seiko Epson LSA4U130 CIS scanner as an example.

This document describes how to program the NS32FX200 for use with your CIS scanner. It should be considered an addition to, and be used with, the NS32FX200 Data Sheet.

#### 1.0 SCANNING WITH THE NS32FX200

The scanning process in the NS32FX200 includes the following operations:

- Synchronization Signals generation

- Video Signal processing

- Pixel digitization

- Pixel Bitmap generation

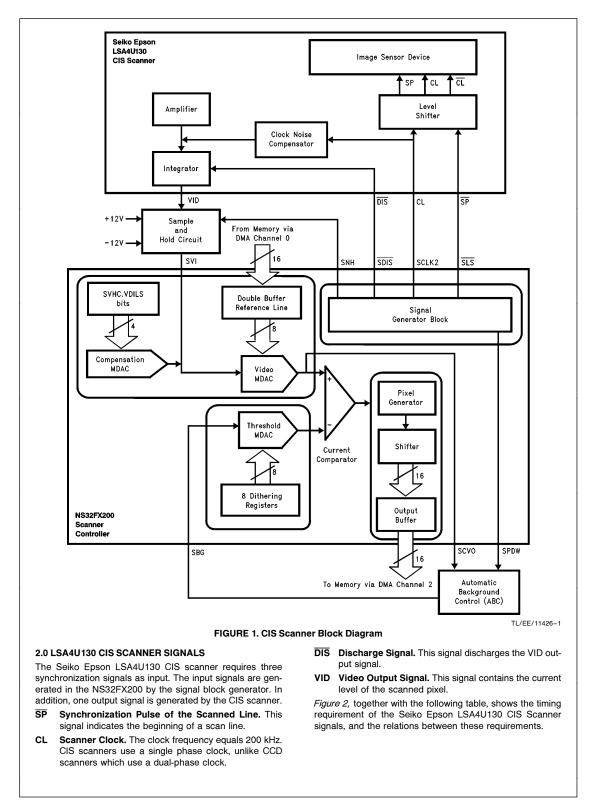

The software activates the signal generator block by setting the SCAN bit in the MCFG register to 1. The signal generator block then generates five synchronization pulses, SNH, SDIS, SLS, SPDW and SCLK2. See block diagram in *Figure 1.*

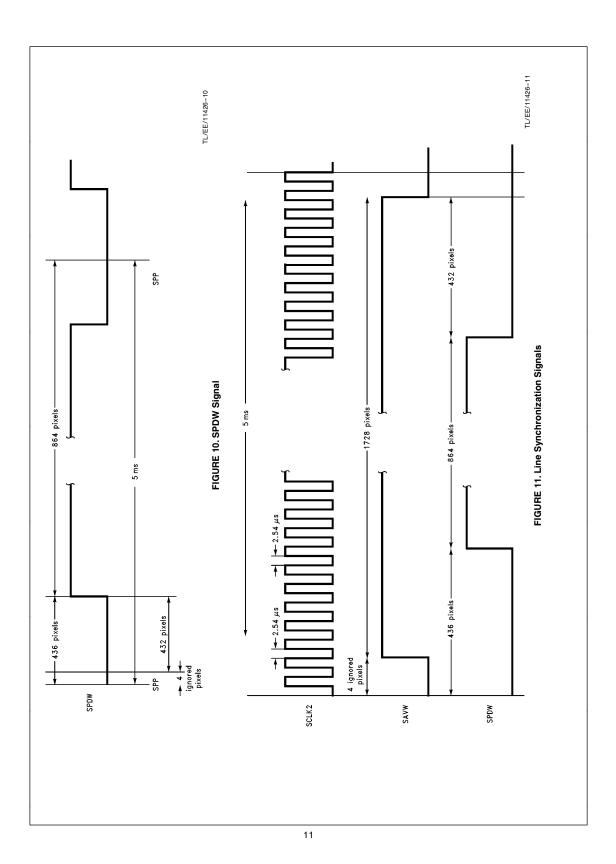

The Scan Line Synchronization ( $\overline{SLS}$ ) signal indicates the beginning of a new scanned line. The frequency of the  $\overline{SLS}$  pulse is controlled by the Scanner Period Pulse (SPP) register, and may be 400 Hz (2.5 ms per line), 200 Hz (5 ms per line), 100 Hz (10 ms per line), or 50 Hz (20 ms per line).

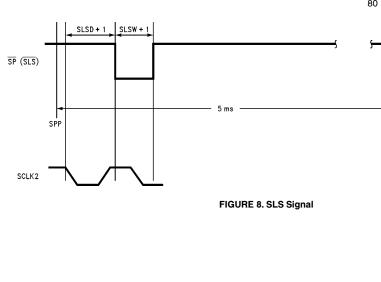

When DMA channel 0 is enabled, it is synchronized by the NS32FX200 scanner controller to the internal Scanner Active Video Window (SAVW) signal, which defines the total time during which the scanner controller collects data. The NS32FX200 scanner controller outputs a Scanner Peak Detect Window (SPDW) signal to the sample and hold circuit. This signal defines the time period during which the scanner controller calculates the peak current of the input pixels. The time period defined by SPDW occurs during the time period defined by the SAVW signal.

When the software activates the DMA0 bit in the MCFG register and the CHEN bit in the CNTL0 register, it enables DMA channel 0 to operate with the internal scanner controller. The channel starts the required DMA operation, i.e., it requests the first two bytes, to fill the double buffer reference line. This line is then sent to the CIS scanner.

For each scanner pixel, the NSFAX software uses a successive approximation algorithm to evaluate the exact correction value needed to compensate for the difference between the maximum (white) analog value and the actual value of these pixels. These 8-bit correction values are stored in memory as "white line correction values". After the white line correction values are evaluated, scanning may start.

During scanning, the white line correction value for each pixel that was synchronized to the Sample and Hold (SNH) signal, is transferred to the double buffer reference line. The correction value from the compensation MDAC, and the analog input, Scanner Video Input (SVI) signal, are both fed into the video DAC from the sample and hold circuit. The video DAC then produces the compensated analog level of the pixel, Scanner Compensated Video Output (SCVO). The SVCO signal is input to the current comparator and to the Automatic Background Control (ABC) circuit.

At the same time, for each pixel, 8-bit data from the eight dithering registers, and the Scanner Background (SBG) signal from the ABC circuit, are fed into a second Multiplying Threshold DAC (MDAC) that produces a darkness threshold level.

During bi-level dithering, each of the eight dithering registers contains a constant threshold value, and the peak detected value of the SCVO register is input to the MDAC via the SBG input signal.

During gray scale dithering, the eight dithering registers contain eight different threshold levels, and the SBG input signal is forced to a constant level.

The compensated analog value of a pixel, and its darkness threshold level, are fed to the current comparator that creates a digital 0 or 1 signal. This bit is input to a pixel generator. The output from the pixel generator is shifted into a shift register. When the shift register is full, and DMA channel 2 is enabled by setting the Channel Enable (CHEN) bit in the CNTL2 register, the shifted word is written to the output buffer, and via DMA channel 2 to memory.

rogramming the NS32FX200 for Use with a Contact Image Sensor (CIS) Scanner

AN-821

© 1995 National Semiconductor Corporation TL/EE11426

RRD-B30M75/Printed in U. S. A

| F $F$ $F$ $F$ $F$ $F$ $F$ $F$ $F$ $F$                                                                                                               |                                                                              |                                               |                           |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------|---------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Item                                                                                                                                                |                                                                              | Min                                           | Max                       | Max Units Description                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                                                                                                                                                     |                                                                              |                                               |                           |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| CL Rise & Fall Time                                                                                                                                 | t1, t2                                                                       | 600                                           | 100                       | ns                                                                   | 10 defines the time between the vising edge of CL and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| CL Rise & Fall Time<br>CL and SP<br>Relationship                                                                                                    | t1, t2<br>t3                                                                 | 600                                           | 100                       | ns<br>ns                                                             | t3 defines the time between the rising edge of CL and the falling edge of SP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| CL and SP                                                                                                                                           |                                                                              | 600<br>800                                    | 100                       |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| CL and SP                                                                                                                                           | t3                                                                           |                                               | 100                       | ns                                                                   | falling edge of SP.<br>t4 defines the time between the falling edge of CL and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| CL and SP                                                                                                                                           | t3<br>t4                                                                     | 800                                           | 100                       | ns<br>ns                                                             | falling edge of SP.         t4 defines the time between the falling edge of CL and the rising edge of SP.         t5 defines the time between the falling edge of SP and the                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| CL and SP                                                                                                                                           | t3<br>t4<br>t5                                                               | 800<br>800                                    | 100                       | ns<br>ns<br>ns                                                       | falling edge of SP.         t4 defines the time between the falling edge of CL and the rising edge of SP.         t5 defines the time between the falling edge of SP and the rising edge of CL.         t6 defines the time between the rising edge of SP and the                                                                                                                                                                                                                                                                                                                            |  |  |  |

| CL and SP<br>Relationship                                                                                                                           | t3<br>t4<br>t5<br>t6                                                         | 800<br>800                                    |                           | ns<br>ns<br>ns<br>ns                                                 | falling edge of SP.         t4 defines the time between the falling edge of CL and the rising edge of SP.         t5 defines the time between the falling edge of SP and the rising edge of CL.         t6 defines the time between the rising edge of SP and the                                                                                                                                                                                                                                                                                                                            |  |  |  |

| CL and SP<br>Relationship<br>SP Rise & Fall Time                                                                                                    | t3<br>t4<br>t5<br>t6<br>t7, t8                                               | 800<br>800<br>800                             |                           | ns<br>ns<br>ns<br>ns<br>ns                                           | falling edge of SP.         t4 defines the time between the falling edge of CL and the rising edge of SP.         t5 defines the time between the falling edge of SP and the rising edge of CL.         t6 defines the time between the rising edge of SP and the falling edge of CL.                                                                                                                                                                                                                                                                                                        |  |  |  |

| CL and SP<br>Relationship<br>SP Rise & Fall Time<br>SP Pulse Width                                                                                  | t3<br>t4<br>t5<br>t6<br>t7, t8<br>t9                                         | 800<br>800<br>800                             | 100                       | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns                               | falling edge of SP.         t4 defines the time between the falling edge of CL and the rising edge of SP.         t5 defines the time between the falling edge of SP and the rising edge of CL.         t6 defines the time between the rising edge of SP and the falling edge of CL.                                                                                                                                                                                                                                                                                                        |  |  |  |

| CL and SP<br>Relationship<br>SP Rise & Fall Time<br>SP Pulse Width<br>DIS Rise and Fall Time                                                        | t3<br>t4<br>t5<br>t6<br>t7, t8<br>t9<br>t10, t11                             | 800<br>800<br>800<br>1000                     | 100                       | ns<br>ns<br>ns<br>ns<br>ns<br>ns                                     | falling edge of SP.         t4 defines the time between the falling edge of CL and the rising edge of SP.         t5 defines the time between the falling edge of SP and the rising edge of CL.         t6 defines the time between the rising edge of SP and the falling edge of CL.         t9 defines SP pulse width.         t12 defines DIS high level time (The time between the rising                                                                                                                                                                                                |  |  |  |

| CL and SP<br>Relationship<br>SP Rise & Fall Time<br>SP Pulse Width<br>DIS Rise and Fall Time                                                        | t3<br>t4<br>t5<br>t6<br>t7, t8<br>t9<br>t10, t11<br>t12                      | 800<br>800<br>800<br>1000<br>1875             | 100                       | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns                         | falling edge of SP.         t4 defines the time between the falling edge of CL and the rising edge of SP.         t5 defines the time between the falling edge of SP and the rising edge of CL.         t6 defines the time between the rising edge of SP and the falling edge of CL.         t9 defines SP pulse width.         t12 defines DIS high level time (The time between the rising edge of CL and the falling edge of CL and the falling edge of DIS).                                                                                                                            |  |  |  |

| CL and SP<br>Relationship<br>SP Rise & Fall Time<br>SP Pulse Width<br>DIS Rise and Fall Time<br>DIS Pulse Width                                     | t3<br>t4<br>t5<br>t6<br>t7, t8<br>t9<br>t10, t11<br>t12<br>t13               | 800<br>800<br>800<br>1000<br>1875<br>625      | 100                       | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns             | falling edge of SP.         t4 defines the time between the falling edge of CL and the rising edge of SP.         t5 defines the time between the falling edge of SP and the rising edge of CL.         t6 defines the time between the rising edge of SP and the falling edge of CL.         t9 defines SP pulse width.         t12 defines DIS high level time (The time between the rising edge of CL and the falling edge of CL and the falling edge of CL and the falling edge of DIS).                                                                                                 |  |  |  |

| CL and SP<br>Relationship<br>SP Rise & Fall Time<br>SP Pulse Width<br>DIS Rise and Fall Time<br>DIS Pulse Width<br>DIS and CL Relate                | t3<br>t4<br>t5<br>t6<br>t7, t8<br>t9<br>t10, t11<br>t12<br>t13<br>t14        | 800<br>800<br>800<br>1000<br>1875<br>625      | 100                       | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns             | falling edge of SP.         t4 defines the time between the falling edge of CL and the rising edge of SP.         t5 defines the time between the falling edge of SP and the rising edge of CL.         t6 defines the time between the rising edge of SP and the falling edge of CL.         t9 defines SP pulse width.         t12 defines DIS high level time (The time between the rising edge of CL and the falling edge of CL and the falling edge of DIS).         t13 defines DIS pulse width.         t15 defines the time in which VID output changes from 0% to                   |  |  |  |

| CL and SP<br>Relationship<br>SP Rise & Fall Time<br>SP Pulse Width<br>DIS Rise and Fall Time<br>DIS Pulse Width<br>DIS and CL Relate<br>VID(0%–90%) | t3<br>t4<br>t5<br>t6<br>t7, t8<br>t9<br>t10, t11<br>t12<br>t13<br>t14<br>t15 | 800<br>800<br>800<br>1000<br>1875<br>625<br>0 | 100<br>100<br>100<br>1500 | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns | falling edge of SP.         t4 defines the time between the falling edge of CL and the rising edge of SP.         t5 defines the time between the falling edge of SP and the rising edge of CL.         t6 defines the time between the rising edge of SP and the falling edge of CL.         t9 defines SP pulse width.         t12 defines DIS high level time (The time between the rising edge of CL and the falling edge of CL and the falling edge of DIS).         t13 defines DIS pulse width.         t15 defines the time in which VID output changes from 0% to 90% of its value. |  |  |  |

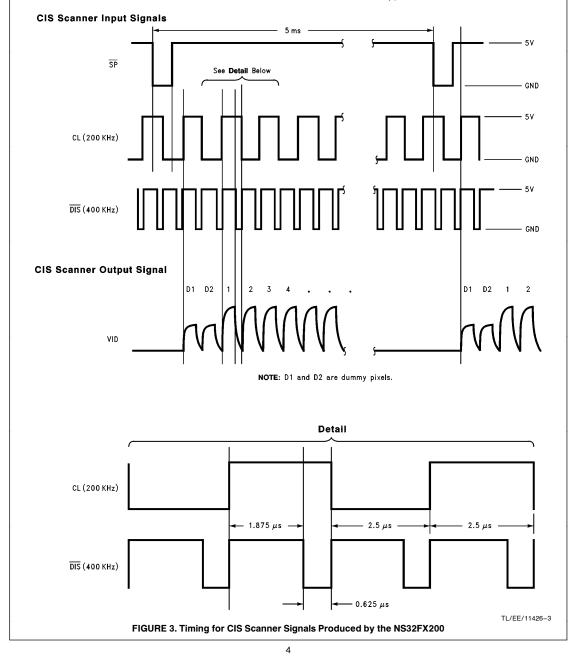

The signal block generator also generates, in addition to the CIS scanner control signals, an SNH signal that is sent to the sample and hold circuit. The sample and hold circuit uses it to sample the VID signal that is output from the CIS scanner.

When the VID signal reaches about 90 percent of its maximum value, the sample and hold circuit generates a signal that holds the pixel value for approximately 80 per cent of the pixel cycle, in order to ease the digital and analog signal timing requirements of the internal NS32FX200 scanner controller. Approximately 90 per cent of the value of the pixel should be sampled and held. The SNH signal should not be active when the output line is discharged. The minimum delay between any edge of CL and the rising edge of SNH for the Seiko Epson LSA4U130 scanner is 1.6  $\mu$ s (t16).

After the sample and hold operation is finished, the scanner output should be prepared for the next pixel by the  $\overline{\rm DIS}$  signal.

The minimum delay between an edge of CL and the falling edge of  $\overline{\text{DIS}}$ , for the LSA4U130 scanner, is 1.875  $\mu$ s (t12). The minimum width of the  $\overline{\text{DIS}}$  signal is 0.625  $\mu$ s (t13). The delay plus the width of the  $\overline{\text{DIS}}$  signal is 2.5  $\mu$ s, i.e., CL

phase width.

- Note 1: The frequency of the SNH and DIS signals (400 kHz) is twice that of the CL signal (200 kHz).

- Note 2: The minimum time required by the scanner to scan one pixel is 2.5  $\mu$ s. The maximum time per pixel is limited by the maximum time from the beginning of one line to the beginning of the next line, which may not exceed 5 ms. There may be up to 1728 pixels plus four to six dummy pixels in a line.

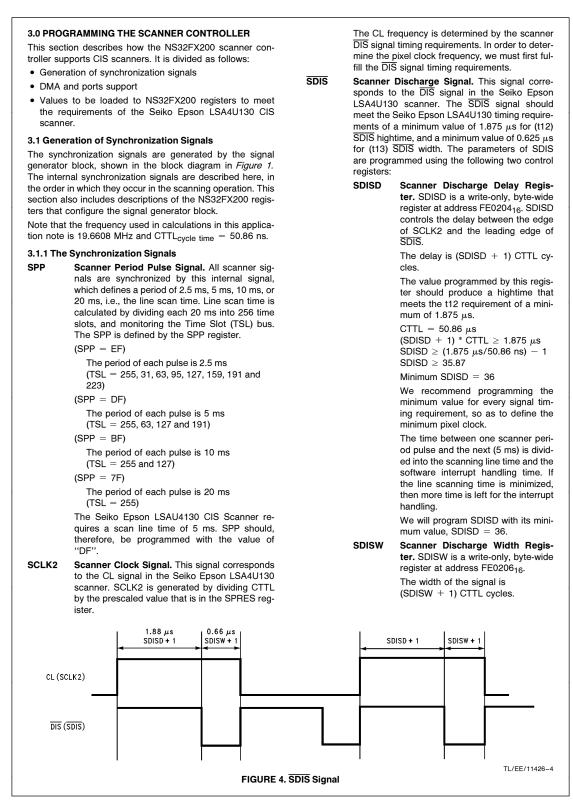

SNH The value programmed by this register should Sample and Hold Pulse. This signal correproduce a Scanner Discharge width time that sponds to the SNH in the Seiko Epson meets the t13 requirements of a minimum of LSA4U130 scanner. The SNH signal should 0.625 μs. meet the Seiko Epson LSA4U130 timing requirements of a maximum t15 (VID 0%-90%) of (SDISW + 1) \* CTTL  $\geq$  0.625  $\mu$ s 1.5  $\mu$ s, and a t16 (VID sampling period) which SDISW  $\geq$  (0.625  $\mu$ s/50.86 ns) - 1 extends from a minimum of 1.6  $\mu$ s to a maximum SDISW  $\geq$  11.28 of 1.87  $\mu$ s. The parameters of SNH are pro-We will program the minimum SDISW value = grammed using the following two control regis-12. ters: The programmed values define delay and width SNHD Sample and Hold Delay Register. times of: SNHD is a write-only, byte-wide reg- $SDIS_{delay} = (36 + 1) * 50.86 \text{ ns} = 1.88 \ \mu \text{s}$ ister at address FE020816. SNHD  $SDIS_{width} = (12 + 1) * 50.86 \text{ ns} = 0.66 \ \mu \text{s}$ controls the delay between the edge of SCLK2 and the leading edge of The pixel clock is, therefore: SNH.  $\overline{\text{SDIS}}_{\text{hightime}} + \overline{\text{SDIS}}_{\text{width}} = 1.88 \ \mu\text{s} + 0.66 \ \mu\text{s}$ The delay is (SNHD + 1) CTTL cycles. = 2.54 μs (SNHD + 1) \* 50.86 ns  $\geq$  1.6  $\mu s$ The pixel clock cycle time defines CL (SCLK2) SNHD ≥ 30.46 phase time. SCLK2 cycle time is 5.08 µs. SCLK2 Min SNHD = 31 (CL) frequency is defined by using the prescale Programmed value should be 31 value programmed in the SPRES register.  $\text{SNH}_{\text{delay}}$  = 32 \* 50.86 ns = 1.63  $\mu\text{s}$ Scanner Prescale Register. SPCLK SPRES Sample and Hold Width Register. SNHW = CTTL/(SPRES + 1). SPRES is a SNHW is a write-only, byte-wide regwrite-only, byte-wide register at adister at address FE020A<sub>16</sub>. dress FE022216. The width of the signal is (SNHW + 1) CTTL  $\begin{array}{l} \text{SPCLK}_{\text{cycle time}} = \text{CTTL}_{\text{cycle time}} * \left[2 * (\text{SPRES} + 1)\right] = 2 * 2.54 \ \mu \text{s} = 5.08 \ \mu \text{s} \end{array}$ cycles. The SNH signal should be deactivated before  $5.08 \ \mu s = 50.86 \ ns * [2 * (SPRES + 1)]$  $\overline{\text{SDIS}}$  goes low-1.88  $\mu\text{s}$  after the edge of SPRES =  $(5.08 \ \mu s/2 \ ^{*} \ 50.86 \ ns) - 1 = 49$ SCLK2. The timing requirements of t1, t2, t7, t8, t10, t11 SNH<sub>delay</sub> + SNH<sub>width</sub> should not exceed are guaranteed by design. 1.88 µs. The next signal to determine is the Sample and  $[(SNHD + 1) + (SNHW + 1)] * 50.86 \text{ ns} \leq$ Hold (SNH) pulse. 1.88 µs SNHW < 3.864SNHW will be programmed with the value of 3.  $SNH_{width} = (3 + 1) * 50.86 \text{ ns} = 0.2 \ \mu \text{s}$  $\frac{1}{1.83 \ \mu s} + \frac{1}{1.83 \ \mu s} = \frac{1}{1.83 \ \mu s} + \frac{1}{1.83 \ \mu s} = \frac{1}{1.83 \$ SNHD + 1 SNHW + 1 SNHD + 1 SNH₩ + 1 CL (SCLK2) SNH (SNH) TL/EE/11426-5 FIGURE 5. SNH Signal

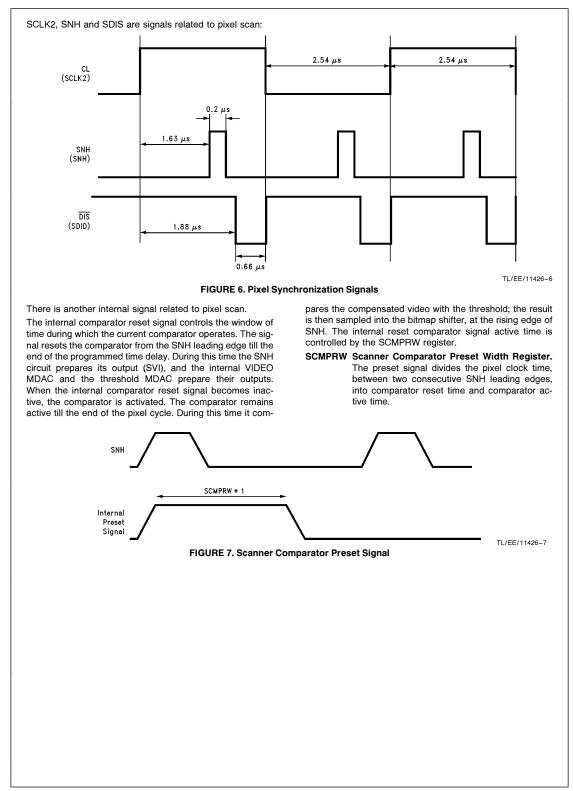

The internal analog reset width (SCMPRW + 1) is equal to, or greater than the SVI set-up time plus 200 ns. The SVI set-up time is determined by the performance of the SNH circuit. The analog reset should be terminated at least 300 ns before the next SNH leading edge. min SCMPRW  $\rightarrow$  (SCMPRW + 1) \*  $CTTL_{cycle time} \ge SVI_{setup} + 200 \text{ ns}$ max SCMPRW  $\rightarrow$  [(SPRES + 1) -(SCMPRW + 1)] \* CTTL<sub>cycle time</sub>  $\geq$  300 ns min SCMPRW = (SVI\_{setup}/CTTL\_{cycle time}) + 3 max SCMPRW  $\rightarrow$  SCMPRW  $\leq$  50 - 1 -(300 ns/50.86 ns) = 43.1 max SCMPRW = 43 To achieve the highest possible speed and accurately the reset signal should be active during 70 percent of the pixel cycle, starting from the leading edge of SNH SCMPRW + 1 = 70% (SPRES + 1)  $\rightarrow$ SCMPRW = 50 \* 0.7 - 1 = 34SCMPRW = 34

The next stage, after the signals related to pixel processing have been calculated, is to calculate the signals related to the whole line.

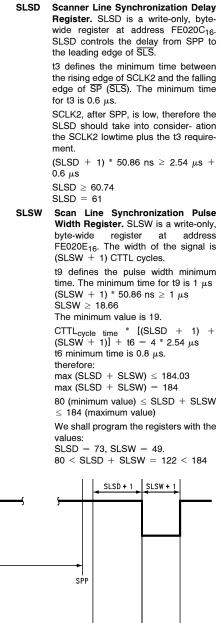

SLS Scan Line Synchronization Pulse. This pulse indicates the beginning of a new scan line. SLS corresponds to the SP signal in the Seiko Epson LSA4U130 scanner. SLS signal timing is determined according to Seiko Epson LSA4U130 timing requirements t3, t4, t5, t6, and t9 (see *Figure* 2). SLS parameters are programmed using the following two control registers:

TL/EE/11426-8

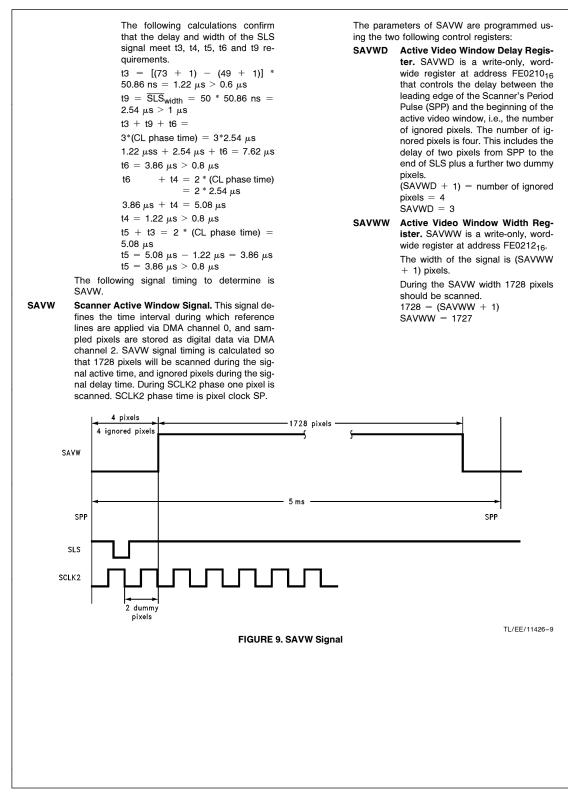

| SPDW       | Scanner                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|            | signal en<br>which the<br>To achie<br>only whe<br>following<br>the narro<br>page, and<br>er mecha<br>to either<br>the ABC | Peak Detection Window Signal. This<br>ables definition of a time interval during<br>e peak detector of the ABC is changed.<br>ve the best results, charge the ABC<br>in the real document is scanned. In the<br>example, we assume that the width of<br>west document scanned is half an A4<br>d that the document is centered. In oth-<br>nical set-ups, the document is adjusted<br>the left or the right of the scanner, and<br>window will be shifted accordingly<br>meters of SPDW are programmed us-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BY<br>3.2 Scanner (<br>This section of<br>channels 0 ar<br>configured, Di<br>troller with ref<br>bitmap data.<br>3.2.1 Configu    |

|            | •                                                                                                                         | blowing two control registers:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | To configure                                                                                                                      |

| SPDWD      | SPDWD i<br>dress FE<br>the leadin<br>(SPP) an<br>window.<br>SPDWD                                                         | etection Window Delay Register.<br>s a write-only, word-wide register at ad-<br>0214 <sub>16</sub> that controls the delay between<br>ng edge of the scanner's period pulse<br>d the beginning of the peak detector<br>+ 1 = (1728/4) + 4 ignored pixels =<br>SPDWD = 435                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | function as in<br>tions:<br>1. Define DN<br>DMA0, in t<br>2. Define sca<br>outputs fro<br>bits 4, 6, 9<br>register to             |

| SPDWW      | Peak De<br>write-only                                                                                                     | tection Window Width. SPDWW is a<br>v, word-wide register at address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3. Enable sca                                                                                                                     |

|            | FE0216 <sub>10</sub><br>The width<br>1728/2 =                                                                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | B Output E<br>4. Define SN<br>controller<br>Select (PC                                                                            |

| 3.1.2 Sigr | 863<br>Ial Genera                                                                                                         | tion Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5. Enable the<br>2 of the Po                                                                                                      |

| •          | ation Regi                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.2.2 Program                                                                                                                     |

| generatio  | n block of                                                                                                                | bed in this section configure the signal the NS32FX200 for use with a Seiko                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADCA0, ADC                                                                                                                        |

| •          | U4130 CIS                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | De<br>0 :                                                                                                                         |

| SGC        | -                                                                                                                         | Generator Control Register. The po-<br>ne synchronization signals is controlled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |

|            |                                                                                                                           | amming the SGC register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | de                                                                                                                                |

| 7          |                                                                                                                           | Imming the SGC register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | de<br>cle                                                                                                                         |

| 7          |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | rei<br>de<br>cle<br>bit<br>sp                                                                                                     |

| 7          | by progra                                                                                                                 | 4     3     2     1     0       4     3     2     1     0       LSPP     PDWP     SNHP     DISP   Scanner Discharge Pulse Polarity. 0 = Active low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | de<br>cle<br>bit<br>sp<br>AL<br>the<br>be                                                                                         |

| 7          | reserved                                                                                                                  | 4       3       2       1       0         4       3       2       1       0         LSPP       PDWP       SNHP       DISP         Scanner Discharge Pulse Polarity.         0       = Active low         1       = Active high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | de<br>cle<br>bit<br>sp<br>A[<br>th<br>be<br><b>BLTC0, BLTC</b>                                                                    |

| 7          | by progra                                                                                                                 | 4     3     2     1     0       4     3     2     1     0       LSPP     PDWP     SNHP     DISP   Scanner Discharge Pulse Polarity. 0 = Active low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | de<br>cle<br>bit<br>sp<br>Al<br>th<br>be<br><b>BLTC0, BLT(</b><br>BI                                                              |

| 7          | by progra<br>reserved<br>DISP<br>SNHP                                                                                     | 4       3       2       1       0         4       3       2       1       0         LSPP       PDWP       SNHP       DISP         Scanner Discharge Pulse Polarity.         0       =       Active low         1       =       Active high         Sample and Hold Pulse Polarity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | de<br>cle<br>bit<br>sp<br>AI<br>th:<br>be<br><b>BLTC0, BLTC</b><br>BI<br>an                                                       |

| 7          | reserved                                                                                                                  | 4       3       2       1       0         4       3       2       1       0         LSPP       PDWP       SNHP       DISP         Scanner Discharge Pulse Polarity.         0       = Active low         1       = Active high         Sample and Hold Pulse Polarity.         0       = Active high         Sample and Hold Pulse Polarity.         0       = Active high         Powe         Powe         Active low         1         Active high         Peak Detector Window Polarity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | de<br>cle<br>sp<br>Al<br>be<br><b>BLTC0, BLT(</b><br><b>BI</b><br>ar<br>nu<br>re                                                  |

| 7          | by progra<br>reserved<br>DISP<br>SNHP                                                                                     | 4       3       2       1       0         4       3       2       1       0         LSPP       PDWP       SNHP       DISP         Scanner Discharge Pulse Polarity.         0       =       Active low         1       =       Active high         Sample and Hold Pulse Polarity.         0       =       Active low         1       =       Active low         1       =       Active low         1       =       Active high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | de<br>cle<br>bit<br>sp<br>AI<br>th<br>be<br><b>BLTCO, BLT(</b><br><b>BI</b><br>an<br>nu<br>re<br>pr<br>ea                         |

| 7          | by progra<br>reserved<br>DISP<br>SNHP                                                                                     | 4       3       2       1       0         4       3       2       1       0         LSPP       PDWP       SNHP       DISP         Scanner Discharge Pulse Polarity.         0       =       Active low         1       =       Active high         Sample and Hold Pulse Polarity.         0       =       Active high         Sample and Hold Pulse Polarity.         0       =       Active high         Petector Window Polarity.         0       =       Active low         1       =       Active low         1       =       Active high         Line Synchronization Pulse Polari-       Polari-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | de<br>cle<br>bit<br>sp<br>AI<br>th<br>be<br>BLTC0, BLT(<br>BI<br>ar<br>nu<br>re<br>pr<br>ea<br>MODE0, MOI                         |

| 7          | by progra<br>reserved<br>DISP<br>SNHP<br>PDWP                                                                             | 4       3       2       1       0         4       3       2       1       0         1       LSPP       PDWP       SNHP       DISP         Scanner Discharge Pulse Polarity.         0       =       Active low         1       =       Active high         Sample and Hold Pulse Polarity.         0       =       Active low         1       =       Active high         Line Synchronization Pulse Polarity,       0         0       =       Active low         1       =       Active high         Line Synchronization Pulse Polarity,       0         0       =       Active low                                                                                                                                                                                                                                                                                   | de<br>cle<br>bit<br>sp<br>Al<br>th<br>be<br>BLTC0, BLT(<br>BI<br>an<br>nu<br>re<br>mu<br>re<br>MODE0, MOI<br>Mu<br>an             |

|            | reserved<br>DISP<br>SNHP<br>PDWP<br>LSPP                                                                                  | 4       3       2       1       0         4       3       2       1       0         1       LSPP       PDWP       SNHP       DISP         Scanner Discharge Pulse Polarity.         0       =       Active low         1       =       Active high         Sample and Hold Pulse Polarity.         0       =       Active high         Detector Window Polarity.         0       =       Active high         Line Synchronization Pulse Polarity         0       =       Active high         Line Synchronization Pulse Polarity       0       =         0       =       Active low         1       =       Active high                                                                                                                                                                                                                                                                                                                                                          | de<br>cle<br>bit<br>sp<br>AL<br>tha                                                                                               |

| SVHC       | by progra<br>reserved<br>DISP<br>SNHP<br>PDWP<br>LSPP<br>Scanner                                                          | 4       3       2       1       0         LSPP       PDWP       SNHP       DISP         Scanner Discharge Pulse Polarity.         0       = Active low         1       = Active high         Sample and Hold Pulse Polarity.         0       = Active high         Sample and Hold Pulse Polarity.         0       = Active low         1       = Active high         Peak Detector Window Polarity.         0       = Active low         1       = Active high         Line Synchronization Pulse Polarity.         0       = Active low         1       = Active low         1       = Active low         1       = Active low         1       = Active high         Video Handling Control Register.                                                                                                                                                                                     | de<br>ch<br>bit<br>sp<br>AI<br>BLTC0, BLTC<br>BI<br>an<br>nu<br>re<br>pr<br>ea<br>MODE0, MOI<br>an<br>re                          |

| SVHC<br>7  | reserved<br>DISP<br>SNHP<br>PDWP<br>LSPP                                                                                  | 4       3       2       1       0         LSPP       PDWP       SNHP       DISP         Scanner Discharge Pulse Polarity.         0       = Active low         1       = Active high         Sample and Hold Pulse Polarity.         0       = Active high         Sample and Hold Pulse Polarity.         0       = Active low         1       = Active low         1       = Active low         1       = Active low         1       = Active high         Line Synchronization Pulse Polarity.         0       = Active low         1       = Active logh         Video Handling Control Register.         4       0                                                                                                                                                                                                    | de<br>cle<br>bit<br>sp<br>AI<br>th<br>be<br>BLTC0, BLTC<br>BI<br>ar<br>nu<br>re<br>pr<br>ea<br>MODE0, MOI<br>MM<br>ar<br>re<br>ea |

| SVHC       | by progra<br>reserved<br>DISP<br>SNHP<br>PDWP<br>LSPP<br>Scanner<br>6 5<br>PASS INVER                                     | 4       3       2       1       0         4       3       2       1       0         1       LSPP       PDWP       SNHP       DISP         Scanner Discharge Pulse Polarity.         0       =       Active low         1       =       Active high         Sample and Hold Pulse Polarity.         0       =       Active low         1       =       Active high         Detector Window Polarity.         0       =       Active high         Line Synchronization Pulse Polarity (SLS).         0       =       Active high         Video Handling Control Register.         4       0       T         VDILS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | de<br>cle<br>bit<br>sp<br>Al<br>BLTCO, BLTC<br>BI<br>an<br>nu<br>re<br>mon<br>ea<br>MODEO, MOI<br>Mu<br>an<br>re<br>ea<br>15      |

| SVHC       | reserved<br>DISP<br>SNHP<br>PDWP<br>LSPP<br>Scanner<br>6 5                                                                | 4       3       2       1       0         4       3       2       1       0         1       LSPP       PDWP       SNHP       DISP         Scanner Discharge Pulse Polarity.         0       =       Active low         1       =       Active high         Sample and Hold Pulse Polarity.         0       =       Active high         Powe Polarity.         0       =       Active high         Powe Polarity.         0       =       Active high         Detector Window Polarity.         0       =       Active high         Line Synchronization Pulse Polarity         0       =       Active high         Line Synchronization Pulse Polarity         0       =       Active high         Video Handling Control Register.         4                                                                                                                                                                                                                                                                                                                                                                                | de<br>cle<br>bit<br>sp<br>Al<br>BLTCO, BLTC<br>BI<br>an<br>nu<br>re<br>mon<br>ea<br>MODEO, MOI<br>Mu<br>an<br>re<br>ea<br>15      |

| SVHC       | by progra<br>reserved<br>DISP<br>SNHP<br>PDWP<br>LSPP<br>Scanner<br>6 5<br>PASS INVER                                     | 4       3       2       1       0         LSPP       PDWP       SNHP       DISP         Scanner Discharge Pulse Polarity.         0       = Active low         1       = Active high         Sample and Hold Pulse Polarity.         0       = Active high         Detector Window Polarity.         0       = Active high         Peak Detector Window Polarity.         0       = Active high         Line Synchronization Pulse Polarity (SLS).         0       = Active low         1       = Active low         1 <td>de<br/>cla<br/>bit<br/>sp<br/>AE<br/>thi<br/>be<br/>BLTC0, BLTC<br/>BI<br/>an<br/>nu<br/>rea<br/>MODE0, MOE<br/>MODE0, MOE<br/>an<br/>rea</td> | de<br>cla<br>bit<br>sp<br>AE<br>thi<br>be<br>BLTC0, BLTC<br>BI<br>an<br>nu<br>rea<br>MODE0, MOE<br>MODE0, MOE<br>an<br>rea        |

| YPASS | The SBYPS input signal is selected        |

|-------|-------------------------------------------|

|       | by the pixel generator, and the com-      |

|       | parator output is ignored, if this bit is |

|       | set to 1.                                 |

#### **Controller DMA and Ports Support**

describes how to configure and program DMA nd 2 to function as internal channels. When so MA channels 0 and 2 provide the scanner conerence lines, and enable the scanner to output

#### ring DMA Channels 0 and 2 as Internal

DMA channels 0 and 2, of the NS32FX200, to ternal channels, perform the following opera-

- IA channel 0 as internal, by setting bit 4, the MCFG register to 1.

- inner signals SCLK, SDIS, SPDW and SLS as om the scanner controller module, by setting and 11 of the Port B Module Select (PBMS) 1.

- anner output signals by setting bit 0 of the Port Enable (PBEN) register to 1.

- H scanner signal as output from the scanner module by setting bit 2 of the Port C Module MS) register) to 1.

- scanners SNH signal as output by setting bit ort C Output Enable (PCEN) register to 1.

#### nming Internal DMA Channels 0 and 2 A2

evice Address Counters for DMA Channels and 2, respectively. Bits 0-23 hold the curnt address of the source data in the addressed vice. Bits 24-31 are reserved, and should be eared to 0. After each DMA transfer, if the ADA of the MODE0 register or MODE2 correonding register is set to 1, the corresponding DCA is updated as defined by the DEC bit in at MODE register. ADCA0 and ADCA2 should programmed to have even addresses.

#### 22

ock Length Counters for DMA Channels 0 d 2, respectively. Bits 0-23 hold the current mber of bytes to be transferred. Bits 24-31 are served, and should be cleared to 0. The approiate BLTC counter is decremented by 2 after ch DMA transfer.

#### DE2

ode Control Registers for DMA Channels 0 d 2, respectively. The appropriate MODE gister is used to specify the operating mode of ch channel.

|   |                                                             | ~  |     |                                                                             |     |     |     |     |  |

|---|-------------------------------------------------------------|----|-----|-----------------------------------------------------------------------------|-----|-----|-----|-----|--|

| 5 |                                                             | 10 | 9   | 8 4                                                                         | з   | 2   | 1   | 0   |  |

|   | reserved                                                    |    | ADA | reserved                                                                    | DIR | res | DEC | res |  |

|   | DEC Decrement/Increment the appro-<br>priate ADCA Register. |    |     |                                                                             |     |     |     |     |  |

|   |                                                             |    | 0 = | Increment ADC<br>after each transf<br>is set to 1.                          |     | ÷.  |     |     |  |

|   |                                                             |    | 1 = | Decrement ADCA0 or ADCA<br>after each transfer cycle, if AD<br>is set to 1. |     |     |     |     |  |

|                                                 | DIR                                                       | Transfer Direction. In MODE0 this                                                                                                                                                                    | 3.3.1 The | Signal Generation Block Registers                                                                                                                                  |

|-------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                 |                                                           | bit should be cleared to 0. Implied I/O is the destination. In MODE2 this bit should be set to 1. Implied I/O is                                                                                     | SPP       | = DF <sub>16</sub><br>A period pulse is issued every 5 ms (TSL = 255,63, 127 and 191).                                                                             |

|                                                 |                                                           | the source.                                                                                                                                                                                          | SPRES     | = 49                                                                                                                                                               |

|                                                 | ADA                                                       | <b>Device Address Control.</b> The ADA<br>bit controls updating of the corre-<br>sponding ADCA counter, after each<br>transfer cycle, as follows:                                                    | of fillo  | SPCLK = CTTL/(SPRES + 1) =<br>19.6608/(49 + 1) = 0.394 MHz = 394 kHz<br>CTTL/2(SPRES + 1) = 19.6608/2 (49 + 1)                                                     |

|                                                 |                                                           | 0 = Do not change the address                                                                                                                                                                        |           | = 0.197 MHz = 197 kHz                                                                                                                                              |

|                                                 |                                                           | stored in the relevant ADCA.<br>1 = Change the address stored in<br>the relevant ADCA.                                                                                                               | SLSD      | = 73<br>The delay from SPP is (SLSD + 3) CTTL cy-<br>cles, or 3.87 $\mu$ s.                                                                                        |

| STATO, S                                        | TAT2                                                      |                                                                                                                                                                                                      | SLSW      | = 49                                                                                                                                                               |

|                                                 | respectiv                                                 | egister for DMA Channels 0 and 2,<br>ely. These registers hold status infor-                                                                                                                         |           | The width of $\overline{SLS}$ is (SLSW $+$ 1) CTTL cycles, or 2.54 $\mu s.$                                                                                        |

|                                                 | and are us                                                | r DMA channels 0 and 2 respectively,<br>sed to enable or mask the appropriate<br>rrupt when the corresponding counter                                                                                | SDISD     | = 36<br>The delay from SCLK2 edge is (SDISD + 1)                                                                                                                   |

|                                                 |                                                           | , i.e., when the transfer is completed.                                                                                                                                                              | SDISW     | CTTL cycles, or 1.88 $\mu$ s.<br>= 12                                                                                                                              |

| 7<br>res                                        | 5<br>served                                               | 4         3         2         1         0           ETC         CHAC         reserved         TC                                                                                                     | 02.011    | The width of $\overline{\text{SDIS}}$ is (SDISW + 1) CTTL cycles, or 0.66 $\mu$ s.                                                                                 |

|                                                 | тс                                                        | <b>Terminal Count.</b> The appropriate TC is set to 1 when its corresponding                                                                                                                         | SNHD      | = 31<br>The delay from SCLK2 edge is (SNHD + 1)<br>CTTL cycles, or 1.63 $\mu$ s.                                                                                   |

|                                                 |                                                           | BLTC counter reaches 0, i.e., when the transfer is completed.                                                                                                                                        | SNHW      | = 3                                                                                                                                                                |

|                                                 | CHAC                                                      | <b>Channel Active.</b> The appropriate CHAC bit is set to 1 when DMA chan-                                                                                                                           |           | The width of SNH is (SNHW $+$ 1) CTTL cycles, or 0.20 $\mu s.$                                                                                                     |

|                                                 |                                                           | nel 0 or 2 is active, i.e., when the<br>CHEN bit in the corresponding CNTL<br>register is set to 1, and the corre-                                                                                   | SGC       | = 6<br>SDIS active low                                                                                                                                             |

|                                                 |                                                           | sponding BLTC counter is greater<br>than 0. CHAC is read only.                                                                                                                                       |           | SNH active high<br>SPDW active high                                                                                                                                |

|                                                 | ETC                                                       | Enable Terminal Count. ETC en-                                                                                                                                                                       |           | SLS active low                                                                                                                                                     |

|                                                 |                                                           | ables an interrupt when its corre-<br>sponding BLTC counter reaches 0.                                                                                                                               | SAVWD     | = 3<br>The delay in CTTL cycles from first SCLK2                                                                                                                   |