# MF2 Compatible Keyboard with COP8 Microcontrollers

#### ABSTRACT

This application note describes the implementation of an IBM MF2 compatible keyboard with National Semiconductor's COP888CL or COP943C/COP880CL microcontrollers. Two different solutions have been developed. One solution, suitable for laptop/notebook keyboards is based on the COP888CL with special power saving techniques. The other for most price competitive standard desktop keyboards is based on the COP943C/COP880C microcontrollers. The same principles can be applied to all types of keyboards or data input devices.

#### FEATURES

- Single chip solution

- · Low cost R/C or ceramic oscillator optional

- LED direct drive capability

- I/Os with software programmable on chip pull-ups

- Current saving M2CMOS technology

- Multi-input wakeup and HALT mode for further power consumption reduction (COP888CL only)

- · Software key rollover

- Schmitt triggers on keyboard data and clock lines

#### INTRODUCTION

The expression MF2 keyboard stands for multi-functional keyboard version 2. This type of keyboard was first developed and defined by IBM for use with all types of PC (XT,

National Semiconductor Application Note 734 Volker Soffel February 1991

MF2 Compatible Keyboard with COP8 Microcontrollers

AT, PS/2). In the meantime it has become an industry standard and today nearly all PCs have an MF2 compatible keyboard. As the name suggests, this keyboard features all operation modes which are necessary to stay compatible with the older XT and AT type keyboards. In the following chapters the features and functions of an MF2 keyboard as well as their implementation with a COP8 microcontroller are described.

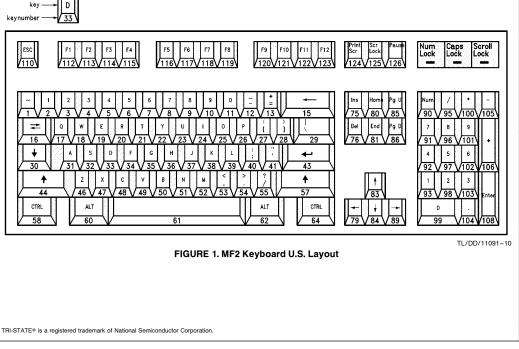

#### MF2 KEYBOARD KEY-LAYOUT

*Figure 1* shows the key layout of the U.S. version of an MF2 keyboard. Its outer appearance is characterized by 101 keys (102 for some countries), a separate cursor and numeric key pad, and 12 function keys in the upper row. The keyboard sends a "make" code if a key is depressed and a "break" code if the key is released. These make and break codes are independent of any country-specific keyboard layouts, which means they are independent of the symbols printed on the keys. These codes are solely determined by the physical position of a key on an MF2 keyboard is defined by its assigned key number, which is shown in *Figure 1*.

## HARDWARE

# Laptop/Notebook Keyboard With COP888CL

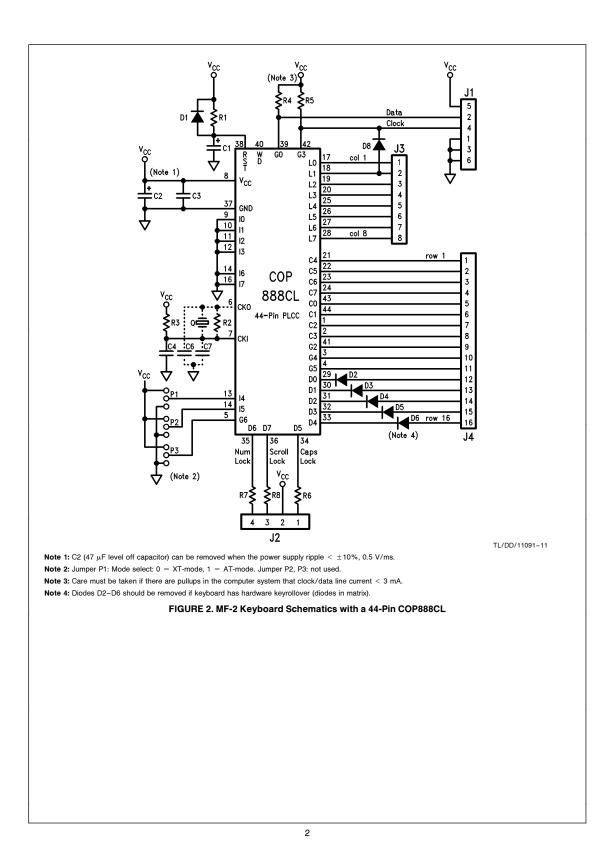

*Figure 2* shows the schematics of an MF2 keyboard with a COP888CL microcontroller. The G, C and L ports of the COP888CL are software programmable I/Os and can be programmed either as TRI-STATE® inputs, inputs with weak pull-up, push-pull output low, or push-pull output high.

© 1995 National Semiconductor Corporation TL/DD11091

RRD-B30M75/Printed in U. S. A

AN-734

The keyboard is organized as an 8 input by 16 output matrix. The COP888CL's L port is configured as a weak pull-up input port, thus allowing the use of the multi-input wakeup feature. Most of the time the chip is in the current saving HALT mode (Idd  $\leq$  10  $\mu$ A). Any keystroke or a data transmission from the computer will create a high to low transition on one of the L lines, which wakes up the  $\mu$ C from HALT mode. After returning from the HALT mode, the keyboard is scanned in order to detect which key is pressed and the appropriate key code is sent to the computer. This event-driven keyboard scanning results in lowest possible current consumption as HALT mode is even entered between successive single keystrokes. The diodes in the D-lines of the key matrix prevent a high current from being drawn. When two keys in the same column are pressed, two outputs could be potentially connected together: one of the D output lines, which is high and the polled line, which is pulled low. In this case, excessive current would be drawn without the protection diodes. These diodes can be omitted if the keyboard already has decoupling diodes in its matrix (hardware key rollover). All other matrix lines source current in the µA range and there is no need for current limiting diodes.

The G0 and G3 pins are used for the keyboard data and clock lines. The pull-ups on these lines ensure a defined logic "1" level. The keyboard interface on the computer side uses open collector drivers and the G0, G3 pins of the COP888CL are configured as TRI-STATE (Hi–Z) inputs when a "1" is written to the data or clock line. To output a logic "0" the  $\mu$ C pulls the data or clock line low (push-pull low output). A maximum current of 3 mA can be sunk into the data and clock pins. Schmitt triggers on the data are clock line inputs reduce the risk of errors in the data received by the keyboard.

The microcontroller provides the option of using a low cost R/C oscillator with frequency variation tight enough to fulfill the requirements for a keyboard, in addition to the option of using a crystal or a ceramic clock.

The XT or AT/PS-2 operation mode can be selected via a hardware switch. Additional inputs for customer specific settings are available.

The three LEDs of an MF2 keyboard are driven directly by three of the COP888CL's high sink D-lines (max. 15 mA for each pin), thus eliminating the need for additional LED drivers or transistors.

The keyboard logic generates a Power-On Reset (POR) signal when the power is first applied to the keyboard. After POR the keyboard performs the Basic Assurance Test (BAT). The BAT consists of a keyboard controller self-test. During the BAT, any activity on the data and clock lines is ignored. The 3 keyboard LEDs are turned on at the beginning and turned off at the end of the BAT. Upon satisfactory completion of the BAT, the keyboard sends the BAT completion code (hex AA) to the computer and keyboard scanning begins. Any code other than hex AA is interpreted by the computer as a BAT error.

## Desktop Keyboard with COP943C or COP880C

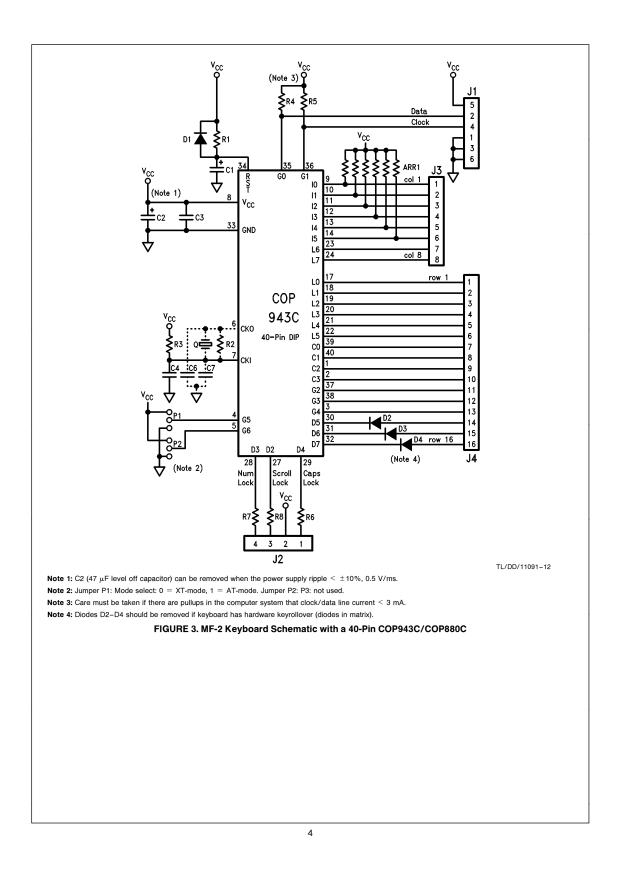

*Figure 3* shows the schematic for an MF2 keyboard with the COP943C/COP880C. The only difference compared to COP888CL solution is that the COP943C/COP880C microcontrollers do not have the multi-input wakeup feature, which allows an event driven keyboard scanning. The key matrix is therefore continuously scanned in a loop. With the COP943C/COP880C solution a part of the I port is used as the key matrix input. The I port is a TRI-STATE (Hi–Z) input port (requires external pull-ups).

# **Key Matrix Organization**

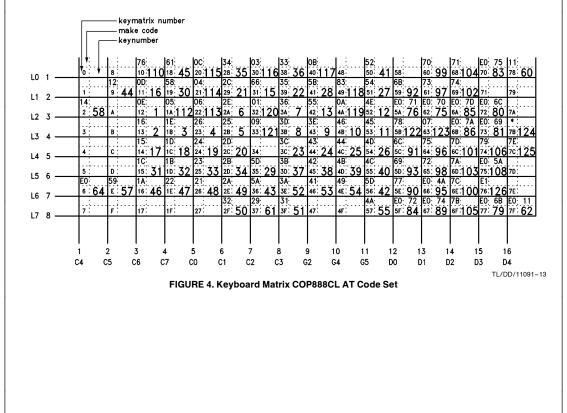

*Figure 4* shows an example of what an MF2 keyswitch matrix could look like. Each key position in the matrix is marked with its key number.

For example: Key number "58" is located at the key matrix position number "2" and has the AT-set make code "14

Hex". Looking at *Figure 1*, one can see that key number "58" belongs to the left "CNTRL" key. Note that the "SHIFT", "CNTRL" and "ALT" keys are located in their own matrix lines, separate from all other keys. The reasons for that will be explained in the chapter "Software Key Rollover".

## **Code Sets**

The MF2 keyboard supports 3 different sets of make and break codes. Code set 1 is used for XT/PC and PS/2-30 compatible computers. Code set 2 is used for AT and all other PS/2 models compatible computers and code set 3 is used for workstations and terminal emulations on the PC. The country specific keyboard driver on the PC side converts the "key position" codes from the keyboard into the ASCII codes that correspond to the characters printed on the keycaps (as long as the right driver is installed on the PC). Appendix 1 gives a complete overview of the key numbers and their make and break codes for all 3 code sets. The symbols of the U.S. keyboard layout are only listed for reference and are different for other country layouts. The break code for code set 1 is equal to the make code with the most significant bit set. The make codes preceded with a "F0 Hex" code give the break codes of code sets 2 and 3.

# **KEYBOARD SOFTWARE**

The software of the keyboard microcontroller can be subdivided into the following five main tasks:

- · key detection

- software key rollover

- key decoding and encoding

- keycode transmission

- · keyboard command set

#### **Key Detection**

Key detection is done by scanning the keyboard matrix in the following way. Sequentially each of the 16 matrix output lines are pulled low, while all the others are high. The 8 matrix input lines are read and the 8-bit input value is compared with the result of the previous scanning of the same matrix output line (a history of the previous scan is kept in the  $\mu$ C's RAM). Thus the keyboard microcontroller's key detection routine detects any key change in that matrix output line (key pressed or released) since the previous scan. It is important to recognize released keys, as the MF2 keyboard not only sends a key's "make" code when the key is pressed, but also a key's "break" code when the key is released. Key debouncing is performed by software by making sure that the time between two scans is bigger than the key bounce time (typically 8 ms).

## Software Key Rollover

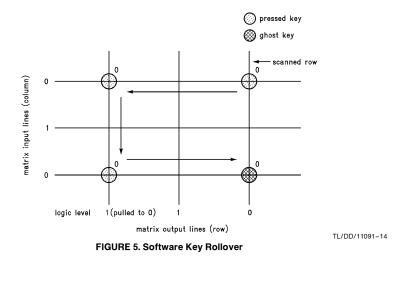

Software key rollover means that no decoupoing diodes are used in the key switch matrix. However, the keyboard action is still N key rollover in nature. That is, if N keys are depressd in some sequence and held down, the make code of these keys is transmitted in that sequence. However, if three keys from three corners of a rectangle in the key switching matrix are depressed, a "ghost" key (a key which is not really pressed) would be created (see Figure 5). To prevent this, a special algorithm, which checks for such special key combinations, has been implemented into the keyboard software. If a "ghost" key has been detected the keyboard outputs the "key detection error code" and the N key rollover reverts to a 2 key rollover. To ensure that all 3-key combinations used on a PC (e.g., CNTRL+ALT+DEL) are still possible, keyboard manufacturers using this method organize the key switch matrix accordingly (an example is given in Figure 4).

SOFTWARE KEY ROLLOVER ;LENGTHC: COUNTER FOR NO. OF BYTES (15 FOR A 16 BY 8 MATRIX) WHICH HAVE TO BE COMPARED WITH THE ACTUAL SCANNED BYTE. ;LASTSCN: RAM LOCATION WHICH CONTAINS THE RESULT OF THE ACTUAL SCANNED LINE ;PNTSCAN: RAM LOCATION WHICH CONTAINS A POINTER TO THE RAM CELL IN THE SCAN HISTORY TABLE THAT STORES THE RESULT OF THE PREVIOUS SCAN FOR THE ACTUAL SCANNED MATRIX LINE ;SCNLOT: START ADRESS OF THE RAM SCAN HISTORY TABLE (16 BYTES) ;MATLEN: MATRIX LENGTH (IN THIS CASE MATLEN=16dec) SHIFT COUNTER FOR BYTE SHIFT RAM ADRESS OF TYPEMATIC RATE SAVE REGISTER ;BITC : ;TYPSAV: ;TYPST : RAM ADRESS FOR TYPEMATIC RATE VALUE ;STATUS: RAM ADRESS OF GENERAL STATUS FLAG REGISTER ;STAT2 : RAM ADRESS OF GENERAL STATUS FLAG REGISTER 2 ;TYPCO1: RAM ADRESS OF REGISTER THAT CONTAINS TYPEMATIC KEY MAKE CODE ;SCNCNT: SCAN COUNTER FOR 16 MATRIX LINES ; ; .LOCAL KEYROL: LD LENGTHC, #00F ;LOAD TABLE LENGTH COUNTER ; POINT TO RAM LOCATION WHERE LD X,#LASTSCN ; RESULT OF PREVIOUS SCAN IS ; STORED LDA, PNTSCAN ;LOAD POINTER TO ACTUAL SCAN ;LINE INC Α ; POINT TO THE NEXT SCAN LINE Х A,B \$NEXTB: IFBNE #((SCNLOT+MATLEN)&00F) ;IF END OF HISTORY SCANTABLE ; IN RAM NOT REACHED ; THEN OK JP \$1 LDB, #SCNLOT ;ELSE POINT TO BEGINNING OF TABLE \$1: LDA, [X] ; COMPARE NEW SCANNED MATRIX LINE ;WITH ALL OTHER PREVIOUS SCANNED OR A,[B] ;BYTES IN TABLE IFEQ A,#OFF ; IF NO KEYS PRESSED IN ;SAME INPUT LINE JP \$INCB ; THEN COMPARE WITH NEXT BYTE ; IN SCAN TABLE ;ELSE LOOK IF MORE THAN ; TWO KEYS ARE PRESSED ; IN ONE OF THE TWO ;COMPARED BYTES ;LOAD 1ST OF COMP.BYTES LDA, [X] TL/DD/11091-1

| <b>A</b> 6 <b>A</b>  | LD          | BITC,#08                                | ;LOAD BIT COUNTER                                           |               |

|----------------------|-------------|-----------------------------------------|-------------------------------------------------------------|---------------|

| \$ZERO1:             | RRC         | А                                       |                                                             |               |

|                      | IFNC<br>JP  | \$ZERO3                                 | ;IF 1 KEY PRESSED<br>;THEN TEST IF 2ND                      |               |

|                      |             |                                         | ;KEY IS PRESSED                                             |               |

|                      | DRSZ<br>JP  | BITC<br>\$ZERO1                         | ;IF NOT ALL BITS CHECKED<br>;THEN CONTINUE CHECK            |               |

|                      | JP          | \$INCB                                  | ,                                                           |               |

| \$ZERO2:             |             |                                         |                                                             |               |

|                      | RRC<br>IFNC | А                                       | ; IF 2ND KEY PRESSED                                        |               |

| 4 4.0                | JP          | \$ENDLP                                 | ;THEN ERROR: "GHOST KEY"                                    |               |

| \$ZERO3:             | DRSZ<br>JP  | BITC<br>\$ZERO2                         | ;IF NOT ALL BITS CHECKED<br>;THEN CONTINUE CHECK            |               |

| \$INCB:              | TD          |                                         |                                                             |               |

|                      | LD<br>DRSZ  | A, [B+]<br>LENGTHC                      | ;INC B<br>;IF NEW SCANNED MATRIX LINE                       |               |

|                      |             |                                         | ;NOT COMPARED WITH ALL OTHER<br>;BYTES IN TABLE             |               |

|                      | JP          | \$NEXTB                                 | ;THEN COMP. WITH NEXT                                       |               |

|                      | SC          |                                         | ;BYTE IN TABLE<br>;IF ALL COMPARED, SET NO ERROR            |               |

| <b>A</b> -11-1-1-1-1 | 50          |                                         | ;FLAG                                                       |               |

| \$ENDLP:             | LD          | b,#STAT2                                | ;POINT TO STATUS FLAG REGISTER                              |               |

|                      | IFNC<br>JP  | \$ERROR                                 | ;ERROR DURING THIS SCAN?<br>;YES, DO ERROR PROCEDURE        |               |

|                      |             | ERR2, [B]                               | ;ERROR DURING PREVIOUS SCANS,                               |               |

|                      |             |                                         | ;BUT NO ERROR DURING THIS ;SCAN?                            |               |

|                      | JP          | \$RESTORE                               | ;YES, RESTORE TYPEMATIC RATE                                |               |

|                      | RET         |                                         |                                                             |               |

| \$RESTOR             | E:<br>RBIT  | ERR2,[B]                                |                                                             |               |

|                      | JSR         | TSTOP                                   | ;STOP TYPEMATIC TIMER                                       |               |

|                      | LD<br>X     | A, TYPSAV<br>A, TYPST                   | ;LOAD SAVED TYPEMATIC VALUE<br>;RESTORE OLD TYPEMATIC VALUE |               |

|                      | RET         |                                         | ;NO ERROR DURING THIS SCAN:                                 |               |

|                      |             |                                         | ;RETURN                                                     |               |

| \$ERROR:             | IFBIT       | ERR2,[B]                                | ; IF ERROR OCURRED ALREADY                                  |               |

|                      |             | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ;DURING PREVIOUS SCAN                                       |               |

|                      | JP<br>SBIT  | \$ERREND<br>ERR2,[B]                    | ;THEN DO NOTHING<br>;ELSE SET PREVIOUS ERROR FLAG           |               |

|                      | LD          | B, #TYPST                               | ; POINT TO TYPEMATIC VALUE                                  |               |

|                      | LD          | A,[B]                                   | ;REGISTER                                                   |               |

|                      | X<br>LD     | A, TYPSAV<br>[B], #07F                  | ;SAVE TYPEMATIC RATE/DELAY<br>;SET TYPEMATIC TO 1s DELAY,   |               |

|                      | ЦU          | [b] <b>,</b> #0/r                       | ;2 CHARACTERS/s FOR ERROR CODE                              |               |

|                      |             |                                         |                                                             | TL/DD/11091-2 |

|                      |             |                                         |                                                             |               |

|                      |             |                                         |                                                             |               |

|                      |             |                                         |                                                             |               |

|                      |             |                                         |                                                             |               |

|                      |             |                                         |                                                             |               |

; REPETITION LDA,#000 ; IF SET2, 3 ERROR CODE 00 ; POINT TO STATUS FLAG REGISTER LDB, #STATUS SET1,[B] IFBIT LDA,#OFF ;ELSE ERROR CODE FF Х A, TYPCO1 ;PUT IN TYPEMATIC BUFFER JSR TSTART ; INIT & START TYPEMATIC TIMER \$ERREND: LD A, SCNCNT ; INCREMENT SCAN COUNTER INCA х A, SCNCNT RETSK ;RET AND SKIP FOR ROLLOVER ERROR .LOCAL .END

## Key Decoding and Encoding

After detection of a key change (pressing or releasing a key), the software first has to determine the physical location of the key in the key matrix. This decoding process is done by calculating an internal key number out of the key matrix column and row position of the changed key. At the same time, it is determined if the key has been pressed or released. A pressed or released key is then signaled by setting or resetting a "key down" flag in RAM. The internal key number and the "key down" status flag are the input parameters to the key encoding procedure. The internal key number is used to get the "make" code for the key out of a ROM look-up table, which has been matched to the physical matrix organization of the keyboard. If the "key down" flag is reset (key is released) the software calculates the key "break" code out of the previously fetched key "make" code. In this way, each pressed or released key is encoded with its appropriate "make" or "break" code, which is then written to the keyboard controllers 16 byte output buffer (FIFO) until the computer interface is ready to receive it. Before writing to the FIFO the software checks whether there is still enough capacity to store the key code.

#### **Key Repetition**

All keys are typematic (repetitive) by default. That means when a key is pressed and held down, the  $\mu$ C continues to send the "make" code for that key until it is released. When two or more keys are held down, only the code for the last key pressed is repeated. Typematic operation will stop

TL/DD/11091-3

when this key is released, even if other keys are still held down.

The default values for typematic operation are:

delay time = 500 ms

repetition rate = 10 characters/second,

where the delay time is the time which is inserted before a character is repeated for the first time.

## **Operating Protocol**

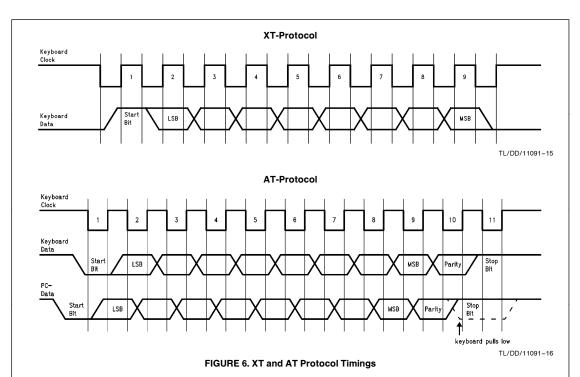

There are two different transmission protocols for an MF2 keyboard: the AT transmission protocol and the XT transmission protocol. Data transmission to and from the keyboard is synchronous serial, the data format for the XT mode is:

9 bits in length

1 start bit (high)

8 data bits (LSB first)

The data format for AT and PS/2 modes is:

- 11 bits in length

- 1 start bit (low)

- 8 data bits (LSB first)

- 1 parity bit (odd)

- 1 stop bit (high)

If no data is transmitted, both data and clock lines are in the high state. The clock signal is always provided by the keyboard. *Figure 6* shows the XT and the AT protocol timings.

#### Keyboard Data Transmission in XT Format

At the falling edge of the clock, the start bit (high) is shifted out, followed by the 8 data bits (least significant bit first). Data is valid on the rising edge of the clock and changes after the falling edge of the clock.

## Keyboard Data Transmission in AT Format

Before sending data, the keyboard monitors the clock and data lines. If the clock line is low, then the keyboard is disabled by the computer and no data is transmitted. The microcontroller continues to scan the keyboard and stores key data in its output buffer. If the data line is low, while the clock line is high, the computer requests to send and the keyboard goes into receive mode. The keyboard is only allowed to transmit data when both data and clock lines are high.

The keyboard pulls the data line low (start bit) and starts the clock. The 8 data bits (least significant bit first) are shifted out, followed by the parity (odd) and stop bit (high). Data is valid after the falling edge of the clock and changes after the rising edge of the clock. If no data is transmitted both data and clock lines are high. If the computer pulls the clock line low for at least 60  $\mu$ s before the 10th bit is transmitted, the keyboard stops transmission and stores the aborted data in its output buffer.

SENDBY: SEND BYTE TO COMPUTER ; INPUT PARAMETER: ;BYTSEN: RAM LOCATION CONTAINING THE BYTE TO BE TRANSMITTED ; ;OUTPUT: DATSEN FLAG IN STATUS REGISTER ; 1=BYTE SENT, 0=BYTE NOT SENT ; PARCNT: PARITY COUNTER REGISTER ;BITC : DATA LENGTH COUNTER FOR TRANSMISSION LOOP ;CLOCK HIGH TIME (=CLOCK LOW TIME) = 40us ;AT 3.58MHz CLOCK (INSTR. CYCLE = 2.79us) ;DATA REGISTER OF PORT G DATA AND CLOCK LINES IS ;PRESET WITH "0" .LOCAL SendBy: ;POINT TO STATUS FLAG REGISTER B,#STATUS LD;RESET "BYTE SEND" FLAG RBIT DatSen,[B] ;LOAD BYTE TO SEND LDA,BytSen ;DATA LENGTH LD BITC,#009 ;IF XT MODE IFBIT PCXT, [B] ; THEN JUMP TO XT ; SEND ROUTINE PCMode JMP ;ELSE SEND AT PROTOCOL \$ATSEND: LD PARCNT, #10 ;LOAD PARITY COUNTER ; POINT TO GPORT INPUT B, #PORTGP LD;REGISTER WAITS: TL/DD/11091-4

|          | TDDTO                                    |                                                            |                                                                                              |  |

|----------|------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|

|          | IFBIT<br>JP<br>JP                        | ClockL,[B]<br>\$ClocOK<br>WAITS                            | ;IF CLOCKLINE HIGH<br>;THEN OK<br>;ELSE KEYBOARD DISABLED:<br>;WAIT                          |  |

| \$ClocOK | :<br>IFBIT<br>JP<br>RET                  | DataLn,[B]<br>\$DataOK                                     | ;IF DATALINE IS HIGH<br>;THEN OK<br>;ELSE PC SENDS DATA:<br>;RETURN (GOTO RECEIVE)           |  |

| \$DataOK | :                                        |                                                            |                                                                                              |  |

|          | LD<br>RC                                 | B, #PORTGC                                                 | ;POINT TO PORT G CONFIGURATION<br>;REGISTER<br>;STARTBIT = 0                                 |  |

| \$SendBt |                                          | ClockL,PORTGP<br>\$ClockH                                  | ;SET CLOCKLINE HIGH (TRI-STATE)                                                              |  |

| \$ClockH | :                                        |                                                            |                                                                                              |  |

|          | IFC<br>JP<br>SBIT<br>JP                  | \$DATHI<br>DataLn,[B]<br>\$CLKLOW                          | ;IF BIT TO TRANSMIT = "1"<br>;THEN DATALINE HIGH<br>;ELSE DATALINE LOW<br>;SET CLOCKLINE LOW |  |

| \$DATHI: | RBIT                                     | DataLn,[B]                                                 | ;SET DATALINE HIGH (TRI-STATE)                                                               |  |

| \$CLKLOW | :                                        |                                                            |                                                                                              |  |

|          | SBIT<br>IFC<br>DRSZ<br>RRC<br>NOP        | ClockL,[B]<br>PARCNT<br>A                                  | ;SET CLOCKLINE LOW<br>;IF BIT=1<br>;THEN DECR. PARITY COUNTER<br>;SHIFT NEXT BIT INTO CARRY  |  |

| \$PARITY | DRSZ<br>JP                               | BITC<br>\$SendBt                                           | ;IF NOT ALL BITS SENT<br>;THEN TRANSMIT NEXT BIT<br>;SEND PARITY BIT<br>;DELAY               |  |

|          | NOP<br>RBIT<br>IFBIT<br>JP<br>RBIT<br>JP | ClockL,[B]<br>00,PARCNT<br>\$DLOW<br>DataLn,[B]<br>\$CLKL2 | ;SET CLOCKLINE HIGH<br>;IF NUMBER OF "1" = ODD<br>;THEN PARITY = 0<br>;ELSE PARITY = 1       |  |

| \$DLOW:  | SBIT<br>NOP                              | DataLn,[B]                                                 | ;SET DATALINE LOW                                                                            |  |

|          | NOL                                      |                                                            |                                                                                              |  |

|                         | NOP<br>SBIT<br>JSR                                           | ClockL,[B]<br>DEL12                        | ;SET CLOCKLINE LOW<br>;INSERT DELAY 12 INSTR. CYCLES                                                                                           |               |

|-------------------------|--------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|                         | RBIT                                                         | ClockL,[B]                                 | ;SET CLOCKLINE HIGH                                                                                                                            |               |

| \$ENDSB:                | RBIT<br>JSR<br>SBIT<br>JSR                                   | DataLn,[B]<br>DEL11<br>Clockl,[B]<br>DEL12 | ;TRANSMIT STOP BIT<br>;SET DATA LINE HIGH (STOP BIT)<br>;INSERT DELAY 11 INSTR. CYCLES<br>;SET CLOCKLINE LOW<br>;INSERT DELAY 12 INSTR. CYCLES |               |

| ζΕΝΟ3Β.                 | RBIT<br>RBIT<br>LD<br>SBIT                                   | DATALN, [B]<br>B,#STATUS                   | ;SET CLOCKLINE HIGH<br>;DATA HIGH (XT MODE)<br>;POINT TO STATUS FLAG REG.<br>;SET DATA SENT FLAG                                               |               |

|                         | LD<br>IFEQ                                                   | A,BYTSEN<br>A,#0FE                         | ; IF SENT BYTE = RESEND                                                                                                                        |               |

|                         | RET<br>X                                                     | A, SENBYT                                  | ;COMMAND<br>;THEN DON'T SAVE<br>;ELSE SAVE LAST SENT BYTE<br>;IN SENBYT IN CASE PC ASKS                                                        |               |

|                         | RET                                                          |                                            | ;KEYBOARD TO RESEND                                                                                                                            |               |

| ;XT TRAN<br>PCMode:     | NSMISSIO                                                     | N PROTOCOL                                 |                                                                                                                                                |               |

|                         | IFBIT<br>JP<br>JMP                                           | CLOCKL,PORTGP<br>\$PCSND<br>POWRUP         | ;CLOCKLINE HIGH?<br>;YES,START TO SEND<br>;ELSE RESET                                                                                          |               |

| \$PCSND:                | LD<br>SBIT<br>SC                                             | B, #PORTGC<br>DATALN, [B]                  | ;DATA LINE LOW BEFORE<br>;START TO SEND<br>;START BIT = 1                                                                                      |               |

| \$PCSEND                | :                                                            |                                            |                                                                                                                                                |               |

|                         | SBIT<br>IFC<br>JP<br>SBIT<br>NOP<br>NOP<br>NOP<br>NOP<br>NOP | ClockL,[B]<br>\$DATH2<br>DataLn,[B]        | ;CLOCKLINE LOW<br>;IF BIT TO SEND=1<br>;THEN SET DATALINE HIGH<br>;ELSE SET DATALINE LOW<br>;DELAY                                             |               |

| \$DATH2:                | JP                                                           | \$CLKHI                                    |                                                                                                                                                |               |

| <i><b>YD11112</b></i> . | RBIT<br>IFBIT<br>JP                                          | DataLn,[B]<br>DATALN,PORTGP<br>\$CLKHI     | ;SET DATALINE HIGH<br>;IF DATALINE HIGH<br>;THEN OK                                                                                            |               |

|                         | RBIT                                                         | CLOCKL, [B]                                | ;ELSE KEYBOARD DISABLED<br>;CLOCKLINE HIGH                                                                                                     | TL/DD/11091-6 |

|                         |                                                              |                                            |                                                                                                                                                |               |

|                         |                                                              |                                            |                                                                                                                                                |               |

|                         |                                                              |                                            |                                                                                                                                                |               |

| \$CLKHI: | RET                                     |                                                                   | ;STOP TO SEND                                                     |               |

|----------|-----------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|---------------|

|          | RBIT<br>RRC                             | ClockL,[B]<br>A                                                   | ;SET CLOCKLINE HIGH<br>;SHIFT NEXT BIT TO TRANSMIT<br>;INTO CARRY |               |

|          | NOP<br>NOP<br>NOP<br>NOP                |                                                                   | ; DELAY                                                           |               |

| \$PCOK:  | DRSZ<br>JP<br>SBIT<br>SBIT<br>JSR<br>JP | BITC<br>\$PCSEND<br>CLOCKL,[B]<br>DATALN,[B]<br>DELAYD<br>\$ENDSB | •                                                                 |               |

|          | NOP<br>NOP<br>RET<br>.LOCAL<br>.END     |                                                                   |                                                                   |               |

|          |                                         |                                                                   |                                                                   | TL/DD/11091-7 |

## **Keyboard Receives Data**

The keyboard can only receive data from the computer in AT-PS/2 mode. The computer pulls the data line low (start bit) after which the keyboard starts to shift out 11 clock pulses within 15 ms. Transmission has to be completed within 2 ms. Data from the computer changes after the falling edge of the clock and is valid before the rising edge of

the clock. After the start bit, 8 data bits (least significant bit first), followed by the parity bit (odd) and the stop bit (high) are shifted out by the computer with the clock signal provided by the keyboard. The keyboard pulls the stop bit low in order to acknowledge the receipt of the data. If a transmission error occurred (parity error or similar) the keyboard is sues the "RESEND" command to the PC.

; ; RECDAT: RECEIVE DATA COMMING FROM PC ;RETURN, IF PARITY ERROR ;RETURN SKIP , IF BYTE WAS RECEIVED ;WITHOUT ERROR ; BTRECV: RAM LOCATION CONTAINING THE RECEIVED BYTE ; ; ;BITC : RECEIVE LOOP COUNTER REGISTER ;PARCNT: PARITY COUNTER REGISTER : RecDat: CLRA ;B POINT TO PORT G B, #PORTGC LD ; CONFIGURATION ;X POINT TO RECEIVED BYTE X, #BTRECV LD ;RAM CELL PARCNT, #10 ;LOAD PARITY COUNTER LD;LOAD RECEIVE LOOP COUNTER BITC, #009 LD;(8 DATABITS + 1 PARITY BIT) ;START BIT= "0" RC RdByte: SBIT ClockL, [B] ;SET CLOCKLINE LOW ; (CLOCK IN START BIT) ; IF "1"-BIT RECEIVED IFC ; THEN DECR. PARITY COUNTER DRSZ PARCNT ;SHIFT CARRY TO BIT 7 OF ACCU RRC Α Х A,[X] ;STORE RECEIVED BYTE A,[X] ; RESTORE AS LONG AS NOT LD ;FULL BYTE RECEIVED ;SET CLOCKLINE HIGH RBIT ClockL,[B] ;READ IN RECEIVED BIT ;RECEIVED BIT= "0" RC ; IF DATALINE = "1" IFBIT DataLn, PORTGP ;THEN RECEIVED BIT= "1" SC DRSZ BITC ;9 BITS RECEIVED? RdByte ;NO,LOOP JP ;CLOCK LOW PULSE AFTER PARITY HAS BEEN RECEIVED ClockL,[B] ;SET CLOCKLINE LOW SBIT DELAYD ; INSERT 10 INSTR. CYCLES DELAY JSR RBIT ClockL, [B] ;SET CLOCKLINE HIGH ;PC SENDS STOP BIT ;PULL STOP BIT LOW SBIT DataLn,[B] TL/DD/11091-8

| ;CLOCK 1           |                          | , [_]                 | ;TO ACKNOWLEDGE RECEIPT OF BYTE<br>;INSERT DELAY<br>EDGE FOR PC)<br>;SET CLOCKLINE LOW<br>;INSERT DELAY<br>;SET CLOCKLINE HIGH |

|--------------------|--------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|

|                    | RBIT                     | DataLn,[B]            | ;RETURN DATA TO HIGH                                                                                                           |

| ;PARITY<br>ParOne: |                          | 00,PARCNT<br>PARO     | ; IF NO. OF RECEIVED DATA "1"=ODD<br>;THEN PARITY BIT MUST BE "0"<br>;ELSE PARITY BIT MUST BE "1"                              |

|                    | IFC<br>RETSK<br>JP       | PARERR                | ;IF RECEIVED PARITY BIT=1<br>;THEN OK,RETURN SKIP<br>;ELSE PARITY ERROR                                                        |

| PAR0:              | IFNC<br>RETSK            |                       | ;IF RECEIVED PARITY BIT =0<br>;THEN OK,RETURN SKIP<br>;ELSE PARITY ERROR                                                       |

| ParErr:            | LD<br>JSR<br>RET<br>.END | BytSen,#0FE<br>SByWPo | ;LOAD "RESEND" CODE<br>;SEND RESEND CODE TO PC<br>;ERROR,RETURN                                                                |

**Commands from the Computer**

The following table shows the commands and their hexadecimal values the computer may send to the keyboard. Only AT-PS/2 compatible computers can send commands to the keyboard and the keyboard can only receive the commands when operated in the AT-mode.

The commands can be sent to the keyboard at any time. The keyboard responds within 20 ms to any valid transmission with ACK (FA Hex), except for the ECHO command where the keyboard responds with EE Hex, the RESEND command and the reserved commands.

| Command                   | Hex Value |

|---------------------------|-----------|

| Set/Reset Mode Indicators | ED        |

| Echo                      | EE        |

| Reserved                  | EF        |

| Select Alternate Code Set | F0        |

| Reserved                  | F1        |

| Read Keyboard ID          | F2        |

| Set Typematic Rate/Delay  | F3        |

| Enable                    | F4        |

| Default Disable           | F5        |

| Set Default               | F6        |

| Set All Keys              |           |

| Typematic/No Break        | F7        |

| Make/Break/No Typematic   | F8        |

| Make/No Typematic         | F9        |

| Typem./Make/Br.           | FA        |

| Set Key Type              |           |

| Typematic/No Break        | FB        |

| Make/Break/No Typematic   | FC        |

| Make/No Typematic         | FD        |

| Resend                    | FE        |

| Reset                     | FF        |

In the XT mode the keyboard only accepts the RESET command, which is assumed when the computer pulls the clock line low for at least 10 ms.

TL/DD/11091-9

## Commands to the Computer

The following table shows the commands and their hexadecimal values the keyboard may send to the system.

| Command              | Hex Value           |

|----------------------|---------------------|

| Key Detection Error/ | 00                  |

| Buffer Overrun       | (Code Sets 2 and 3) |

| Keyboard ID          | 83AB                |

| BAT Completion Code  | AA                  |

| BAT Failure Code     | FC                  |

| Echo                 | EE                  |

| Acknowledge          | FA                  |

| Resend               | FE                  |

| Key Detection Error/ | FF                  |

| Buffer Overrun       | (Code Set 1)        |

# SUMMARY

When using National Semiconductor's microcontroller to implement the functions of an MF2 keyboard, very few external components are necessary. Figure 2 shows the complete schematic of an MF2 keyboard based on the COP888CL. The implementation of software key rollover eliminates the need for decoupling diodes in the 16 by 8 key matrix. LED direct drive capability of the COP8 and a RC oscillator with tolerances tight enough to meet the requirements for a keyboard further reduce component count and price. Schmitt triggers on the ports used for the keyboards data and clock lines add additional security against transmission errors. Where low power consumption is the most important design factor (e.g., laptop or notebook computers) the COP8's M2CMOS technology and the multi-input wakeup feature offer a remarkable improvement over the NMOS controllers used in most of today's existing solutions.

National Semiconductor offers three chips tailored for the needs of a keyboard designer. Starting with the most price competitive 2.5k ROM device COP943C, an upgrade path is provided with the COP880C to 4k ROM. Both devices are intended for the use in standard MF2 desktop keyboards. The COP888CL is ideally suited for notebook or lap-

top keyboards, as it has special power saving features. The complete software for an MF2 keyboard as well as complete demo keyboards and keyboard evaluation boards for the COP888CL and COP943C/COP880C microcontrollers are available. Contact National Semiconductor's  $\mu C$  marketing or applications for further information.

| Ke  | y Position<br>and |      | ble I<br>PS/2 30) |      | ole II<br>/2 50, 60, 80) |      | Table III<br>ninal MODE) |

|-----|-------------------|------|-------------------|------|--------------------------|------|--------------------------|

| 9   | Symbol            | Make | Break             | Make | Break                    | Code | Туре                     |

| 01  | ~                 | 29   | A9                | 0E   | F0-0E                    | 0E   | Typematic                |

| 02  | ! 1               | 02   | 82                | 16   | F0-16                    | 16   | Typematic                |

| 03  | @ 2               | 03   | 83                | 1E   | F0-1E                    | 1E   | Typematic                |

| 04  | # 3               | 04   | 84                | 26   | F0-26                    | 26   | Typematic                |

| 05  | \$ 4              | 05   | 85                | 25   | F0-25                    | 25   | Typematic                |

| 06  | % 5               | 06   | 86                | 2E   | F0-2E                    | 2E   | Typematic                |

| 07  | ∧ 6               | 07   | 87                | 36   | F0-36                    | 36   | Typematic                |

| 08  | & 7               | 08   | 88                | 3D   | F0-3D                    | 3D   | Typematic                |

| 09  | * 8               | 09   | 89                | 3E   | F0-3E                    | 3E   | Typematic                |

| 10  | ( 9               | 0A   | 8A                | 46   | F0-46                    | 46   | Typematic                |

| 11  | ) 0               | 0B   | 8B                | 45   | F0-45                    | 45   | Typematic                |

| 12  |                   | 0C   | 8C                | 4E   | F0-4E                    | 4E   | Typematic                |

| 13  | + =               | 0D   | 8D                | 55   | F0-55                    | 55   | Typematic                |

| 15  | B.S. ←            | 0E   | 8E                | 66   | F0-66                    | 66   | Typematic                |

| 16  | TAB               | 0F   | 8F                | 0D   | F0-0D                    | 0D   | Typematic                |

| 17  | Q                 | 10   | 90                | 15   | F0-15                    | 15   | Typematic                |

| 18  | w                 | 11   | 91                | 1D   | F0-1D                    | 1D   | Typematic                |

| 19  | E                 | 12   | 92                | 24   | F0-24                    | 24   | Typematic                |

| 20  | R                 | 13   | 93                | 2D   | F0-2D                    | 2D   | Typematic                |

| 21  | Т                 | 14   | 94                | 2C   | F0-2C                    | 2C   | Typematic                |

| 22  | Y                 | 15   | 95                | 35   | F0-35                    | 35   | Typematic                |

| 23  | U                 | 16   | 96                | 3C   | F0-3C                    | 3C   | Typematic                |

| 24  | I                 | 17   | 97                | 43   | F0-43                    | 43   | Typematic                |

| 25  | 0                 | 18   | 98                | 44   | F0-44                    | 44   | Typematic                |

| 26  | Р                 | 19   | 99                | 4D   | F0-4D                    | 4D   | Typematic                |

| 27  | ] }               | 1A   | 9A                | 54   | F0-54                    | 54   | Typematic                |

| 28  | } ]               | 1B   | 9B                | 5B   | F0-5B                    | 5B   | Typematic                |

| 29* | \                 | 2B   | AB                | 5D   | F0-5D                    | 5C   | Typematic                |

| 30  | Caps Lk           | ЗA   | BA                | 58   | F0-58                    | 14   | Make/Break               |

| 31  | A                 | 1E   | 9E                | 1C   | F0-1C                    | 1C   | Typematic                |

| 32  | S                 | 1F   | 9F                | 1B   | F0-1B                    | 1B   | Typematic                |

| 33  | D                 | 20   | A0                | 23   | F0-23                    | 23   | Typematic                |

| 34  | F                 | 21   | A1                | 2B   | F0-2B                    | 2B   | Typematic                |

| 35  | G                 | 22   | A2                | 34   | F0-34                    | 34   | Typematic                |

APPENDIX I. KEY NUMBERS AND THEIR CORRESPONDING MAKE/BREAK CODES FOR ALL THREE CODE SETS

|      | and (XT and PS/2 30) (AT and PS/ |       | able II<br>S/2 50, 60, 80) | Table III<br>(Terminal MODE) |          |      |            |

|------|----------------------------------|-------|----------------------------|------------------------------|----------|------|------------|

| S    | ymbol                            | Make  | Break                      | Make                         | Break    | Code | Туре       |

| 36   | н                                | 23    | A3                         | 33                           | F0-33    | 33   | Typematic  |

| 37   | J                                | 24    | A4                         | 3B                           | F0-3B    | 3B   | Typematic  |

| 38   | к                                | 25    | A5                         | 42                           | F0-42    | 42   | Typematic  |

| 39   | L                                | 26    | A6                         | 4B                           | F0-4B    | 4B   | Typematic  |

| 40   | : ;                              | 27    | A7                         | 4C                           | F0-4C    | 4C   | Typematic  |

| 41   |                                  | 28    | A8                         | 52                           | F0-52    | 52   | Typematic  |

| 42** |                                  | 2B    | AB                         | 5D                           | F0-5D    | 53   | Typematic  |

| 43   | Enter (L)                        | 1C    | 9C                         | 5A                           | F0-5A    | 5A   | Typematic  |

| 44   | Shift (L)                        | 2A    | AA                         | 12                           | F0-12    | 12   | Typematic  |

| 45** | Macro                            | 56    | D6                         | 61                           | F0-61    | 13   | Typematic  |

| 46   | Z                                | 2C    | AC                         | 1A                           | F0-1A    | 1A   | Typematic  |

| 47   | x                                | 2D    | AD                         | 22                           | F0-22    | 22   | Typematic  |

| 48   | С                                | 2E    | AE                         | 21                           | F0-21    | 21   | Typematic  |

| 49   | V                                | 2F    | AF                         | 2A                           | F0-2A    | 2A   | Typematic  |

| 50   | В                                | 30    | B0                         | 32                           | F0-32    | 32   | Typematic  |

| 51   | N                                | 31    | B1                         | 31                           | F0-31    | 31   | Typematic  |

| 52   | М                                | 32    | B2                         | 3A                           | F0-3A    | ЗA   | Typematic  |

| 53   | < ,                              | 33    | B3                         | 41                           | F0-41    | 41   | Typematic  |

| 54   | > .                              | 34    | B4                         | 49                           | F0-49    | 49   | Typematic  |

| 55   | ? /                              | 35    | B5                         | 4A                           | F0-4A    | 4A   | Typematic  |

| 57   | Shift (R)                        | 36    | B6                         | 59                           | F0-59    | 59   | Make/Breal |

| 58   | Ctrl (L)                         | 1D    | 9D                         | 14                           | F0-14    | 11   | Make/Breal |

| 60   | Alt (L)                          | 38    | B8                         | 11                           | F0-11    | 19   | Make/Breal |

| 61   | Space                            | 39    | B9                         | 29                           | F0-29    | 29   | Typematic  |

| 62   | Alt (R)                          | E0-38 | E0-B8                      | E0-11                        | E0-F0-11 | 39   | Make       |

| 64   | Ctrl (R)                         | E0-1D | E0-9D                      | E0-14                        | E0-F0-14 | 58   | Make       |

| 90   | Num Lk                           | 45    | C5                         | 77                           | F0-77    | 76   | Make       |

| 91   | 7 Home                           | 47    | C7                         | 6C                           | F0-6C    | 6C   | Make       |

| 92   | 4 ←                              | 4B    | СВ                         | 6B                           | F0-6B    | 6B   | Make       |

| 93   | 1 End                            | 4F    | CF                         | 69                           | F0-69    | 69   | Make       |

| 96   | 8 ↑                              | 48    | C8                         | 75                           | F0-75    | 75   | Make       |

| 97   | 5                                | 4C    | CC                         | 73                           | F0-73    | 73   | Make       |

| 98   | 2 ↓                              | 50    | D0                         | 72                           | F0-72    | 72   | Make       |

| 99   | 0 Ins                            | 52    | D2                         | 70                           | F0-70    | 70   | Make       |

| 100  | *                                | 37    | B7                         | 7C                           | F0-7C    | 7E   | Make       |

\*\*102-Keyboard only

| Key Position<br>and |                 | Table I<br>(XT and PS/2 30) |       |       | Table II<br>(AT and PS/2 50, 60, 80) |      | Table III<br>(Terminal MODE) |  |

|---------------------|-----------------|-----------------------------|-------|-------|--------------------------------------|------|------------------------------|--|

| S                   | ymbol           | Make                        | Break | Make  | Break                                | Code | Туре                         |  |

| 101                 | 9 Pg UP         | 49                          | C9    | 7D    | F0-7D                                | 7D   | Make                         |  |

| 102                 | $6 \rightarrow$ | 4D                          | CD    | 74    | F0-74                                | 74   | Make                         |  |

| 103                 | 3 Pg DN         | 51                          | D1    | 7A    | F0-7A                                | 7A   | Make                         |  |

| 104                 | Del             | 53                          | D3    | 71    | F0-71                                | 71   | Make                         |  |

| 105                 | -               | 4A                          | CA    | 7B    | F0-7B                                | 84   | Make                         |  |

| 106                 | +               | 4E                          | CE    | 79    | F0-79                                | 7C   | Make                         |  |

| 108                 | Enter           | E0-1C                       | E0-9C | E0-5A | E0-F0-5A                             | 79   | Typemati                     |  |

| 110                 | Esc             | 01                          | 81    | 76    | F0-76                                | 08   | Make                         |  |

| 112                 | F1              | 3B                          | BB    | 05    | F0-05                                | 07   | Make                         |  |

| 113                 | F2              | 3C                          | BC    | 06    | F0-06                                | 0F   | Make                         |  |

| 114                 | F3              | 3D                          | BD    | 04    | F0-04                                | 17   | Make                         |  |

| 115                 | F4              | 3E                          | BE    | 0C    | F0-0C                                | 1F   | Make                         |  |

| 116                 | F5              | 3F                          | BF    | 03    | F0-03                                | 27   | Make                         |  |

| 117                 | F6              | 40                          | C0    | 0B    | F0-0B                                | 2F   | Make                         |  |

| 118                 | F7              | 41                          | C1    | 83    | F0-83                                | 37   | Make                         |  |

| 119                 | F8              | 42                          | C2    | 0A    | F0-0A                                | 3F   | Make                         |  |

| 120                 | F9              | 43                          | C3    | 01    | F0-01                                | 47   | Make                         |  |

| 121                 | F10             | 44                          | C4    | 09    | F0-09                                | 4F   | Make                         |  |

| 122                 | F11             | 57                          | D7    | 78    | F0-78                                | 56   | Make                         |  |

| 123                 | F12             | 58                          | D8    | 07    | F0-07                                | 5E   | Make                         |  |

| 125                 | Scr Lk          | 46                          | C6    | 7E    | F0-7E                                | 5F   | Make                         |  |

| Key Position<br>and<br>Symbol |                                                                                          | Cu                          | Table III |       |                            |                 |           |

|-------------------------------|------------------------------------------------------------------------------------------|-----------------------------|-----------|-------|----------------------------|-----------------|-----------|

|                               |                                                                                          | Table I<br>(XT and PS/2 30) |           |       | ıble II<br>S/2 50, 60, 80) | (Terminal Mode) |           |

|                               |                                                                                          | Make                        | Break     | Make  | Break                      | Code            | Туре      |

| 75                            | Insert                                                                                   | E0-52                       | E0-D2     | E0-70 | E0-F0-70                   | 67              | Make      |

| 76                            | Delete                                                                                   | E0-53                       | E0-D3     | E0-71 | E0-F0-71                   | 64              | Typematic |

| 79                            | ←                                                                                        | E0-4B                       | E0-CB     | E0-6B | E0-F0-6B                   | 61              | Typematic |

| 80                            | Home                                                                                     | E0-47                       | E0-C7     | E0-6C | E0-F0-6C                   | 6E              | Make      |

| 81                            | End                                                                                      | E0-4F                       | E0-CF     | E0-69 | E0-F0-69                   | 65              | Make      |

| 83                            | <b>↑</b>                                                                                 | E0-48                       | E0-C8     | E0-75 | E0-F0-75                   | 63              | Typematic |

| 84                            | $\downarrow$                                                                             | E0-50                       | E0-D0     | E0-72 | E0-F0-72                   | 60              | Typematic |

| 85                            | PG UP                                                                                    | E0-49                       | E0-C9     | E0-7D | E0-F0-7D                   | 6F              | Make      |

| 86                            | PG DN                                                                                    | E0-51                       | E0-D1     | E0-7A | E0-F0-7A                   | 6D              | Make      |

| 89                            | $\rightarrow$                                                                            | E0-4D                       | E0-CD     | E0-74 | E0-F0-74                   | 6A              | Typematic |

|                               | r Pad Key— <num l<br="">Nake Code == E0-</num>                                           |                             |           |       |                            |                 |           |

| В                             | reak Code == Brea                                                                        | ak Code-E0-AA               |           |       |                            |                 |           |

| Table II: I                   | Make Code == E0-                                                                         | 12-Make Code                |           |       |                            |                 |           |

| E                             | Break Code == Brea                                                                       | ak Code E0-F0-12            |           |       |                            |                 |           |

|                               | r Pad Key— <num l<="" td=""><td></td><td></td><td></td><td></td><td></td><td></td></num> |                             |           |       |                            |                 |           |

|                               | Nake Code = E0-AA<br>reak Code = Break                                                   |                             |           |       |                            |                 |           |

| Table II: I                   | Make Code = E0-F0                                                                        | 0-12-Make Code              |           |       |                            |                 |           |

| E                             | Break Code = Break                                                                       | Code E0-12                  |           |       |                            |                 |           |

|                             |                             | TABLE I. XT ar     | nd PS/2 30      |                           |                        |

|-----------------------------|-----------------------------|--------------------|-----------------|---------------------------|------------------------|

|                             | Key Position<br>and Symbols | Ма                 | ke              |                           | Break                  |

| 126                         | Pause                       | E1-1D-45-          | -E1-9D-C5       | No E                      | Break Code (Make Only) |

|                             | Ctrl-"Pause"                | E0-46-             | -E0-C6          | No E                      | Break Code (Make Only) |

| 124                         | Print Screen                | E0-2A-             | -E0-37          |                           | E0-B7-E0-AA            |

|                             | Shift-"PRTSC"               | E0-                | -37             |                           | E0-B7                  |

|                             | Ctrl-"PRTSC"                | E0-                | -37             |                           | E0-B7                  |

|                             | Alt-"PRTSC"                 | 5                  | 4               |                           | D4                     |

| 95                          | /                           | E0-                | -35             |                           | E0-B5                  |

|                             | Shift-"/"                   | E0-AA-             | -E0-35          | E0-B5-E0-2A               |                        |

|                             |                             | TABLE II. AT and F | PS/2 50, 60, 80 |                           |                        |

| Key Position<br>and Symbols |                             | Mak                | (e              | Break                     |                        |

| 126                         | Pause                       | E1-14-77-E1-       | F0-14-F0-77     | No                        | Break Code (Make Only) |

|                             | Ctrl-"Pause"                | E0-7E-E0-F0-7E     |                 | No Break Code (Make Only) |                        |

| 124                         | Print Screen                | E0-12-E0-7C        |                 | E0-F0-7C-E0-F0-12         |                        |

|                             | Shift-"PRTSC"               | E0-7C              |                 | E0-F0-7C                  |                        |

|                             | Ctrl-"PRTSC"                | E0-                | 7C              |                           | E0-F0-7C               |

|                             | Alt-"PRTSC"                 | 84                 | ļ               |                           | F0-84                  |

| 95                          | 1                           | E0-                | 4A              |                           | E0-F0-4A               |

|                             | Shift-"/"                   | E0-F0-12           | E-E0-4A         |                           | E0-F0-4A-E0-12         |

|                             |                             | TABLE III. Tern    | ninal Mode      |                           |                        |

|                             | Key Position and Sym        | bols               | Code            |                           | Туре                   |

| 126                         | 6 P                         | ause               | 62              |                           | Make                   |

| 124                         | 4 P                         | rint Screen        | 57              |                           | Make                   |

| 95 /                        |                             |                    | 77              |                           | Make                   |

# **APPENDIX II. REFERENCES**

1. IBM Technical Reference Manuals XT, AT and PS/2

2. Chicony, Chicony Keyboards General Specification, 1988

C' T Magazin fuer Computertechnik, No. 6, 1988, pages 148ff. No. 7, 1988, pages 178ff. Martin Gerdes, "Knoepfchen, Knoepfchen"

# LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| 0 | National Semiconductor<br>Corporation<br>2900 Semiconductor Drive<br>P.O. Box 58090<br>Santa Clara, CA 95052-8090<br>Tel: 1(800) 272-9959<br>Tel: 100) 272-9959<br>TWX: (910) 339-9240 | National Semiconductor<br>GmbH<br>Livry-Gargan-Str. 10<br>D-82256 Fürstenfeldbruck<br>Germany<br>Tel: (81-41) 35-0<br>Telex: 527649<br>Ener (61 41) 95 5 | Chiba-City,                                                       | Tel: (852) 2737-1600 | National Semiconductores<br>Do Brazil Ltda.<br>Rue Deputado Lacorda Franco<br>120-3A<br>Sao Paulo-SP<br>Brazil 05418-000<br>Tel: (55-11) 212-2066<br>Tel: (55-11) 212-2066 | National Semiconductor<br>(Australia) Pty, Ltd.<br>Building 16<br>Business Park Drive<br>Monash Business Park<br>Nottinghill, Melbourne<br>Victoria 3168 Australia |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                                                                                        | Fax: (81-41) 35-1                                                                                                                                        | Ciba Prefecture 261<br>Tel: (043) 299-2300<br>Fax: (043) 299-2500 | Fax: (852) 2736-9960 | Telex: 391-1131931 NSBR BR<br>Fax: (55-11) 212-1181                                                                                                                        | Tel: (3) 558-9999<br>Fax: (3) 558-9998                                                                                                                             |

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

**AN-734**